# **Evaluating Techniques for Wireless Interconnected 3D Processor Arrays**

Amir Mansoor Kamali Sarvestani

PhD

University of York

Department of Computer Science

September 2013

#### **Abstract**

In this thesis the viability of a wireless interconnect network for a highly parallel computer is investigated. The main theme of this thesis is to project the performance of a wireless network used to connect the processors in a parallel machine of such design. This thesis is going to investigate new design opportunities a wireless interconnect network can offer for parallel computing.

A simulation environment is designed and implemented to carry out the tests. The results have shown that if the available radio spectrum is shared effectively between building blocks of the parallel machine, there are substantial chances to achieve high processor utilisation. The results show that some factors play a major role in the performance of such a machine. The size of the machine, the size of the problem and the communication and computation capabilities of each element of the machine are among those factors. The results show these factors set a limit on the number of nodes engaged in some classes of tasks. They have shown promising potential for further expansion and evolution of our idea to new architectural opportunities, which is discussed by the end of this thesis.

To build a real machine of this type the architects would need to solve a number of challenging problems including heat dissipation, delivering electric power and Chip/board design; however, these issues are not part of this thesis and will be tackled in future.

# **Table of Contents**

| Abstract                                                     | 2  |

|--------------------------------------------------------------|----|

| Table of Contents                                            | 3  |

| List of Figures                                              | 7  |

| List of Tables                                               | 11 |

| List of Algorithms                                           | 13 |

| Acknowledgments                                              | 14 |

| Declaration                                                  | 16 |

| Chapter 1) Introduction                                      |    |

| 1.2) Motivation                                              | 23 |

| 1.3) Main Contributions                                      | 27 |

| 1.4) Organisation                                            | 31 |

| Chapter 2) Literature Review                                 |    |

| 2.2) Network Topologies                                      | 37 |

| 2.2.1) Network Properties and Performance Metrics            | 39 |

| 2.2.2) Fat Tree and Hypertree                                | 40 |

| 2.2.3) Butterfly                                             | 41 |

| 2.2.4) Dragonfly                                             | 43 |

| 2.2.5) Mesh, Torus and Hypercube                             | 45 |

| 2.2.5) Infiniband                                            | 46 |

| 2.2.6) Blue Gene/Q                                           | 49 |

| 2.2.7) Network Topology Comparison                           | 50 |

| 2.3) Routing Algorithms                                      | 52 |

| 2.3.1) Store-And-Forward                                     | 52 |

| 2.3.2) Cut-Through                                           | 53 |

| 2.3.3) Wormhole                                              | 54 |

| 2.4) Parallel programming Models                             | 55 |

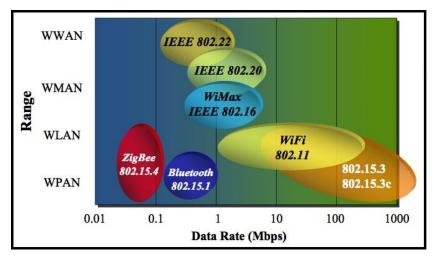

| 2.5) Wireless Communication                                  | 57 |

| 2.5.1) IEEE Wireless Protocols                               | 57 |

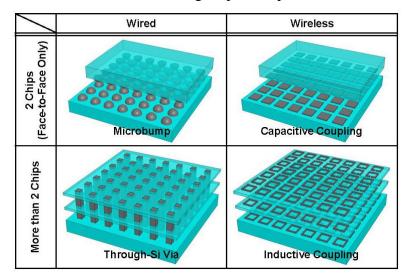

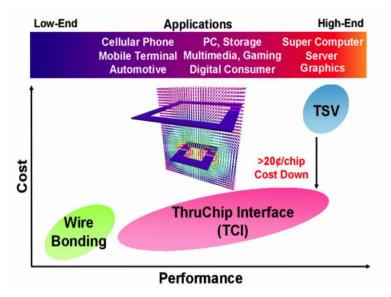

| 2.5.2) Inter-chip 3D Network of processors                   | 59 |

| 2.5.3) On-chip Short-Range High-Speed wireless communication | 62 |

| 2.5.4) Multi-Channel Communication                           | 68 |

| 2.6) Packet Collision in Wireline and Wireless Networks      | 68 |

| 2.7) Network-partitioning                                    | 71 |

|    | 2.8) Deadlock Detection/Avoidance/Recovery                                 | 74  |

|----|----------------------------------------------------------------------------|-----|

|    | 2.8.1) Deadlock Conditions                                                 | 75  |

|    | 2.8.2) Deadlock Detection                                                  | 75  |

|    | 2.8.3) Deadlock Prevention                                                 | 75  |

|    | 2.8.4) Deadlock Avoidance                                                  | 76  |

|    | 2.9) Network Simulation tools                                              | 77  |

|    | 2.9.1) NS Family                                                           | 77  |

|    | 2.9.2) OPNET                                                               | 78  |

|    | 2.9.3) NetSim                                                              | 78  |

|    | 2.10) Some Related Works                                                   | 79  |

|    | 2.10.1) SpiNNaker                                                          | 79  |

|    | 2.10.2) Amorphous computing                                                | 80  |

|    | 2.10.3) Multicore Processors                                               | 82  |

|    | 2.10.4) Net-X                                                              | 85  |

|    | 2.11) Summary                                                              | 85  |

| Cl | hapter 3: Hypothesis and Rationale                                         |     |

|    | 3.2) Ball Computer                                                         | 88  |

|    | 3.3) Data Communication Rate                                               | 90  |

|    | 3.4) Communication Distance                                                | 92  |

|    | 3.5) Power Consumption                                                     | 92  |

|    | 3.6) Occupied Area                                                         | 99  |

|    | 3.7) Locality of Communication                                             | 100 |

|    | 3.8) Buffer Management, Routing, Deadlock Avoidance                        | 101 |

|    | 3.9) Summary                                                               | 103 |

| Cl | hapter 4: Communication Media and Network Topology4.1) Communication Media |     |

|    | 4.2) Radio Modules per Node                                                | 105 |

|    | 4.3) Hexagonal topology                                                    | 107 |

|    | 4.4) Performance Metrics                                                   | 110 |

| Cl | hapter 5: Network-partitioning                                             |     |

|    | 5.2) Network-partitioning Criteria                                         | 112 |

|    | 5.2) Network-partitioning Criteria                                         | 112 |

|    | 5.3) Zoning; Proposed Algorithm                                            |     |

|    |                                                                            | 113 |

| 5.6) Summary                                                                      | 124 |

|-----------------------------------------------------------------------------------|-----|

| Chapter 6: Task-modelling                                                         |     |

| 6.2) A Simple Parallel Task-model (SPTM)                                          | 129 |

| 6.3) A Highly Dependent Task-model                                                | 131 |

| 6.4) Modified FFTTM                                                               | 133 |

| 6.5) Summary                                                                      | 138 |

| Chapter 7: Simulation and Visualisation Tools                                     |     |

| 7.1.1) Choice of Simulation tool                                                  | 140 |

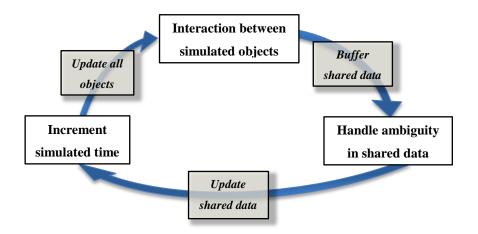

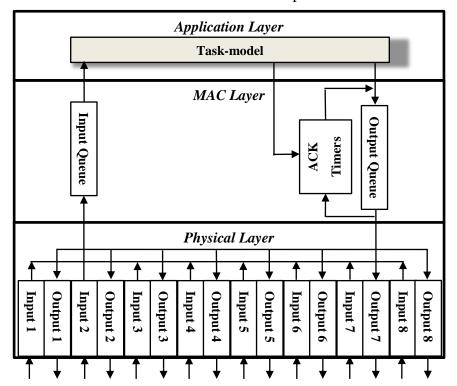

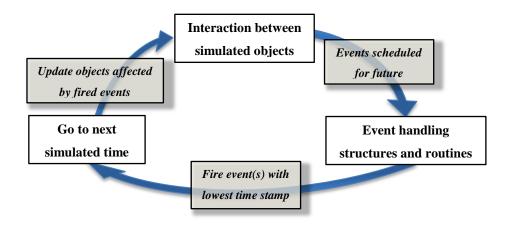

| 7.1.2) Discrete Time Simulator vs. Discrete Event Simulator                       | 141 |

| 7.1.3) Network Partitioning and Channel Assignment                                | 150 |

| 7.1.4) Independent Channel Objects                                                | 151 |

| 7.1.5) Decentralised Simulation platform                                          | 153 |

| 7.1.6) Multi-part packet delivery                                                 | 154 |

| 7.1.7) Buffer Management Strategy and Deadlock Avoidance                          | 156 |

| 7.2) Visualisation tools                                                          | 159 |

| 7.2.1) Process Visualisation                                                      | 159 |

| 7.2.2) Results Visualisation                                                      | 161 |

| Chapter 8: Primary Network Optimisation                                           |     |

| 8.2) Hidden Node Problem and Packet Collision                                     | 163 |

| 8.3) Cubic Networks vs. Spherical Networks                                        | 164 |

| 8.4) Multi-Tasking and Multiple Workloads                                         | 166 |

| 8.5) Task-model Modifications and Load Balancing                                  | 173 |

| 8.6) Tuning the Number of Branches per Node                                       | 174 |

| Chapter 9: Overall Study of the Behaviour of the Network 9.1) FFTTM on 1000 Nodes |     |

| 9.2) FFTTM on 2000 Nodes                                                          | 179 |

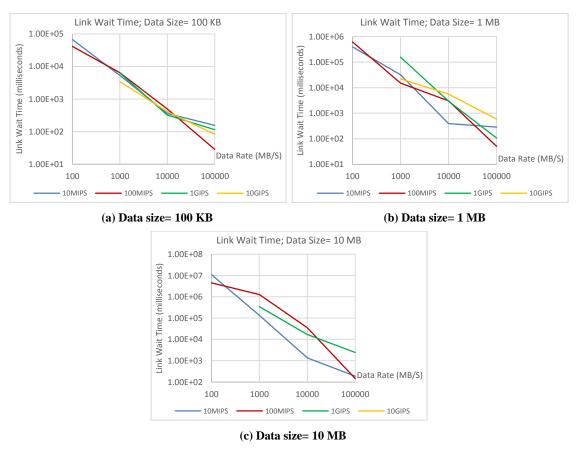

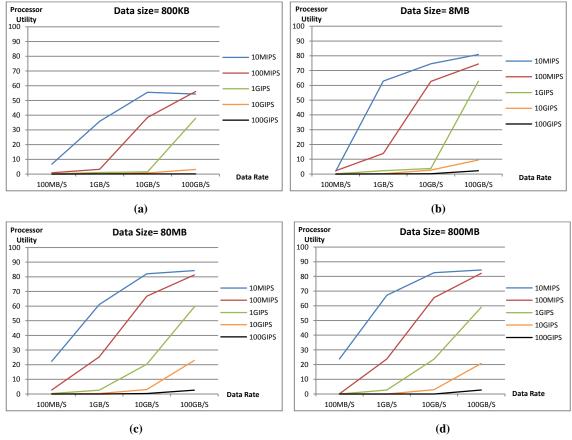

| 9.3) SPTM on 1000 Nodes                                                           | 182 |

| 9.4) SPTM on 2000 Nodes                                                           | 185 |

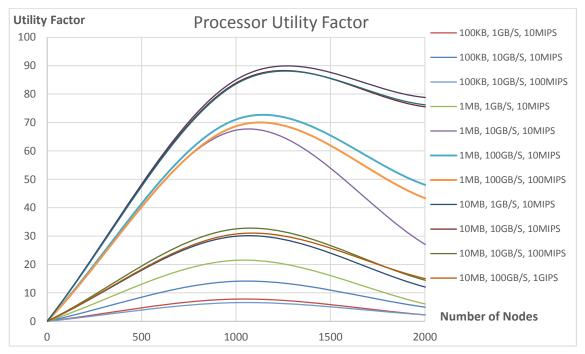

| 9.5) Network Size                                                                 | 188 |

| 9.6) Transfer Rate                                                                | 189 |

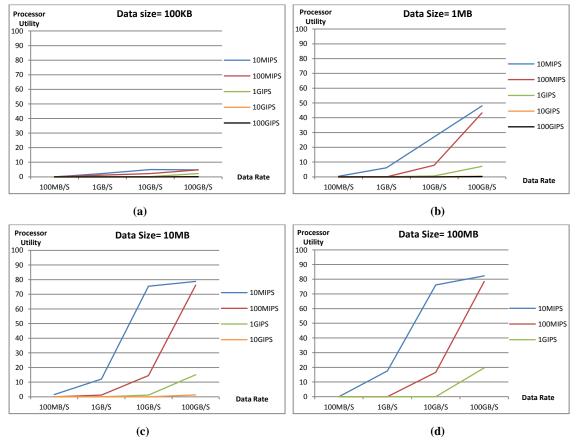

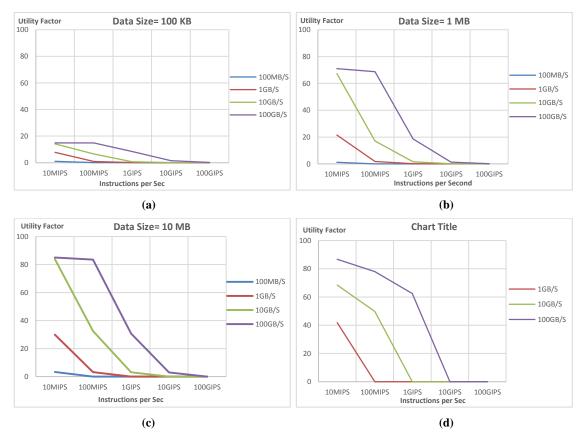

| 9.7) Computational Ability                                                        | 190 |

| 9.8) Data Size                                                                    | 192 |

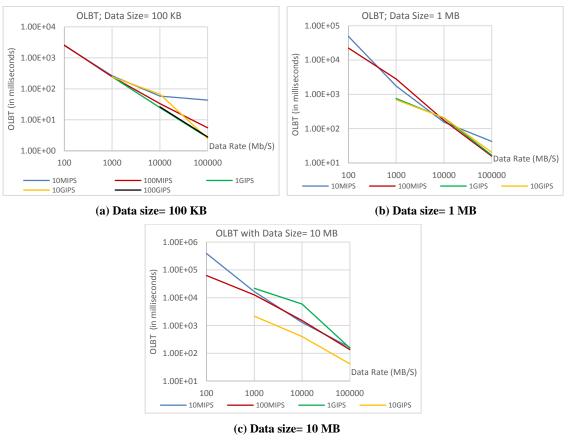

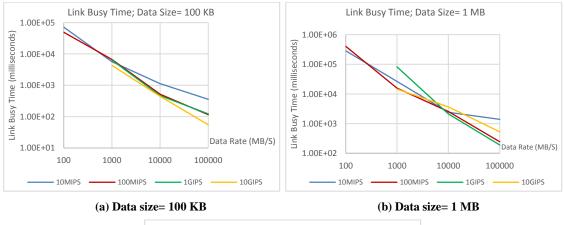

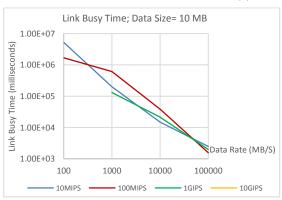

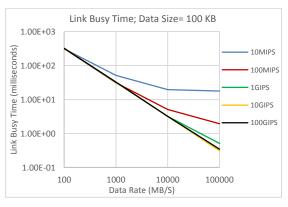

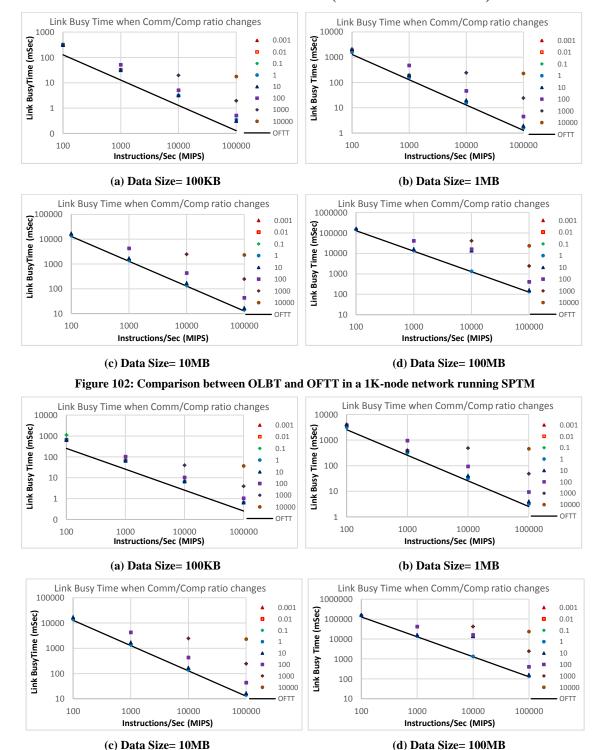

| 9.9) Link Busy Time                                                               | 193 |

| 9.10) Link Utility                                                          | 196 |

|-----------------------------------------------------------------------------|-----|

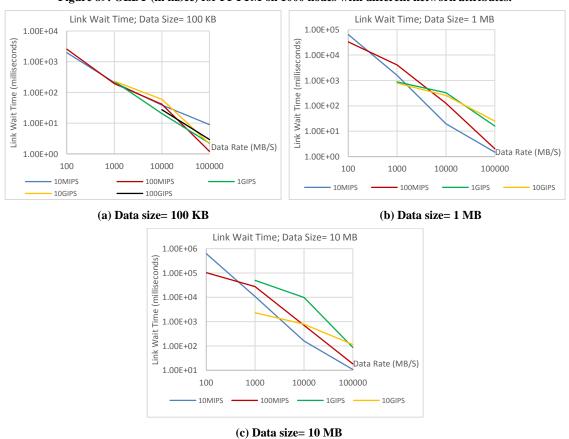

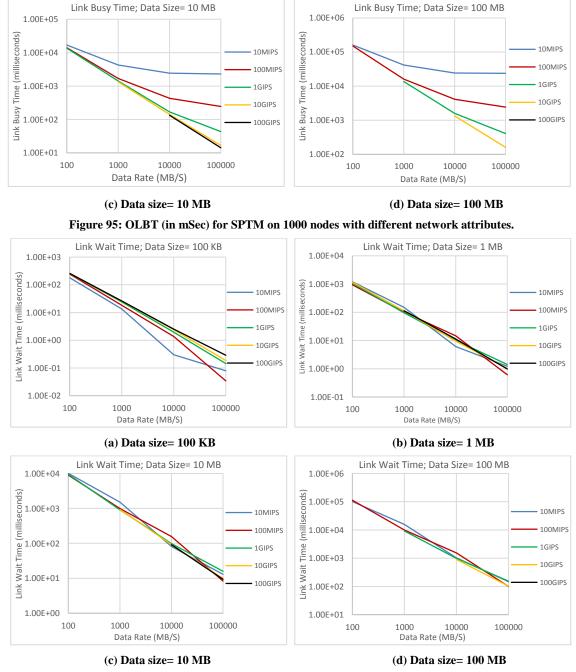

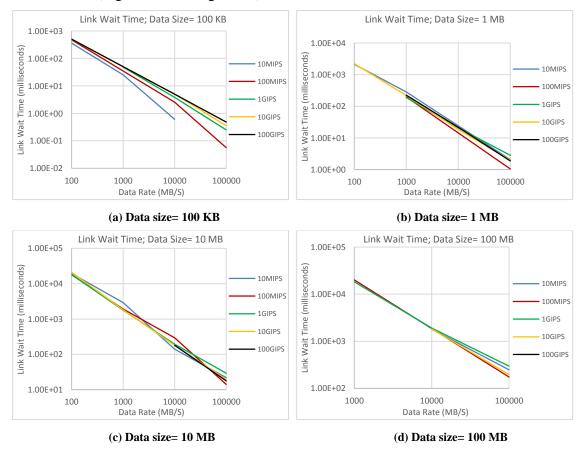

| 9.11) Link Wait Time                                                        | 198 |

| Chapter 10: Conclusion                                                      |     |

| 10.2) Packet Collision and Network Partitioning                             | 202 |

| 10.3) Routing and Deadlock Avoidance                                        | 202 |

| 10.4) Load Balancing                                                        | 203 |

| 10.5) Final Analysis                                                        | 203 |

| 10.6) Future Work                                                           | 204 |

| 10.6.1) Current Simulator                                                   | 204 |

| 10.6.2) Extending the Simulator                                             | 205 |

| 10.6.3) Beyond Simulation                                                   | 206 |

| Glossary                                                                    | 226 |

| Appendices Appendix A: Summary of short-range on-chip wireless technologies |     |

| Appendix B: More Detailed Architectural Data about Simulation               | 216 |

| Network Partitioning and Channel Assignment                                 | 216 |

| Packet Structure                                                            | 217 |

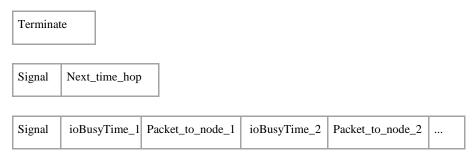

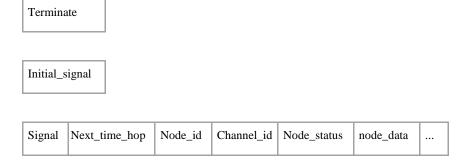

| Appendix C: More Detailed Architectural Data about a Distributed Simulation | 219 |

| From Channel to simulator                                                   | 221 |

| From Simulator to Channel                                                   | 222 |

| From Cluster to Simulator                                                   | 222 |

| From Simulator to Cluster                                                   | 222 |

| Elements of a packet                                                        | 222 |

|                                                                             |     |

| Appendix D: Details about visualisation tool log files                      | 224 |

# **List of Figures**

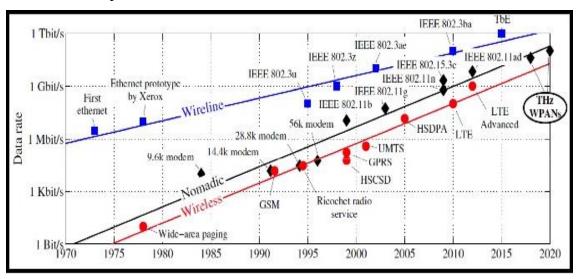

| Figure 1: Evolution of data rates in wireless                                     | 25     |

|-----------------------------------------------------------------------------------|--------|

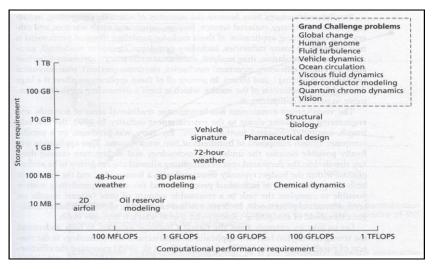

| Figure 2: Grand challenges as projected in 1999                                   | 33     |

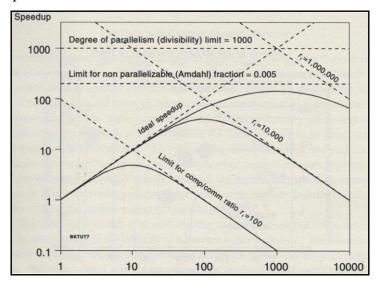

| Figure 3: Different factors limiting the speedup factor                           | 36     |

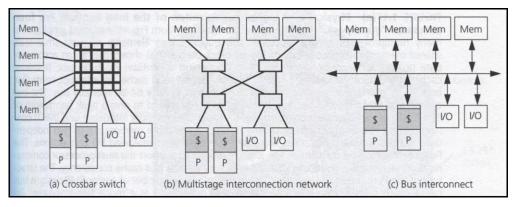

| Figure 4: Network interconnect topologies                                         | 37     |

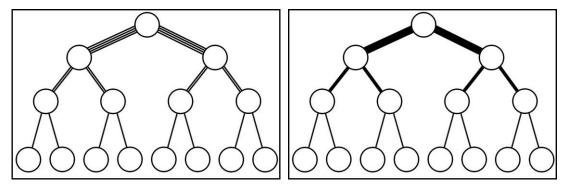

| Figure 5: Two implementations of fat trees                                        | 40     |

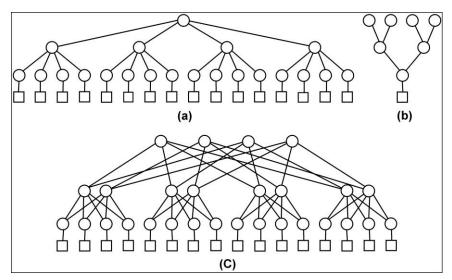

| Figure 6: (a) A k-ary tree; (b) An upside down binary tree and (c) a hypertree    | 41     |

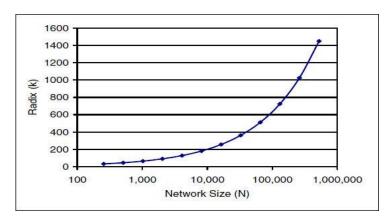

| Figure 7: "Radix (k) of the routers required to scale the network                 | 42     |

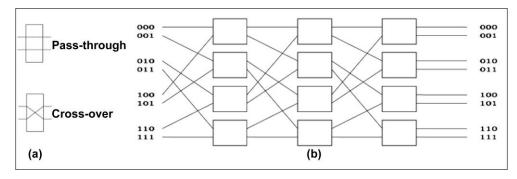

| Figure 8: (a) Two modes of a 2*2 switch; and (b) an omega network of 2*2 switches | es .43 |

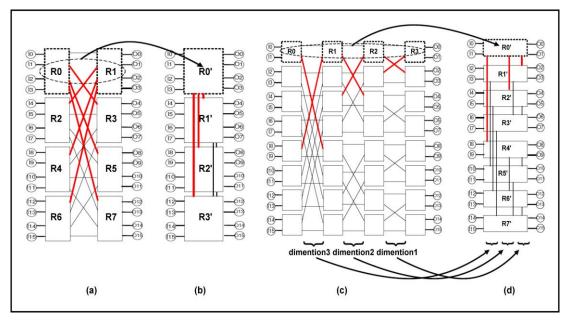

| Figure 9: Butterfly topologies (a, c) and Flattened Butterfly topologies (b, d)   | 43     |

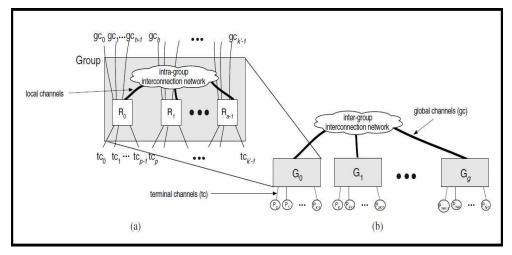

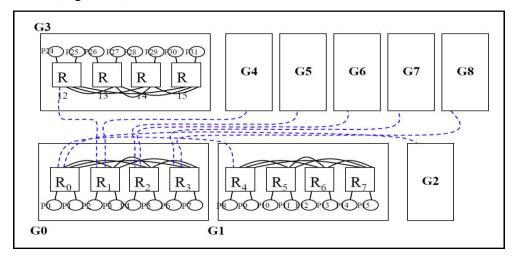

| Figure 10: (a) Diagram of a group and (b) block diagram of a Dragonfly topology.  | 44     |

| Figure 11: A sample implementation of Dragonfly topology                          | 44     |

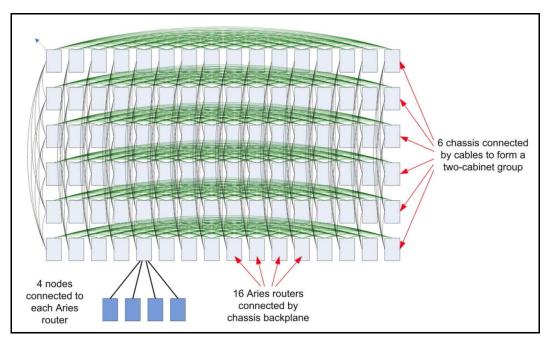

| Figure 12: Structure of a Cray XC system's electrical group                       | 45     |

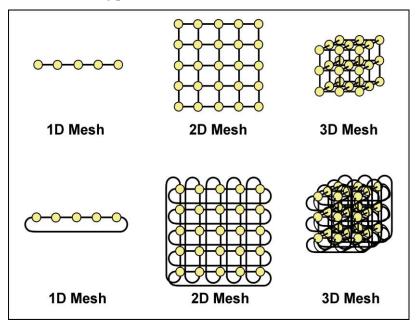

| Figure 13: Mesh and torus topologies in 1D, 2D and 3D                             | 45     |

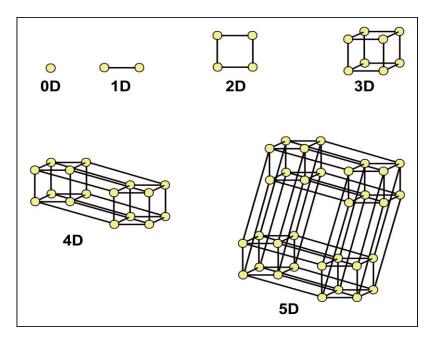

| Figure 14: Cube and hypercube topologies of dimension 0 to 5                      | 46     |

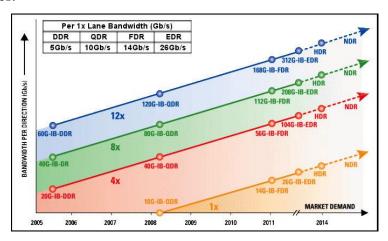

| Figure 15: IBA's current and future data rates adopted from 2010 roadmap          | 47     |

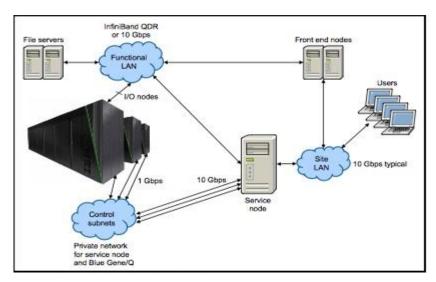

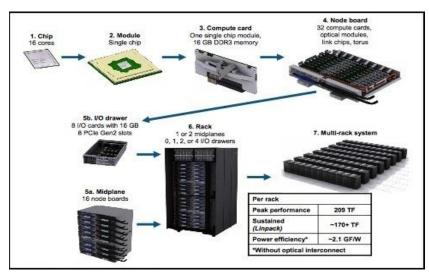

| Figure 16: IBM Blue Gene/Q system architecture                                    | 49     |

| Figure 17: Blue Gene/Q hardware overview                                          | 50     |

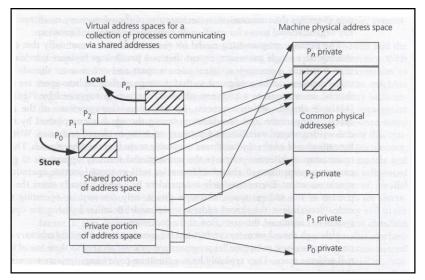

| Figure 18: Shared Memory model and its similarity to multi-threading              | 56     |

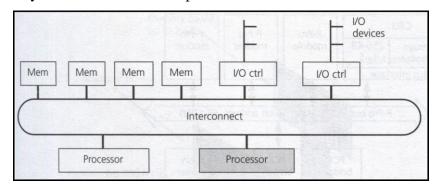

| Figure 19: An SMP architecture                                                    | 56     |

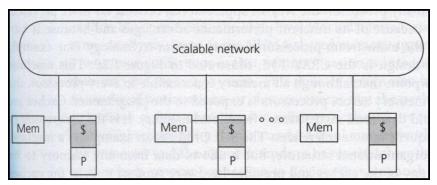

| Figure 20: A NUMA architecture                                                    | 56     |

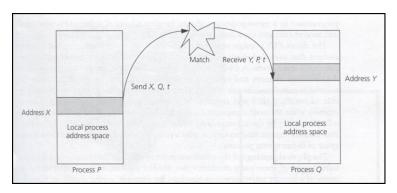

| Figure 21: A message passing communication method                                 | 57     |

| Figure 22: Comparing IEEE 802 protocols                                           | 58     |

| Figure 23: Different solutions for 3D stack of processor interfaces               | 60     |

| Figure 24: Cost/Performance Comparison between Wire Bonding, TCI and TSV          | 61     |

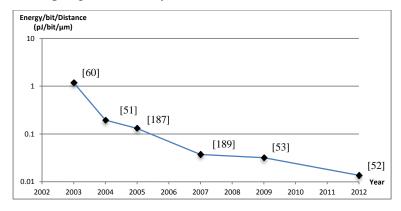

| Figure 25: The energy for sending a bit over one μm using capacitive coupling     | 63     |

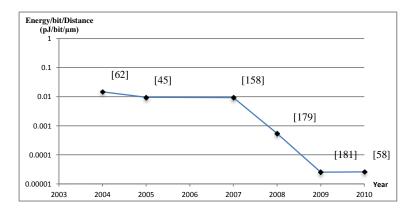

| Figure 26: The energy for sending a bit over one μm using inductive coupling      | 65     |

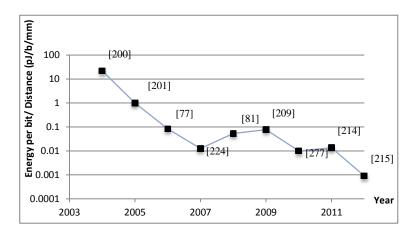

| Figure 27: The energy for sending a bit over one mm using radio waves             | 67     |

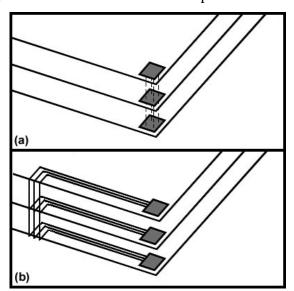

| Figure 28: Comparing the distance of links in (a) wireless and (b) wired networks | 67     |

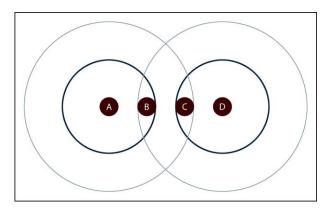

| Figure 29: Hidden node problem in wireless networks                               | 71     |

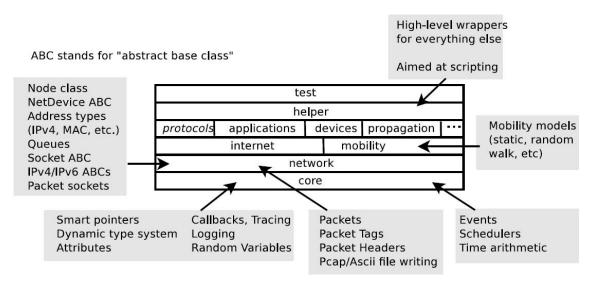

| Figure 30: Software organization of ns-3                                          | 78     |

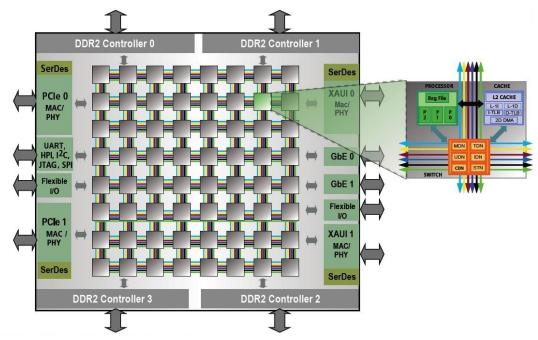

| Figure 31: Block diagram of the TILEPro64 Processor                               | 83     |

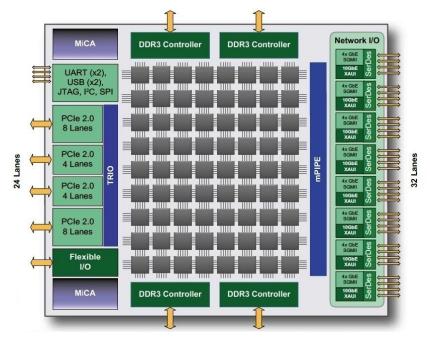

| Figure 32: Tile-Gx8072 processor block diagram                                    | 83     |

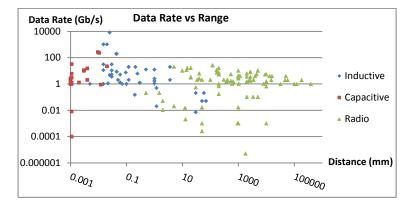

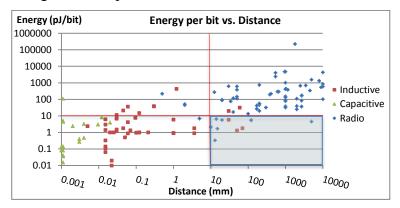

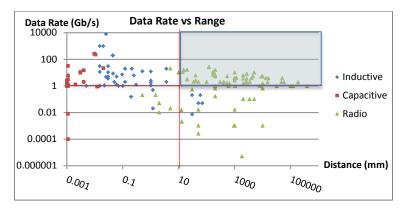

| Figure 33: Comparing wireless technologies in terms of data communication rate    | 91     |

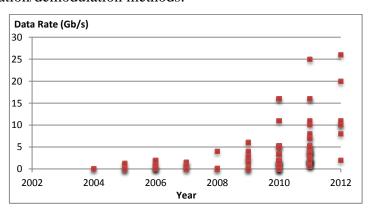

| Figure 34: Improvement of data rates in radio devices during last decade91              |

|-----------------------------------------------------------------------------------------|

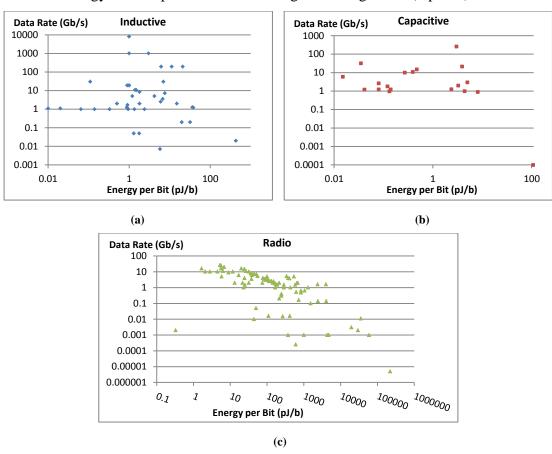

| Figure 35: Comparing data rate vs. energy per bit for (a) capacitive coupling, (b)      |

| inductive coupling and (c) radio wave technologies96                                    |

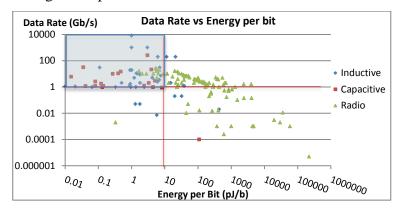

| Figure 36: Comparing wireless technologies in terms of power consumption and data       |

| rate97                                                                                  |

| Figure 37: Comparing wireless technologies in terms of power consumption and            |

| communication distance97                                                                |

| Figure 38: Comparing wireless technologies in terms of data rate and communication      |

| distance98                                                                              |

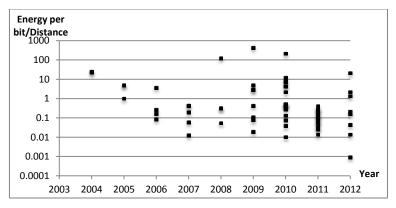

| Figure 39: Mutual improvement in range and energy per bit for radio devices98           |

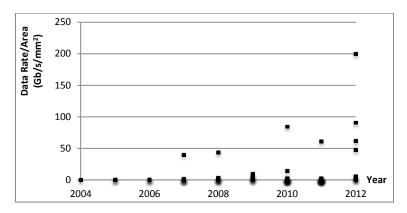

| Figure 40: Improvement in data rate and occupied area in radio devices                  |

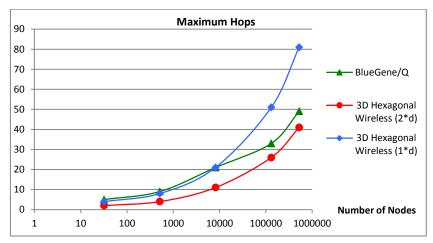

| Figure 41: Number of hops in Blue Gene/Q and Ball Computer                              |

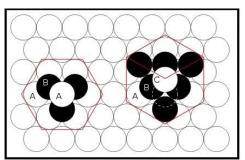

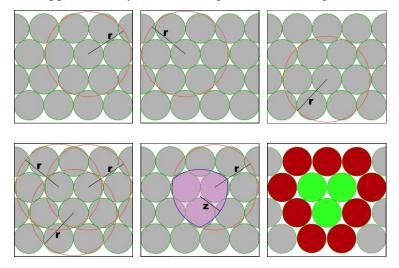

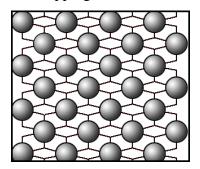

| Figure 42: HCP (left) and FCC (right) lattices                                          |

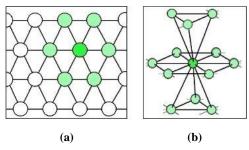

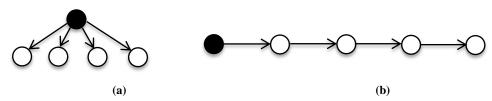

| Figure 43: The topology of a ball computer in (a) 2D and (b) 3D                         |

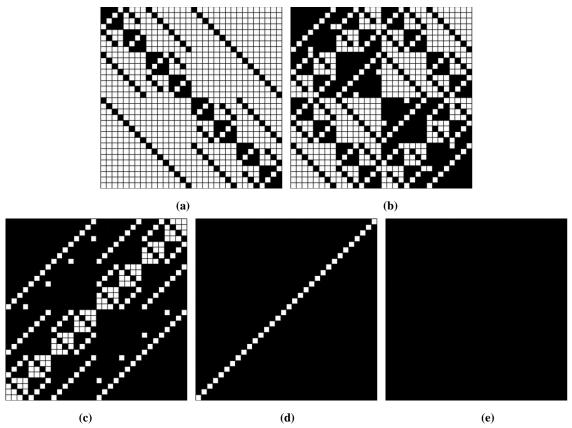

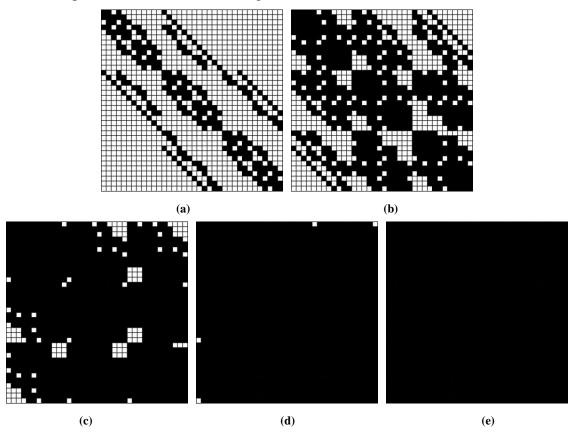

| Figure 44: Connectivity matrices of a 5D grid (2*2*2*2*2)                               |

| Figure 45: Connectivity matrices of a 3D hexagonal grid (3*3*4)                         |

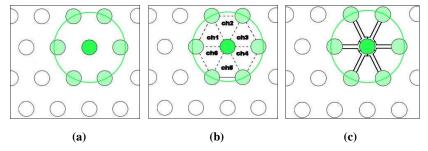

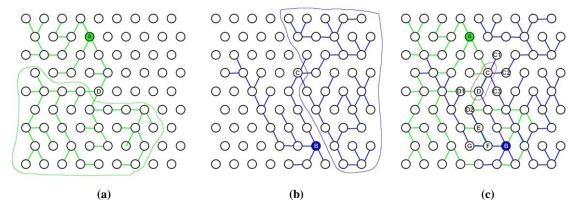

| Figure 46: The process of forming a zone                                                |

| Figure 47: (a) and (b) A central node and its zones. (c) Compared the wireless          |

| connections with their wireline equivalent                                              |

| Figure 48: A wireline equivalent of the proposed wireless network in 2D115              |

| Figure 49: A 3D grid of wireless devices and the pyramid partitions around a node 120   |

| Figure 50: Representing channel assignment as a variation of map coloring problem 123   |

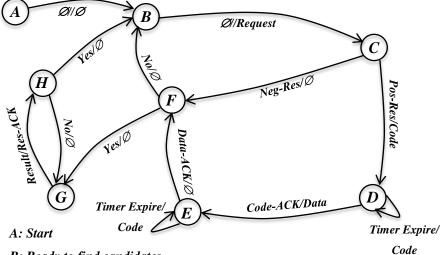

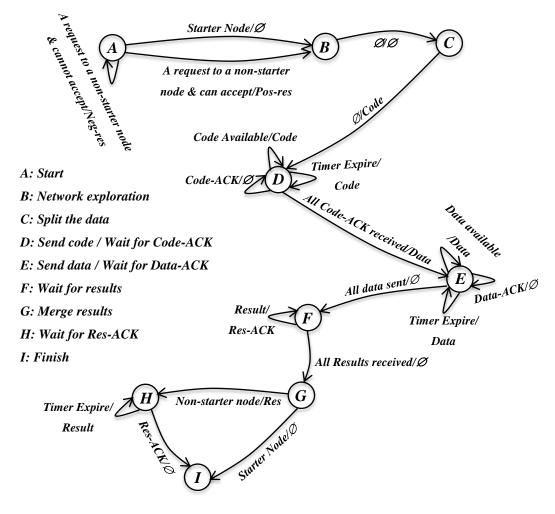

| Figure 51: State diagram of SPTM in parent node                                         |

| Figure 52: State diagram of SPTM in child node                                          |

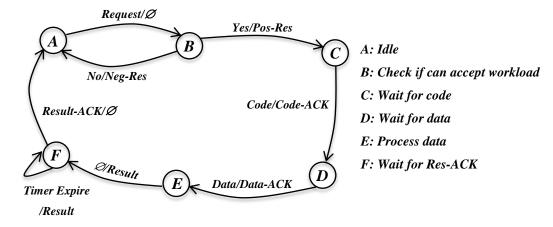

| Figure 53: State diagram of FFTTM                                                       |

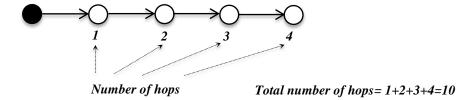

| Figure 54: Total number of hops needed to contact all nodes in a tree from the root 135 |

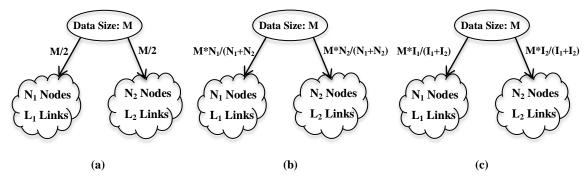

| Figure 55: Three approaches for assigning workload to sub-trees                         |

| Figure 56: Comparing the number of link traversals when the number of nodes and the     |

| number of links are equal                                                               |

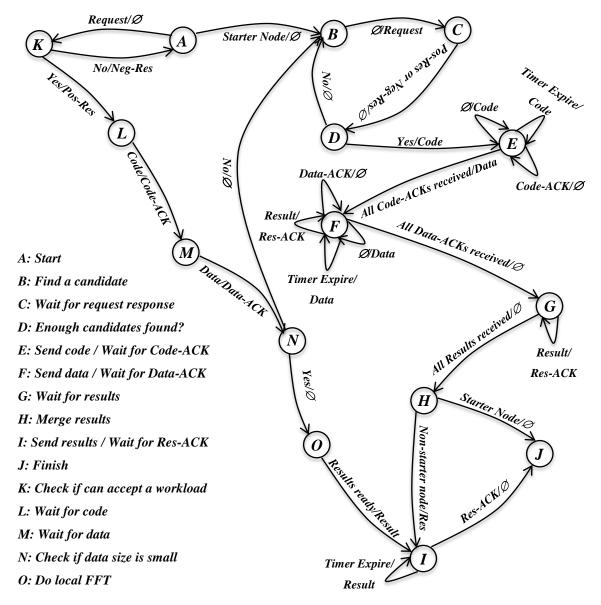

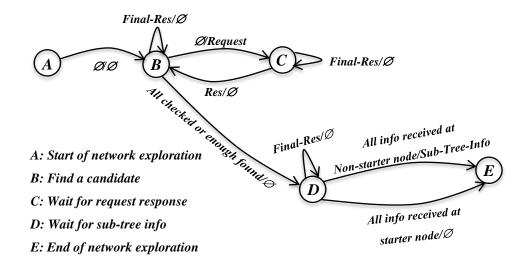

| Figure 57: State diagram of the network exploration of modified version of FFTTM.136    |

| Figure 58: State diagram of the modified version of FFTTM                               |

| Figure 59: A discrete time architecture for the first version of the simulator143       |

| Figure 60: The block diagram of the internal structure of a simulated node144           |

| Figure 61: An equivalent of the simulator with discrete event architecture              |

| Figure 62: The second version of the simulator                                          |

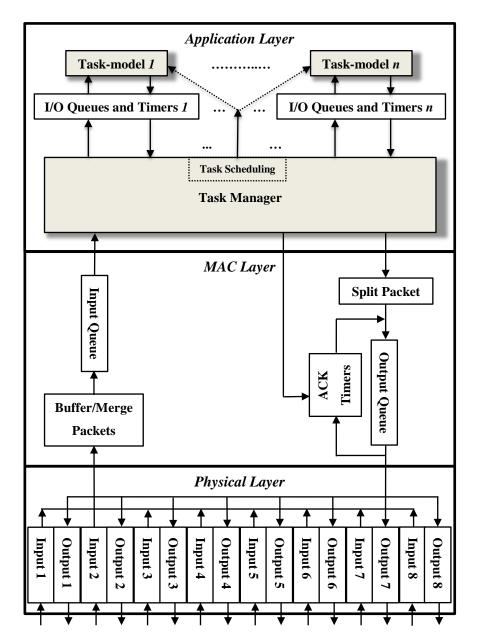

| Figure 63: The block diagram of the structure of a node with multi-tasking              |

| Figure 64: The structure of the node object after introduction of channel object | 152  |

|----------------------------------------------------------------------------------|------|

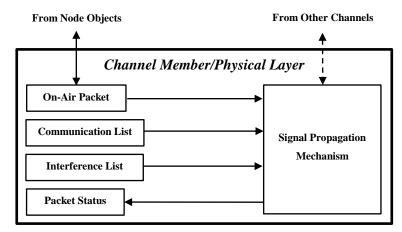

| Figure 65: The structure of the channel object                                   | 152  |

| Figure 66: The internal block diagram of a channel member node                   | 153  |

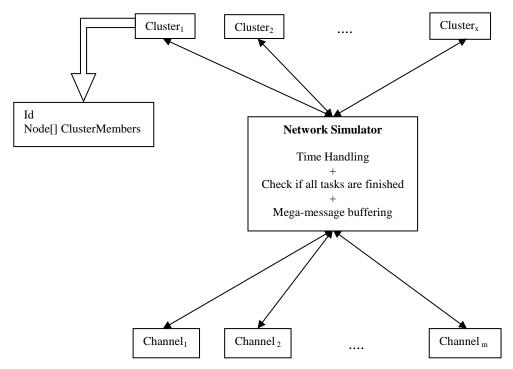

| Figure 67: Block diagram of proposed distributed simulator                       | 154  |

| Figure 68: Block diagram of a network node with split/merge mechanism            | 155  |

| Figure 69: How two separate FFTTM can contribute in forming a deadlock           | 159  |

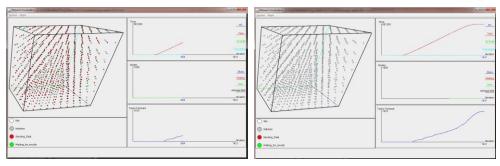

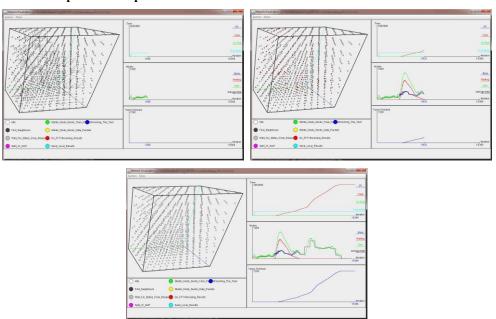

| Figure 70: Two snapshots of the process visualizer tool for an SPTM              | 160  |

| Figure 71: Three snapshot of the process visualizer tool for an FFTTM            | 160  |

| Figure 72: A snapshot of the results visualizer for a 3D 10*10*10 network        | 161  |

| Figure 73: The Processor Utility of a cubic ball computer                        | 165  |

| Figure 74: The Processor Utility of a spherical ball computer                    | 166  |

| Figure 75: Nodes involved in a single task FFTTM                                 | 167  |

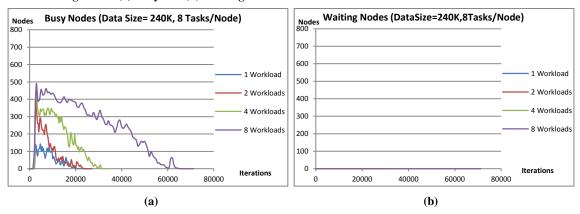

| Figure 76: Nodes involved in a multi task FFTTM                                  | 168  |

| Figure 77: Nodes involved in a set of multi-task FFTTM                           | 168  |

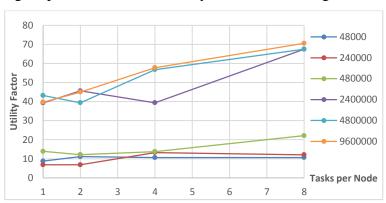

| Figure 78: The improvement of performance as the number of tasks/node increases  | s169 |

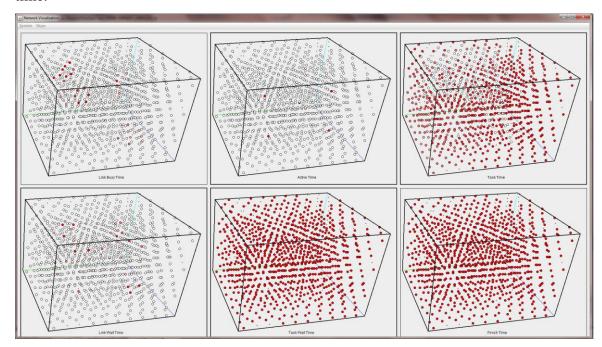

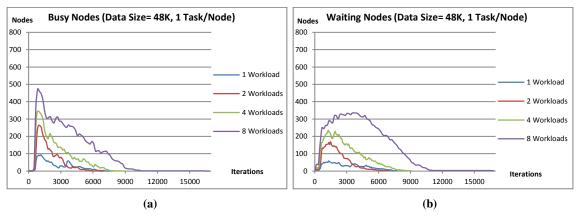

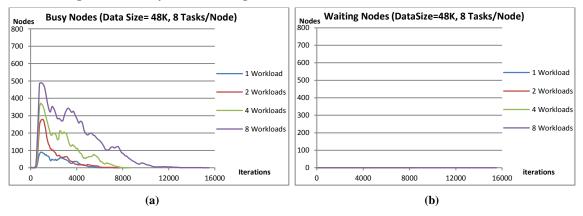

| Figure 79: (a) Busy and (b) Waiting nodes in a 48K FFTTM with 1 task/node        | 170  |

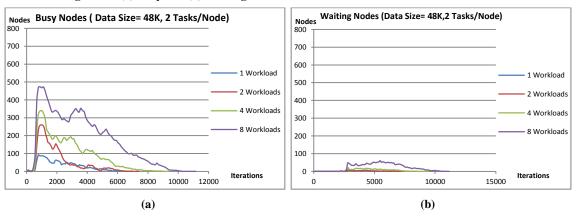

| Figure 80: (a) Busy and (b) Waiting nodes in a 48K FFTTM with 2 task/node        | 170  |

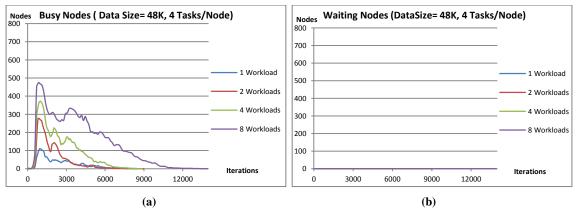

| Figure 81: (a) Busy and (b) Waiting nodes in a 48K FFTTM with 4 task/node        | 170  |

| Figure 82: (a) Busy and (b) Waiting nodes in a 48K FFTTM with 8 task/node        | 170  |

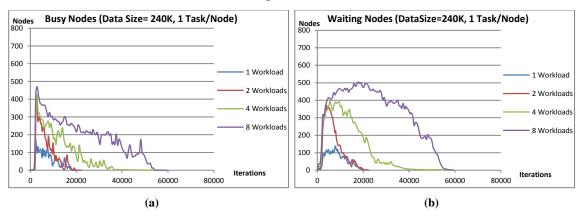

| Figure 83: (a) Busy and (b) Waiting nodes in a 240K FFTTM with 1 task/node       | 171  |

| Figure 84: (a) Busy and (b) Waiting nodes in a 240K FFTTM with 2 task/node       | 171  |

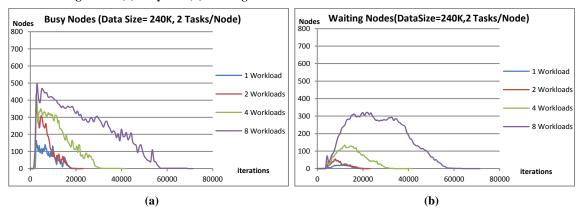

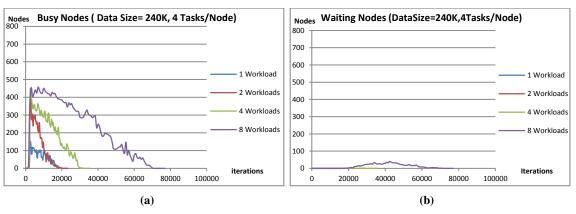

| Figure 85: (a) Busy and (b) Waiting nodes in a 240K FFTTM with 4 task/node       | 172  |

| Figure 86: (a) Busy and (b) Waiting nodes in a 240K FFTTM with 8 task/node       | 172  |

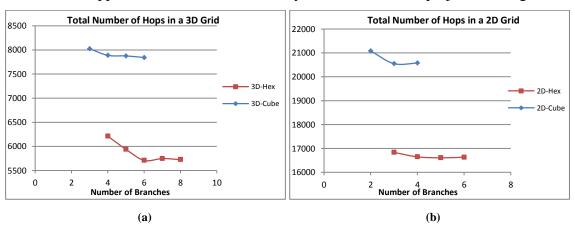

| Figure 87: Total number of hops in Hexagonal and cubic topologies                | 174  |

| Figure 88: Processor Utility (in percentage) for FFTTM on 1000 nodes             | 176  |

| Figure 89: OLBT (in mSec) for FFTTM on 1000 nodes                                | 178  |

| Figure 90: Link Wait Time (in mSec) for FFTTM on 1000 nodes                      | 178  |

| Figure 91: Processor Utility (percentage) of FFTTM on a 2000-node network        | 180  |

| Figure 92: OLBT (in mSec) for FFTTM on 2000 nodes                                | 181  |

| Figure 93: Link Wait Time (in mSec) for FFTTM on 2000 nodes                      | 182  |

| Figure 94: Processor Utility of Simple Parallel tasks on a 1000-node network     | 183  |

| Figure 95: OLBT (in mSec) for SPTM on 1000 nodes                                 | 185  |

| Figure 96: Link Wait Time (in mSec) for SPTM on 1000 nodes                       | 185  |

| Figure 97: Processor Utility of SPTM on a 2002-node network                      | 186  |

| Figure 98: OLBT (in mSec) for SPTM on 2000 nodes                                 | 188  |

| Figure 99: Link Wait Time (in mSec) for SPTM on 2000 nodes                       | 188  |

| Figure 100: The effect of network size on the performance of an FFTTM     | 189 |

|---------------------------------------------------------------------------|-----|

| Figure 101: Processor utility of a network of size 1K nodes running FFTTM | 191 |

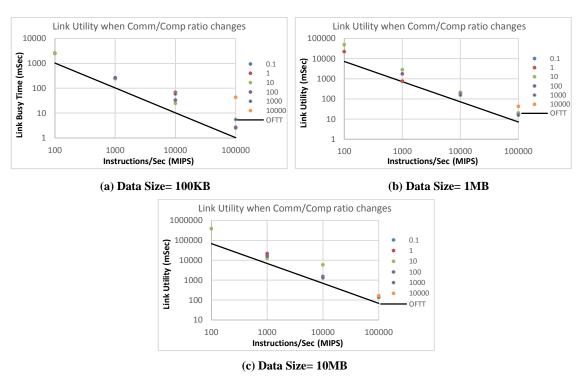

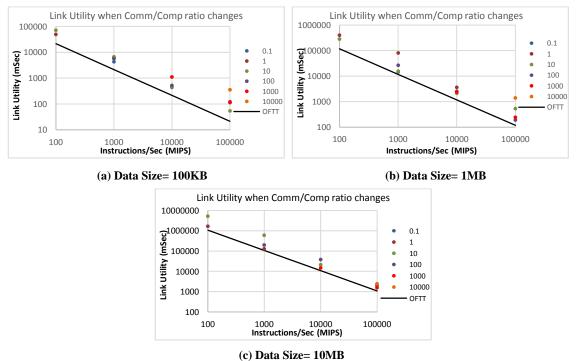

| Figure 102: Comparing OLBT and OFTT in a 1K-node network running SPTM     | 194 |

| Figure 103: Comparing OLBT and OFTT in a 2K-node network running SPTM     | 194 |

| Figure 104: Comparing OLBT and OFTT of 8 FFTTMs in a 1K-node network      | 195 |

| Figure 105: Comparing OLBT and OFTT of 8 FFTTMs in a 2K-node network      | 195 |

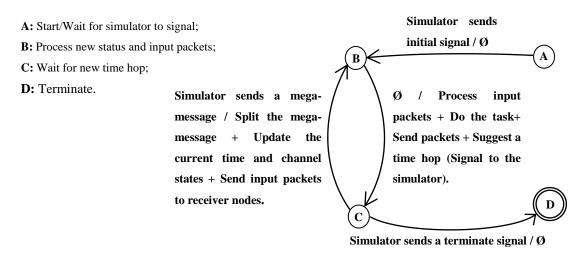

| Figure 106: Main network simulator's state diagram                        | 219 |

| Figure 107: Channel's state diagram.                                      | 221 |

| Figure 108: Node/cluster's state diagram                                  | 221 |

# **List of Tables**

| Table 1: Comparing the cost for 1GFLOPS worth of computation                      | 22   |

|-----------------------------------------------------------------------------------|------|

| Table 2: The cost of a number of most powerful parallel computers in the world    | 23   |

| Table 3: 10 most powerful supercomputers in the world                             | 38   |

| Table 4: Comparing some of the most popular HPC interconnect network topologic    | es51 |

| Table 5: The data rate and power consumption of a number of cables in Dragonfly   | 52   |

| Table 6: Adaptive switching strategy                                              | 54   |

| Table 7: 802.11 Network Standards                                                 | 59   |

| Table 8: Comparing wirelines and fibre optics in term of energy per bit           | 94   |

| Table 9: Comparison of energy consumption in copper and optic technologies        | 94   |

| Table 10: An energy consumption comparison between copper and fibre optic         | 95   |

| Table 11: A number of short-range wireline links operating under 100 cm           | 95   |

| Table 12: Candidate wireless technologies suitable for a 3D wireless grid         | 99   |

| Table 13: Comparing the maximum number of hops in Blue Gene and BC                | 100  |

| Table 14: The increase in the number of neighbours with increase in radio range   | 106  |

| Table 15: List of packets in SPTM protocol.                                       | 130  |

| Table 16: List of packets in FFTTM protocol                                       | 133  |

| Table 17: List of packet types in FFTTM with load balancing protocol              | 137  |

| Table 18: Packet collision in a 2D hex. array with different frequencies per node | 164  |

| Table 19: Processor Utility of a cubic ball computer consisting of 800 nodes      | 165  |

| Table 20: Processor Utility of a spherical ball computer consisting of 783 nodes  | 166  |

| Table 21: The effect of multi-tasking in an FFTTM with different data sizes       | 169  |

| Table 22: Comparing the performance of two versions of FFTTM                      | 173  |

| Table 23: Range of values for four major network attributes                       | 175  |

| Table 24: Processor Utility in a set of FFTTMs on a network of 1000 nodes         | 176  |

| Table 25: OLBT in a set of FFTTMs on a network of 1000 nodes                      | 177  |

| Table 26: LWT in a set of FFTTMs on a network of 1000 nodes                       | 177  |

| Table 27: Processor Utility for FFTTM on a network of 2000 nodes                  | 179  |

| Table 28: OLBT in a set of FFTTMs on a network of 2000 nodes                      | 180  |

| Table 29: Link Wait Time in a set of FFTTMs on a network of 2000 nodes            | 181  |

| Table 30: Processor Utility in a set of SPTMs on a network of 1000 nodes          | 183  |

| Table 31: OLBT in a set of SPTMs on a network of 1000 nodes                       | 184  |

| Table 32: Link Wait Time in a set of SPTMs on a network of 1000 nodes             | 184  |

| Table 33: Processor Utility in a set of SPTMs on a network of 2000 nodes          | 186  |

| Table 34: OLBT in a set of SPTMs on a network of 2000 nodes                       | 187  |

| Table 35: Link Wait Time in a set of SPTMs on a network of 2000 nodes             | 187 |

|-----------------------------------------------------------------------------------|-----|

| Table 36: Processor Utility for a network of size 1000 nodes running an FFTTM     | 192 |

| Table 37: Processor Utility for a network of size 2000 nodes running an FFTTM     | 192 |

| Table 38: Average Link Utility of 8 FFTTMs running on a 1K-node network           | 196 |

| Table 39: Average Link Utility of 8 FFTTMs running on a 2K-node network           | 197 |

| Table 40: Average Link Utility of SPTM running on a 1K-node network               | 198 |

| Table 41: Average Link Utility of SPTM running on a 2K-node network               | 198 |

| Table 42: OLBT to OLWT ratio of 8 FFTTMs running on a 1K-node network             | 199 |

| Table 43: OLBT to OLWT ratio of 8 FFTTMs running on a 2K-node network             | 199 |

| Table 44: OLBT to OLWT ratio of SPTM running on a 1K-node network                 | 200 |

| Table 45: OLBT to OLWT ratio of SPTM running on a 2K-node network                 | 200 |

| Table 46: Comparing inductive coupling data transfer technologies                 | 209 |

| Table 47: Comparing capacitive coupling data transfer technologies                | 209 |

| Table 48: Wireless Power transfer technologies based on inductive coupling        | 210 |

| Table 49: Comparing short range radio data transfer technologies                  | 215 |

| Table 50: The first row of the data saved by network partitioning algorithm       | 216 |

| Table 51: The third row of data saved by network partitioning algorithm           | 216 |

| Table 52: Information about zones of a node.                                      | 216 |

| Table 53: A zone stored by the network partitioning to be used by channel objects | 216 |

| Table 54: The basic structure of a packet implemented for the simulator           | 217 |

| Table 55: Buffered packet structure designed for physical layer                   | 218 |

| Table 56: Packet structure used by channel objects                                | 218 |

| Table 57: A new packet structure to support ACK timer expiration mechanism        | 218 |

| Table 58: How the three groups of agents interact                                 | 220 |

| Table 59: Different types of data stored in the visualization log file            | 224 |

| Table 60: The fields logged by data type "B"                                      | 224 |

| Table 61: The fields logged by data type "C"                                      | 224 |

| Table 62: The fields logged by data type "N"                                      | 224 |

| Table 63: The fields logged by data type "I".                                     | 224 |

| Table 64: The fields logged by data type "L".                                     | 225 |

| Table 65: The fields logged by data type "U"                                      | 225 |

| Table 66: The fields logged by data type "P"                                      | 225 |

# **List of Algorithms**

| Algorithm 1: Zoning sub-algorithm                               | 116 |

|-----------------------------------------------------------------|-----|

| Algorithm 2: An enhanced version of Zoning sub-algorithm        | 119 |

| Algorithm 3: Channel assignment sub-algorithm                   | 122 |

| Algorithm 4: Task scheduling algorithm for a multi-tasking node | 149 |

# **Acknowledgments**

I would like to use this opportunity to thank my supervisors Professor Jim Austin and Dr. Christopher Crispin-Bailey for their restless efforts to convert me from a student to a scientist. They helped me correct my views in computer science and in scientific thinking in general. Their enthusiasm, support, constructive critique and guidance were vital in writing this thesis without which had no chance to succeed. This thesis —in particular- was so loosely connected to many research fields in its nature so that without their support and timely guidance it could end up in a mess. Besides other helps Chris has also helped me with turning the two-part network partitioning algorithm into pseudo-code used in this thesis. I would like to thank them for being good supervisors and fantastic friends to me during my PhD.

The Cybula team in the Department of Computer Science was a big source of technical and moral support for me. I would like to thank Aaron Turner who helped me through the simulation experiments running on the White Rose Grid.

I thank the members of the Advanced Computer Architecture group including Richard Hind who helped me have a better understanding about available solutions for wireless power delivery. I also thank Nathan Burles and Dai Chengliang for their helps.

I also want to thank my parents who always were my role models. They taught me most of the seriously important things I learned in my life. I thank them for supporting me during my life and particularly during my PhD time. Their presence in the last few months prior to submission was a big moral boost for me. Sadly my father was passed away by the time the final version of this thesis was published; but I am sure his sole is happy about this.

With no doubt the biggest thank goes to my beloved wife Arwin who were with me all these years. She helped me going through difficulties of a new life and returning to academia. I cannot find proper words to thank her. Without her support I had no chance to be in this position and this thesis would never be written. I had not the chance to return her favours yet but I hope I can do so sometime in the future.

To my dearest and closest in the world: my mother and my wife

Aali and Arwin

And in ever-living memory of my grandfather, Nasser and my father Rahim.

This was one of their dreams;

So I hope this sheds sparkles of light on their endless silent nights

And makes their soul happy for ever!

## **Declaration**

This thesis is the result of my own work and includes nothing that is the outcome of work done in collaboration except where specifically indicated in the text. The work in this thesis is my own and has not been submitted for examination at this or any other institution for another award.

Chapter 2 and parts of chapters 3, 4, 5, 6 and 8 are based at the following paper:

M. Kamali, C. Crispin-Bailey, J. Austin; "On advantages and Limitations of 3D Wireless Grids as Parallel Platforms"; International Conference on Selected Topics in Mobile and Wireless Networking, MoWNeT'2013; August 19<sup>th</sup>-21<sup>st</sup> 2013; Montreal, QC, Canada; pp 48-55.

Also chapters 8 and 9 are based on the following paper:

M. Kamali, C. Crispin-Bailey, J. Austin; "Evaluating 3D wireless Grids as Parallel Platforms"; International Journal of Ad Hoc and Ubiquitous Computing, 2015; In Press.

# **Chapter 1: Introduction**

In this thesis the viability of a wireless interconnect network for a highly parallel computer is tested with the focus on connectivity. It starts with an introduction chapter in which a general overview of the idea is presented very briefly. More detailed discussions are available in next chapters (chapter 3 in particular). Following the overview is a discussion on the motivations behind the idea. It will discuss the importance of workong on this topic, the gaps in the literature it fills, the advantages of proposed model over current parallel computers and why it is the right time to work on it,. Furthermore, the main scientific contributions of the thesis are listed which will be discussed in more details throughout the rest of the thesis. The chapter finishes with presenting an outline for the rest of the thesis.

#### 1.1) Overview

In this thesis we want to show whether wireless interconnect networks are suitable for massively parallel computers. A wireless interconnect network has the chance to reduce a supercomputer's production costs due to eradication of extensive wiring between processing nodes. Also, wireless networks are more flexible than wireline networks because nodes can join a wireless network just by tuning to proper channel; while in a wireline network the nodes are located on process boards with fixed capacity and the capacity of each shelf and rack is also fixed. Therefore, it is anticipated that a wireless interconnect network will be more flexible and less complex than wireline networks.

The idea of building a wireless platform for parallel processing raises questions such as:

- 1. Is there any wireless technology at the moment that suits this purpose?

- 2. How high the performance of such a computer will be?

- 3. What are the benefits of having such a platform?

- 4. How Hidden Node Problem is going to be tackled?

- 5. How such a computer may look like?

- 6. How the electrical power is delivered to processing nodes?

- 7. How the heat generated by nodes is dissipated?

The ultimate goal is to build a parallel computer with wireless interconnects containing at least thousands of nodes that is able to compete with modern commercial parallel computers; however, this thesis does not deal with all the questions listed above. The main questions this thesis answers are:

- 1. Is there any wireless technology at the moment that suits for this purpose?

- 2. What are the benefits of having such a platform?

- 3. How a wireless parallel computer may look like?

- 4. How Hidden Node Problem is going to be tackled?

- 5. How high the performance of such a computer will be?

To have a picture about the available wireless choices, a broad survey on different wireless technologies has been carried out. The results of that survey are included in the thesis.

A number of implementation challenges have been researched separately by *Richard Hind* [1]. Among other things he has investigated solutions for wire-free technologies for power transmission and cooling techniques for a large 3D grid. Those issues are not covered in this thesis but this chapter will have a brief look at some of those solutions. Another major target of this thesis is measuring the performance of a proposed wireless network connecting the processors in a parallel machine with a 3D physical topology. To do such measurements, a simulation and data visualisation tool kit is designed and developed. The thesis also tackles a number of challenges like packet collision and network partitioning.

The proposed concept 3D wireless parallel architecture is called Ball Computer (BC). Each element of a BC (a ball) is a standalone processing and communicating entity in form of an electronic board with a processor of a reasonable computational ability equipped with a series of wireless transceivers. Based on the current level of electronic technology the whole package is sought to occupy not more than a couple of square centimetres. When massed produced, the balls can be available with reasonably low prices. The whole package will be put in a plastic (or any other suitable substance) to avoid electrical contact between balls. The whole collection of the balls will be submerged in water (or any other suitable liquid). The liquid will be in charge of heat dissipation and perhaps power delivery as well. To minimise the space occupied by the nodes and also to maximise the number of neighbours per node, a 3D hexagonal topology is selected for the network. In this scheme each node is in physical contact with 12 direct neighbours. Should a 2D hexagonal topology used for the network; the number of neighbours would be 6.

Regarding the novelty of the idea, there are a number of challenges in making such a computer. This thesis focuses on connectivity issues including solving Hidden Node Problem and packet collision by introducing a multi-channel transmission scheme enhanced with a two-stage network partitioning algorithm to assign proper channels to wireless devices.

Another big question is how to deliver electrical power to nodes. Since the idea of BC is implemented in a simulation environment, the answer to the power delivery question does not directly affect the plan at its current state. At the time of implementation an effective power delivery mechanism is required. To be faithful to the original idea of an entirely wireless computer, the priority is to have a wire-free power delivery mechanism but other mechanisms may be considered should it is proven that wired solutions have significant benefit over the wireless options.

Hind [1] has listed a number of wire-free power delivery mechanisms including:

- Inductive Coupling;

- Capacitive Coupling;

- Radio Frequency;

- Optical;

- Piezoelectric;

- Dynamo;

- Chemical.

It is shown in the aforementioned source that all those approaches have some shortcomings. Also, there are chances that a hybrid solution (a combination of two or more mechanisms) may have better performance in terms of power delivery to the circuitry envisaged in this thesis (a processor and a set of fast wireless devices). *Hind* [1] particularly suggests the combination of RF and inductive (or optic) methods may be effective (each operating over different distances).

Among the methods listed above, inductive and capacitive coupling methods are efficient in distances shorter than what is envisaged in this thesis; but their performance drop significantly over longer distances. The possibility of using the cooling liquid to deliver the electrical power is another option. A properly chosen conductive liquid solution may be able to deliver electrical power to nodes and at the same time help dissipating the heat out of the nodes. There are; however, concerns about how to deal with the potentially toxic nature of the substances used in this method. The idea of storing power for transmission to other nodes is another idea that can improve any power delivery mechanism. Apart from wire-free power delivery mechanisms, direct (wired) power delivery solutions can also be considered. In this scheme nodes are placed on trays that not only fix their positions but also accommodate power lines to support nodes.

Another issue that is not part of this thesis is heat dissipation. Like standard High Performance Computing (HPC) systems, gas and/or liquid substances are candidates for cooling the proposed platform. It is anticipated that the circuitry envisaged in the proposed architecture will generate high level of heat per volume unit. This may rule out heat dissipation strategies based on air flow. It is already mentioned in this thesis that a liquid-based heat dissipation mechanism can also be used as a means for power delivery as well. More information about different aspects of BC architecture is available in chapters 3 to 6.

A simulation test bed helps investigating the behaviour of the proposed network without dealing with any hardware implementation challenges. In real world, modern parallel computers usually use hundreds of thousands of processors. A quick survey on the network simulators already available showed that it is a challenge for all of them to accommodate networks with such a volume. For this reason designing and implementing a simulation and data visualisation tool set is part of the thesis. However, there are limitations on the number of simulated nodes in the simulation tool due to the size of memory needed for running the software. Another reason for building a new tool kit is the level of abstraction required for this research which does not match existing network simulation tools.

There has been very little research on this topic. For this reason, we have to be careful in how we compare our work with other research. Also it is tricky to evaluate the cost of such a computer. This makes it hard to have an accurate cost-benefit analysis. Since no wireless parallel machine is made yet, all the performance measurements presented in this thesis are based on simulated models. Some aspects of the simulator are based on ideal models rather than realistic ones for simplicity; therefore, the measurements are approximations of real figures. More accurate simulated models are envisaged for the next stages of this research. To have a justifiable quantitative comparison in terms of performance between this research and available massively parallel computers we need to have both an implementation of the proposed concept computer in real world and a very precise cost valuation of that platform. At this stage, what this thesis is going to investigate are the new design opportunities a wireless interconnect network can offer to parallel computer architects.

To tackle the problem with packet collision, a Multi-Radio-Multi-Channel (MRMC) scheme is devised for nodes. The radio devices should be tuned to proper frequency channels to make sure no packet collision occurs. As part of this thesis a novel two-stage network-partitioning algorithm is designed and implemented. This is a collision avoidance scheme to guarantee that, by using different channels for communication between different (yet overlapping) groups of neighbouring nodes (zones), there would

be no interference between any two packets all over the network. In the thesis it is shown that the network size plays no major role in determining the number of channels needed. In fact the network topology and the radio range (and the interference range) of nodes dictate the number of channels.

MRMC technologies have been used in different applications including mobile phone networks and wireless Internet access devices. Also, in all of these applications a network partitioning algorithm is essential to assign frequency channels to partitions of the wireless network. The differences between those algorithms are mainly in the criteria they satisfy and the topology of the network they are applied to. It is proven in the thesis that the proposed network partitioning is capable of solving the Hidden Node Problem and eradicating packet collision both in theory and practice.

To evaluate the performance of the network in the simulated environment, tasks are reduced to a degree of abstraction so that just their pattern of communication and computation are retained. By doing this, the communication to computation ratio, the rate of occurrence, the duration, the order and the pattern of the communication and computation intervals are preserved. Furthermore, any possible dependencies between communication and computation intervals are left untouched. Therefore, a level of task abstraction, called a task-model, is achieved which is a virtual traffic generator that mimics a class of real world tasks in terms of processor and channel usages patterns. When task X is turned to a task-model the computational nature of X is not preserved. As a result, the task-model is no longer dependent on the software implementation of its original task.

To have an overall understanding of the behaviour of the proposed parallel machine, its performance is studied over a range of network sizes, transfer rates and computational ability of the nodes. The results are shown and analysed in the thesis. A visualisation tool is also developed to improve our understanding of the behaviour of the proposed system through graphical description of its performance at different points.

To have a cost-benefit analysis for the proposed BC architecture, we need to have information about the cost of processors as well as the cost of data links. A brand new processor is not going to be designed for the nodes in a BC platform. The nodes will use off-the-shelf processors with known prices. But to have a cost-benefit analysis an estimation of the cost of the wireless links sought in this thesis is required. The links surveyed in this thesis are all in research stages and there is still no commercial price tag on them. Also some data rates used in simulated experiments are not available at the moment. They were chosen only to cover a range of possible data rates from the past,

the present and the future. It does not mean that they are completely unrealistic; instead, the range of data rates chosen for experiments matches the expected technologies overseen for the near future.

It is possible; however, to check the costs for existing parallel processing. Table 1 shows how the cost for HPC has decreased over time. This table just concerns the processors rather than networking (which is of particular interest in this thesis), cooling and other issues that contribute in total finished cost. A more accurate estimation on a whole parallel computer or its interconnect network is needed to have a precise figure of how much should a BC cost to be as commercially efficient as modern commercially available parallel platforms.

| Date       | Approximate cost per<br>GFLOPS                          | Technology                                              |

|------------|---------------------------------------------------------|---------------------------------------------------------|

| 1961       | US\$1.1 trillion, or US\$1,100<br>per FLOPS             | About 17 million IBM 1620 units costing \$64,000 each   |

| 1984       | US\$15,000,000                                          | Cray X-MP                                               |

| 1997       | US\$30,000                                              | Two 16-processor Beowulf clusters with Pentium Pro CPUs |

| 2000, Apr. | \$1,000                                                 | Bunyip Beowulf cluster                                  |

| 2000, May  | \$640                                                   | KLAT2                                                   |

| 2003, Aug. | \$82                                                    | KASY0                                                   |

| 2007, Mar. | \$0.42                                                  | Ambric AM2045                                           |

| 2009, Sep. | \$0.13                                                  | ATI Radeon R800                                         |

| 2009, Nov. | \$0.59 (double precision);<br>\$0.14 (single precision) | AMD Radeon HD 5970 Hemlock                              |

Table 1: Comparing the cost for 1GFLOPS worth of computation during last decades. 1

In lack of such numbers what we can do is to base our comparison on prices announced for (possibly isolated cases of) parallel platforms. Such a price also includes an unknown - and possibly considerably high- profit margin. To have a very rough estimation, a BC can be valuated based on the cost announced for a number of the most powerful supercomputers in the world. Table 2 lists a few of such supercomputers as in June 2014. It should be noticed that supercomputers are not usually mass produced and therefore in many cases their construction cost are not publically known.

The table shows that at the moment 1GFLOPS of computation costs approximately \$10. Based on available processors in the market it is realistic if we assume each node in a BC have 1GFLOPS of computational ability. In this case –and based on Table 2- a single node (processor plus all the wireless modules) has a price tag of \$10. According to Table 1, the processors have just a very narrow share in that overall cost (something

-

<sup>&</sup>lt;sup>1</sup> Shortened from a table presented in: http://en.wikipedia.org/wiki/FLOPS.

in range of \$0.5 as announced in 2009). The remainder can be allocated to the wireless modules and other costs like cooling. This is just a case for comparison and should not be regarded as a scientific conclusion. The comparison above lacks high precision as there are many unknown issues on both sides of the comparison (i.e. the real cost of many supercomputers as well as the costs for components of a node in BC interconnect network). Therefore, it is not a scientific analysis. However, this can be a good starting point for further investigation to achieve more accurate cost-benefits analysis.

| Construction | Rank              | Computer | Speed    | Cost          | Approximate cost |

|--------------|-------------------|----------|----------|---------------|------------------|

| Date         | (as in Jun. 2014) | Name     | (PFlops) | (USD million) | per GFLOPS (\$)  |

| Jun. 2003    | 1                 | Tianhe-2 | 33.86    | 390           | 11.52            |

| Oct. 2012    | 2                 | Titan    | 17.59    | 92            | 5.23             |

| 2012         | 5                 | Mira     | 8.586    | $50^{2}$      | 5.82             |

Table 2: The cost of a number of most powerful parallel computers in the world derived from Wikipedia<sup>3</sup>.

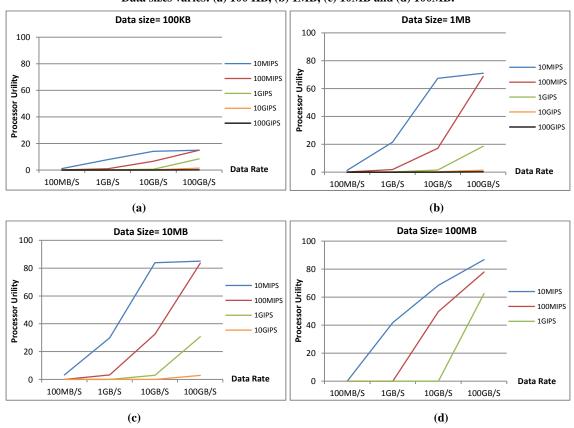

This thesis shows at least some of the existing on-chip wireless technologies can be used in a wireless interconnect for an HPC system; although, they are not originally designed for this purpose. The results demonstrated in this thesis show that for a given set of network attributes (in particular when the ratio of the links' transfer rate to the processors' computational ability is more than 1000) the performance is between 70% and 85% in terms of processor utility.

### 1.2) Motivation

The platform presented in this thesis is based on a number of technologies and algorithms some of which are separately researched and developed in other fields. Some others are inspired by existing algorithms and techniques. In this thesis we will see if these algorithms and techniques are mature enough to construct a new wireless HPC platform.

Wireless devices are available in different shapes, sizes and prices. They are used in a wide range of applications including sensor networks, mobile networks, ad-hoc networks and wearable devices. But at the same time there are applications in which wireless modules are not traditionally considered as good choices. Time critical applications, applications requiring high data rates, applications in which energy consumption should be kept very low and applications with high load of data transfer are among such applications. On the positive side, wireless devices increase the flexibility and scalability of a transmission scheme. They also reduce cost and complexity by removal of wirings.

-

<sup>&</sup>lt;sup>2</sup> It is an estimated cost.

<sup>&</sup>lt;sup>3</sup> http://en.wikipedia.org/wiki/TOP500.

It should be noticed that wireless devices have improved in terms of data rates and energy consumption in recent years. Until very recently, traditional wireless technologies have not been a good choice for time-critical applications like parallel processing.

The main motivation behind the idea of using wireless devices in parallel platforms is the new emerging wireless technologies. The recent developments in low-range high-speed wireless communication have already opened their way into some time-critical applications including inter- and intra-chip applications. Some advantages of a wireless interconnect scheme from a systems composition viewpoint are scalability, simplicity of assembly, potential for reduced power consumption, the obvious elimination of complex wiring problems and the ability to achieve economical three-dimensional physical packing of components.

The main disadvantages of radio devices are their low bandwidth compared to wireline networks, packet collision which ends up in re-transmission of the data and the energy consumption which needs even more reductions to compete with wireline solutions.

There are a number of bottlenecks in field of HPC, each of which are subject of intense research. The interconnect network has always been one of these bottlenecks. Among others are power consumption, software tools (operating systems, compilers and communication APIs) and management of high volume of data generated by these systems. Thus, the quest for novel network architectures is as lively as ever.

Traditionally wired network technology has been the only candidate for connecting processors in a parallel machine. Wireless devices have seriously suffered from a number of shortfalls, which do not let it be a favourite option for a parallel computer. On the other hand a typical wireline network is usually made of compute boards with fixed capacity for processors, shelves with fixed capacity for compute boards (and/or IO boards) and racks with fixed capacity for shelves. Adding new processing elements to such a system is not always easy and straightforward because this may need some changes in the design and instalment of the network. But wirelessly communicating processing elements can be tuned to proper channels and join a 3D wireless network. This means that wireless networks can scale easier than their wired counterparts. The reduction of the wiring complexity and expense are also among the attractive aspects of a wireless architecture; however, the deficiencies of wireless technologies have outweighed their benefits and have discouraged the architects to use them so far.

In light of new developments in wireless technologies it is now a good time to see if high speed wireless transceivers can be used to make a wireless network for HPC applications. It is shown in different surveys that the gap between the bandwidth supported by wired and wireless technologies is narrowing during recent years. *Kürner* [2] has shown that although wireline technologies were always faster than their wireless counterparts, the difference between their data rates is constantly narrowing. There is a healthy chance to have commercially available THz-scale wireless (RF, inductive and capacitive coupling) devices in future which means the gap between wireline and wireless communication links is expected to become even narrower. Figure 1 compares the wireline and wireless technologies for local area networks during the last forty years to illustrate this point.

Figure 1: Evolution of data rates in wireless as projected in [2]

Improvements in signalling techniques and coding/decoding methods are among the reasons why wireline data rates are increased. Many of these improvements can be used to improve wireless technologies as well. Parallel to these improvements, researchers have tackled other restrictions exclusively concern wireless communications including power consumption. This means that there were more improvements in wireless devices than wireline technologies. This can explain why the gap between these two categories of technologies is narrower than past.

In inter- and intra-chip communication the same reduction in difference between these two types of technologies can be observed. *Moore et al* [3] has shown that there is a cap in transmission speed on wires in those applications. This gives a chance for narrowing the gap between wireline and wireless devices in terms of data rates.

Latency and bandwidth are two issues in any communication network. The bandwidth in both wired and wireless networks is now higher than ever. But the signal latency is not changed as much because to a great extent it depends on the communication media. This means that now signal latency plays a bigger role in network performance

compared to bandwidth. Sources of signal latency (AKA packet delivery time) can be hardware-based and/or software-based. Hardware latency can be expressed as:

$$Latency = Transmission Time + Propagation Delay$$

Eq. 1

These two factors should not be confused with each other. For a piece of data of size n, the transmission time is defined as:

Transmission Time =

$$\frac{n}{Transfer Rate}$$

Eq. 2

The propagation delay is related to the medium of communication and is the time from sending a bit of data in the transmitter side until its reception in the receiver side (Eq. 3).

Propagation Delay =

$$\frac{d}{s}$$

Eq. 3

Where d is the distance between the transmitter and receiver of signal, and s is the propagation speed. The propagation delay is not expected to be very significant regarding the high propagation speed of electromagnetic waves (300000000 m/s) and very short communication distances sought in the platform proposed in this thesis. For a 1 cm wireless link the propagation time is around 33.3 ps (3.33 \*  $10^{-11}$ ). The transmission time in both wired and wireless networks are higher than such a number. As an example, transmission time of a packet of data of size 1 kb over a 10 Gb/s link is  $10^{-7}$  s. As a result, the hardware latency can be estimated by transmission time. In the absence of parallel transmission of data in wireless transceivers the transmission time relates to the inverse bandwidth of the data link.

Software latency is believed to be around two degrees of magnitude higher than the hardware latency (An example is given in [4]). The coding/decoding procedure, queuing time, resource competition are among major contributors of software latency. Many of the contributors to software latency are common between wired and wireless networks and therefore do not play a major role in their comparing.

In addition to latency, the bisection bandwidth and overall throughput are other issues that are envisaged to be improved by the platform proposed in this thesis. Details about these factors can be found in coming chapters. All these have encouraged us to think if high speed low latency short range wireless modules can perform the same as wireline connections in parallel processing platforms.

MRMC devices have already been used in applications like wireless internet access networks. The same idea can be adopted over much shorter distances for on-chip wireless modules to accommodate in the platform proposed in this thesis. The number of channels and the mechanism used to manage them are different from previous applications.

A wireless HPC platform should have a solution for packet collision caused by the Hidden Node Problem. A variety of network-partitioning methods have been developed for different applications. These algorithms fall into two main categories: centralized (e.g. [5] [6] [7]) and distributed algorithms (e.g. [8] [9] [10]). These methods are used as part of a solution for packet collision in different wireless networks. This gives a chance to the author of this thesis to adopt a network partitioning algorithm that matches the characteristics of the proposed network. This is necessary to avoid excessive packet collision while all nodes in a localised group communicate on a same frequency. This is a crucial factor to build a multi-channel wireless grid for parallel computing.

Some crucial elements of a wireless HPC system have been researched and developed separately and some of them have been used in different (yet relevant) applications. This implies that there are substantial chances to borrow and adopt technologies and algorithms to make a wireless parallel computer. The cost and complexity of such a computer will be reduced due to removal of the wiring system; however, the extra cost imposed by adding the wireless modules to nodes are yet to be measured. Also, such a system scales easier as there is no restriction imposed by wiring system.

The idea of a wireless HPC platform has never been researched before. In addition to the novelty of the idea, its potential benefits over the traditional wireline interconnect networks and the fact that some crucial aspects of the plan are already researched and developed separately are the main motivations behind this thesis. Since the field is new, it can open new fields of research to researchers from different disciplines to explore its different aspects and even expand the idea to yet unknown territories. This thesis can be a start point for all those efforts.

### 1.3) Main Contributions

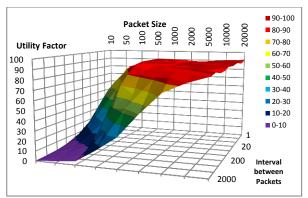

This thesis will investigate positive and negative aspects of using wireless interconnect networks for massively parallel computers. This thesis will show that the state-of-art on-chip radio devices are the best choice for such a platform. However, we will see that those devices still need to improve in transfer rate and more importantly in energy consumption.

A novel network partitioning algorithm will be proposed to solve Hidden Node Problem and eliminate packet collision. This thesis uses series of simulation experiments to show that the platform it has proposed yields excellent results (in terms of processor utility as well as link utility) for a certain range of networks. We will see that the best results are achieved when the ratio between the link's communication speed (in bit/sec) and the

processor's computational ability (in instruction/sec) is more than 1000. Also we will see that the performance of the proposed is higher when it deals with larger data sizes.

The weaknesses of the proposed network are also investigated. The thesis shows that the main problem is in the type of routing and buffer management strategy adopted for this platform. Suggestions for improvement are made for future work.

The main scientific contributions of the thesis are listed below:

- 1. Introducing the concept of Ball Computer as a wireless infrastructure for HPC. Designing a simulated wireless-enabled processing module in order to be used as a member of a Ball Computer in a simulation environment.

- a. Introducing the concept of Ball Computer as a wireless HPC infrastructure.

- b. Designing a layered structure for nodes.

- c. Designing a two-layer message passing protocol for communications between layers of a node as well as different nodes in the network.

- d. Evaluating the network performance in the simulated environment.

- i. Studying how size of packets and other network parameters can be chosen to yield best performance for two major task-models.

- ii. Optimising the number of branches for a divide-and-conquer task-model in the proposed topology.

- e. Studying the behaviour of the Ball Computer under different circumstances.

- Running two sets of experiments with both FFT and Simple parallel task-models on a Ball Computer of sizes 1000 and 2000 nodes when other network attributes change.

- Analysing the results of those sets of experiments to demonstrate the benefits and limitations of Ball Computer under different circumstances.

- iii. Investigating the role of each chosen network attributes on the behaviour of the network.

- iv. Demonstrating the significance of the role of communication to computation ratio in determining the behaviour of the network.

- v. Finding if there is a limit on the size of workload in a wireless parallel machine.

- 2. Solving the hidden node problem for the particular network proposed in this thesis and eliminating packet collision problem by using multiple radio devices.

- a. Designing a multi-radio-multi-channel (MRMC) scheme.

- b. Designing a two-stage network-partitioning algorithm to partition the network into zones in first stage.

- c. Introducing a systematic method (second stage of the partitioning algorithm) to assign channels to zones to solve the hidden node problem and minimise the number of channels at the same time.

- 3. Designing a set of task-models to study the behaviour of different tasks in simulated environment.

- a. Introducing the concept of task-models as communication/computation pattern generators.

- b. Demonstrating how a class of tasks can be converted to a common task-model.

- c. Generating two task-models with very different communication patterns inspired by real-world tasks.

- d. Design and implementation of a communication protocol for each of those task-models.

- 4. Studying tailor-made load balancing methods which fit the characteristics of the network.

- a. Showing how the unique topology of Ball Computer gives space for balancing workload to increase the performance of a Ball Computer.

- b. Introducing two load balancing metrics for a divide-and-conquer task.

- c. Discussion about potential benefits and limitations of each of those two load balancing metrics.

- d. Measuring the increase of performance using multi-tasking and multipleworkloads using one of introduced load balancing methods.

- e. Introducing new task-models with load balancing for a better performance.

In addition to the scientific contributions of this thesis, a set of software tools are designed and implemented which can be used and/or modified by other researchers who work on the same level of abstraction. They are listed below:

- 1. Discussing the potential benefits and restrictions of using wireless technologies in parallel processing.

- a. Discussion on the advantages and limitations of wireless technologies for

a 3D wireless parallel computer. Showing from what aspects and how

- wireless technologies can be better than their wired equivalents in this application.

- b. Listing a number of available research technologies which can be candidates for wireless links in the proposed grid.

- 2. Implementation of a novel large wireless network simulation and visualisation tool kit.

- a. Developing a simulation tool to measure the performance of a very large wireless network.

- b. Designing and implementing ideal wireless links for such a simulated network.

- c. Giving an independent identity to channels as software modules in the simulation tool which leads to easier and more perfect control over their activities and guarantees their robust performance.

- d. Making two different versions of the simulator (with and without clusters of nodes). Testing the benefits of both approaches.

- e. Studying the geometric and task-related attributes of a wireless parallel machine.

- f. Design and implementation of a set of visualisation tools to find the network's bottlenecks.

- g. Using the visualisation results to analyse the performance of simulated network.

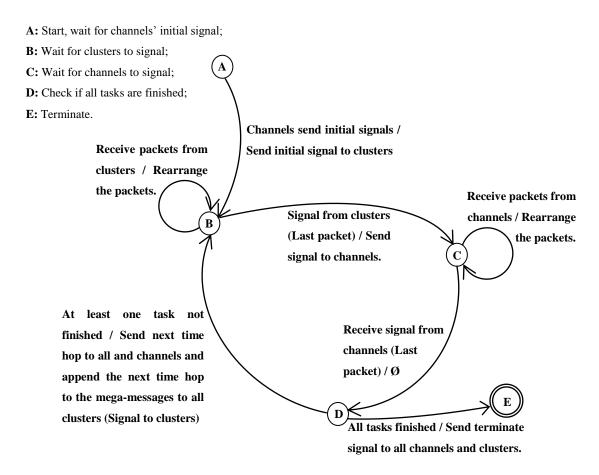

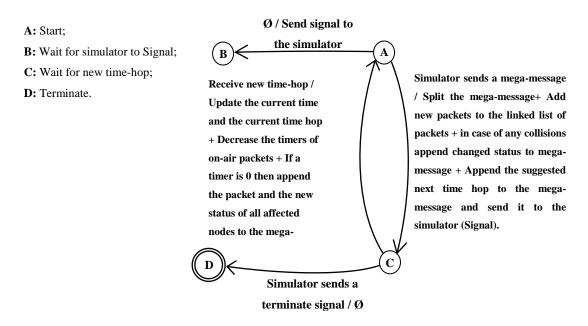

- 3. Design and implementation of a distributed simulation tool.

- a. Design and implementation of independent software agents capable of communicating with each other to run a simulated large wireless grid.

- b. Design and implementation of a communication protocol for the distributed simulation tool.

- c. Running simulation experiments to test the performance of the distributed simulator.

- 4. Design and implementation of a communication protocol for a multi-part packet transfer mechanism.

- a. Design and implementation of extra software layers to handle multi-part messages.

- b. Design and implementation of a communication protocol for a multi-part packet transfer mechanism.

c. Running simulation experiments to test the performance of the multi-part packet transfer mechanism.

## 1.4) Organisation

This thesis consists of ten chapters. Chapter 1 is the introduction chapter which gives a general idea about the subject of the thesis and the motivations behind it. It contains answers to the questions like why this topic has attracted our attention, how important this topic is and how the results from this thesis help filling some gaps in the research literature. Also the main contributions of this PhD thesis are listed.

Chapter 2 takes us through a brief background review of the relevant fields of research to be prepared for the main part of the thesis in which some of those related researches are being used.

Chapters 3 to 7 are dedicated to design and implementation of the proposed platform. In chapter 3 the main research question and the main hypothesis backing the research is presented and explained. It shows what the scope of the thesis is and defines the objectives of the thesis. It also shows what experiments are going to be run and how they are going to be measured to check the level of satisfaction.

In chapter 4 we will see what kind of communication media is going to be adopted for the proposed network and why it looks fit for this specific purpose. This does not contain many electronic details as this thesis is entirely based on a simulation of wireless networks in which not all the electrical characteristics of the elements are (and are needed) to be implemented. In this chapter it is shown what attributes of the network are important from the simulator's point of view.

Inspired by what was reviewed in previous chapters, a novel network-partitioning algorithm is presented in chapter 5 which is tailor-made for this research. The criteria against which this algorithm is designed are listed. It will be explained why those criteria are chosen and how they are different from the other network-partitioning algorithms.

In chapter 6 it is explained what is meant by "task-model" in this thesis and why it is important to use task-models instead of real tasks. It will be shown how real world tasks can be transformed to task-models to be fit for simulations. It will be shown how task-models can be used to decrease the test and analyse time for a potentially large number of tasks in real world.

Chapter 7 goes through implementation details of the simulation and data visualisation tool kit implemented in this research. Key data structures and communication protocols are presented in this chapter. It will be shown how the ideas originated from previous

chapters are translated to data structures and pieces of code. In addition to the main simulator, an off-line data visualisation tool is implemented and introduced in this chapter to present the results in an illustrative form to help analysing the results and verifying the initial hypothesis of the thesis.

The next two chapters are dedicated to results derived from the simulation tests. One of the main targets of the thesis is solving the Hidden Node Problem and elimination of packet collision. In chapter 8 results will be presented to back the claim that the packet collision is completely eliminated. Also other preliminary results are presented in this chapter. The results show how the performance of the proposed system changes when network nodes are multi-tasking. Also it is shown how using multiple independent workloads improves the overall performance of the system. Included in this chapter are results that show how successful the idea of load balancing is and how the task-models used need to be changed to let the load balancing mechanism work effectively. Another part of this chapter is dedicated to a comparison between two main task-models introduced in this thesis. As it will be discussed in details later in this thesis, the main difference between these two task-models is the degree of dependency between tasks in different nodes of the network. This chapter finishes with a set of experiments on the optimal number of child nodes per parent node in a divide-and-conquer task-model in a 2D and 3D grid.

Chapter 9 covers one of the major parts of this thesis in which the behaviour of the system is studied when its four most important parameters change. The parameters are the network size, the transfer rate of links, the computation ability of nodes and the workload (data) size. Two different task-models and two different network sizes are used in this set of experiments.

Chapter 10 is dedicated to the conclusion and future work. This chapter contains final analysis of the results presented in last two chapters. Results from previous chapters are used to assess how beneficial the idea of ball computers can be. It shows for what values for network parameters the proposed platform yields good results and for what values for those parameters the performance is not satisfactory. This chapter concludes with a look at how this thesis can be expanded. A number of new fields of research derived from this research are listed.

# **Chapter 2: Literature Review**

A wireless platform for a parallel computer needs to borrow ideas, algorithms and technologies from a variety of fields of research. Throughout this chapter some of these fields are reviewed to choose or tune those that best fit the wireless grid proposed in this thesis. Some background on the parallel processing and interconnect networks are also included in this chapter.

#### 2.1) Parallel Processing

From the early days of computing history researchers have been challenged by problems that need excessive computation labour. This put a constant pressure on the architects to come up with new machines that can handle larger numbers of calculations in a given time. Some of the grand challenges are plotted in Figure 2 to present their storage and computational requirements as in 1999.

Figure 2: Grand challenges as projected in 1999 in [11]

The term "grand challenges" is first used in 1980's in US governmental documents to refer to the main challenges for the future in the field of HPC. At present the challenges are almost the same with the exception that the computational performance and storage requirements are increased now. A 2011 report published by USA's National Science Foundation [12] lists the grand challenges as:

- Advanced new materials;

- Prediction of climate change;

- Energy through fusion;

- Water sustainability;

- Condensed matter theory and Quantum

chromodynamics;

- Semiconductor design and manufacturing;

- Assembling the tree of life;

- Drug design and development;

- Understanding biological systems;

- New combustion systems;

- Astronomy and cosmology;

- Hazard analysis and management;

- Human sciences and policy;

- Virtual product design;

- Cancer detection and therapy;

- CO<sub>2</sub> sequestration.

Some of the 2011's challenges can be found in Figure 2 (dated 1999) and others are new. The challenges in present time have more computational and storage demands compared to the last years of  $20^{th}$  century. This is mainly because those challenges deal with larger data sizes now.

Weather forecast, for example, is projected in Figure 2 as a 48-hour forecast which needs around 100 MFLOPS of computational capability and a 72-hour forecast with less than 10 GFLOPS; but today's challenge in this filed is forecasting for longer periods and demanding higher computational capability. As theorized by *DeBenedictis* [13] in 2005, the climate modelling needs zettaFLOPS-scale computational capacities for a time span of a couple of weeks.

A single simulation of gamma ray bursts needs around 18 million PFLOPS [12]. This means with a PFLOPS-scale parallel computer it is practically impossible to run a single simulation of that type in less than 100 days.

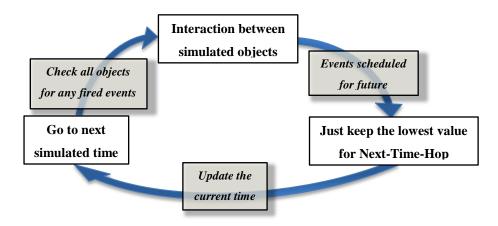

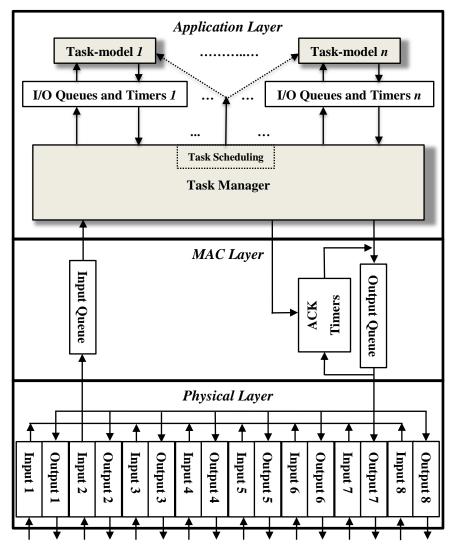

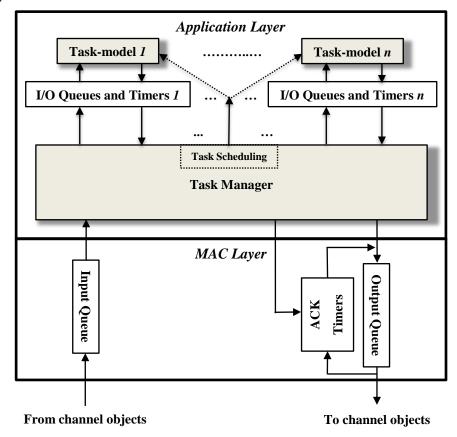

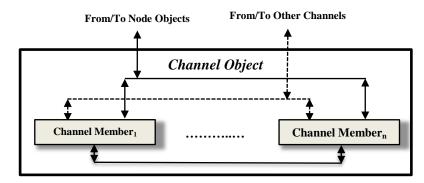

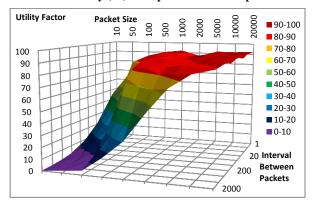

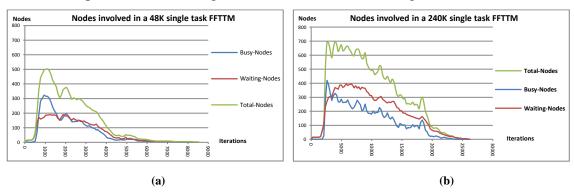

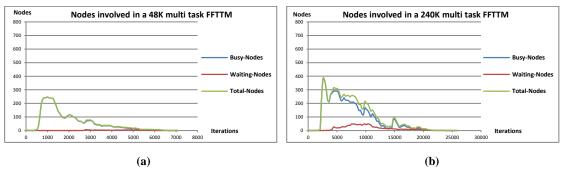

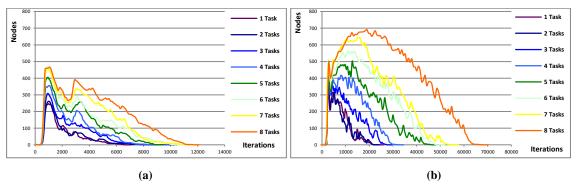

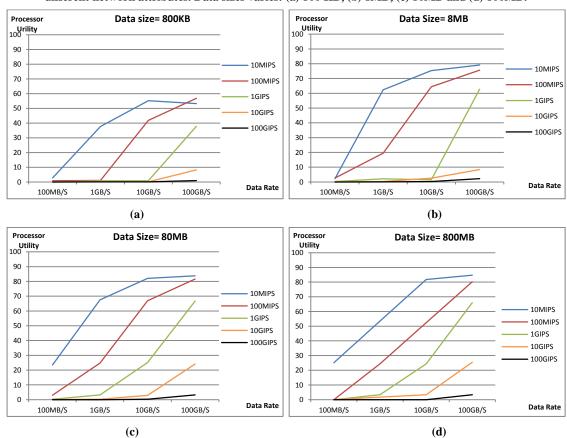

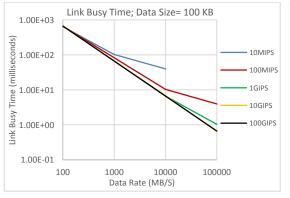

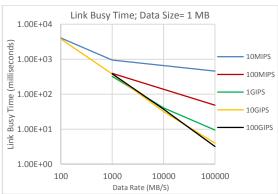

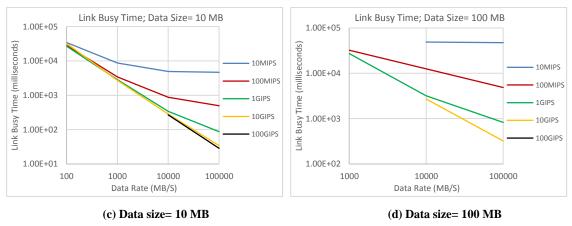

To simulate a high pressure turbine blade needs a total of 1000 PFLPS and 1PB of memory [14]. These are just a few examples of present challenges for current PFLOPS-scale computers<sup>4</sup> which push HPC community to head for Exascale computing.