## Ultra Low Phase Noise Microwave Oscillators

### ST. JOHN GILBERT

Doctor of Philosophy

University of York,

School of Physics, Engineering and Technology

### Abstract

This thesis presents the findings of research into low phase noise oscillators. Four design approaches have been developed with the common aim of achieving ultra low phase noise performance. The main body is split into four chapters which detail each design starting with a 1.5 GHz dielectric resonator oscillator, a 16 GHz distributed Bragg resonator oscillator with parallel amplifiers used in the feedback loop, the development of the feedforward technique for use in a low noise oscillator before finishing with the latest measurements of a 5 MHz crystal oscillator.

The development of a 1.5 GHz dielectric resonator oscillator is presented in Chapter 3 which details the design process of each part and the assembly of the complete oscillator in a metal enclosure. The design of the coupling probes, resonator enclosure and the phase shifting circuits are presented. This chapter ends with the presentation and discussion of ultra low oscillator phase noise measurements.

In the fourth chapter the design of the feedback circuit to be used with a 16 GHz distributed Bragg resonator cavity is presented as well as research into the coupling mechanisms used with this resonator. Initial oscillator phase noise measurements are presented.

A new technique is introduced in Chapter 5 using a feedforward amplifier in an oscillator to suppress the flicker noise introduced by the sustaining amplifier. A derivation of design equations are presented as well as measurements of a 100 MHz oscillator showing that a variable gain feedforward amplifier can be used in the feedback loop without the need for external power limiting circuits.

The sixth and final technical chapter presents state of the art measurements of a 5MHz crystal oscillator. This chapter includes the design of an electronic phase shifter as well as measurements of the individual parts of the oscillator.

## Acknowledgements

I thank my supervisors, Professor Jeremy Everard and Dr Simon Bale for their knowledge, experience, encouragement and support throughout this research. Their constant feedback and critical analysis of my work has been invaluable in the completion of this project.

Thank you to all the staff within the school of PET who have helped me with technical work and advice in manufacturing all the parts and PCBs I have used in my measurements.

My friends and fellow PhD students within this research group, Luke Dummott and Stuart Kenny for their support, encouragement and stimulating conversations throughout. A further thank you to Luke for teaching me how to play chess - a welcomed distraction during our many lunch breaks both during lockdown and afterwards! I thank Prof. Andy Marvin for his insight into research practices, support and sharing his valuable experience with me whilst we have been sharing the office.

I wish to express a very special thanks to my parents, Nick and Debi, for without whom I would not have begun this research let alone get to a point in which I could have written this thesis. Thank you for pushing me through this period of my life and encouraging me to persevere with my research.

Finally, a very special thank you my love, Molly. I cannot write in enough detail how much your support, love and encouragement has helped me throughout this work. Without you, I would have never completed this research.

St. John Gilbert, York, March 2024.

## Declaration

I declare that this thesis is a presentation of original work and I am the sole author. This work has not previously been presented for a degree or other qualification at this University or elsewhere. All sources are acknowledged as references.

# Contents

| Li | st of | tables                                                    | xiii |

|----|-------|-----------------------------------------------------------|------|

| Li | st of | figures                                                   | xv   |

| 1  | Inti  | roduction                                                 | 1    |

|    | 1.1   | Research aims                                             | 1    |

|    | 1.2   | Thesis Structure                                          | 2    |

|    | 1.3   | Related Publications                                      | 4    |

| 2  | Pha   | se noise theory and literature                            | 5    |

|    | 2.1   | Feedback Oscillator                                       | 5    |

|    | 2.2   | Oscillator Phase Noise                                    | 7    |

|    |       | 2.2.1 Ideal and real oscillators                          | 7    |

|    |       | 2.2.2 Thermal Noise                                       | 9    |

|    |       | 2.2.3 Shot Noise                                          | 10   |

|    |       | 2.2.4 Flicker Noise                                       | 10   |

|    | 2.3   | Oscillator Phase Noise Models                             | 12   |

|    |       | 2.3.1 Leeson's model and Parker's extension               | 12   |

|    |       | 2.3.2 Everard's Model                                     | 13   |

|    |       | 2.3.3 Optimisation for Minimum Phase Noise                | 20   |

|    |       | 2.3.4 Oscillator Phase Noise Spectrum                     | 22   |

|    | 2.4   | Cross correlation residual phase noise measurement system | 24   |

CONTENTS

| 3 | 1.5  | GHz d  | lielectric resonator oscillator                                              | <b>27</b>  |

|---|------|--------|------------------------------------------------------------------------------|------------|

|   | 3.1  | Introd | luction to Dielectric Resonator Oscillators                                  | 27         |

|   | 3.2  | Curre  | nt state-of-the-art                                                          | 30         |

|   | 3.3  | 1.5 GI | Hz DRO design and measurements                                               | 33         |

|   |      | 3.3.1  | Resonator                                                                    | 34         |

|   |      | 3.3.2  | Gain stage                                                                   | 42         |

|   |      | 3.3.3  | Closed loop phase shift and tuning                                           | 49         |

|   |      | 3.3.4  | Output Coupler                                                               | 58         |

|   | 3.4  | Comp   | lete oscillator phase noise measurement                                      | 63         |

|   |      | 3.4.1  | Oscillator tuning and power measurements                                     | 64         |

|   |      | 3.4.2  | Theoretical oscillator phase noise                                           | 66         |

|   |      | 3.4.3  | Single oscillator phase noise measurements using Rohde and Schwarz FSWP 50   |            |

|   |      |        | phase noise measurement system                                               | 67         |

|   |      | 3.4.4  | Dual oscillator phase noise measurement using Symmetricom 5120 A (Option 01) | 71         |

|   | 3.5  | Concl  | usions                                                                       | 77         |

| 4 | 16 ( | GHz D  | Distributed Bragg Resonator Oscillator                                       | <b>7</b> 9 |

|   | 4.1  | Distri | buted Bragg Resonator                                                        | 79         |

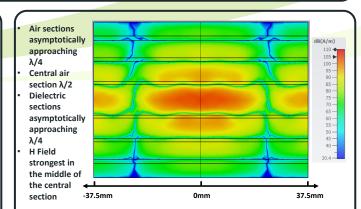

|   |      | 4.1.1  | ABCD parameter model                                                         | 81         |

|   |      | 4.1.2  | CST Eigenmode solver simulation of 16GHz DBR                                 | 85         |

|   |      | 4.1.3  | Spira Shield                                                                 | 86         |

|   | 4.2  | Coupl  | ing to resonator                                                             | 89         |

|   |      | 4.2.1  | Initial loop probe measurements                                              | 89         |

|   |      | 4.2.2  | Loop probe simulations                                                       | 91         |

|   |      | 4.2.3  | External impedance transformation network                                    | 93         |

|   |      | 4.2.4  | Waveguide Coupling                                                           | 105        |

|   | 4.3  | Ampli  | fiers                                                                        | 116        |

|   |      | 4.3.1  | Parallel Amplifier design                                                    | 118        |

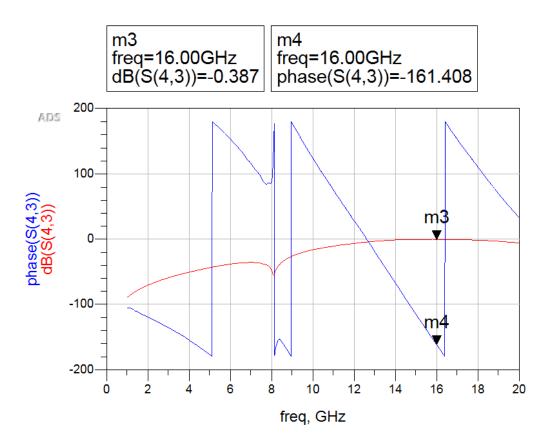

|   |      | 4.3.2  | Simulated couplers placed back to back                                       | 124        |

CONTENTS xi

|   |     | 4.3.3  | Manufactured straight through boards                                | 130 |

|---|-----|--------|---------------------------------------------------------------------|-----|

|   |     | 4.3.4  | Ripple in the passband investigation                                | 132 |

|   |     | 4.3.5  | 2 Way Splitting and combining circuits with WithWave connectors     | 140 |

|   |     | 4.3.6  | 4 Way splitting and combining measurements                          | 142 |

|   |     | 4.3.7  | Parallel Amplifier Measurements                                     | 143 |

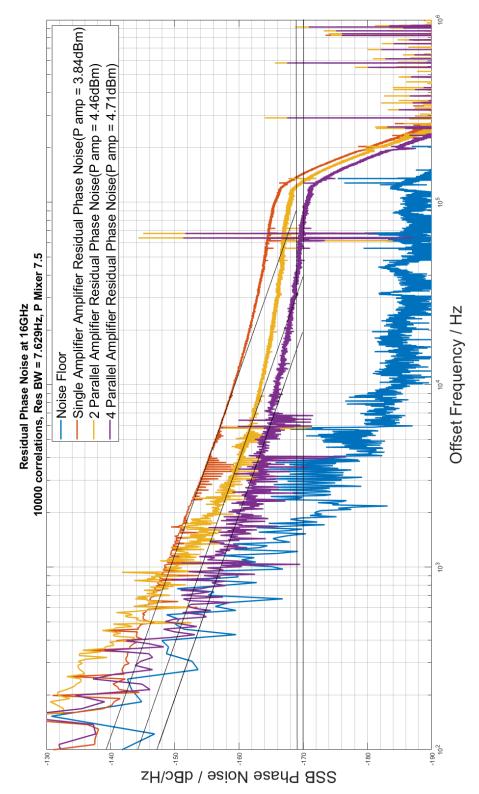

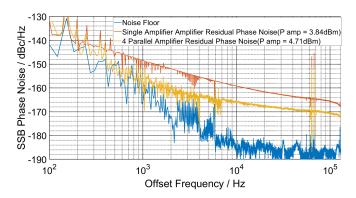

|   |     | 4.3.8  | Residual phase Noise measurements of single and parallel amplifiers | 147 |

|   | 4.4 | Phase  | shifters                                                            | 150 |

|   |     | 4.4.1  | Prototype PCBs and measurements                                     | 153 |

|   | 4.5 | Outpu  | at coupler                                                          | 158 |

|   | 4.6 | Comp   | lete oscillator                                                     | 160 |

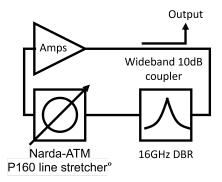

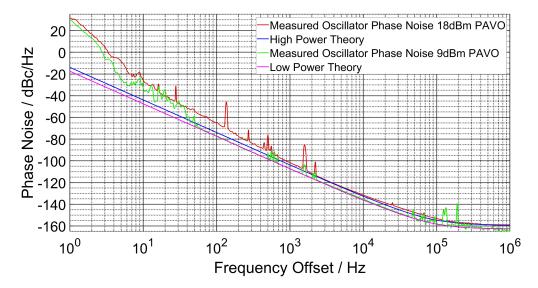

|   |     | 4.6.1  | Measured oscillator phase noise                                     | 166 |

|   | 4.7 | Concl  | usions and further work                                             | 171 |

| 5 | Fee | dforwa | ard amplifier Oscillator                                            | 173 |

|   | 5.1 | Introd | luction                                                             | 173 |

|   | 5.2 | Curre  | nt state-of-the-art                                                 | 174 |

|   | 5.3 | Theor  | y of operation                                                      | 176 |

|   |     | 5.3.1  | Phasor analysis and derivation of design equations                  | 178 |

|   |     | 5.3.2  | Loop cancellation                                                   | 180 |

|   |     | 5.3.3  | Noise figure                                                        | 183 |

|   | 5.4 | Varial | ole gain feedforward amplifier                                      | 184 |

|   | 5.5 | 100 M  | Hz feedforward amplifier                                            | 185 |

|   |     | 5.5.1  | Amplifier simulations and Feedforward amplifier simulations         | 185 |

|   |     | 5.5.2  | First FF Iteration                                                  | 194 |

|   |     | 5.5.3  | Calibration                                                         | 196 |

|   |     | 5.5.4  | Second Iteration                                                    | 202 |

|   | 5.6 | 100 M  | Hz feedforward amplifier oscillator                                 | 224 |

|   |     | 5.6.1  | LC Oscillator                                                       | 224 |

|   |     | 5.6.2  | Noise Injection                                                     | 232 |

xii CONTENTS

|                  | 5.7            | Conclusions and further work                                                | 235         |

|------------------|----------------|-----------------------------------------------------------------------------|-------------|

| 6                | 5 M            | IHz crystal oscillator                                                      | 237         |

|                  | 6.1            | Introduction                                                                | 237         |

|                  | 6.2            | 5 MHz crystal                                                               | 239         |

|                  |                | 6.2.1 5MHz crystal measurements                                             | 239         |

|                  | 6.3            | Long-tailed Pair Differential Amplifier                                     | 244         |

|                  |                | 6.3.1 Amplifier Design                                                      | 244         |

|                  |                | 6.3.2 Amplifier Measurements                                                | 246         |

|                  | 6.4            | Electronically Tunable Phase Shifter                                        | 246         |

|                  |                | 6.4.1 Closed loop Phase Shift                                               | 248         |

|                  |                | 6.4.2 Modified High Pass Filter Design                                      | 250         |

|                  |                | 6.4.3 Phase Shift Measurements                                              | 253         |

|                  | 6.5            | Oscillator Measurements                                                     | 253         |

|                  | 6.6            | Conclusions and further work                                                | 257         |

| 7                | Con            | nclusions and future work                                                   | <b>259</b>  |

|                  | 7.1            | 1.5GHz DRO discussion and suggested further work                            | 259         |

|                  | 7.2            | 16 GHz DBR oscillator discussion and suggested further work                 | 261         |

|                  | 7.3            | 100 MHz Feedforward amplifier oscillator                                    | 261         |

|                  | 7.4            | 5 MHz Feedforward amplifier oscillator                                      | 262         |

| $\mathbf{A}_{]}$ | ppen           | dices                                                                       | 267         |

| $\mathbf{A}$     | $\mathbf{Ard}$ | luino source code to control ZX76-31R75PP-S+ digital step attenuator        | 267         |

| В                | Ultı           | ra low phase noise 16GHz oscillator using a distributed Bragg resonator cor | 1-          |

|                  | fere           | ence paper and poster                                                       | <b>27</b> 1 |

| Bi               | bliog          | graphy                                                                      | 277         |

| R                | efere          | nces                                                                        | 277         |

# List of Tables

| 3.1  | Original and scaled 3.8 GHz puck dimensions                                                  | 36  |

|------|----------------------------------------------------------------------------------------------|-----|

| 3.2  | Real 1.5 GHz Puck Dimensions                                                                 | 36  |

| 3.3  | Eigenmode solver simulated $Q_0$ and $f_0$ with varying enclosure height                     | 39  |

| 3.4  | Eigenmode solver simulated $Q_0$ and $f_0$ with varying enclosure radius                     | 39  |

| 3.5  | Resonant frequency and insertion loss, $Q_{\rm L}$ and $Q_0$ at the resonant frequency with  |     |

|      | varying probe radius                                                                         | 40  |

| 3.6  | Measured resonant frequency and $S_{21},Q_L$ and $Q_0$ at the resonant frequency             | 42  |

| 3.7  | BFG591 gain, noise figure and 1dB compression point measurements                             | 49  |

| 3.8  | Summary Table of measured and simulated S-Parameters of Broadband Coupler                    | 63  |

| 3.9  | Parameters used to calculated the theoretical oscillator phase noise                         | 65  |

| 3.10 | Parameters used to calculated the cascaded noise figure of components in the oscillator      |     |

|      | loop                                                                                         | 66  |

| 3.11 | Theoretical oscillator phase noise at key offset frequencies                                 | 66  |

| 3.12 | Theoretical and measured oscillator phase noise at key offsets                               | 69  |

| 4.1  | Dimensions of air gaps and plates                                                            | 85  |

| 4.2  | Dimensions and material of RG405 coaxial cable used to manufacture the DBR probes.           | 89  |

| 4.3  | Calculated lengths and Widths from LineCalc after optimisation                               | 96  |

| 4.4  | Calculated lengths and Widths from LineCalc after optimisation                               | 101 |

| 4.5  | Simulated resonant frequency, insertion loss and $Q_0$ with decreasing Alumina loss tangent. | 110 |

xiv LIST OF TABLES

| 4.6  | Simulated resonant frequency, insertion loss and $Q_0$ where the Alumina loss tangent is                     |      |

|------|--------------------------------------------------------------------------------------------------------------|------|

|      | set to $2 \times 10^{-5}$ and the aperture width is varied. The adaptive mesh option was not                 |      |

|      | selected                                                                                                     | 111  |

| 4.7  | Measured insertion loss at resonance, resonant frequency and $\mathbf{Q}_1$ and calculated $\mathbf{Q}_0$ of |      |

|      | the DBR with different aperture coupling mechanisms                                                          | 115  |

| 4.8  | Measured amplifier parameters at 16 GHz from three amplifiers considered suitable for                        |      |

|      | use in a 16 GHz oscillator                                                                                   | 118  |

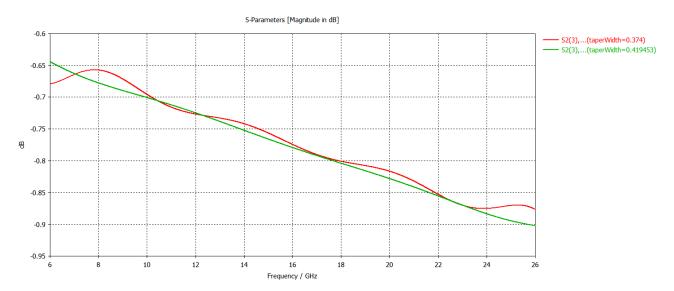

| 4.9  | Calculated Dolph-Tchebycheff impedances at distance X mm from the centre of the                              |      |

|      | taper. The impedances are then converted to a microstrip track width at 16 GHz using                         |      |

|      | 0.25 mm Rogers 4350 substrate                                                                                | 123  |

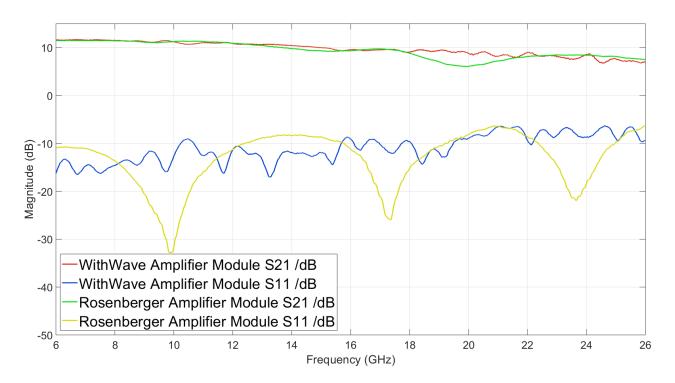

| 4.10 | Gain, NF and P1dB at 16 GHz for the two amplifier modules using the Rosenberger                              |      |

|      | SMA connectors with the narrow centre conductor and the WithWave 2.92mm connectors.                          | .139 |

| 4.11 | Gain, NF and P1dB at 16 GHz for all amplifier configurations                                                 | 147  |

| 5.1  | Calculated resistor values for the $\pi$ Networks used in the digital attenuator. The atten-                 |      |

|      | uation of each stage is double that of the previous stage to allow for a binary code to                      |      |

|      | be used to change the attenuation                                                                            | 210  |

| 5.2  | Parameters used for the theoretical oscillator phase noise calculation. The noise figure                     |      |

|      | for the loop components is different but all other parameters are the same. $\dots$                          | 228  |

| 5.3  | LC oscillator components in order from resonator output to resonator input, the error                        |      |

|      | correction loop is omitted from the amplifier so the main amplifier is in series with the                    |      |

|      | splitters and phase shifter                                                                                  | 228  |

| 5.4  | LC oscillator components in order from resonator output to resonator input, the error                        |      |

|      | correction loop is included and amplifier is treated as one component with a noise figure                    |      |

|      | calculated using $(5.26)$                                                                                    | 228  |

# List of Figures

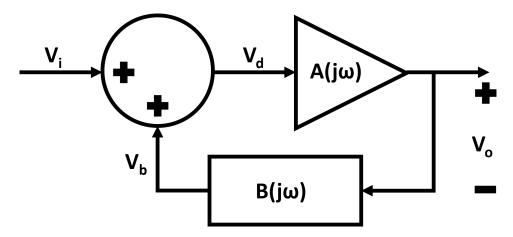

| 2.1 | Positive feedback applied to a two port device block diagram. An oscillator can be                         |    |

|-----|------------------------------------------------------------------------------------------------------------|----|

|     | modelled as a two port device where the input is white Gaussian noise                                      | 6  |

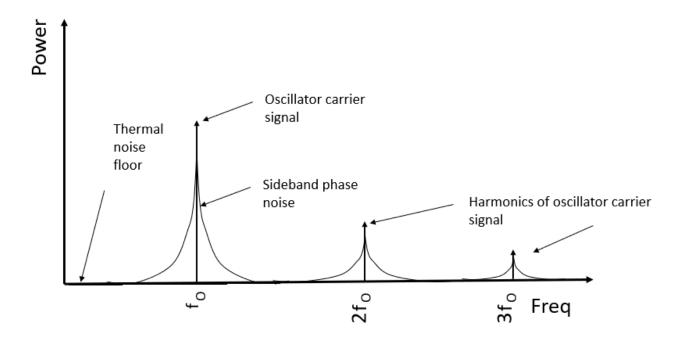

| 2.2 | Spectrum of real oscillator output                                                                         | 7  |

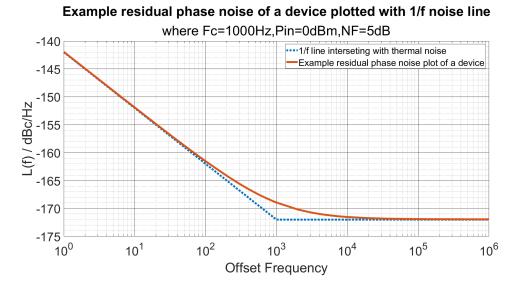

| 2.3 | Example $\frac{1}{f}$ noise intersecting with the thermal noise to give the flicker noise corner           | 11 |

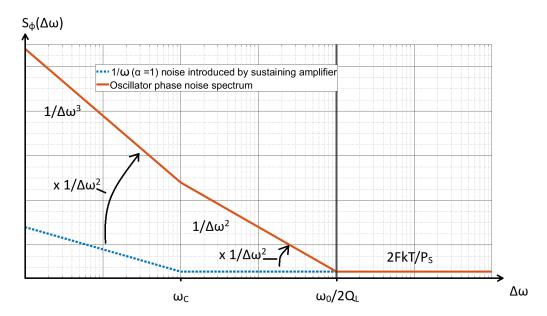

| 2.4 | Oscillator noise power spectral density plotted variation with frequency from the os-                      |    |

|     | cillator frequency. The $1/\Omega$ noise from the amplifier is multiplied by the $1/\Omega^2$ noise        |    |

|     | introduced by the resonator above and below $\omega_{\text{\scriptsize C}}.$                               | 12 |

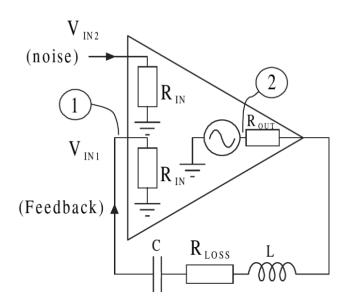

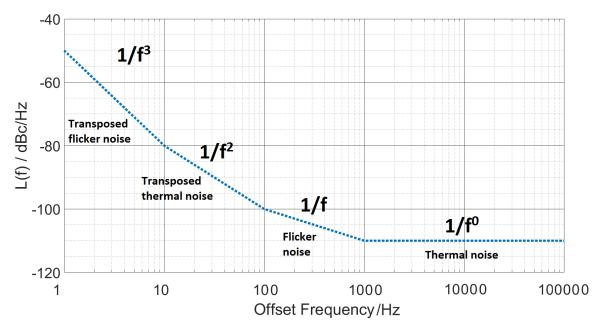

| 2.5 | Oscillator equivalent circuit model [17]                                                                   | 14 |

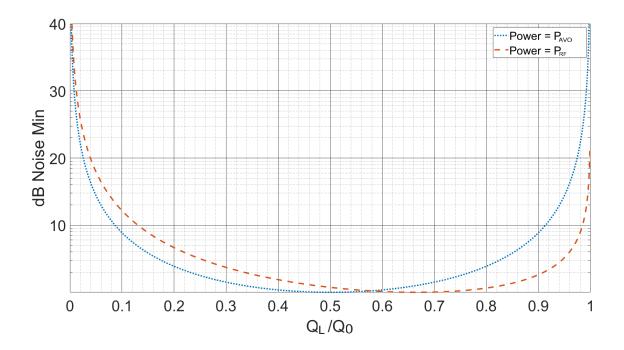

| 2.6 | Oscillator phase noise degradation as a result of varying $\frac{Q_L}{Q_0}$ and $S_{21}$ for two different |    |

|     | power definitions                                                                                          | 21 |

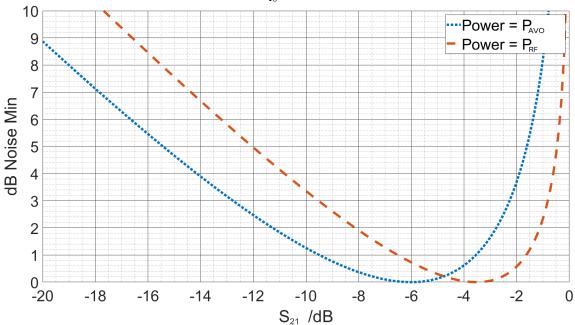

| 2.7 | Example oscillator phase noise spectrum with transposed flicker and thermal noise to                       |    |

|     | the carrier frequency                                                                                      | 23 |

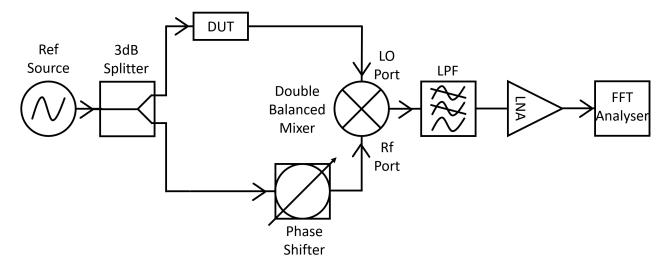

| 2.8 | Single channel residual phase noise measurement system where two identical devices                         |    |

|     | are being measured                                                                                         | 24 |

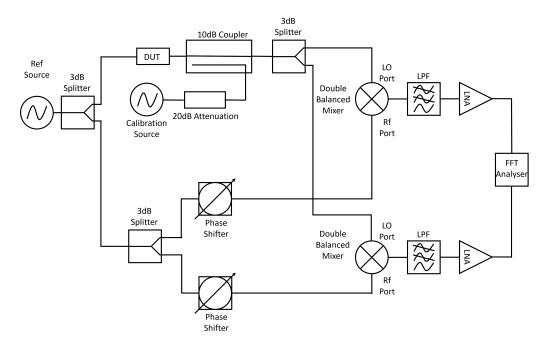

| 2.9 | Cross correlation residual phase noise measurement system                                                  | 26 |

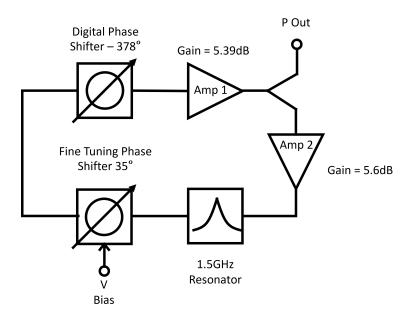

| 3.1 | Complete 15.GHz dielectric resonator oscillator block diagram developed in this chapter.                   | 33 |

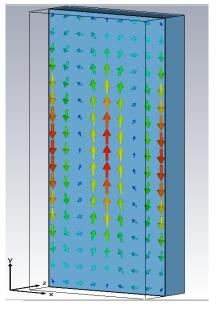

| 3.2 | Bird's Eye view of model of the pucks used in Eigenmode simulation showing E-Field                         |    |

|     | maximum                                                                                                    | 35 |

| 3.3 | Cross section view of the Eigenmode simulation of the 3.8 GHz pucks, showing the                           |    |

|     | positions of the maximum H-Field                                                                           | 35 |

|     |                                                                                                            |    |

xvi LIST OF FIGURES

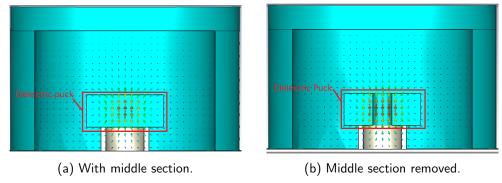

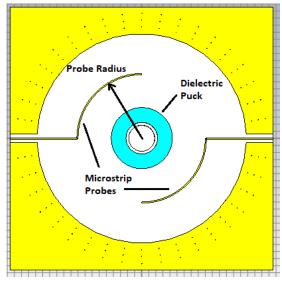

| 3.4  | CST frequency domain simulation used for probe and enclosure design                              | 38 |

|------|--------------------------------------------------------------------------------------------------|----|

| 3.5  | Resonator Measurement using Anritsu 37377C Vector Network Analyser                               | 41 |

| 3.6  | Push-pull topology of two parallel amplifiers                                                    | 43 |

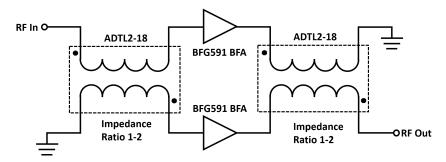

| 3.7  | Single Stage BFG591 Amplifier schematic                                                          | 44 |

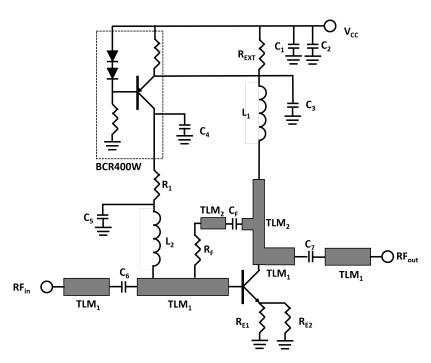

| 3.8  | Manufactured push-pull amplifier                                                                 | 45 |

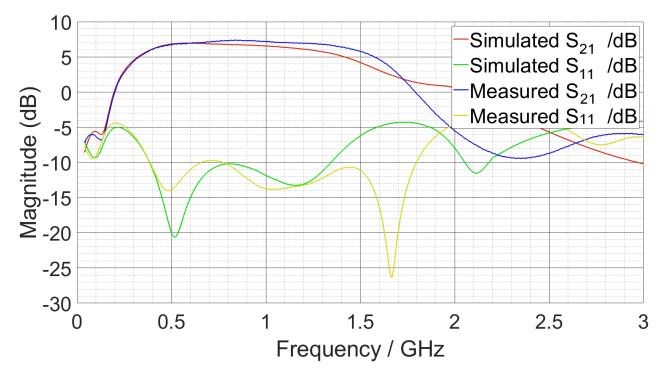

| 3.9  | Amplifier simulated and measured gain and return loss                                            | 46 |

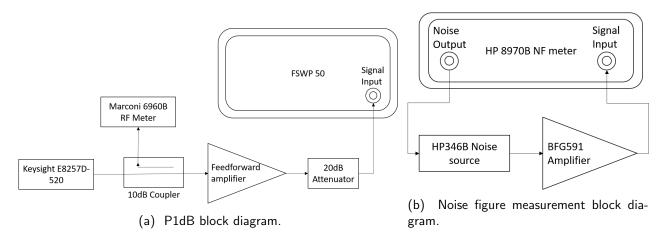

| 3.10 | Block diagrams of the P1dB and noise figure measurement setup                                    | 47 |

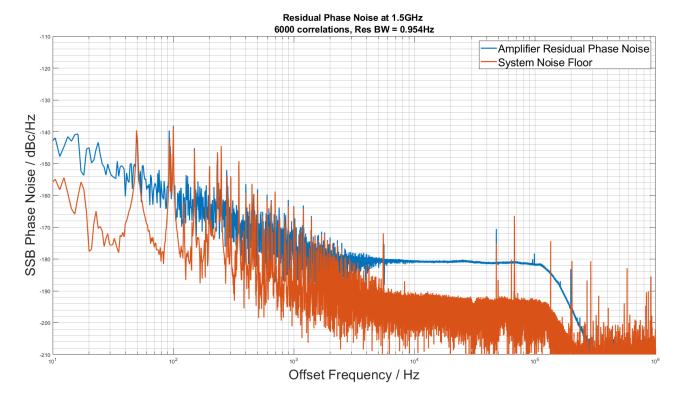

| 3.11 | Amplifier Residual Phase Noise Measurement, $P_{\rm in}=20{\rm dBm.}$                            | 48 |

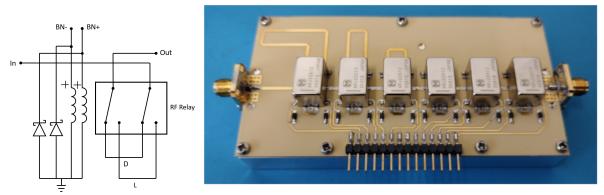

| 3.12 | 1 bit digital phase shifter schematic and the assembled 6 bit digital phase shifter              | 50 |

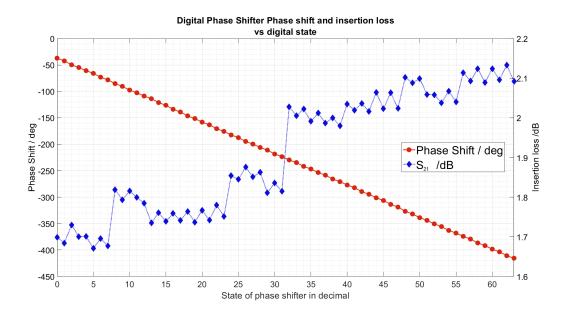

| 3.13 | Measured phase shift and insertion loss vs decimal state of the digital phase shifter at         |    |

|      | 1.5GHz                                                                                           | 51 |

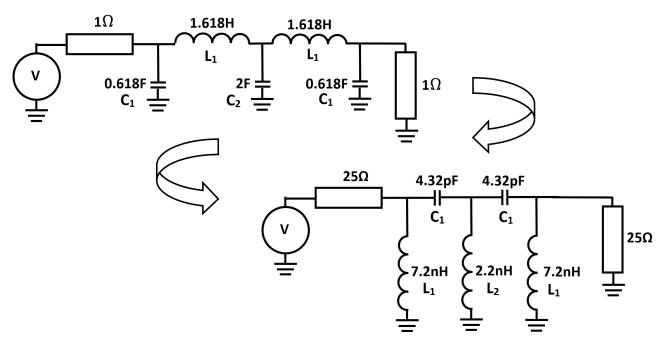

| 3.14 | 5th Order LPF prototype transformed to a $5^{\mathrm{th}}$ order HPF where $f_0{=}0.9$ GHz and   |    |

|      | $Z_0 = 25\Omega$                                                                                 | 52 |

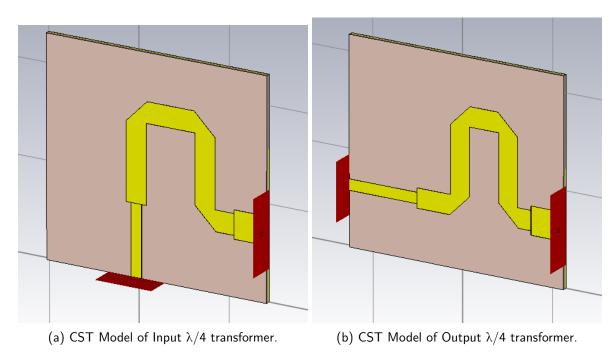

| 3.15 | CST models of input and output quarter wave transformer sections with 90° mitre bends.           | 53 |

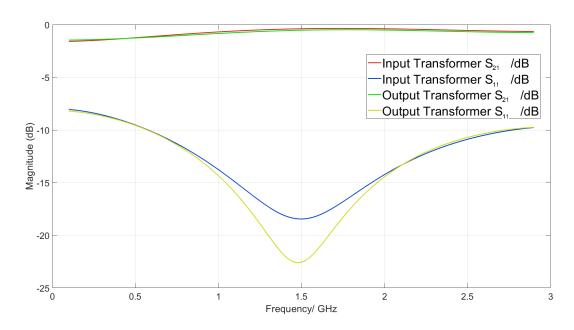

| 3.16 | Input and output transformer $S_{21}$ and $S_{11}$ simulated in CST                              | 54 |

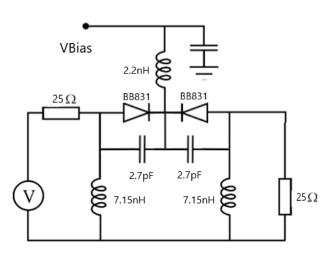

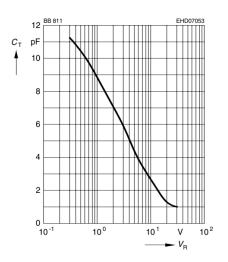

| 3.17 | 1.5 GHz tunable phase shifter schematic including BB831 varactor diode and a plot of             |    |

|      | the CV characteristics of the BB831                                                              | 55 |

| 3.18 | Simulated insertion loss /dB and Phase ° vs Bias Voltage /V                                      | 55 |

| 3.19 | Tunable Phase Shifter board with optimised 35.4 $\Omega$ and $\lambda/4$ transformers and mitred |    |

|      | bends                                                                                            | 56 |

| 3.20 | Measured insertion loss /dB and Phase ° vs Bias Voltage /V                                       | 57 |

| 3.21 | Residual phase noise of both phase shifters measured using cross correlation measure-            |    |

|      | ment system                                                                                      | 58 |

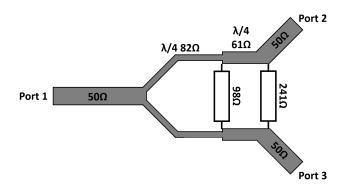

| 3.22 | Wideband Wilkinson Divider where $f_1/f_2=2.$                                                    | 59 |

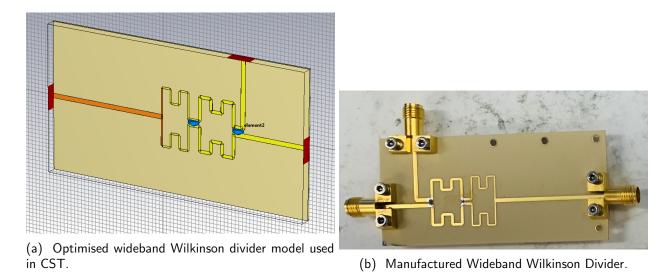

| 3.23 | CST model and manufactured wideband coupler                                                      | 60 |

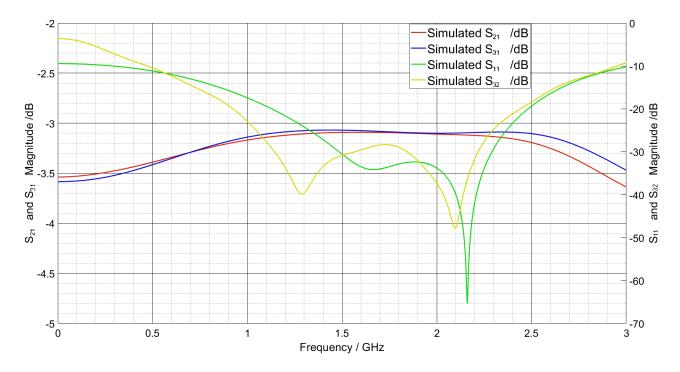

| 3.24 | Simulated wideband coupler S-Parameters after optimisation                                       | 61 |

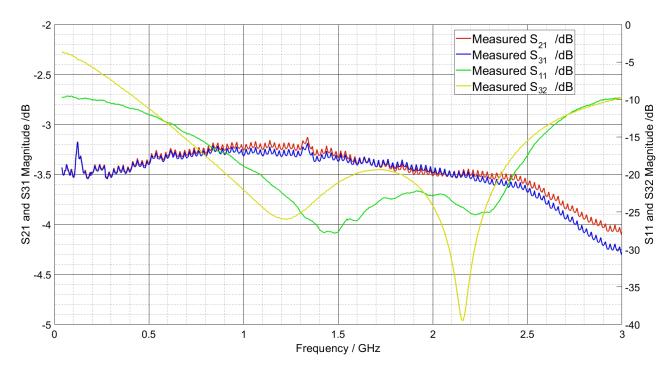

| 3.25 | Manufactured wideband Wilkinson divider measured S-Parameter                                     | 62 |

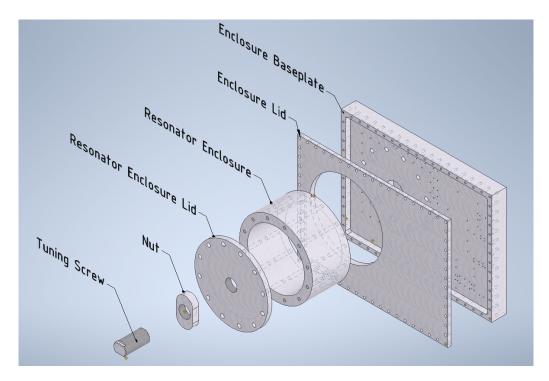

| 3.26 | Autodesk Inventor drawing of metal enclosure.                                                    | 64 |

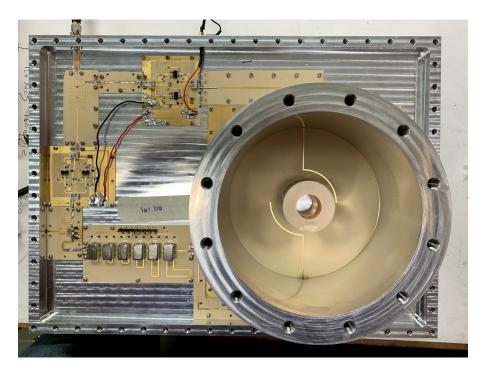

| 3.27 | Birds Eye view of the complete oscillator with lid removed                                       | 65 |

LIST OF FIGURES xvii

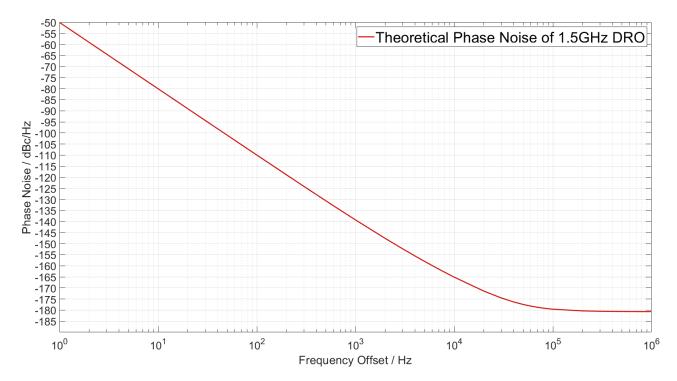

| 3.28 | Theoretical oscillator phase noise calculated using $2.59$ and the parameters from $3.9$                                                                                                                                                                            | 67 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

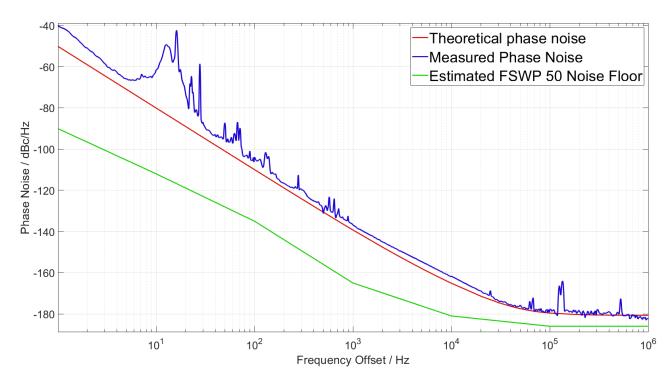

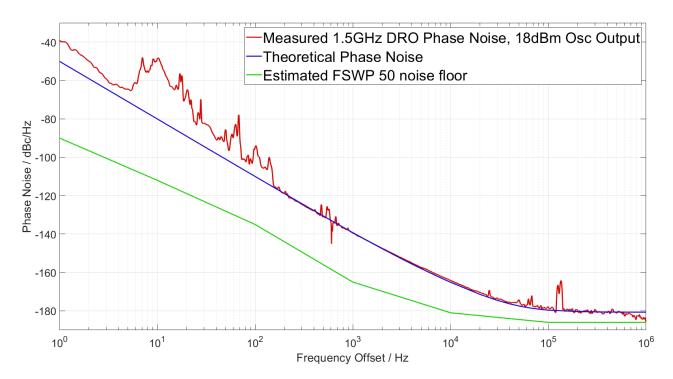

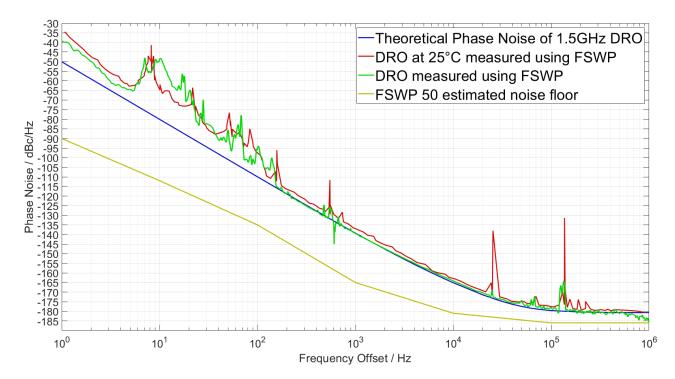

| 3.29 | Initial Oscillator phase noise measurement with theoretical plot                                                                                                                                                                                                    | 69 |

| 3.30 | Best oscillator phase noise measurement with theoretical plot                                                                                                                                                                                                       | 71 |

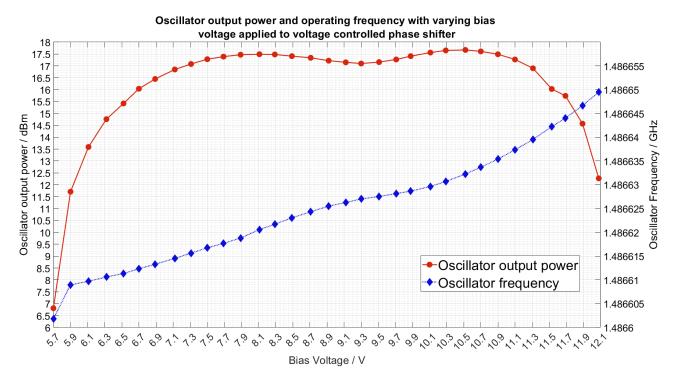

| 3.31 | Oscillator Frequency (solid diamond) and Output power (solid dot) plotted against bias voltage applied to the electronically tunable phase shifter. No output signal from the oscillator was observed outside the bias range 5.7V-12.1V. The frequency tuning range |    |

|      | is 47 kHz                                                                                                                                                                                                                                                           | 72 |

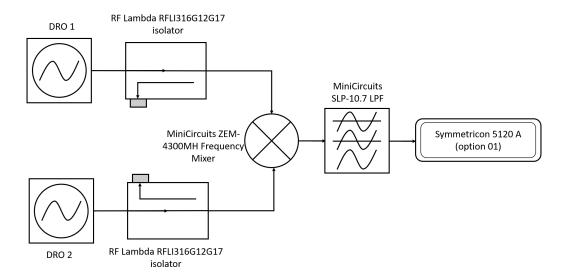

| 3.32 | Block diagram of the measurement setup using the Symmetricom 5120 A phase noise                                                                                                                                                                                     |    |

|      | measurement system. The phase noise of the beat signal is measured in this setup. $$ .                                                                                                                                                                              | 73 |

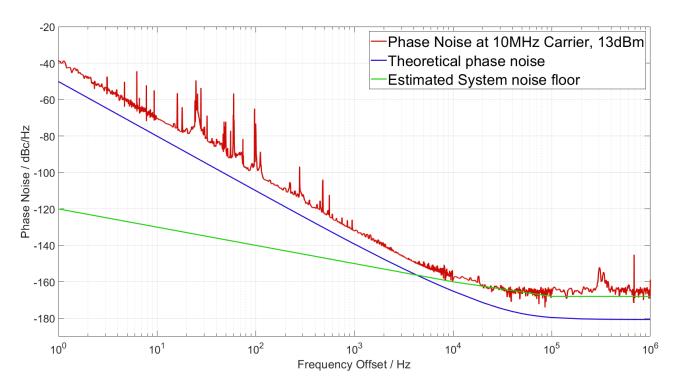

| 3.33 | Oscillator phase noise measurement of two DROs using the Symmetricom $5210\mathrm{A}$ option                                                                                                                                                                        |    |

|      | 01 phase noise measurement system. The measurement was terminated with an error                                                                                                                                                                                     |    |

|      | stating the input frequency had changed significantly                                                                                                                                                                                                               | 74 |

| 3.34 | Original DRO measurement sat at ambient temperature and oscillator phase noise mea-                                                                                                                                                                                 |    |

|      | surement of the DRO placed inside a temperature controlled chamber and held at 25° measurements plotted together                                                                                                                                                    | 76 |

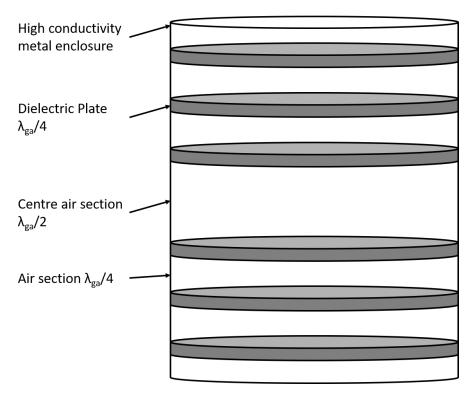

| 4.1  | Periodic DBR diagram with equal $\lambda/4$ air and dielectric sections. An aperiodic DBR                                                                                                                                                                           |    |

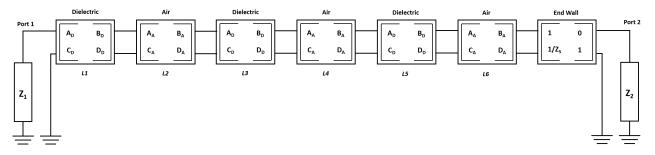

|      | would be optimised such that the size of the sections asymptotically approach $\lambda/4$                                                                                                                                                                           | 82 |

| 4.2  | Series of waveguide ABCD parameter models used to model half of the 6 plate DBR.  The resonator is symmetrical so it is therefore possible to consider half of the sections                                                                                         |    |

|      | in the model                                                                                                                                                                                                                                                        | 82 |

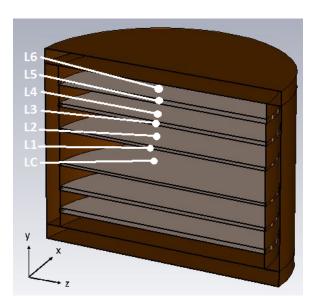

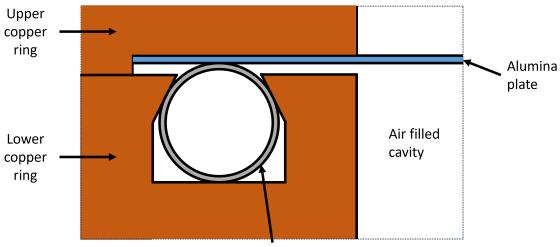

| 4.3  | Cross section of the model of the 16 GHz DBR used in the eignemode simulations with                                                                                                                                                                                 |    |

|      | labelled Air/Dielectric sections that match the labels given in table 4.1                                                                                                                                                                                           | 86 |

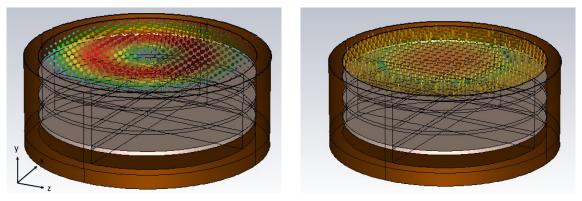

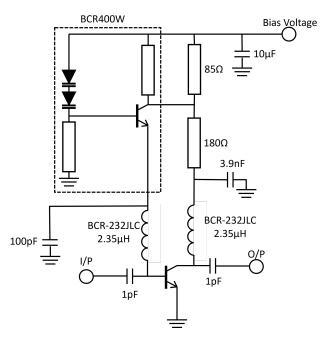

| 4.4  | EM field patterns on the $z=0$ and $y=0$ planes demonstrating the correct field patterns or the $TE_{011}$ mode. The resonant frequency is 15.7872 GHz                                                                                                              | 87 |

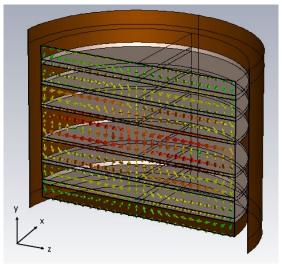

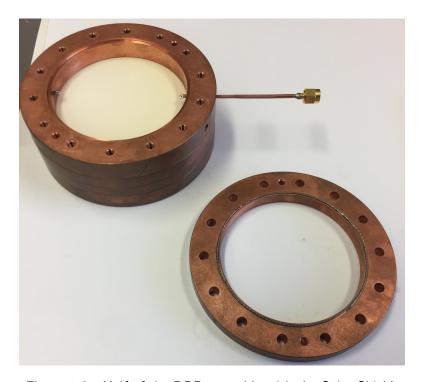

| 4.5  | Cross section of the DBR side wall showing the Spira shield gasket pressing the alumina                                                                                                                                                                             |    |

|      | plate against the upper copper ring                                                                                                                                                                                                                                 | 88 |

| 4.6  | Half of the DBR assembly with the Spira Shield                                                                                                                                                                                                                      | 88 |

xviii LIST OF FIGURES

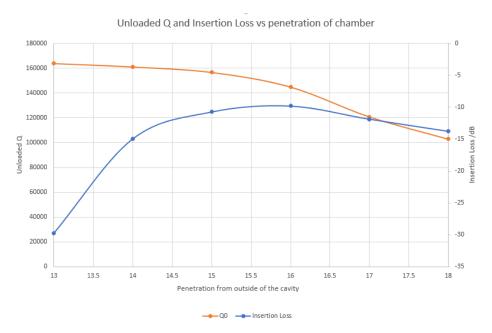

| 4.7  | $\mathbf{Q}_0$ and Insertion loss variation plotted against the penetration of the loop probes into    |     |

|------|--------------------------------------------------------------------------------------------------------|-----|

|      | the cavity                                                                                             | 90  |

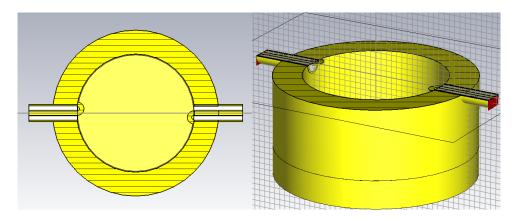

| 4.8  | CST model of the DBR with variable coaxial probes at 5 GHz. The same model was                         |     |

|      | later modified such that the dimensions were smaller and the $\mathrm{TE}_{011}$ mode was resonant     |     |

|      | at 16 GHz                                                                                              | 91  |

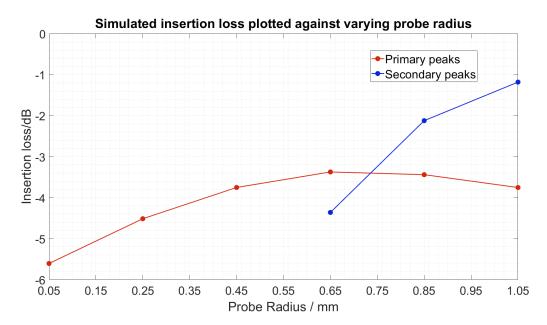

| 4.9  | Simulated insertion loss plotted against bore depth of the probe with constant radius                  |     |

|      | at 16 GHz                                                                                              | 92  |

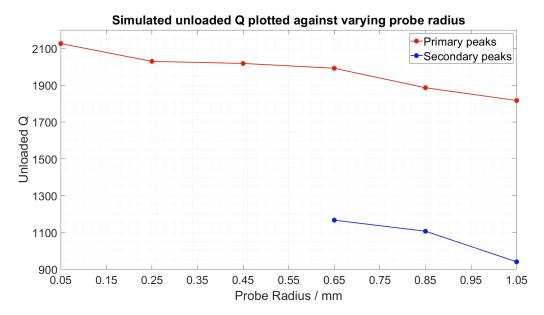

| 4.10 | Calculated $Q_0$ , using (4.16) and simulated $Q_L$ , plotted against the probe bore depth of          |     |

|      | the probe with constant radius at 16 GHz                                                               | 93  |

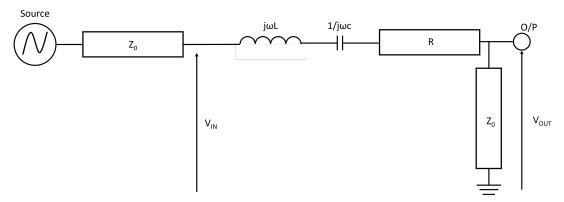

| 4.12 | ADS Schematic for external impedance transformation networks with optimised mi-                        |     |

|      | crostrip lengths and widths. The S2P file created from the measurement of the $16~\mathrm{GHz}$        |     |

|      | DBR is loaded into the 'S2P' ADS component                                                             | 97  |

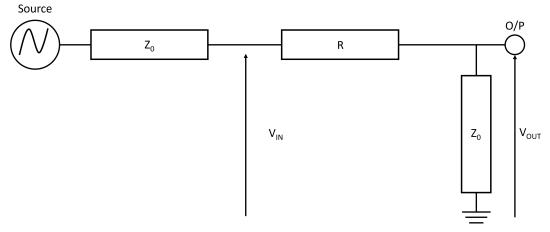

| 4.13 | Measured $S_{21}$ of the resonator (green trace), the simulated $S_{21}$ of the measured $S_{21}$ with |     |

|      | the external matching network designed to reduce the insertion loss to 6dB, (red trace), $$            |     |

|      | and simulated resonant peak with 20% shorter length microstrip lines that accounts for                 |     |

|      | the worst case tolerance in the manufacture                                                            | 98  |

| 4.14 | Manufactured 'identical' probes. These updated probes were manufactured by hand so                     |     |

|      | they cannot be perfectly identical                                                                     | 99  |

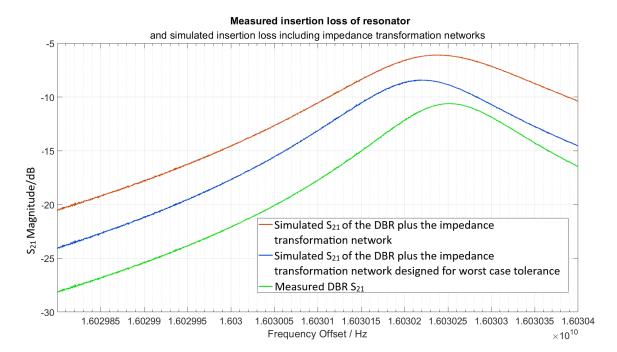

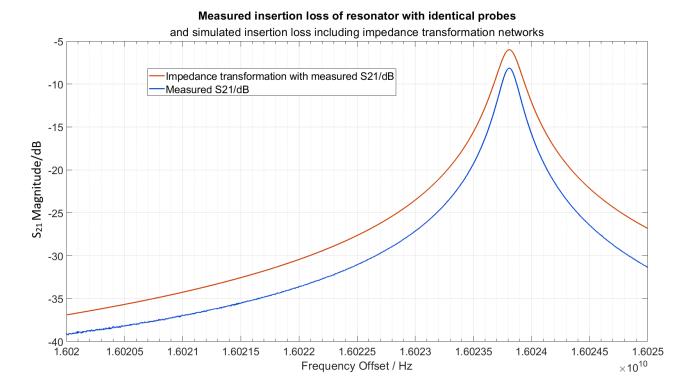

| 4.15 | Measured magnitude of $S_{21}$ of DBR using the new 'identical' probes and simulated                   |     |

|      | magnitude of $S_{21}$ of the impedance transformation network and the S2P file from the                |     |

|      | DBR measurement                                                                                        | 100 |

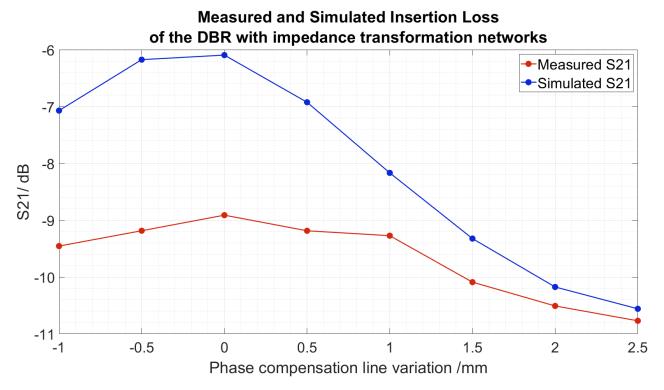

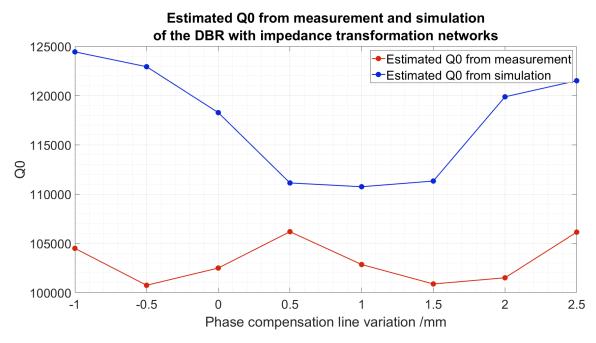

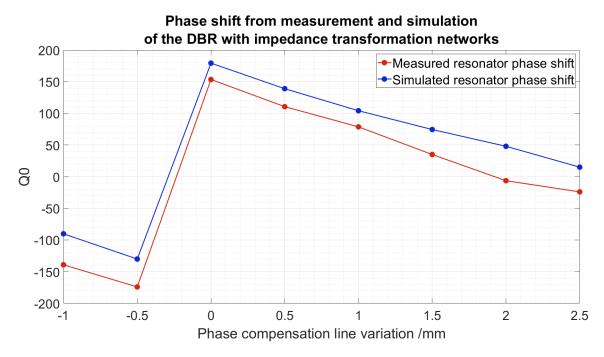

| 4.16 | Measured and simulated resonator insertion loss at resonance with impedance transfor-                  |     |

|      | mation networks connected plotted against varying phase compensation microstrip line                   |     |

|      | length variation.                                                                                      | 102 |

| 4.17 | Measured and simulated resonator unloaded Q at resonance with impedance transfor-                      |     |

|      | mation networks connected                                                                              | 103 |

| 4.18 | Measured and simulated resonator phase shift at resonance with impedance transfor-                     |     |

|      | mation networks connected                                                                              | 104 |

LIST OF FIGURES xix

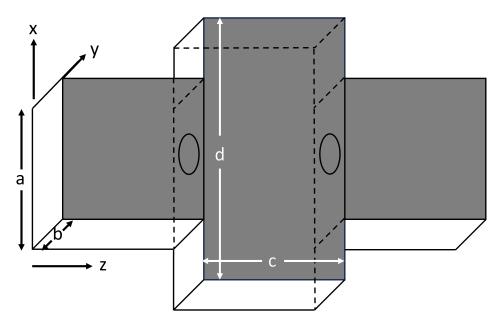

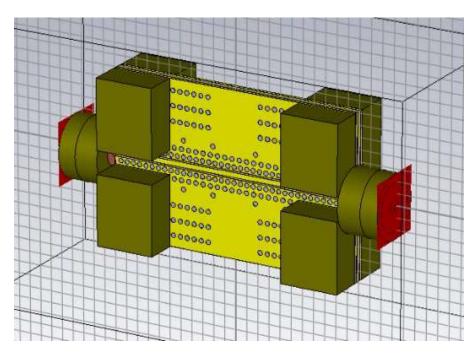

| 4.19 | Two port cavity system taken from [61] and used as the starting point for the design of            |      |

|------|----------------------------------------------------------------------------------------------------|------|

|      | the aperture coupling to the DBR                                                                   | 106  |

| 4.20 | Magnetic field patterns plotted on a plane of $\mathrm{TE}_{101}$ mode in a rectangular cavity and |      |

|      | the $\mathrm{TE}_{011}$ showing the similarities between the H fields in both modes                | 107  |

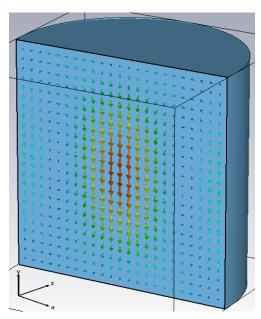

| 4.21 | Autodesk Inventor assembly file generated from the different parts that were designed to           |      |

|      | replace the existing central section of the DBR with waveguide to aperture transitions,            |      |

|      | all parts have been highlighted to emphasise the edges that could be hidden in this view           | .114 |

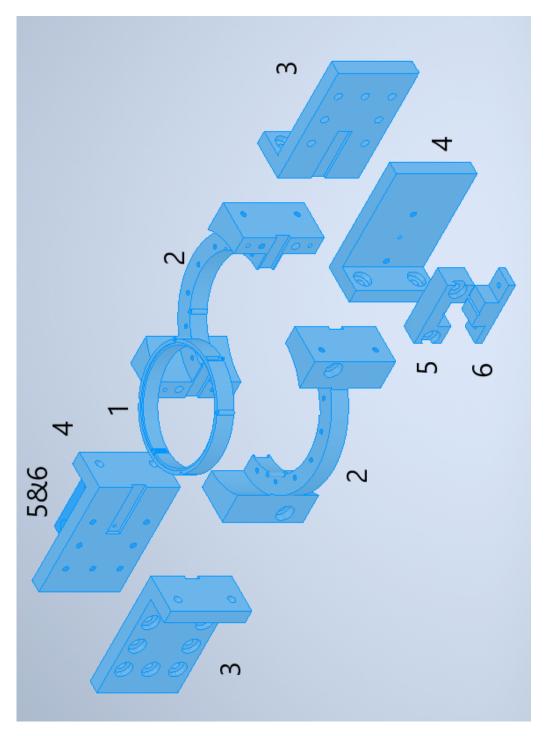

| 4.22 | BFU730 Transistor amplifier schematic using BCR400W active bias                                    | 117  |

| 4.23 | 'Rat Race' Coupler schematic for the coupler arranged such that the two output ports               |      |

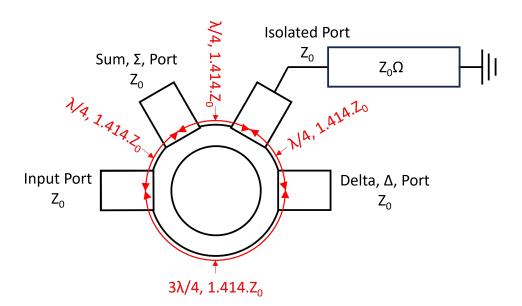

|      | provide equal power in antiphase                                                                   | 120  |

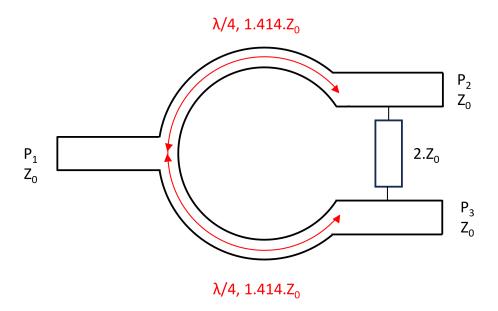

| 4.24 | Wilkinson divider that equally splits the input power between the two output ports                 |      |

|      | with equal phase of the output signals                                                             | 121  |

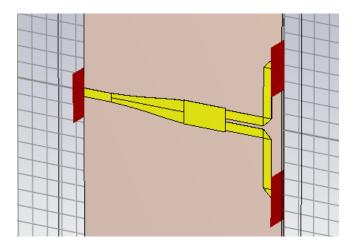

| 4.25 | CST model of the 2 Way splitter incorporating the Dolph-Tchebycheff taper designed                 |      |

|      | for use above 16 GHz on Rogers 4350 substrate with maximum permissible reflection                  |      |

|      | coefficient of -30dB. All ports present 50 $\Omega$ impedance                                      | 124  |

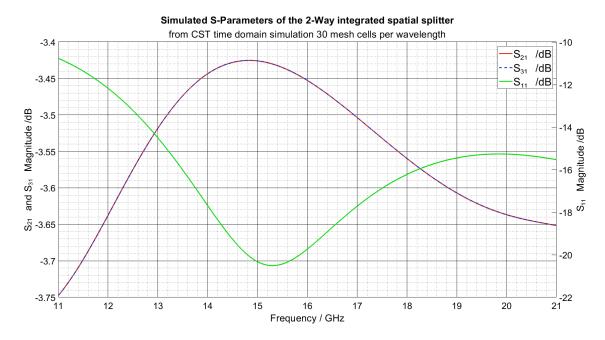

| 4.26 | Simulated S-Parameters of the modelled circuit. The return loss of the whole structure             |      |

|      | is 10dB less than the expected return loss of the taper, this can be attributed to the             |      |

|      | sharp transition from $25\Omega$ microstrip to 2 $50\Omega$ microstrip lines. The large impedance  |      |

|      | change has caused some of the propagating signal to reflect                                        | 125  |

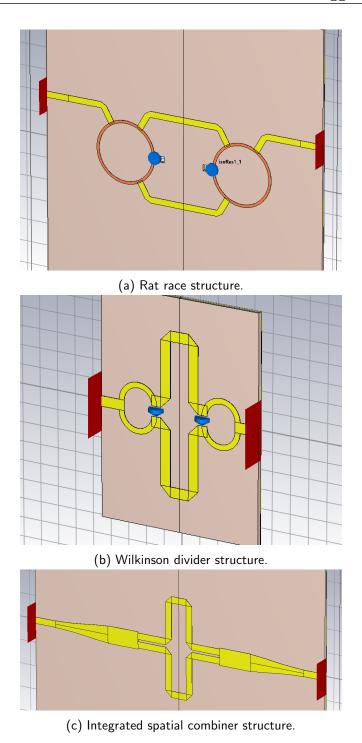

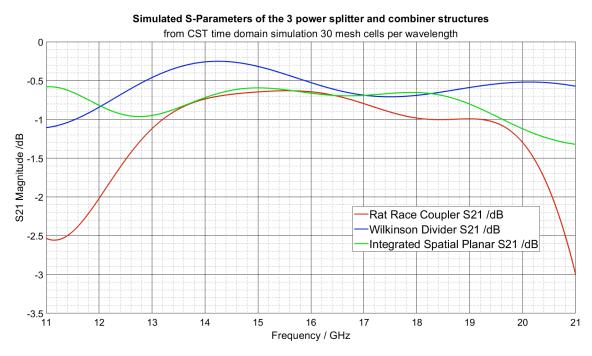

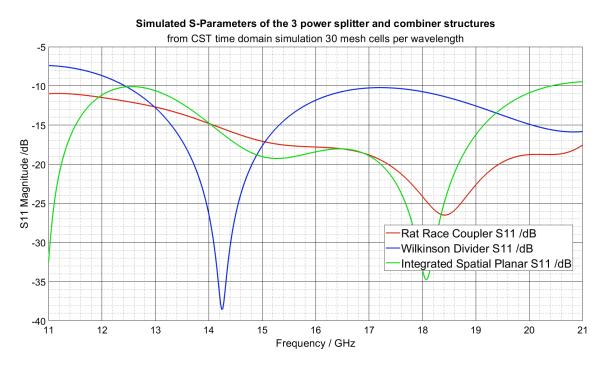

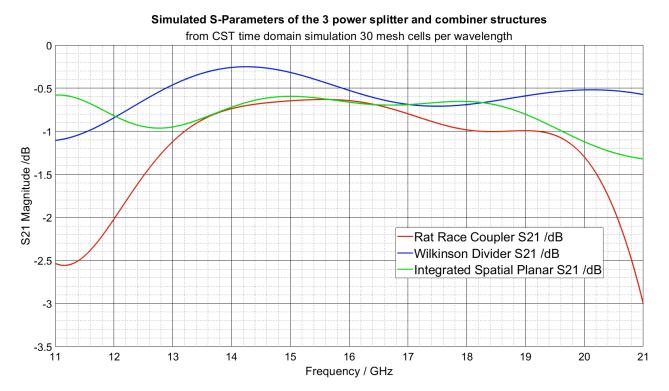

| 4.27 | 3 back to back models used to simulate the S-Parameters of the power splitting and                 |      |

|      | combining structures                                                                               | 126  |

| 4.28 | Simulated insertion loss of the three 2-way power splitting and combining structures               | 127  |

| 4.29 | Simulated return loss of the three 2-way power splitting and combining structures                  | 127  |

| 4.30 | The 3 4-Way power splitting and dividing models used to simulate the S-Parameters of               |      |

|      | the power splitting and combining structures                                                       | 129  |

XX LIST OF FIGURES

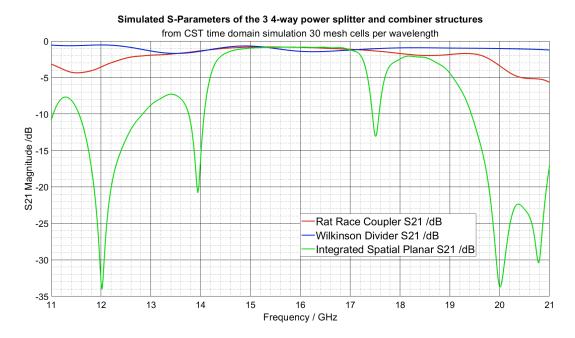

| 4.31 | Simulated $S_{21}$ for the 3 types of splitter/combiners where the power is divided between                   |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

|      | four ports before recombining through a mirror of the power dividers. The length of                           |     |

|      | microstrip used at the output ports of the splitting stage are determined by the Marki                        |     |

|      | APM 6849SM PCB footprint for all designs. Additional lengths of microstrip were                               |     |

|      | added to the integrated spatial planar design to ensure the phase of the four output                          |     |

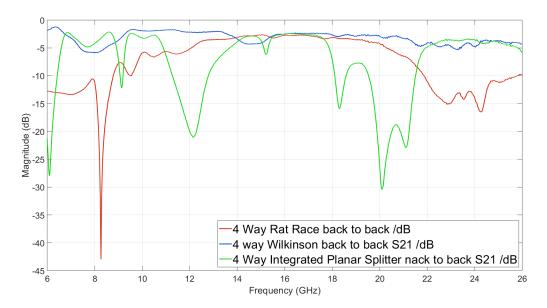

|      | signals from the splitting stage were in phase                                                                | 131 |

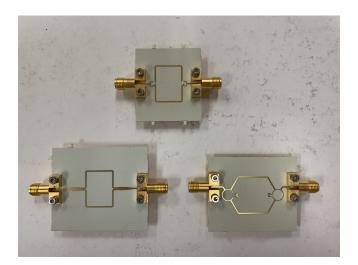

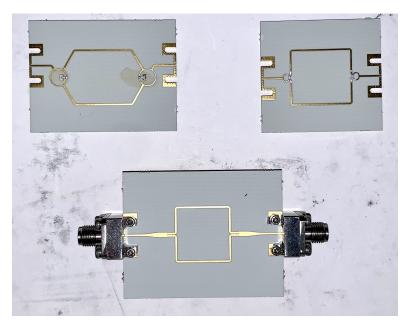

| 4.32 | Back-to-back (clockwise from top), Wilkinson divider, Rat Race Coupler and Integrated                         |     |

|      | planar spatial power combiner                                                                                 | 131 |

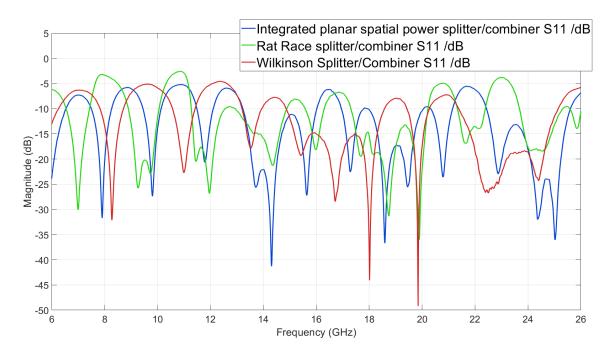

| 4.33 | Measured insertion loss of three back-to-back power dividing structure                                        | 132 |

| 4.34 | Measured return loss of three back-to-back power dividing structure                                           | 133 |

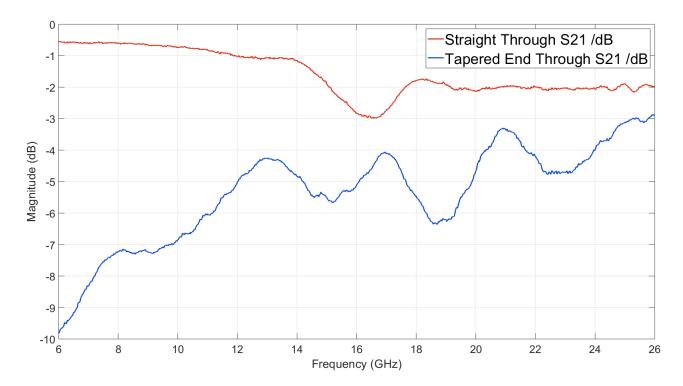

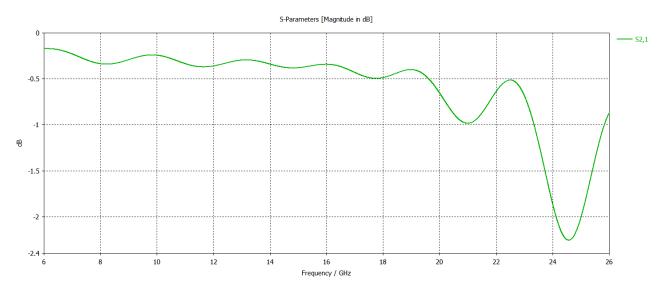

| 4.35 | CPWG Through test board measurements                                                                          | 134 |

| 4.36 | CST Simulated $S_{21}$ varying the width of the taper between the designed taper value                        |     |

|      | and taking the CPWG to the end of the board                                                                   | 135 |

| 4.37 | CST model of the straight through board with varying taper width                                              | 135 |

| 4.38 | CST model of the through board including Rosenberger connector model                                          | 136 |

| 4.39 | Simulated insertion loss of the through board with the Rosenberger SMA connector                              |     |

|      | model                                                                                                         | 137 |

| 4.40 | Measured insertion and return loss of the demo board obtained from With<br>Wave. $\ . \ . \ .$                | 137 |

| 4.41 | Image of the microstrip test boards with both the air core WithWave $2.92 \mathrm{mm}$ connector              |     |

|      | (top) and the PTFE core Rosenberger SMA connector (bottom)                                                    | 138 |

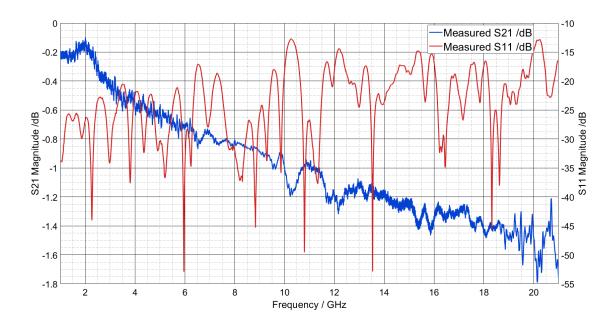

| 4.42 | Measured insertion loss and return loss of the same straight through piece of microstrip                      |     |

|      | with the two different connectors                                                                             | 139 |

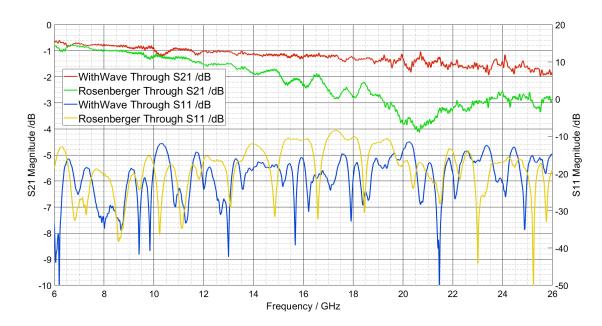

| 4.43 | Measured $\mathrm{S}_{21}$ and $\mathrm{S}_{11}$ for both amplifier modules with the two different connectors | 140 |

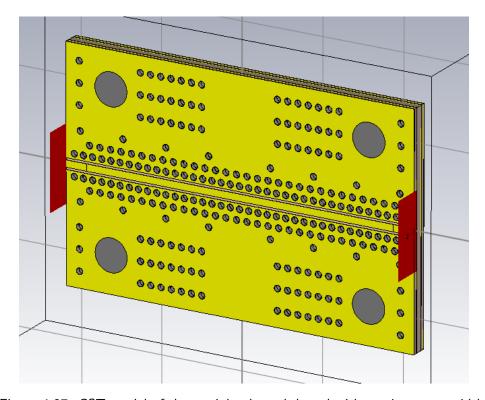

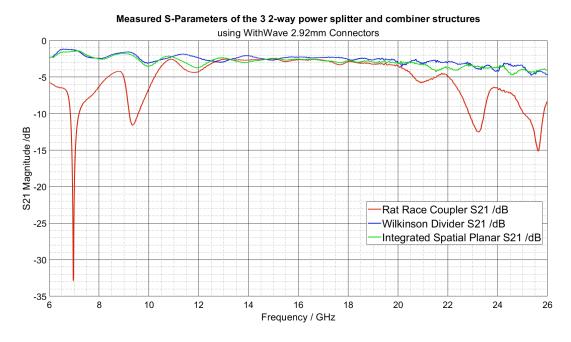

| 4.44 | Updated PCBs including the landing pattern for the WithWave connectors                                        | 141 |

| 4.45 | Measured insertion loss of the 3 power and splitter combiner structures with the With-                        |     |

|      | Wave connectors                                                                                               | 141 |

| 4 46 | Simulated insertion loss of the three 2-way power splitting and combining structures                          | 149 |

LIST OF FIGURES xxi

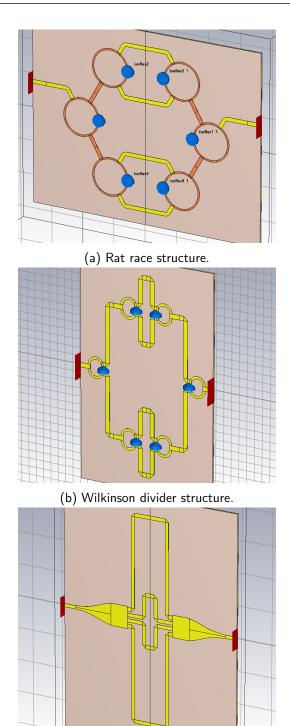

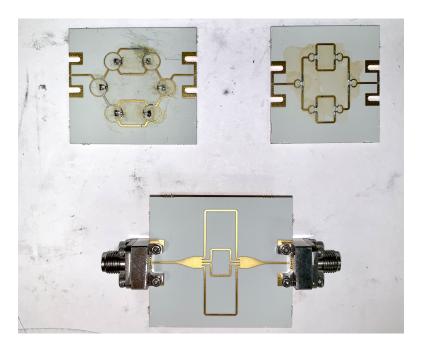

| 4.47 | 4 Way power splitter and combiner networks with WithWave connectors. Clockwise                   |      |

|------|--------------------------------------------------------------------------------------------------|------|

|      | from the top left is the Rat Race structure, the Wilkinson divider structure and the             |      |

|      | integrated spatial planar combiner structure                                                     | 143  |

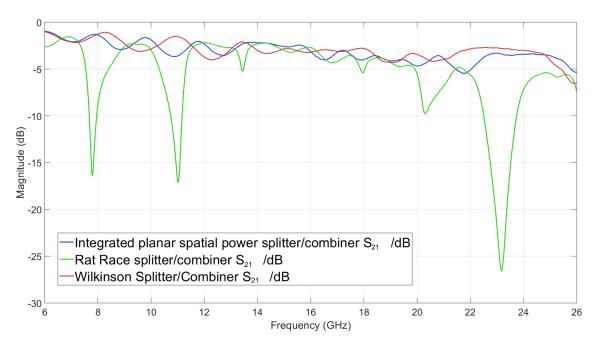

| 4.48 | Comparison of $S_{21}$ for the 3 types of splitter/combiners where the power is divided          |      |

|      | between four ports before recombining through a mirror of the power dividers                     | 144  |

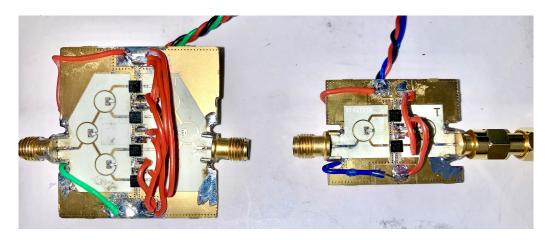

| 4.49 | Image of the parallel amplifiers with four (left) and two (right) devices and the Johnson-       |      |

|      | Cinch 2.92mm connectors                                                                          | 145  |

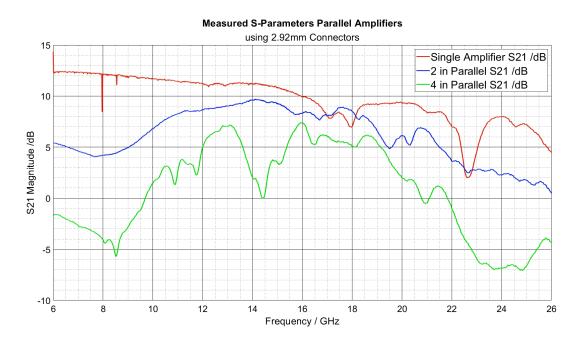

| 4.50 | Measured Gain of the parallel amplifiers, the single stage amplifier is included for com-        |      |

|      | parison                                                                                          | 146  |

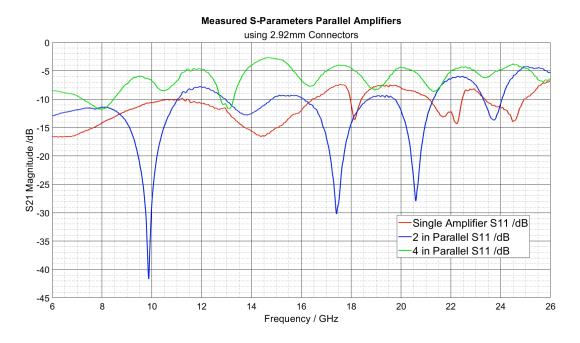

| 4.51 | Measured return loss of the parallel amplifiers, the single stage amplifier is included for      |      |

|      | comparison                                                                                       | 146  |

| 4.52 | Residual phase noise measurements of the $3$ amplifiers plotted with the measured system         |      |

|      | noise floor for a power level of 7.5dBm to the input mixer. 10,000 correlations were made.       | .149 |

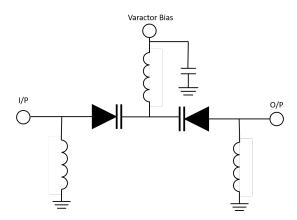

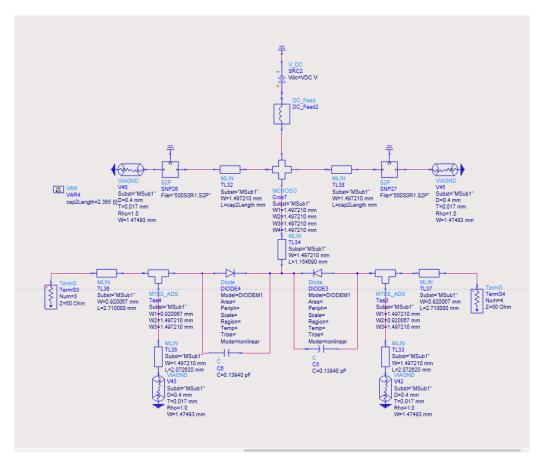

| 4.53 | Electronically Tunable Phase shifter circuit diagram                                             | 150  |

| 4.54 | Electronically tunable phase shifter model used in ADS to simulated the frequency                |      |

|      | response of the phase shifter. A SPICE model of the varactor diode was used as well              |      |

|      | as microstrip line models and the ADS model for a via hole                                       | 151  |

| 4.55 | Simulated $S_{21}$ phase $/^{\circ}$ and magnitude $/dB$ when $VBias = 7V. \dots \dots \dots$    | 152  |

| 4.56 | Notch at 8 GHz caused by the biasing network of the phase shifter                                | 153  |

| 4.57 | L-R Manufactured 16 GHz phase shifters using MACOM MAVR-000120-1411 varactor                     |      |

|      | diodes 0402 size decoupling 0.1pF capacitors, MACOM MA46H120 varactor diodes with                |      |

|      | 0402 size decoupling capacitors, MACOM MAVR-000120-1411 varactor diodes $0201$ size              |      |

|      | decoupling $0.1\mathrm{pF}$ capacitors and MACOM MA46H120 varactor diodes with $0201$ size       |      |

|      | decoupling capacitors                                                                            | 154  |

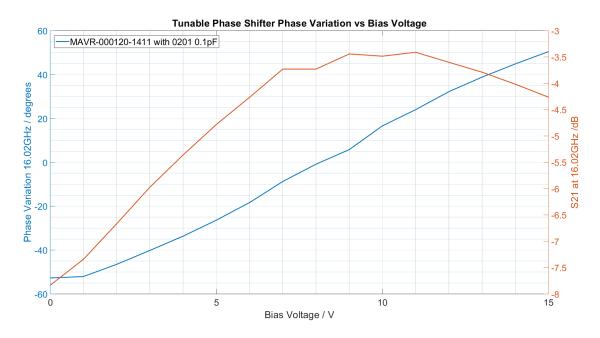

| 4.58 | Measured insertion loss and phase plotted against varying bias voltage for the $16~\mathrm{GHz}$ |      |

|      | phase shifter using MAVR-000120-1411 varactor diodes 0201 size decoupling $0.1 \mathrm{pF}$ ca-  |      |

|      | pacitors                                                                                         | 155  |

xxii LIST OF FIGURES

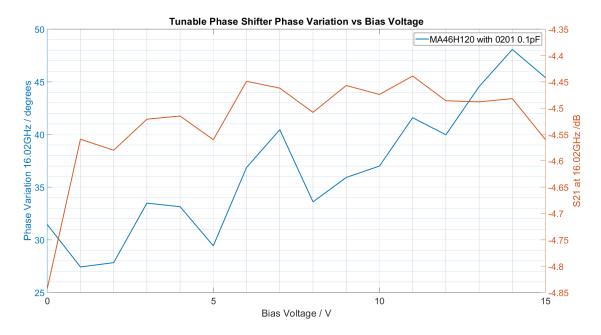

| 4.59 | Measured insertion loss and phase plotted against varying bias voltage for the 16 GHz            |     |

|------|--------------------------------------------------------------------------------------------------|-----|

|      | phase shifter using MACOM MA46H120 varactor diodes with 0201 size decoupling                     |     |

|      | capacitors                                                                                       | 155 |

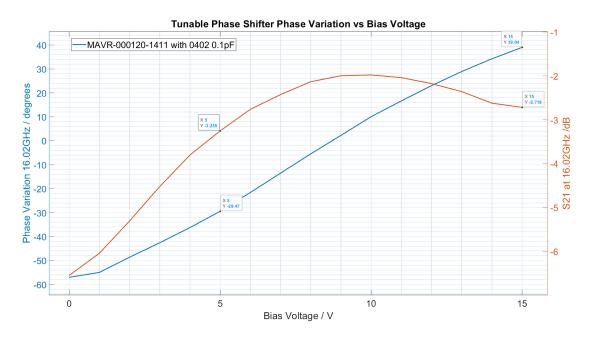

| 4.60 | Measured insertion loss and phase plotted against varying bias voltage for the $16~\mathrm{GHz}$ |     |

|      | phase shifter using MAVR-000120-1411 varactor diodes 0402 size decoupling 0.1pF ca-              |     |

|      | pacitors                                                                                         | 157 |

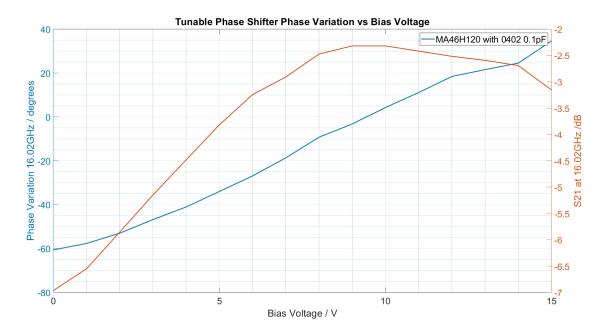

| 4.61 | Measured insertion loss and phase plotted against varying bias voltage for the $16~\mathrm{GHz}$ |     |

|      | phase shifter using MACOM MA46H120 varactor diodes with $0402$ size decoupling                   |     |

|      | capacitors                                                                                       | 157 |

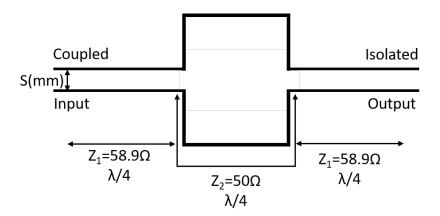

| 4.62 | Circuit diagram for broadband directional coupler                                                | 158 |

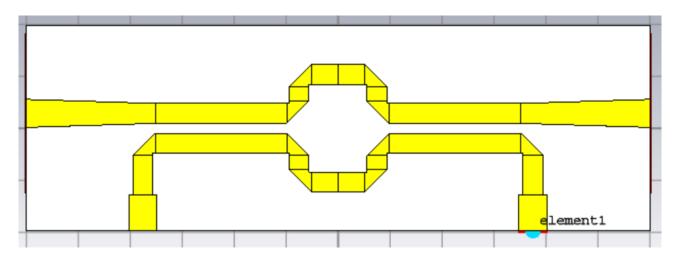

| 4.63 | CST model for broadband directional coupler used to optimise the separation between              |     |

|      | the input and output lines and the dimensions of the microstrip lines                            | 160 |

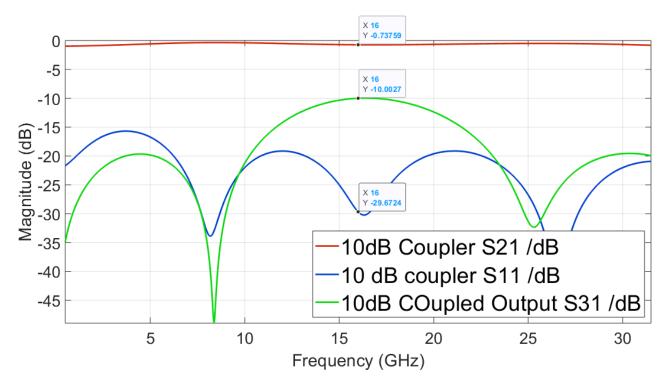

| 4.64 | Simulated S-Parameters of the CST model for the 10dB directional coupler                         | 161 |

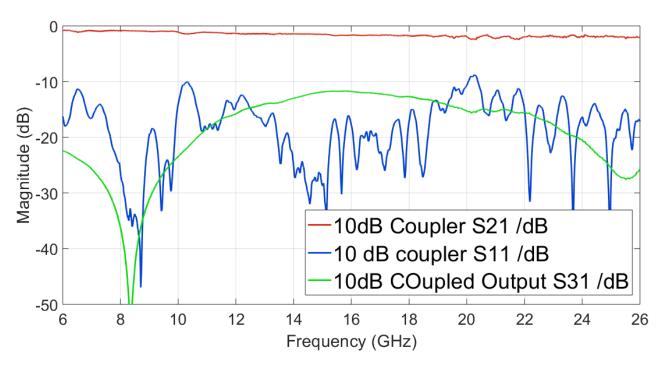

| 4.65 | Measured S-Parameters of the CST model for the 10dB directional coupler                          | 161 |

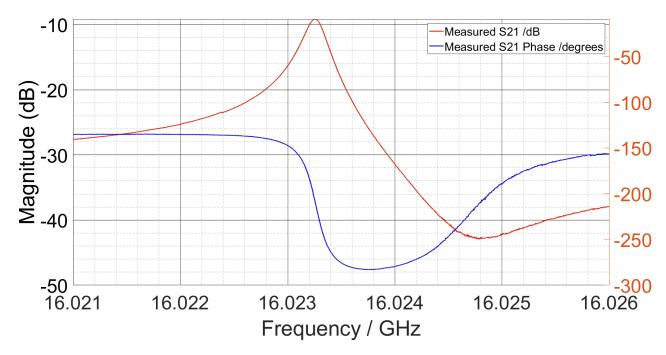

| 4.66 | Measured insertion loss of the resonant peak at 16.02 GHz                                        | 162 |

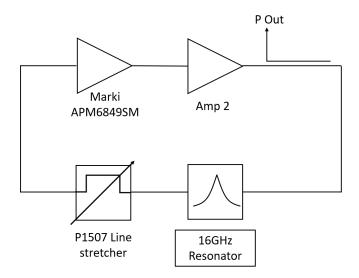

| 4.67 | Typical oscillator configuration block diagram. Amplifier 2 is changed for each mea-             |     |

|      | surement and consists of different number of parallel amplifiers/series attenuators/series       |     |

|      | amplifiers                                                                                       | 163 |

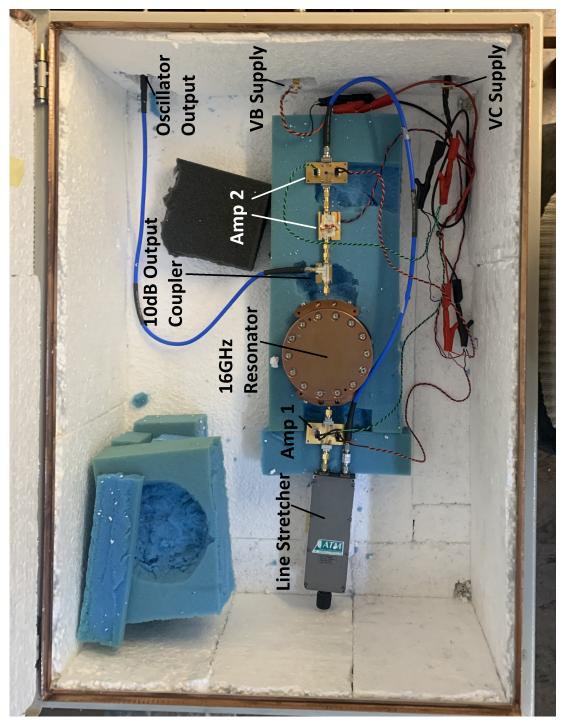

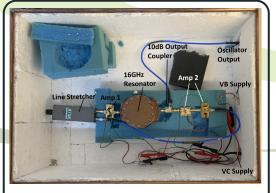

| 4.68 | 16 GHz oscillator placed in shielding box and surrounded by foam. In this image 'Amp             |     |

|      | $2^{\circ}$ is a series combination of a single APM6849 and the PCB with two APM6849 devices     |     |

|      | in parallel. A 6dB attenuator is placed before the single amplifier, after the line stretcher    |     |

|      | to reduce the excess gain in the loop and therefore reduce the saturation of the devices.        | 165 |

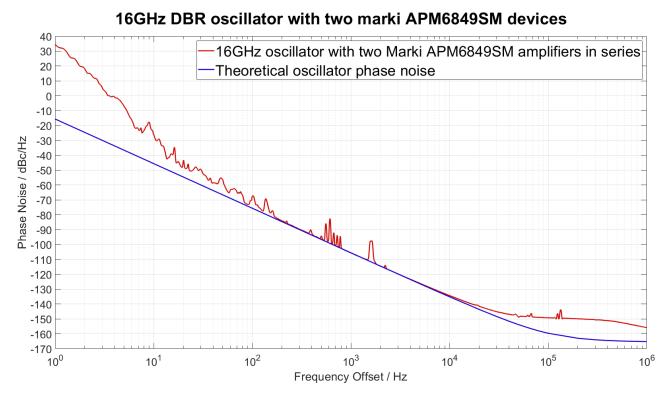

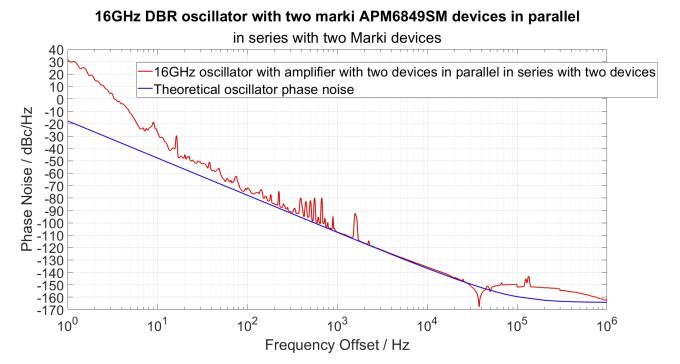

| 4.69 | Measured 16 GHz DBR oscillator where 'Amp 2' is a single Marki APM6849SM device.                 |     |

|      | This configuration therefore has two of the Marki devices in the feedback loop separated         |     |

|      | by the line stretcher and the SMA to SMA coaxial cable. $\hdots$                                 | 166 |

| 4.70 | Measured 16 GHz DBR oscillator where 'Amp 2' is a series combination of a 6dB                    |     |

|      | attenuator, a single Marki APM6849SM device and the amplifier with two devices                   |     |

|      | placed in parallel                                                                               | 168 |

LIST OF FIGURES xxiii

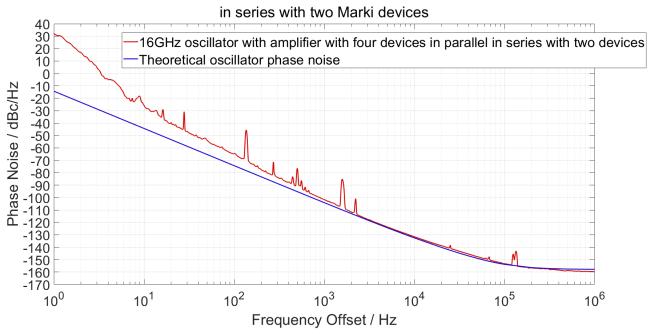

| 4.71 | Measured 16 GHz DBR oscillator where 'Amp 2' is a series combination of a 6dB                                                                                                                                                                                                                                                                            |       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | attenuator, a single Marki APM6849SM device and the amplifier with four devices                                                                                                                                                                                                                                                                          |       |

|      | placed in parallel                                                                                                                                                                                                                                                                                                                                       | 170   |

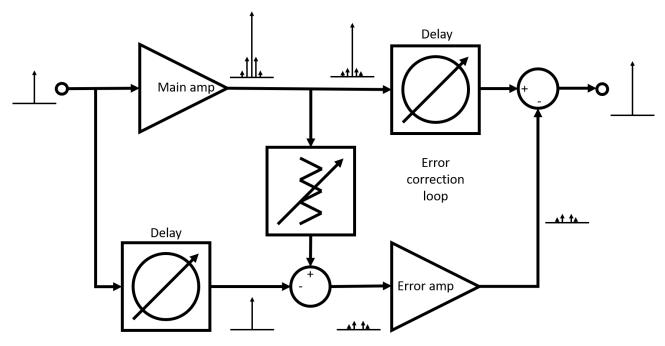

| 5.1  | Feedforward basic operation principle                                                                                                                                                                                                                                                                                                                    | 174   |

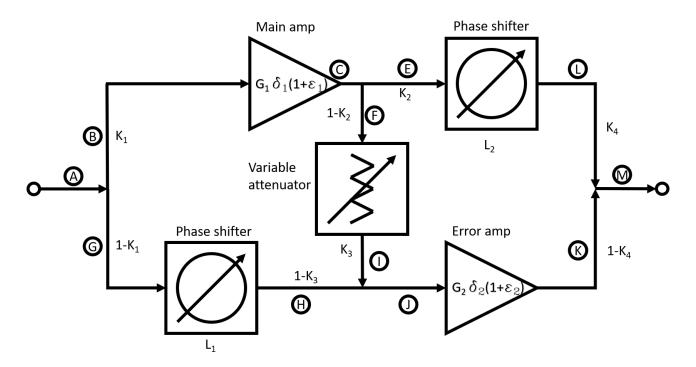

| 5.2  | Simplified Feedforward Amplifier                                                                                                                                                                                                                                                                                                                         | 177   |

| 5.3  | Phasor plot of the loop cancellation                                                                                                                                                                                                                                                                                                                     | 181   |

| 5.4  | Loop cancellation with varying amplitude and phase error                                                                                                                                                                                                                                                                                                 | 182   |

| 5.5  | ADS harmonic balance simulation of single stage amplifier used to simulate the amplifier residual phase noise                                                                                                                                                                                                                                            | 186   |

| 5.6  | Plot of the simulated residual phase noise of the amplifier. The far from carrier noise is $-152 dBc/Hz$ which agrees with the theoretical thermal noise floor                                                                                                                                                                                           | 186   |

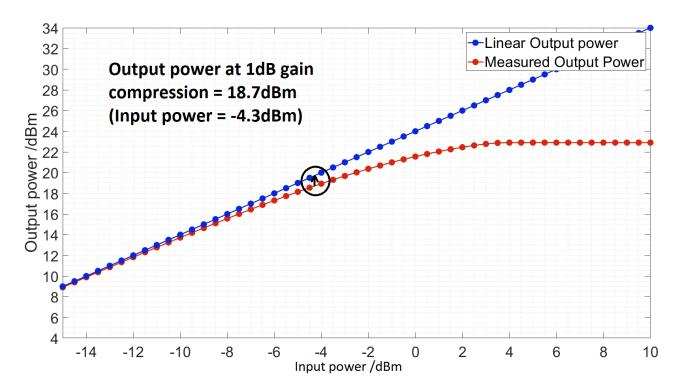

| 5.7  | The simulated output power with increasing input power of the amplifier and the theoretical linear power increase of the amplifier. The plot shows the output power to be 19dBm in 1dB compression and the saturated power to be 25dBm as expected                                                                                                       | 187   |

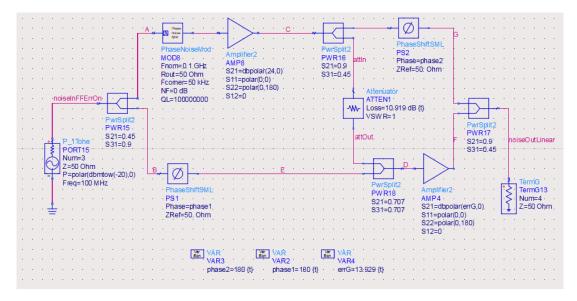

| 5.8  | Simulation model of the feedforward amplifier. The main amplifier and phase noise modulation block are the same as used in the previous simulation. The error amplifier is the same ADS amplifier model but with a different gain. The noise figure of the error amplifier was kept at 5dB. The coupler ratios are $K_{1,4}=7dB~\&~K_2=1dB~\&~K_3=3dB$ . | . 188 |

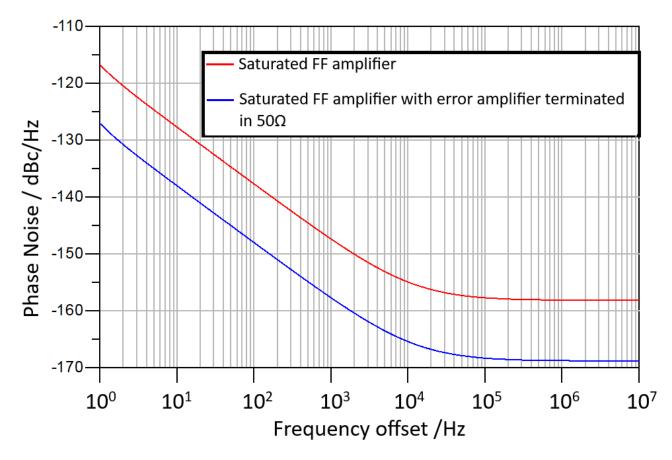

| 5.9  | Simulated residual phase noise of the feedforward amplifier with the error correction loop correctly designed and a residual phase noise plot of the feedforward amplifier with the error correction amplifier removed. The output of the error amplifier and input to coupler $K_4$ were terminated in $50\Omega$ to remove the error correction loop   | 189   |

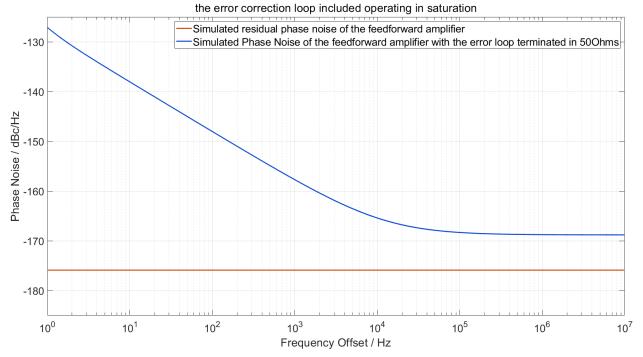

| 5.10 | Simulated resiual phase noise of the saturating ideal feedforward amplifier. The main amplifier is operating in 3dB gain compression and the overall gain has decreased to 1.942dB                                                                                                                                                                       | 190   |

xxiv LIST OF FIGURES

| 5.11 | The simulated residual phase noise plot of the corrected feedforward amplifier with            |      |

|------|------------------------------------------------------------------------------------------------|------|

|      | high input power. The error amplifier cancels the residual phase noise introduced by           |      |

|      | the saturated main amplifier now that the attenuator and error amplifier gain have been        |      |

|      | changed                                                                                        | 192  |

| 5.12 | Broadband feedback design with biasing resistors and load resistor to ensure the device        |      |

|      | will remain stable regardless of the connected load. The shunt load resistor can be            |      |

|      | placed at the input in series though this is generally not preferred as this causes an         |      |

|      | increase in the noise figure                                                                   | 193  |

| 5.13 | Feedforward amplifier design using two ZFL-1000VH+ amplifiers                                  | 195  |

| 5.14 | Calibration spectrum of the amplifier with the error amplifier output terminated in $50\Omega$ | .196 |

| 5.15 | Calibration spectrum of the feedforward with error correction                                  | 197  |

| 5.16 | Feedforward amplifier noise figure measurement setup using the noise figure measure-           |      |

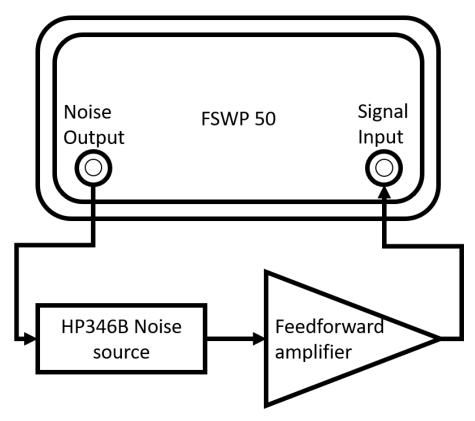

|      | ment mode on the Rohde and Schwarz FSWP 50 phase noise measurement system                      | 198  |

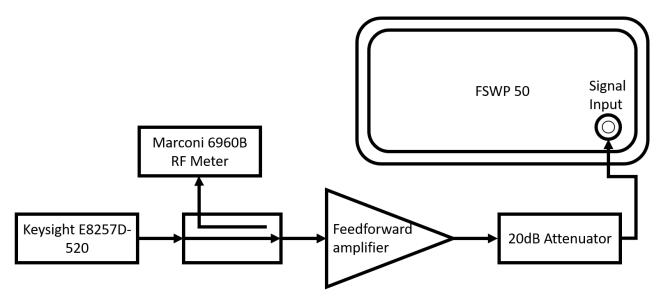

| 5.17 | Output power at 1dB compression measurement setup                                              | 199  |

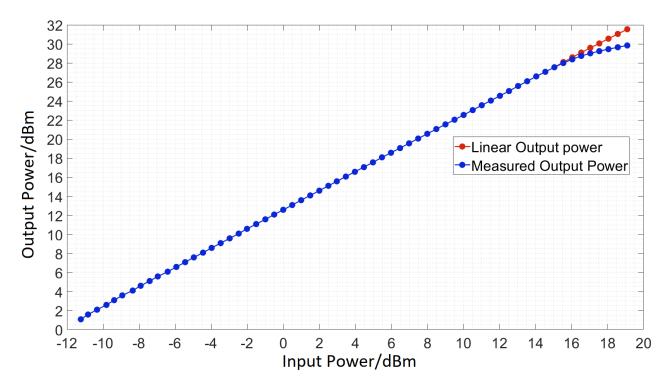

| 5.18 | Output power at 1dB compression measurement plot                                               | 200  |

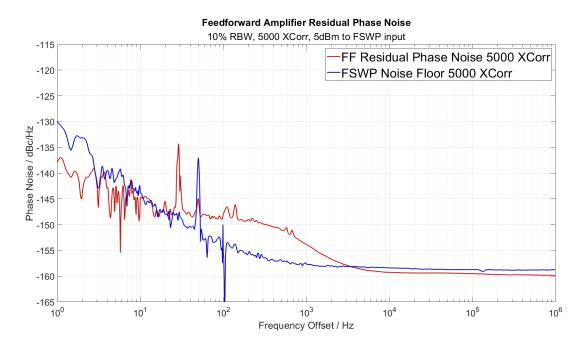

| 5.19 | Feedforward amplifier residual phase noise                                                     | 201  |

| 5.20 | Residual phase noise plots of digital attenuator                                               | 202  |

| 5.21 | MAR-06 schematic as suggested by the manufacturer and the manufactured PCB                     |      |

|      | mounted in an aluminium box. Biasing is via a Filterconn that filters the power lines          |      |

|      | to remove high frequency interference                                                          | 203  |

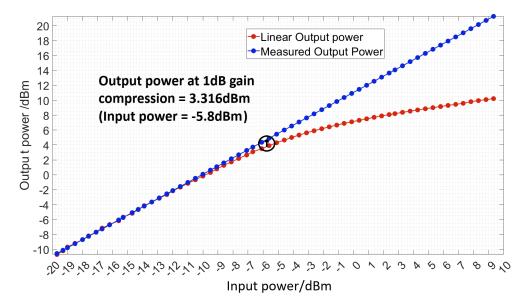

| 5.22 | MAR06 Output power with increasing input power. The output power at 1dB com-                   |      |

|      | pression is 3.316dBm                                                                           | 204  |

| 5.23 | MAR06 gain at 100 MHz with varying bias voltage, -20dBm input power                            | 205  |

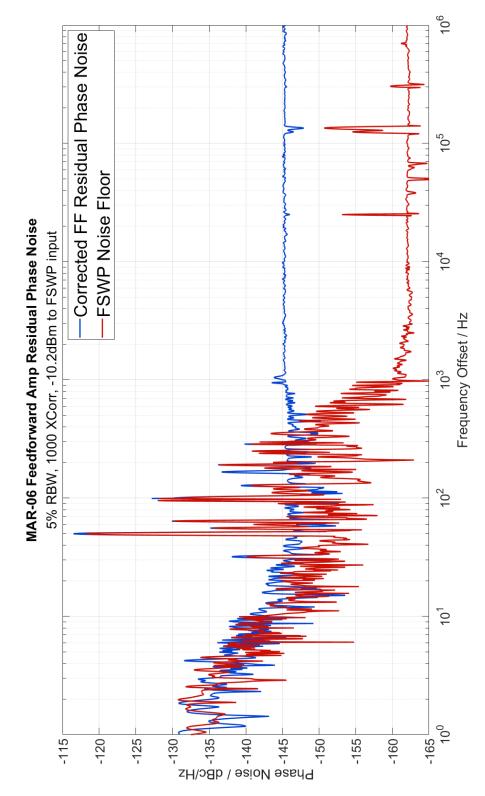

| 5.24 | MAR06 residual phase noise measurement in linear regime. The input power to the                |      |

|      | amplifier was -21.4dBm and the power to the input of the R $\&$ S FSWP for both                |      |

|      | measurements was -0dBm. The measurement was run for 1000 cross correlations with               |      |

|      | a 5% resolution bandwidth                                                                      | 206  |

| 5.25 | Manufactured 100Mhz digital phase shifter housed in an aluminium enclosure. The                |      |

|      | maximum delay this device can switch in to the circuit is 180°                                 | 207  |

LIST OF FIGURES xxv

| 5.26 | 100 MHz phase shifter phase shift and insertion loss plotted against the decimal state                   |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | of the device                                                                                            | 208 |

| 5.27 | 1 Bit digital attenuator design, 6 1 bit sections can be connected in series to increase                 |     |

|      | the attenuation. The resistive $\pi$ networks provide attenuation from 0.1dB to 3.2dB                    |     |

|      | where the previous section presents half the attenuation of the current one so that the                  |     |

|      | attenuator can be controlled with a binary input, similar to the phase shifter design                    | 209 |

| 5.28 | Manufactured digital attenuator housed in an aluminium enclosure                                         | 211 |

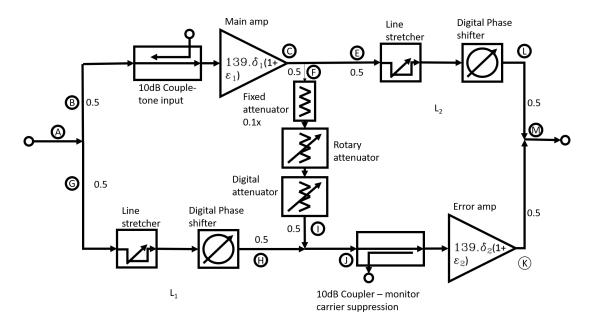

| 5.29 | Complete feedforward schematic with MAR-06 amplifiers, digital attenuation and dig-                      |     |

|      | ital phase shifting                                                                                      | 212 |

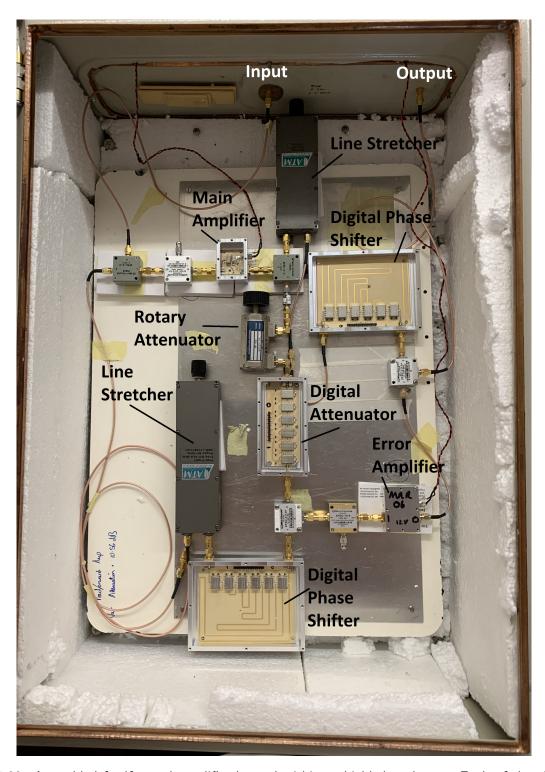

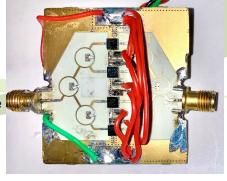

| 5.30 | Assembled feedforward amplifier housed within a shielded enclosure. Each of the circuits                 |     |

|      | is hosed in an aluminium enclosure, the lids are removed in this image to allow for tuning $\frac{1}{2}$ |     |

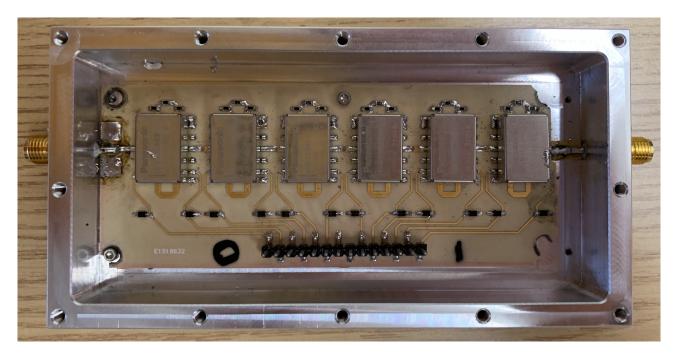

|      | of the amplifier                                                                                         | 213 |

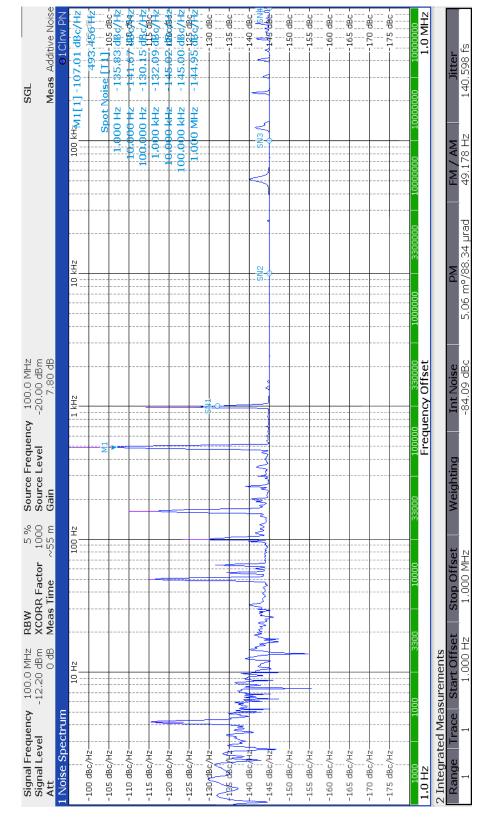

| 5.31 | Screenshot of residual phase noise measurement with calibration tone applied to the                      |     |

|      | system. The tone is at an offset frequency of 294 Hz from the carrier and the measured                   |     |

|      | power at the output relative to the carrier is -107.01<br>dBc/Hz, shown by marker M1                     | 215 |

| 5.32 | Residual phase noise measurement of the calibrated feedforward amplifier with input                      |     |

|      | power -20dBm and the phase noise of the measurement system                                               | 218 |

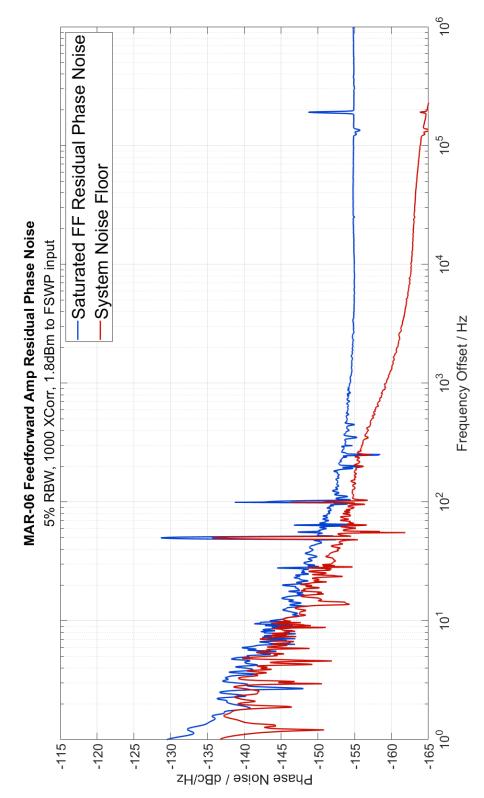

| 5.33 | Residual phase noise measurement of the feedforward amplifier with input power -5dBm                     |     |

|      | in order to saturate the main amplifier. The correcting loop is calibrated for $-20 \mathrm{dBm}$        |     |

|      | input power but the input power was increased to -5dBm in order to cause the main                        |     |

|      | amp to enter saturation. The expected gain compression is 4.2dB                                          | 220 |

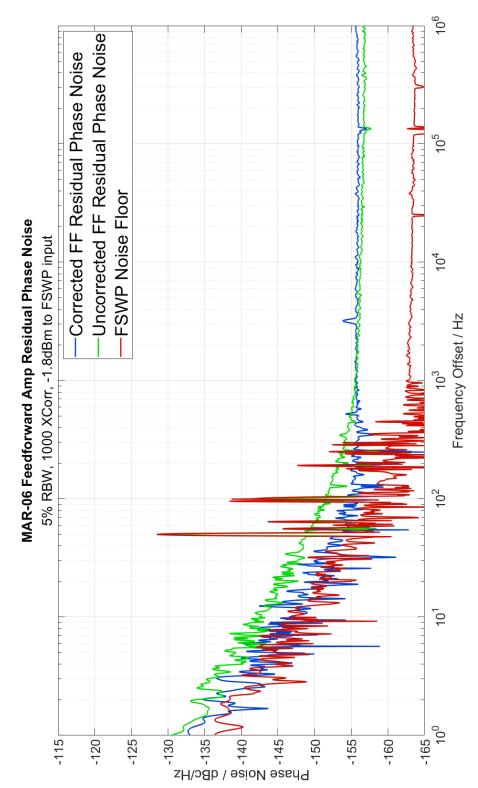

| 5.34 | Residual phase noise measurement of the calibrated feedforward amplifier with input                      |     |

|      | power -5dBm and a residual phase noise plot of the feedforward amplifier with the error                  |     |

|      | amplifier removed. The plot also includes the measured residual phase noise of the R                     |     |

|      | & S FSWP 50 measurement system                                                                           | 223 |

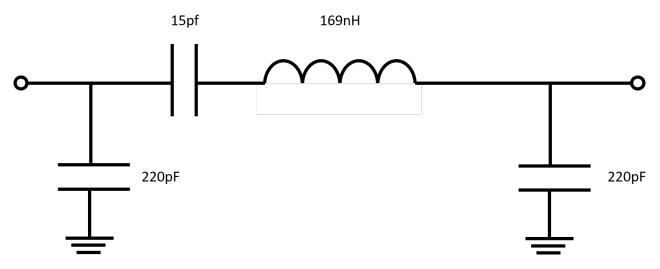

| 5.35 | LC resonator schematic with $Q_L=48.51$ and $S_{21}=-4.45 dB$ at 100 MHz                                 | 225 |

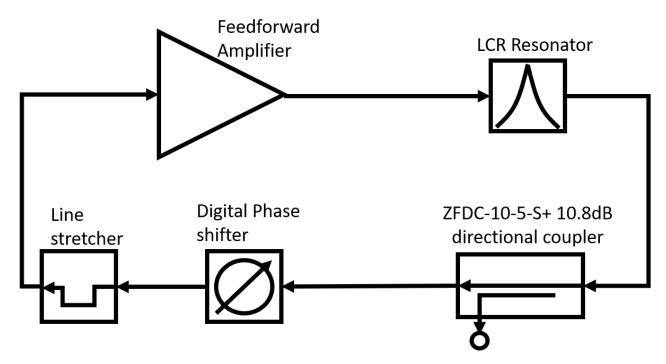

| 5.36 | LC oscillator block diagram with the feedforward amplifier used in the feedback loop.                    | 226 |

xxvi LIST OF FIGURES

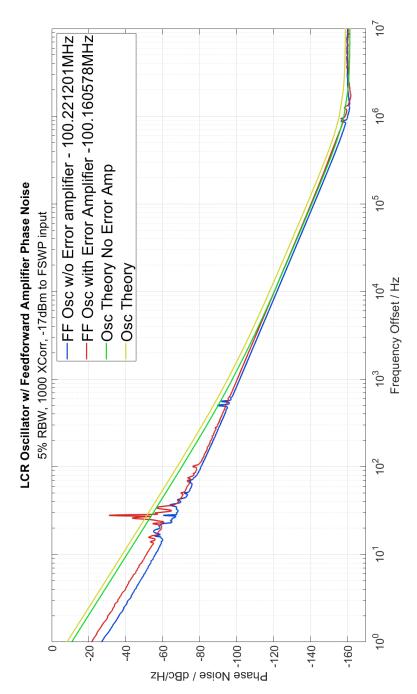

| 5.37 | Measured LC oscillator phase noise with the feedforward amplifier used in the feed-                             |      |

|------|-----------------------------------------------------------------------------------------------------------------|------|

|      | back loop. Two measurements were made, with and without the error correction loop                               |      |

|      | connected. The theoretical oscillator phase noise is calculated based on the measured                           |      |

|      | parameters for both oscillator configurations                                                                   | 229  |

| 5.38 | The feedforward amplifier with the error correction loop removed output power mea-                              |      |

|      | sured with increasing input power. The output power in 1dB compression is $5.5 dBm$ ,                           |      |

|      | for the output power to be -2.363dBm the input power must be approximately -12.2dBm                             | .230 |

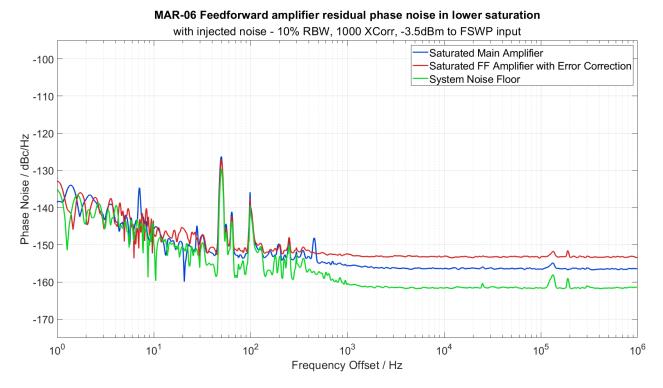

| 5.39 | The residual phase noise measurements of the feedforward amplifier with and without                             |      |

|      | the error correction loop connected. The main amplifier saturation was reduced to ap-                           |      |

|      | proximately $0.1 \mathrm{dB}$ and the output power of the amplifiers was approximately $-2.636 \mathrm{dBm}$    | .231 |

| 5.40 | The residual phase noise measurements of the feedforward amplifier with and without                             |      |

|      | the error correction loop connected with the white noise source injecting noise into the                        |      |

|      | system. The noise introduced into the system is shown to be suppressed by 27dB. $$                              | 233  |

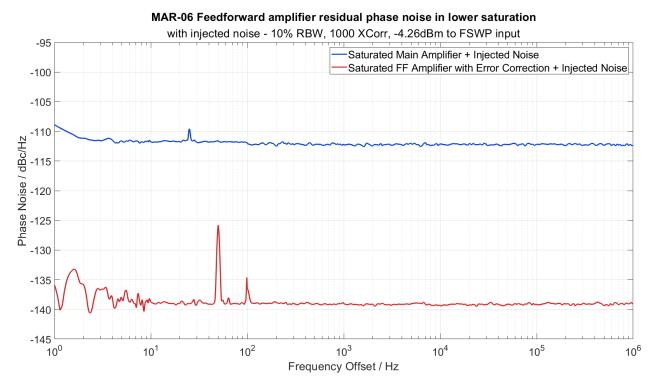

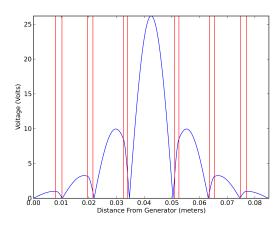

| 5.41 | Oscillator phase noise measurement with noise injected. The phase noise plot is up                              |      |

|      | converted thermal noise that decreases at a rate equal to $\frac{1}{f^2}$ . There is 20dB suppression           |      |

|      | of noise between the two oscillation configurations                                                             | 234  |

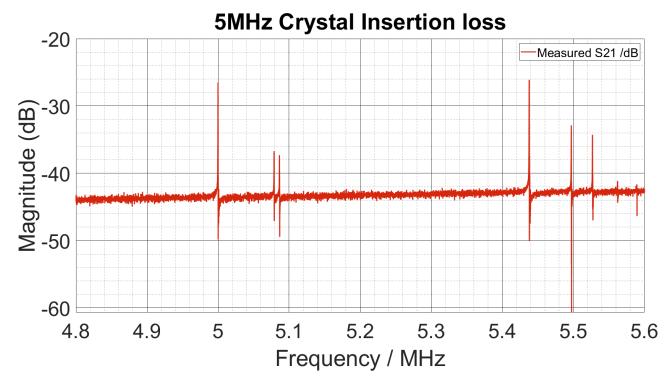

| 6.1  | Broadband sweep $S_{21}$ using USB DG8SAQ vector network analyser [103]. The reso-                              |      |

|      | nance at $4.999818\mathrm{MHz}$ is the required peak to use in the oscillator, the resonance at                 |      |

|      | 5.44 MHz is the unwanted                                                                                        | 238  |

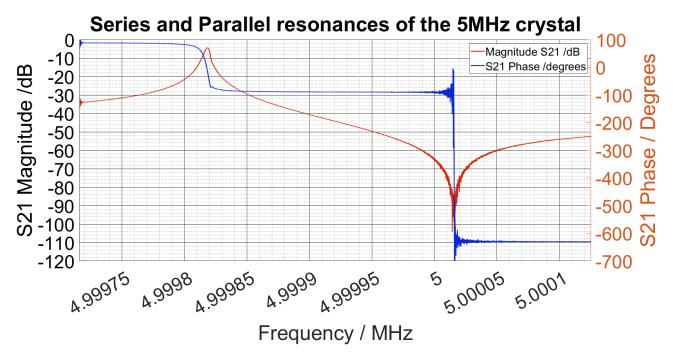

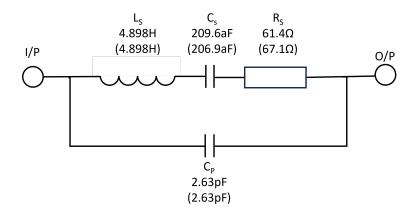

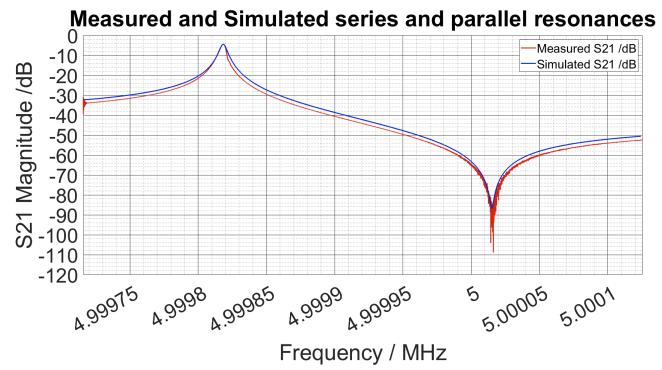

| 6.2  | S-Parameter sweep of the series resonant peak at 4.999 MHz. The insertion loss at                               |      |

|      | resonance is -4.14dB and the $\mathbf{Q}_{l}$ measurement of 950,541. $\mathbf{Q}_{0}$ is then calculated to be |      |

|      | 2,506,315                                                                                                       | 239  |

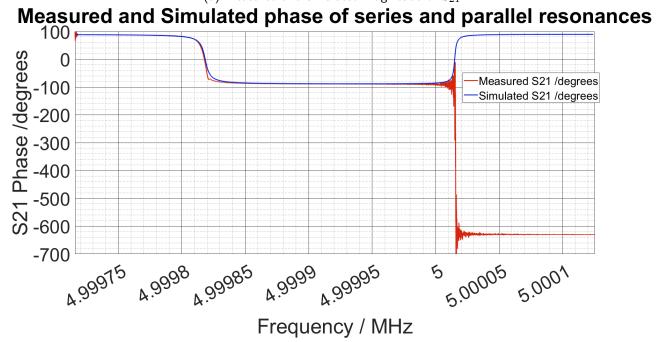

| 6.3  | Quartz crystal LCR model including calculated components and tuned component values                             | .240 |

| 6.4  | Measured and simulated $S_{21}$ of the 5 MHz crystal resonator                                                  | 241  |

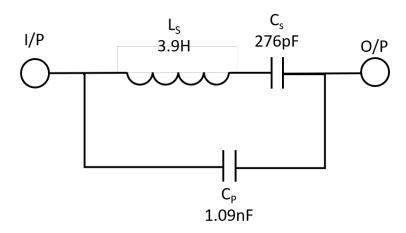

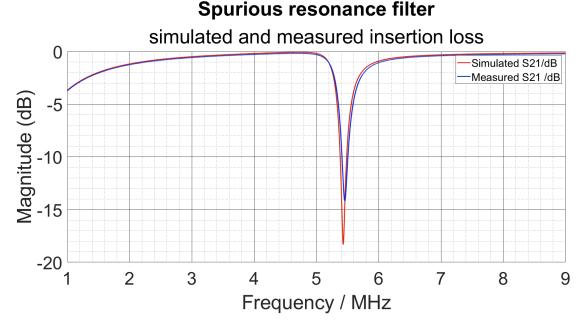

| 6.5  | Schematic of spurious resonance filter                                                                          | 242  |

| 6.6  | Measured and simulated insertion loss of the notch filter                                                       | 243  |

| 6.7  | Long tailed pair differential amplifier with input impedance transformer and variable                           |      |

|      | emitter resistor                                                                                                | 244  |

LIST OF FIGURES xxvii

| 6.8  | Plots of noise voltage and current density plotted against frequency, taken from the                  |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | SSM2210 datasheet [106]                                                                               | 245 |

| 6.9  | Minimum and maximum gain and phase measurement for the differential amplifier                         | 247 |

| 6.10 | $5~\mathrm{MHz}$ oscillator closed loop S-Parameter measurement setup. The oscillator compo-          |     |

|      | nents except for the phase shifter are connected in series to measure the excess gain                 |     |

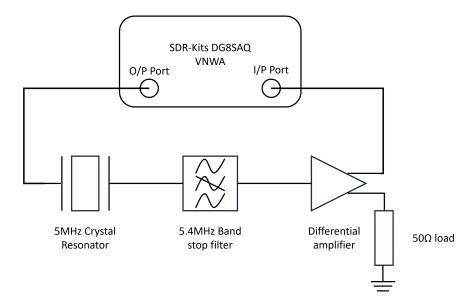

|      | and phase of the loop at 5 MHz                                                                        | 248 |

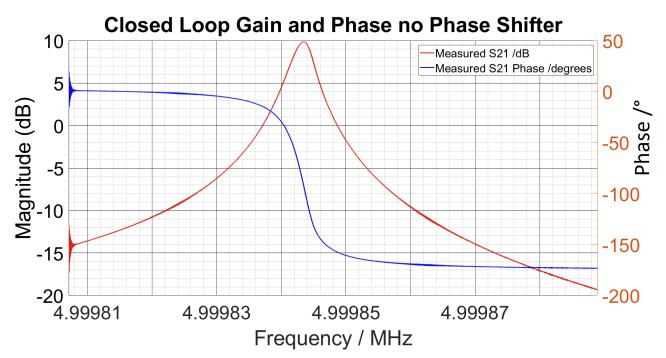

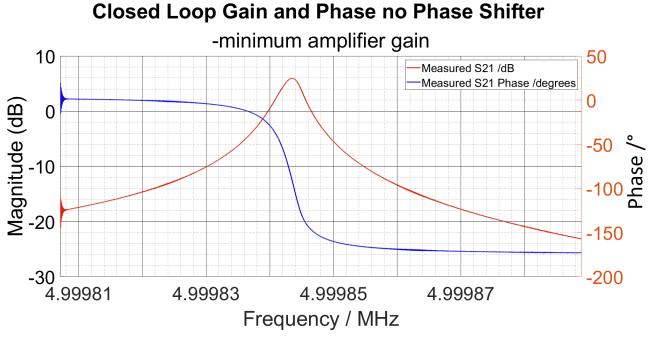

| 6.11 | Closed loop S-Parameter measurements with maximum and minimum amplifier output                        |     |

|      | power                                                                                                 | 249 |

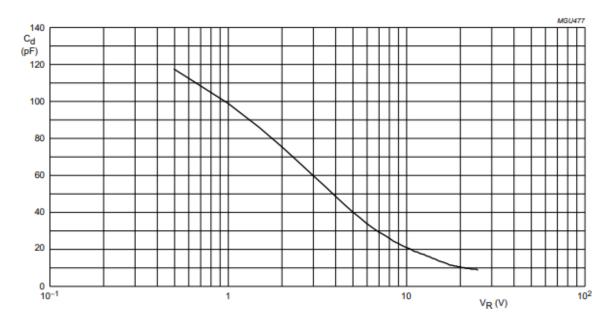

| 6.12 | ${ m CV}$ characteristics of the BB201 varactor diode [108], from 0-12V reverse voltage the           |     |

|      | range of capacitance is from 118pF - 9pF                                                              | 250 |

| 6.13 | 5th order Butterworth high pass filter where $f_0=2.4 \mathrm{MHz}$ and denormalised to $50\Omega.$ . | 251 |

| 6.14 | Modified 5th order Butterworth high pass filter including parallel tunable capacitors to              |     |

|      | model the phase shifter tuning range                                                                  | 251 |

| 6.15 | $5~\mathrm{MHz}$ phase shifter schematic based on a 5th order butter worth high pass filter. A        |     |

|      | 330nF capacitor is used for decoupling, the bias voltage is applied via inductor L2 as                |     |

|      | this is used to isolate the RF line from the DC path                                                  | 252 |

| 6.16 | Measured insertion loss and phase shift of the voltage controlled phase shifters                      | 253 |

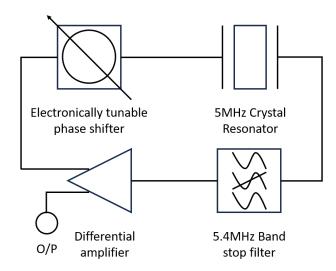

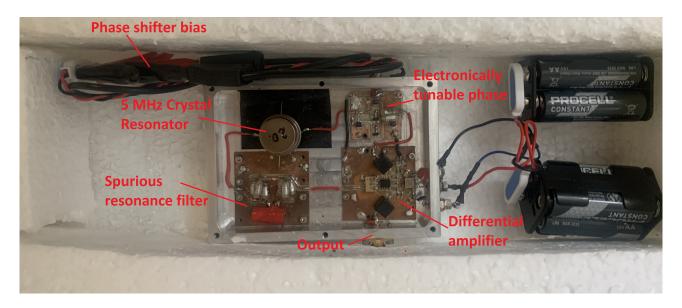

| 6.17 | Complete 5 MHz crystal oscillator block diagram                                                       | 254 |

| 6.18 | 5 MHz Oscillator enclosed in polystyrene and placed within a shielded box                             | 254 |

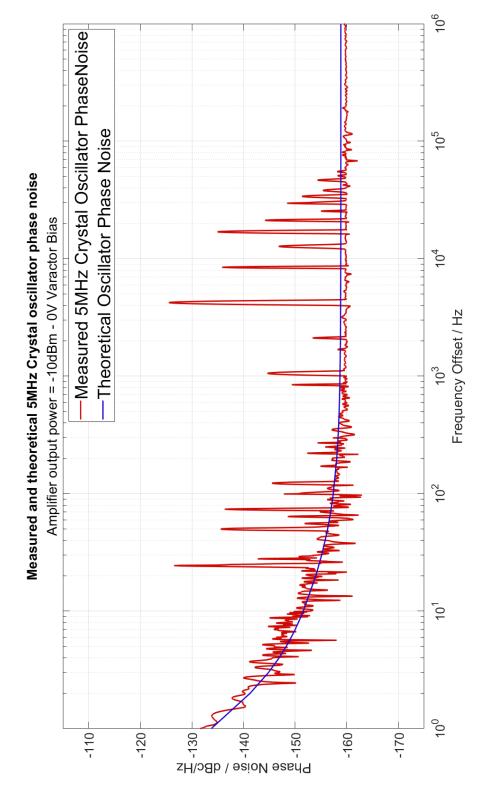

| 6.19 | $5~\mathrm{MHz}$ oscillator phase noise measurement with theoretical phase noise plotted on the       |     |

|      | same graph                                                                                            | 256 |

xxviii LIST OF FIGURES

### Chapter 1

### Introduction

An oscillator is an electronic device that produces a periodic oscillating output signal without an external input. They are essential timing elements in almost all modern electronic systems including communication, measurement and instrumentation systems providing a reference signal that is used to propagate, synchronise and process signals. The oscillator therefore sets the ultimate noise performance of such systems as large phase noise generated by an oscillator can mask the required signal leading to the introduction of errors into the system. A key characteristic of an oscillator is its frequency stability, which, can be divided into long term and short term stability. Long term stability is the frequency drift of the device as a result of device ageing, poor buffering and thermal effects. Short term stability is the close to carrier frequency stability of an oscillator as a result of phase and amplitude modulation.

Phase noise is defined as the ratio of the phase noise power at a given offset in a 1Hz bandwidth to the total carrier power in a single sideband. It is expressed in dBc/Hz. Phase fluctuations are introduced to the oscillator output spectrum by the transposition of flicker (1/f) noise from the oscillator circuit elements as well as transposed thermal noise.

#### 1.1 Research aims

The aim of the research presented in this thesis is to improve on the phase noise performance of four different oscillators using different design approaches. The four oscillators developed in this research 2 Introduction

operate at 1.5 GHz, 16 GHz, 100 MHz and 5 MHz with each presenting their own challenges specific to their configurations. The contribution to the phase noise from all oscillator components is investigated and analysed.

The oscillators developed are feedback oscillators containing amplifiers, phase shifters and output couplers which are all designed to minimise oscillator phase noise. Furthermore, the oscillators use different types of resonator, at 1.5 GHz a dielectric resonator is used, at 16 GHz a distributed Bragg resonator is used, at 100 MHz both and LC and crystal oscillator is used and at 5 MHz a crystal is used. In each case the unloaded Q,  $Q_0$ , is kept as high as possible to minimise oscillator phase noise.

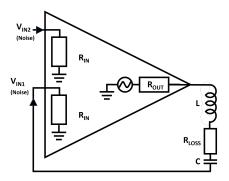

Throughout the design phase, low noise design procedures have been followed in order to reduce the noise introduced into the oscillator loop by the individual oscillator elements. In the 1.5 GHz and 16 GHz oscillators, parallel combinations of amplifiers are investigated so that the power available to the resonator is high and to reduce the flicker noise introduced by the devices. In the 100 MHz oscillator a variable gain feedforward amplifier is used to ensure the flicker noise suppression that can be achieved by this amplifier configuration is not degraded by external power limiting components that are used to keep the feedforward amplifier operating correctly.

#### 1.2 Thesis Structure

The thesis is organised into seven chapters. Chapter 2 is a general introduction to oscillator theory and low phase noise design. This includes a review of the literature containing material on the background and operation principles of ultra low phase noise oscillators. The various types of noise including thermal noise, flicker noise and shot noise that contribute to the overall phase noise are introduced before a model for an ultra low phase noise oscillator, developed by Everard [1] is discussed. A full derivation of the equation for oscillator phase noise from this model is also presented that demonstrates how the various oscillator parameters affect the oscillator phase noise. Each subsequent chapter contains a review of the literature specific to the type of oscillator design presented in each chapter.

The third chapter describes the design and manufacture of a 1.5 GHz Dielectric Resonator Oscillator (DRO). Field solver simulations of the resonator are obtained using CST Studio Suite, a software package for 3D electromagnetic analysis. The simulation results are presented as well as an in depth

1.2 Thesis Structure 3

description and analysis of the circuit designs for all of the oscillator elements. The measurements of the individual oscillator components and state of the art oscillator phase noise measurements are presented.

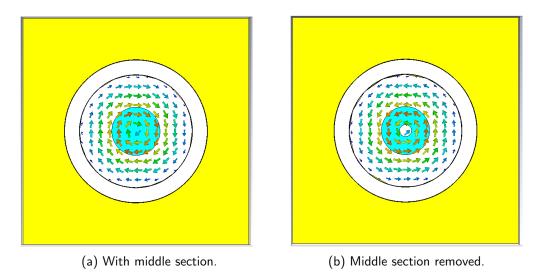

Chapter 4 contains the design process, implementation and measurements of a 16 GHz Distributed Bragg Resonator (DBR) oscillator. A maximum  $Q_0$  of 160,000 at 16 GHz has been measured. There is also an investigation into the coupling to the resonator for optimum oscillator phase noise that considers loop probes, external impedance transformation networks and aperture coupling, with the aim of achieving 6dB insertion loss at resonance whilst exhibiting the highest possible  $Q_0$ . The amplifier design process includes the design of a parallel amplifier used to reduce the flicker noise introduced and to increase the output power when compared to using a single amplifier device. There is also a description of the design of a 10dB output coupler and an electronically tunable phase shifter. This chapter concludes with measurements of the 16 GHz oscillator phase noise performance.

In Chapter 5, research into the suitability of a variable gain feedforward amplifier for use in an ultra low phase noise oscillator is presented. It has previously been shown that the feedforward amplifier can suppress flicker noise introduced by the main amplifier by approximately 20dB [2]. However, incorporating this amplifier configuration into an oscillator reduces the level of flicker noise suppression because in an oscillator, the main amplifier enters saturation, causing its gain to reduce. There is a gain and phase imbalance between the two amplifiers (main and error correction amplifiers) in the feedforward design, that, result in a decrease in the flicker noise suppression.

Using PIN diode limiters to reduce the level of saturation in the main amplifier has been shown to decrease the flicker noise in an oscillator at 7.6 GHz [2]. However the level of flicker noise suppression is reduced to 13dB as the PIN diode contributes flicker noise to the oscillator phase noise spectrum that is not suppressed by the feedforward amplifier. The approach presented in this chapter is to allow the main amplifier to saturate to the level required to ensure the gain of the amplifier is equal to the loop losses in the oscillator. Then, the gain of the error correction amplifier, the attenuation between the amplifier loops and the phase shift between the loops can be adjusted accordingly to remove the need for additional components that will introduce additional flicker noise. The derivation of a complete set of design equations that can be used to design a feedforward amplifier of a specified gain is presented. Measurements of the feedforward amplifier using a variable gain, error correction

4 Introduction

amplifier are presented as well as oscillator phase noise measurements of a 100 MHz oscillator using the feedforward amplifier to suppress flicker noise.

The sixth chapter introduces the design and measurement of a 5 MHz crystal oscillator building on the work presented in [3] and [4]. A state of the art phase noise measurement of -132dBc/Hz at 1 Hz offset from the carrier is presented. The design includes an electronically tunable phase shifter that is used to introduce a phase shift into the loop in order to sustain oscillation but also provides a range of phase shifts for tuning the oscillator as the crystal ages causing the resonant frequency to drift.

Finally, conclusions, observations and suggestions for further work are given in the seventh chapter including a brief analysis of the outcomes of this research.

#### 1.3 Related Publications

St.John Gilbert, Simon Bale and Jeremy Everard. Ultra Low Phase Noise 16GHz Oscillator using a Distributed Bragg Resonator European Frequency and Time Forum (EFTF), Neuchatel, 2024. This conference paper was submitted after the submission of this thesis and includes additional measurements of oscillator phase noise the improve on those presented here. The author won the student poster competition for the Oscillators and Noise category.

The work presented in Chapter 6 was previously presented at the joint FCS-ISAF 2020 Virtual Conference (held virtually due to COVID-19 impacting travel).

### Chapter 2

## Phase noise theory and literature

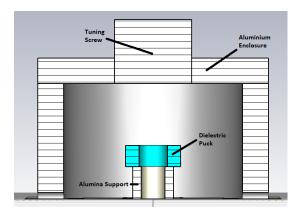

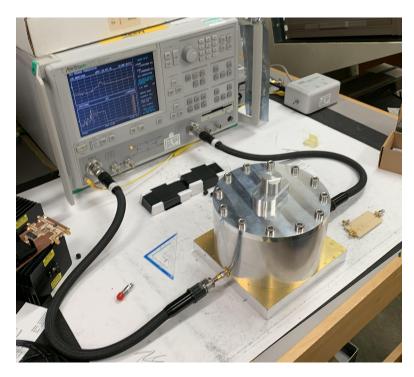

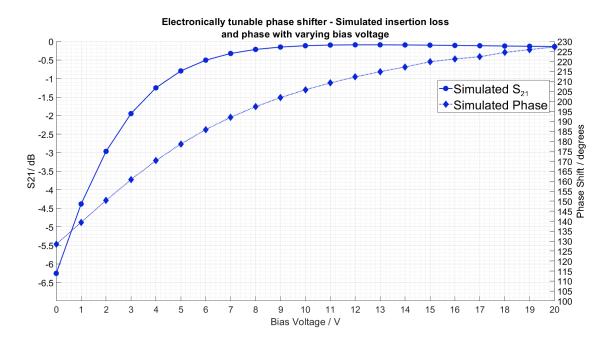

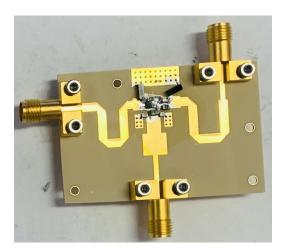

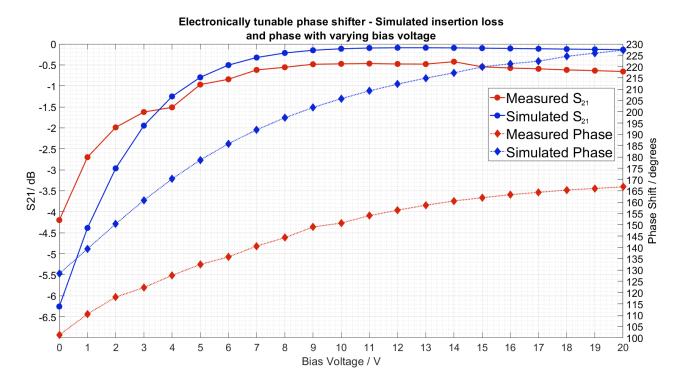

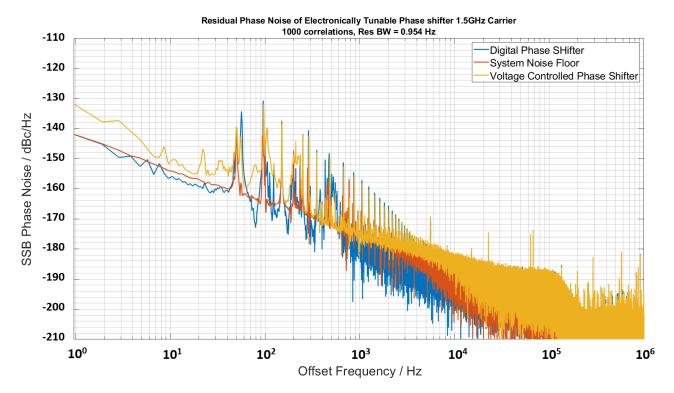

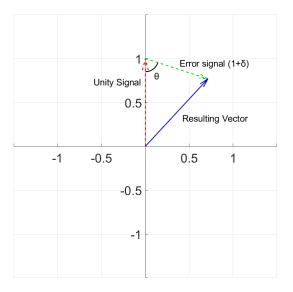

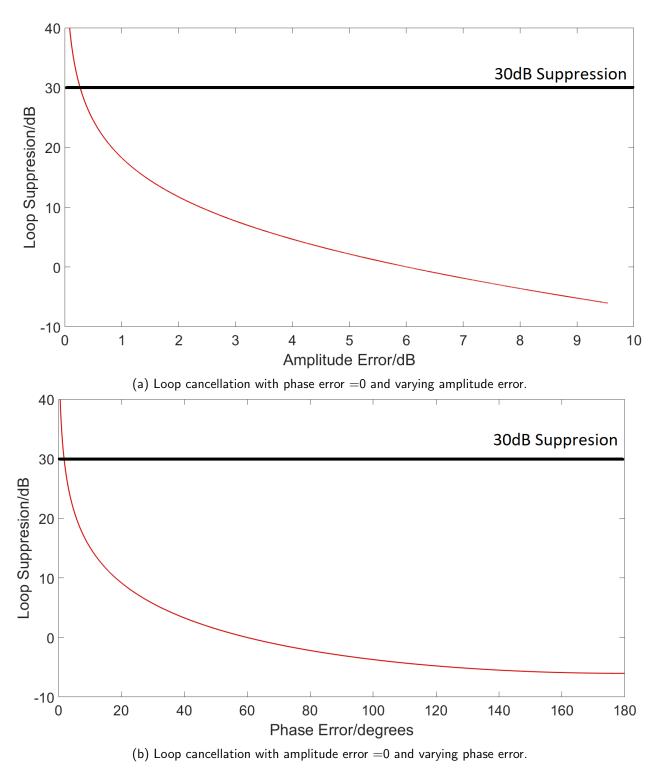

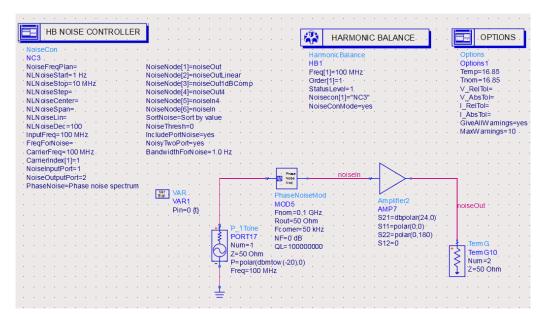

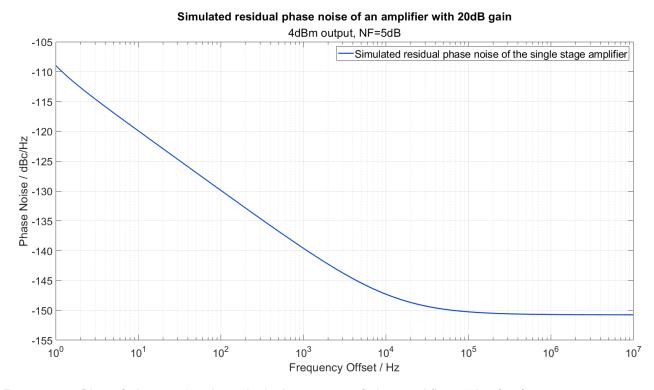

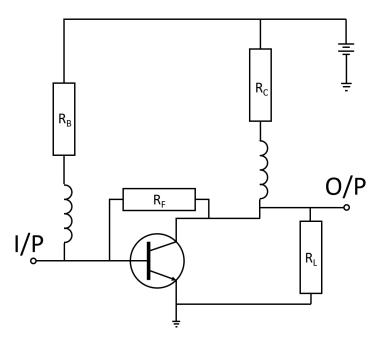

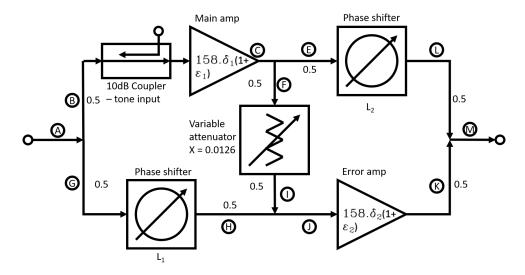

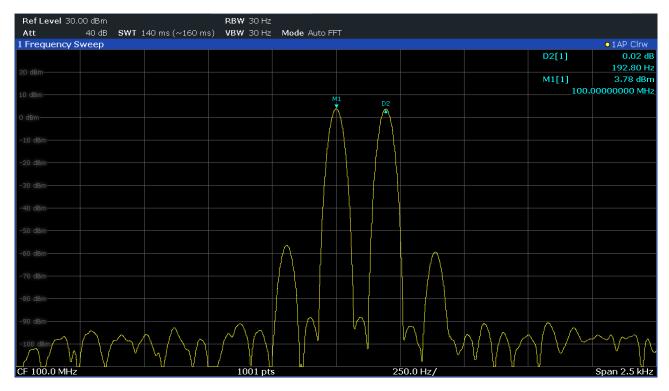

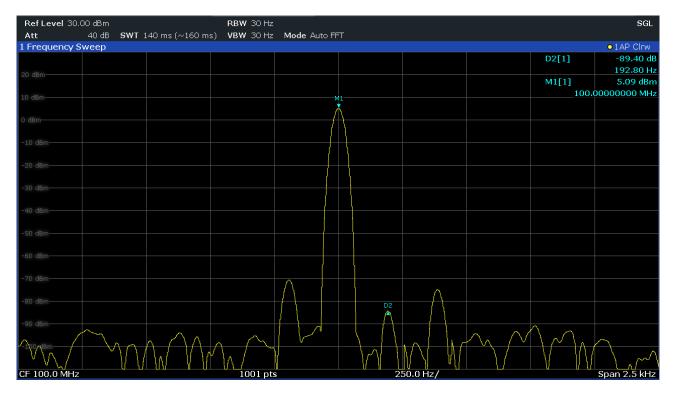

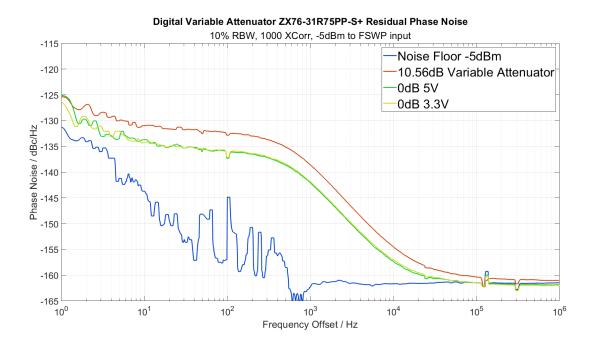

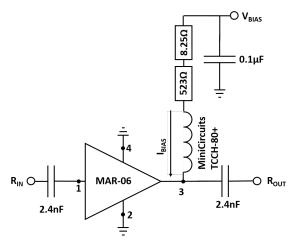

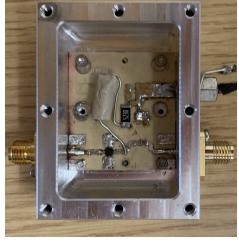

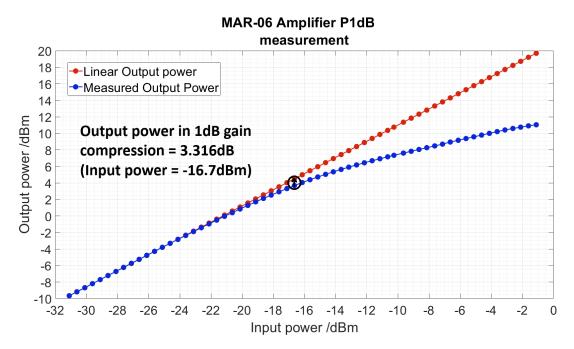

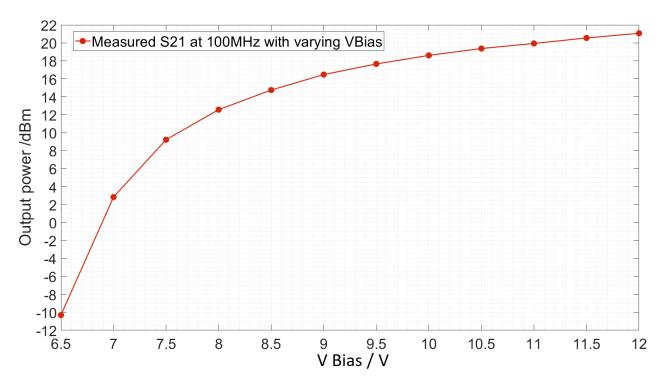

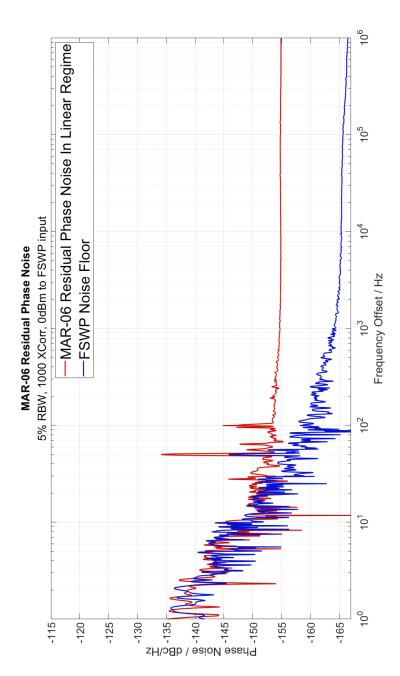

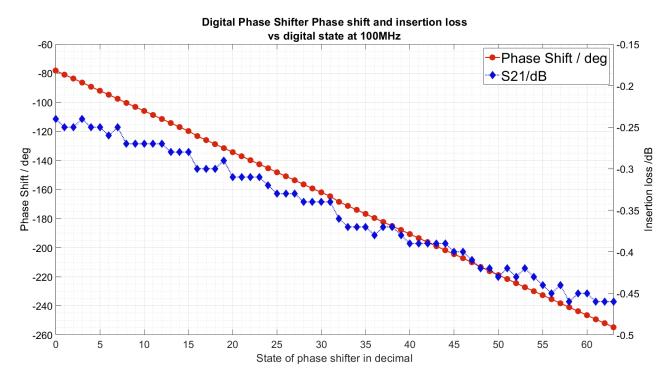

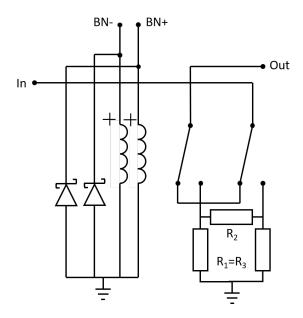

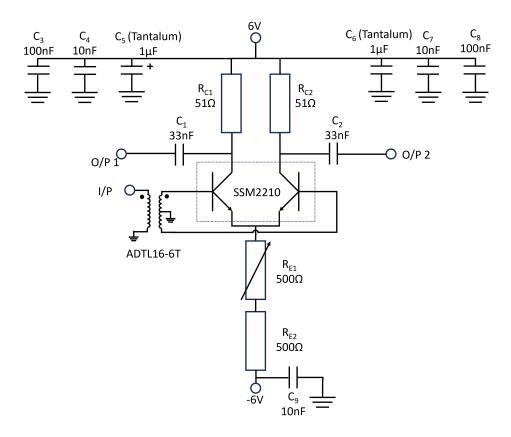

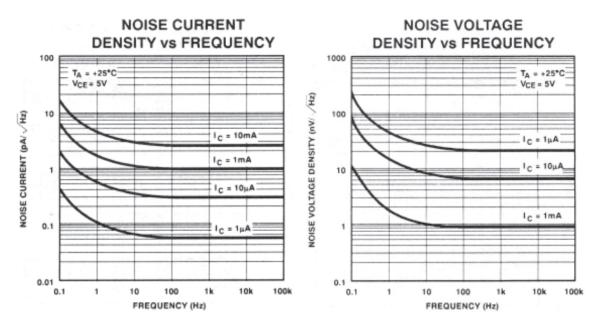

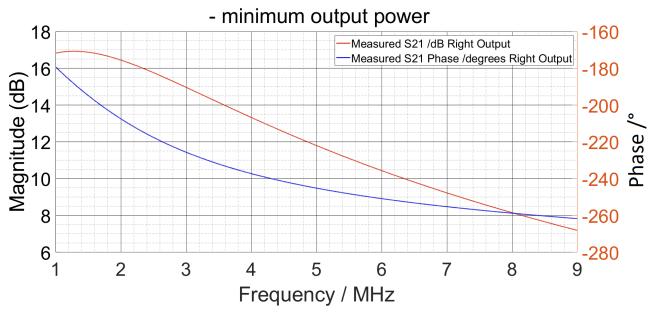

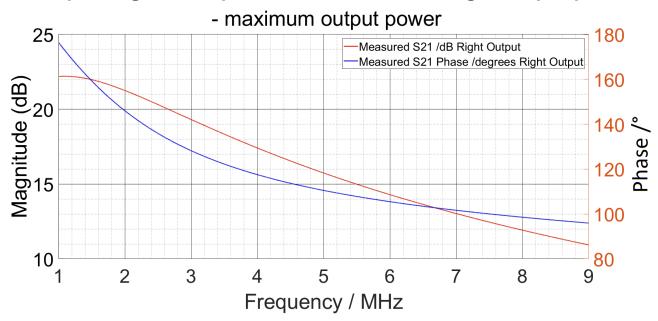

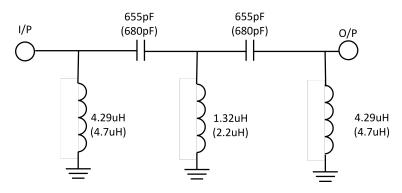

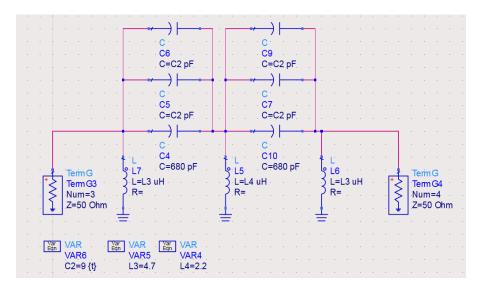

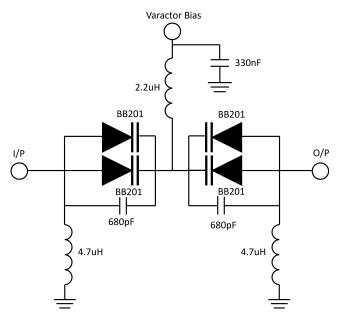

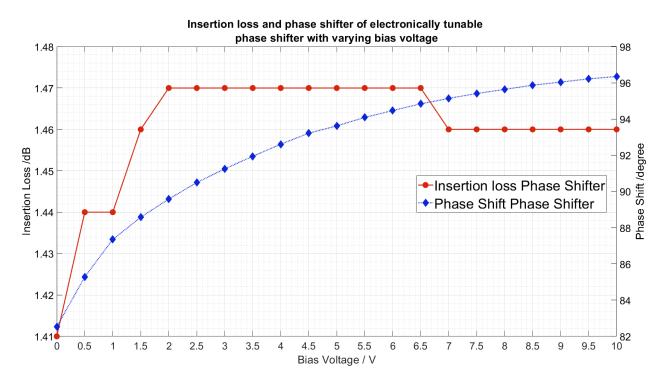

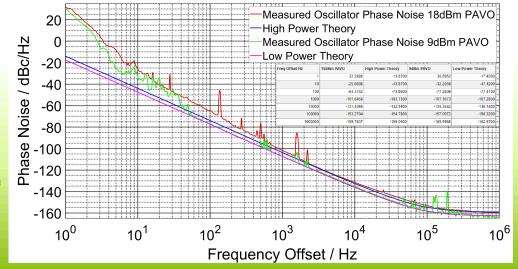

### 2.1 Feedback Oscillator