The Electronic and Electrical Engineering

Electrical Machines and Drives Research Group

Dead Time Compensation and Phase Lag Compensation in 2-Level and 3-Level Grid Connected H-Bridge Power Inverter

By

### LEI WEI

Supervised by Prof Martin Paul Foster and Prof David Stone

# Abstract

Dead Time ( $T_d$ ) is a certain time which is added into power inverter for avoiding short circuit events when power switches are turning on or off. Although dead time is used in H-Bridge to avoid a shoot-through event from occurring, it will inevitably cause distortion and energy loss. Methods such as Dead Time Compensation (DTC) and Dead Time Elimination (DTE) are used for compensating power loss, voltage drop, and high distortion caused by dead time  $T_d$ . In many literatures, most of DTC or DTE are used in 2-level H-Bridge PWM system for motor drives and open-loop system. This thesis presents a DTC technology which is used in a single phase 2-level and 3-level Grid Connected H-Bridge Power Inverter. As result, except DTC technology, the technology of Phase Locked Loop (PLL) and PI current control are described and discussed as well. Moreover, MATLAB Simulink simulation results, and electrical circuit design experimental results about the DTC in Grid Connected Power Inverter presented in the thesis is discussed.

# Content

|                                                                         | _          |

|-------------------------------------------------------------------------|------------|

| Chapter 1 Introduction                                                  | .5         |

| 1.1 Background1                                                         | .5         |

| 1.2 Motivation1                                                         | 8          |

| 1.3 Contribution2                                                       | 21         |

| 1.4 Thesis Structure2                                                   | 23         |

| Chapter 2 Background information and literature review                  | 25         |

| 2.1 Introduction                                                        | 25         |

| 2.2 H-Bridge Power Inverter2                                            | 26         |

| 2.2.1 H-Bridge Inverter2                                                | 26         |

| 2.2.2 PWM Control System in 2-level H-Bridge inverter                   | 34         |

| 2.3 3-level H-Bridge inverter and its PWM control4                      | 1          |

| 2.4 Dead Time Effect and Dead Time Compensation4                        | 7          |

| 2.5 <i>LCL</i> filter5                                                  | 50         |

| 2.6 Grid connected power inverter system5                               | 3          |

| 2.6.1 Phase locked loop ( <i>PLL</i> )5                                 | 3          |

| 2.6.2 Current controller                                                | 8          |

| 2.7 PV power system6                                                    | 1          |

| 2.8 Analysis leakage current in PV grid connected power inverter6       | <b>i</b> 3 |

| 2.9 Chapter Conclusion                                                  | <b>58</b>  |

| Chapter 3 Dead time and Dead time compensation                          | 59         |

| 3.1 Dead time effect in 2-level H-Bridge inverter6                      | 59         |

| 3.2 Modelling and analysis of the deadtime process                      |            |

| 3.3 Dead Time Compensation of 2-level H-Bridge inverter                 |            |

| 3.3.1 Deadtime Compensation ( <i>DTC</i> )                              |            |

| 3.3.2 Phase Lag Compensation ( <i>PLC</i> )                             |            |

| 3.4 MATLAB Simulation of the dead time compensation in 2-level H-Bridge |            |

| inverter                                                                | 6          |

| 3.5 Dead Time effect analysis in 3-level H-Bridge inverter9             | 2          |

| 3.5.1 Dead Time effect at positive half period of $Vsin(t)$ 9           | 2          |

| 3.5.2 Dead Time effect at negative half period of $Vsin(t)$ 9           | 7          |

| 3.6 Dead Time Compensation in 3-level H-Bridge inverter101                                                    |

|---------------------------------------------------------------------------------------------------------------|

| 3.7 MATLAB Simulink simulation of Dead Time Compensation in 3-level H-Bridge inverter                         |

| 3.8 Chapter Conclusion113                                                                                     |

| Chapter 4 Power electronic hardware system design115                                                          |

| 4.1 Design of <i>LCL</i> filter116                                                                            |

| 4.1.1 Inverter side inductor <i>Linv</i> design118                                                            |

| 4.1.2 Capacitor <i>Cf</i> design120                                                                           |

| 4.1.3 Grid side inductor ( <i>Lgrid</i> ) design121                                                           |

| 4.1.4 Damping resistor <i>Rd</i> design122                                                                    |

| 4.2 Grid Connected Power Inverter System124                                                                   |

| 4.2.1 Phase Locked Loop (PLL)124                                                                              |

| 4.2.2 PI current control128                                                                                   |

| 4.3 Circuit design of H-Bridge inverter133                                                                    |

| 4.4 Current and voltage detector138                                                                           |

| 4.5 MAX913 current zero-crossing detector circuit design147                                                   |

| 4.6 H-Bridge protection circuit design151                                                                     |

| 4.7 Chapter Conclusion164                                                                                     |

| Chapter 5 Microcontroller System Design166                                                                    |

| 5.1 The PWM system in microcontroller STM32F407ZGT6168                                                        |

| 5.2 Design and implementation of Dead Time Compensation175                                                    |

| 5.3 ADC Sampling in microcontroller182                                                                        |

| 5.4 Microcontroller system design of <i>PLL</i> 186                                                           |

| 5.5 Microcontroller system design of <i>PI</i> current controller191                                          |

| 5.6 A summary of the whole <i>PWM</i> timing and control system194                                            |

| 5.7 Chapter Conclusion                                                                                        |

| Chapter 6 Simulation and Experimental Validation201                                                           |

| 6.1 Dead Time compensation in H-Bridge201                                                                     |

| 6.2 PLL and PI current close-loop control212                                                                  |

| 6.3 Dead Time Effect and Dead Time Compensation operation with grid <i>PLL</i> and <i>PI</i> current control. |

| 6.4 MATLAB Simulation validation of dead time effect and DTC operation |                                          | 'C operation in |

|------------------------------------------------------------------------|------------------------------------------|-----------------|

| a Grid C                                                               | onnected 3-level H-Bridge Power inverter | 232             |

| <b>6.5</b> Chap                                                        | ter Conclusion                           | 239             |

| Chapter 7                                                              | Conclusion and Future Plan               | 240             |

| 7.1 Thesi                                                              | s Conclusion                             | 240             |

| 7.2 Futu                                                               | re work                                  | 244             |

# List of Figure

| Figure 2-1: Block Diagram of Grid Connected H-Bridge Power Inverter 26               |

|--------------------------------------------------------------------------------------|

| Figure 2-2 : Basic Structure of H-Bridge Inverter28                                  |

| Figure 2-3: (a) $VAB = +VDC$ , $IAB > 0$ . (b) $VAB = -VDC$ , $IAB < 0$ . (c)        |

| Voltage and current waveform with restive load29                                     |

| Figure 2-4: Output load voltage VAB and current IAB waveform with                    |

| inductive load30                                                                     |

| Figure 2-5: Voltage and current direction in H-Bridge from when time $t$ from        |

| t0 to t4. (a) t0 to t1, (b) t1 to t2, (c) t2 to t3, (d) t3 to t431                   |

| Figure 2-6 : Control pulse Duty Cycle34                                              |

| Figure 2-7: (a) Block diagram of $PWM$ system. (b) waveform of $Vtri(t)$ ,           |

| Vsin(t), $PWM1$ , $PWM1$ , $VAB(t)$ and $IAB(t)$ 37                                  |

| Figure 2-8: Diagram of waveform of signal $Vsin(t)$ , $Vtri(t)$ and output           |

| <i>VAB(t)</i> in one <i>Tpwm</i> 39                                                  |

| Figure 2-9: (a) Block diagram of <i>PWM</i> system in 3-level H-Bridge inverter.     |

| (b) PWM input and output signal and output voltage42                                 |

| Figure 2-10: Relation between $Vsin(t)$ , $Vtri1(t)$ and $VAB(t)$ during             |

| positive half-cycle45                                                                |

| Figure 2-11: Relation between $Vsin(t)$ , $Vtri2(t)$ and $VAB(t)$ during             |

| negative half cycle46                                                                |

| Figure 2-12: LCL filter with damping resistor51                                      |

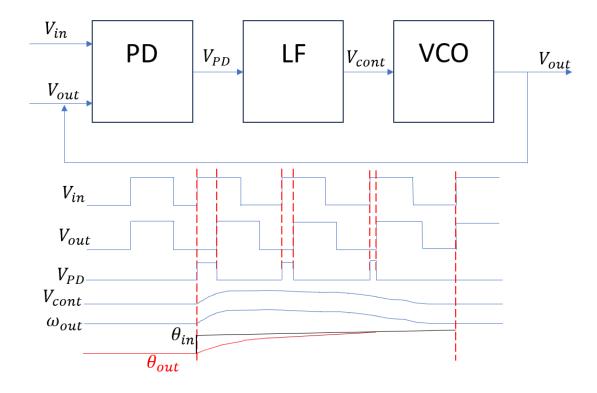

| Figure 2-13 :A basic Phase Locked Loop54                                             |

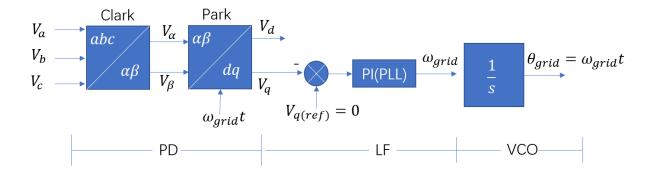

| Figure 2-14 : The block diagram of SRF- PLL55                                        |

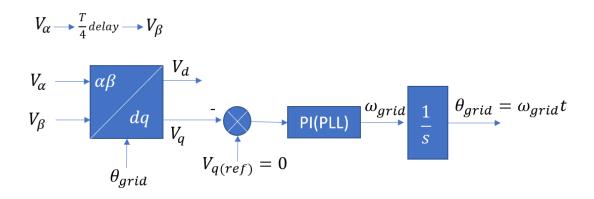

| Figure 2-15: Basic block diagram of <i>PLL</i> in single phase grid system56         |

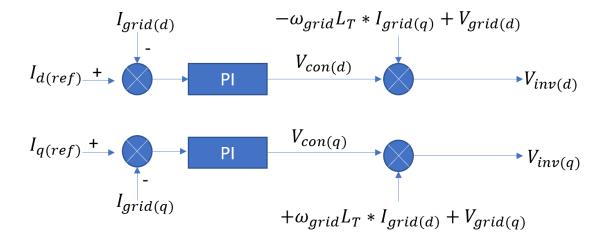

| Figure 2-16: PI current control in single phase grid connected power inverter.       |

| 59                                                                                   |

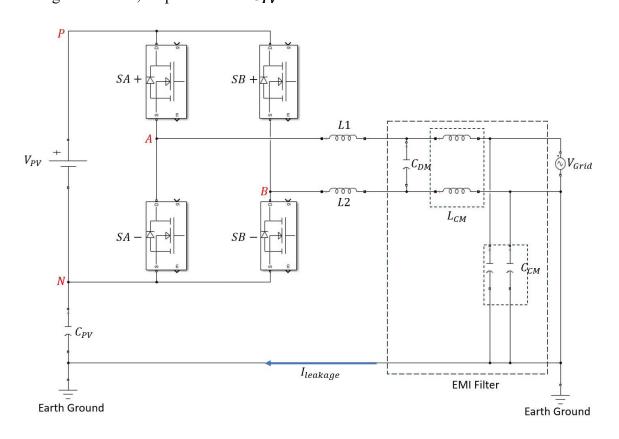

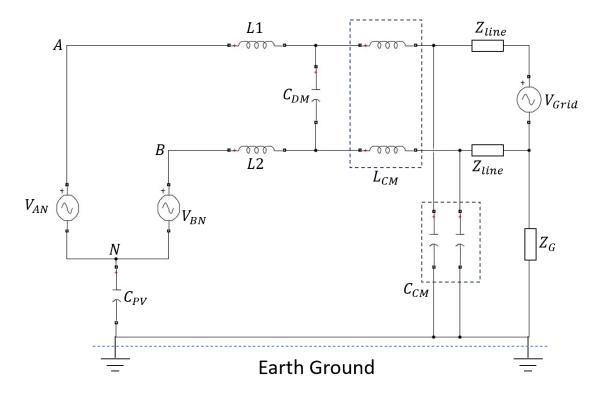

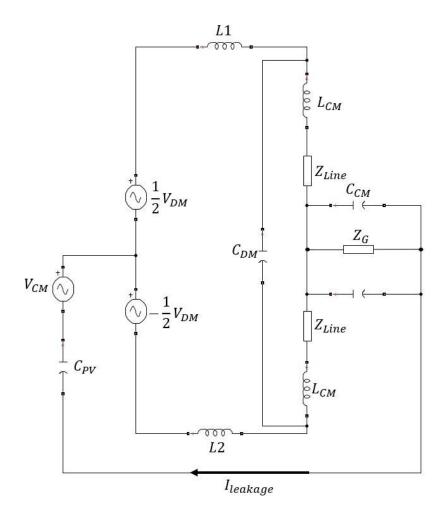

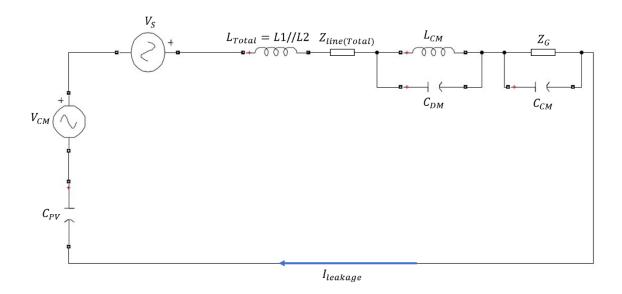

| Figure 2-17: PV grid connected power inverter with EMI filter63                      |

| Figure 2-18: Equivalent circuit for VAN and VBN64                                    |

| Figure 2-19: Equivalent circuit of PV power inverter in VCM and VDM mode.            |

|                                                                                      |

| Figure 2-20 : Final equivalent circuit for PV power inverter system                  |

| Figure 3-1: <i>PWM</i> signal, Gate Signal, Switch Signal and output <i>VAB</i> when |

| IAB > 0                                                                              |

| Figure 3-2: PWM signal, Gate Signal, Switch Signal and output VAB when               |

| IAB < 0                                                                              |

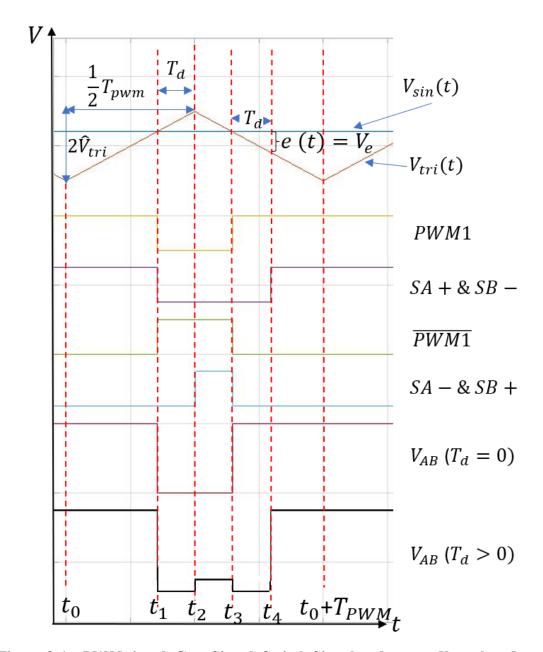

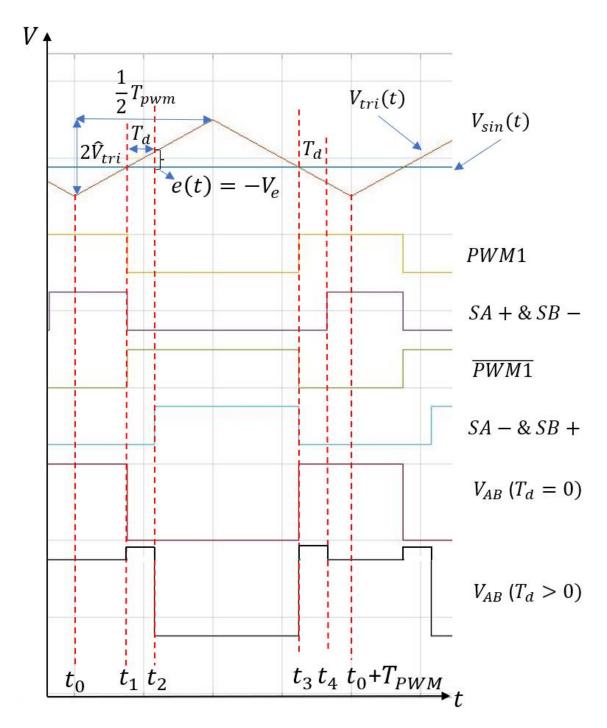

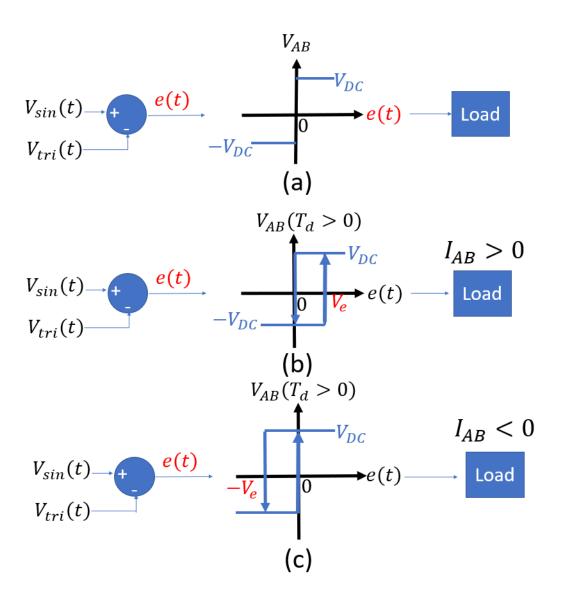

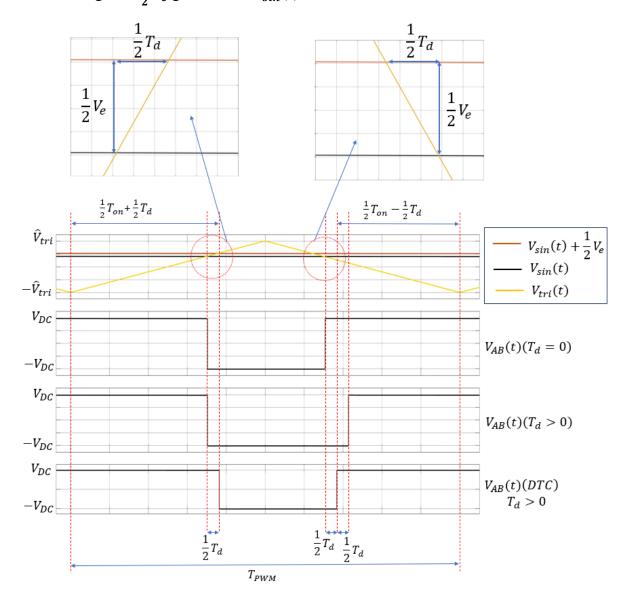

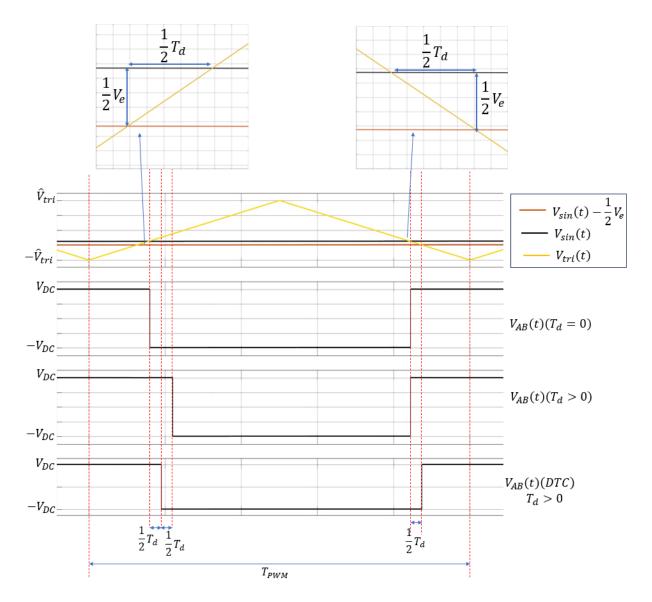

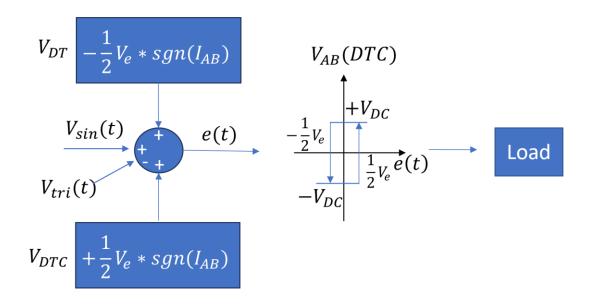

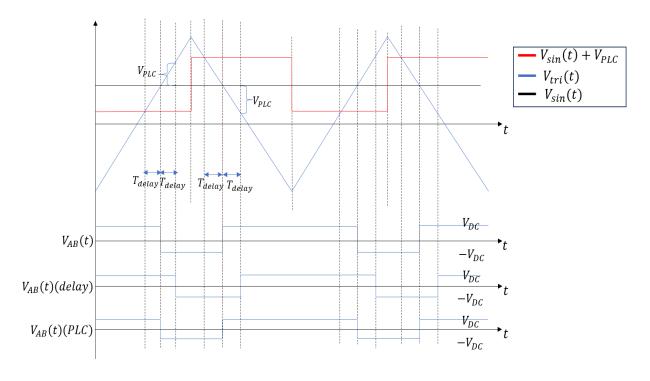

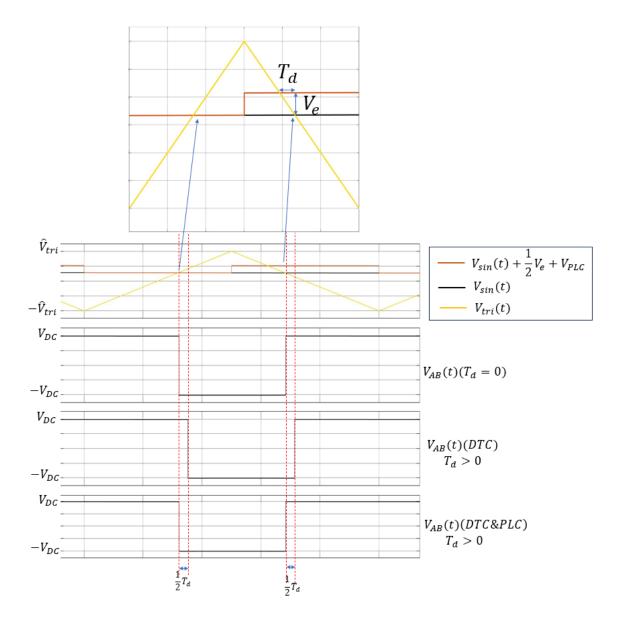

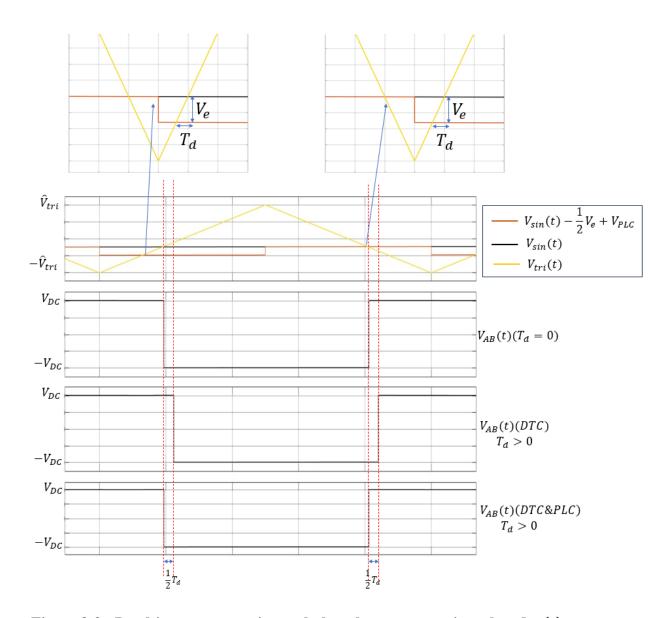

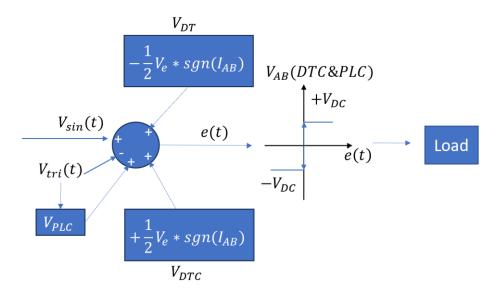

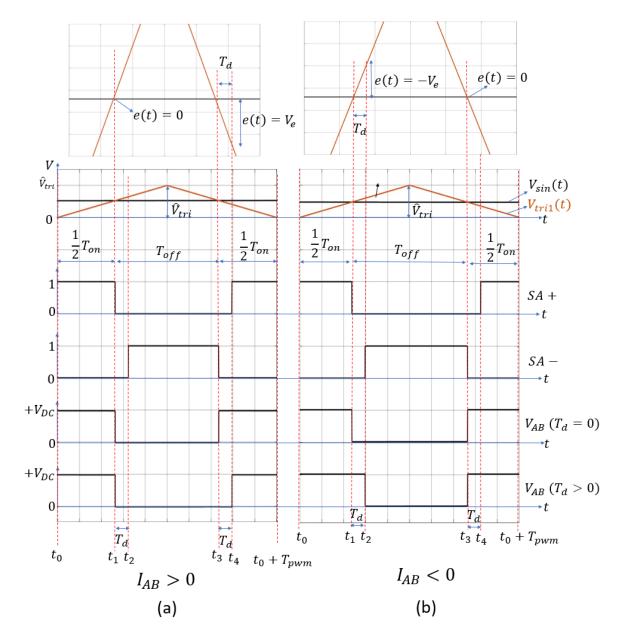

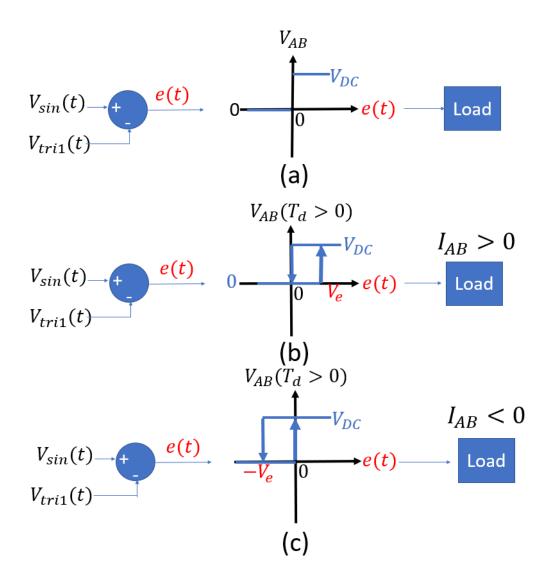

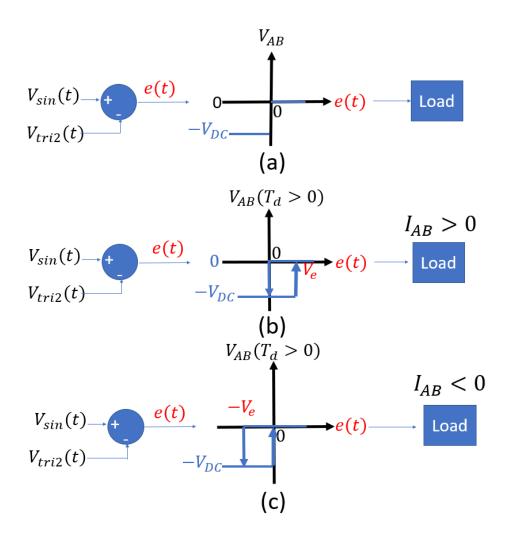

| Figure 3-3: Relation between signal difference $e(t)$ and output voltage $VAB$ .     |

| (a) $Td = 0$ , (b) $Td > 0$ and $IAB > 0$ , (c) $Td > 0$ and $IAB < 0$               |

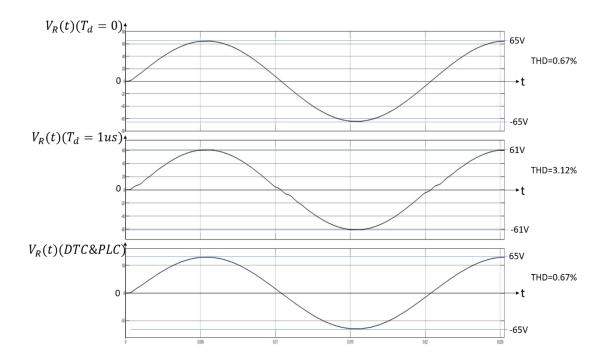

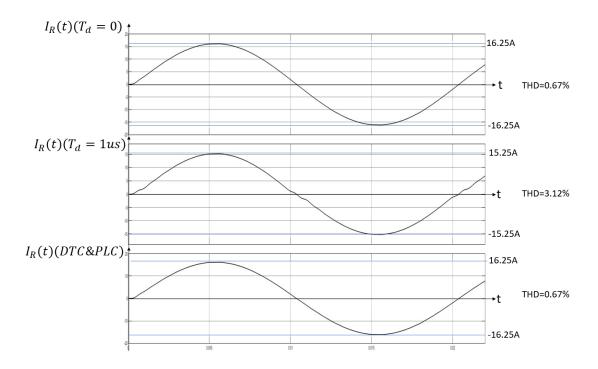

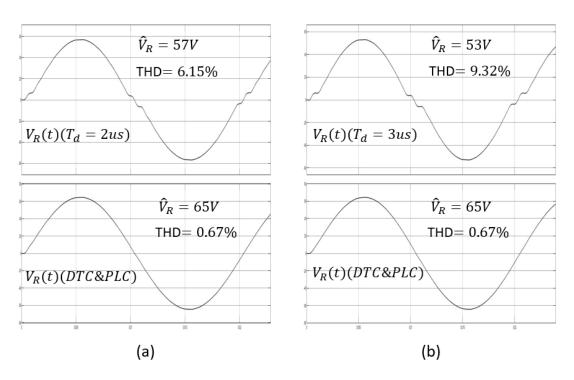

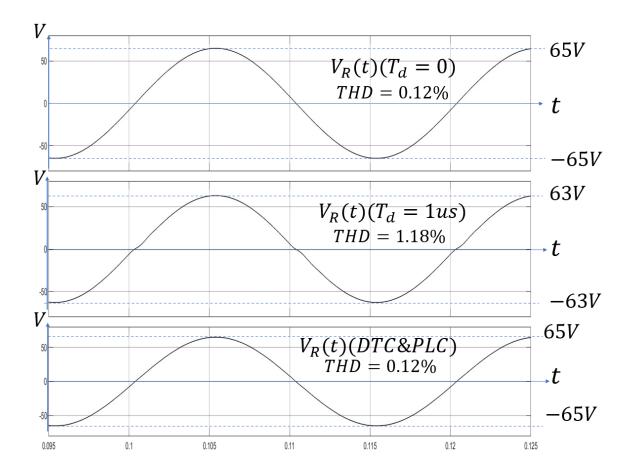

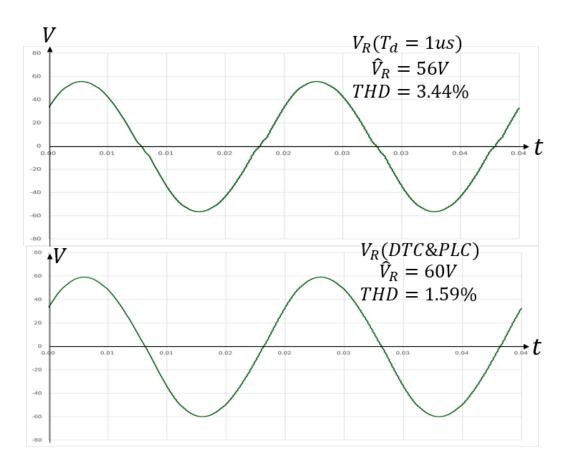

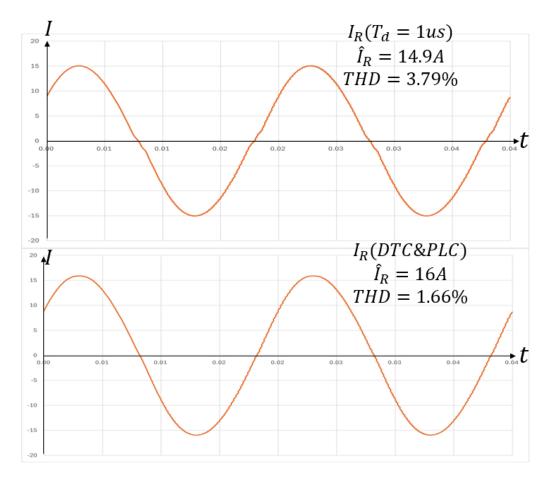

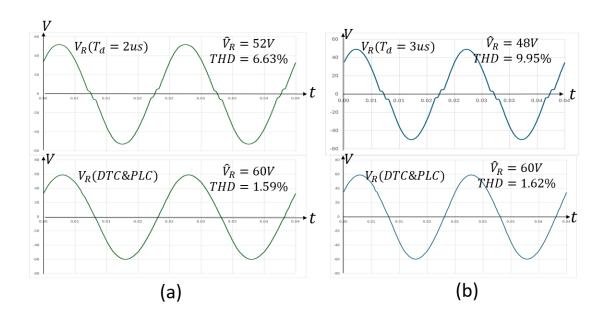

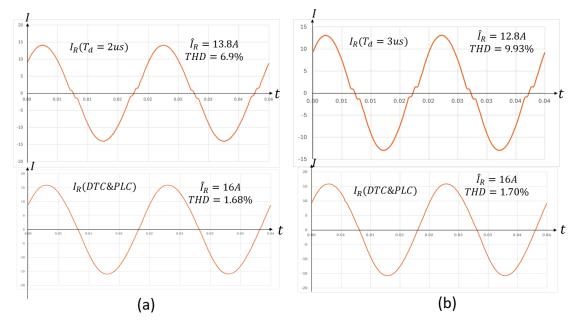

| Figure 3-29: $VR(t)$ with different conditions                                    |

|-----------------------------------------------------------------------------------|

| Figure 3-30: resistor current $IR(t)$ under different conditions                  |

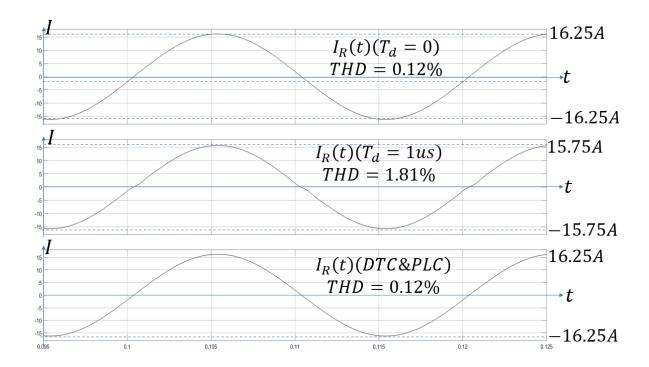

| Figure 3-31: waveform of output voltage $VR(t)$ . (a) $Td = 2us$ , (b) $Td = 3us$ |

| 112                                                                               |

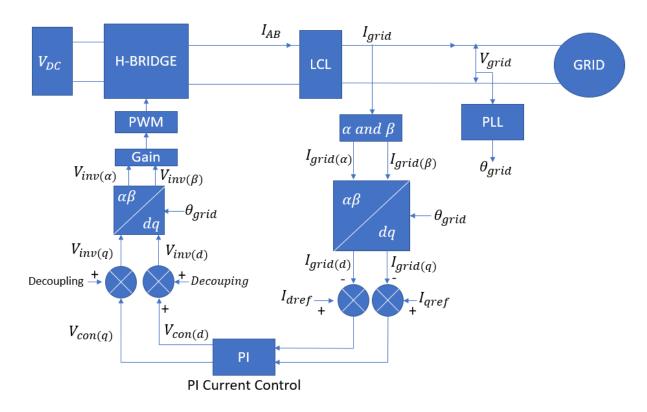

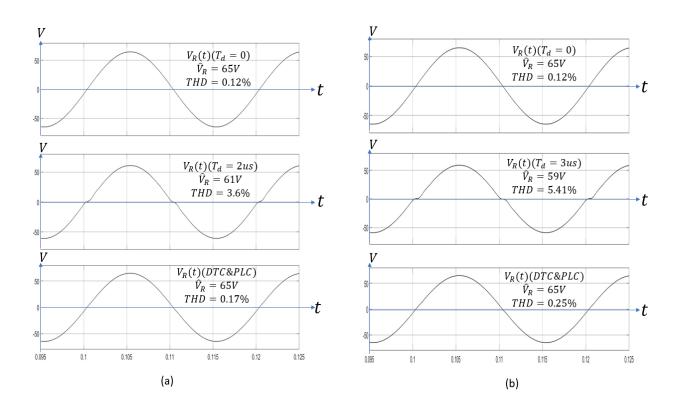

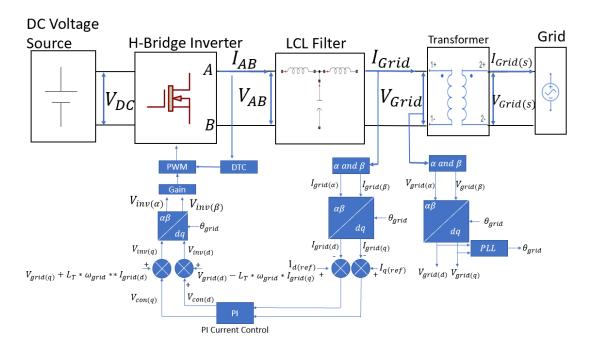

| Figure 4-1: Block Diagram of grid connected power inverter circuit 115            |

| Figure 4-2: A basic electrical circle of <i>LCL</i> filter116                     |

| Figure 4-3: Block diagram of Grid connected H-Bridge inverter117                  |

| Figure 4-4: inverter side inductor voltage and max current ripple119              |

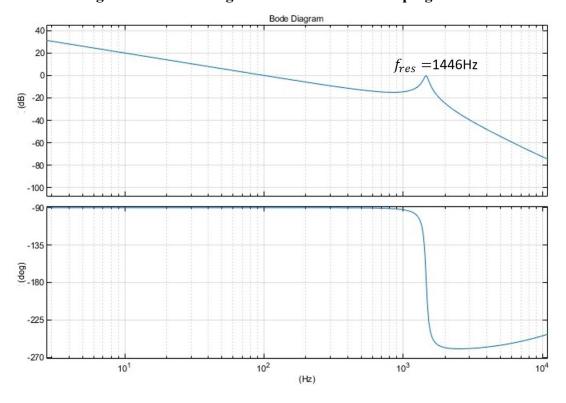

| Figure 4-5: Bode diagram of LCL without damping resistor                          |

| Figure 4-6: Bode diagram of <i>LCL</i> with damping resistor123                   |

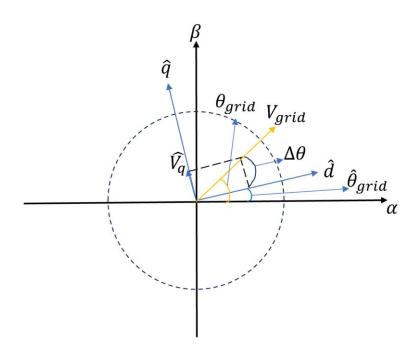

| Figure 4-7: dq reference frame in PLL system of grid125                           |

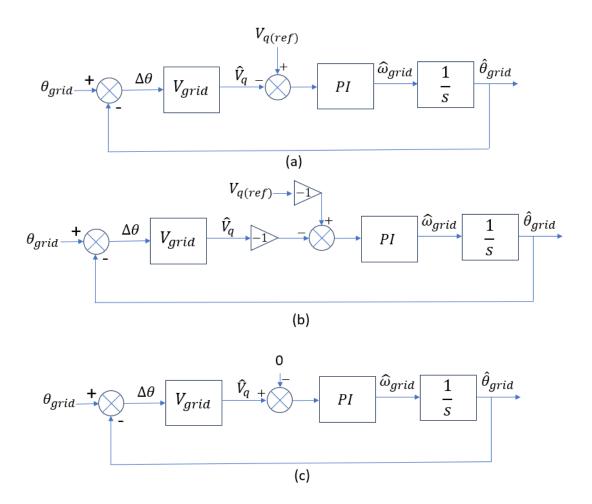

| Figure 4-8: Block diagram of PLL loop126                                          |

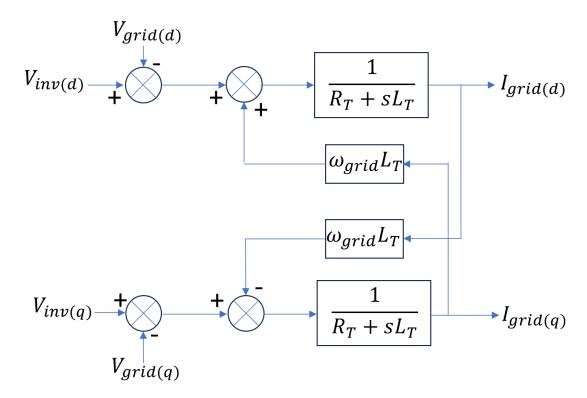

| Figure 4-9: Block diagram about inverter and grid side voltage and current        |

| in <i>dq</i> frame130                                                             |

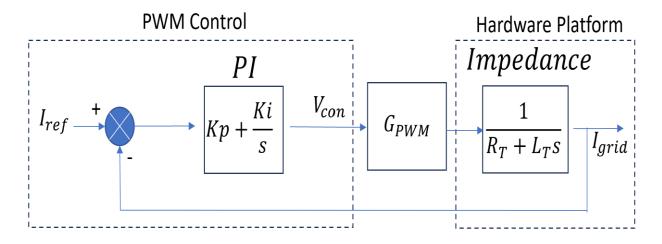

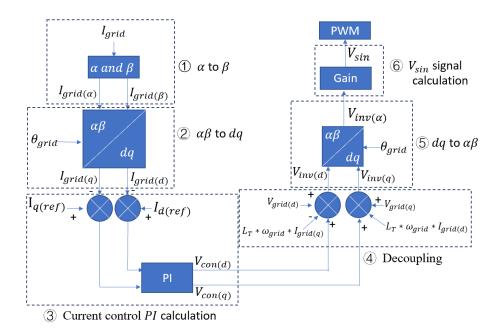

| Figure 4-10: Block diagram of decoupling system131                                |

| Figure 4-11 : Close loop of PI current Control system131                          |

| Figure 4-12: Block Diagram of whole PI current control and PLL system.            |

| 132                                                                               |

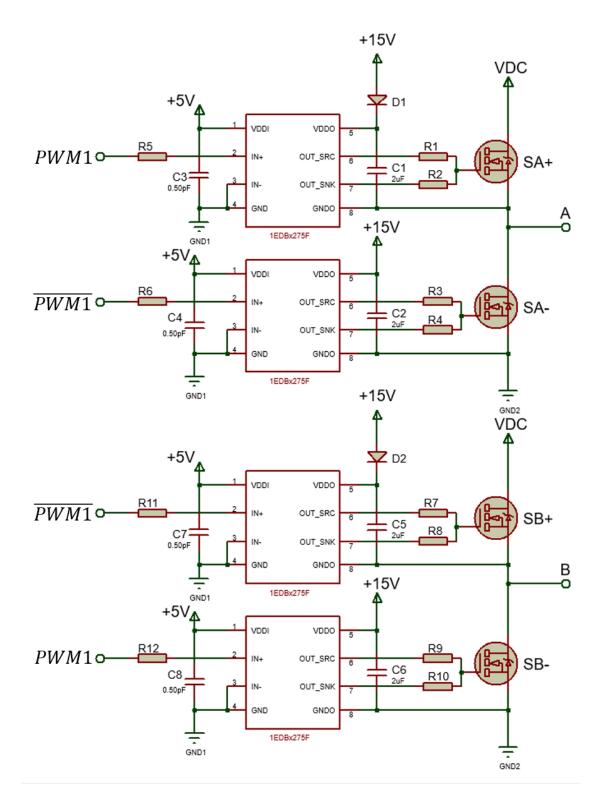

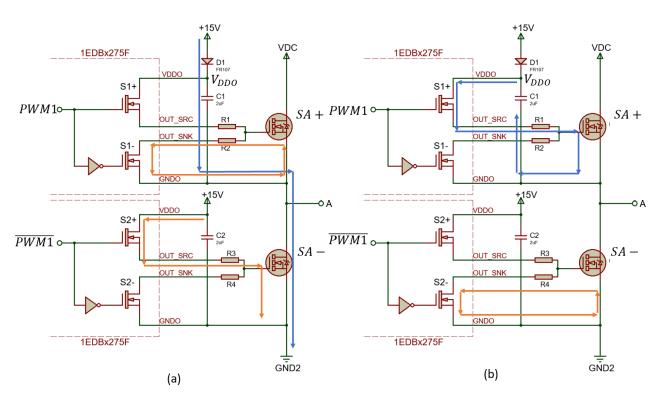

| Figure 4-13: The schematic circuit diagram of H-Bridge drive circuit134           |

| Figure 4-14: Current flow in bootstrap circuit (a) When PWM1 is low and           |

| PWM1 is high, (b) When PWM1 is high and PWM1 is low135                            |

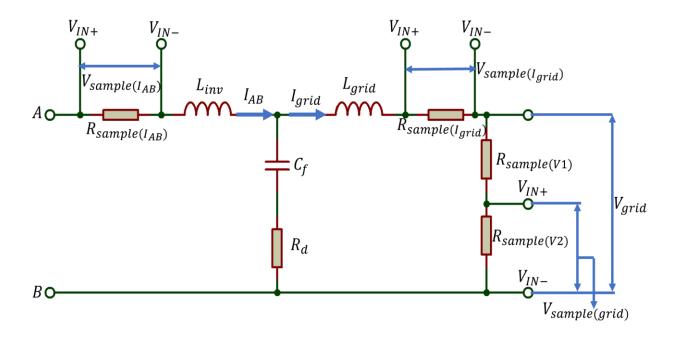

| Figure 4-15: Schematic circuit diagram of main output circuit with sample         |

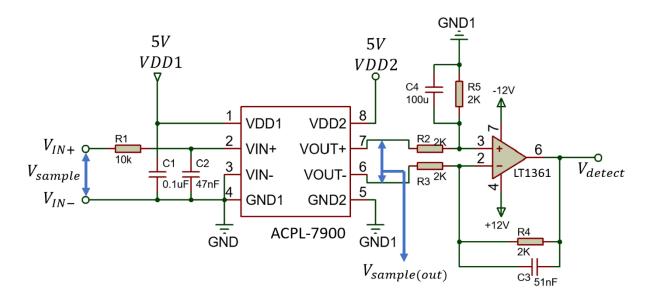

| resistor139                                                                       |

| Figure 4-16 : Schematic diagram of detector circuit140                            |

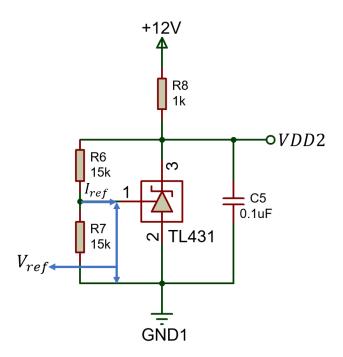

| Figure 4-17: voltage regulator for converting $+12V$ to $+5V$ supplying $VDD2$    |

| 143                                                                               |

| Figure 4-18 : Detector module144                                                  |

| Figure 4-19: Schematic diagram of the offset voltage circuit for                  |

| Vdetect(Vgrid)145                                                                 |

| Figure 4-20: Schematic diagram of MAX913 zero-crossing detect circuit.            |

| 148                                                                               |

| Figure 4-21: The input and output signal of MAX913 comparator with                |

| Schmitt trigger capacitor150                                                      |

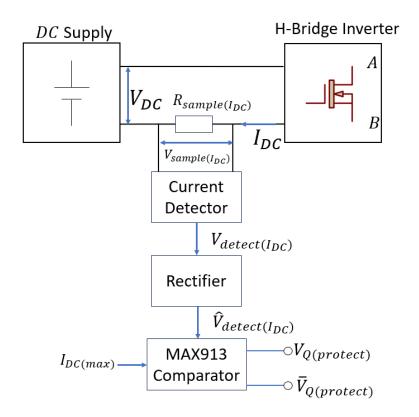

| Figure 4-22: <i>IDC</i> protect circuit block diagram152                          |

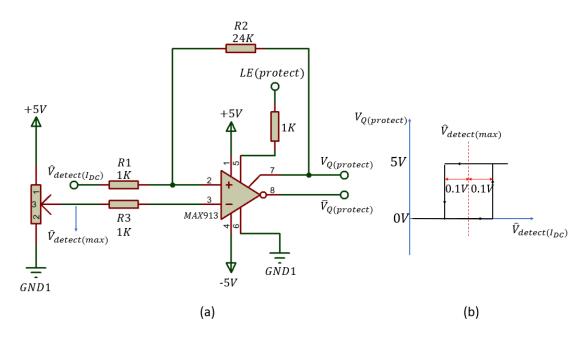

| Figure 4-23: MAX913 Schmitt trigger comparator. (a) Electrical circuit,           |

| (b)Hysteresis Curve of Schmitt trigger153                                         |

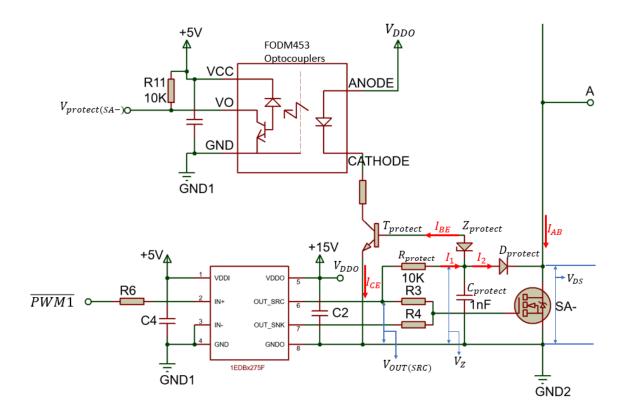

| Figure 4-24: Protection circuit of switch SA —155                                 |

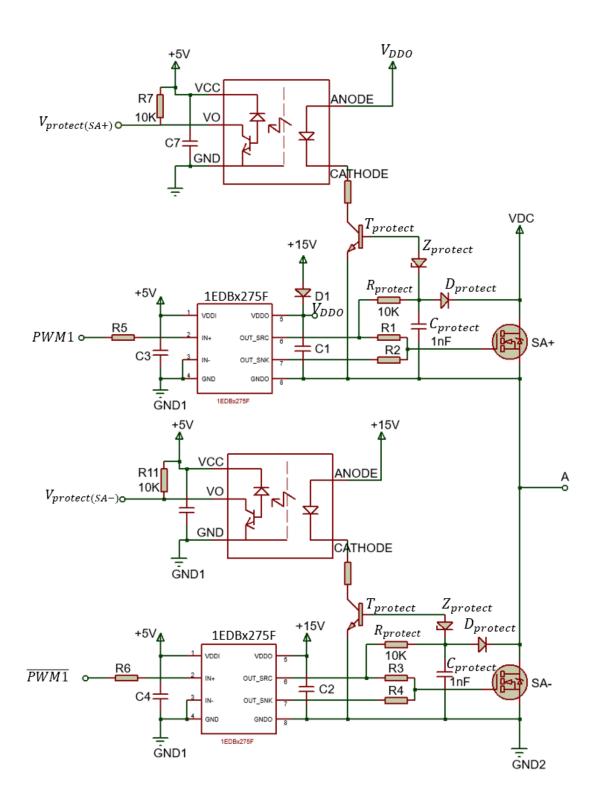

| Figure 4-25: Protection system for leg A power switches in H-Bridge inverter.        |

|--------------------------------------------------------------------------------------|

| 161                                                                                  |

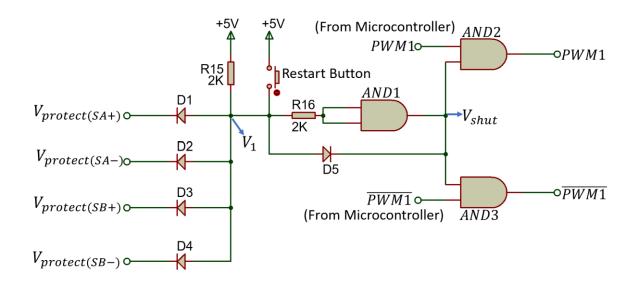

| Figure 4-26: Latch off circuit in protection system162                               |

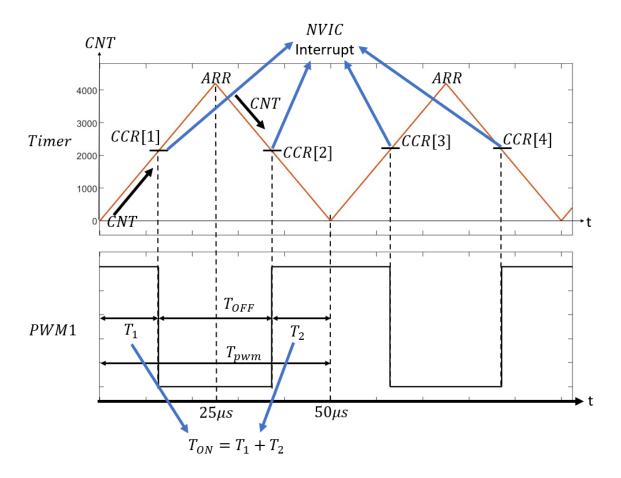

| Figure 5-1: The Timer system and output PWM1 signal169                               |

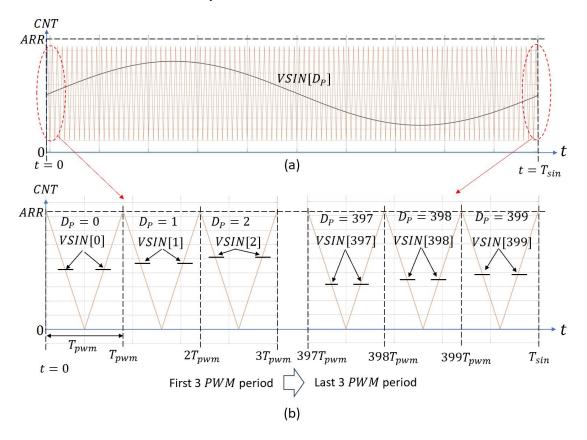

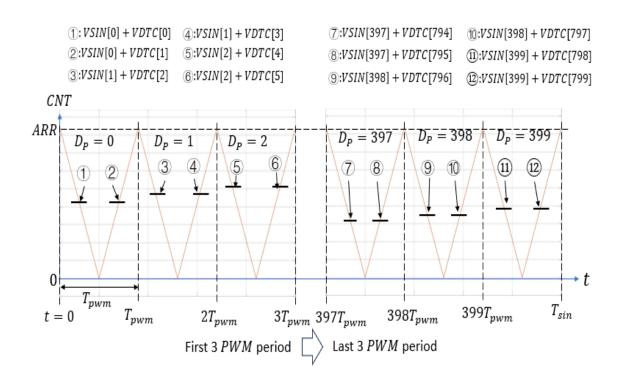

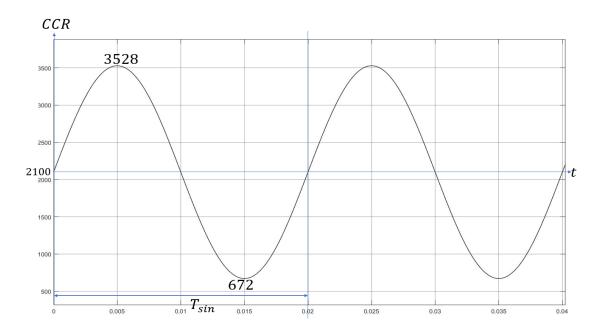

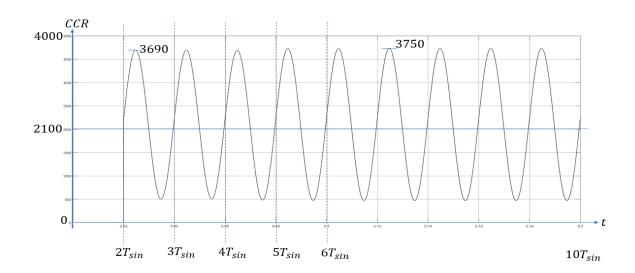

| Figure 5-2: (a) VSIN[DP] and CNT in a Vsin period, (b) The CCR value in              |

| the first and last 3 Tpwm periods173                                                 |

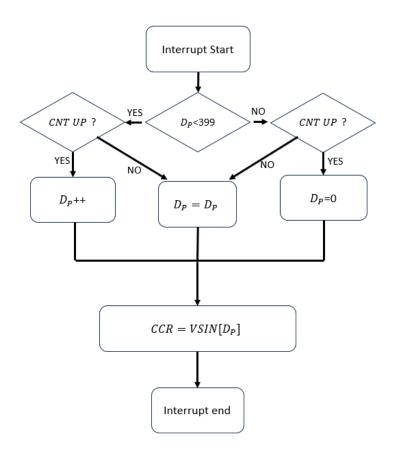

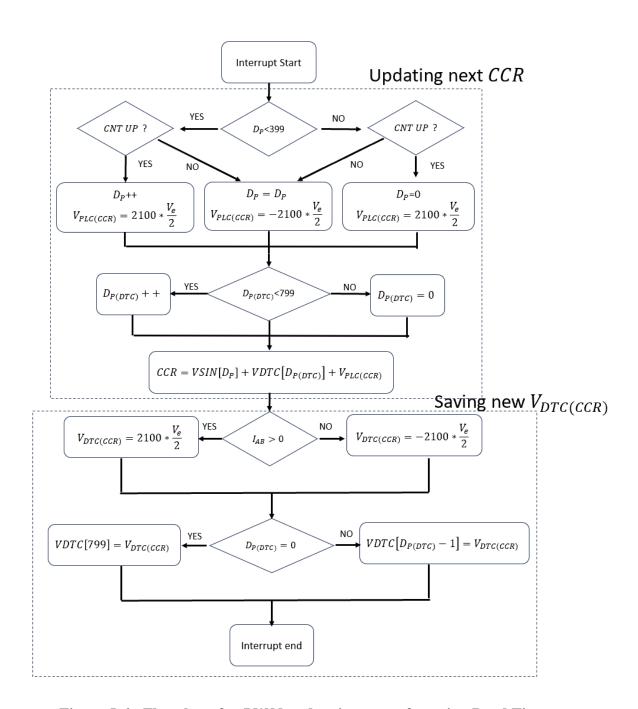

| Figure 5-3: The flowchart of CCR value update175                                     |

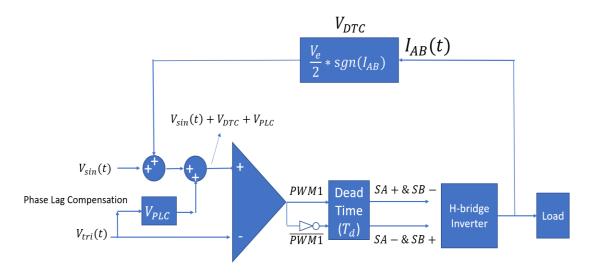

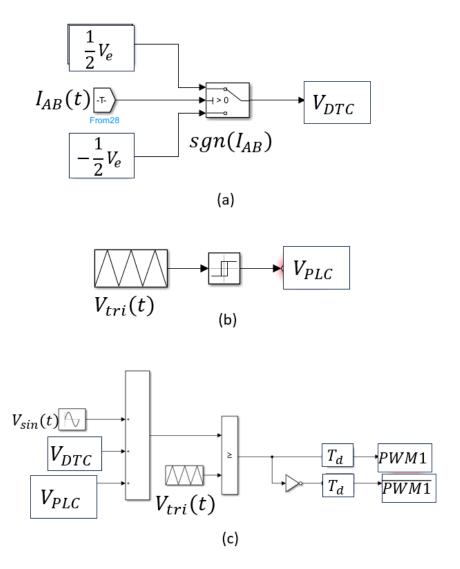

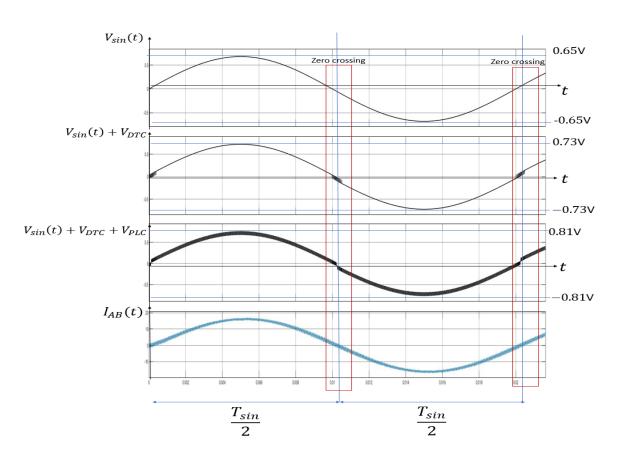

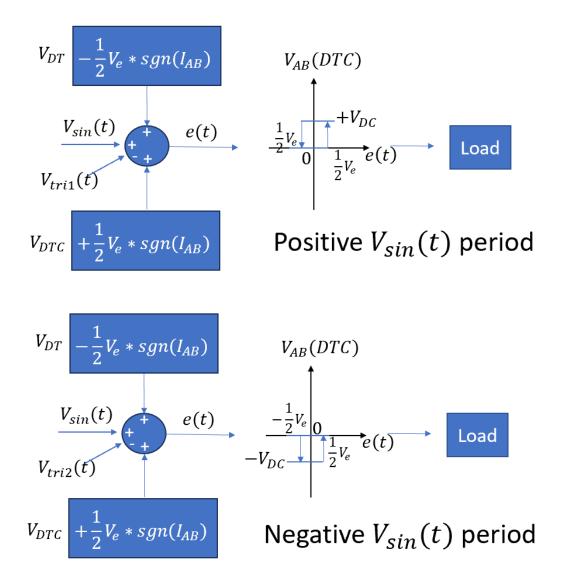

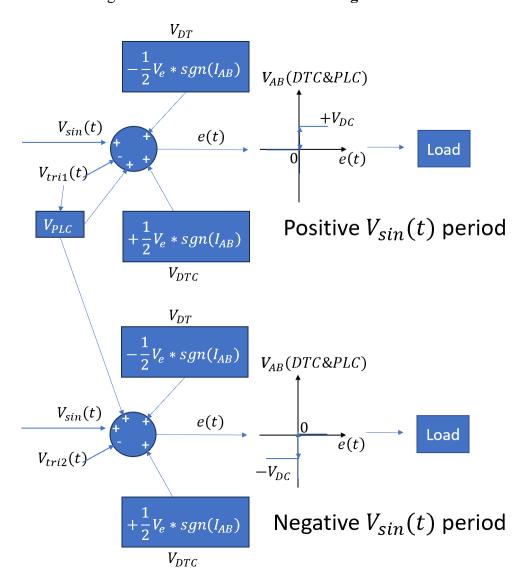

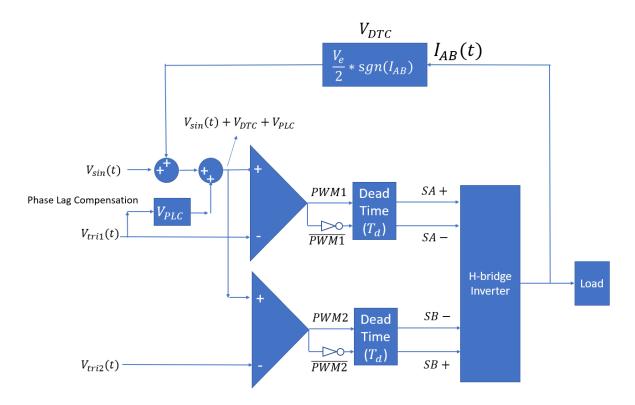

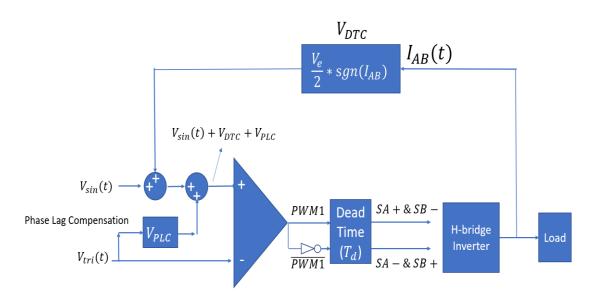

| Figure 5-4: Block diagram of PWM system with DTC and PLC176                          |

| Figure 5-5: The CCR value with DTC system in the first and last 3 Tpwm               |

| periods in a <i>Vsin</i> period178                                                   |

| Figure 5-6: Flowchart for PWM update interrupt featuring Dead Time                   |

| Compensation181                                                                      |

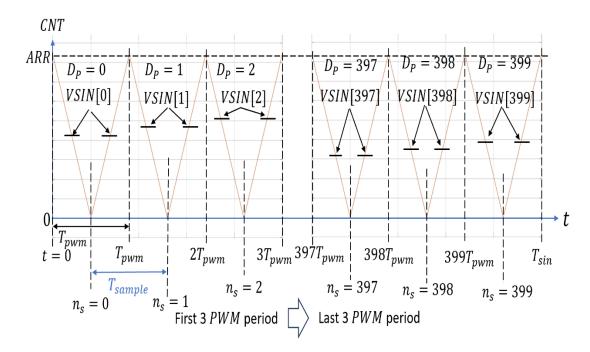

| Figure 5-7: The first and last 3 Tpwm in a Vsin period with ADC sample.              |

| 183                                                                                  |

| Figure 5-8: Basic close-loop system for calculating VSIN LUT185                      |

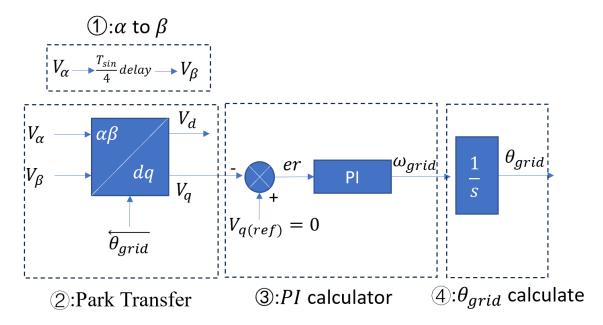

| Figure 5-9: Block diagram of <i>PLL</i> 186                                          |

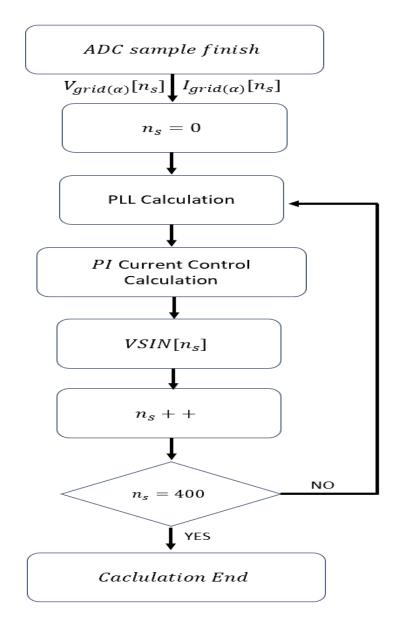

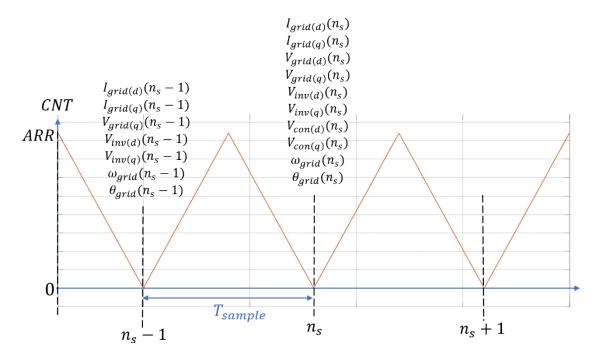

| Figure 5-10: The example of calculation system with ADC ns sample188                 |

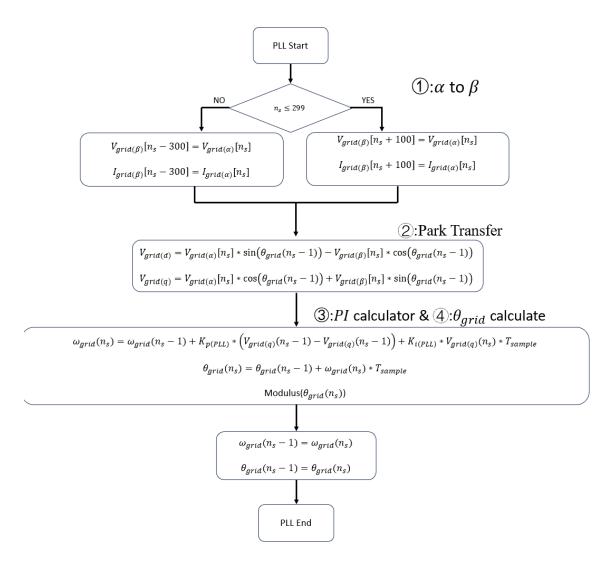

| Figure 5-11: The program flowchart of PLL system190                                  |

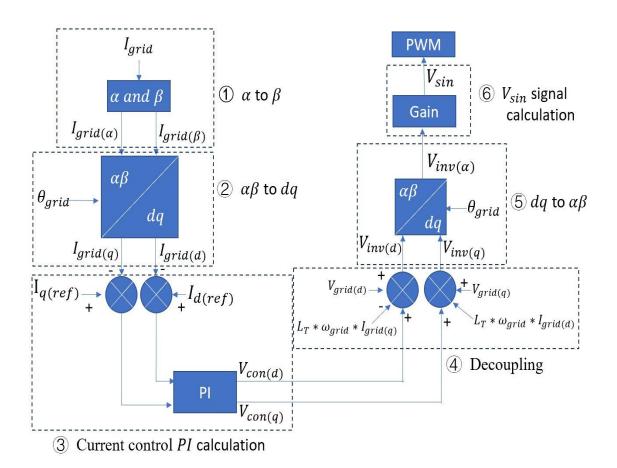

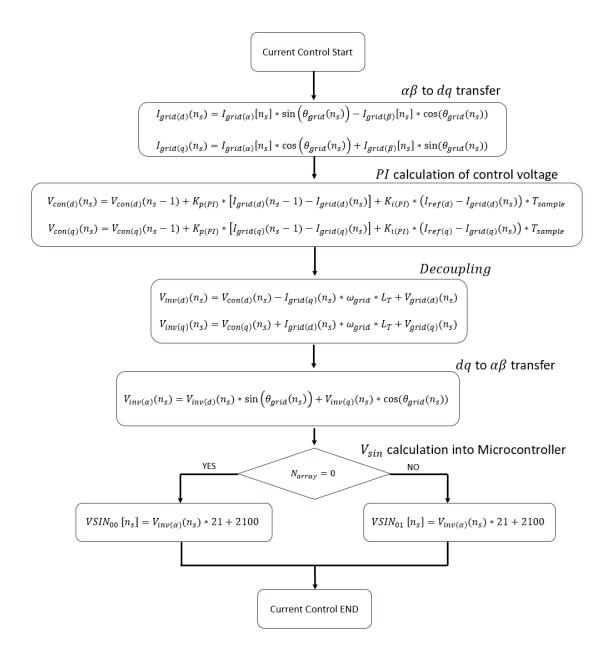

| Figure 5-12: Block diagram of PI current controller191                               |

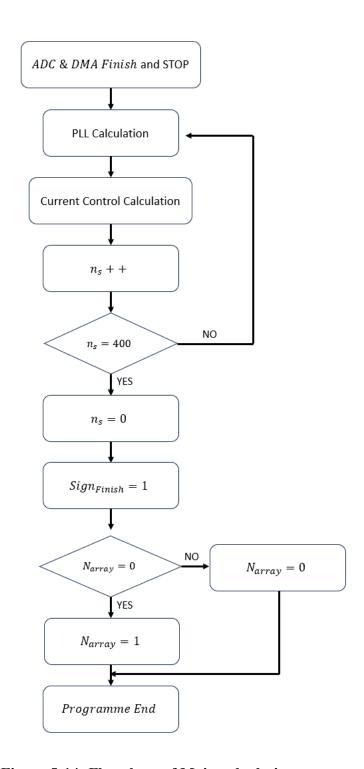

| Figure 5-13: The flowchart of PI current controller in microcontroller 194           |

| Figure 5-14: Flowchart of Main calculation program196                                |

| Figure 5-15: Flowchart of PWM interrupt program with DTC and grid                    |

| connected system198                                                                  |

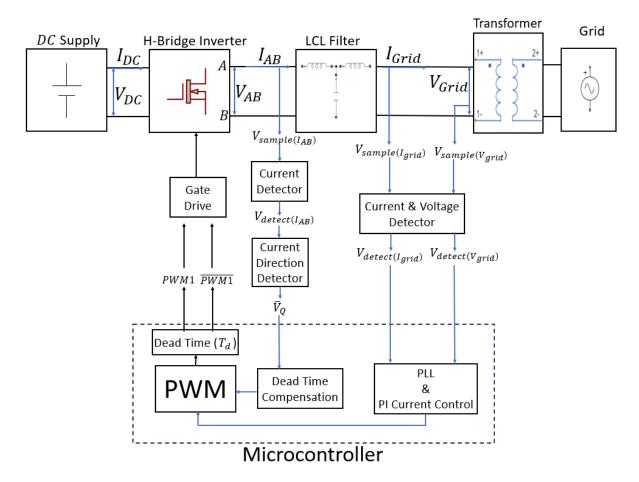

| Figure 6-1: Block diagram of H-Bridge inverter with Dead time compensation           |

| in open-circuit202                                                                   |

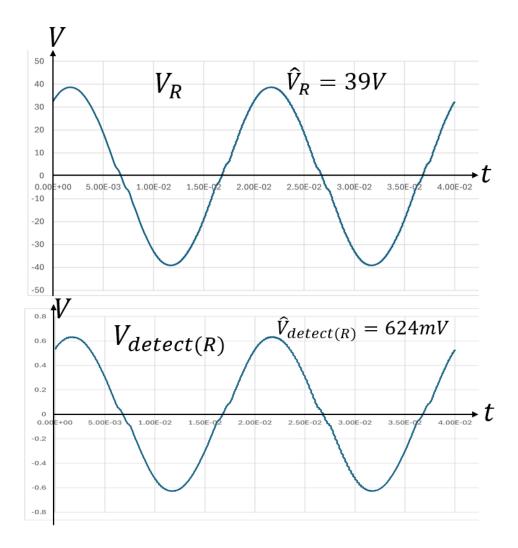

| Figure 6-2: experimental result of VR and Vdetect(R)204                              |

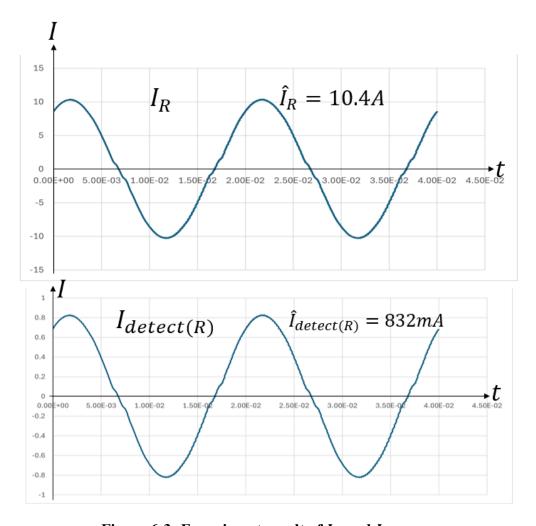

| Figure 6-3: Experiment result of IR and Idetect(R)205                                |

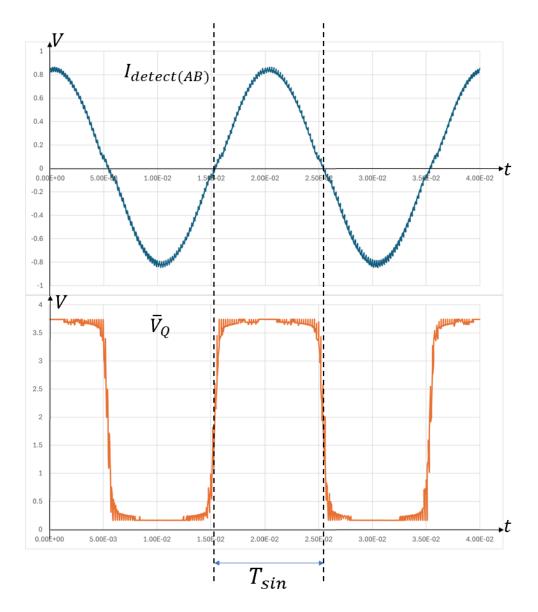

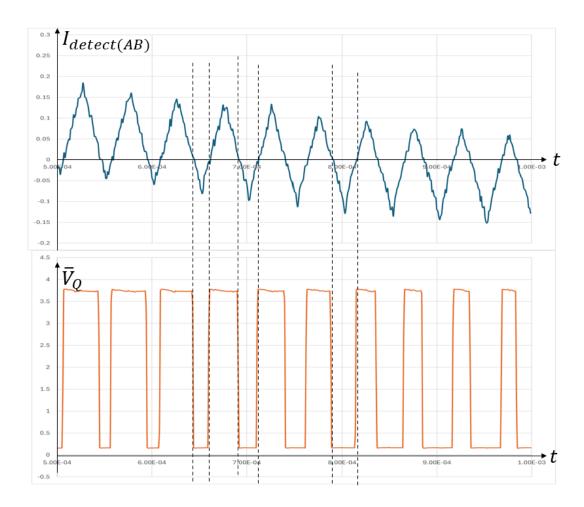

| Figure 6-4: Current waveform Idetect(AB) and VQ output from MAX913                   |

| in <i>Vsin</i> period206                                                             |

| Figure 6-5: Zoom of <i>Idetect(AB)</i> and <i>VQ</i> during zero-crossing207         |

| Figure 6-6: CCR value in VSIN LUT in PWM system in microcontroller208                |

| Figure 6-7: Experiment result of output voltage $VR$ when $Td = 1us$ and with        |

| DTC&PLC compensation209                                                              |

| Figure 6-8: Experiment result of output current $IR$ when $Td = 1us$ and with        |

| DTC compensation210                                                                  |

| Figure 6-9: Experiment result of output voltage $VR$ (a) $Td = 2us$ , (b) $Td = 2us$ |

| 3 <i>us</i>                                                                          |

| Figure 6-10: Experiment result of output current $IR$ (a) $Td = 2us$ , (b) $Td = 2us$ |

|---------------------------------------------------------------------------------------|

| 3 <i>us</i> 211                                                                       |

| Figure 6-11: Block diagram of Grid-connected H-Bridge power inverter                  |

| system213                                                                             |

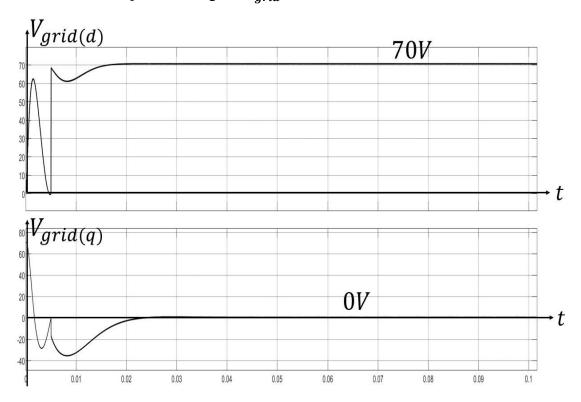

| Figure 6-12: MATLAB simulation result of $Vgrid(d)$ and $Vgrid(q)$ 214                |

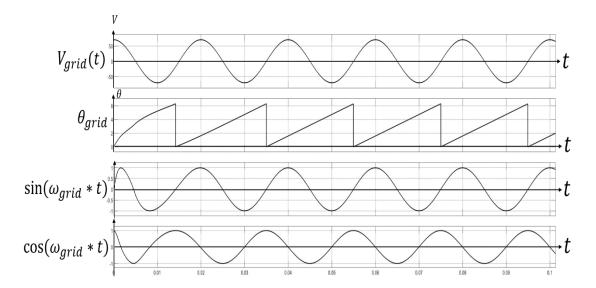

| Figure 6-13: The relation between grid voltage $Vgrid(t)$ and calculated grid         |

| angle $\theta grid$ in MATLAB simulation215                                           |

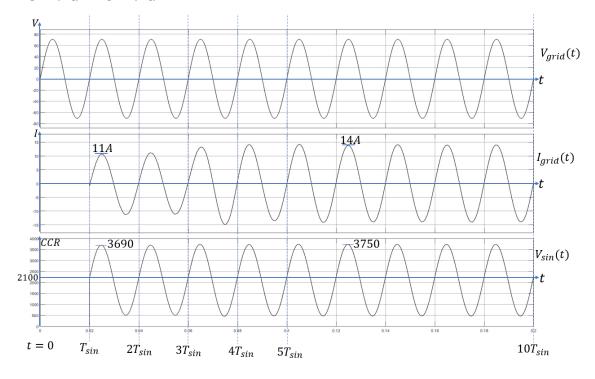

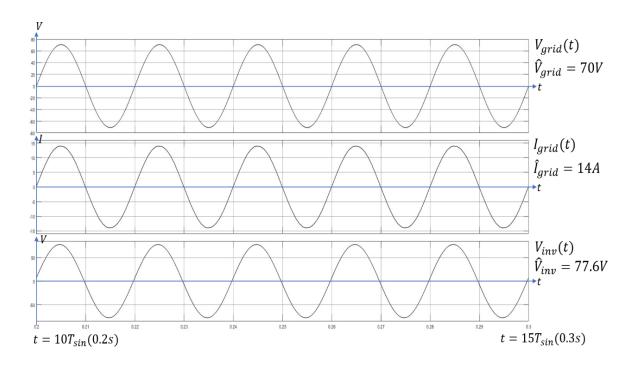

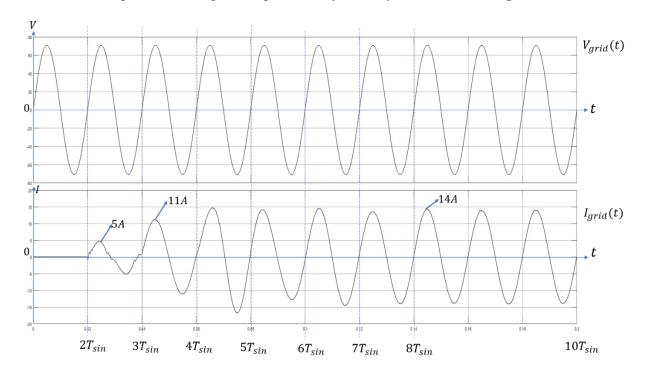

| Figure 6-14: Simulation of $Vgrid(t)$ , $Igrid(t)$ and $Vsin(t)$ during initial       |

| system217                                                                             |

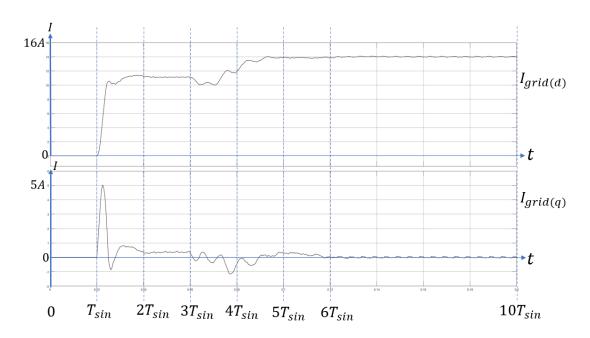

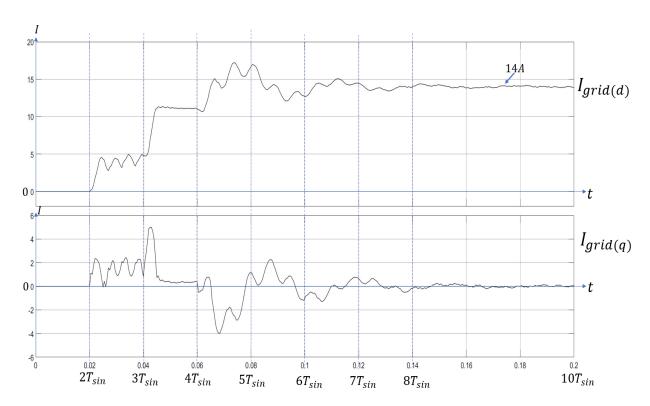

| Figure 6-15: Simulation result of $dq$ axis current of $Igrid(t)$ , $Igrid(d)$ and    |

| <i>Igrid(q)</i> 218                                                                   |

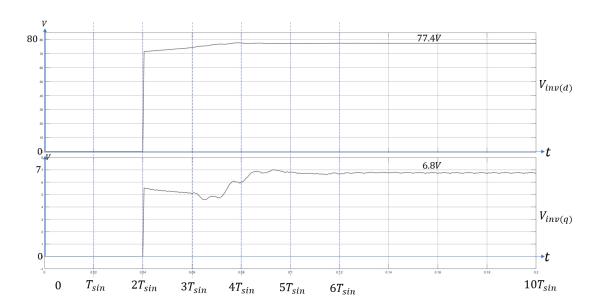

| Figure 6-16: Simulation result of inverter side fundamental $dq$ -axis voltage.       |

| 219                                                                                   |

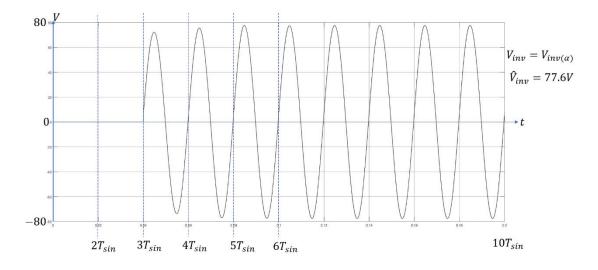

| Figure 6-17: Simulation result of fundamental inverter side voltage $Vinv(t)$ .       |

| Figure 6-18: Modulation signal $Vsin(t)$ in microcontroller produced from             |

| the PI current control220                                                             |

| Figure 6-19: Simulation result of output waveform from grid connected H-              |

| Bridge power inverter221                                                              |

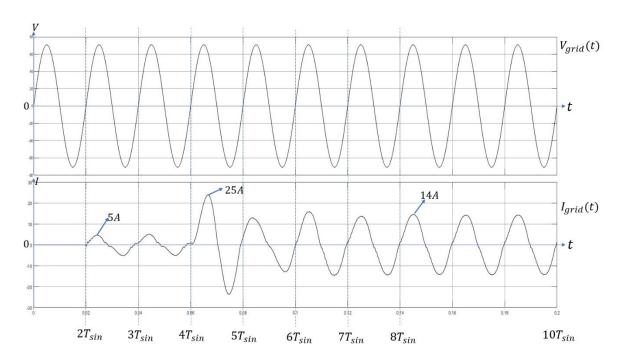

| Figure 6-20: Simulation result of $Vgrid(t)$ and $Igrid(t)$ during initial time       |

| with $Td = 1us$ 223                                                                   |

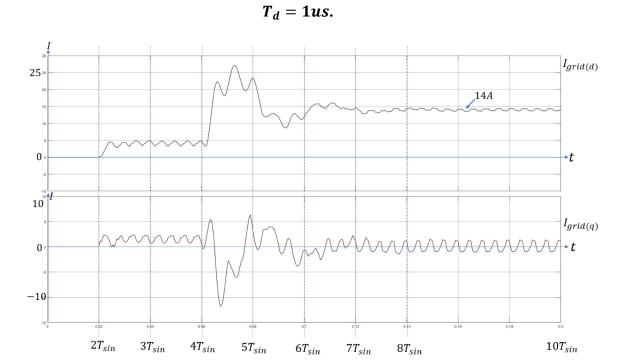

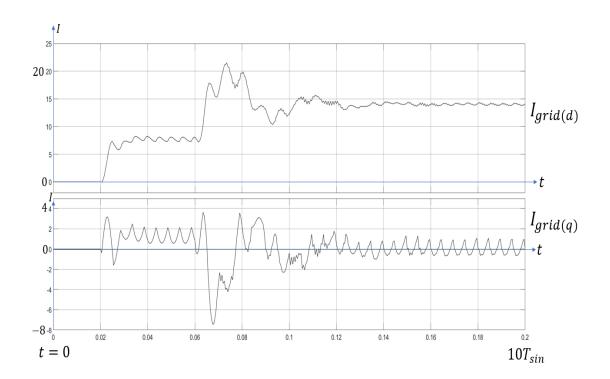

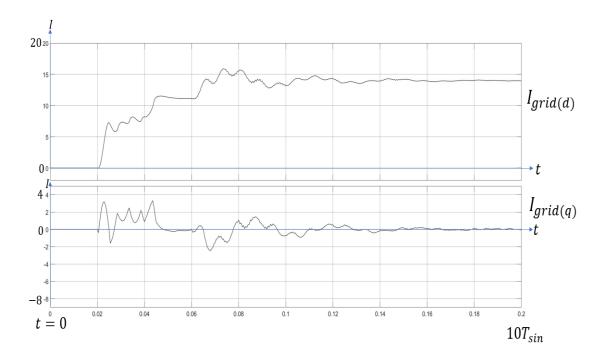

| Figure 6-21: Simulation result of $dq$ -axis current with $Td = 1us$ 223              |

| Figure 6-22: Simulation result of $Vgrid(t)$ and $Igrid(t)$ during the initial        |

| time with <i>DTC</i> system224                                                        |

| Figure 6-23: Simulation result of $dq$ -axis current of $Igrid$ with DTC system       |

| 225                                                                                   |

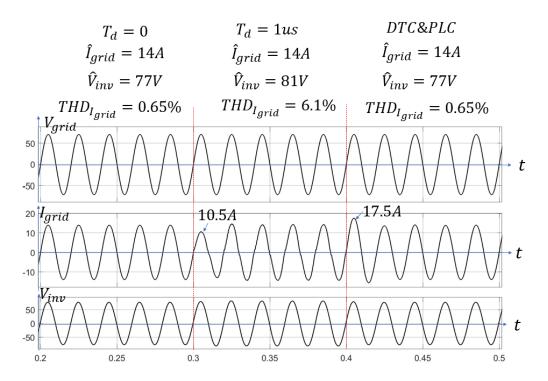

| Figure 6-24: Simulation result of Vgrid, Igrid and Vinv waveform under                |

| dead time effect and dead time compensation effect226                                 |

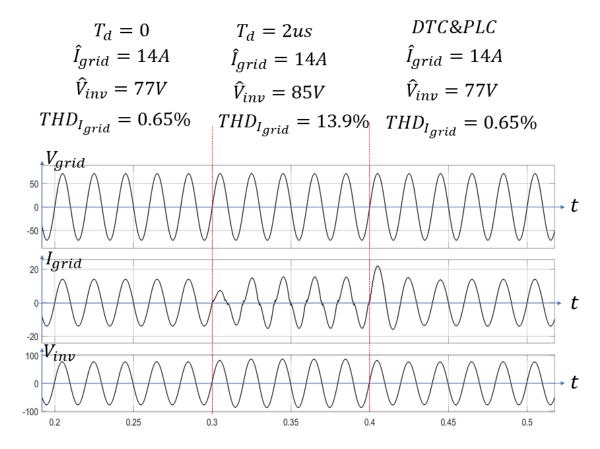

| Figure 6-25: Simulation result of Vgrid, Igrid and Vinv waveform under                |

| dead time effect and dead time compensation effect227                                 |

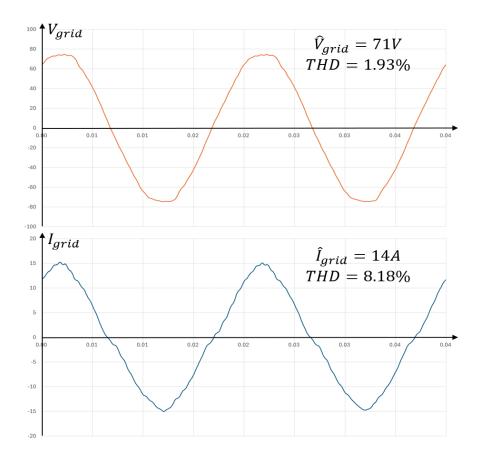

| Figure 6-26: Experimental result of grid voltage <i>Vgrid</i> and output current      |

| Igrid when $Td = 1us$ 228                                                             |

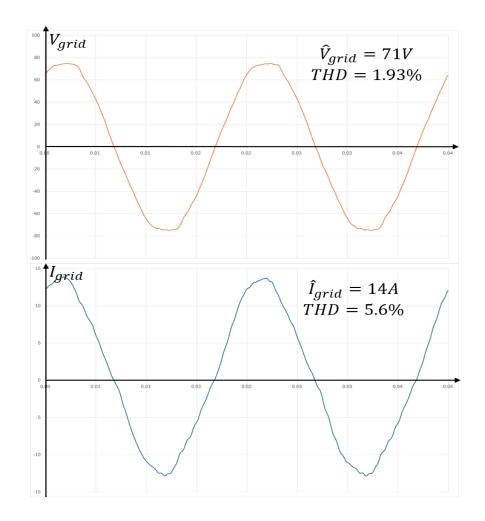

| Figure 6-27: Experimental result of grid voltage <i>Vgrid</i> and output current      |

| <i>Igrid</i> when $Td = 1us$ and adding Dead time Compensation229                     |

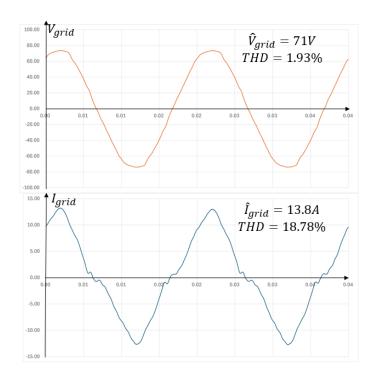

| Figure 6-28: Experimental result of grid voltage <i>Vgrid</i> and output current      |

| $Igrid \text{ when } Td = 2us. \dots 230$                                             |

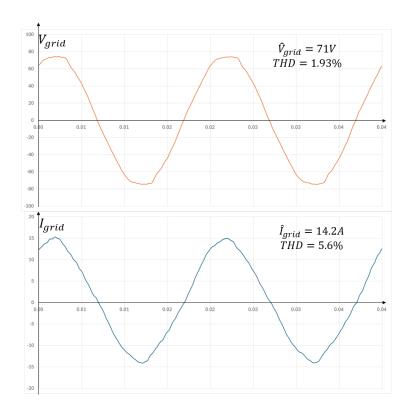

| Figure 6-29: Experimental result of grid voltage <i>Vgrid</i> and output current      |

| Igrid when $Td = 2us$ and with Dead time compensation230                              |

| Figure   | 6-30: Grid Connected 3-level H-Bridge power inverter MATLAB                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Sin      | nulation233                                                                                                                                   |

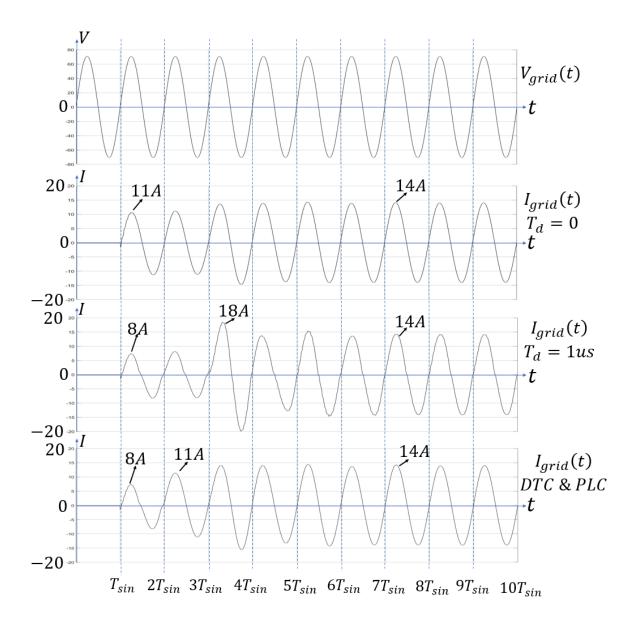

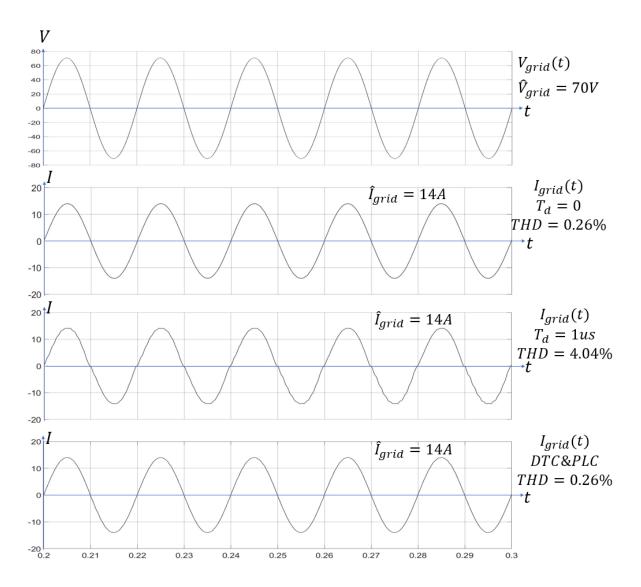

| Figure   | 6-31: Simulation result of $Vgrid(t)$ and comparation of $Igrid(t)$                                                                           |

| unc      | der different conditions during initial time234                                                                                               |

| _        | 6-32: Simulation result of $Igrid(d)$ and $Igrid(q)$ with $Td = 1us$                                                                          |

| Figure   | 6-33: Simulation result of $Igrid(d)$ and $Igrid(q)$ with DTC eration236                                                                      |

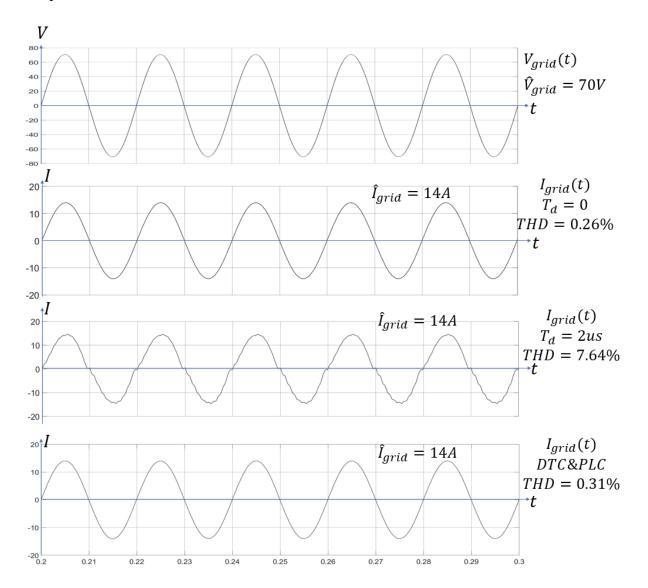

| unc      | 6-34: Simulation result of $Vgrid(t)$ , and comparation of $Igrid(t)$ der different conditions after steady-state of $PI$ current controller. |

| Figure ( | 6-35: Simulation result of $Vgrid(t)$ , and comparation of $Igrid(t)$ der different conditions after steady-state of $PI$ current controller  |

| wit      | h $Td = 2us$ 238                                                                                                                              |

# List of Table

| Table 1: switching status and output voltage VAB relation44                    |

|--------------------------------------------------------------------------------|

| Table 2: Output voltage of 2-level H-bridge inverter and switches sequence.    |

|                                                                                |

| Table 3: Total output voltage in Asymmetric system which L1=L and L2=0.        |

| 67                                                                             |

| Table 4: Total output voltage in Symmetric system which $L1=L2=\frac{L}{2}$ 67 |

| Table 5 : Parameter in the <i>LCL</i> filter design118                         |

| Table 6: Parameter in H-Bridge inverter circuit and <i>PWM</i> system202       |

| Table 7: parameter in grid-connected H-Bridge power inverter213                |

# List of Symbol

| zest of zymoot                            |                        |

|-------------------------------------------|------------------------|

| Name                                      | Symbol                 |

| <b>DC</b> Power Supply                    | $V_{DC}$               |

| Output voltage from H-Bridge              | $V_{AB}$               |

| Average Voltage                           | $V_{AV}$               |

| Fundamental Voltage of $V_{AB}$           | $V_{inv}$              |

| Grid Voltage                              | $V_{grid}$             |

| Peak Grid Voltage                         | $\hat{V}_{grid}$       |

| Inverter side Current                     | $I_{AB}$               |

| Grid side Current                         | $I_{grid}$             |

| Peak Grid Current                         | $\hat{I}_{grid}$       |

| Phase Locked Loop                         | PLL                    |

| Proportional-Integral Current Control     | PI Current Control     |

| <b>d</b> -axis Grid Voltage               | $V_{grid(d)}$          |

| <b>q</b> -axis Grid Voltage               | $V_{grid(q)}$          |

| <b>d</b> -axis Grid current               | $I_{grid(d)}$          |

| <b>q</b> -axis Grid current               | $I_{grid(q)}$          |

| Proportional parameter of <b>PLL</b>      | $K_{p(PLL)}$           |

| Integral parameter of <b>PLL</b>          | $K_{i(PLL)}$           |

| Proportional parameter of Current         | $K_{p(PI)}$            |

| Control                                   | <b>P</b> ()            |

| Integral parameter of Current Control     | $K_{i(PI)}$            |

| Calculated voltage from <b>PI</b> Current | $V_{con}$              |

| Controller                                |                        |

| Reference <b>d</b> -axis Grid Voltage     | $V_{d(ref)}$           |

| Reference <b>q</b> -axis Grid Voltage     | $V_{q(ref)}$           |

| Reference <b>d</b> -axis Grid Current     | $I_{d(ref)}$           |

| Reference <b>q</b> -axis Grid Current     | $I_{q(ref)}$           |

| Reference Modulation Signal               | $V_{sin}$              |

| Peak voltage of $V_{sin}$                 | $V_{sin}$              |

| Carrier signal                            | V <sub>tri</sub>       |

| Peak voltage of $V_{tri}$                 | $\widehat{m{V}}_{tri}$ |

| Modulation index                          | $m_i$                  |

| Duty Cycle                                | D                      |

| Duty Cycle of $V_{AB}$                    | $D_{AB}$               |

| Sinusoidal Pulse Width Modulation         | SPWM                   |

| <b>PWM</b> frequency                      | $f_{pwm}$              |

| Modulation signal frequency               | $f_{sin}$              |

| Grid frequency                            | $f_{grid}$             |

| Dead Time Compensation                    | DTC                    |

| Deadtime Compensation                     | DTC                    |

| Phase Lag Compensation                    | PLC                    |

| Dead Time Elimination                     | DTE                    |

| Dead Time                                 | $T_d$                  |

| Dead Time Error                | $V_e$      |

|--------------------------------|------------|

| Dead Time Duty Cycle           | $D_{T_d}$  |

| Dead Time Voltage Reduction    | $V_{DT}$   |

| Dead Time Compensation Voltage | $V_{DTC}$  |

| Phase Lag Compensation Voltage | $V_{PLC}$  |

| Inverter side inductor         | $L_{inv}$  |

| Inverter side ESR              | $R_{inv}$  |

| Grid side inductor             | $L_{grid}$ |

| Grid side ESR                  | $R_{grid}$ |

| Filter Capacitor               | $C_f$      |

| Damping Resistor               | $R_d$      |

# Chapter 1

## Introduction

### 1.1 Background

transforming electrical energy using the various types of semiconductor power devices, thereby ensuring electrical products are able to work in the right situation and giving the highest efficiency. There are four main types of power electronic converters, DC to DC (buck, boost), AC to AC (frequency conversion), AC to DC (rectifier) and DC to AC (inverter). Power converter could not only change the waveform of voltage and current, but also change other parameters such as frequency and phase angle etc. The concept and principle of inverter has already been mentioned by David Prince in 1925 through an article in the GE review titled "The Inverter" [1]. Based on research on rectifier device, David Prince gave the idea about converting DC power to AC power or signal, which encouraged the research not only on the inverter, but also the research on thyristor decade later with the advent of semiconductor devices. The development of inverter was challenging and time consuming due to the limits of power devices. Before 1956, the research about inverter is based on rectifier device such as highvacuum or gas-discharge tube [2]. As result, output power, AC waveform and efficiency are poor. It was not until research regarding the first thyristor was published, spurring investment from industry in 1956, after which the development of power inverter

What is the power electronic converter? It is an essential piece of technology for

started to grow up quickly. After invention of thyristor, the growing process of power inverter could be separated into three stages.

The first stage was from 1956 to 1980. The function of thyristor is similar to a diode, limiting the current flow direction. The difference between thyristor and diode is that thyristor could be turned "on" or "off" through the gate signal and it is because of this controllable characteristic that it is able to be utilised in inverter circuits. Voltage-Regulated SCR (Silicon-Controlled Rectifier) inverter was published first. After that, researchers realize that it was important to improve the output waveform from power inverter by designing better strategy to control gate signal. As result, in 1964, F.G.Turnbull put forward strategy "Selected Harmonic Reduction" method for use in the power inverter [3]. This method reduced troublesome harmonics and gave an output waveform which closer to a sinusoidal waveform. This method led to the basic idea for the future research and design on Pulse-Width Modulation (PWM) method. Between 1956 and 1980, most of power devices, thyristor mainly, could only work in low switching frequency. As result, most of inverters could only gave low frequency output around 400Hz. At that time, the size of the power inverter, transformer and filter were large, and also the transfer efficiency of inverter was low.

The second stage was from 1981 to 2000. During this stage, the design of power inverter was based on high switching frequency power devices such as Gate Turn-off Thyristor, MOSFET (Metal-Oxide-Semiconductor field-effect transistor) and IGBT (Insulated-

gate Bipolar Transistor) etc. Many electrical equipment such as transformer and filter inductor are related to the switching frequency which needs to be attenuated to improve output waveform fidelity. With higher switching frequency, the size of transformer and inductor can be smaller, which decreasing cost. Higher switching frequencies also afford a larger separation from output fundamental waveform, thereby, reducing the attenuation burden on the filter. As result, increasing switching frequency in the PWM system for driving power inverter is of great importance during this time.

The third stage starts after 2000. Although increasing switching frequency is desirable, increasing it without limit causes issues such as Skin effect, Electromagnetic interface and switching energy loss on power devices are becoming more significant. An important question arises in how to balance energy loss and frequency to reach the highest efficiency. In order to decrease the power loss on power devices, soft-switching technologies such as zero-voltage and zero-current switch had been developed. In addition, multi-level inverter technologies were becoming more popular, and since has become one of the main areas in development of inverter. The advantage of multi-level inverter is that it makes an output AC waveform with smaller voltage quantization transitions, and this lowers total harmonic distortion and decreases power loss in every single power device in an inverter. After 2000, the technologies on microelectronics, computers, intelligent control, and software keep developing. As result, *PWM* control technologies are becoming more intelligent, efficient and complex, which increases the output efficiency of power inverters.

Power inverters are widely used in many areas – motor drive, induction heater and air conditioner etc. Nowadays, power inverters are important in developing renewable energy technologies such as wind power and solar power. The aim of developing these renewable energy technologies is to decrease the use of non-renewable energy such as fossil fuel and coal and decrease greenhouse gas emissions. In addition, with the new goal of government policy in global areas, further boosting development of renewable. Achieving Zero-Carbon in 2050 is one of the most important goals in the UK [4][5]. Zero-Carbon is important not only in the UK, but also in the whole world [6]. From the global forecast summary in [7][8], renewable electricity capacity has increased from 750GW in 2016 to 950GW in 2024. And then the capacity goal in 2030 is at least 11000GW. In renewable energy technologies, Photovoltaic solar (PV) technology is a popular and fast-growing technology. The electric capacity of PV power increased from 90GW in 2016 to 400GW in 2024 [7]. Grid Connected PV power inverter system is a main research area in PV power technology. It transfers DC energy from PV panels to AC output into Grid. Power inverter is very important since it directly influences the efficiency of energy transfer from PV to Grid. As result, switching speed, control technologies and power inverter structure are important research areas in Grid connected PV power system.

#### 1.2 Motivation

With development of renewable energy technologies, higher efficiency power inverter system is required. In any power inverter, a dead time interval is necessary to guarantee a certain time for both devices in a single leg to be 'off' to avoid short circuit event during the commutation of power switches. Although dead time can ensure no short circuit event in *PWM* control, it will inevitably cause distortion since a diode is needed to conduct inductive load current especially during current zero-crossing. In addition, it will cause more problems such as power loss and output voltage reduction etc. In summary, without modification dead time usually negatively affects the performance of the power inverter since without dead time the devices turn-on and off would crossover giving rise to shoot-through, and this would increase power dissipation; the achieved maximum and/or minimum pulse width is affected, and the bridge voltage is not easily controlled at zero current crossings. As result, some technologies such as Dead Time Elimination (DTE) and Dead Time Compensation (DTC) are used to decrease dead time effect in power inverters.

Most DTC and DTE are used in 2-level power inverter in motor drives since the output current and voltage drop directly influences output power on motor. In addition, the voltage and current fluctuation during zero-crossing also influence motor drives. As result, they are used in the power inverter in motor drives for solving the reduction of voltage and current, and the fluctuation during zero-crossing. Main difference between DTC and DTE is current polarity detect method.

On the other hand, some DTC and DTE are also used in grid-connected power inverter. They focus on eliminating the distortion caused by dead time effect during zero-crossing through regulating the close-loop calculations (PLL, PI, PID control etc). Around 2005 technology dictated the dead time ( $T_d$ ) is usually to be set larger than 5us because of the switching speed of power switch is slow at that time. With new material and technologies for building power switch, switching speed is much faster now. By using high switching speed (short turn on and off time) power switch, dead time  $T_d$  can be set to very short ( $T_d < 0.5us$ ). As result, dead time effect is ignored in research when dead time is very short. On the other hand, very high-speed power switch is expensive which increase the cost in product. Besides, the default dead time in most PWM driver IC and microcontroller is 1us or more.

On the other hand, **0.5** us dead time is short in the power inverter system with **20**kHz switching frequency. What if switching frequency is increased to **60**kHz or higher, then **0.5** us dead time is long in this much higher switching frequency power inverter system. In the future, the turn-on and turn-off time of power switches will be shorter which decrease the dead time. But with the increase of requirement of higher switching frequency, the dead time effect will be more serious.

In conclusion, the technology for compensating dead time effect is still necessary in power inverter system.

#### 1.3 Contribution

In this thesis, a novel Dead Time Compensation (DTC) used in single phase Grid Connected 2-level and 3-level Power Inverter system will be introduced and described. The DTC is consisted of two parts, a deadtime value Compensation (*DTC*) and a Phase Lag Compensation (*PLC*). All contribution presents in this thesis focuses on proving accurate and stable DTC system in grid-connected H-Bridge power inverter. This section presents the contributions in this thesis mainly in Chapter 2, Chapter 3, Chapter 4 and Chapter 5.

#### **Chapter 2**

- Literature review and summary of DTC and DTE technologies.

- Literature review of various of **PLL** system,  $\alpha\beta$  signal transfer method in single phase system.

- Literature review of technologies of current controller in grid connected systems.

#### **Chapter 3**

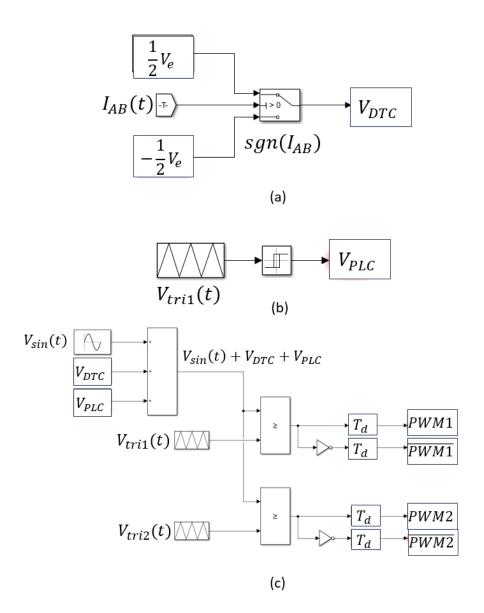

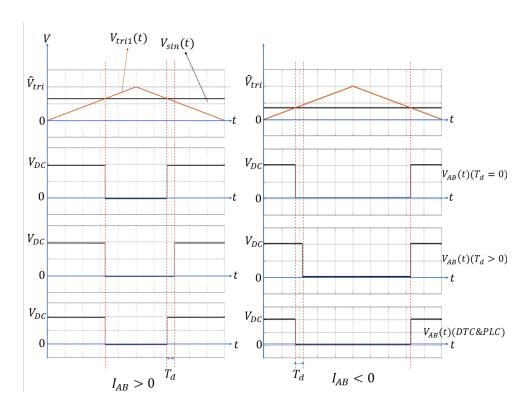

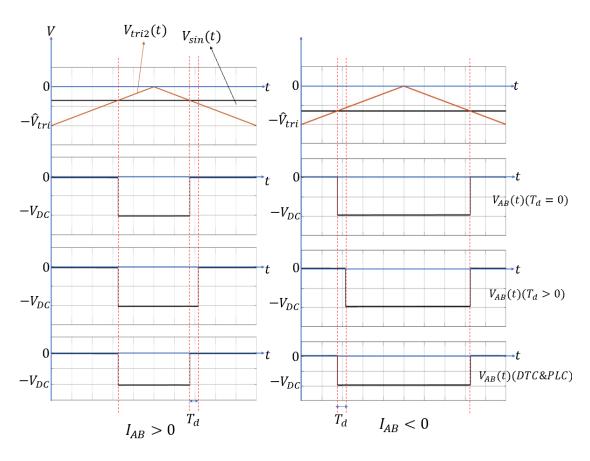

- Deadtime Compensation ( *DTC* ) operation in 2-level H-Bridge *SPWM* compensating power reduction and distortion caused by dead time.

- Phase Lag Compensation (*PLC*) in 2-level H-Bridge *SPWM* compensating every phase lag caused by dead time and every signal transfer time delay between output

*PWM* signal and power switches.

- Deadtime Compensation (*DTC*) operation in 3-level H-Bridge Level-shift *SPWM*.

- Phase Lag Compensation (*PLC*) operation in 3-level H-Bridge Level-shift *SPWM*.

#### **Chapter 4**

- Detail of **PI** parameter calculation in **PLL** and **PI** current controller, and decoupling system in **PI** current controller.

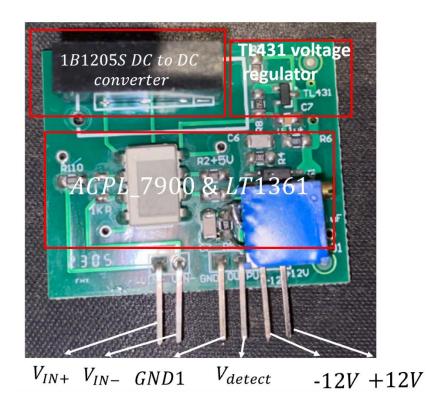

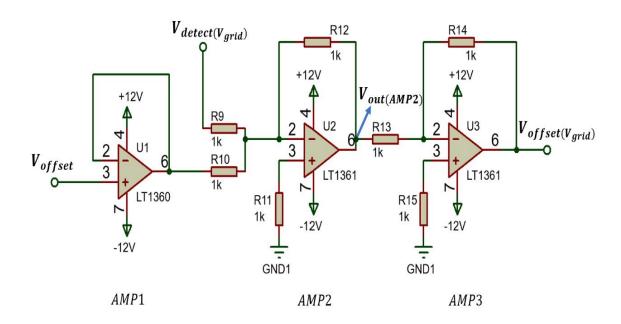

- An improved current detector based on *ACPL*\_7900 available for detecting high switching frequency component of output current from H-Bridge inverter.

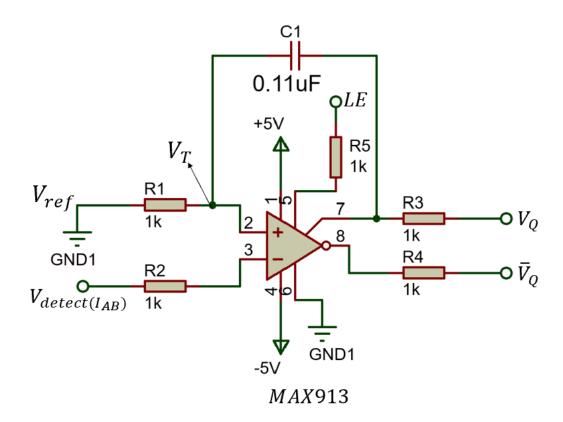

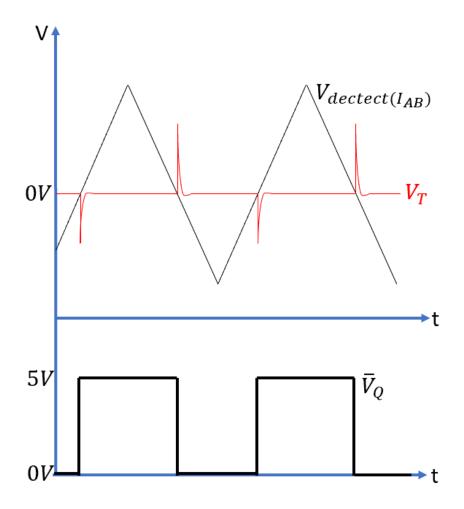

- An improved current polarity detector flows the current detector for providing accurate current direction information for DTC system.

#### Chapter 5

Providing flowchart detail of how the DTC (*DTC* & *PLC*) is operated and cooperated with *PLL* and *PI* current controller without changing their calculation progress in STM32F407 microcontroller.

#### 1.4 Thesis Structure

#### Chapter 2

Providing background information and literature review. Section 2.1 provides a short introduction of whole grid-connected power inverter system. Section 2.2 describes the structure of a H-Bridge inverter and *SPWM* system of 2-level H-Bridge inverter system. Section 2.3 describes the *SPWM* system in a 3-level H-Bridge inverter. Section 2.4 provides literature review about DTC and DTE technologies. Section 2.5 provides the background information and basic structure of a low-pass filter *LCL*. Section 2.6 introduces the basic information about Phase-Locked Loop (*PLL*) and *PI* current controller in a grid connected system. Section 2.7 and 2.8 provides the literature review about challenge and technologies in PV power system.

#### Chapter 3

Section 3.1 and 3.2 describes the detail of dead time effect in a 2-level H-Bridge inverter including the effect on output voltage, duty cycle and distortion. Section 3.3 describes DTC system operation in a 2-level H-Bridge inverter. Section 3.4 presents a MATLAB Simulink simulation about DTC operation in an open-loop 2-level H-Bridge inverter. Section 3.5 and 3.6 describes the detail of dead time effect and DTC system in a 3-level H-Bridge inverter system. Then, in section 3.7, a simulation of DTC operation in an open-loop 3-level H-Bridge inverter is shown.

#### Chapter 4

This chapter focuses on describing the design of experimental platform for DTC operation in grid connected H-Bridge inverter. Section 4.1 provides detail of every component design in a low-pass filter *LCL*. Section 4.2 provides detail about design of *PLL* and *PI* current controller, including the calculation of *PI* (Proportional and Integral) compensator parameters. From section 4.3 to 4.6, the design of power switch drive circuit, detector, current polarity detector and safety modules is described.

#### **Chapter 5**

This chapter introduces microcontroller system design of *PWM*, DTC, *PLL* and *PI* current controller. And then providing detail about how the *SPWM*, *DTC*, *PLL* and *PI* current controller cooperates in the microcontroller STM32F407.

#### Chapter 6

Section 6.1 presents the experimental results of current and voltage detector operation, and then the results of current polarity detector operation in DTC system. Section 6.2 and 6.3 together present the Simulation and Experiment validation about dead time effect and DTC operation in a grid connected 2-level H-Bridge inverter. Finally, section 6.4 shows only the MATLAB simulation result of dead time effect and DTC operation in a grid connected 3-level H-Bridge power inverter.

# Chapter 2

# Background information and literature review

The previous chapter set out the goals of the research and described the motivation in this project. This chapter reviews relevant research publications providing further insight into the topic and provides a benchmark for the present state-of-the-art. Prior to reviewing the literature, the basic structure of the power electronic converter system is introduced.

#### 2.1 Introduction

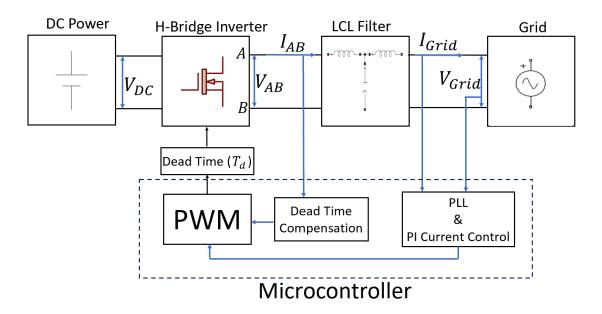

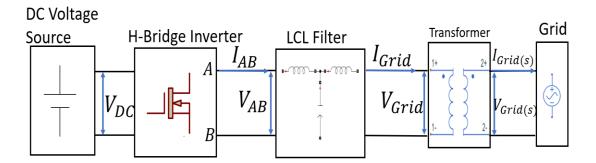

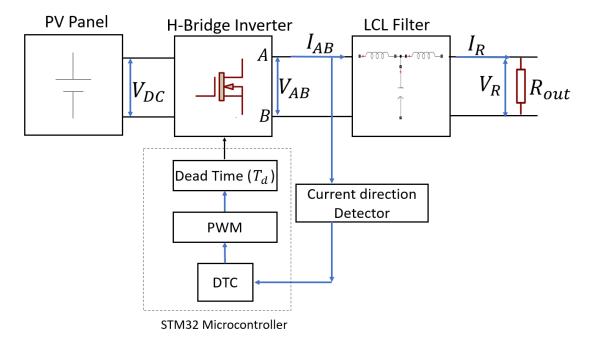

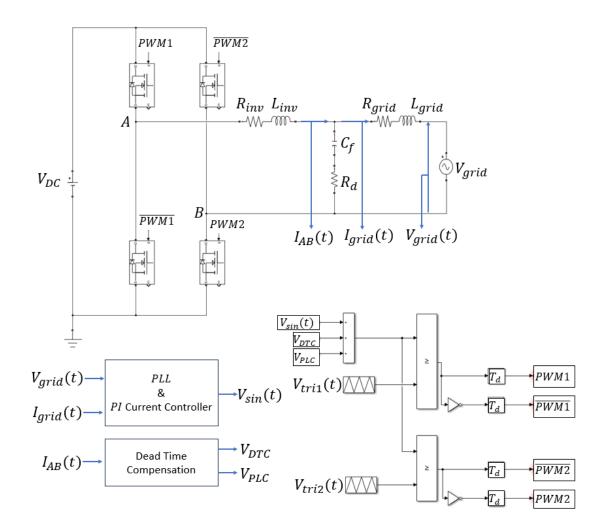

This project focuses on developing a grid connected power inverter system. Fundamentally this system consists of an H-Bridge power inverter, pulse width modulator (*PWM*) system, *PI* current controller and a *PLL* to synchronize inverter system to grid as shown in **Figure 2-1**

Operation of the system is as follows:

With reference to **Figure 2-1**, DC power is transformed into AC via the single-phase inverter stage which then injects AC currents into the grid. The input signals to system are active and reactive power demands and the output is an AC voltage waveform which is synchronized to the grid and an AC current which is phase-shifted from the AC

voltage to inject the requested reactive power. The inverter itself consists of a H-bridge inverter power stage, *PWM* generator, *PI* current controllers and a phased-locked loop (*PLL*) for synchronizing the inverter output to grid. The inverter output voltage is filtered by a *LCL* filter before connecting to grid.

Figure 2-1: Block Diagram of Grid Connected H-Bridge Power Inverter.

## 2.2 H-Bridge Power Inverter

## 2.2.1 H-Bridge Inverter

Power inverter is a system which transfers DC power to AC power, and it is widely used in many areas such as motor control, grid power system and renewable energy transfer systems. Of the many types of inverter circuits described in the literature, half-bridge and H (full) bridge are still the most popular due to low-component count and the inherent cost advantage this brings. The work described in this thesis is focused on

H-bridge due to its lower voltage overhead requirements when compared to the half-bridge inverter.

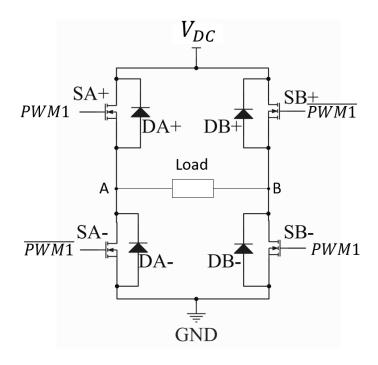

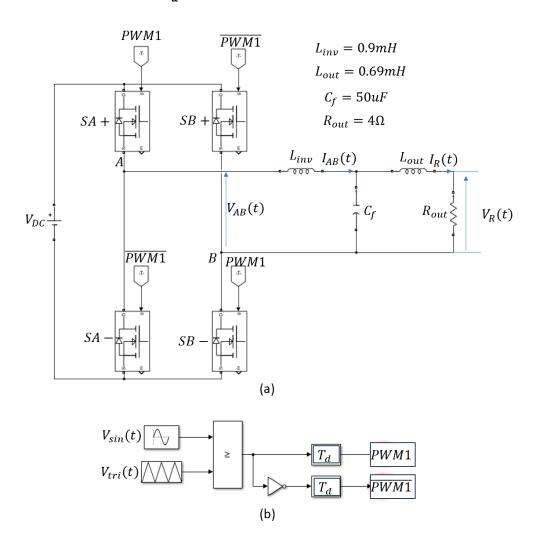

**Figure 2-2** shows a basic structure of H-Bridge inverter which consists of four power switches such as MOSFET and IGBT. In this project, the MOSFET power switch is used in the design of H-Bridge inverter.

H-Bridge inverter contains two power switch legs A and B, and each leg contains two power switches with the symbol + denoting the high-side device and – denoting the low-side device. Thus, leg A consists of switches SA + and SA –, while the leg B consists of switch SB + and SB – DA + and DA – are the freewheeling diodes of power switches in leg A, DB + and DB – are the freewheeling diodes of power switches of leg B. In MOSFET power switches, all freewheeling diode functions are achieved by body diodes between drain and source terminals om MOSFET.

The output of leg A is labelled as node A, and the output of leg B is labelled node B and the load is connected between these two nodes. The PWM1 and  $\overline{PWM1}$  are complementary PWM signals used to control the respective switches. The PWM system is described later in this section.

Figure 2-2: Basic Structure of H-Bridge Inverter.

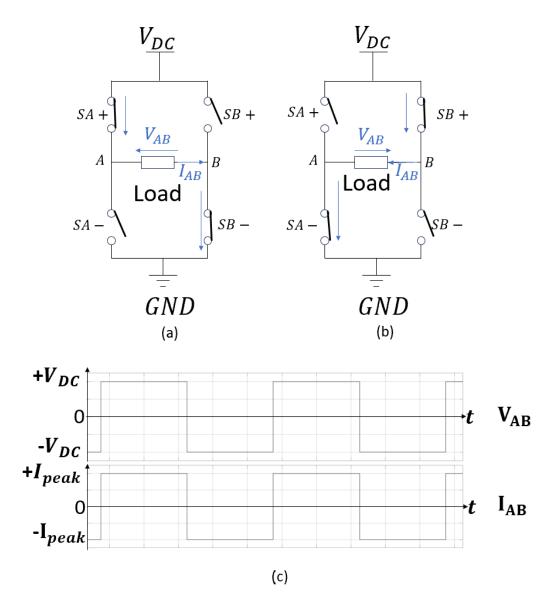

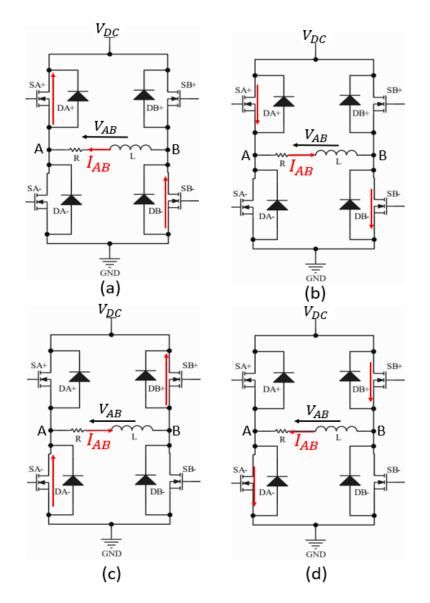

2-level H-bridge produces a bipolar output voltage  $V_{AB}$ . As shown in Figure 2-3 (a), when the switches SA + and SB - are turned on, switches SA - and SB + are turned off. Current flows from leg A to leg B, with a positive peak current ( $I_{AB} = +I_{peak}$ ), and the load voltage  $V_{AB} = +V_{DC}$ . When the switches SA + and SB - are turned off, the switches SA - and SB + are turned on, current flows from leg B to leg A, as shown in Figure 2-3 (b). So, the current direction is negative ( $I_{BA} = -I_{AB}$ ) and the load voltage is  $V_{AB} = -V_{DC}$ . Figure 2-3 (c) shows the load voltage and current waveforms for a resistive load H-Bridge inverter.

Figure 2-3 : (a)  $V_{AB}=+V_{DC}, I_{AB}>0$ . (b)  $V_{AB}=-V_{DC}, I_{AB}<0$ . (c) Voltage and current waveform with restive load.

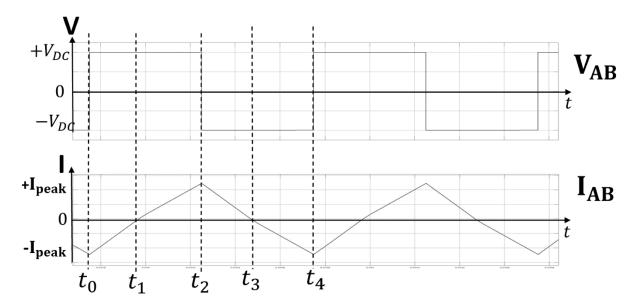

With an inductive load the behavior of H-Bridge is different. The output current with an inductive load cannot change instantaneously. After the inductor flux has been established it will act as current source, and it will continue to maintain current flow (both amplitude and direction) regardless of the status of the switching devices. As result, the freewheeling diodes (body diodes) of switches are used for maintaining the

current path when the power switches are turned off. **Figure 2-4** and **Figure 2-5** shows the direction of output voltage and current between the leg **A** and **B** of H-Bridge when the load is inductive.

Figure 2-4 : Output load voltage  $V_{AB}$  and current  $I_{AB}$  waveform with inductive load.

Figure 2-5: Voltage and current direction in H-Bridge from when time t from  $t_0$  to  $t_4$ . (a)  $t_0$  to  $t_1$ , (b)  $t_1$  to  $t_2$ , (c)  $t_2$  to  $t_3$ , (d)  $t_3$  to  $t_4$ .

Before time  $t_0$ , the switch SA + and SB - are kept off, while SA - and SB + are kept on. The load voltage  $V_{AB} = -V_{DC}$  and load current  $I_{AB} = -I_{peak}$ . At time  $t_0$ , SA + and SB - turns on, while SA - and SB + turns off,  $V_{AB} = +V_{DC}$ . From time  $t_0$  to  $t_1$ , the energy stored in inductive load start to release, current keeps flowing from leg B to

leg A. Because MOSFET switch is bidirectional after it is conducted, the load current  $I_{AB}$  flows from leg B to leg A through the SB — and SA + as shown in Figure 2-5(a). At time  $t_1$ , the energy stored in load inductance has been fully released, hence the current reaches to 0A. From  $t_1$  to  $t_2$ , the switches SA + and SB — are still on, while SA — and SB + are still off,  $V_{AB}$  is still equal to  $+V_{DC}$ . The load current  $I_{AB}$  flows from leg A to leg B through SA + and SB —, which is shown in Figure 2-5 (b). The inductive load is charged at positive direction and  $I_{AB}$  start to increase.

At time  $t_2$ , the switches SA + and SB - turns off, while SA - and SB + turns on, load voltage  $V_{AB}$  changes from  $+V_{DC}$  to  $-V_{DC}$ . The load current  $I_{AB}$  reaches to the  $+I_{peak}$ . From  $t_2$  to  $t_3$ , the energy stored in the load starts to release and this maintains current flow from leg A to leg B through the SA - and SB + as shown in Figure 2-5(c).

At time  $t_3$ , the energy in inductive load is fully released, hence  $I_{AB}$  decrease to 0. From  $t_3$  to  $t_4$ , SA — and SB + are still on, while SA + and SB — are still off,  $V_{AB}$  is still equal to  $-V_{DC}$ . The load current  $I_{AB}$  start to flow from leg B to leg A through the SB + and SA — as shown in Figure 2-5 (d). During this time, the inductive load is charged in negative direction, which increases from 0 to  $-I_{peak}$ .

The time  $t_4$  is equal to  $t_0 + T_{PWM}$ , where  $T_{PWM}$  is the period time of PWM wave. At this time,  $I_{AB}$  reaches to  $-I_{peak}$  and a new PWM period starts.

From time  $t_3$  to  $t_4$ , switches SA + and SB - turns on (SA - & SB + off),  $V_{AB} = +V_{DC}$ . Now, the energy stored in the inductor starts to release, current keeps flowing from leg B to leg A through switches SA + and SB -.  $I_{AB}$  increases from  $-I_{peak}$  to 0.

In conclusion, when  $I_{AB}$  is positive, the inductor is charged when  $V_{AB} = V_{DC}$ , while discharged when  $V_{AB} = -V_{DC}$ . When  $I_{AB}$  is negative, the inductor is charged when  $V_{AB} = -V_{DC}$ , while discharged when  $V_{AB} = +V_{DC}$ . It is clear to see that the output current is only conducted by the MOSFET power switches in ideal H-Bridge, and the voltage drop on power switches is zero since the resistance of switches is 0 ideally. If the power switches are changed to IGBT, the inductive current from inductive load will be conducted by extra free-wheeling diodes, which may cause voltage drop on diodes. In addition, the effect of diode recovery will affect the system under high frequency. In the previous discussion, the switches turn on and off at low frequency, and the duty cycle of switches is always 50%. It is clear to see that the energy in the inductor is released and stored completely during the work of the H-Bridge. The inductor in load acts as a filter, which changes the waveform shape of output current and voltage. Comparing the load current waveform in Figure 2-3 (c) and Figure 2-4,  $I_{AB}$  is changed from square wave to a triangle wave after inductive filter, but still far from a sin or cos waveform. The output from H-Bridge is related to the filter and circuit design of load. In addition, the control system of H-Bridge is very important. In the next section, the **PWM** control system is described.

# 2.2.2 PWM Control System in 2-level H-Bridge inverter

Before describing **PWM** system, two definitions relating to **PWM** system needed to be described, which are Duty Cycle and Fundamental signal.

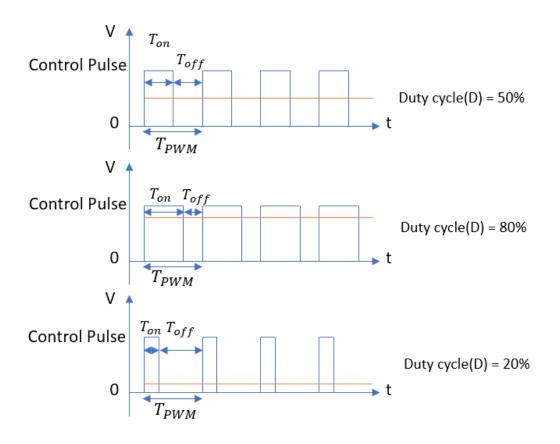

The duty cycle is the ratio of ON time  $T_{on}$  of the switch to the PWM time period  $T_{PWM}$ . The PWM time period  $T_{PWM}$  is fixed which is equal to the total time of  $T_{on}$  and  $T_{off}$  time. Figure 2-6 shows the duty cycle change of a control pulse and equation (1) presents the calculation of duty cycle. The duty cycle of control pulse in PWM system decides the duty cycle of output voltage  $V_{AB}(t)$  from H-Bridge inverter.

Figure 2-6: Control pulse Duty Cycle.

$$Duty Cycle = D = \frac{T_{on}}{T_{PWM}}$$

(1)

Fourier analysis demonstrates that a repeating signal f(t) can be represented by an infinite series of sin/cos waveforms. Typically, a waveform is decomposed into integer multiples of its fundamental frequency  $\omega_0$  where the coefficients associated with each sin/cos term represent the contribution of a particular harmonic component. The Fourier series and fundamental signal are important in H-Bridge inverter and PWM system as they are used to determine the total harmonic distortion (THD) in the output voltage/current waveforms and help in the design of the output filter. THD is used for checking how much noise or other signals are mixed with the fundamental signal. The definition of the Fourier series is given below where equation (2) shows how a time varying signal f(t) can be decomposed into an infinite sum of sine and cosine terms. Equations (3)-(5) define the coefficients for (2). Equations (6) and (7) define the complex form of the Fourier series.

$$f(t) = \frac{a_0}{2} + \sum_{n=1}^{\infty} [a_n \cos(n\omega_0 t) + b_n \sin(n\omega_0 t)]$$

(2)

$$a_0 = \frac{2}{T} \int_0^T f(t)dt = 0 (no bias)$$

(3)

$$a_n = \frac{2}{T} \int_0^T f(t) \cos(n\omega_0 t) dt$$

(4)

$$b_n = \frac{2}{T} \int_0^T f(t) \sin(n\omega_0 t) dt$$

(5)

$$f(t) = \sum_{n=-\infty}^{n=\infty} C_n e^{in\omega_0 t}$$

(6)

$$C_n = \frac{1}{T} \int_0^T f(t)e^{-in\omega_0 t} dt \tag{7}$$

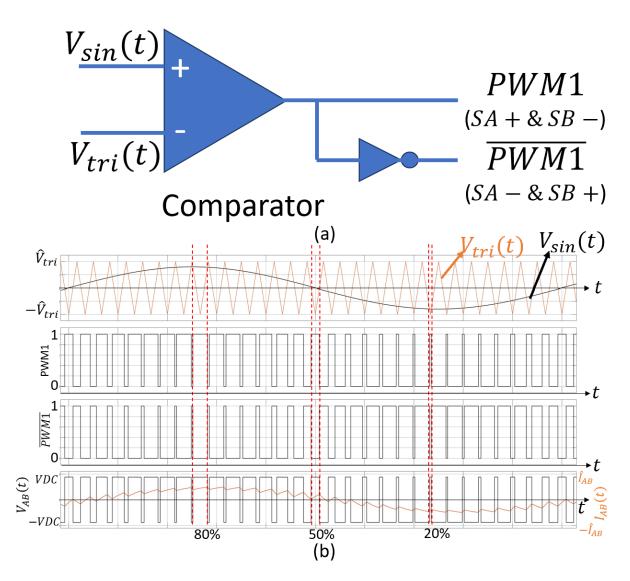

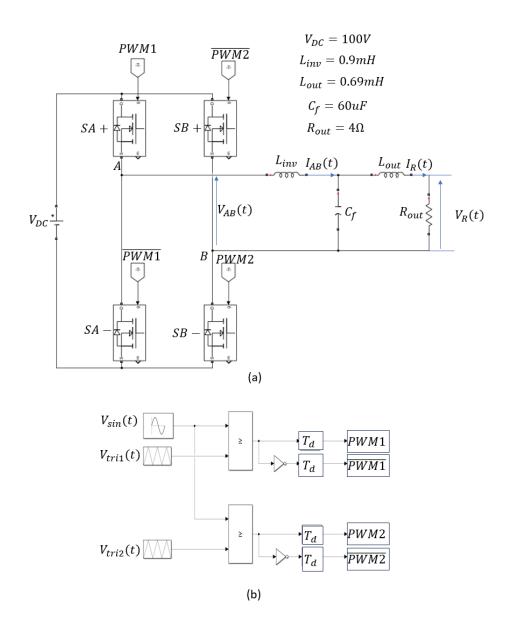

Sinusoidal PWM (SPWM) is commonly used in controlling power switches in H-Bridge inverters. Figure 2-7 (a) shows the block diagram of a Sinusoidal Pulse Width Modulation (SPWM) system.  $V_{sin}(t)$  is the reference sine waveform which is called modulation signal, and it is the amplitude and frequency of this waveform which influences amplitude and frequency of output waveform from inverter.  $V_{tri}(t)$  is the triangle wave which is called carrier signal. The signals PWM1 and  $\overline{PWM1}$  are output PWM signal produced by comparing two signals  $V_{sin}(t)$  and  $V_{tri}(t)$ , they are used for controlling the gate of power switches.

In a 2-level H-Bridge inverter, the switches SA + and SB - are controlled by PWM1, while  $SA - \text{and } SB + \text{are controlled by } \overline{PWM1}$ . In Figure 2-7, the values 0 and 1 correspond to conduction states of the switches with 0 being off (not conducting) and 1 being on (conducting). The signal PWM1 and  $\overline{PWM1}$  are complementary. When  $V_{sin}(t) > V_{tri}(t)$ , PWM1 = 1 (SA + & SB - are on) and  $\overline{PWM1} = 0$  (SA - & SB + are off),  $V_{AB}(t) = +V_{DC}$ . This time is on time  $T_{on}$ . When  $V_{sin}(t) < V_{tri}(t)$ , PWM1 = 0 (SA - & SB + are off) and  $\overline{PWM1} = 1$  (SA - & SB + are on).  $V_{AB}(t) = -V_{DC}$ . This time is off time  $T_{off}$ .

Figure 2-7 : (a) Block diagram of PWM system. (b) waveform of  $V_{tri}(t), V_{sin}(t),$   $PWM1, \overline{PWM1}, V_{AB}(t) \text{ and } I_{AB}(t).$

For the description that follows it has been assumed that the load has been inductively filtered and the corner frequency of the inductive filter is significantly lower than PWM frequency but higher than the sinusoid frequency such that the current is sinusoidal with a small ripple and has negligible phase shift with respect to the reference. With SPWM control system, the duty cycle of  $V_{AB}(t)$  varies according to the reference signal

$V_{sin}(t)$ . The duty cycle also influences the energy charge and release in the inductive load, which influences the increase or decrease of  $I_{AB}(t)$ .

The reference modulation signal  $V_{sin}(t)$  is a per unit value which represents a low frequency sin waveform with equation (8).

$$V_{sin}(t) = \widehat{V}_{sin} * \sin(\omega_{sin} t) \quad \omega_{sin} = 2\pi f_{sin} \quad f_{sin} = \frac{1}{T_{sin}}$$

(8)

where  $\hat{V}_{sin}$  is the peak value of  $V_{sin}(t)$ ,  $f_{sin}$  is the frequency of  $V_{sin}(t)$  and it is also the fundamental frequency of output waveform from H-Bridge inverter.  $V_{tri}(t)$  is a triangle carrier wave which changes between  $\pm \hat{V}_{tri}$  with high carrier frequency  $f_{tri}$ . In equation (9),  $\hat{V}_{tri}$  is the peak voltage of  $V_{tri}(t)$ , the  $f_{pwm}$  is the high carrier frequency which is also the PWM frequency. During the first half PWM period from 0 to  $\frac{T_{pwm}}{2}$ ,  $V_{tri}(t)$  increases from negative peak value  $-\hat{V}_{tri}$  to positive peak value  $\hat{V}_{tri}$  during half PWM period from  $\frac{T_{pwm}}{2}$  to  $T_{pwm}$ ,  $V_{tri}(t)$  is decreasing from  $+\hat{V}_{tri}$  to  $-\hat{V}_{tri}$ .

$$V_{tri}(t) = \begin{cases} \frac{4\hat{V}_{tri}}{T_{pwm}} * t - \hat{V}_{tri} & 0 < t < \frac{T_{pwm}}{2} \\ \hat{V}_{tri} - \frac{4\hat{V}_{tri}}{T_{nwm}} * t & \frac{T_{pwm}}{2} < t < T_{pwm} \end{cases} \qquad T_{pwm} = \frac{1}{f_{pwm}}$$

(9)

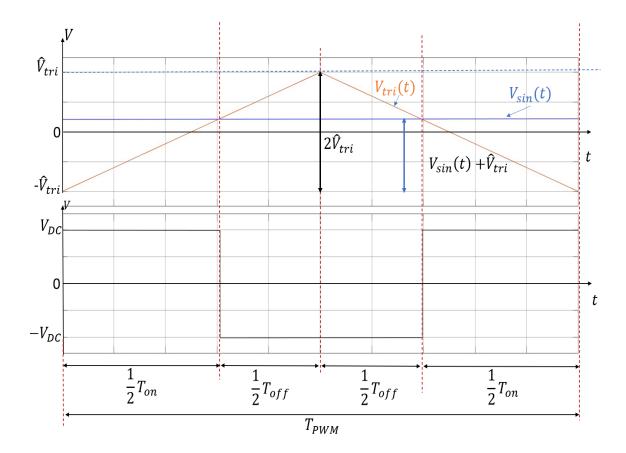

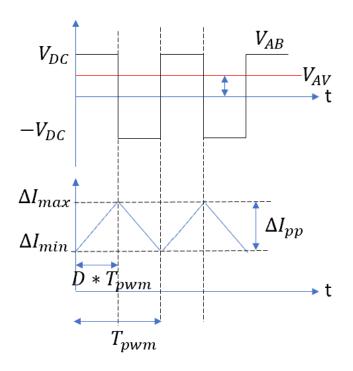

Figure 2-8 shows the zoomed diagram of waveform of signal  $V_{sin}(t)$ ,  $V_{tri}(t)$  and  $V_{AB}(t)$  in a single PWM period. Because frequency of  $V_{tri}(t)$  is much higher than  $V_{sin}(t)$ , after zooming in one period of  $V_{tri}(t)$ , the  $V_{sin}(t)$  can be seen as a constant value. In PWM system, for avoiding over modulation, the peak value of modulation waveform  $\hat{V}_{sin}$  is lower than  $\hat{V}_{tri}(-\hat{V}_{tri} < V_{sin}(t) < \hat{V}_{tri})$ .

**Figure 2-8 :** Diagram of waveform of signal  $V_{sin}(t)$ ,  $V_{tri}(t)$  and output  $V_{AB}(t)$  in one  $T_{nwm}$

In SPWM system, the total time of one PWM period is  $T_{PWM}$  which is equal to  $T_{on} + T_{off}$ . The duty cycle  $D = \frac{T_{on}}{T_{PWM}}$  and it is related to the ratio between  $V_{sin}(t)$  and  $V_{tri}(t)$ . Using the similar triangle method the D can be calculated as equation (10) below.

$$D = \frac{T_{on}}{T_{pwm}} = \frac{V_{sin}(t) + \hat{V}_{tri}}{2\hat{V}_{tri}} = \frac{1}{2} \left[ \frac{V_{sin}(t)}{\hat{V}_{tri}} + 1 \right]$$

(10)

Since the modulation signal  $V_{sin}(t) = \hat{V}_{sin} * \sin(\omega_{sin}t)$ , equation (10) can be equivalent to equation (11).

$$D = \frac{1}{2} \left[ \frac{V_{sin}(t)}{\widehat{V}_{tri}} + 1 \right] = \frac{1}{2} \left[ \frac{\widehat{V}_{sin}}{\widehat{V}_{tri}} * sin(\omega_{sin}t) + 1 \right]$$

(11)

As shown in equation (12), the ratio between  $V_{sin}(t)$  and  $\hat{V}_{tri}$  is termed  $m_i$  which is called Modulation Index in SPWM system. Then equation (13) shows the D related to the  $m_i$ .

$$m_{i} = \frac{V_{sin}(t)}{\widehat{V}_{tri}} = \frac{\widehat{V}_{sin}}{\widehat{V}_{tri}} * sin(\omega_{sin}t)$$

(12)

$$D = \frac{1}{2}[m_i + 1] \tag{13}$$

The voltage after low-pass filter of  $V_{AB}(t)$  is  $V_{inv}(t)$  and its equation is,

$$V_{inv}(t) = V_{DC} * m_i \tag{14}$$

Now, it is clear to see that the D is varies with the modulation signal  $V_{sin}(t)$ , so as the  $V_{inv}(t)$ . The voltage  $V_{inv}(t)$  is also the fundamental voltage signal of  $V_{AB}(t)$ . In conclusion, the parameter of modulation signal  $V_{sin}(t)$  decides the frequency, amplitude and phase of output voltage and current from inverter. As shown in Figure 2-7 (b), the load voltage  $V_{AB}(t)$  is a high frequency pulse wave changed between  $\pm V_{DC}$ , and the load current  $I_{AB}(t)$  is a waveform consisted of a low frequency sin wave with fundamental frequency  $f_{sin}$  plus a small ripple wave with high  $f_{pwm}$  frequency. A suitable low pass filter is required to filter high frequency part from load voltage and current, only leaving the fundamental composition. The design of filter is related to the  $f_{pwm}$ . Normally, the inductor filter is chosen to have corner frequency lower than  $f_{pwm}$ . As result, increasing switching frequency to increase  $f_{pwm}$  in PWM system is one important research now. The typical technology is the development of GaN material power switches.

## 2.3 3-level H-Bridge inverter and its *PWM* control

In the previous two sections, the basic operation of a H-Bridge inverter and its SPWM system are described. With a modulation signal  $V_{sin}(t)$  and a carrier signal  $V_{tri}(t)$ , the SPWM signal is produced to drive the power device in a 2-level H-Bridge inverter. In this section, the 3-level H-Bridge inverter and its SPWM system will be introduced. The 3-level H-Bridge inverter is a kind of multi-level power inverters. The electrical circuit structure of H-Bridge inverter in 2-level and 3-level system are same which shown in Figure 2-2 in section 2.2.1, but with different SPWM control system. Figure 2-9 shows the block diagram of SPWM system of 3-level H-Bridge power inverter.

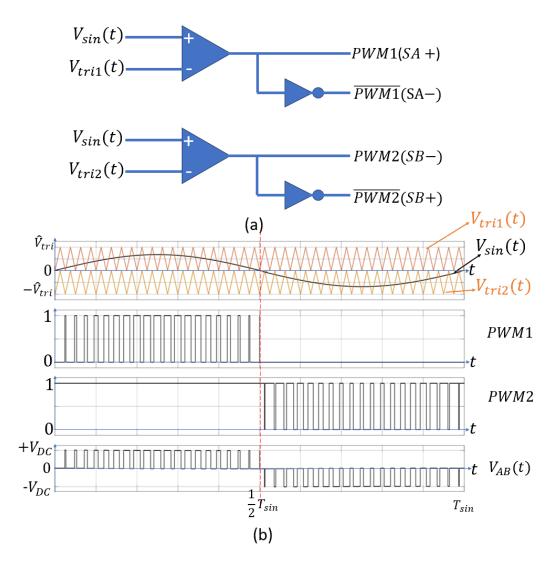

Figure 2-9: (a) Block diagram of *PWM* system in 3-level H-Bridge inverter. (b) *PWM* input and output signal and output voltage.

As shown in Figure 2-9 (b), the output voltage from H-Bridge inverter  $V_{AB}(t)$  with 3-level SPWM system is changed between  $+V_{DC}$ , 0V and  $-V_{DC}$ .

Referring to Figure 2-9 (a), SA side switches and SB side switches are controlled separately by two PWM output signals PWM1 and PWM2. As result, in 3-level SPWM system, two carrier signals are required which are  $V_{tri1}(t)$  and  $V_{tri2}(t)$ . Equation (15) and (16) show equation of  $V_{tri1}(t)$  and  $V_{tri2}(t)$ .

$$V_{tri1}(t) = \begin{cases} \frac{2\hat{V}_{tri}}{T_{pwm}} * t & 0 < t < \frac{T_{pwm}}{2} \\ \hat{V}_{tri} - \frac{2\hat{V}_{tri}}{T_{pwm}} * t & \frac{T_{pwm}}{2} < t < T_{pwm} \end{cases} \qquad T_{pwm} = \frac{1}{f_{pwm}} \qquad (15)$$

$$V_{tri2}(t) = \begin{cases} \frac{2\hat{V}_{tri}}{T_{pwm}} * t - \hat{V}_{tri} & 0 < t < \frac{T_{pwm}}{2} \\ -\frac{2\hat{V}_{tri}}{T_{pwm}} * t & \frac{T_{pwm}}{2} < t < T_{pwm} \end{cases} \qquad T_{pwm} = \frac{1}{f_{pwm}} \qquad (16)$$

$$V_{tri2}(t) = \begin{cases} \frac{2\hat{V}_{tri}}{T_{pwm}} * t - \hat{V}_{tri} & 0 < t < \frac{T_{pwm}}{2} \\ -\frac{2\hat{V}_{tri}}{T_{pwm}} * t & \frac{T_{pwm}}{2} < t < T_{pwm} \end{cases} \qquad T_{pwm} = \frac{1}{f_{pwm}}$$

(16)

Referring to Figure 2-9 (b), signal  $V_{tri1}(t)$  is a triangle waveform changes between 0V and  $+\hat{V}_{tri}$  with  $f_{pwm}$ . Signal  $V_{tri2}(t)$  is a triangle waveform changes between  $-\hat{V}_{tri}$  and 0V with the same  $f_{pwm}$ . The frequency and phase of  $V_{tri1}(t)$  and  $V_{tri2}(t)$ are same with different voltage bias, so, this type of SPWM multi-level control is named as Level-Shift SPWM control.

The output of PWM signals PWM1 and  $\overline{PWM1}$  are complementary, PWM2 and  $\overline{PWM2}$  are complementary. The power switch SA + and SA - are controlled by **PWM1** and  $\overline{PWM1}$ . The SB + and SB - are controlled by  $\overline{PWM2}$  and PWM2. As shown in Figure 2-9 (a), the production of **PWM1** signal is only related to  $V_{sin}(t)$  and  $V_{tri1}(t)$ . While the **PWM2** is only related to  $V_{sin}(t)$  and  $V_{tri2}(t)$ .

When  $V_{sin}(t) > V_{tri1}(t)$ , PWM1 = 1 (SA + is on), while  $\overline{PWM1} = 0$  (SA - is off). When  $V_{sin}(t) < V_{tri1}(t)$ , PWM1 = 0 (SA + is off), while  $\overline{PWM1} = 1$  (SA - is on). On the other hand, when  $V_{sin}(t) > V_{tri2}(t)$ , PWM2 = 1 (SB - is on), while  $\overline{PWM2} = 0$  (SB + is off). When  $V_{sin}(t) < V_{tri2}(t)$ , PWM2 = 0 (SB - is off), while  $\overline{PWM2} = 1 (SB + is on)$ .

**Table 1** shows all switching status and the output voltage  $V_{AB}$  in an ideal 3-level H-Bridge inverter.

Table 1: switching status and output voltage  $V_{AB}$  relation.

| Status | PWM1(SA+) | $\overline{PWM1}(SA-)$ | $\overline{PWM2}(SB+)$ | PWM2(SB-) | $V_{AB}(V)$ |

|--------|-----------|------------------------|------------------------|-----------|-------------|

| 1      | 0         | 1                      | 0                      | 1         | 0           |

| 2      | 1         | 0                      | 0                      | 1         | $+V_{DC}$   |

| 3      | 0         | 1                      | 1                      | 0         | $-V_{DC}$   |

| 4      | 0         | 1                      | 0                      | 1         | 0           |

Referring to Figure 2-9 (b), from time t = 0 to  $\frac{1}{2}T_{sin}$ ,  $V_{sin}(t) > 0$ .  $V_{sin}(t)$  at its positive half sin period. Since  $V_{sin}(t)$  is always larger than  $V_{tri2}(t)$  during this time, PWM2 = 1 (SB – is on) and  $\overline{PWM2} = 0$  (SB + is off). When  $V_{sin}(t) > V_{tri1}(t)$ , SA + is on, SA – is off, the voltage between leg A and leg B is  $V_{AB} = +V_{DC}$ , current flow through the SA + and SB – from leg A to B, charging the inductor in output load. The  $I_{AB}$  direction is positive ( $I_{AB} > 0$ ). When  $V_{sin}(t) < V_{tri1}(t)$ , SA + is off, SA – is on. Since both SA – and SB – are conducting, the point A and B are both conducted to the ground,  $V_{AB} = 0$ . The current from inductor keeps flows in same direction through the SA – and SB –. During the positive half period of  $V_{sin}(t)$ , the  $T_{on}$  is the time when  $V_{sin}(t) > V_{tri1}(t)$ .

From time  $t = \frac{1}{2}T_{sin}$  to  $T_{sin}$ , the  $V_{sin}(t) < 0$ ,  $V_{sin}(t)$  at its negative half sin period. During this time, the  $V_{sin}(t)$  is always lower than  $V_{tri1}(t)$  and so, SA + is off, SA – is on. When  $V_{sin}(t) < V_{tri2}(t)$ , SB + is on, SB – is off,  $V_{AB} = -V_{DC}$ , current  $I_{AB}$  through the SB + and SA – from leg B to A, charging the inductor in negative direction,  $I_{AB} < 0$ .  $V_{sin}(t) > V_{tri2}(t)$ , SB + is off, SB – is on, since SA – and SB – are both conducting,  $V_{AB} = 0V$  again. The inductive current keeps flowing in negative direction

through the SB – and SA –,  $I_{AB}$  < 0. During the negative half period of  $V_{sin}(t)$ , the  $T_{on}$  is the time when  $V_{sin}(t) > V_{tri2}(t)$ .

The main idea of 3-level **SPWM** is same to the system in the 2-level **PWM** system, by changing the duty cycle of power switch to control the duty cycle of output voltage  $V_{AB}(t)$ .

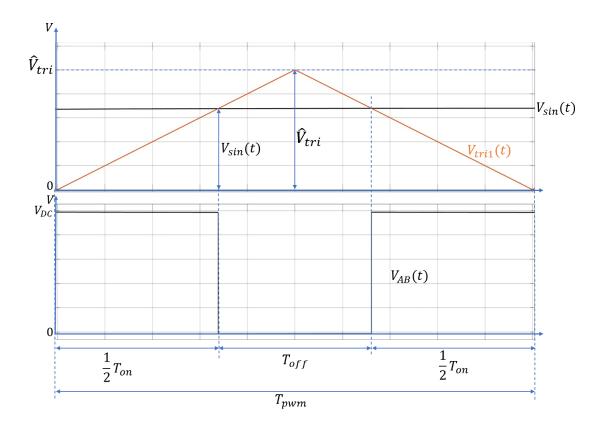

During the positive half period of  $V_{sin}(t)$ ,  $V_{AB}(t)$  only changes between 0 and  $+V_{DC}$ , and it is related to the  $V_{sin}(t)$  and  $V_{tri1}(t)$ . Figure 2-10 shows their relationship.

Figure 2-10: Relation between  $V_{sin}(t)$ ,  $V_{tri1}(t)$  and  $V_{AB}(t)$  during positive half-cycle.

Referring to Figure 2-10, by using the similar triangle equation, the duty cycle during the positive half period of  $V_{sin}(t)$  in 3-level is,

$$D = \frac{T_{on}}{T_{pwm}} = \frac{V_{sin}(t)}{\widehat{V}_{tri}} = \frac{\widehat{V}_{sin}}{\widehat{V}_{tri}} * \sin(\omega_{sin}t) = m_i$$

$$45$$

(17)

In positive half period of  $V_{sin}(t)$ ,  $1 \ge \sin(\omega_{sin}t) \ge 0$ . The voltage after low-pass filter is,

$$V_{inv}(t) = V_{DC} * m_i \tag{18}$$

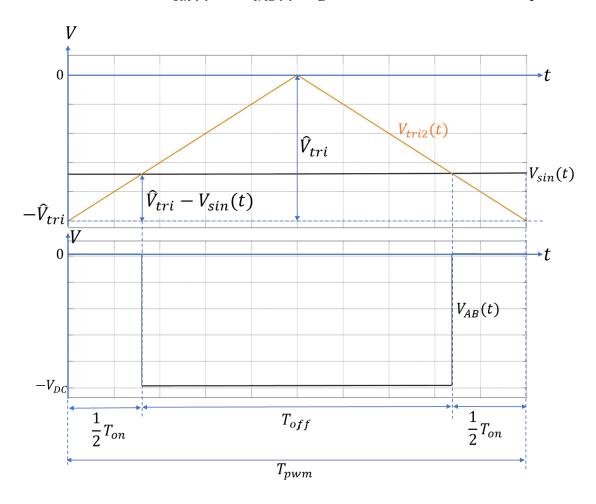

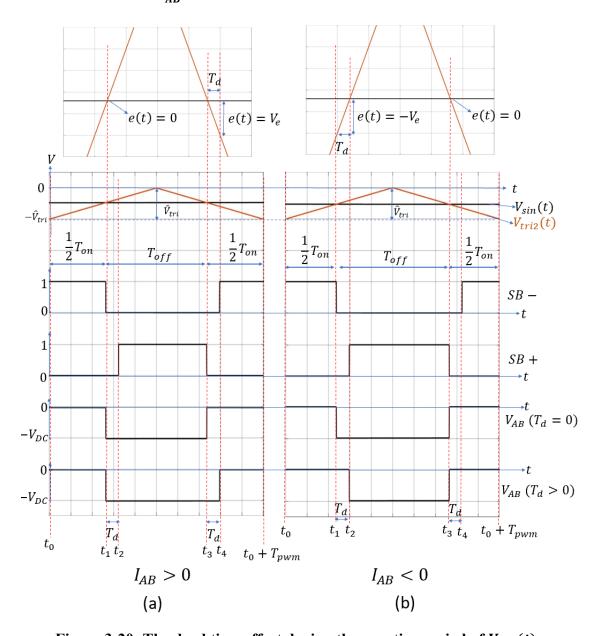

During the negative half period of  $V_{sin}(t)$ ,  $V_{AB}(t)$  only changes between 0 and  $-V_{DC}$ , and it is related to the  $V_{sin}(t)$  and  $V_{tri2}(t)$ . Figure 2-11 shows their relationship.

Figure 2-11: Relation between  $V_{sin}(t), V_{tri2}(t)$  and  $V_{AB}(t)$  during negative half cycle

Referring to Figure 2-11, the duty cycle **D** is equal to

$$D = \frac{T_{on}}{T_{pwm}} = \frac{V_{sin}(t) - (-\hat{V}_{tri})}{\hat{V}_{tri}} = 1 + m_i$$

(19)

During the negative half period of  $V_{sin}(t)$ ,  $-1 \le \sin(\omega_{sin}t) \le 0$ . The equation of fundamental voltage is

$$V_{inv}(t) = V_{DC} * m_i \tag{20}$$

It is clear to see that, the  $V_{inv}(t)$  equation in a whole  $V_{sin}(t)$  period is same.

In a 2-level H-Bridge inverter, with only one output SPWM signal PWM1, all power switches in leg A and leg B works under high switching frequency in a whole period of  $V_{sin}(t)$ , which increase power loss on every switches. With 3-level PWM system, the power switches on each side of H-Bridge inverter (SA or SB) will only work under high switching frequency in a half period of  $V_{sin}(t)$ . SA side power switches work in high frequency at positive period of  $V_{sin}(t)$  while SB side power switches work in high frequency at negative period. As result, even for the same high switching frequency, comparing to the 2-level H-Bridge inverter, the power loss on each power switch in a H-Bridge inverter during the switching is decreased. On the other hand, with the increase of numbers of carrier signal in PWM system, PWM system will be more complex.

# 2.4 Dead Time Effect and Dead Time Compensation.

The descriptions provided in the previous section assumed the switching devices exhibited ideal switch characteristics and could turn-on and turn-off instantaneously.

Real devices take a finite time to turn-on and turn-off and, therefore, the behavior of the circuit is more complex.

In a two-level or three-level H-Bridge inverter, the two switches on same leg (SA + & SA – or SB + & SB –) must not be turned on at same time to avoid short circuit occurring. The high currents that flow during a short circuit may break the power switches with may even lead to the destruction of whole circuit system. In the previous section, all power switches in H-Bridge work under ideal situation, which they can turn on and off instantly. In actual work, any power switch requires a certain time for turning on or off. In order to ensure two switches in same leg are not on at same time, a certain delay time called dead time ( $T_d$ ) is added between the turning off of one device (i.e. SA –).

Although dead time is used in H-Bridge to avoid short-circuit events, it will inevitably cause distortion since the body diode will be needed to conduct the inductive load current. This distortion becomes significant during the zero-crossing points of the reference signal. In addition, it will cause more energy loss in H-Bridge inverter [9][14]. In order to decrease the dead time effect, the dead time compensation (DTC) is required.

There are two main methods for decreasing the dead time effect, Dead Time Compensation (DTC) and Dead Time Elimination (DTE). The purpose of DTC [15]-[27] is compensating the output voltage, current reduction and distortion caused by dead time. The dead time still exists, but by producing the right duty cycle of output voltage  $V_{AB}$ , the voltage and current reduction can be compensated. So as the distortion. Most

DTC techniques rely on knowing the polarity of the inverter current and therefore require accurate current sensor especially for reading high switching frequency component. DTE usually detects the voltage on the freewheeling diode parallel to power switches instead of detecting current polarity [29]-[34]. As result, the accurate current detector is not required in DTE. On the other hand, since every voltage on diode in a power inverter is required to be detected, multiple detectors are required in DTE technologies. Most DTC and DTE calculate the error voltage from output average voltage for compensation, and most of them are used in inverter system in three phase open-loop motor control. But still there are some DTC and DTE technologies are used in close-loop power inverter system [34]-[36], especially in the Neutral-Point-Clamp Converter (NPC) system. In close-loop power inverter system, the DTC and DTE are usually achieved by adding extra calculation into the *PLL* or current control calculation for decreasing distortion.

In this research, the DTC will be used for compensating the dead time effects in the single-phase grid connected H-Bridge power inverter without influence the close-loop control calculation progress. The proposed dead-time compensation techniques used in 2-level and 3-level H-Bridge inverter are described in detail in Chapter 3. Many DTC technologies require high accuracy current detectors for taking all current data, but these current detectors are expensive. On the other hand, some current detects technologies take filtered current data and then create simulated inverter current in microcontroller for DTC, but it may cause delay during data transfer and progress and inaccurate current polarity data. In Chapter 4 in this thesis, a cheap and easily design

current detector and current polarity detector designed for DTC system is introduced. It directly produces current polarity information of inverter side current from H-Bridge which can detect high frequency current zero-crossing information, avoiding delay of data transfer as well.

#### 2.5 *LCL* filter

LCL filter is a stable and useful low-pass filter used inside H-bridge inverter system especially for grid-connected H-Bridge power inverter, even in the PV energy system [37]-[39]. In addition, a suitable LCL filter is important in the analysis of dead time effect and DTC. The LCL filter included in inductive load maintains the current flows and voltage output from H-Bridge inverter. During dead time, all power switches are turned off, only the energy stored in the inductive load acting as a current source maintaining output voltage and current flow in H-Bridge inverter. A suitable LCL filter is required not only for filter, but also for supplying enough energy to maintain current flow and voltage during dead time in H-Bridge especially during current zero-crossing time. The DTC technology in this thesis can produce ideal output voltage from inverter, but the  $T_d$  still exists. As result, if LCL filter is not suitable, output current from H-Bridge inverter still contains unexpected distortion especially during current zero-crossing even DTC is already operated.

Comparing to L and LC low pass filter, *LCL* filter is third-order filter, after the cut-off frequency, the slop of dB attenuation can reach to -60dB/dec. As result, it can provide

low current ripple and good harmonic attenuation with smaller size of inductor [40][43].

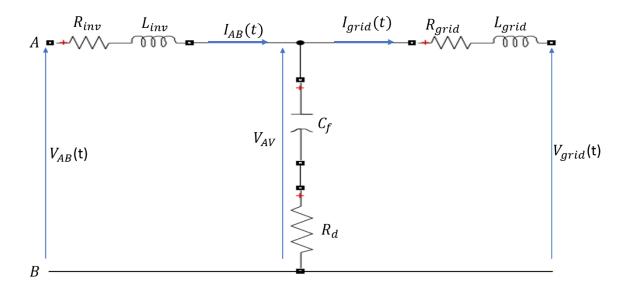

LCL filter in H-Bridge inverter is used to filter high frequency component in PWM output voltage and current from H-Bridge inverter. Figure 2-12 shows a typical LCL filter with damping resistor system.

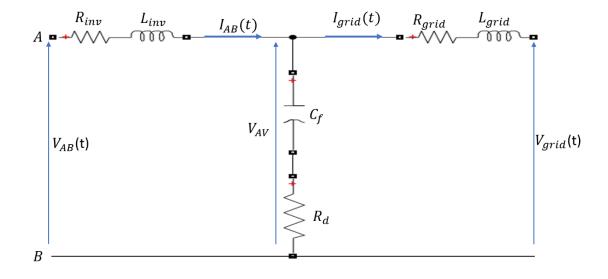

Figure 2-12: LCL filter with damping resistor.

As shown in Figure 2-12, the input of LCL filter is  $V_{AB}(t)$  from power inverter, while the output from LCL filter is connected to the grid system which is equal to  $V_{grid}(t)$ . The design of LCL filter can be separated into four parts, the design of inverter side inductor  $L_{inv}$ , capacitor  $C_f$ , grid side inductor  $L_{grid}$  and damping resistor  $R_d$ . The methods for calculating LCL parameter are always related to power switching frequency, modulation index, the max ripple of current, maximum output power and maximum voltage drop on two inductors [44]-[49].

The  $L_{inv}$  is designed for filtering the highest harmonic component in  $V_{AB}(t)$  which occurs at switching frequency  $f_{tri}$ . After the filtering of  $L_{inv}$ , the filtered voltage  $V_{AV}$

is directly equal to the fundamental voltage  $V_{inv}(t)$ . In addition, it is mainly used to limit the maximum ripple current in inverter side current  $I_{AB}(t)$ , which is usually from 5% to 10% [50]. In Chapter 4, equation of calculating  $L_{inv}$  according to the ripple current, duty cycle and  $V_{AB}(t)$  will be presented.

The design of capacitor  $C_f$  is related to the power factor. In order to maintain certain power factor, the  $C_f$  is used to absorb the reactive power from total rated power from grid and the reactive power should be lower than 10% of rated power [48].

In one factor, the second inductor  $L_{grid}$  can further attenuate the harmonic after the  $L_{inv}$  and  $C_f$ . The  $L_{grid}$  can increase inverter robustness under weak and large variation grid system [51]. In LCL filter, the total inductance  $L_T = L_{inv} + L_{grid}$  should be as small as possible for decreasing the voltage drop on the  $L_T$ . Under low fundamental frequency, the  $C_f$  can seem like an open circuit, only  $L_{inv}$  and  $L_{grid}$  need to be considered. The voltage drops on  $L_T$  should be lower than 10% of grid voltage. The  $L_{inv}$  has already calculated at first part, after getting the  $L_T$ , the  $L_{grid}$  can be calculated easily.

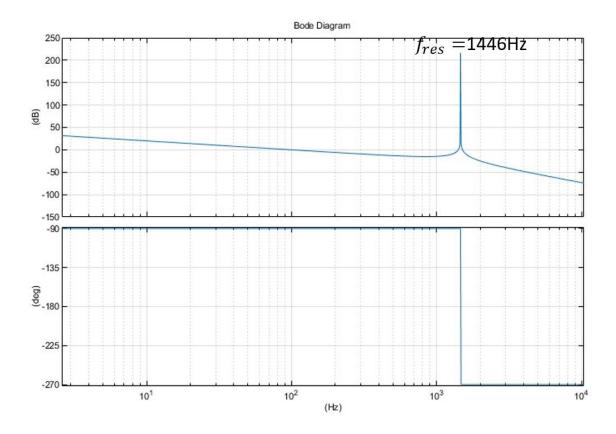

After  $L_{inv}$ ,  $L_{grid}$  and  $C_f$  is calculated, the resonance frequency  $f_{res}$  of LCL filter can be calculated as well. It is important to ensure that the  $f_{res}$  is lower than half of the  $f_{tri}$  and high than 10 times of  $f_{sin}$  [48][50]. Frequency  $f_{res}$  can be used to check whether the design of inductors and capacitor are suitable for the inverter and grid system.

One drawback of *LCL* filter is its instability caused by the resonance frequency itself [51]. A damping system is used for solving this problem. There are two main types of damping system, passive damping and active damping. In passive damping system, the

passive damping element is added into LCL filter to decrease the resonance peak of the system. In general, passive damping element includes extra resistor or capacitor [49]. The advantage of passive damping is that it does not requires any change on the control strategy. On the contrary, the extra damping element will cause more power loss in filter. Active damping technology focusing on adding extra close-loop system into control strategy to decrease influence from  $f_{res}$  [49][53]. The advantage of this method is that it does not require extra damping component, which avoid extra power loss. But the design of control strategy will be complex. In this research, the passive damping technology will be used, and it is presented in section 4.11ater.

The detail of calculation of parameter in **LCL** filter is presented in a later chapter.

#### 2.6 Grid connected power inverter system.