# Design, Optimisation, and Analysis of Multi-Level SiC Converters

By

#### Zixiao Li

A thesis submitted in fulfilment of the requirements for the degree of

Doctor of Philosophy

Department of Electronic and Electrical Engineering

Faulty of Engineering

The University of Sheffield

November 2023

#### **Abstract**

Silicon Carbide (SiC) devices, known for their thermal stability, high efficiency, and excellent high-temperature performance, have become vital in power electronics after decades of development. These devices offer significant potential for higher switching speeds, lower energy losses, and enhanced system performance. Multi-level converters (MLCs) are especially valued for their capability to increase output voltage levels, minimise power losses, reduce harmonic distortion, and decrease voltage stress on switching devices. This thesis explores the design, application, modelling, and analysis of MLC based on SiC power devices.

This thesis firstly focuses on analysing the performance of three-level topologies (NPC, ANPC, T-type) under varying conditions using precise device parameter models. Key factors like voltage stress and power losses are evaluated, with particular attention to the suitability of SiC MOSFETs in high-voltage aviation applications, providing recommendations for topology selection for different applications. It also highlights a fully integrated three-level NPC module optimised for specific applications, focusing on electrical, electromagnetic, and thermal performance. Unlike combined several two-level modules, it minimises parasitic inductance and uses a novel baseplate for better efficiency and thermal management in aerospace. Using an equivalent heat transfer coefficient instead of CFD simulations quickly estimates power device temperatures, reducing computational time and cost. A linear estimation method determines output power under varying airflow rates and assesses scalability. For the three-level NPC topology, a two-port small-signal model is established. Sparameters are measured using a VNA and converted to Z-parameters for parasitic inductance extraction, with validation showing an error of less than 10%. The extracted parameters are applied to DPT simulation and platform testing, confirming their accuracy.

## Acknowledgement

Throughout my PhD research journey, I have been fortunate to receive support and guidance from many outstanding people whose help has been crucial to my academic growth and personal development. I would like to express my deepest gratitude.

First and foremost, I would like to thank my supervisor, Prof. Antonio Griffo, for his invaluable guidance and support during my studies. His wisdom, patience and motivation have been my driving force. I am very grateful to him for his guidance in writing my thesis. I am honoured to be his PhD student. I would like to thank my second supervisor, Prof. Jiabin Wang, for providing me with knowledge and advice. I would also like to express my sincere gratitude to Dr Shangjian Dai for his help in my experiments, and the challenges and successes we shared together will be my precious memories forever.

I would like to thank my parents, especially for their support and encouragement in completing my studies. Their love, encouragement and sacrifices have been a strong shield for me to pursue my academic dreams.

I would also like to thank all the staff of the Department of Electrical and Electronic Engineering at the University of Sheffield for their support and dedication. Special thanks go to my colleagues and my friends for their help and support.

I would like to express my sincere gratitude to all those who have supported me. This thesis is the result of our joint efforts.

# **Table of Acronyms and Symbols**

## Acronyms

| Acronym | Description                       |  |  |  |

|---------|-----------------------------------|--|--|--|

| AC      | Alternating current               |  |  |  |

| ANPC    | Active neutral point clamped      |  |  |  |

| ВЈТ     | Bipolar transistor                |  |  |  |

| CFD     | Computational fluid dynamics      |  |  |  |

| СНВ     | Cascaded H-bridge                 |  |  |  |

| CSC     | Current source converter          |  |  |  |

| CTE     | Coefficient of thermal expansion  |  |  |  |

| DC      | Direct current                    |  |  |  |

| DCB     | Direct copper bonded              |  |  |  |

| DPT     | Double pulse test                 |  |  |  |

| DUT     | Device under test                 |  |  |  |

| EMI     | Electromagnetic interference      |  |  |  |

| EV      | Electric vehicle                  |  |  |  |

| FC      | flying capacitor                  |  |  |  |

| FEM     | Finite element method             |  |  |  |

| FET     | Field effect transistor           |  |  |  |

| FRD     | Fast recovery diode               |  |  |  |

| GaN     | Gallium Nitride                   |  |  |  |

| HEV     | Hybrid electric vehicle           |  |  |  |

| IGBT    | Insulated gate bipolar transistor |  |  |  |

|         | I                                 |  |  |  |

MLC Multi-level converter

MOR Model order reduction

MOSFET Metal-oxide-semiconductor filed-effect transistor

NPC Neutral point clamped

NTC Negative temperature coefficient

PCB Printed circuit board

PCM Phase change material

PEEC Partial element equivalent circuit

PM Power module

PMSM Permanent magnet synchronous machine

PWM Pulse width modulation

RMS Root-mean-square

RF Radio frequency

SBD Schottky barrier diode

Si Silicon

SiC Silicon carbide

SVPWM Space vector pulse width modulation

TDR Time-domain reflectometry

TIM Thermal interface material

TNPC T-type neutral point clamped

THD Total harmonic distortion

UPS Uninterruptible power supply

VNA Vector network analyzer

VSC Voltage source converter

WBG Wide bandgap

# **Symbols**

| Symbol             | Description                                    |  |  |  |

|--------------------|------------------------------------------------|--|--|--|

| $C_{ds}$           | Drain-source capacitance                       |  |  |  |

| $\mathcal{C}_{gd}$ | Gate-drain capacitance                         |  |  |  |

| $\mathcal{C}_{gs}$ | Gate-source capacitance                        |  |  |  |

| $C_{iss}$          | Input capacitance                              |  |  |  |

| $C_{oss}$          | Output capacitance                             |  |  |  |

| $E_B$              | Breakdown field                                |  |  |  |

| $E_g$              | Bandgap energy                                 |  |  |  |

| $E_{off}$          | Turn-off energy                                |  |  |  |

| $E_{on}$           | Turn-on energy                                 |  |  |  |

| $E_{sw}$           | Switching energy                               |  |  |  |

| $f_{load}$         | Load frequency                                 |  |  |  |

| $f_{res}$          | Resonant frequency                             |  |  |  |

| $f_{sw}$           | Switching frequency                            |  |  |  |

| $i_{ds}$           | Drain-source current                           |  |  |  |

| $L_{loop}$         | Loop inductace                                 |  |  |  |

| m                  | Modulation index                               |  |  |  |

| M                  | Switch angle number in the first quarter cycle |  |  |  |

| $P_{cond}$         | Conduction loss                                |  |  |  |

| $P_{off}$          | Turn-off power                                 |  |  |  |

| $P_{on}$           | Turn-on power                                  |  |  |  |

| $P_{on}$           | Turn-on power                                  |  |  |  |

| $P_{sw}$      | Switching loss                           |  |  |  |  |

|---------------|------------------------------------------|--|--|--|--|

| $R_g$         | Gate resistance                          |  |  |  |  |

| $R_{ds(on)}$  | drain-source on resistance               |  |  |  |  |

| $R_{ m thjc}$ | Thermal resistance from junction to case |  |  |  |  |

| $T_{j}$       | Junction temperature                     |  |  |  |  |

| $V_{BR}$      | Breakdown voltage                        |  |  |  |  |

| $V_{ds}$      | Drain-source voltage                     |  |  |  |  |

| $V_{ds(on)}$  | On-state voltage                         |  |  |  |  |

| $V_{gs}$      | Grain-source voltage                     |  |  |  |  |

| $V_{th}$      | Threshold voltage                        |  |  |  |  |

| $v_{sat}$     | Saturation drift velocity                |  |  |  |  |

| $V_{dc}$      | DC-link voltage                          |  |  |  |  |

| $\mu_n$       | Electron mobility                        |  |  |  |  |

| $\mu_p$       | Hole mobility                            |  |  |  |  |

| λ             | Thermal conductivity                     |  |  |  |  |

| $arepsilon_r$ | Relative permittivity                    |  |  |  |  |

| *             | Reference quantity                       |  |  |  |  |

# **Table of Contents**

| Abstract                                                                        | II         |

|---------------------------------------------------------------------------------|------------|

| Acknowledgement                                                                 | III        |

| Table of Acronyms and Symbols                                                   | IV         |

| Table of Contents                                                               | VIII       |

| CHAPTER 1 General Introduction                                                  | 11         |

| 1.1 Background and Motivation                                                   | 11         |

| 1.2 Power Electronics System                                                    | 15         |

| 1.2.1 WBG Power Semiconductors                                                  | 15         |

| 1.2.2 Power Converters Using WBG Devices                                        | 19         |

| 1.2.3 Power Electronics Packaging and Power Module                              | 23         |

| 1.3 Overview of Non-ideal Effects of Power Electronics                          | 26         |

| 1.3.1 Power Losses in Converters                                                | 28         |

| 1.3.2 Parasitic Parameters and Reduction                                        | 30         |

| 1.3.3 Thermal Management                                                        | 36         |

| 1.4 Scope and Overview of Research                                              | 40         |

| 1.4.1 Aim and Objectives                                                        | 40         |

| 1.4.2 Main Contributions                                                        | 43         |

| 1.4.3 Organization of Thesis                                                    | 45         |

| 1.5 List of Publications                                                        | 47         |

| CHAPTER 2 Comparative Analysis of Three-Level Converter for an                  | n Aircraft |

| Starter-Generator 48                                                            |            |

| 2.1 Introduction                                                                | 48         |

| 2.2 Advantages, Disadvantages, and Characteristics of MLCs                      | 49         |

| 2.3 Three-Level Converter Performance Analysis                                  | 56         |

| 2.3.1 Device Selection in Three-level Converters for Aircraft Starter-Generator | r56        |

| 2.3.2 Performance Comparison of Converters with Different Topologies            | 64         |

| 2.4 Canalusions                                                                 | 71         |

| CHAPTER 3 | Three Level NPC SiC Power Module Design and Considerations |

|-----------|------------------------------------------------------------|

|           | 72                                                         |

| 3.1 Introduction                                           |                 |

|------------------------------------------------------------|-----------------|

| 3.2 Evaluation and Impact of Power Losses in Power Module  | s73             |

| 3.3 Loop Parasitic Inductance Effects and Impact of NPC To | pology 80       |

| 3.4 Power Module Design and Layout Optimisation            | 86              |

| 3.4.1 Selection of Power Semiconductor Devices             | 87              |

| 3.4.2 Power Module Layout Optimisation                     | 88              |

| 3.4.3 Power Module Construction                            | 93              |

| 3.5 Thermal Considerations                                 | 94              |

| 3.5.1 Steady State Thermal Analysis                        | 95              |

| 3.5.2 Transient Thermal Analysis                           | 100             |

| 3.5.3 CFD Thermal Analysis                                 | 102             |

| 3.5.4 Maximum Achievable Power with Forced Air Cooling     | 106             |

| 3.6 Conclusions                                            | 107             |

| CHAPTER 4 Comprehensive Analysis of Three Phase Con        | verter: Design. |

| Construction, Measurement, and Electrical Performance      | J               |

| ·                                                          |                 |

| 4.1 Introduction                                           | 110             |

| 4.2 From Power Module to Three Phase Converter             | 111             |

| 4.2.1 Converter Busbar Design                              | 111             |

| 4.2.2 Three-Level SiC Converter Construction               | 115             |

| 4.3 Parasitic Inductance Extraction of Three-Level NPC Pow | er Module 118   |

| 4.4 Experiment Verifications                               | 126             |

| 4.4.1 Parasitic inductance extraction                      | 126             |

| 4.4.2 Double-Pulse Test of Three-Level Power Module        | 130             |

| 4.5 Conclusions                                            | 141             |

| CHAPTER 5 Conclusions and Future Work                      | 142             |

| 5.1 Conclusion                                             | 142             |

|                                                            |                 |

| 5.2 Future Work                                            | 144             |

| APPENDIX A Three Level PCB-Based Embedded Converter        | Using SiC Bare  |

| Die                                                        | 147             |

| A.1 Introduction                                           | 147             |

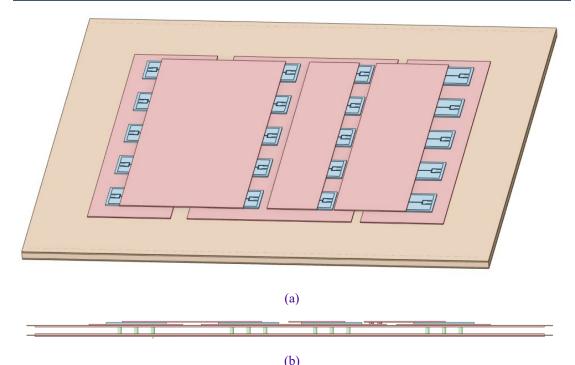

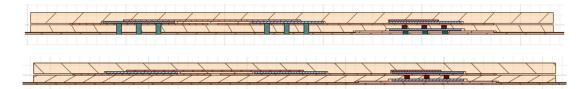

| A.2 PCB-Based Converter Model Development            | 148               |

|------------------------------------------------------|-------------------|

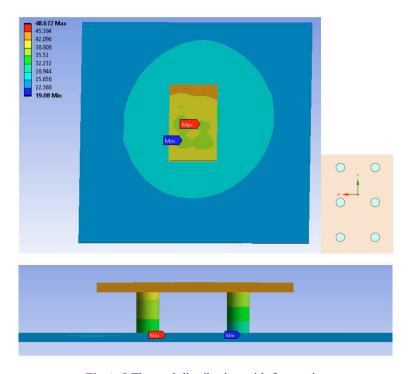

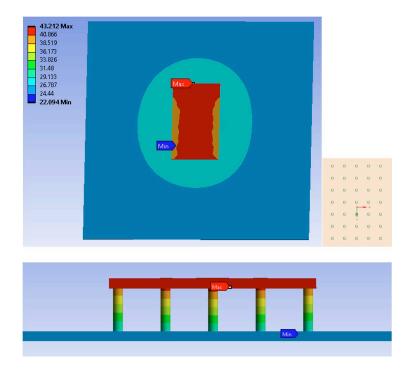

| A.3 PCB-Based Converter Thermal Considerations       | 152               |

| A.4 Summary                                          | 159               |

| APPENDIX B Three-level SiC Converter Power Losses at | t 125°C and 175°C |

| Junction Temperature                                 | 161               |

| References                                           | 164               |

| List of Figures                                      | 178               |

| List of Tables                                       | 182               |

#### **CHAPTER 1**

#### **General Introduction**

## 1.1 Background and Motivation

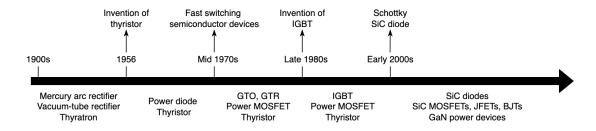

After a hundred years of development, power electronic technology has been widely used in various electrical conversion systems. The history of power electronics can be traced back to the early 20th century, with a primary focus on power conversion and control, Fig.1-1 shows the development milestone of power electronics technology. Long-term advances in power semiconductor devices have enabled power electronic systems with higher switching speeds, wider temperature ranges, higher achievable power, higher efficiency, and reliability. In the future, the technology should be developed towards high efficiency, low cost, and low consumption.

Fig.1-1 Development milestone of Power Electronics technology [1]

Early power electronics relied heavily on discrete devices that were large and limited in efficiency and power density. As these devices evolved, particularly with the advent of bipolar transistors (BJTs) and field effect transistors (FETs), they allowed for more efficient and controllable AC to DC, DC to AC, and DC to DC conversions. In order to integrate these power devices more efficiently while ensuring reliability and efficiency, manufacturers have integrated these devices with diodes, passive components and driver circuits into a single module, and this integration has led to the creation of the power module.

In addition, at the end of the last century, advances in substrate materials and packaging technology, as well as the excellent properties of SiC and Gallium Nitride (GaN), have made the power module an even more desirable solution in the field of power electronic conversion. In 1975, SEMIKRON introduced the first power module to the market.

Overall, the history of power electronics has been a progression from single power device to integrated solutions, and power modules have played a key role in this process, helping designers more easily meet changing requirements.

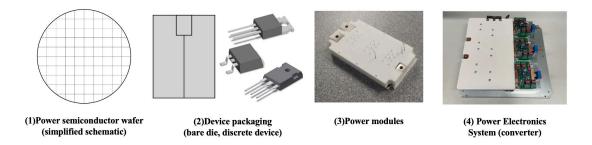

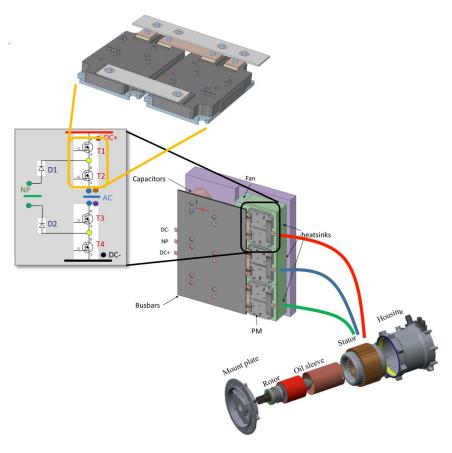

Fig.1-2 shows the path from a semiconductor wafer to a converter that can drive a load. Completing this transition involves multiple steps and levels of technology. The following is a general process for moving from a power device to a full-featured converter:

Fig.1-2 From power semiconductors to converter

- Power semiconductor devices: Wafers are processed through several steps including doping, ion implantation and etching to form the required basic power semiconductor devices.

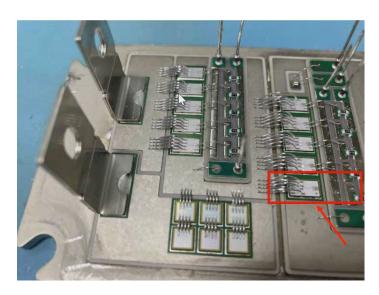

- 2. Device packaging: To facilitate practical use, semiconductor devices need to be properly packaged after fabrication. They are usually placed in a protective enclosure, which provides physical support, electrical connections, and thermal management. In addition to this, unpackaged semiconductor bare dies without any leads or enclosures can also be integrated directly into power modules, which saves a lot of space and allows for efficient heat dissipation due to direct contact with the substrate. However, it requires more complex circuit connection and special manufacturing techniques which may result in defects and device failures. Fig.1-3 shows an example of a failed weld.

Fig.1-3 Gate failure in one MOSFET

- 3. Power module integration: Multiple power devices are often combined into power modules for higher power applications. These modules may incorporate cooling, gate drive circuitry and protection. Assembly and packaging are critical here as they affect the thermal performance, reliability, and overall efficiency of the module.

- 4. Converter design and assembly: To form a converter, power modules need to be integrated into the system. This includes: designing the circuit topology (e.g., half-bridge, full-bridge, or multi-level). Designing control circuits to control the switching action of the power module. Integrating the DC input power supply, DC-link capacitors, busbars, and protection circuits. Selecting the appropriate heat sink and housing for the converter to achieve higher power levels and provide physical protection.

Finally, converters can be integrated into larger systems. For example, power supplies for electronic devices, motor drives, inverters for solar panels, or any other application. This process demonstrates the multidisciplinary character of power electronics, incorporating materials science, semiconductor processing, electrical engineering, and thermal management.

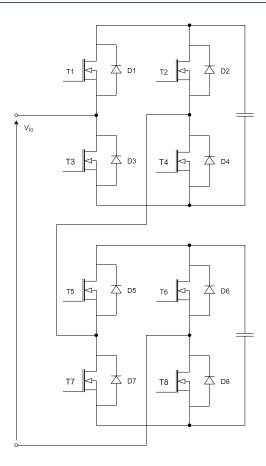

Current research heavily focuses on Si IGBT modules and SiC MOSFET modules for two-level and three-level topologies. This thesis fucuses on the development of three-level power modules and converters. To achieve three-level topologies, many industrial applications use multiple two-level modules connected electrically. The advantage of this approach is that there is no need to consider the special internal

structure of the modules, and the system capacity can be increased by connecting multiple modules in parallel. However, it is not possible to reduce the parasitic parameters by changing the internal structure of the modules, and the converter size may be larger, with an increase in system losses and a higher cost due to the need for multiple modules.

Another way to implement a three-level topology is to use a three-level module directly, which, as a comparison, is usually able to optimise the output waveform using a simpler control strategy, and generally has better efficiency and lower losses, but increasing the system capacity may increase the cost.

In conclusion, power modules are more than simple integration of components, they also involve thermal management, electromagnetic compatibility, as well as driving and protection techniques. This thesis will analyse these aspects in a detailed study. The advent of power modules provides a simplified approach to enable efficient power conversion and control in a system more easily.

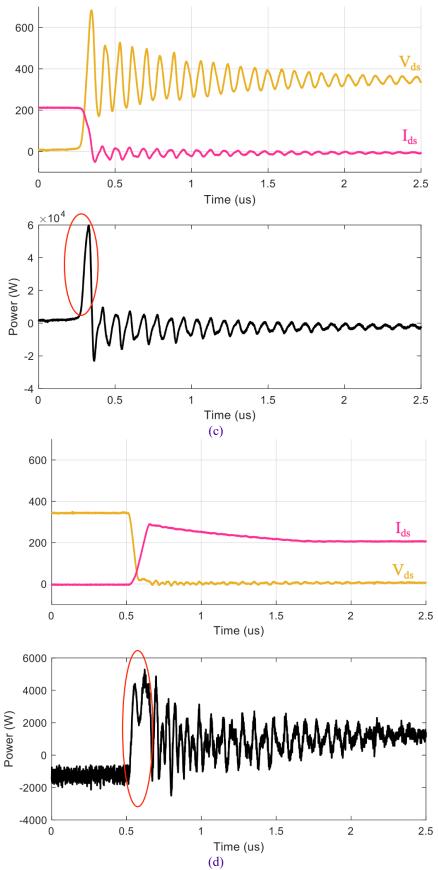

Recently, as an alternative to the use of power modules in power converters, printed circuit boards (PCB) embedded packaging technology has also been proposed to integrate power devices. The biggest advantage is to facilitate system integration. With the gradual maturity of the PCB process, the devices embedded in the printed circuit board, the system volume can be further reduced, and reliability can be further improved compared to traditional PCB.

Whichever of the above technologies, it is vital that they are investigated not only for technological and industrial progress, but also for meeting social and economic needs, achieving sustainable development, and protecting the environment.

To meet these trends, the general active research areas in power electronic systems are:

- 1. Use of new semiconductor materials (e.g. SiC/GaN)

- 2. New chip technologies: smaller structures, higher operating temperatures and current densities, higher stability.

- 3. Novel packaging technologies: optimised internal electrical connections, improved heat dissipation and reduced material costs.

- Integration and modularity, which helps to reduce size and weight as well as improve system reliability and stability. Integration and modularity also help to simplify system design and reduce costs, for example by adding in a single package control, protection, and monitoring functions.

- High frequency and high-power density packaging requiring low resistance and low parasitic inductance design.

## 1.2 Power Electronics System

Power electronic systems are a fundamental part of modern technology. They play an indispensable role in the efficient and flexible conversion and control of electricity. While the end of the previous section provided a variety of future directions for power electronics, they also provided a variety of potential challenges. This section describes the basic components and technical challenges of power electronic systems.

#### 1.2.1 WBG Power Semiconductors

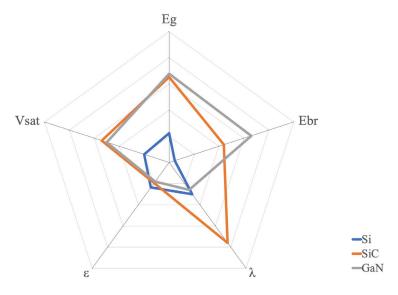

Previous studies have shown that the performance of Si power switching devices has reached its theoretical limits, which is determined by the fundamental material parameters [2] (e.g., the critical field for avalanche breakdown). Therefore, extensive research on new materials has been conducted in the past few decades, and the development focus on wide-bandgap (WBG) semiconductors, including SiC and GaN. They are attractive for advanced power devices due to their superior physical properties, these wide-bandgap materials can provide better performance [3]-[7]. SiC has many homogeneous polytypes with similar crystal structures, such as 3C-SiC, 6H-SiC, and 4H-SiC. In the field of power electronics, 4H-SiC is usually chosen to manufacture power devices. Table 1-1 summarises the comparison of the physical properties of semiconductor materials [8].

Table 1-1 Comparison of characteristics of different semiconductor materials

| Properties                                                          | Si   | 4H-SiC | GaN  |

|---------------------------------------------------------------------|------|--------|------|

| Bandgap Energy: Eg (eV)                                             |      | 3.26   | 3.39 |

| Electron Mobility: μ <sub>n</sub> (cm <sup>2</sup> /Vs)             | 1400 | 950    | 1500 |

| Hole Mobility: $\mu_p$ (cm <sup>2</sup> /Vs)                        | 600  | 100    | 200  |

| Saturation Drift Velocity: v <sub>sat</sub> (cm/s) ×10 <sup>7</sup> |      | 2.7    | 2.5  |

| Breakdown Field: E <sub>br</sub> (MV/cm)                            |      | 2.2    | 3.3  |

| Thermal Conductivity: λ (W/cmK)                                     |      | 3.8    | 1.3  |

| Relative Permittivity ε                                             |      | 9.7    | 9.0  |

As can be seen from Table 1-1, SiC has ten times the dielectric breakdown field strength compared with Si, this means that SiC can withstand higher breakdown voltage, at the same breakdown voltage, SiC devices can be made to have much thinner drift layer with higher doping concentration. The resistance of high-voltage semiconductor devices is mainly determined by the width of the drift layer [9]. Under the same breakdown voltage, compared with the Si device, the SiC device can reduce the specific on-resistance in the drift region by 300 times [10]. The currently used Si MOSFETs support a maximum breakdown voltage of around 900V, while SiC MOSFETs can support a breakdown voltage of up to 1700V.

Fig.1-4 shows a comparison of three semiconductor materials, the bandgap determines the temperature limit for device operation, the breakdown field determines the stability and reliability of semiconductor devices at high voltages, a high breakdown electric field means higher voltage withstand capability [11]. High voltage operation means the possibility of less required devices. Thermal conductivity determines heat dissipation characteristic of semiconductor device, high thermal conductivity helps to reduce the operating temperature of the device and prolongs the life of the device, means less cooling is required. Saturation velocity affects the device's carrier transported switching speed, WBG semiconductor materials have higher saturation drift velocity and are therefore more suitable for high frequency and high-power applications. In conclusion, SiC MOSFETs offer several advantages over Si IGBTs: fast switching speed, high operating temperature, high breakdown voltage and linear current-voltage (I-V) characteristics [12]-[19].

Fig.1-4 Physical parameters of different semiconductor materials

Overall, SiC can withstand higher voltages and temperatures, can operate at higher frequencies, switching faster, resulting in lower power losses and improved overall energy efficiency. Despite the above device advantages, SiC MOSFETs are not perfect and there are still some challenges that prevent SiC MOSFETs from entering mass market applications, and the disadvantages of SiC devices are listed below:

- 1. High manufacturing cost: The fabrication process for SiC devices is more complex compared to Si devices, which results in higher manufacturing costs for SiC-based products. At the device level, SiC MOSFETs still face challenges of gate oxide reliability and threshold voltage (Vth) instability [20]-[22]. However, costs are expected to decrease as the technology matures.

- 2. Material quality and defects: Some defective problems are still bothering SiC substrates and epitaxy [23], which can further affect device performance and production. Achieving high-quality, defect-free SiC substrates is challenging and increases production costs.

- 1. Limited market supply: Due to the relatively short time to commercialisation and low production yields, the market share of SiC devices has not yet reached the level of Si devices. This may result in a limited supply of higher priced SiC devices [24].

- 2. Relatively low current handling: Despite their advantages in voltage handling and thermal performance, SiC devices typically have lower current handling compared to Si devices, However, the current capacity of a single SiC device may be lower than that of a corresponding Si device due to the higher material and fabrication costs of SiC, resulting in SiC device designs that may favour high voltage over high current applications under the same cost and size constraints. This can limit their use in some high-current applications. While higher current handling can be achieved by paralleling multiple devices, current imbalance between parallel SiC MOSFETs is also a real problem in high-current applications, where unbalanced current distribution can lead to thermal imbalance and reduced reliability [25].

- 3. Complex gate drive circuits: SiC devices require dedicated gate drive circuits due to their unique electrical characteristics. The faster switching speeds of

SiC devices result in a high sensitivity to circuit parasitics [26]-[27], and therefore require precise gate control and the design of more appropriate power loop circuit layouts, which can be more complex to design and implement than Si devices.

Despite these limitations, the strengths of SiC described previously make it a semiconductor material with great potential for the future. Current research and development efforts are focused on addressing these weaknesses and further optimising SiC technology to release its full potential.

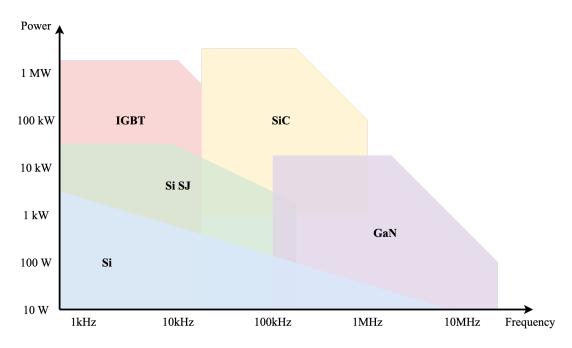

SiC MOSFETs combine the advantages of SiC materials and MOSFETs devices, they can withstand high breakdown voltage, have lower on-resistance, and fast switching. When turned on, since SiC MOSFETs have linear I-V characteristics [28], they have low conduction losses over a wide current range. MOSFETs do not exhibit the tail current that IGBTs do during turn-off, which requires additional time for the current to decay in IGBTs. This feature allows for sharper and quicker turn-off in MOSFETs, reducing energy loss during switching. Based on these reasons, SiC MOSFETs are more and more widely used in high-efficiency converters and industrial power supplies. Fig.1-5 shows a comparison of the working range of different power devices made of different materials [29].

Fig.1-5 Power semiconductor device applications based on power and frequency levels

Efficient power conversion is heavily dependent on the power semiconductor devices used in the power conversion system. High-power applications are becoming more efficient and smaller in size because of improvements in power device technology. Such devices include IGBTs and SiC MOSFETs, which are a good fit in high-power applications due to their high voltage ratings, high current ratings, and low conduction and switching losses.

Specifically, applications with bus voltages >400V require device voltage ratings >650V to leave sufficient margin for safe operation. Applications including industrial motor drives, electric vehicles/ hybrid electric vehicles (EVs/HEVs), traction inverters and solar inverters for renewable energy are at the power level of a few kilowatts (kW) to a megawatt (MW) and beyond. Applications for SiC MOSFETs and IGBTs are at similar power levels, but split as the frequency increases, as shown in Fig.1-5.

SiC MOSFETs are becoming common in power factor correction power supplies, solar inverters, DC/DC for EVs/HEVs, traction inverters for EVs, motor drives and railway, while IGBTs are common in motor drives (AC machines), uninterruptible power supplies (UPSs), solar central- and string-type power inverters <3kW, and traction inverters EVs/HEVs.

## 1.2.2 Power Converters Using WBG Devices

The converter converts DC input to AC output, essential for power electronics, EVs, airplanes, and renewable energy. It is categorized into voltage type and current type converters based on the DC power supply. In the mid-20th century, medium and high-power converters used thyristor switching devices, however, the thyristors could not switch themselves off once they were turned on, and additional forced commutation circuits were required. Forced commutation circuits increase the weight, size, and cost of the converter, limit the switching frequency, and reduce system reliability. Based on technological advances, the vast majority of today's converters utilize fully controlled power semiconductor switching devices, and in this thesis, only converters consisting of fully controlled devices are discussed.

In order to meet the needs of high-power applications with higher withstand voltages and higher currents, one solution is to connect the devices directly in parallel

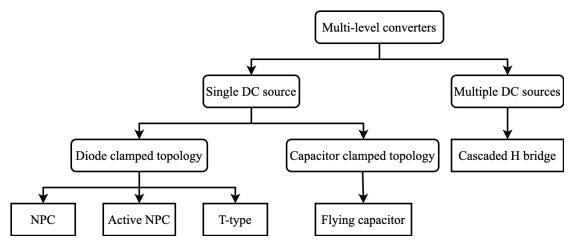

to increase the current rating, and to connect the devices directly in series to increase the withstand voltage rating. However, it is difficult to ensure that the current distribution during the operation of each switching device, especially during turn-on and turn-off, is identical [30]. Moreover, directly connecting devices in series or parallel usually requires lowering the operating frequency, so this is not the most effective measure to expand the output capacity of the converter. Other common ways to increase converter capacity are multi-level techniques. The primary reason for using MLCs is their unique voltage stacking capability, which effectively allows for an increase in voltage levels. This capability enables the combination of multiple lower voltage sources to produce a high voltage output, rather than relying on a single high voltage source. MLCs can generate output waveforms that are closer to a sine wave as they can switch between multiple different voltage levels. Such waveforms have lower Total harmonic distortion (THD), providing smoother voltage output, which is particularly important for applications requiring high power quality. This innovation started in the 1970s with the cascaded H-bridge (CHB) converter [31]. The circuit topologies of MLCs are varied and relatively complex, and several common topologies are described below, while a detailed numerical comparison of various MLCs will be analysed in Chapter 2.

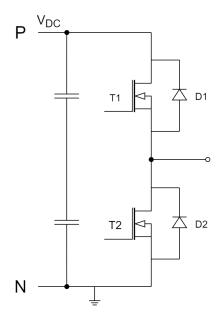

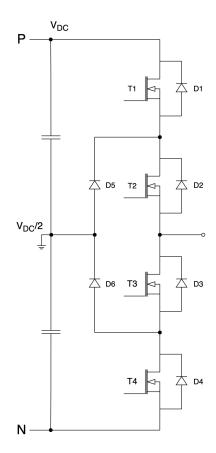

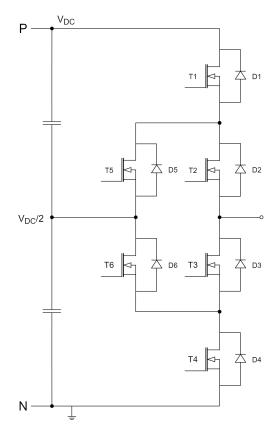

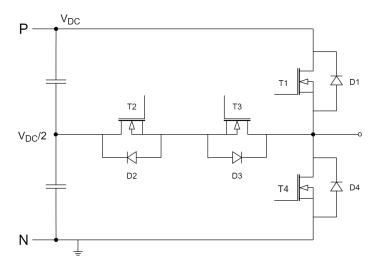

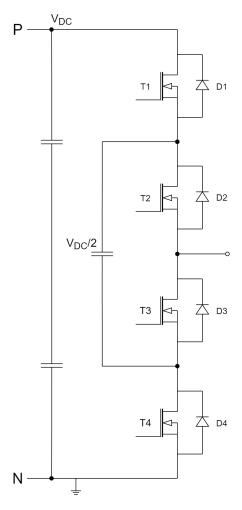

In the last few decades, three-level converters have gradually gained interest as an alternative solution to the standard VSC. Among the many topologies that have been developed, these include neutral point clamped (NPC), T-type NPC (TNPC), Active NPC (ANPC), flying capacitor (FC), CHB, and other structures. Several studies have highlighted the advantages offered by three-level converters [32]-[37]. In these topologies, NPC and T-type are considered to be competitive solutions and have received the most research attention [38]-[40].

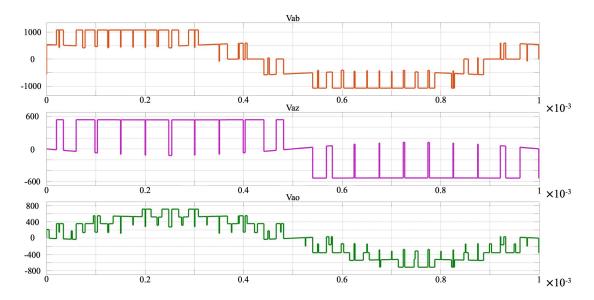

The three-level NPC converter proposed in [41] is widely used in the power electronics system. The converter's output terminal potential clamps to the neutral point potential. Compared with the conventional VSC, the NPC converter output contains less harmonic content. This three-level NPC converter is used to drive a three-phase induction motor, experimental results show that the output current contains very small low-order harmonics. A further advantage of the three-level converter circuit is that each main switching device is switched off at only half the

voltage of the DC side. Therefore, this circuit is particularly suitable for high-voltage, high-capacity applications.

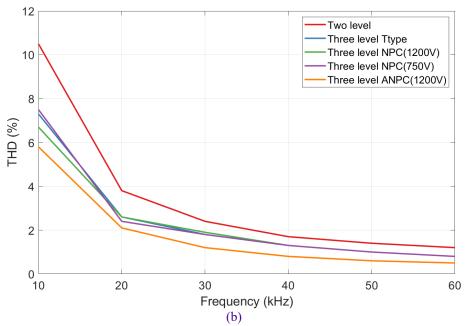

[42]-[43] paid more attention to the research of three-level T-type converters, and developed an average loss model, in this model, losses are affected by different factors (e.g. modulation index, power factor). In addition to the low output harmonics mentioned above, three-level T-type converters also use devices with lower rated voltages and only use half of the DC bus voltage, resulting in lower switching losses compared to two level VSC. In these papers, experiments show that compared with two-level converter and three-level NPC converter, three-level T-type has a higher efficiency in the range of 10-30kHz. [42] also focus on the three-level T-type converter, the purpose is to prove the feasibility and advantages of using three-level T-type converter instead of two-level converter in low-voltage applications. By using a three-level T-type prototype for experimental measurement, the three converters were compared under different power factor angles and different switching frequencies. Within 10-30kHz, the efficiency of three-level T-type converter is significantly higher than that of two-level converter, while there is little difference within 10kHz, therefore, the trade-off between cost and efficiency can be considered in this range. In the frequency range above 30kHz, three-level NPC converter slightly exceeds three-level T-type in efficiency. However, it is worth noting that, unlike conventional NPC topology, the T-type cannot benefit from voltage stress splitting, which limits its use in high-voltage applications [44].

ANPC converter is an improved mid-point clamped MLC, which adds some active components to the conventional NPC converter to solve the problems of voltage balance and switching losses that exist in the conventional NPC converter [45]-[46]. ANPC converters can better balance the voltage of the DC side capacitor by adding additional active switches. By optimising the switching sequence, ANPC converters can reduce the switching losses and thus improve the efficiency of the converter. ANPC converters have gained significant interest in low- and medium-voltage power electronics applications [47]-[48]. However, due to the high cost of SiC switches, the use of six SiC MOSFETs per phase leg leads to a significant increase in the cost of the converter system [49]-[50], while the ANPC converter may have a higher structural and control complexity than a conventional NPC converter. To reduce the cost, some research [51]-[53] replace active switches from SiC MOSFETs

to Si IGBTs, the proposed topology utilises SiC MOSFETs to reduce the switching losses and achieves zero-current switching of Si IGBTs.

FC converters arose in the 1990s to achieve multi-level outputs by using flying capacitors to create intermediate voltage [54]. There is no DC link balancing problem due to the absence of neutral point. In this topology, the flying capacitor is used to replace the DC source while generating the voltage level. In general, FC converters have a modular design that allows higher voltage levels to be achieved by adding more capacitors and switches than the NPC converter, which provides flexibility in system design. However, the voltage control of the flying capacitor, the pre-charging of the capacitors during start-up and the large number of capacitors employed are the main challenges faced by such topologies [55]-[56]. FC topologies are not competitive in low to medium switching frequency applications due to the high cost of flying capacitors at low to medium switching frequencies [57].

Compared to conventional converters, MLCs typically use more semiconductor chips, resulting in larger volumes and requiring additional gate drive circuits. However, the increased number of output voltage levels and the step reduction in voltage amplitude allow MLCs to significantly improve the quality of output voltage and current. This improvement reduces the need for Electromagnetic Interference (EMI) filters and improves load efficiency. According to the above content, Fig.1-6 summarises the classification of mainstream MLCs topologies. This classification highlights the different approaches to achieving multi-level conversion, either through a single DC source with various clamping methods or through multiple DC sources with cascaded H-bridges.

Fig.1-6 Multi-level converter classification

#### 1.2.3 Power Electronics Packaging and Power Module

This section examines the fundamentals of power electronics packaging and power modules, emphasizing their role in modern power systems. Power electronics packaging involves encasing electronic components and circuits in protective casings to enhance system reliability, performance, and efficiency under diverse environmental conditions. The process covers encapsulating electronic components and integrated circuits in a suitable case or package to protect them and provide the necessary connections, which increases the durability of the equipment and reduces the failure rate while also improving the overall performance and efficiency of the system.

A MOSFET die represents an unpackaged semiconductor chip from the manufacturing process, used directly in product integration without leads or casing. Power modules, typically integrating multiple semiconductor devices like IGBTs, MOSFETs, and diodes, come in compact, user-friendly packages. They include necessary circuitry and thermal management, offering electrical and mechanical support. These modules address specific power and voltage needs, ensuring efficient power conversion and control, crucial for high-power applications.

Currently on the commercial market, the power modules used in high voltage and high current applications are mainly occupied by IGBT modules [58] that combine Si IGBTs and Si FRDs (fast recovery diodes). According to the above introduction, the power modules made by SiC can reduce the switching loss caused by the tail current and the diode recovery current and can work in the high frequency range. Therefore, it has very good development prospects, and the following literature specifically analyses the advantages of SiC power modules.

In order to verify the fast-switching capability of the SiC power module, [59] firstly evaluated the static current-voltage characteristics and capacitance-voltage characteristics, and then evaluated the performance of using SiC devices and Si devices in a DC-DC boost converter through experiments, indicating that due to the small input capacitance and lower Miller effect, SiC module has fast switching capability. However, the experimental results show that compared to the Si IGBT power module, a larger voltage oscillation will produce in the SiC MOSFET power module when the switch is turned off. Through the double pulse experiment, [60]

verified that the sic module can reduce the conduction loss and the diode reverse recovery loss, and the performance is tested in the three-phase permanent magnet motor platform. Through observation and comparison, the reverse recovery current of the Si diode is much higher than that of the SiC diode under the same forward current, thus the reverse recovery loss of the diode is reduced due to the smaller reverse recovery current in the module. When comparing different modules with the same three-phase permanent magnet motor load, obtained in a very wide range of speed, the efficiency of the SiC module is higher than that of the Si module. This paper uses a hybrid SiC power module and does not use a full SiC power module. Although the performance improvement is not as great as that use of a full SiC module, it also verifies the advantages of SiC materials. In [61], the developed full SiC power module is applied to the traction inverter. Compared with the Si IGBT module, under the output power of 220kW, the weight and volume of the SiC module are smaller, and the achieved power density is more than 50% higher than that of Si IGBT modules. In a wide output power range, the efficiency of the full SiC MOSFET module is higher than that of Si IGBT module.

At present, in some special applications, the power module needs to work at a higher temperature (> 200°C). In order to meet this demand, special power module packaging technology is needed. [62]-[63] improve the heat dissipation design, use air cooling, and use a new bonding technology for interconnection. Performance tests are carried out through experiments, and the results show that these modules can run above 200°C, which is higher than the 150°C operating temperature of traditional Si IGBT power modules. At the same time, a comparison of switching losses has been carried out, and it is found that the switching loss of SiC MOSFET modules is one third of that of Si IGBT modules. As packaging technology is still developing rapidly, reliable packaging and optimisation at high temperatures still have much room for improvement.

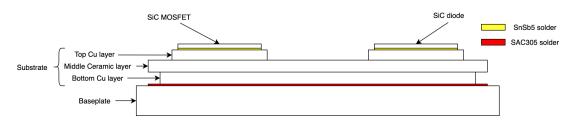

Fig.1-7 shows a typical SiC power module package, typically, power modules consist of a multi-layer structure with heterogeneous materials including semiconductor devices, substrate, baseplates, and solders, etc. The heat generated by the power devices is transmitted vertically through the substrate and baseplate to the heatsink, and the electrical connection between the devices is mainly achieved through aluminium bonding wires. This type of package generates a high current

density at the bonding wires, which results in relatively high temperatures. High interconnect reliability can be achieved by low-temperature silver sintering of power devices, increasing reliability by a factor of about 10 [64].

Fig.1-7 Cross sectional diagram of a typical SiC power module

The packaging of power modules requires suitable material selection, packaging materials and technologies must be adapted to the stringent thermal and electrical constraints [65]-[67]. Table 1-2, Table 1-3 lists the physical properties of some common materials used in power modules. Materials with closer coefficient of thermal expansion (CTE) will enhance the lifetime of the module and can reduce the stresses in the interface materials and internal materials, the higher the thermal conductivity, the lower the Junction-case thermal resistance will be and the lower the junction temperature difference in operation.

Another important characteristic is the material density, especially the substrate, for example, using the copper substrate as a reference, the density of AlSiC material is 1/3, while CuW has twice the density, so AlSiC will provide considerable weight reduction and improve reliability. With the reduction in material cost, Si<sub>3</sub>N<sub>4</sub> is highly recommended for power module packaging. Si<sub>3</sub>N<sub>4</sub> has a similar CTE as Si, resulting in lower thermo-mechanical stresses during temperature changes. As a result, power modules packaged in Si<sub>3</sub>N<sub>4</sub> have improved reliability in high power and high temperature SiC packages.

| Table 1-2 Relationship between the combination of coefficient of thermal expansion and thermal |

|------------------------------------------------------------------------------------------------|

| conductivity of different materials and thermal resistance                                     |

|                                       | CTE (ppm/K) | Thermal conductivity (W/mK) | Rthjc (K/W) |

|---------------------------------------|-------------|-----------------------------|-------------|

| Silicon die                           | 4           | 136                         |             |

| Cu/Al <sub>2</sub> O <sub>3</sub>     | 17/7        | 390/25                      | 0.35        |

| AlSiC/ Al <sub>2</sub> O <sub>3</sub> | 7/7         | 170/25                      | 0.38        |

| Cu/AlN                                | 17/5        | 390/170                     | 0.28        |

| AlSiC/AlN                             | 7/5         | 170/170                     | 0.31        |

| AlSiC/Si <sub>3</sub> N <sub>4</sub>  | 7/3         | 170/60                      | 0.31        |

Table 1-3 Typical properties of different materials for substrates and substrates

|           | Material                       | CTE     | Thermal conductivity | Density    |

|-----------|--------------------------------|---------|----------------------|------------|

|           |                                | (ppm/K) | (W/mK)               | $(g/cm^3)$ |

| Baseplate | CuW                            | 6.5     | 190                  | 17         |

|           | AlSiC                          | 7       | 170                  | 2.9        |

|           | Cu                             | 17      | 390                  | 8.9        |

| Substrate | Al <sub>2</sub> O <sub>3</sub> | 7       | 25                   |            |

|           | AlN                            | 5       | 170                  |            |

|           | Si <sub>3</sub> N <sub>4</sub> | 3       | 60                   |            |

| Die       | Si                             | 4       | 136                  |            |

|           | SiC                            | 2.6     | 270                  |            |

The objective of SiC module packaging is to realize its application at high temperatures and high frequencies, so a series of new considerations for packaging must be made. The development trend of SiC power semiconductor packages is mainly reflected in three aspects: module structure, materials, and technology.

In conclusion, SiC power module has the advantages of high efficiency, lower losses, high temperature resistance and high-power density. Therefore, it is widely used in automotive, aerospace, PV, and other industrial fields. For example, in EVs, SiC power modules can improve charging efficiency and shorten charging time [68]; in aircraft power system, it can reduce the weight and heat generation of the whole system and improve efficiency [69]-[71]; it reduces the effect of common mode voltage for PV inverters [72].

# 1.3 Overview of Non-ideal Effects of Power Electronics

In the rapidly evolving field of power electronics, the performance of a system depends not only on the ideal behaviour of the components but is also significantly affected by a range of non-ideal effects. These effects are often due to physical and practical limitations of components and materials, and they present challenges that require complex engineering solutions. A more comprehensive overview of these non-ideal effects is provided below, focusing on their impact on system design and operation.

1. Loss Mechanisms: The loss mechanisms of power devices include conduction losses, switching losses, and reverse recovery losses. Conduction losses occur during device conduction due to the resistance of the conduction path, depending on the conduction resistance and current. Switching losses happen during the transition between "on" and "off" states, influenced by switching

frequency, device characteristics, voltage and current during the transition, and switching times. Reverse recovery losses occur in power diodes when stored charge is removed during the switch from on to blocking state, causing brief reverse current flow. To reduce these losses and enhance system efficiency, selecting devices with low on-resistance, low reverse recovery time, and low gate charge, along with optimising circuit design, is essential. Understanding and managing these loss mechanisms is critical for improving the efficiency and reliability of power electronic systems.

- 2. Parasitic Effects: In electronic circuits, components inherently have parasitic components such as parasitic capacitance, inductance and resistance. These components, although unintended and may be present in the component itself or in the layout of the circuit board, can cause energy loss, oscillations, voltage overshoots, and other undesirable effects. Parasitic inductors and capacitors, in particular, can cause ringing and oscillation in circuits, which not only interferes with the normal performance of the device, but can also cause additional losses.

- 3. Thermal Management Challenges: Power devices generate heat due to internal losses during operation, which not only affects their performance and efficiency, but may also shorten the service life of the equipment. Without effective thermal management measures, excessive heat accumulation can lead to performance degradation or even equipment failure. Especially when the heat is excessive, it may lead to thermal runaway, causing the device temperature to rise to the point of self-destruction. Therefore, it is critical to develop efficient thermal management solutions that help ensure that heat is dissipated efficiently and that device temperatures are maintained within safe operating ranges, thus avoiding early failures due to overheating.

- 4. Electromagnetic Compatibility: The nonlinear components and switching actions of power electronic devices can generate harmonics and EMI that can affect the performance and reliability of other electronic devices and systems. Noise generated by power electronic circuits can interfere with other equipment by conduction or radiation. EMI is particularly influential on the performance of sensitive equipment and must be carefully considered and controlled at the design stage, for example using shielding, optimised layouts and the addition of filters.

In summary, these non-ideal effects must be fully considered and addressed in the design and application of power electronic converters. By optimising device losses, improving thermal management, reducing parasitic effects and controlling EMI, the performance and reliability of the system can be significantly enhanced, extending the lifespan of the equipment. These efforts not only help to enhance the overall efficiency of the power electronics system, but also ensure its stable and reliable operation in various application environments.

#### 1.3.1 Power Losses in Converters

Power losses in power electronics systems have a significant impact on their performance, reliability, and efficiency. These systems are integral to a variety of applications ranging from power supplies, renewable energy systems, to EVs. Their primary function is to convert and control electrical power, however, this process is not entirely efficient, and some energy is inevitably lost in the form of heat. Power losses in power electronics are primarily divided into three categories: conduction losses, switching losses, and reverse recovery losses. These power losses lead to an increase in the temperature of the device, and if not properly managed, can cause device failure. Therefore, it is essential to design power electronic systems that minimise these losses and effectively dissipate the heat generated [73]-[74].

- 1. Conduction losses: Conduction losses refer to the power dissipated due to the resistance of the conduction path when a semiconductor device is in the "on" state. As the current flowing through the device increases or the on-resistance increases, these losses also rise. When current flows through a semiconductor device, the internal resistance causes energy to be dissipated as heat. Conduction loss is generally proportional to the square of the current flowing through the device and depends on the device's on-resistance. This type of loss is typically the most significant among all types of losses.

- 2. Switching losses: The switching devices of a power electronic converter incur switching losses each time they are switched on or off. During the state transition, both the voltage across the device and the current flowing through it are non-zero, causing energy to be dissipated as heat, thereby resulting in power losses. The switching frequency and device characteristics, such as the

- gate charge of the MOSFET, have a significant effect on the extent of these losses.

- 3. Reverse recovery losses: In rectifier diodes and some types of MOSFETs, the charge stored in the diode needs to be removed when the diode switches from the on state to the off state. Losses are incurred in this process, which are called reverse recovery losses. In MOSFETs, the body diode is a built-in component with reverse recovery time and reverse recovery losses. This body diode acts during reverse conduction of the MOSFET. For SiC MOSFETs, the reverse recovery losses of the body diode are typically much smaller than that of Si MOSFETs due to the characteristics of the SiC material. Furthermore, many high-performance SiC MOSFET power module designs use an additional Schottky diode to further minimise reverse recovery losses. This is because Schottky diodes have no carrier storage and therefore no reverse recovery loss. Since this thesis focuses on the performance of SiC-based power electronic systems, it will not be overly concerned with reverse recovery losses.

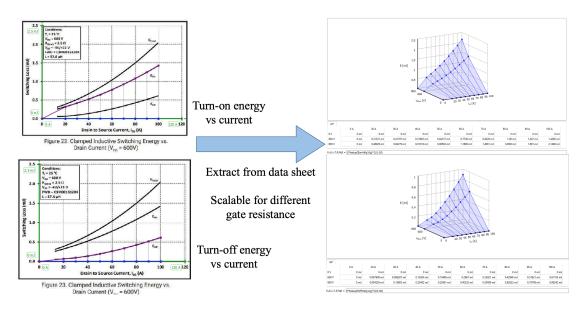

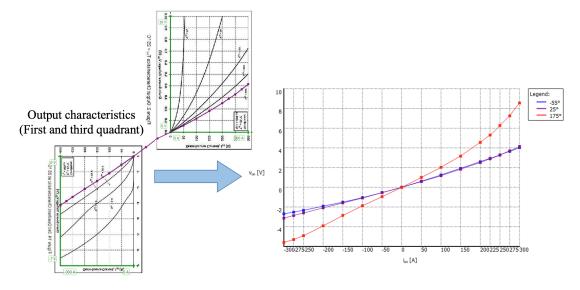

On this basis, it is crucial to understand the specific mechanisms of these losses in different converter topologies. It is especially critical to develop more accurate models to predict and reduce power losses by studying the behaviour of power devices and semiconductor devices such as diodes. The literature extensively examines losses in two-level and three-level converters, focusing on semiconductor losses. While approximations of IGBT and diode I–V switching characteristics, some earlier studies [75]-[77] have been used to estimate switching losses, an alternative, more straightforward method employs the switching energy-current (Esw-I) characteristics. This approach indicates that the switching losses of an IGBT-diode pair approximately correlate with the switching voltage and current, as detailed in [78]. Research on switching losses, utilizing a second-order approximation of the IGBT and diode Esw-I characteristics, is presented in [79] for a three-level NPC converter, along with analytical formulas specific to switching losses in two-level converters. It is noted that for two-level converters, all continuous pulse width modulation (PWM) techniques yield identical switching losses, irrespective of the load phase angle [80].

Regarding conduction losses in two-level converters, detailed formulas are provided in [76] and [81]. These calculations hinge on the linear I–V characteristics of IGBT–diode modules. Differing from switching losses, the conduction losses in two-level converters are influenced by the choice of PWM strategy and the load power factor. For NPC converters, expressions accounting for various modulation strategies are documented in [82]. Regarding the calculation of different losses, several methods have been proposed. [83] proposes a fast calculation method based on the datasheet. The MOSFET is modelled, the amount of stored charge is related to the energy in the parasitic capacitance to calculate the voltage drop and rise time. The theoretical model was verified through experiments, and finally it was proved through comparative data that the model can allow the estimation of losses within the error range of up to 10%. It is worth noting that the module assumed and used in this paper has a low stray inductance, so the voltage oscillation is relatively small, when the stray inductance is large, the model may no longer be valid, or the charge calculation needs to be corrected.

#### 1.3.2 Parasitic Parameters and Reduction

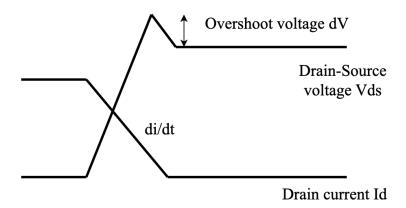

Parasitic inductance has a significant effect on the turn-on and turn-off processes of power switching devices. This is mainly due to the voltage response of parasitic inductance in the face of current variations. This effect is particularly noticeable in high-frequency, high-speed switching applications. The following are the main effects of parasitic inductance of power switching devices [84]-[86]:

1. Overvoltage: When a power device is switched off, the current flowing through the switching device attempts to fall rapidly to zero. However, due to the presence of parasitic inductance, a voltage surge is produced across it that is proportional to the rate of change of current. This can cause a rapid rise in switching voltage that may exceed the device's rating and damage the device. The overshoot voltage dV is equal to the parasitic inductance multiplied by the rate of change of current di/dt. Fig.1-8 describes the voltage overshoot caused by the inductance.

Fig.1-8 Voltage overshooting caused by parasitic inductance

- 2. Delayed turn-off: The turn-off time of a switching device may be slightly delayed due to the inductance limiting the rapid change in current.

- 3. Increased switching losses: During turn-on and turn-off, the transitions in current and voltage due to parasitic inductance are not instantaneous, meaning that during these transitions the device is between on and off states, resulting in additional switching losses.

- 4. Oscillations: Parasitic inductors and other capacitors (e.g., MOSFET output capacitance C<sub>oss</sub>, or other parasitic capacitors) may form an LC oscillating circuit, causing oscillations in the voltage and current on the device. This not only increases switching losses but may also interfere with the normal operation of other parts.

As mentioned in the previous subsection, The SiC MOSFET and with no reverse recovery SiC schottky barrier diode (SBD) can reduce the reverse recovery current and thus further reduce the switching losses [91]. However, they also aggravate oscillations during switching [88]-[89], making SiC MOSFET and SiC SBD more suitable for high-frequency converters. These effects may be more noticeable in power modules due to their more complex interconnections, higher currents, and more stored electromagnetic energy. To simulate and mitigate these negative effects, the parasitic inductance of these high-speed power modules needs to be improved.

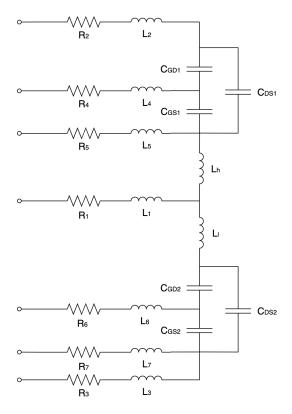

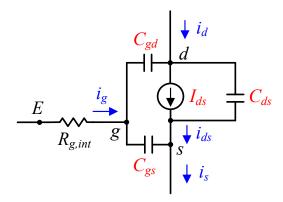

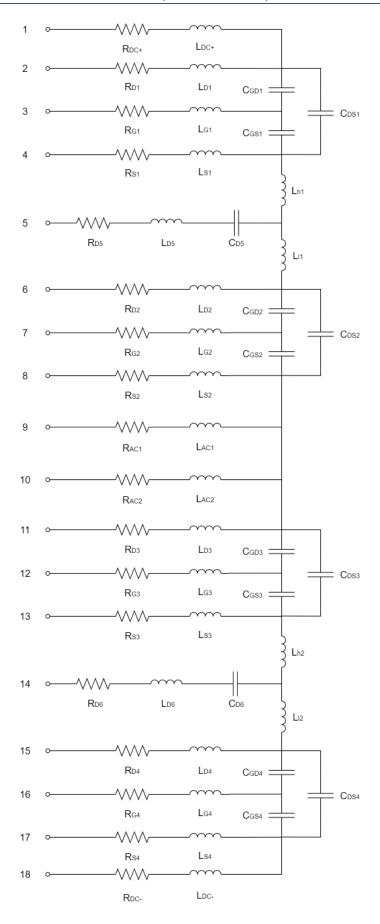

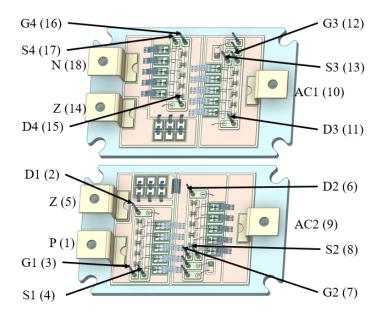

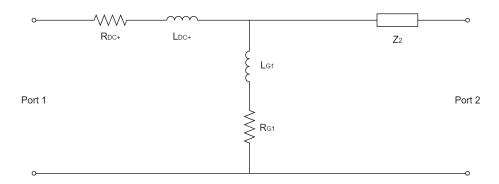

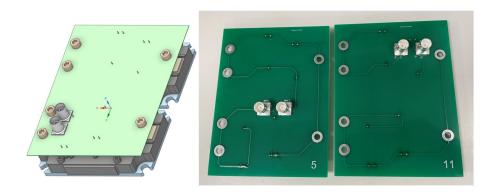

The fast-switching capability of a power device is affected by the parasitics introduced due to the semiconductor die itself and the package of the module itself, as the latter produces a fraction of the overall parasitic inductance. More detailed parasitic parameter models can be obtained by considering the parasitic inductance of the module package, i.e., copper busbars, terminal pins, and bonding wires. Fig.1-9

shows the parasitic parameter model for one phase leg of a two-level module. The model describes the power module during switching transients. This model includes the gate capacitance ( $C_{gs}$ ,  $C_{gd}$ ), output capacitance ( $C_{ds}$ ), gate inductance ( $L_g$ ), drain and source inductances ( $L_d$ ,  $L_s$ ) introduced by the MOSFET die itself.

Fig.1-9 Parasitics of the SiC MOSFET die and parasitics added by the packaging

It is widely recognised that commutation inductance causes significant voltage overshoot and ringing at turn-off [90]-[94], Therefore, minimising these parasitics in the design of power modules is an important challenge for high-performance converter systems.

Due to the difficulty of reducing the parasitic parameters of the MOSFET die itself, the question of how to minimise the parasitic parameters of the package has become a recurring theme in the literature on WBG power modules and their applications over the last few years [95]-[99]. New module designs with much lower parasitic inductances inside the module than their predecessors have been introduced for high power modules. [100] measured the parasitic inductance of SiC power module and found that the inductance between the terminals of the module is as low as about 15nH, compared with the IGBT module with the same structure has 40nH stray inductance. The module arranges internal bonding wires to make the drain

current and source current as close as possible to reduce stray inductance. The power module used in [101] removes the bond wires, using a new planar packaging technology to achieve low-inductance design, and apply a RC-C snubber between the two DC terminals DC+ DC- to reduce the loop inductance. [102] proposes a SiC halfbridge power module. The low inductance design of the module comes from minimising the length of the power loop and choosing to increase the width of the power terminals to distribute the current evenly among each device. [103] shows a sandwich SiC power module structure without bonding wires. In order to minimise the parasitic inductance caused by the wiring between the positive and negative terminals (DC+/DC-), the design connects the source of the upper semiconductor and the drain of the lower semiconductor to the same substrate, compared with the traditional bonding wire connection, this can shorten the wiring length between the upper and lower semiconductors. Integrating the DC bus capacitor and gate driver in the power module can reduce the parasitic inductance in the commutation loop and gate loop of the half-bridge power module [104]. Through simulation comparison, it is found that the power module with integrated DC bus capacitor can reduce the voltage overshoot by three times, the stray inductance reduced by three times to 7.2nH. Other power modules use multi-layer substrates, including three layers of copper and two layers of ceramics, to achieve 1.15nH stray inductance. Such a substrate design can compensate for the thermal effect of ceramics because heat is diffused in the copper layer [105]. [106] provides another way to reduce stray inductance by using laminated busbar and snubber capacitors. Since the inductance of the laminated busbar is proportional to the distance and length, and inversely proportional to the width, the relationship between the length and width of the busbar needs to be considered in the design, and finally the optimal aspect ratio is obtained through modelling and analysis. The buffer capacitor can compensate the inductance between the main capacitor and should be placed as close as possible to the power module. However, too many capacitors will cause the bus circuit to be longer, which will increase the stray inductance. Therefore, it is necessary to conduct multiple simulations and experiments to determine the best solution.

To design and optimise the internal circuit layout of the power module, simulation modelling is required when designing the power module. The goal of packaging is to obtain a low-inductance power module that can work at high power. In any case, the

result is that many key components are very close to each other, and the multiphysics coupling effect becomes more prominent. Finite element method (FEM) is very effective for solving the partial differential equations involved in the mathematical expressions of many physical phenomena (electromagnetic, mechanical, thermal).

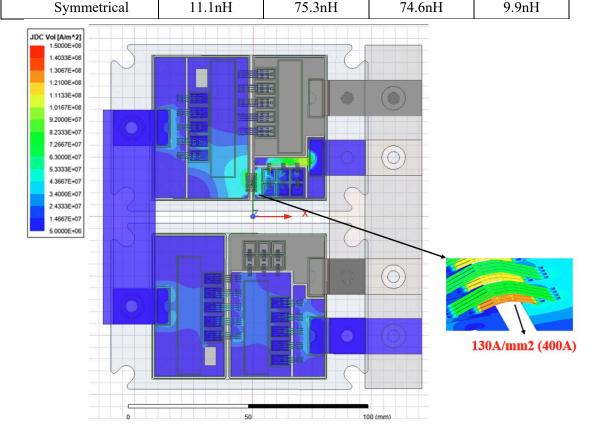

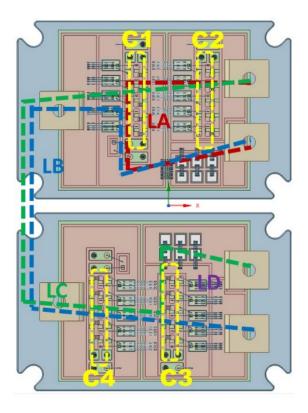

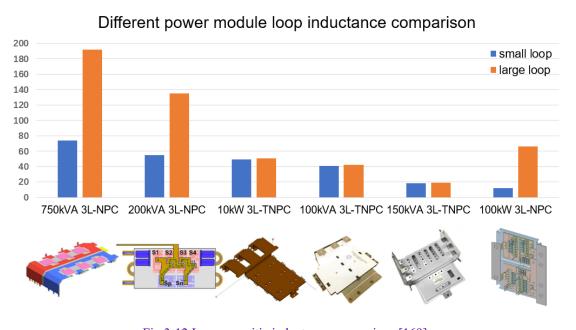

Minimisation of module parasitics is most easily achieved by using modelling tools to assess the impact of system constraints and design approaches on performance. Due to time and cost constraints, it is often not feasible to evaluate intermediate design solutions through hardware prototyping. Instead, computationally based methods such as FEA and partial element equivalent circuit (PEEC) can often be used for this purpose. The package of the SiC power module needs to reduce the parasitic impedance. To achieve this goal, most packages are as compact as possible. However, this will cause difficulties in the measurement of electrical parameters, so in order to obtain these parameters, need to rely more on simulation. Electromagnetic modelling relies on numerical techniques used to solve Maxwell's equations in terms of unknown electric and magnetic field distributions and/or current and charge distributions in space. To simulate the module's inductances, a quasi-static EM solver, in this case ANSYS Q3D Extractor, was used, the workflow of Q3D is shown in Fig.1-10. The software allows for visualising the current distribution at high frequencies and extracting self and mutual inductances of current paths. Q3D has been used to evaluate parasitic inductance in SiC MOSFET power modules [107]-[111], and Si IGBT power modules [112]-[113].

Fig.1-10 Q3D solve procedure

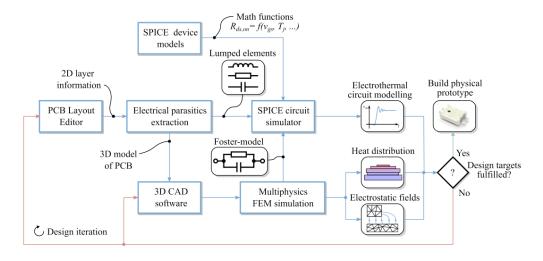

Two electromagnetic modelling methods are introduced in [114] to extract the parasitic parameters of the power module package. The first is to use the ANSYS Q3D Extractor solver, and the second is to use the PEEC solver. The second solution method has good prospects and can solve some of the limitations of Q3D electromagnetic modelling. This paper takes TO-247 package and sic half-bridge power module as examples to verify these two modelling methods respectively, analyse the advantages and disadvantages of the two methods, and prove that the PECC method can more accurately predict the parasitic parameters of the package, However, further improvements are needed to increase the calculation speed. [115] provides design ideas for power modules, Fig.1-11 shows the flow chart of designing a power module, this paper focuses on the role of different software in the design process and the sequence of use.

Fig.1-11 A design example of power modules [115]

The method presented in the previous subsection can be effective in quickly obtaining the parasitic parameters, however, very large and complex models may require a significant amount of computational time and may not easily converge, and detailed structural information about the internal structure of most commercial power modules is not available to obtain the partial parasitic inductance through software modelling. Measurement-based methods can be further divided into two subcategories: time-domain reflectometry (TDR) and frequency-domain impedance measurements. TDR is a technique used to measure and locate faults in a cable or transmission line. TDR works by sending a pulse or high-speed stepping signal to the cable and then measuring the signal that is reflected back. Based on the timing and amplitude of the

reflected signal, the location and nature of the fault can be determined [116]-[117]. TDR methods require complex experimental setups, special hardware (TDR/sampling header) and software, as well as an iterative multistep process, and are thus practical applications are limited. Frequency-domain impedance measurements are a technique for measuring resistance, capacitance, inductance, or other complex impedance values at different frequencies. Such measurements are usually done using a network analyzer or frequency response analyzer. The purpose of the measurement is to understand and analyse how the electrical impedance of a particular circuit changes as the frequency changes. The impedance measurement method has gained wide acceptance as a simple and easy-to-use technique with higher accuracy and ease of use for circuit designers [118]-[121]. This method basically involves making frequency domain impedance (Z-parameter) measurements between two terminals of a power device by means of an impedance analyzer or a vector network analyzer (VNA). However, this impedance measurement is currently limited to a single-port configuration between two device terminals, with the third terminal floating during the measurement. As we will demonstrate in later sections, the unconnected floating terminal introduces significant measurement errors due to parasitic coupling to ground. For microwave field effect transistors such as GaAs MESFETs, a characterization technique based on VNA-based S-parameter measurements was developed to extract small-signal equivalent circuits and intrinsic components [122]-[124]. This Sparameter measurement method has also been applied to Si power MOSFETs [125], but it requires a cumbersome de-embedding procedure prior to S-parameter measurements and iteratively obtaining the inductance values by converting and matching the Y parameters with the reference Y parameters, which inevitably increases the complexity of the measurements and reduces the measurement accuracy. A simple two-port measurement technique and applied it to some discrete power MOSFETs is proposed [126] and Si IGBT power modules with satisfactory results [127].

## 1.3.3 Thermal Management

Thermal management of power modules has become an important area of research due to the increasing demand for high performance electronic systems. Efficient thermal management of these modules is essential to ensure their reliability and longevity, as high temperatures can cause permanent damage and shorten the life of

electronic components. A number of approaches have been proposed for thermal management of power modules, including the use of heat sinks, forced air cooling, liquid cooling, and phase change materials (PCM) [128]-[130].

- 1. Heat sinks are common thermal management tools that increase the surface area for heat dissipation. Typically made of highly conductive materials like aluminium or copper, heat sinks are designed to maximise heat transfer from the power module to the surrounding environment.

- 2. Forced air cooling uses a fan to circulate air over the power module, increasing the heat transfer rate to the environment. Due to its low cost and ease of operation, it is widely used in high-power systems such as data centres and power electronics. However, fans can present noise and reliability issues and are limited by ambient temperature.

- 3. Liquid cooling has proven to be an effective thermal management method because it has a higher thermal conductivity compared to air cooling. The use of liquid cooling also allows for a compact cooling system, which is beneficial for space-constrained applications. However, liquid cooling requires a closed-loop system, which increases the cost and complexity of the thermal management solution.

- 4. PCM has been proposed as a thermal management method because these materials undergo a phase change at a specific temperature, providing greater heat storage capacity. PCM can be used alongside other thermal management strategies to enhance overall performance. PCM has proven effective in reducing temperature spikes in high-power systems.

The choice of thermal management strategy depends on the system's specific requirements and may include heat sinks, forced air cooling, liquid cooling, or PCM. Effective thermal management is critical to ensuring the reliability and longevity of power modules, as high temperatures can cause permanent damage to electronic components. Using SiC power modules, which have lower conduction and switching losses, can help simplify thermal management, much research has been conducted on thermal management of power modules.

In addition to the low-induction design of the power module [101] also provides a real-time temperature monitoring technology. The principle of this method is that the

threshold voltage  $V_{th}$  and the on-state voltage  $V_{ds(on)}$  of the power MOSFET change linearly with temperature within a certain working range. Through the measured threshold voltage and/or on-state voltage, find  $T_j(V_{th})$  and/or  $T_j(V_{ds(on)})$  on look-up table to estimate the temperature.

The thermal response and high-temperature operating capability of the SiC power module was evaluated through experiments and numerical values [131], and the temperature dependence of the module's thermal dynamics was modelled for thermal analysis. The electro-thermal model is analysed by combining the electrical characteristics of the SiC device and the equivalent thermal circuit. Numerical analysis results show that SiC devices in power modules can operate at high temperature and reduce heat dissipation through simplified cooling systems. The numerical results of electrical response and thermal response are consistent with the experimental results from ambient temperature to extremely high temperature. However, this method will waste a lot of time when analysing a complex structure and a large number of modules, it is not suitable for all applications. This aspect requires subsequent research and improvement.

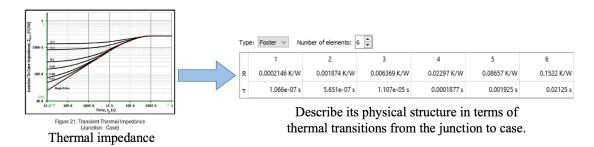

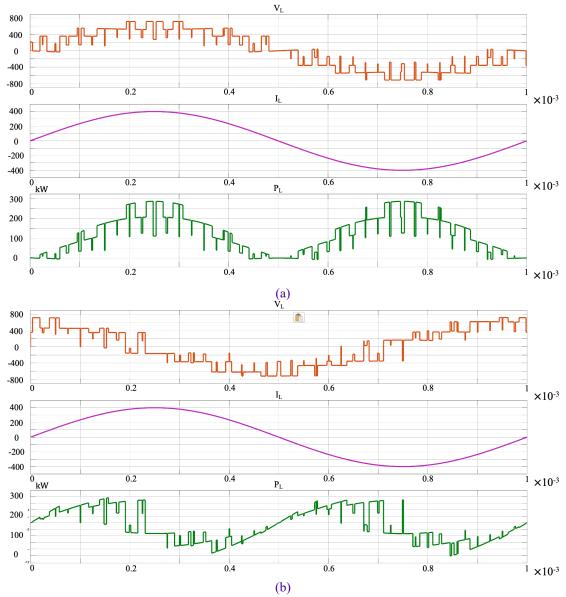

[132] studies the static and dynamic modelling and loss prediction methods of SiC power modules. The static model uses the expression of the channel current to describe the transfer and output characteristics at different temperatures. The dynamic characteristic model includes the junction capacitance, dynamic transconductance and stray parameters of the package. On the basis of these two models alone with the thermal network, a method for predicting loss and junction temperature is proposed. This method integrates the voltage and current obtained through the model to calculate the losses. If the power losses are applied to the RC network, it can be equivalent to the current from the junction temperature terminal to the case temperature terminal to calculate the junction temperature.

A simplified analytical thermal model of the power module was developed in [133]. This model considers the thermal interaction between different module chips based on the analysis method. The thermal interaction between components depends on the boundary conditions, the value of the power dissipation in the different components and the number of working chips. Modelling this effect as simply calculated energy and thermal resistance allows a reasonably low measurement of the

module. A method is proposed to use RC network to evaluate thermal resistance and thermal capacity, then estimate the transient thermal resistance of semiconductor devices.

[134] using the simulation software COMSOL Multiphysics to conduct thermal simulation and fluid dynamics simulation, to obtain the change of thermal resistance under different coolant temperature and fluid velocity. The results show that the thermal performance of the half-bridge power module using epoxy resin lead frame module is improved by about 40%, and the parasitic inductance of this module is 12nH, which is about 40% less than the DCB-based module. In addition, the double pulse test shows that the overcharge voltage can be reduced when the DC link capacitor is integrated inside the module.

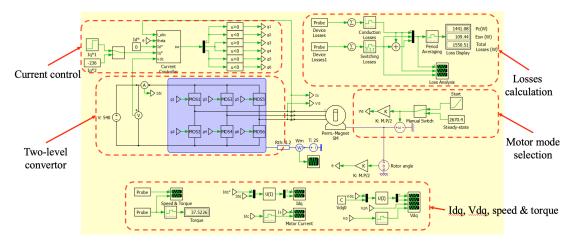

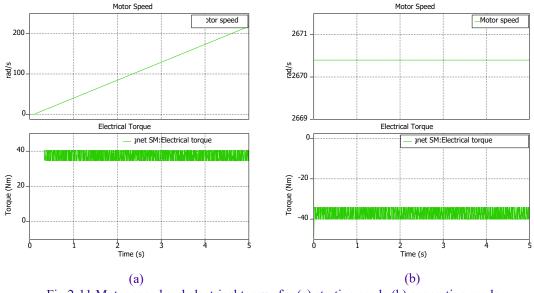

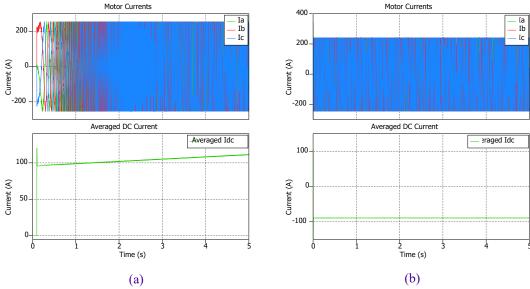

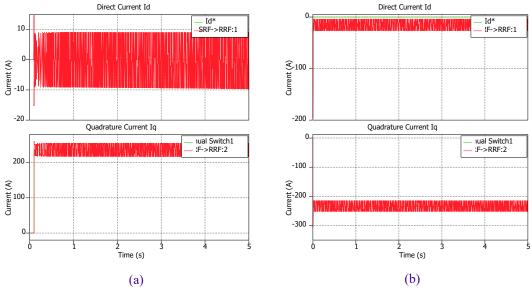

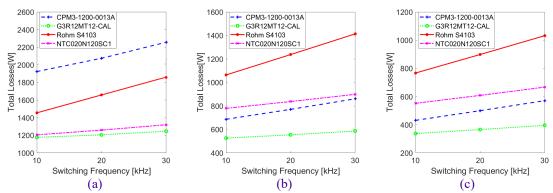

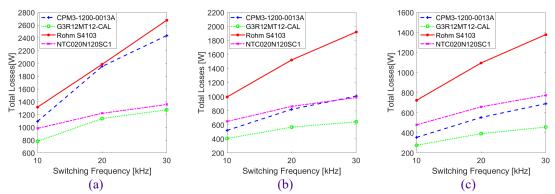

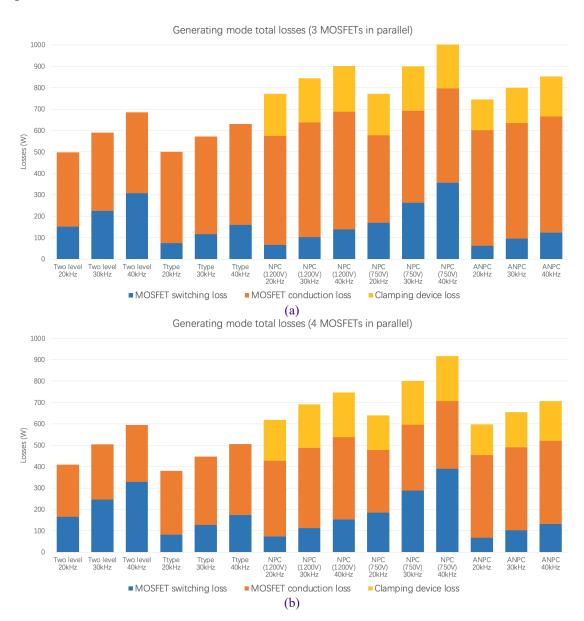

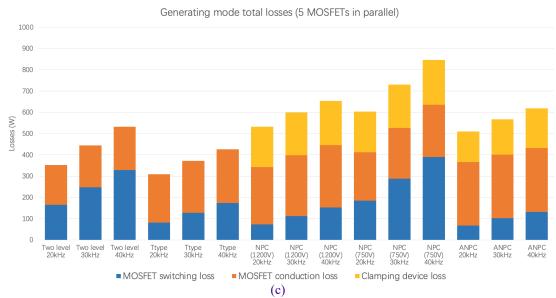

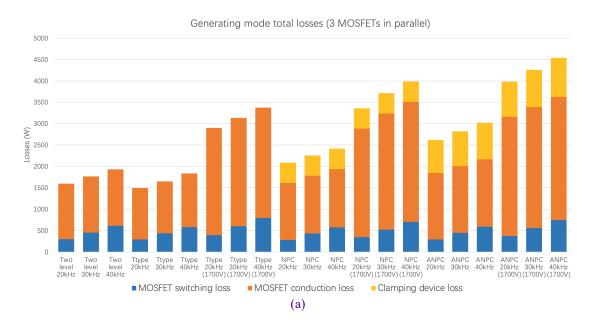

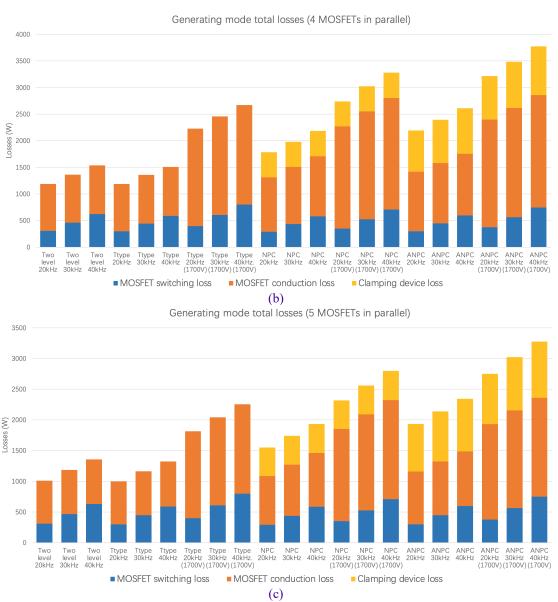

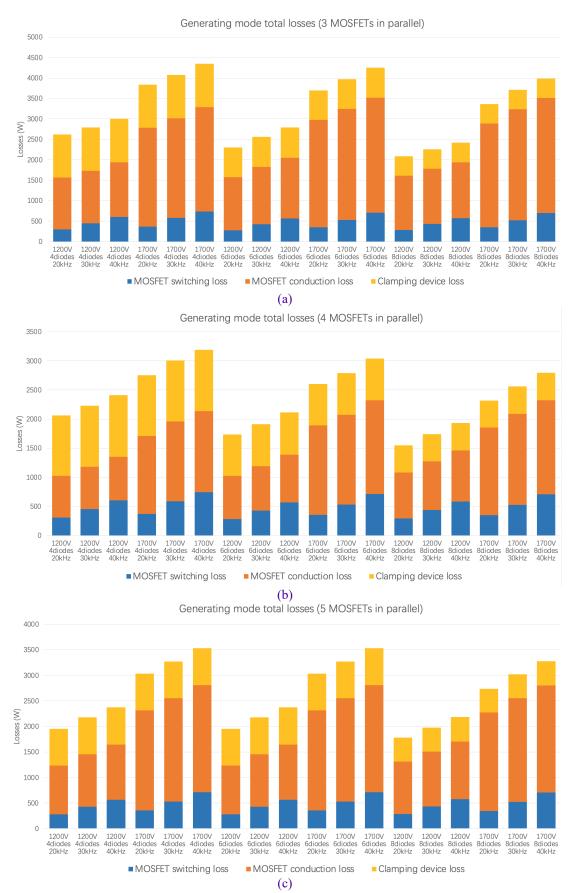

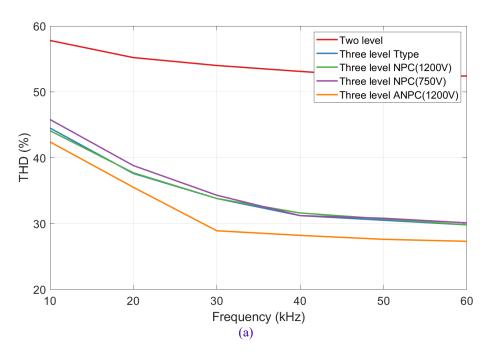

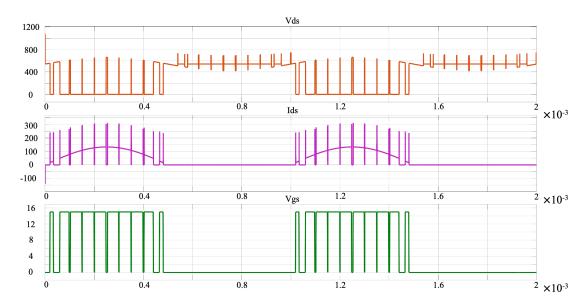

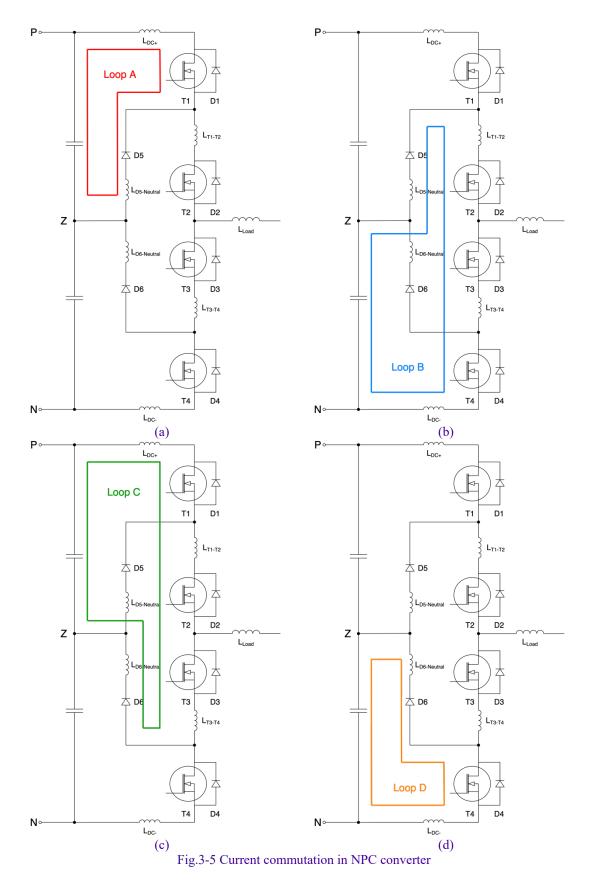

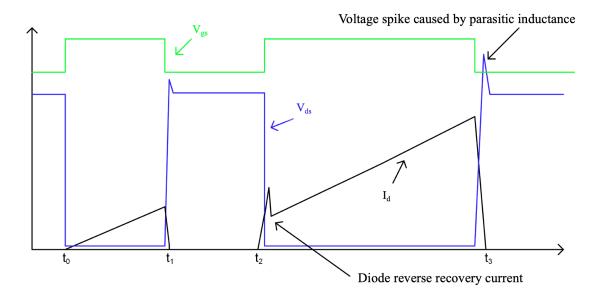

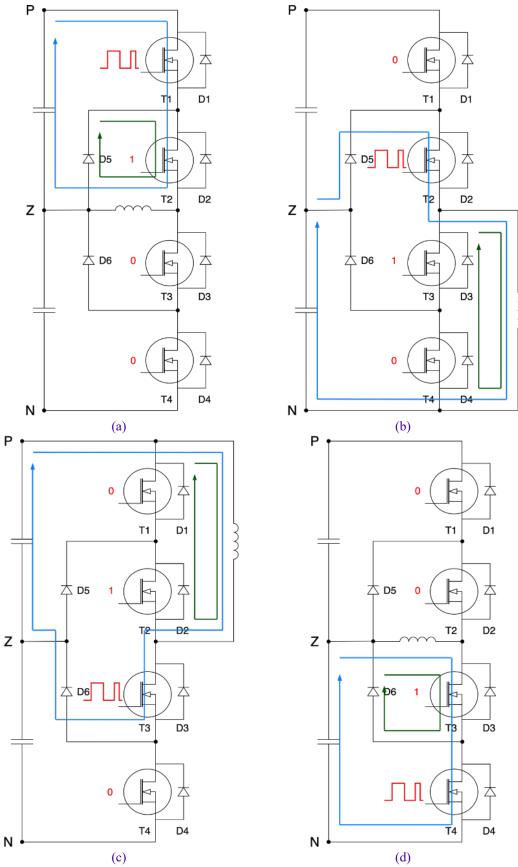

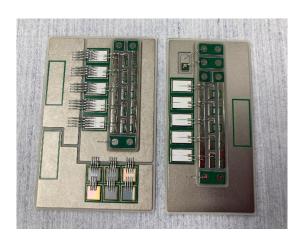

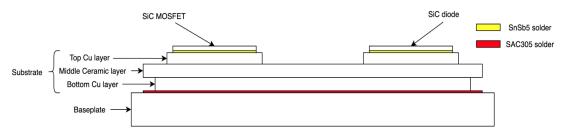

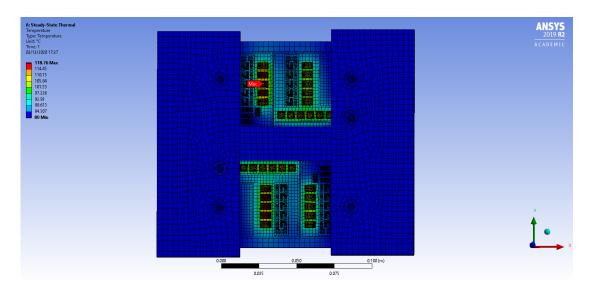

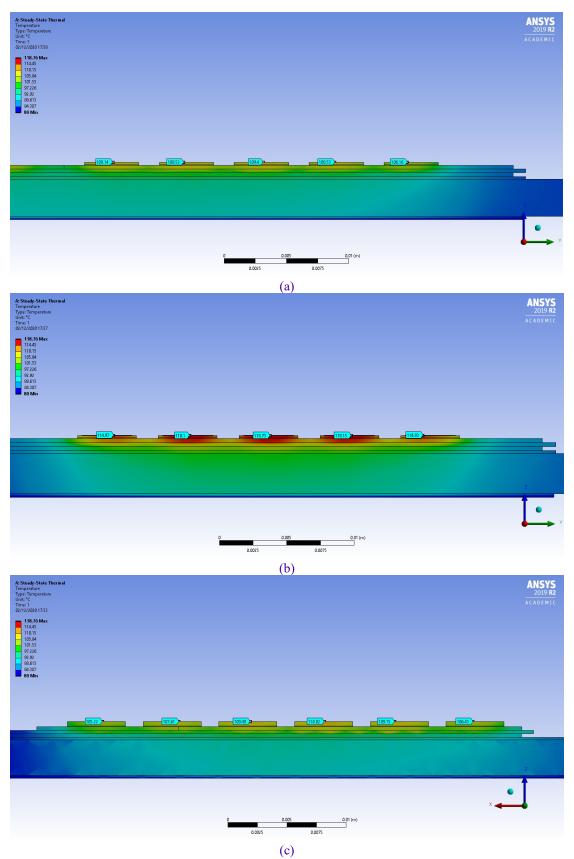

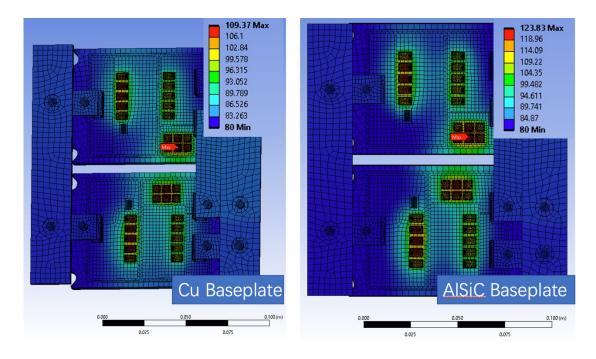

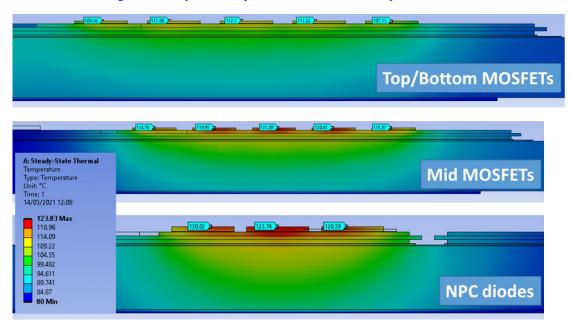

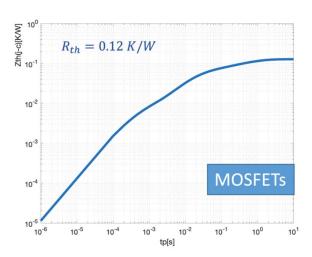

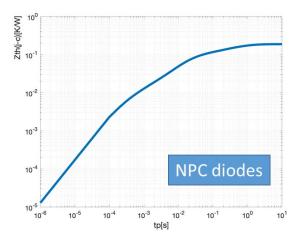

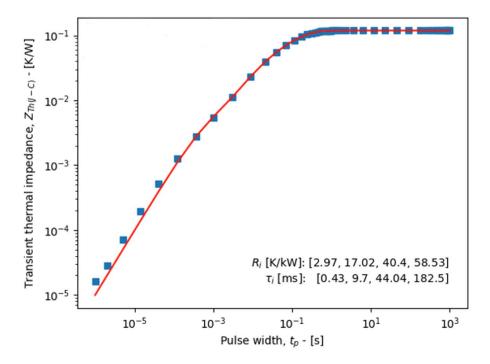

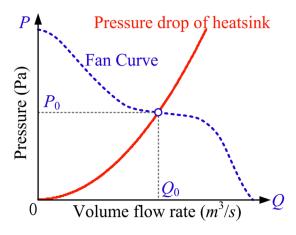

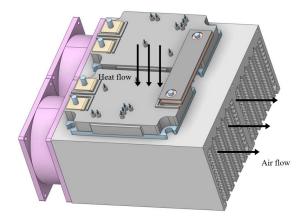

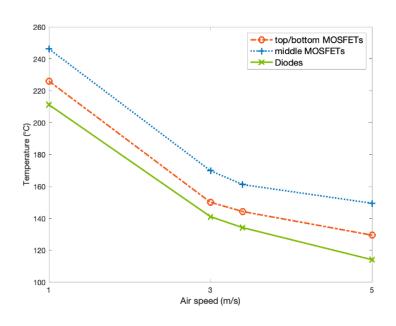

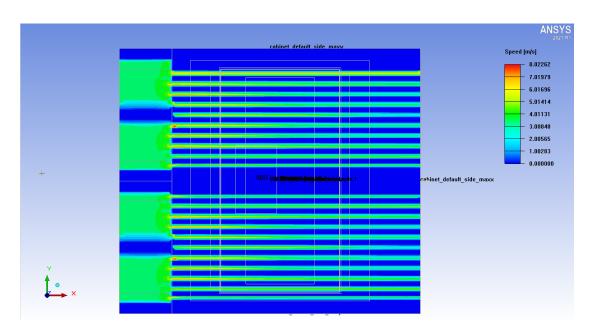

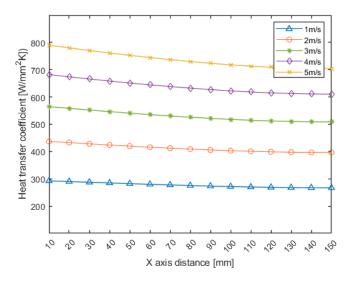

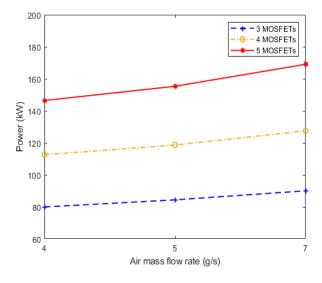

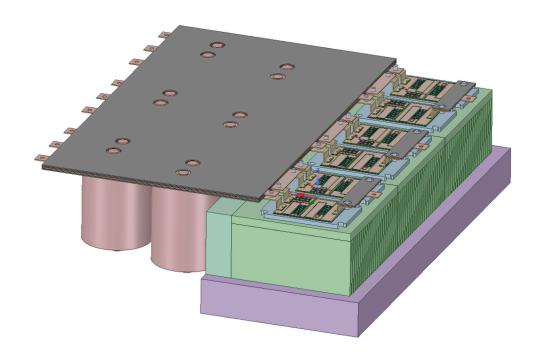

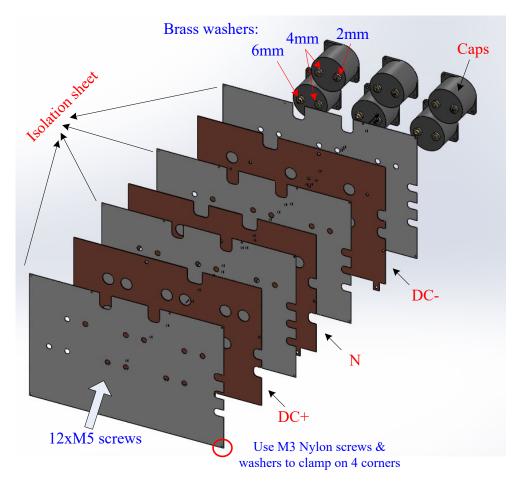

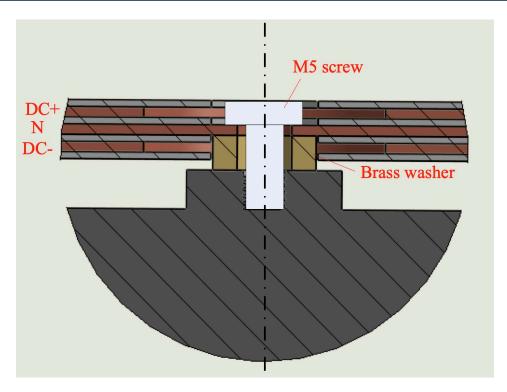

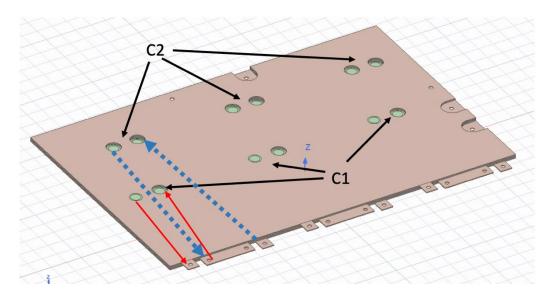

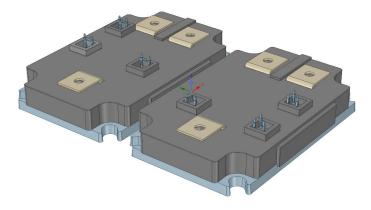

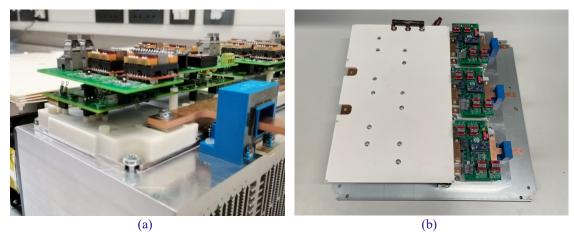

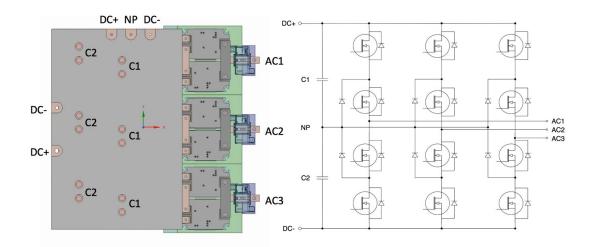

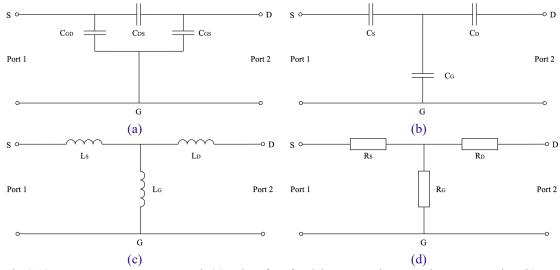

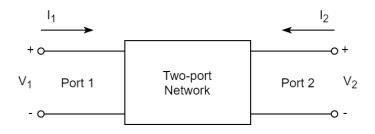

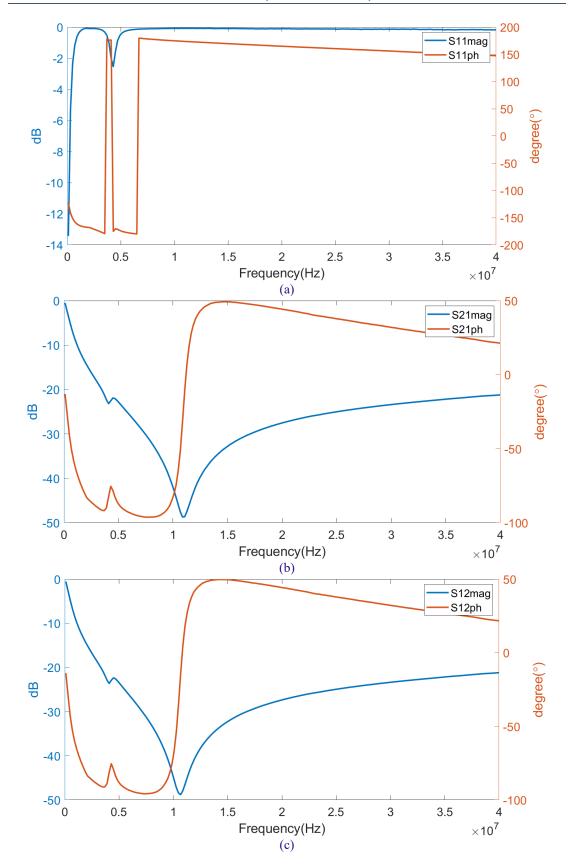

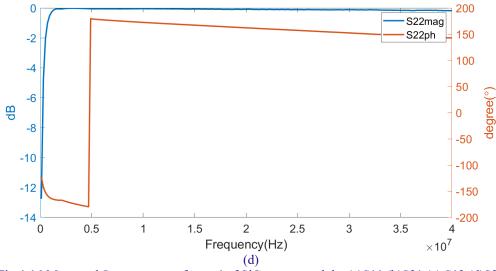

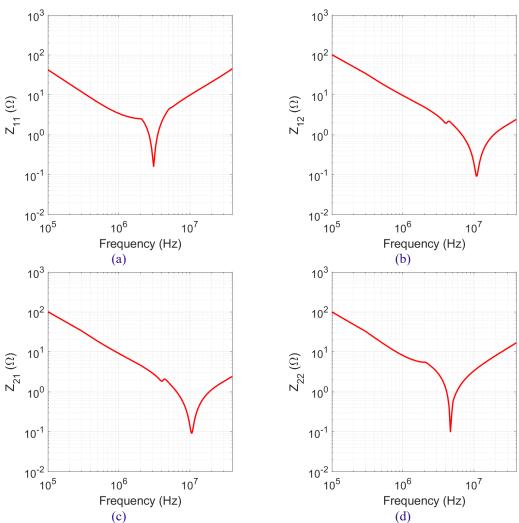

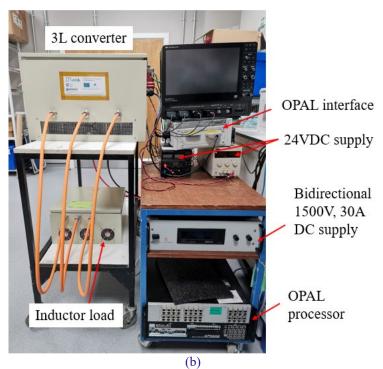

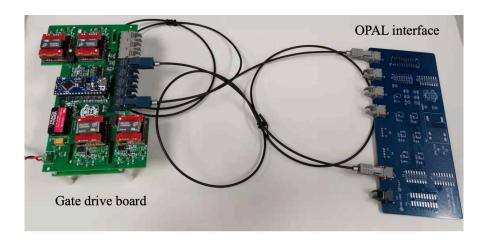

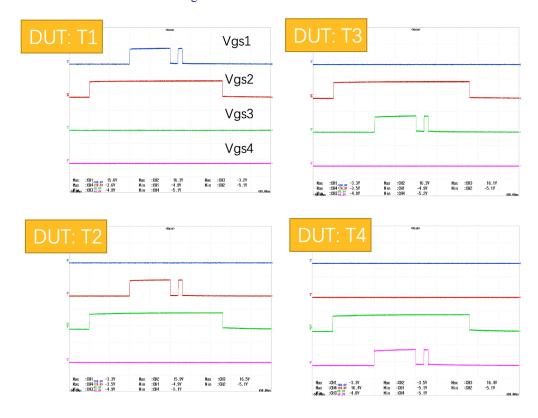

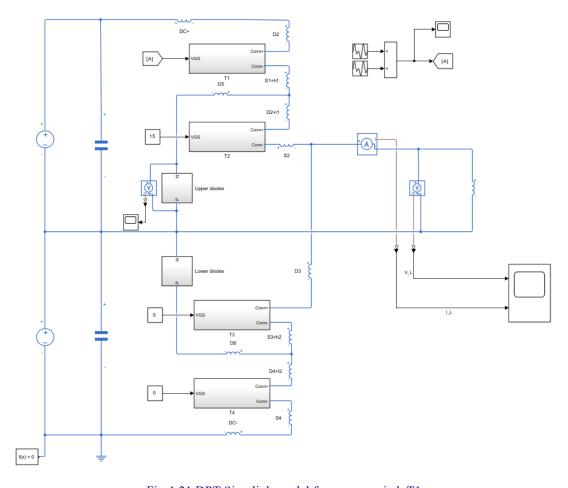

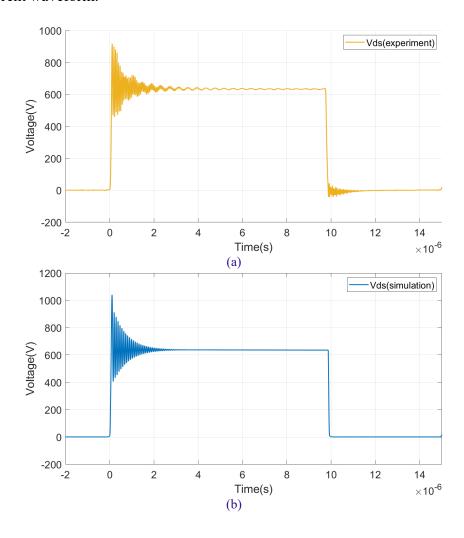

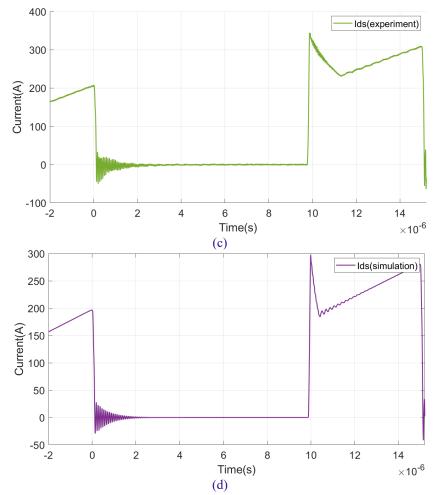

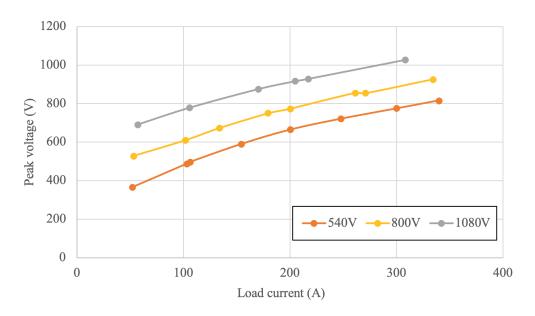

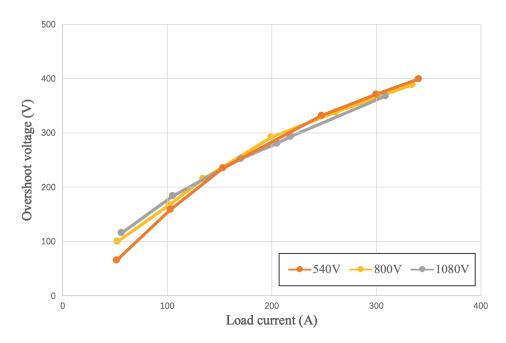

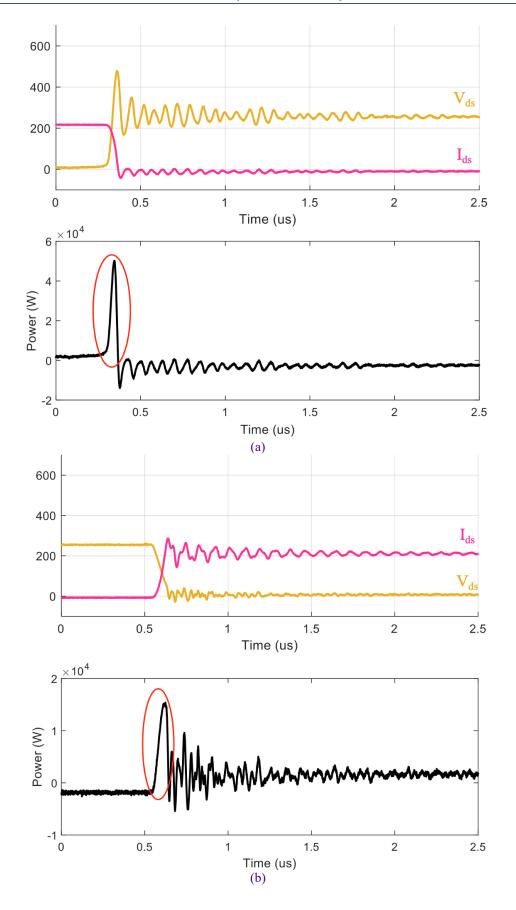

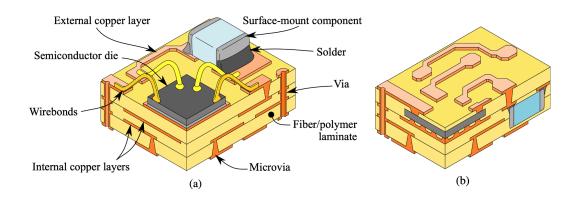

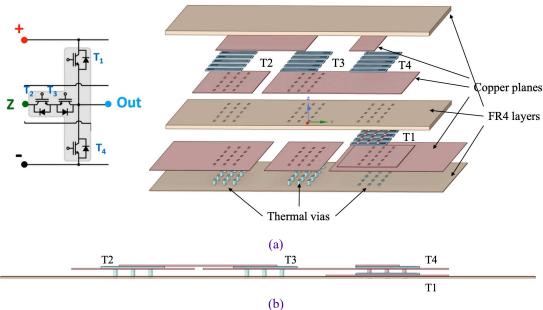

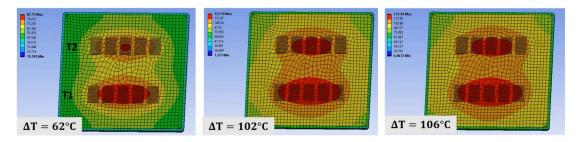

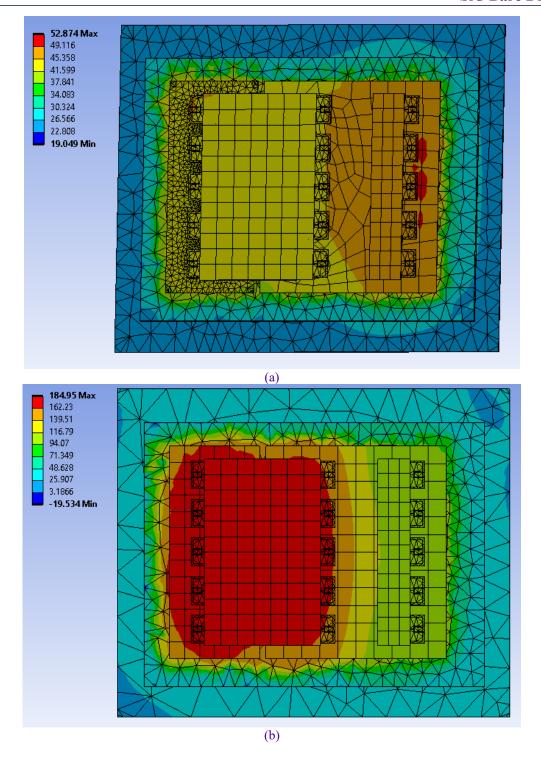

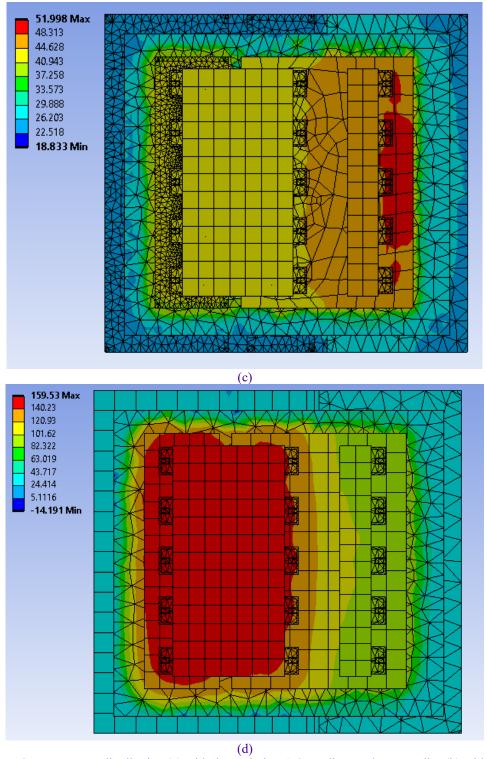

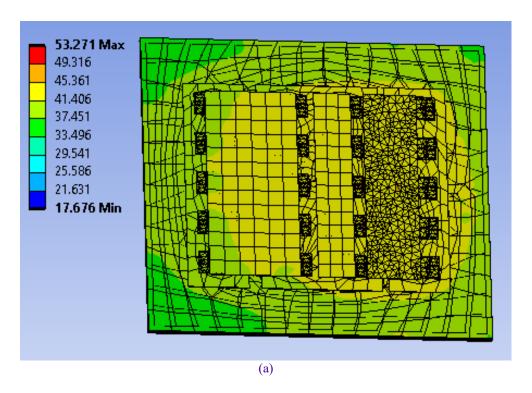

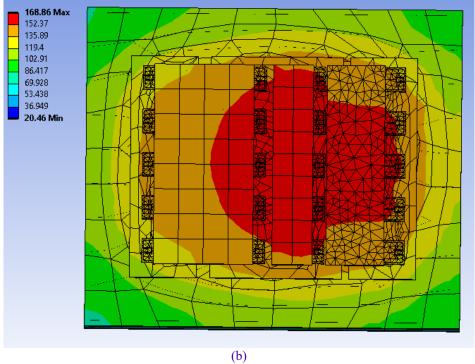

Most power modules use a heatsink-fan cooling system, but the geometry of the heatsink and fan operating point will affect the thermal performance. [135] proposed a model to predict the performance of the fan and verified the results through numerical simulations and experiments. The results show that using this model with a given thermal resistance can reduce weight to the greatest extent.