# A Contribution Towards Intelligent Autonomous Sensors Based on Perovskite Solar Cells and Ta<sub>2</sub>O<sub>5</sub>/ZnO Thin Film Transistors

A thesis submitted for the degree of Doctor of Philosophy by:

## Xiaoyao Song

Submitted to the Department of Electronic and Electrical Engineering

The University of Sheffield

DOCTOR OF PHILOSOPHY

June 2023

### **DECLARATION**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or processional qualification except as specified.

### **ACKNOWLEDGMENTS**

I would like to express my deepest gratitude to my supervisor, Prof. Maria Merlyne De Souza. Starting from the moment she offered me the opportunity to join her team, her continuous guidance, support, and encouragement, especially during difficult times, have been invaluable. Her constant encouragement and unparalleled expertise have served as the driving forces behind my academic journey, providing me with the motivation and knowledge to overcome numerous challenges.

I would also like to express my sincere thanks to my colleagues, Premlal Pillai, Ashwani Kumar, and Nagaditya Poluri. Their unwavering support and collaborative spirit have significantly enhanced my research experience. Their unique perspectives and thoughtful conversations have substantially contributed to my professional growth, making this journey all the more enjoyable.

I wish to acknowledge the significant roles played by the dedicated staff members Jon Wall, Jonathan D. Milner, Paul Haines, and Stephen Gricmanis. The completion of the experimental work and recovery from the fire accident would not have been possible without their consistent support.

Lastly, and most importantly, I dedicate this work to my parents, Guihua Wang and Youzhong Song. Their unconditional love and support have made my journey possible, and I am forever grateful for their unwavering faith in me. They have taught me the value of hard work and perseverance, lessons that have been fundamental throughout this journey.

To everyone mentioned and those unmentioned who have contributed to this journey, I extend my heartfelt thanks. This work stands as a testament to your invaluable contribution.

### ABSTRACT

Many broad applications in the field of robotics, brain-machine interfaces, cognitive computing, image and speech processing and wearables require edge devices with very constrained power and hardware requirements that are challenging to realize. This is because these applications require sub-conscious awareness and require to be always "on", especially when integrated with a sensor node that detects an event in the environment. Present day edge intelligent devices are typically based on hybrid CMOS-memristor arrays that have been so far designed for fast switching, typically in the range of nanoseconds, low energy consumption (typically in nano-Joules), high density and endurance (exceeding 10<sup>15</sup> cycles). On the other hand, sensory-processing systems that have the same time constants and dynamics as their input signals, are best placed to learn or extract information from them. To meet this requirement, many applications are implemented using external "delay" in the memristor, in a process which enables each synapse to be modeled as a combination of a temporal delay and a spatial weight parameter.

This thesis demonstrates a synaptic thin film transistor capable of inherent logic functions as well as compute-in-memory on similar time scales as biological events. Even beyond a conventional crossbar array architecture, we have relied on new concepts in reservoir computing to demonstrate a delay system reservoir with the highest learning efficiency of 95% reported to date, in comparison to equivalent two terminal memristors, using a single device for the task of image processing. The crux of our findings relied on enhancing our capability to model the unique physics of the device, in the scope of the current thesis, that is not amenable to conventional TCAD simulations. The model provides new insight into the redox characteristics of the gate current and paves way for assessment

of device performance in compute-in-memory applications. The diffusion-based mechanism of the device, effectively enables time constants that have potential in applications such as gesture recognition and detection of cardiac arrythmia.

The thesis also reports a new orientation of a solution processed perovskite solar cell with an efficiency of 14.9% that is easily integrable into an intelligent sensor node. We examine the influence of the growth orientation on film morphology and solar cell efficiency. Collectively, our work aids the development of more energy-efficient, powerful edge-computing sensor systems for upcoming applications of the IOT.

# TABLE OF CONTENTS ABSTRACT......5 LIST OF FIGURES ......12 Basics of Perovskite solar cells and Amorphous Oxide Thin Film Transistors 38 2.2.2 Basic structure and property of perovskite material ........................40 2.2.4 Perovskite solar cells: device structure and working principle.......47 2.2.6 Stability of perovskite solar cells......55 2.3 Amorphous Oxide Semiconductors ......56

| 2.3.1 Applications of AOS semiconductors                 | 56               |

|----------------------------------------------------------|------------------|

| 2.3.2 Basic structure and property of                    | amorphous oxide  |

| semiconductors                                           | 59               |

| 2.3.3 Deposition method of Amorphous Oxide               | Semiconductors63 |

| 2.3.4 Thin film Transistor architecture                  | 65               |

| 2.3.5 Principle of operation and physics of AOS          | S based TFTs66   |

| 2.4 Summary                                              | 70               |

| 2.5 References                                           | 71               |

| CHAPTER 3                                                | 84               |

| Artificial Neural Networks and Neuromorphic Comput       | ing84            |

| 3.1 Brain-inspired computing                             | 84               |

| 3.2 Artificial Neural Networks                           | 87               |

| 3.2.1 Feed-forward Neural Network                        | 88               |

| 3.2.2 Recurrent Neural Networks                          | 90               |

| 3.2.3 Backpropagation                                    | 91               |

| 3.2.4 Reservoir computing                                | 93               |

| 3.2.5 Spiking Neural Networks                            | 97               |

| 3.3 Emerging memory devices for neuromorphic application | cation98         |

| 3.3.1 Phase-change memories                              | 101              |

| 3.3.2 Oxide based random-access memories                 | 102              |

| 3.3.3 Ferroelectric memories                             | 104              |

| 3.3.4 Spin torque magnetic random access mem             | ories106         |

| 3.3.5 Electrolytes gate transistors                      | 107              |

| 3.3.6 Perovskite in memory applications                                                           |

|---------------------------------------------------------------------------------------------------|

| 3.3.7 Amorphous Oxide Semiconductors in memristor applications110                                 |

| 3.4 Summary                                                                                       |

| 3.5 References                                                                                    |

| CHAPTER 4                                                                                         |

| Solid Electrolyte-Gated Ta <sub>2</sub> O <sub>5</sub> /ZnO Field-Effect transistor: Fabrication, |

| modeling, and device mechanism                                                                    |

| 4.1 Introduction                                                                                  |

| 4.2 Device fabrication                                                                            |

| 4.3 Physics of Ta <sub>2</sub> O <sub>5</sub> /ZnO SE-FETs                                        |

| 4.4 Modeling of the SE-FET                                                                        |

| 4.4.1 Basic of the SE-FET model                                                                   |

| 4.4.2 Proposed gate current model                                                                 |

| 4.5 Summary                                                                                       |

| 4.6 References                                                                                    |

| CHAPTER 5                                                                                         |

| Off-state operation of SE-FETS                                                                    |

| 5.1 Introduction                                                                                  |

| 5.2 Off-state operation for logic in memory                                                       |

| 5.2.1 Basic device characteristics and operation149                                               |

| 5.2.2 Logic operations                                                                            |

| 5.2.3 Benchmark                                                                                   |

| 5.3 Using synaptic properties of SE-FETs for supervised learning in a                               |     |

|-----------------------------------------------------------------------------------------------------|-----|

| crossbar                                                                                            | 166 |

| 5.3.1 Crossbar implementation of the SE-FET                                                         | 166 |

| 5.3.2 Synaptic properties of SE-FETs and supervised learning                                        | 168 |

| 5.3.3 Crossbar arrangement of the SE-FET                                                            | 169 |

| 5.4 Conclusions                                                                                     | 171 |

| 5.5 References                                                                                      | 172 |

| CHAPTER 6                                                                                           | 175 |

| Reservoir computing using SE-FET as Reservoir                                                       | 175 |

| 6.1 Introduction.                                                                                   | 175 |

| 6.2 Reservoir computing using SE-FET                                                                | 175 |

| 6.3 Results and Discussion                                                                          | 180 |

| 6.4 Conclusions                                                                                     | 188 |

| 6.5 References                                                                                      | 189 |

| CHAPTER 7                                                                                           | 191 |

| Seed-assisted method for <202>-oriented CH <sub>3</sub> NH <sub>3</sub> PbI <sub>3</sub> perovskite | 191 |

| 7.1 Introduction.                                                                                   | 191 |

| 7.2 Experimental methods                                                                            | 192 |

| 7.3 Results and discussion                                                                          | 195 |

| 7.4 Summary                                                                                         | 209 |

| 7.5 References                                                                                      | 210 |

| CHAPTER 8                                                                                           | 216 |

| Conclusions and future works                                                                        | 216 |

| 8.1 Summary     | 216 |

|-----------------|-----|

|                 |     |

| 8.2 Future work | 217 |

|                 |     |

| 8.3 References  | 218 |

### LIST OF FIGURES

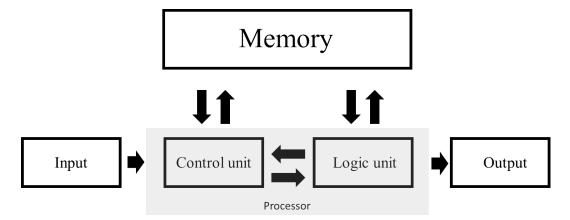

| Fig 1.1 Schematic diagram of Von Neumann architectures                                                                                                                                                                                                    | 27 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

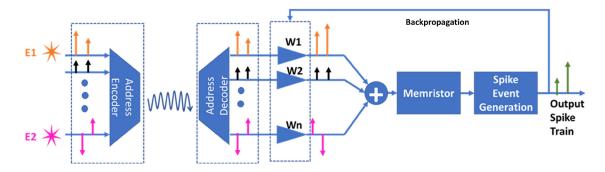

| Fig 1.2 Sensor connected IoT application                                                                                                                                                                                                                  | 29 |

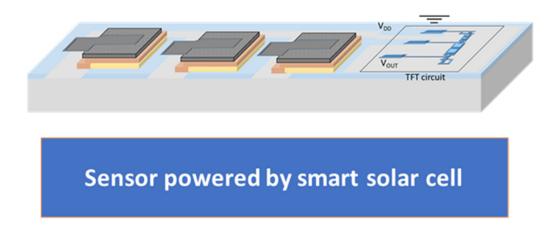

| Fig 1.3 Schematic diagram of of a integrated smart solar cell                                                                                                                                                                                             | 30 |

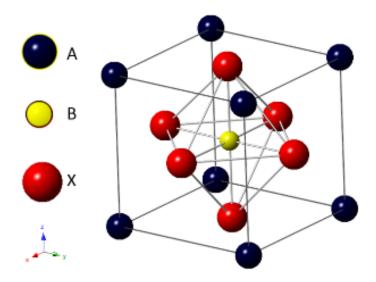

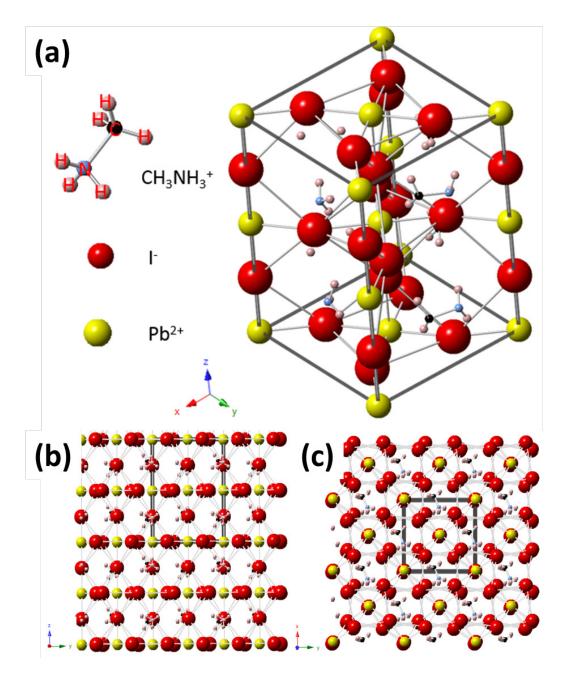

| Fig 2.1 Ideal perovskite crystal structure (cubic)                                                                                                                                                                                                        | 41 |

| Fig 2.2 (a) Unit cell of the tetragonal structure of CH <sub>3</sub> NH <sub>3</sub> PbI <sub>3</sub> . Here, A is CH <sub>3</sub> NH <sub>3</sub> <sup>+</sup> , B is Pb <sup>2+</sup> , and X is I <sup>-</sup> . (b) Side view and (c) top view of the |    |

| tetragonal CH <sub>3</sub> NH <sub>3</sub> PbI <sub>3</sub> structure                                                                                                                                                                                     | 43 |

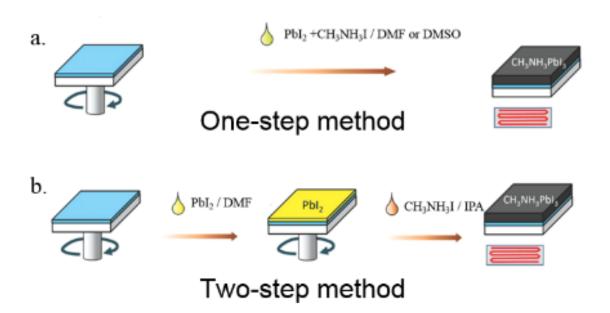

| Fig 2.3 One-step and two-step solution-based methods for CH <sub>3</sub> NH <sub>3</sub> PbI <sub>3</sub> deposition.                                                                                                                                     | 46 |

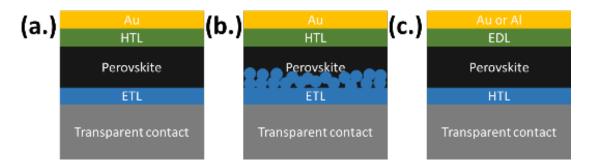

| Fig 2.4 (a) Conventional p-i-n, (b) mesoscopic p-i-n, and (c) inverted n-i-p                                                                                                                                                                              |    |

| perovskite solar cell structures                                                                                                                                                                                                                          | 49 |

| Fig 2.5 Structure of a p-n diode.                                                                                                                                                                                                                         | 50 |

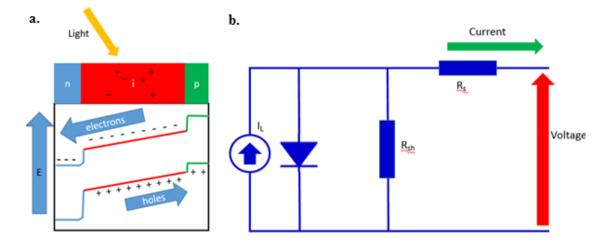

| Fig 2.6 (a) Schematic band diagram of a p-i-n diode and (b) circuit model of a solar cell.                                                                                                                                                                |    |

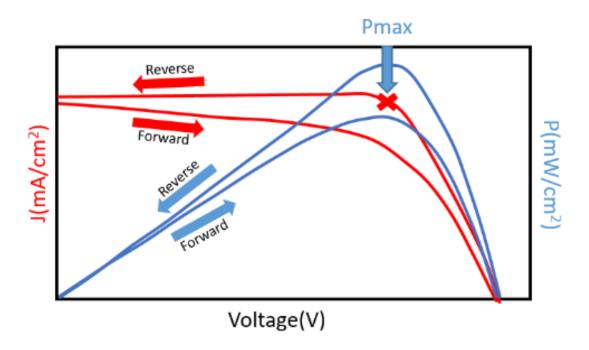

| Fig 2.7 Schematic J-V and P-V curves of a perovskite solar cell measured under simulated solar light at AM1.5                                                                                                                                             | 53 |

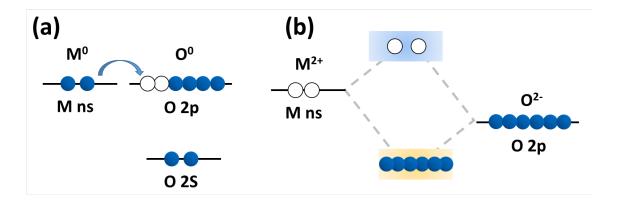

| Fig 2.8 Schematic electronic structures of ionic oxide semiconductors, (a) the    |

|-----------------------------------------------------------------------------------|

| charge transfer from metal to oxygen atoms, (b) the unoccupied s                  |

| orbitals forms the CBM and the fully occupied O 2p orbitals forms the             |

| VBM [99]60                                                                        |

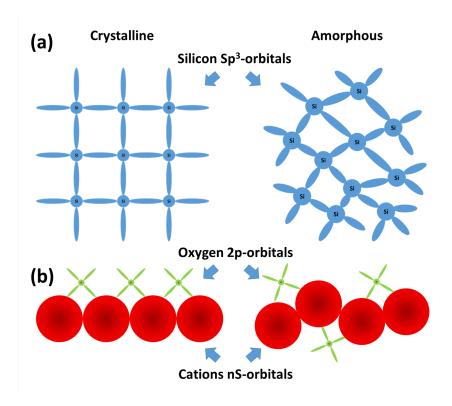

| Fig 2.9 Schematic drawing of the CBM atomic orbital and carrier transport         |

| paths of crystalline and amorphous Si (a) and (b) ionic oxide                     |

| semiconductors [99]6                                                              |

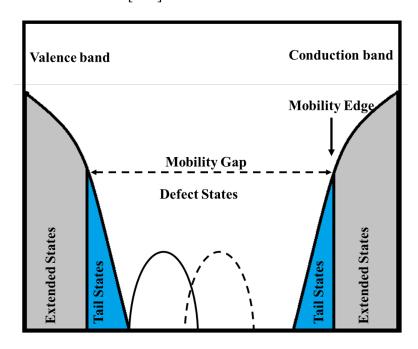

| Fig 2.10 Schematic drawing of amorphous semiconductors Density of States 62       |

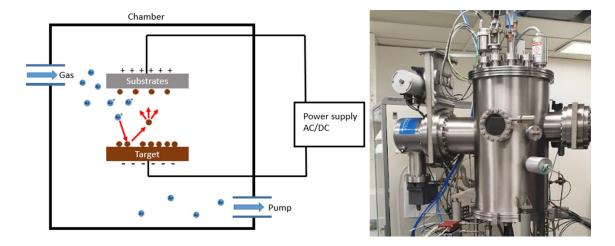

| Fig 2.11 Schematic diagram and photo of the Lesker sputter system used in this    |

| work64                                                                            |

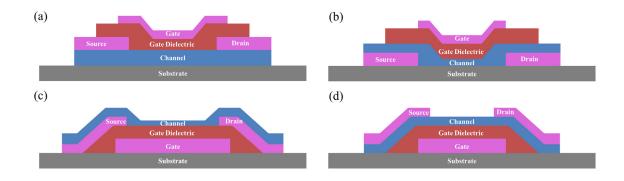

| Fig 2.12 Schematic diagram of basic TFT structures. (a) Top-gate coplanar (b)     |

| Top-gate staggered (c) Bottom-gate bottom coplanar and (d) Bottom-                |

| gate staggered60                                                                  |

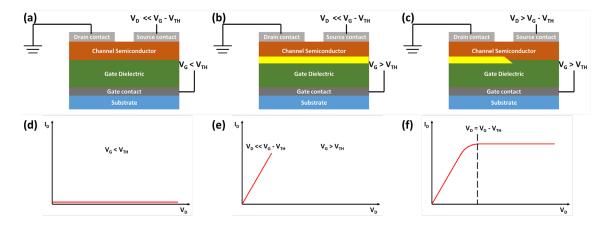

| Fig 2.13 Schematic diagram (a-c) and corresponding $I_D$ – $V_D$ curve (d-f) of a |

| TFT in (a) cut-off region, (b) linear region and (c) saturation region 68         |

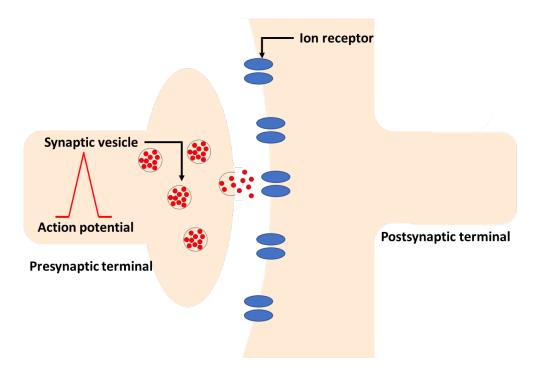

| Fig 3.1 Schematic diagram of a chemical synapse transmission [2]                  |

| Fig 3.2 Schematic diagram of (a) excitatory post synaptic current (EPSC) and      |

| (b) spike timing-dependent plasticity (STDP)87                                    |

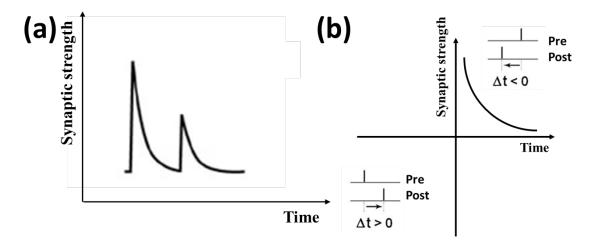

| Fig 3.3 Schematic diagram of hardware artificial neural network                   |

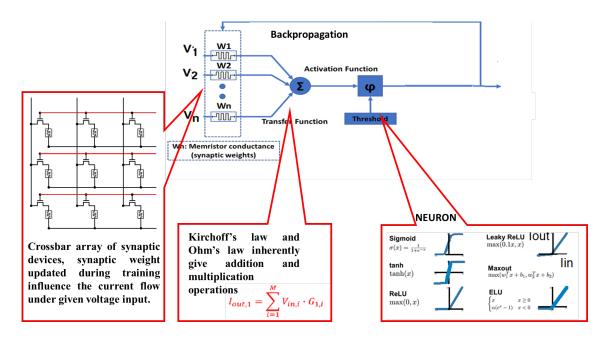

| Fig 3.4 Schematic diagram of a Feedforward Neural Network                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig 3.5 Schematic diagram of recurrent neural networks                                                                                                                                                               |

| Fig 3.6 Schematic diagram of the forward propagation (a) of the input and backward propagation (b) of the error.                                                                                                     |

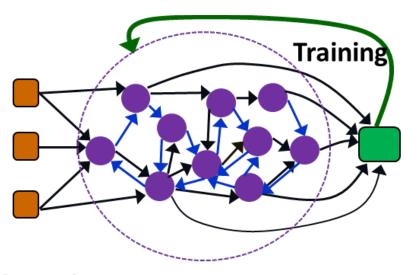

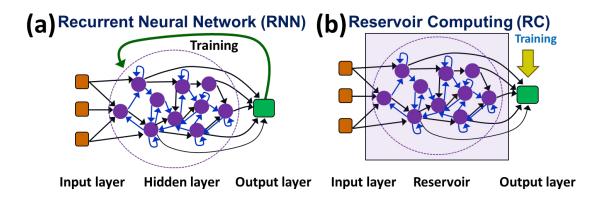

| Fig 3.7 (a) Traditional RNN training methods update all connection weights (red) during the training process. (b) In Reservoir Computing, only the activation function (Reservoir-to-output weights) are updated     |

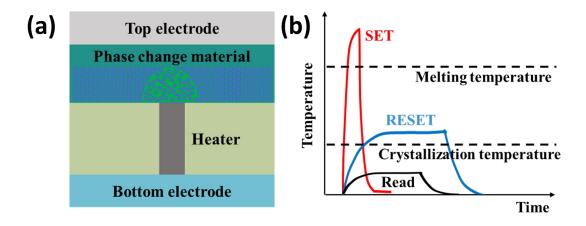

| Fig 3.8 (a) Schematic structure diagram and (b) illustration of the SET/RESET process of the Phase-change memories                                                                                                   |

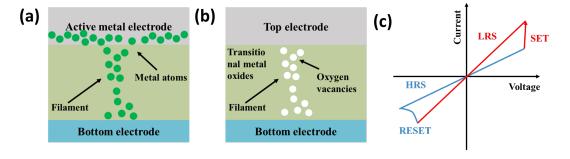

| Fig 3.9 Schematic structure diagram of ReRAM based on (a) active metal contact (CBRAM) and (b) transitional metal oxides (RRAM). (c) illustration of the SET/RESET process of the Oxide based random-access memories |

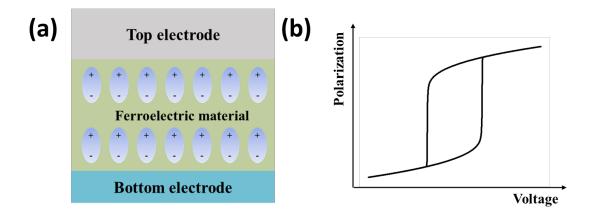

| Fig 3.10 (a) Schematic structure diagram of a FeRAM and (b) the polarization charge of the ferroelectric material                                                                                                    |

| Fig 3.11 (a) Schematic structure diagram of STT-MRAM based on (b) illustration of the R-V curve of the STT-MRAM                                                                                                      |

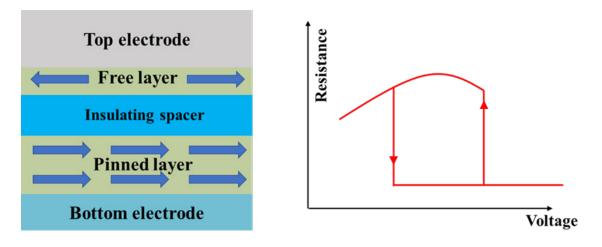

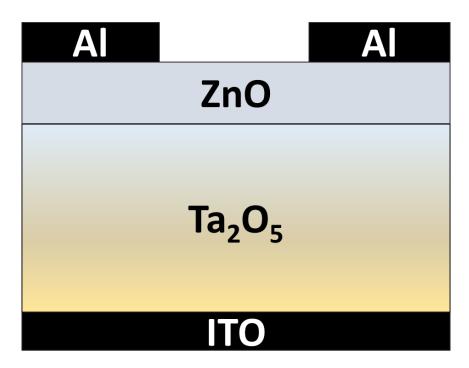

| Fig 4.1 Structure of a Ta2O5/ZnO TFT                                                                                                                                                                                 |

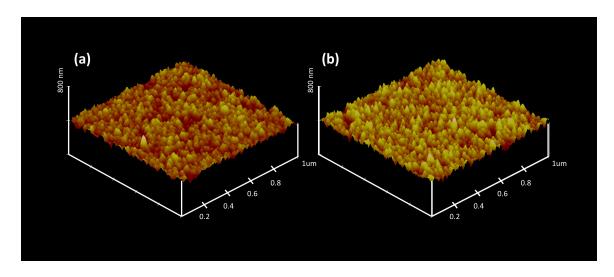

| Fig 4.2 AFM images of (a) 2/5nm Ta <sub>2</sub> O <sub>5</sub> and (b) 40nm ZnO deposited on 11O                 |

|------------------------------------------------------------------------------------------------------------------|

| substrates                                                                                                       |

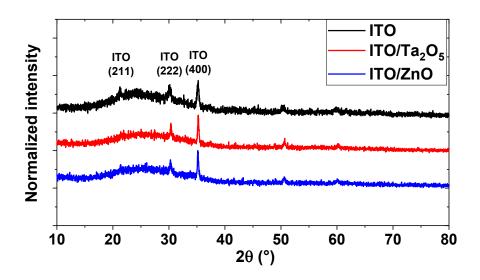

| Fig 4.3 XRD of Ta <sub>2</sub> O <sub>5</sub> and ZnO films and background ITO substrate127                      |

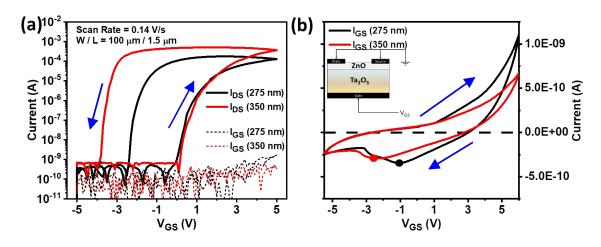

| Fig 4.4 (a) $I_{DS}\text{-}V_{GS}$ and (b) $I_{GS}\text{-}V_{GS}$ characteristics of the $Ta_2O_5/ZnO$ SE-FET at |

| room temperature. $I_{\rm GS}\text{-}V_{\rm GS}$ data were measured when both drain sources                      |

| of the device were grounded                                                                                      |

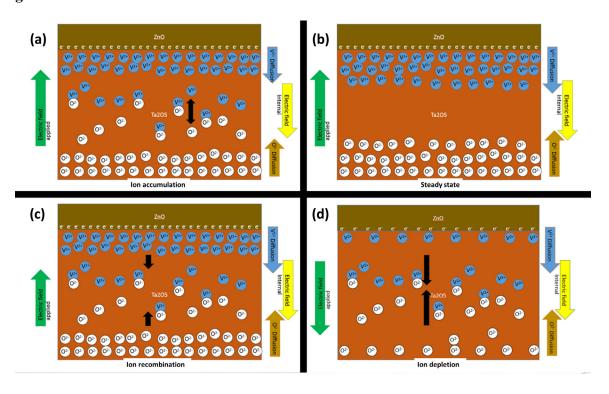

| Fig 4.5 The schematic depicts the motion of ions within the insulator of the                                     |

| device during the dual sweep                                                                                     |

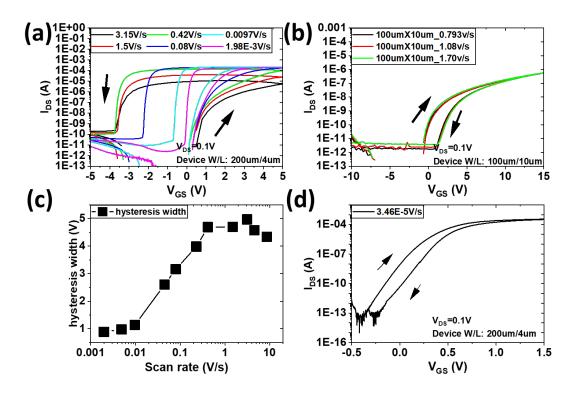

| Fig 4.6 Dual-sweep transfer characteristics I <sub>DS</sub> vs. V <sub>GS</sub> (a) SE-FET with 275-             |

| nm Ta <sub>2</sub> O <sub>5</sub> as gate oxide, and (b) devices with 60-nm SiN + 30-nm                          |

| Ta <sub>2</sub> O <sub>5</sub> . (c) Hysteresis width vs. scan rate at 100 nA. (d) Dual-sweep I <sub>DS</sub>    |

| vs. V <sub>GS</sub> of a 275-nm Ta <sub>2</sub> O <sub>5</sub> device at near steady state                       |

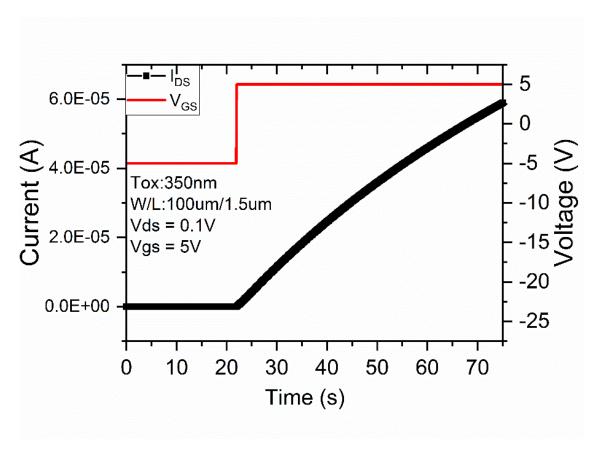

| Fig 4.7 Time-dependent $I_{DS}$ when switching from a constant $V_{GS}$ of -5 V to a                             |

| constant V <sub>GS</sub> of +5 V                                                                                 |

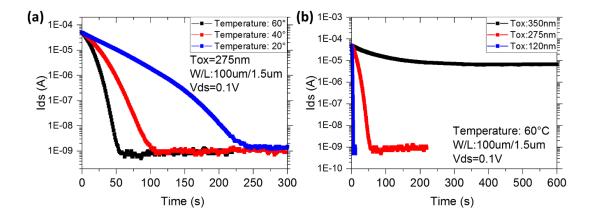

| Fig 4.8 (a) Ids decay of devices with a gate insulator thickness of 275 nm at                                    |

| 20°C, 40°C, and 60 °C. (b) Ids decay of devices with a gate insulator                                            |

| thickness of 120 nm, 275 nm, or 350 nm at 60°C                                                                   |

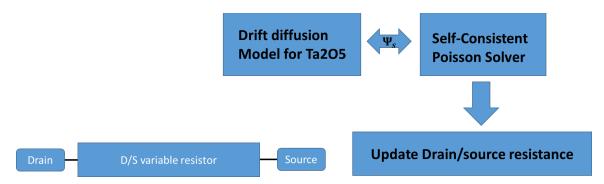

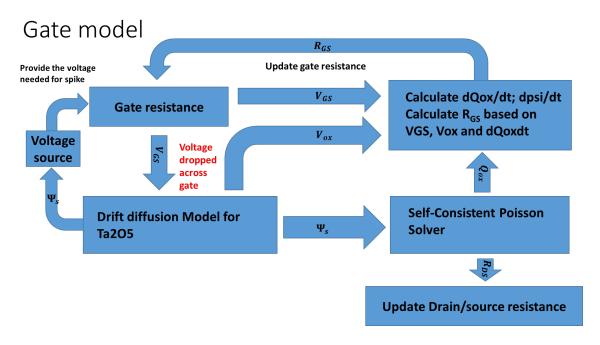

| Fig 4.9 Scheme of the Simulink model based on the original SE-FET proposed                                       |

| by Dr. Ashwani Kumar in [1]                                                                                      |

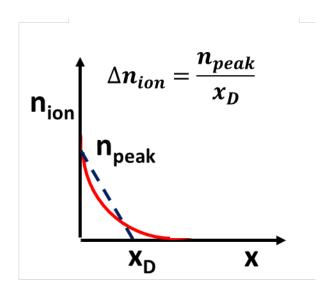

| Fig 4.10 Scheme for linearly approximating the oxide ion concentration (n <sub>peak</sub> ) |

|---------------------------------------------------------------------------------------------|

| decay [1]                                                                                   |

| Fig 4.11 Scheme of the Simulink model of the SE-FET with the gate current                   |

| model                                                                                       |

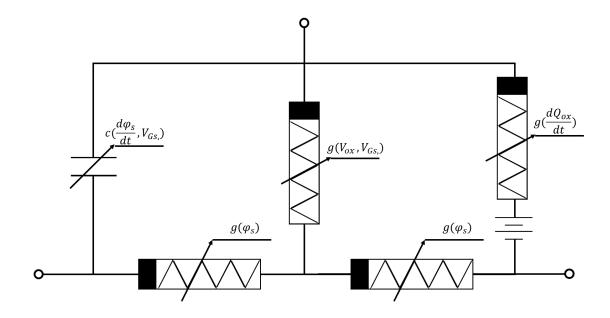

| Fig 4.12 Equivalent circuit model of the SE-FET.                                            |

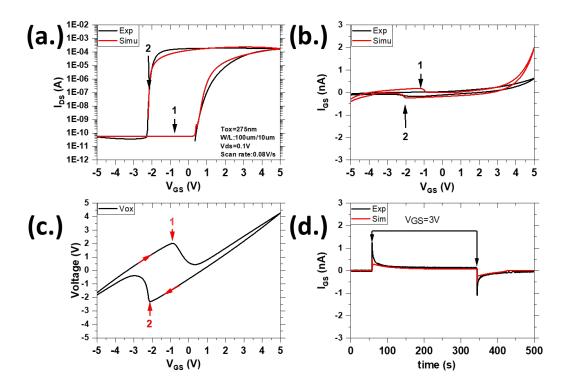

| Fig 4.13 Comparison of (a) measured/simulated transfer I-V curves at a scan                 |

| rate of 0.08 V/s and (b) gate current characteristics of the device at                      |

| steady state. (c) Simulated Vox corresponding to the transfer I-V curve.                    |

| (d) Comparison of the measured/simulated time-dependent gate current                        |

| characteristics at a constant voltage of 3 V                                                |

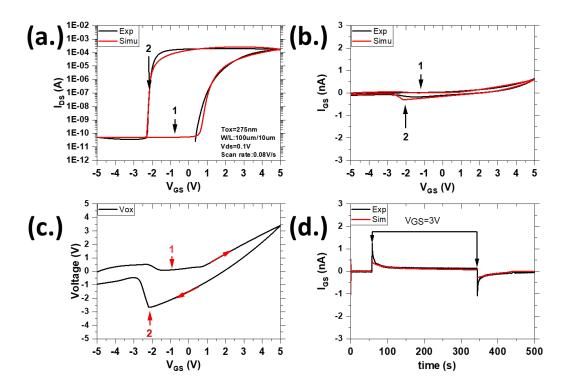

| Fig 4.14 Comparison of (a) measured/simulated transfer I-V curves at a scan                 |

| rate of 0.08 V/s and (b) gate current characteristics of the device at                      |

| steady state. (c) Simulated Vox and Ys for the transfer I-V curve. (d)                      |

| Comparison of measured/simulated time- dependent gate current                               |

| characteristics at a constant voltage of 3 V                                                |

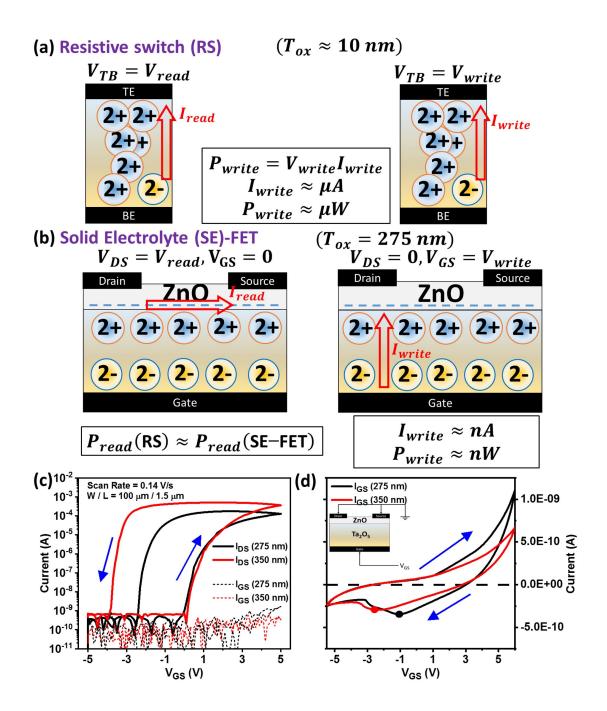

| Fig 5.1 Mechanism of read and write operations in (a) resistive switching and               |

| (b) SE-FETs, demonstrating the possibility of low power consumption                         |

| during writing in SE-FETs. (c) IDS-VGS and (d) IGS-VGS curves of                            |

| the basic device at room temperature                                                        |

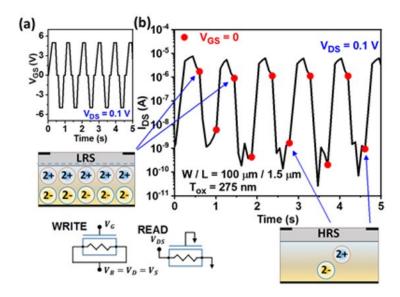

| Fig 5.2 (a) Gate bias pulses at 1 Hz applied to the device with a constant VDS = |

|----------------------------------------------------------------------------------|

| 0.1 V. (b) Measured drain current characteristics as a function of time,         |

| exhibiting two resistance states (HRS and LRS) as the gate bias crosses          |

| zero, indicated by red circles                                                   |

| Fig 5.3 (a) Scheme of 1-Hz bias pulses for VGS and VDS, where VDS = 0 and        |

| VGS ≠ 0 during the write operation and vice versa during the read                |

| operation, ensuring that the write and read operations are exclusive. (b)        |

| Drain current measured during the read operation (VDS = $+0.1 \text{ V}$ ),      |

| indicating the presence of two resistance states (HRS and LRS)                   |

| separated by three orders of magnitude, with a small variance (inset).           |

| (c) Measured gate current characteristics showing that the power                 |

| consumption remains limited to the nanowatt level during the write               |

| operation, as the drain current remains zero                                     |

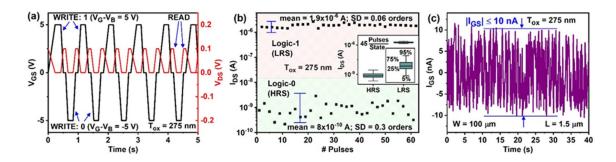

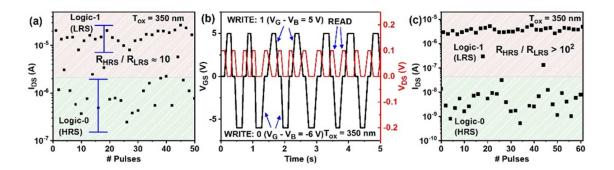

| Fig 5.4 (a) Drain current measurements of a device with a 350-nm-thick oxide     |

| layer for the pulse scheme shown in Fig. 4.3(a). (b) Alternate pulse             |

| scheme at 1.5 Hz, with VGS equal to $+5$ V and $-6$ V for switching              |

| between the LRS and HRS and (c) corresponding drain current                      |

| measurements                                                                     |

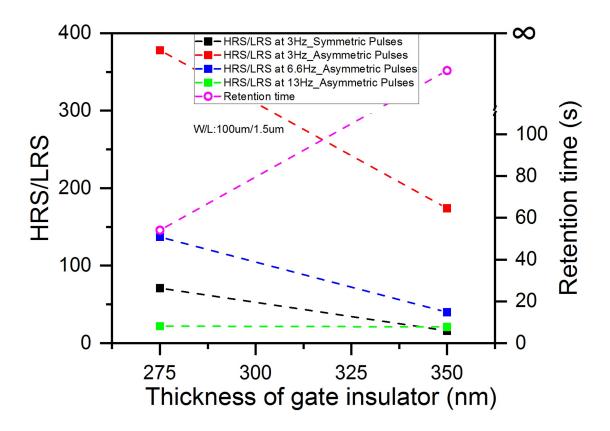

| Fig 5.5 Gate insulator thickness vs. HRS/LRS ratio for asymmetric pulses (275    |

| nm: +6 V/-5 V for set/reset; 350 nm: +5 V/-6 V for set/reset) (left axis)        |

| and retention time at 60°C (right axis)                                          |

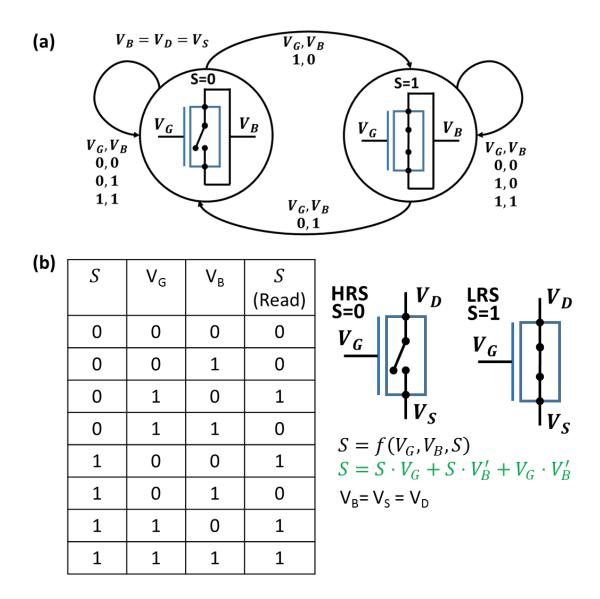

| Fig 5.6 (a) Finite-state diagram of the device, where I for either VG or VB            |

|----------------------------------------------------------------------------------------|

| indicates application of a positive bias and $S = 0$ or 1 indicates the LRS            |

| or HRS, respectively. (b) Truth table describing the state transition 159              |

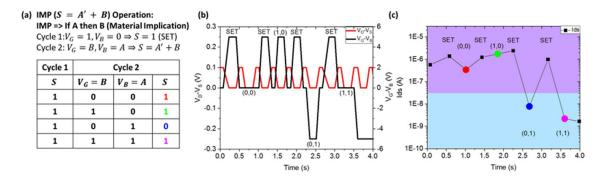

| Fig 5.7 (a) Steps to perform IMP (if A then B) logic operation and a                   |

| corresponding truth table. (b) Applied gate and drain bias pulses. (c)                 |

| Measured drain current for each step indicated in (a). $W \times L =$                  |

| $100 \times 1.5 \ \mu\text{m}$ 2, Tox = 275 $\mu\text{m}$ , frequency = 2 Hz           |

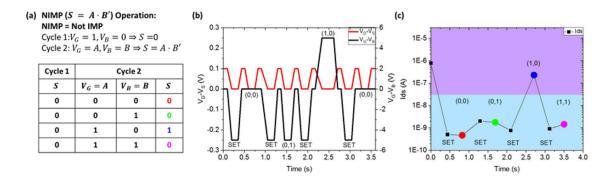

| Fig 5.8 (a) Steps to perform the NIMP logic operation (S=A·B') and a                   |

| corresponding truth table. (b) Applied gate and drain bias pulses. (c)                 |

| Measured drain current for each step indicated in (a). $W \times L =$                  |

| $100 \times 1.5 \ \mu\text{m2}$ , Tox = 275 $\mu\text{m}$ , frequency = 2 Hz           |

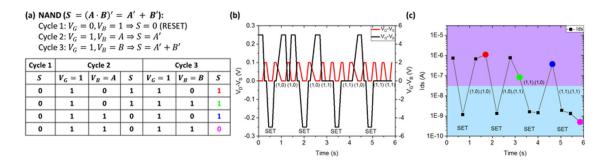

| Fig 5.9 (a) Steps to perform a two-input NAND ( $S = A' + B'$ ) logic operation        |

| and a corresponding truth table. (b) Applied gate and drain bias pulses.               |

| (c) Drain current measured for each of the steps shown in (a). $W \times L =$          |

| $100 \times 1.5 \ \mu\text{m}$ 2, Tox = 275 $\mu\text{m}$ , frequency = 2 Hz           |

| Fig 5.10 (a) Steps to perform a two-input NOR (S = $A' \cdot B'$ ) logic operation and |

| a corresponding truth table. (b) Applied gate and drain bias pulses. (c)               |

| Measured drain current for each step shown in (a). $W \times L =$                      |

| $100 \times 1.5 \mu\text{m2}$ , Tox = 275 $\mu\text{m}$ , frequency = 2 Hz             |

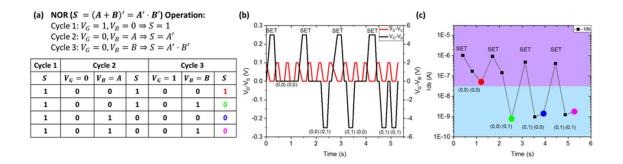

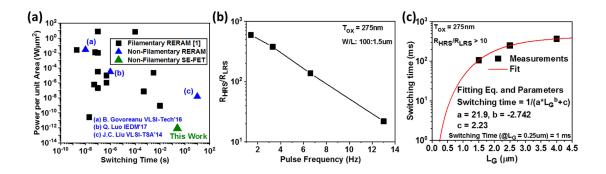

| Fig 5.11 (a) Benchmarking the power consumption per unit device area vs.                    |

|---------------------------------------------------------------------------------------------|

| switching time based on experimental data reported in [1] and our                           |

| current measurements. (b) Measured HRS/LRS ratio vs. input pulse                            |

| frequency and (c) switching time vs. gate length L. The fit to data                         |

| predicts a switching time of 150 ns for L = 20 nm                                           |

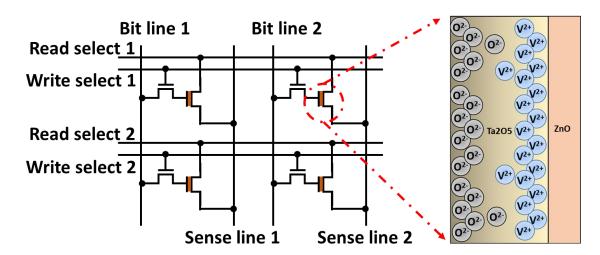

| Fig 5.12 Schematic of a $2 \times 2$ crossbar consisting of an SE-FET and a depletion-      |

| mode MOSFET with two control lines for selecting individual cells and                       |

| the Ta <sub>2</sub> O <sub>5</sub> /ZnO SE-FET                                              |

| Fig 5.13 (a) Bias conditions during the read and write operations. Here, $V_{\text{th}}$ is |

| the threshold voltage of the MOSFET, $V_m$ is the refresh voltage (0.5 V),                  |

| f(ISL) is the output of the activation function (sigmoid) (Eq. (5.2)),                      |

| $V_{\text{Write}}$ is the write voltage for potentiation (0 V + 4 V), and the read          |

| voltage is $V_{Read} = 0.2\ V.$ (b) Truth table for OR and AND and the                      |

| corresponding condition of the sense line                                                   |

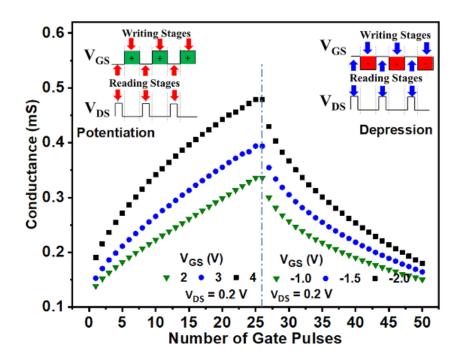

| Fig 5.14 Conductance measured after sequential gate bias pulses of different                |

| amplitudes and polarities, as shown in the inset                                            |

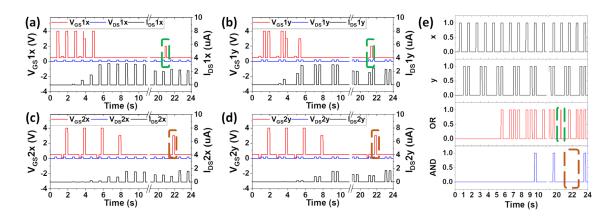

| Fig 5.15 Simulated bias and read currents of devices (a) 1x and (b) 1y in the               |

| crossbar during training for OR operation and devices (c) 2x and (d) 2y                     |

| for AND operation. (e) Simulated output of the activation function for                      |

| OR and AND logic operations, with respect to inputs X and Y. Errors                         |

| at 20 and 22 s due to volatility are refreshed by application of a gate        |

|--------------------------------------------------------------------------------|

| voltage of 2–3 V                                                               |

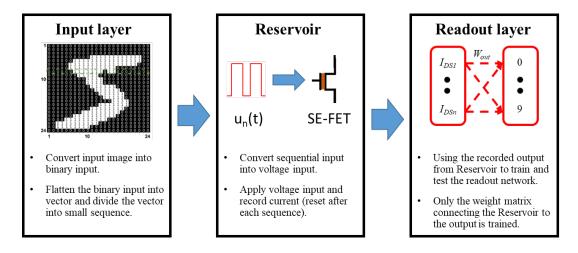

| Fig 6.1 Scheme of the SE-FET-based reservoir framework [1]                     |

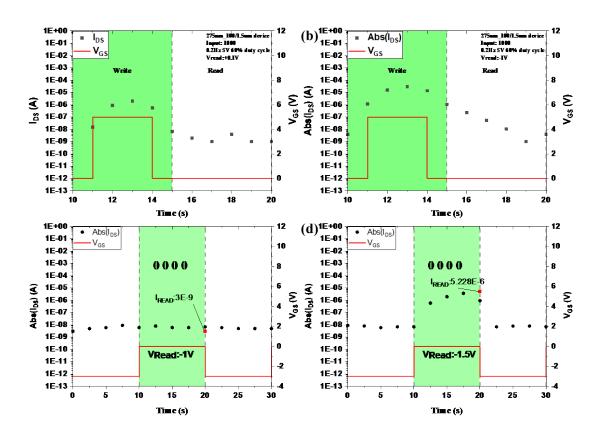

| Fig 6.2 Read current of the SE-FET following a single pulse using +0.1V (a)    |

| and -1.0V (b) of read voltage. The -1.0V read voltage helps to maintain        |

| a more linear and enriched decay state, without offsetting the decay or        |

| writing to the devices. The read current of the SE-FET after reset with        |

| 0V gate votlage using -1V (c) and -1.5V (d) read voltage is also shown.        |

| Utilizing -1V read voltage keeps the device in the off state after a reset     |

| without additional input from reading itself, while a -1.5V read voltage       |

| is sufficient to force the device into a potentiation state by the negative    |

| read voltage                                                                   |

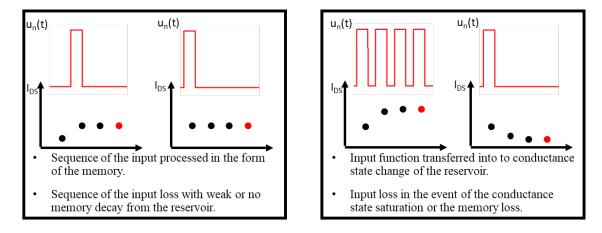

| Fig 6.3 Conductance state saturation and complete memory loss results in       |

| information between input function and reservoir. Weak or no memory            |

| loss results a lost in temporal order of the sequential input                  |

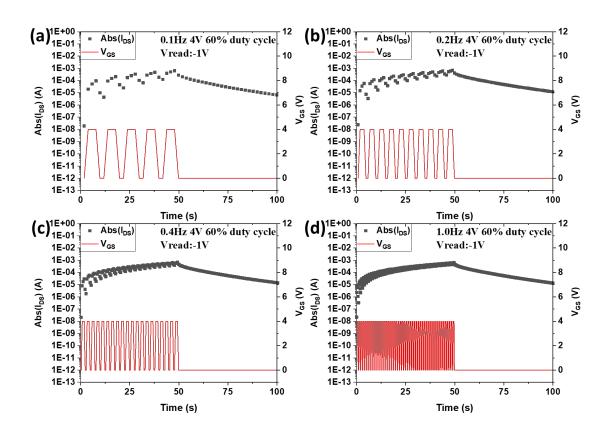

| Fig 6.4 Potentiation conductance of the SE-FET from 0.1 to 1Hz                 |

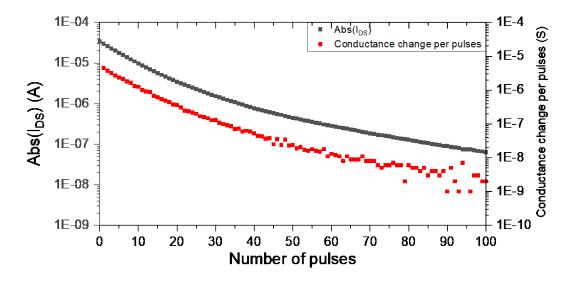

| Fig 6.5 Conductance state decay and conductance state change per pulses record |

| at 0.4 Hz frequency pulses                                                     |

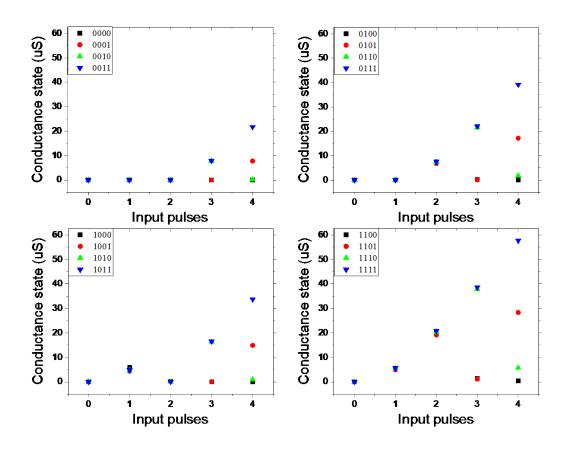

| Fig 6.6 Example of the recorded SE-FET output from one of the devices used           |

|--------------------------------------------------------------------------------------|

| as the reservoirs output database to train and test the network. Devices             |

| recorded at 0.4Hz with 3V 60% duty cycle pulses                                      |

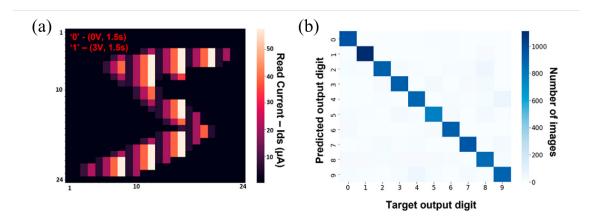

| Fig 6.7 (a) Example of the heat map from the SE-FET response to digit 5 using        |

| data based on the measured results showing Fig 6.8. (b) Confusion                    |

| matrix showing the experimentally obtained classification results of the             |

| SE-FET-based reservoir versus the correct outputs. Ankit Gaurav                      |

| achieved an overall recognition rate of 91.19% using 7-fold cross-                   |

| validation [6]                                                                       |

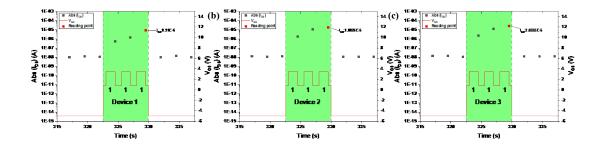

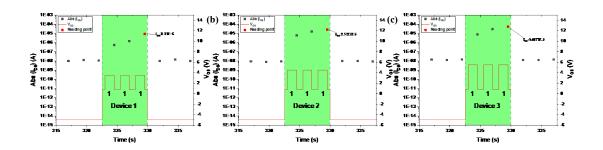

| Fig 6.8 Response of device 1 (a), 2 (b) and 3 (c) when subjected to same input       |

| 111 with same 3.5V pulses. The devices conductivity varies due to                    |

| inherent device-to-device variation                                                  |

| Fig 6.9 Response of device 1 (a), 2 (b) and 3 (c) when subjected to input 111        |

| with 3.5V, 4.5V and 5.5V pulses. The devices conductivity varies due                 |

| to inherent device-to-device variation and the different input function 187          |

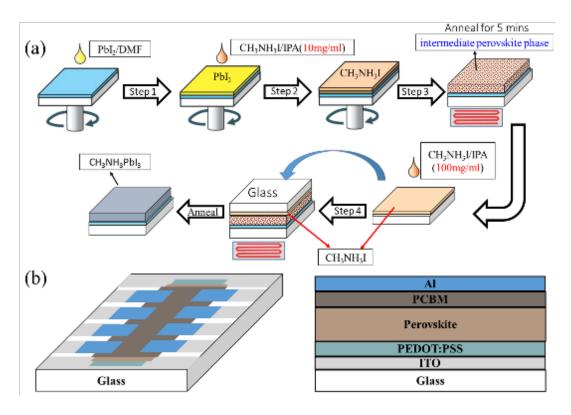

| Fig 7.1 (a) Process flow diagram of the seed-assisted combined method for            |

| <202>-oriented perovskites. (b) Fabricated planar device structures 194              |

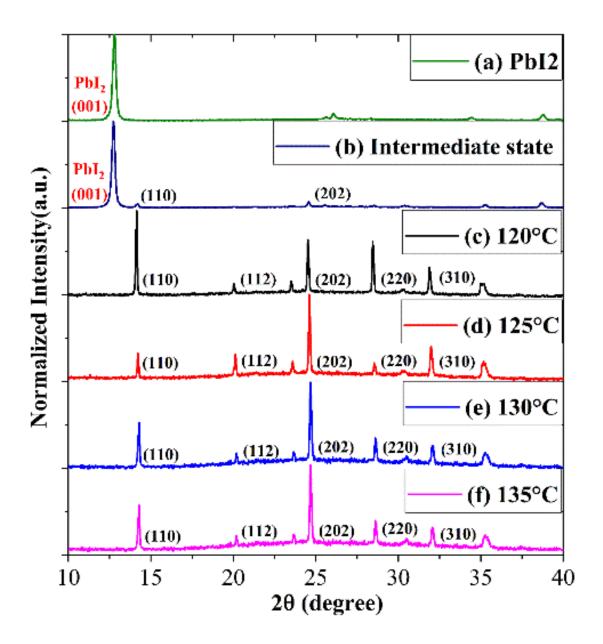

| Fig 7.2 XRD of the (a) PbI <sub>2</sub> film, (b) intermediate seed layer, and (c-f) |

| perovskite film after complete conversion from the intermediate film via             |

| the solid-state process at temperatures of 120°C to 135°C                            |

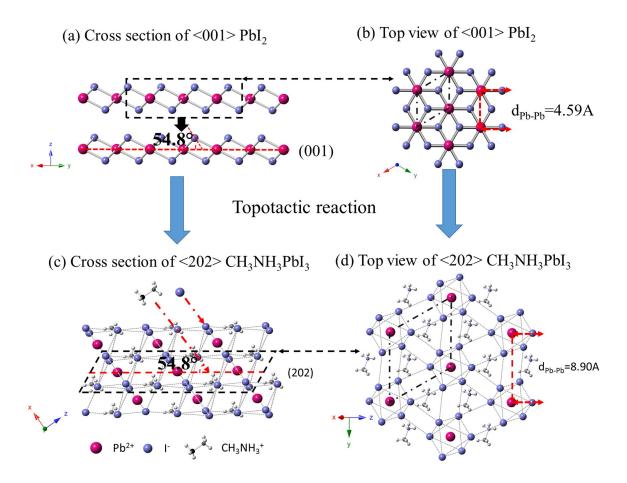

| g 7.3 (a) Cross-section and (b) top view of <001>-oriented Pbl <sub>2</sub> . (c) Cross-                 |

|----------------------------------------------------------------------------------------------------------|

| section and (d) top view of <202>-oriented CH3NH3PbI3 formed via a                                       |

| topotactic reaction process                                                                              |

|                                                                                                          |

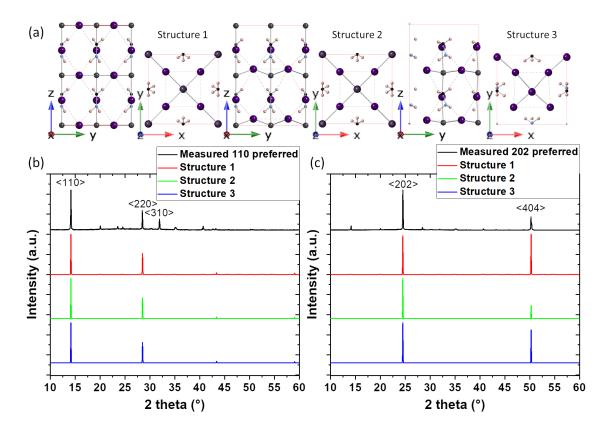

| g 7.4 (a) Three structures used in this study (viewed from the <100> and                                 |

| <001> directions). Structure 1 is an ideal tetragonal structure, Structure                               |

| 2 is based on a unit cell that contains all MA <sup>+</sup> cations aligned along                        |

| <001>[27], and Structure 3 is obtained by performing a DFT relaxation                                    |

| of Structure 2. (b, c) Measured and simulated XRD of the (b) <110>-                                      |

| and (c) <202>-oriented perovskite films from Structures 1–3                                              |

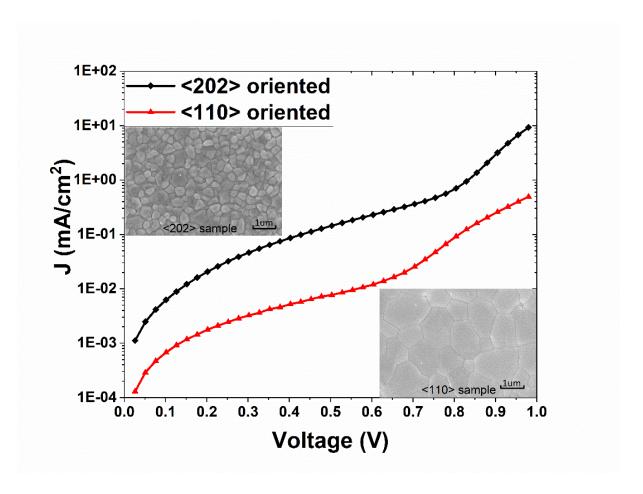

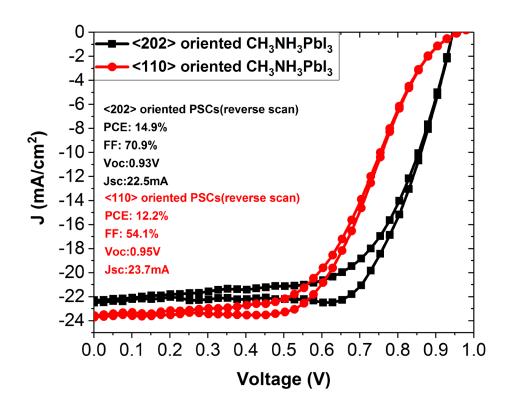

| g 7.5 J–V curves of perovskite solar cells with <110>- and <202>-oriented                                |

| perovskite measured in a dark environment. Corresponding SEM                                             |

| images of each sample are shown in the inset, where the <202>- and                                       |

| <110>-oriented perovskites show a grain size of approximately 0.4 μm                                     |

| and 1.2 µm, respectively                                                                                 |

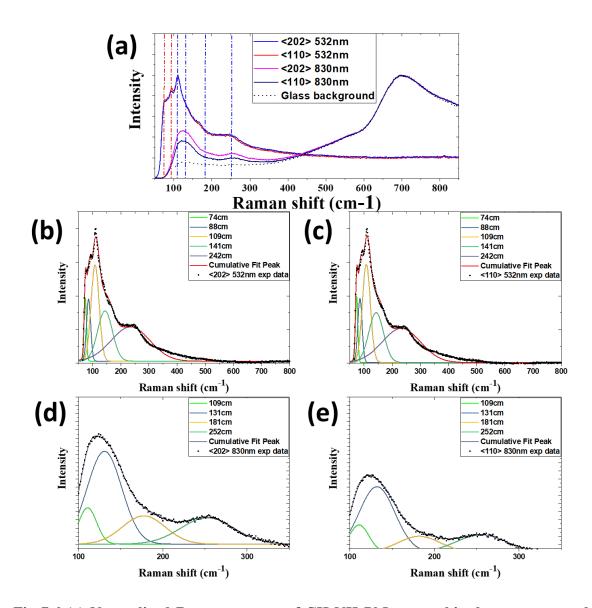

| g 7.6 (a) Normalized Raman spectra of CH <sub>3</sub> NH <sub>3</sub> PbI <sub>3</sub> perovskite layers |

| measured using excitation at 532 nm and 830 nm. The vertical dashed                                      |

| lines indicate the peak positions of the Raman band, obtained by fitting                                 |

| the spectra with Gaussian curves. (b, c) Raman spectra obtained for 532-                                 |

| nm excitation, fitted with Gaussian curves. (d, e) Raman spectra                                         |

| obtained for 830-nm excitation fitted with Gaussian curves                                               |

| Fig 7.7. | J–V curves   | of perovskite | solar cells | with <110> | and <202> | oriented |     |

|----------|--------------|---------------|-------------|------------|-----------|----------|-----|

| р        | erovskites i | under AM1.50  | simulated   | sunlight   |           | •••••    | 209 |

### LIST OF PUBLICATIONS

### **Journals:**

- (1) Gaurav, A.; Song, X.; Manhas, S.; Gilra, A.; Vasilaki, E.; Roy, P.; De Souza, M. M. Reservoir Computing for Temporal Data Classification Using a Dynamic Solid Electrolyte ZnO Thin Film Transistor. *Front. Electron.* 2022, 3. https://doi.org/10.3389/felec.2022.869013.

- (2) Kumar, A.; **Song, X**.; De Souza, M. M. Necessary Conditions for Steep Switching in a Constant Resistor-Capacitor RCFET. *MRS Adv.* **2021**, *6* (21), 540–545. https://doi.org/10.1557/s43580-021-00119-9.

- (3) Song, X.; Kumar, A.; De Souza, M. M. Off-State Operation of a Three Terminal Ionic FET for Logic-in-Memory. *IEEE J. Electron Devices Soc.* 2019, 7 (July), 1232–1238. https://doi.org/10.1109/JEDS.2019.2941076. pp 154–156. https://doi.org/10.1109/EDTM.2019.8731277.

- (4) Kumar, A.; Balakrishna Pillai, P.; Song, X.; De Souza, M. M. Negative Capacitance beyond Ferroelectric Switches. ACS Appl. Mater. Interfaces 2018, 10 (23), 19812– 19819. https://doi.org/10.1021/acsami.8b05093.

- (5) Balakrishna Pillai, P.; Kumar, A.; Song, X.; De Souza, M. M. Diffusion-Controlled Faradaic Charge Storage in High-Performance Solid Electrolyte-Gated Zinc Oxide Thin-Film Transistors. ACS Appl. Mater. Interfaces 2018, 10 (11), 9782–9791. https://doi.org/10.1021/acsami.7b14768.

### Conferences:

(1) Song, X.; Gaurav, A.; Pillai, P. B.; Kumar, A.; Manhas, S.; Gilra, A.; Vasilaki, E.;

- Souza, M. M. De. Reservoir Computing Based on a Solid Electrolyte ZnO TFT: An Attractive Platform for Flexible Edge Computing. *Int. Flex. Electron. Technol. Conf.* **2023**.

- (2) Souza, M. M. De; **Song, X**.; Gaurav, A.; Manhas, S. K.; Pillai, P. B.; Sikdar, S.; Kumar, A.; Gilra, A.; Vasilaki, E. A Delay System Reservoir Based on a Nano-Ionic Solid Electrolyte FET \*. Nanotechnol. Mater. Devices Conf. 2023.

- Gaurav, A.; Song, X.; Manhas, S. K.; Roy, P. P.; De Souza, M. M. A Solid Electrolyte ZnO Thin Film Transistor for Classification of Spoken Digits Using Reservoir Computing. In 2023 7th IEEE Electron Devices Technology & Manufacturing Conference (EDTM); IEEE, 2023; pp 1–3. https://doi.org/10.1109/EDTM55494.2023.10103131.

- (4) **Song, X.**; Kumar, A.; De Souza, M. M. An Ultra-Low Power 3-Terminal Memory Device with Write Capability in the off-State. In 2019 Electron Devices Technology and Manufacturing Conference (EDTM); IEEE, 2019; pp 154–156. https://doi.org/10.1109/EDTM.2019.8731277.

- (5) **Song, X**.; Pillai, P. B.; Batten, T.; Souza, M. M. De. Highly Oriented (202) Mixed Halide Perovskite for Enhanced Solar Cell Performance. In UK semi 2017 conference; 2017.

### CHAPTER 1

### Introduction

### 1.1 Motivation

The escalating demand in global energy presents a formidable challenge to our planet, primarily due to its significant contribution to the alarming increase in greenhouse gas emissions. This situation is further complicated by the ambitious objective of achieving net-zero emissions by 2050. By 2021, the worldwide demand for electricity surged to 24,700 TWh, representing a 6% year-on-year increase from 2020, which was the largest annual increase seen since 2010 [1]. Approximately 46% of this demand, which accounts for a significant proportion of the global increase in CO2 emissions, is attributable to increasing demand in electricity and heat production [2].

Among various sectors contributing to this relentless demand for electricity, technology-oriented sectors, particularly those reliant on heavy data processing, have experienced the steepest growth. For instance, cryptocurrency mining alone accounted for an energy consumption of 100-140 TWh in 2021, marking an astonishing increase of 2000-3000% from 2015 [3].

In the modern landscape, a burgeoning technology known as the Internet of Things (IoT), also referred to as the Industrial Internet, is gaining traction. This technology fosters interaction among global networks, paving way for the emergence of intelligent environments capable of autonomous self-regulation. These networks link sensors and communication devices on a global scale. Currently, IoT implementations necessitate data analysis in the cloud, where data is transferred from the point of generation and subsequently processed for decision-making. Furthermore, it falls short of achieving the

envisioned fully integrated smart functionality of IoT due to its high power consumption, estimated to be between 320 and 460 TWh for data centers alone [4]. It is projected that by 2025, the quantity of IoT devices will proliferate, reaching an astounding figure of 4.7 billion [5]. A substantial portion of the data, generated by these devices, is characterized by its unstructured nature and redundancy. This leads to heightened energy consumption and latency, particularly due to the transmission of this data for processing [6].

The cloud-centric model of the IoT, based on conventional Von Neumann computing architecture that distinctly separates memory and computational elements, is unsustainable (Fig 1.1), due to data transfer bottlenecks and energy inefficiency [7].

Fig 1.1 Schematic diagram of Von Neumann architectures

Despite the strength of CMOS in handling mathematical and logic operations, these devices fail to match the efficiency of human neurons and synapses in processing analog information. Furthermore, Von Neumann architectures inherently lack features that could support learning and problem-solving. For example, despite not having the raw computational power found in modern machines, the human brain excels at solving sensory-related problems through the use of memory and learning. As a result, software based neural networks require tens of MW of power to mimic only a fraction of human

brain function [8], such as identifying images, that too, after repeated training with substantial data. The human brain accomplishes similar image identification tasks using a mere 20 watts of energy, with less training and data [9]. Therefore, developing hardware akin to brain-inspired computing systems that can more accurately mimic biological neurons and synapses is viewed as a significant step towards achieving energy efficiency [10].

Alternatives to the Von Neumann model such as Compute-in-Memory (CIM) and Neuromorphic Computing are being actively explored, which promise improved computational speed and energy efficiency integrating processing and memory functions into the same unit, thereby avoiding speed and energy losses due to data transmission between separate processing and memory units [11].

The implementation of CIM architectures necessitates hardware that offers high speed, high density, and low energy cost [11][12]. Typically, this involves the integration of scalable memory devices with CMOS devices in a crossbar array for massively parallel operations [12], which are inherently compatible with multiplication and addition operations (Fig 1.2).

Memristors are typically used as synapses in such artificial neural networks (ANNs), where they store conductance values as weights. These weights determine the connections between layers and are a key part of the network's learning functions. The sum of currents in the crossbar are fed into neurons which undertake the task of thresholding. Implementing a neuron in large scale crossbars to achieve the activation function or learnable kernels is challenging and expensive, often relying on field-programmable gate

arrays (FPGA) [13], as well as Analogue to Digital (ADC) and Digital to Analogue Converters (DAC) [14][15] to achieve the desired network function.

Fig 1.2 Sensor connected IoT application

Deep neural networks (DNNs) based on memristors devices such as CBRAMs [16], PCMs [17][18], and OxRAMs[19][20] are increasingly popular due to their compatibility with CMOS, scalability, bidirectional switching behavior, and reduced power consumption by three orders of magnitude compared to a CPU with off-chip memory. However, the change in conductance in a ReRAM, which is caused by the formation and rupture of a conducting filament, is inherently analog and stochastic. This leads to variability, relaxation, nonlinear conductance behavior, and a reduction in yield. This approach necessitates additional efforts at the device, architecture, or algorithmic levels to address the loss of accuracy and make it unsuitable for high precision computing. The accuracy of memristor-based computing can be improved by off-chip training methods, which are energy-intensive and occur in the cloud. However, discrepancies between the platforms used in training (usually GPUs) and the crossbar implementation of the ReRAM lead to a loss of learning efficiency. In contrast, on-chip training methods can eliminate this issue, especially as secure communication with the cloud is a critical constraint in health applications. Examples of embedded intelligence in alternate technologies (beyond CMOS) are virtually nonexistent in the commercial world, primarily due to challenges associated with integration, especially when substrate platforms are not silicon-based, as is common in sensor technologies, which may rely on alternate materials that need to meet the constraints of their applications.

Fig 1.3 Schematic diagram of of a integrated smart solar cell

Edge computing (also known as Processing-in-sensor) allows decisions to be made at the source, thereby reducing the need for extensive data storage and transmission to the cloud. This approach emphasizes the processing of information over the transmission of raw sensor data. This effectively reduces the volume of data required for transmission, thereby decreasing energy usage and latency [21]. The ultimate goal is to develop smart IoT devices capable of operation purely on harvested energy and preserving their computational state even when energy sources are depleted. Furthermore, large-scale implementation of such systems requires commitment to low-cost, environmentally sustainable materials. Moreover, the implementation of such a solution necessitates a meticulous balancing act, harmonizing the demands of space, power supply, computational power, and memory within the sensor framework.

In particular, a major challenge faced by autonomous wireless systems is power supply. When power sources such as batteries or capacitors are combined with renewable energy sources, wireless sensor nodes can operate for longer durations, potentially eliminating the need for battery replacement [22]. This leads to an extended device lifespan and a reduction in weight. There are several examples of energy harvesting integration with CMOS transistors [15], such as photovoltaic energy harvesters integrated with power management ICs in CMOS, which have been demonstrated for at least two decades [23]. These are embedded in watches and other wearable sensors today. For instance, a-Si-H solar cells on top of CMOS transistors [15] and a self-powered solar switch fabricated by integrating a crystalline-Si interdigitated back contact (IBC) PV cell with a-IGZO TFTs in a direct 3D stacked single chip have been demonstrated [24].

More recently, a perovskite photovoltaic cell integrated with a 2D MoTe2 transistor was demonstrated [25], in which double-sided scotch tape was used for bonding to integrate these two technologies at the package level. Since 2009, perovskites have emerged as promising photovoltaic materials due to their potential for high efficiency and low cost. Over the past decade, the efficiency of perovskite solar cells has increased from 3.8% [26] to 25.7% [27], making them an emerging candidate for the next generation of solar cells. Furthermore, the hysteresis observed in perovskite solar cells has led to the development of perovskite-based memristors [28], which has sparked interest in their use in neuromorphic systems [29][30].

This thesis contributes to this field, specifically focusing on neuromorphic devices that can be seamlessly integrated with solar cells for energy harvesting and flexible electronics. We aim to explore materials and processes beyond CMOS that are earth-

abundant, can be processed at low temperatures, and are flexible. These innovative devices hold potential for meeting the rising demands of the healthcare sector, particularly in applications such as assisted living and robotics. Technologies capable of real-time contextualization and filtering of sensitive and safety-critical data at the point of sensing can empower artificial intelligence-based systems to proactively provide support, guidance, and intervention in such applications. Furthermore, these devices could be powered by, or even provide control, to the solar cell, leading to the concept of the 'smart' energy harvesting.

### 1.2 Outline of the Thesis

This thesis is built upon two distinct types of materials that constitute the components for the autonomous intelligent sensor node. Chapters 2 and 3 serve as foundational background chapters, containing an exploration of the physics and a literature review of devices relevant to this work. Chapters 4 to 7 are the primary contributory chapters. The organization of this thesis is as follows:

Chapter 2 provides an introduction to the fundamentals of perovskite materials and their use in solar cells, detailing the fabrication and characterization methods employed. The chapter also outlines the basics of amorphous oxide semiconductors and the operating principles of thin-film transistors based on these materials.

Chapter 3 delves into the principles of brain-inspired computing, tracing the evolution of artificial neural networks from feed-forward neural networks (FNNs) to recurrent neural networks (RNNs). This progression includes an overview of the fundamental structures and training processes associated with these networks. The chapter reviews the progression from RNNs to reservoir computing, offering a critique of recent

advancements in physical reservoir computing. It also discusses the key features of the physical synaptic devices and the emerging memory devices used in neuromorphic systems.

Chapter 4 provides a thorough background on a novel non-filamentary thin-film transistor, known as the Solid Electrolyte Field Effect Transistor (SE-FET). This chapter highlights the device performance in synaptic applications, including its Excitatory Post Synaptic Current (EPSC). Moreover, we present a refined model of the SE-FET that facilitates the simulation of the gate current, a crucial aspect for circuit simulation which in Chapter 5. Furthermore, we delve into the physical interpretation of the gate current and discuss the limitations inherent in previous models [31].

Chapter 5 revolves around the deployment of Solid Electrolyte field-effect transistors (SE-FETs) in logic operations and supervised learning within crossbar architectures. We illustrate how the three-terminal nature of these devices facilitates write operations at a remarkably low power consumption level.

Chapter 6 revolves around the basics of physical reservoirs computing and explores the potential of SE-FETs as physical reservoirs in recurrent neural networks (RNNs).

Chapter 7, we demonstrate a new method for controlled perovskite growth, followed by an evaluation of the physical characteristics and performance of perovskite solar cells produced through our method and conventional techniques.

Finally, Chapter 8 presents the concluding remarks, summarizing the findings and contributions of this thesis. We also discuss potential future directions to further extend the scope of this work.

### 1.3 References

- [1] International Energy Agency, "International Energy Agency (IEA) World Energy Outlook 2022," *Https://Www.Iea.Org/Reports/World-Energy-Outlook-2022/Executive-Summary*, p. 524, 2022.

- [2] I. E. Agency, "Global Energy Review: CO2 Emissions in 2021 Global emissions rebound sharply to highest ever level INTERNATIONAL ENERGY," 2021.

- [3] IEA, "Data Centres and Data Transmission Networks," 2022. .

- [4] E. Covi *et al.*, "Adaptive Extreme Edge Computing for Wearable Devices," *Front. Neurosci.*, vol. 15, no. May, pp. 1–27, May 2021.

- [5] L. S. Vailshery, "IoT connected devices globally in 2019 & 2030." [Online].

Available: https://www.statista.com/markets/418/technology-telecommunications/

- [6] F. Zhou and Y. Chai, "Near-sensor and in-sensor computing," *Nat. Electron.*, vol. 3, no. 11, pp. 664–671, Nov. 2020.

- [7] D. V Christensen *et al.*, "2022 roadmap on neuromorphic computing and engineering," *Neuromorphic Comput. Eng.*, vol. 2, no. 2, p. 022501, Jun. 2022.

- [8] S. Dai et al., "Recent Advances in Transistor-Based Artificial Synapses," Adv. Funct. Mater., vol. 29, no. 42, p. 1903700, Oct. 2019.

- [9] R. Ananthanarayanan *et al.*, "The cat is out of the bag: cortical simulations with 109 neurons, 1013 synapses," *High Perform. Comput. Networking, Storage Anal. Proc. Conf.*, no. c, pp. 1–12, 2009.

- [10] Y. Zhang *et al.*, "Brain-inspired computing with memristors: Challenges in devices, circuits, and systems," *Appl. Phys. Rev.*, vol. 7, no. 1, p. 011308, Mar. 2020.

- [11] S. Yu et al., "Compute-in-Memory Chips for Deep Learning: Recent Trends and

- Prospects," IEEE Circuits Syst. Mag., vol. 21, no. 3, pp. 31–56, 2021.

- [12] D. Ielmini and H. S. P. Wong, "In-memory computing with resistive switching devices," *Nat. Electron.*, vol. 1, no. 6, pp. 333–343, 2018.

- [13] R. Fernandez Molanes *et al.*, "Deep learning and reconfigurable platforms in the internet of things: Challenges and opportunities in algorithms and hardware," *IEEE Ind. Electron. Mag.*, vol. 12, no. 2, pp. 36–49, 2018.

- [14] S. Mittal, "A Survey of ReRAM-Based Architectures for Processing-In-Memory and Neural Networks," *Mach. Learn. Knowl. Extr.*, vol. 1, no. 1, pp. 75–114, 2018.

- [15] T. Zhang *et al.*, "Memristive Devices and Networks for Brain-Inspired Computing," *Phys. status solidi – Rapid Res. Lett.*, vol. 13, no. 8, p. 1900029, Aug. 2019.

- [16] J.-H. Cha *et al.*, "Conductive-bridging random-access memories for emerging neuromorphic computing," *Nanoscale*, vol. 12, no. 27, pp. 14339–14368, 2020.

- [17] V. Joshi *et al.*, "Accurate deep neural network inference using computational phase-change memory," *Nat. Commun.*, vol. 11, no. 1, p. 2473, May 2020.

- [18] G. Pedretti *et al.*, "A Spiking Recurrent Neural Network With Phase-Change Memory Neurons and Synapses for the Accelerated Solution of Constraint Satisfaction Problems," *IEEE J. Explor. Solid-State Comput. Devices Circuits*, vol. 6, no. 1, pp. 89–97, Jun. 2020.

- [19] S. Kim *et al.*, "Metal-oxide based, CMOS-compatible ECRAM for Deep Learning Accelerator," in 2019 IEEE International Electron Devices Meeting (IEDM), 2019, pp. 35.7.1-35.7.4.

- [20] Y. Zhang *et al.*, "Oxide-based filamentary RRAM for deep learning," *J. Phys. D. Appl. Phys.*, vol. 54, no. 8, p. 083002, Feb. 2021.

- [21] F. De Roose *et al.*, "12.3 Memory Solutions for Flexible Thin-Film Logic: up to 8kb, >105.9kb/s LPROM and SRAM with Integrated Timing Generation Meeting the ISO NFC Standard," in *2019 IEEE International Solid- State Circuits Conference (ISSCC)*, 2019, vol. 31, pp. 206–208.

- [22] D. Prakash Guragain *et al.*, "Programmable timer triggered energy harvesting wireless sensor-node using long range radio access technology," *Int. J. Electr. Comput. Eng.*, vol. 12, no. 4, p. 3869, Aug. 2022.

- [23] J. Lu *et al.*, "Integration of Solar Cells on Top of CMOS Chips Part I: a-Si Solar Cells," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2014–2021, Jul. 2011.

- [24] S. Ali *et al.*, "Solar Powered Smart Irrigation System," *Pakistan J. Eng. Technol.*, vol. 5, no. 1, pp. 49–55, 2022.

- [25] Y.-M. Juan *et al.*, "Integration of a-IGZO Thin-Film Transistor and Crystalline-Si Interdigitated Back Contact Photovoltaic Cell With 3D Stacking Structure as Self-Powered Solar Switch," *IEEE Electron Device Lett.*, vol. 35, no. 10, pp. 1040–1042, Oct. 2014.

- [26] A. Kojima *et al.*, "Organometal halide perovskites as visible-light sensitizers for photovoltaic cells," *J. Am. Chem. Soc.*, vol. 131, no. 17, pp. 6050–6051, 2009.

- [27] M. A. Green *et al.*, "Solar cell efficiency tables (Version 61)," *Prog. Photovoltaics Res. Appl.*, vol. 31, no. 1, pp. 3–16, Jan. 2023.

- [28] C. Gu and J.-S. Lee, "Flexible Hybrid Organic–Inorganic Perovskite Memory," *ACS Nano*, vol. 10, no. 5, pp. 5413–5418, May 2016.

- [29] J. Choi *et al.*, "Organolead Halide Perovskites for Low Operating Voltage Multilevel Resistive Switching," *Adv. Mater.*, vol. 28, no. 31, pp. 6562–6567, Aug.

2016.

- [30] B. Hwang *et al.*, "Effect of halide-mixing on the switching behaviors of organic-inorganic hybrid perovskite memory," *Sci. Rep.*, vol. 7, no. 1, p. 43794, Mar. 2017.

- [31] A. Kumar *et al.*, "Negative Capacitance beyond Ferroelectric Switches," *ACS Appl. Mater. Interfaces*, vol. 10, no. 23, pp. 19812–19819, Jun. 2018.

#### CHAPTER 2

# Basics of Perovskite solar cells and Amorphous Oxide Thin Film Transistors

### 2.1 Introduction

Perovskite materials and amorphous oxide semiconductors (AOS) have been subjects of increasing attention, motivated primarily for their potential low cost and broad applications in energy harvesting and flexible electronics. Perovskites, with their distinct properties, are viewed as a promising catalyst for significant strides in solar energy conversion, while AOS, due to their exceptional electronic characteristics, hold promise in diverse areas, including display technology, neuromorphic computing, and renewable energy (as carrier transporting layer).

This chapter, therefore, offers an exhaustive background to these vital materials, starting in part 2.2 with a brief history of perovskite solar cells, followed by a comprehensive examination of their fundamental material properties, detailing methodologies employed in their fabrication and characterization and principle of operation of solar cells. Section 2.3 is devoted to Amorphous oxide semiconductors. Subsection 2.3.1 highlights applications of AOSs in the areas particularly of displays and memory. In particular, recent development of using AOS, especially ZnO, as electron transporting layer to address cost and stability in perovskite solar cells is highlighted. This is followed by the structure and properties, with a special emphasis on distinguishing the material differences between AOS and their amorphous silicon counterparts. Subsection 2.3.3 highlights methods of deposition and is followed by the principle of operation of thin film transistors in AOS.

#### 2.2 Perovskite solar cells

## 2.2.1 A brief history of perovskite solar cells

The history of perovskite-based solar cells is relatively brief, spanning just over a decade. The inaugural perovskite-based solar cell was unveiled by A. Kojima and colleagues in 2006. They employed CH<sub>3</sub>NH<sub>3</sub>PbBr<sub>3</sub> as the light-absorption material in a dye-sensitized solar cell (DSSC), achieving a power conversion efficiency (PCE) of 2.2% [1]. The first report specifically centered on perovskite-based solar cells was released by the same team in 2009, where CH<sub>3</sub>NH<sub>3</sub>PbBr<sub>3</sub> was substituted with the now widely used CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>, leading to an improved PCE of 3.83% [2].

A landmark development for perovskite solar cells transpired in 2012, with the enhancement of an all-solid-state structure premised on TiO2 [3]. This pioneering work propelled the perovskite solar cell away from the electrolyte-based DSSC, resulting in the achievement of a PCE exceeding 10% for the first time [4].

In 2013, a notable enhancement was reported that involved doping the film with Cl. It was conjectured that the creation of CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3-x</sub>Cl<sub>x</sub> led to improved carrier diffusion lengths (exceeding 1 μm for both electrons and holes) [5]. In the same year, N. Pellet and associates put forth an improved two-step solution technique that elevated the PCE of perovskite solar cells to 15.0% [6]. This group also introduced the usage of HN=CHNH<sub>3</sub>+ (FA+) as a substitute cation for CH<sub>3</sub>NH<sub>3</sub>+(MA+). The combined perovskite using both FA+ and MA+ exhibited a promising enhancement in the device's short-circuit photocurrent and elevated the PCE to 14.9% [7]. A significant efficiency record of 19.3% was achieved in 2014 by H. Zhou and colleagues by optimizing the interfaces between the perovskite, the electron transport material (ETM), and the hole transport layer (HTL), and

aligning the band structure [8][9]. In 2016, a novel vacuum flash-assisted solution processing method was developed for large-area perovskite solar cells, significantly boosting their certified power conversion efficiency of perovskite solar cells over 1 square centimeter from 15.6% to 19.6% [10].

In 2017, a new technique known as defect passivation was introduced, aimed at enhancing the performance and addressing the stability issues of perovskite solar cells. This method specifically targets and mitigates the imperfections in the perovskite material, leading to improved efficiency and durability of these solar cells [11]. Defect passivation targets the amelioration of surface defect sites at the perovskite layer interface by incorporating a passivation layer between the perovskite and the ETM or hole transport material (HTM), or in some instances, both. Notably, in 2019, Q. Jiang et al. utilized phenethyl ammonium iodide as a passivation layer between the perovskite and the HTM, which led to the achievement of a certified efficiency of 23.32%. Remarkably, the device retained this efficiency for over 500 hours [12]. In 2023, a new record of 25.7% was set for thin film perovskite solar cell [13]. Moreover, using a mixed of different perovskite materials, the Multijunction perovskite/perovskite and perovskite/Si is on the rise. In 2022, Haowen Luo et al. reported a perovskite/perovskite (two hybrid perovskite layer with different band gap) based Multijunction solar with recorded efficiency of 28% [13], and the device is able to maintain 75% of its efficiency after 500 hours of operation [14].

### 2.2.2 Basic structure and property of perovskite material

Perovskites represent a versatile family of materials unified by their ABX<sub>3</sub> structure, as illustrated in Fig 2.1. In this configuration, 'A' denotes a large positively charged compound, 'B' signifies a smaller positively charged ion, and 'X' is a negatively

charged ion, typically arranged in a cubic crystal. B ions inhabit the body center of the cubic cell, while A ions reside at each vertex, and X ions are located at each face-center of the unit cell. This ideal cubic structure can accommodate a broad range of metal oxides, such as CaTiO<sub>3</sub>, LaAlO<sub>3</sub>, or MgSiO<sub>3</sub>. Here, A, B, and X ions possess charge states of A<sup>2+</sup>, B<sup>4+</sup>, and X<sup>2-</sup> or A<sup>3+</sup>, B<sup>3+</sup>, and X<sup>-2</sup>. Intriguingly, organic compounds can also form structures with metal trihalides, where A, B, and X ions are A<sup>+</sup>, B<sup>2+</sup>, and X<sup>-</sup>, respectively [15].

Fig 2.1 Ideal perovskite crystal structure (cubic).

Despite the underlying structural consistency of perovskites, distortions frequently occur depending on factors such as formation temperature and the ionic radii of A, B, and X [16]. Depending on the formation temperature and the ionic radii of the respective ions, the same perovskite group's structure can transition from cubic to tetragonal or even orthorhombic. Such structural shifts are often quantified using a tolerance factor (t) defined as:

$$t = \frac{r_A + r_X}{\sqrt{2}(r_B + r_X)} \tag{Eq 2.1}$$

Here  $r_A$ ,  $r_B$ , and  $r_X$  are the ionic radii of A, B, and X, respectively. The tolerance factor 't' provides an indication of hexagonal perovskite instability [17]. A tolerance factor exceeding 1 suggests challenges in maintaining the perovskite structure, whereas a tolerance factor within the range of  $0.9 \le t \le 1$  is indicative of an optimal cubic perovskite structure. Should the tolerance factor fall between  $0.7 \le t \le 0.9$ , it is usually a sign that 'A' is undersized for the cubic structure, consequently yielding orthorhombic, rhombohedral, or tetragonal structures [17]. A tolerance factor of t < 0.7 implies that 'A' is equivalent to or smaller than 'B', a scenario rarely encountered in perovskite structures.

In the realm of perovskite-based solar cells, the term 'perovskite' generally refers to the organic–inorganic metal trihalide, with CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> being the most extensively utilized perovskite-based material. Here, 'A' is the large organic ion CH<sub>3</sub>NH<sub>3</sub>+( commonly referred to as MA<sup>+</sup>), 'B' is typically a Pb<sup>2+</sup> ion, and 'X' is I. At room temperature, the ionic radii of MA+, Pb2+, and I- are 0.18, 0.132, and 0.206 nm, respectively, yielding a tolerance factor of 0.81 [18]. This value suggests a tetragonal structure for MAPbI<sub>3</sub>, corroborating experimental findings [19].

The tetragonal structure of the MAPbI3 crystal, delineated in Fig 2.2, has lattice constants a = b = 8.85 Å, c = 12.69 Å, and angles  $\alpha = \beta = \gamma = 90^{\circ}$  [20][21]. The Pb-I framework constitutes the fundamental structure of the MAPbI3 unit cell, while CH3NH3<sup>+</sup> molecules are situated within the Pb-I framework. Due to these molecules, the Pb-I framework often exhibits distortion, leading to a less symmetrical structure with each unit cell containing four units of CH3NH3PbI3 [21].

Fig 2.2 (a) Unit cell of the tetragonal structure of CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>. Here, A is CH<sub>3</sub>NH<sub>3</sub><sup>+</sup>, B is Pb<sup>2+</sup>, and X is Γ. (b) Side view and (c) top view of the tetragonal CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> structure.

CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> demonstrates a direct band gap of 1.55~1.6 eV [22][23], in close proximity to the ideal optical band gap for a single-junction solar cell of approximately

1.3~1.4 eV [24][25]. This halide perovskite's band gap is adjustable through mixed-halide superlattices or by altering the halide composition, typically by substituting I with Cl or Br (1.95eV for CH<sub>3</sub>NH<sub>3</sub>PbBr<sub>3</sub> and 2.46 eV for CH<sub>3</sub>NH<sub>3</sub>PbCl<sub>3</sub>) [26]. Moreover, polycrystalline CH<sub>3</sub>NH<sub>3</sub>PbBr<sub>3</sub> exhibits an impressively sharp absorption coefficient, exceeding that of Si and aligning closely with the band gaps of GaAs and CdTe [27]. This property permits high absorption even for thin perovskite films, conferring an advantage in thin-film devices over traditional Si materials. The majority of perovskite solar cells are less than 1 μm thick and achieve efficiencies nearing 20%, significantly surpassing the peak reported efficiency for thin-film Si solar cells (less than 2 μm thick) at 10.5% [28].

Single-crystal CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> has demonstrated a carrier mobility of 30 cm<sup>2</sup>/Vs, with the trap state density reaching as low as 3.6×10<sup>10</sup> cm<sup>3</sup>, comparable to that of Si [29]–[32]. Despite these exceptional properties, the factors contributing to the superior photovoltaic performance and their relation to the perovskite structure are yet to be fully understood [33]. Based on the ferroelectric properties of CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> perovskite [34] and its slow photocurrent response [33], the CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> structure is thought to constitute a well-defined Pb-I framework with a rotational dynamic cation, CH<sub>3</sub>NH<sub>3</sub><sup>+</sup>. Positioned in the Pb-I framework, as shown in Fig 2.2, the CH<sub>3</sub>NH<sub>3</sub><sup>+</sup> molecule is comprised of a neutral NH3 group, with the charge mainly distributed to the CH<sub>3</sub><sup>+</sup> group [35]. This uneven charge distribution within the Pb-I framework influences numerous properties relevant to solar cell performance, and is considered to be one of the causes for the ferroelectric properties and hysteresis observed in these cells [33][36]. The CH<sub>3</sub>NH<sub>3</sub><sup>+</sup> orientation is postulated to be influenced by illumination [33], applied bias [37], and environmental temperature [38],

but the precise rotation mechanism under operational conditions remains a topic of active investigation.

### 2.2.3 Deposition method for CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>

Since the introduction of perovskite solar cells in 2009, a multitude of deposition methods have been established for growing CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> perovskite. Despite the diverse array of methods, all are centered around a simple reaction:

$$CH_3NH_3I + PbI_2 = CH_3NH_3PbI_3$$

This reaction typically takes place at temperatures exceeding 60°C [39] and can be prompted by a reaction between solutions of CH<sub>3</sub>NH<sub>3</sub>I and PbI<sub>2</sub> [40], annealing a dried film of CH<sub>3</sub>NH<sub>3</sub>I and PbI<sub>2</sub> [41], or through a vapor deposition method [19].

The solution-based process is generally the more popular technique for CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>-based perovskite deposition. Here, the manufacturing process involves coating solutions of CH<sub>3</sub>NH<sub>3</sub>I and PbI<sub>2</sub>, layer by layer, in the shape of the desired device structure. As this technique doesn't necessitate a vacuum or high-temperature conditions, fabrication costs are kept to a minimum.

The one-step and two-step solution-based methods are illustrated in Fig 2.3. In the one-step method, a blend of CH<sub>3</sub>NH<sub>3</sub>I and PbI<sub>2</sub> in dimethylformamide (DMF) or dimethyl sulfoxide (DMSO) solution is spin-coated onto the chosen substrate. An annealing process usually follows the spin-coating process to dry the remaining solvent and facilitate the formation of the perovskite layer. Due to the high reaction rate, the one-step method often resulted in a non-uniform film with randomly oriented perovskite in earlier works [42][43]. However, the introduction of solvent engineering [44] techniques and other additives, such

as Triazolium [45] and ammonium benzenesulfonate [46], has significantly enhanced the quality and uniformity of perovskite films.

The two-step method splits the perovskite formation process into two phases. The first step involves depositing a layer of PbI<sub>2</sub> via spin coating. This PbI<sub>2</sub> film is then converted into perovskite through various methods, such as spin coating of an MAI/isopropyl alcohol (IPA) solution [42][40], immersion in a solution of MAI/IPA [47][48], or annealing with a solid MAI film [49]. On the whole, the two-step method is viewed as superior, as it typically yields a better average efficiency and morphology [43].

Fig 2.3 One-step and two-step solution-based methods for CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> deposition.

In 2013, Stranks et al. [5] suggested doping CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> with Cl, a step that has since been widely implemented for both one-step and two-step methods. In the solution method, doping is accomplished by dissolving a small amount of CH<sub>3</sub>NH<sub>3</sub>Cl in a CH<sub>3</sub>NH<sub>3</sub>I solution (or PbCl<sub>2</sub> in a PbI<sub>2</sub> solution). It was assumed that Cl would diffuse into the

CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> and form a mixed CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>-xClx perovskite [5][50]. CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>-xClx is thought to have a superior carrier lifetime compared to the CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> perovskite, with reports showing a device efficiency improvement from 4.2% to 12.2% [5].

Despite the widespread acceptance of the Cl doping method for performance enhancement, the role of Cl doping was ambiguous, as Cl loss is commonly observed during perovskite growth [51]. Utilizing XRD and X-ray photoelectron spectroscopy (XPS) techniques, H. Yu et al. detected no Cl in a sample prepared with 10% Cl doping in an MAI+MACl solution [52]. These results confirmed that while Cl doping is an effective technique, the formation of CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>-xClx is clearly not the cause of the improvement. Given the observed Cl loss and the final reaction product, it is currently believed that Cl enhances perovskite quality by forming an intermediate state during the reaction, rather than by forming the CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>-xClx perovskite. Yu et al. [48] and Williams et al. [53] proposed a possible reaction of the Cl doping technique as follows:

$$\begin{split} \operatorname{PbCl}_2 + \operatorname{3CH}_3\operatorname{NH}_3\operatorname{I} &\stackrel{\Delta}{\to} \operatorname{PbI}_2 + \operatorname{CH}_3\operatorname{NH}_3\operatorname{I} + \operatorname{2CH}_3\operatorname{NH}_3\operatorname{Cl} \\ \operatorname{PbI}_2 + \operatorname{xCH}_3\operatorname{NH}_3\operatorname{I} + \operatorname{yCH}_3\operatorname{NH}_3\operatorname{Cl} &\stackrel{\Delta}{\to} (\operatorname{CH}_3\operatorname{NH}_3)_{x+y}\operatorname{PbI}_{2+x}\operatorname{Cl}_y \\ (\operatorname{CH}_3\operatorname{NH}_3)_{x+y}\operatorname{PbI}_{2+x}\operatorname{Cl}_y &\stackrel{\Delta}{\to} \operatorname{CH}_3\operatorname{NH}_3\operatorname{PbI}_3 + \operatorname{CH}_3\operatorname{NH}_3\operatorname{Cl} \uparrow \end{split}$$

## 2.2.4 Perovskite solar cells: device structure and working principle

Early perovskite solar cells followed a structure akin to Dye-Sensitized Solar Cells (DSSCs); the cell consisted of a photoelectrode with a perovskite layer deposited on TiO2 and Pt as a counter electrode. The two electrodes were separated by an organic electrolyte solution [2]. However, it was discovered that the liquid electrolyte could dissolve the

perovskite layer, resulting in limited performance and stability of perovskite-based DSSCs [54].

Since 2012, all-solid-state structures have replaced liquid-electrolyte perovskite solar cells. There are generally three types of solid-state structures: the conventional p-i-n structure, the mesoscopic p-i-n structure, and the inverted n-i-p structure. Both the conventional and mesoscopic p-i-n structures (Fig 2.4 (a) and (b)) are usually bottom-up structures based on a transparent bottom contact such as fluorine-doped tin oxide (FTO). The electron transport layer (ETL) is typically a compact layer composed of a transparent n-type semiconductor, such as TiO<sub>2</sub> [55] or SiO<sub>2</sub> [56]. In the conventional p-i-n structure, the perovskite layer is deposited on top of the ETL, while in the mesoscopic structure, the perovskite is partly formed within the mesoscopic ETL. Both conventional and mesoscopic p-i-n structures usually require a hole transport layer (HTL) to form the heterojunction. Spiro-MeOTAD is the most commonly used material for the HTL, and the top contact is typically gold (Au) or silver (Ag).

For an inverted n-i-p perovskite solar cell (Fig 2.4 (c)), the transparent bottom contact is usually based on Indium Tin Oxide (ITO). The bottom HTL is usually a transparent p-type semiconductor, commonly PEDOT:PSS [42][57] or a p-type oxide such as NiO<sub>x</sub> [58], and the ETL on top of the perovskite is usually an n-type semiconductor such as PCBM [57],  $C_{60}$  [59], or ZnO [60].

Fig 2.4 (a) Conventional p-i-n, (b) mesoscopic p-i-n, and (c) inverted n-i-p perovskite solar cell structures.

It is worth noting that researchers have demonstrated ETL-free or HTL-free perovskite solar cells based on a simple structure with a perovskite layer and an ETL or HTL sandwiched between two contacts [61][62]. However, these devices usually suffer from relatively poor performance due to a lower fill factor and open circuit voltage.

## 2.2.5 Working principle of perovskite solar cells

Perovskite solar cells, despite their diverse materials and device structures, fundamentally operate like conventional p-n or p-i-n photodiodes, with the utilization of perovskite materials [63].

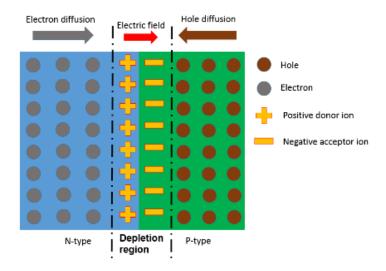

For a conventional p-n diode, due to the carrier concentration gradient at the interface between the p and n side, the electrons tend to diffuse toward the p-type region and leave a space of positively charged donor ions in the n-type material near the interface. The holes migrate from the p-type region toward the n-type region, leaving a region of negatively charged dopants near the interface in the p-type semiconductor. This migration of carriers results in a built-in electric field from n to p, which generates a drift current opposite to the direction of diffusion. This drift and diffusion eventually reach a dynamic equilibrium, creating a region where carriers are depleted.

Fig 2.5 Structure of a p-n diode.

In the case of p-i-n diodes like perovskite solar cells, the p-type material is typically PEDOT:PSS or spiro-MeOTAD, the n-type material is usually PCBM or TiO2, and the intrinsic semiconductor is the perovskite. Both the p-i and i-n interfaces experience diffusion and drift, with the built-in electric field from n to p driven by the potential difference at the p-i and i-n interfaces. The intrinsic perovskite semiconductor acts as an extended depletion region between p- and n-type semiconductors, with its band tilted due to the potential difference between the p-i and i-n interfaces [63].