# Characterisation of Polarization Super-Junction Power devices in Gallium Nitride

Ву

Yangming Du

Department of Electronic and Electrical Engineering

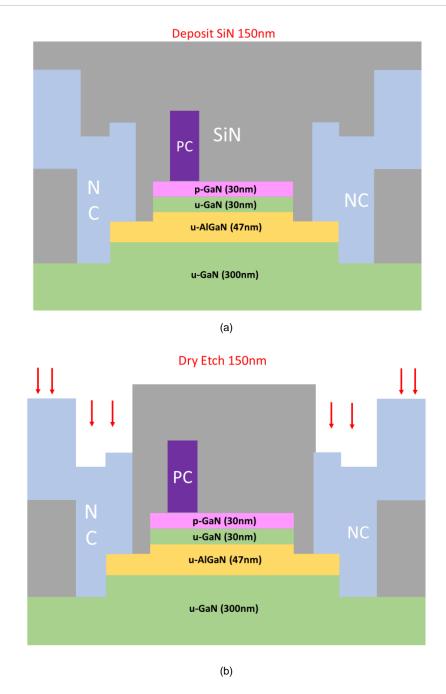

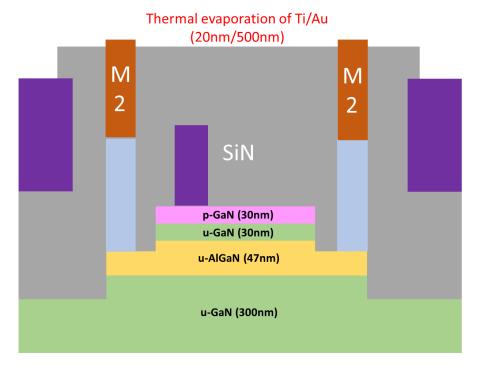

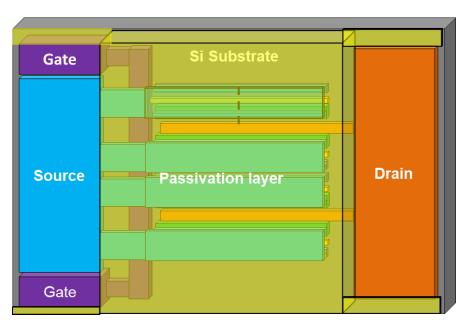

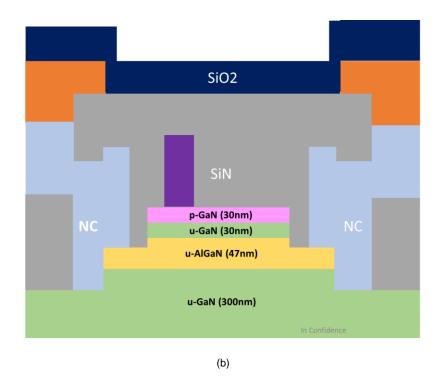

A thesis submitted to the University of Sheffield

for the degree of Doctor of Philosophy

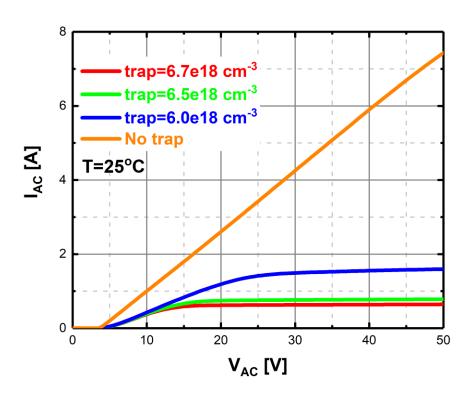

October 2022

# Acknowledgements

I want to sincerely thank and respect my supervisor, Prof. Shankar Ekkanath Madathil, for his patient and kind supervision, insightful advice, and inspirational words. I am able to carry out my doctoral studies thanks to his confidence and encouragement. Additionally, I want to express my gratitude to Dr Akira Nakajima from AIST, Japan, for the insightful remarks on the PSJ diode current saturation behaviour through our Skype calls. I was motivated to investigate this research topic by his recommendations and thoughts on this work. Thanks to Dr Hiroji Kawai, Shuichi Yagi, and Hironobu Narui at POWDEC.K.K in Japan, I was able to do my tests using fantastic PSJ power devices. as well as their insightful remarks on my research and paper.

I want to express my gratitude to the entire EEE department personnel at the University of Sheffield. I thank Mr Adam Stroughair, Dr Kean Boon Lee, and the other technical staff members for their assistance and support with the cleanroom training. I also want to thank Dr Gavin L. Williams for the assistance with the measurements. My deepest appreciation and compliments go out to my Power Microelectronics Team colleagues. I appreciate the warm assistance and patient introduction to my research work from Dr Hong Yao Long when I joined the team group. I would especially want to thank Mr Hongyang Yan and Dr Peng Luo for their assistance with the fabrication and discussion of my work. A special thanks go out to Mr Alireza Sheikhan, who gave me advice and assisted me with the circuit tests.

Last but not least, I'd like to use this chance to thank my parents in the sincerest way possible. Their motivation and assistance allow me to concentrate on my scholarly studies. I want to sincerely thank Yue Wang, my girlfriend, and tell her how much I adore her. My life is brightened by her unfailing love and support during our phone chats, which is how she helps me get over the difficulties and obstacles of my academic research job.

# **Abstract**

GaN Polarisation Superjunction (PSJ) technology utilises charge balance concepts using the polarisation effects in GaN, significantly enhancing the blocking voltage of GaN power devices. Due to these advantages, it has become one of the promising candidates for the next generation of GaN Power technology. Further exploring findings of the characterisation of the PSJ power devices are introduced in this thesis. POWDEC.K.K, Japan, is one of the first companies which started to investigate PSJ technology. They have made several new PSJ power devices and presented their electrical performances based on their mature and complete technologies, including GaN wafer epitaxial growth, wafer process fabrication, dicing and packaging[1], [2]. The findings obtained from the POWDEC.K.K PSJ samples include (1) the impacts from the top u-GaN and AlN nucleation layer on the sheet density of 2DEG and 2DHG, (2) the mechanisms of the current saturation of PSJ diodes and (3) gate reliability and leakage performance of PSJ HFETs. Moreover, the performances of the PSJ-on-Si power devices obtained from the fabricated samples in Sheffield are also introduced in this thesis.

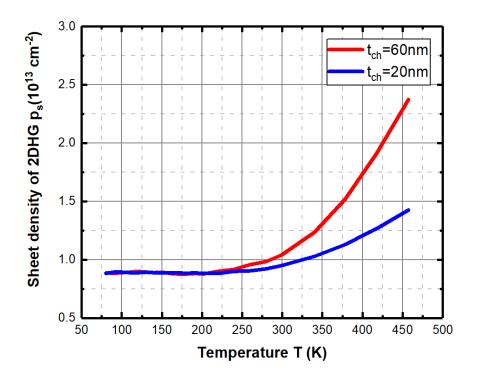

The impacts from the top u-GaN layer thickness on the sheet density of 2DEG and 2DHG in u-GaN/AlGaN/u-GaN double heterostructures are analysed through the theoretical model. It found that the top surface potential determines the relationship. Under the free surface condition, the sheet density of 2DHG is inconsistent with u-GaN thickness. However, the sheet density of 2DHG rises when the Schottky surface conditions are introduced. Similar conclusions can be drawn from the PSJ heterostructures with a P-GaN cap layer. Furthermore, the AlN nucleation layer effects on the 2DEG sheet density are relevant to the relationship between the AlN nucleation layer and u-GaN buffer layer thickness.

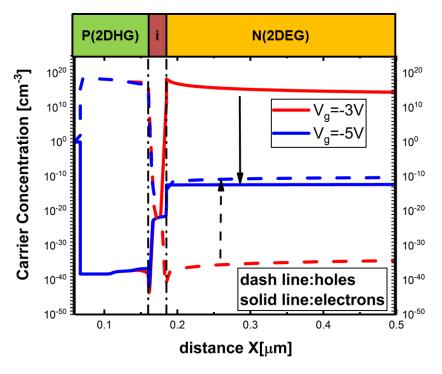

The current saturation behaviour and the saturation mechanisms of the unipolar power GaN diodes: Conventional AlGaN/GaN diode and PSJ hybrid diode are firstly reported and discussed. It is found that velocity saturation, together with the minimal

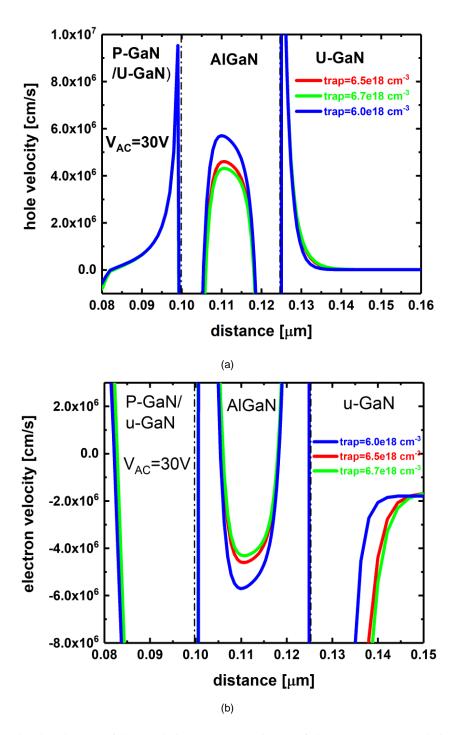

conductivity modulation induced by the minority carrier in the drift region, is the main reason for the saturation behaviour in these two diodes. Moreover, a unique current saturation behaviour of the forward I-V characteristics of the bipolar PSJ PiN diode is also discussed. The negligible and localised conductivity modulation is one of the critical causes of this phenomenon. Moreover, according to the simulation results, trap-induced velocity saturation is also responsible for the current saturation behaviour in the PSJ PiN diodes.

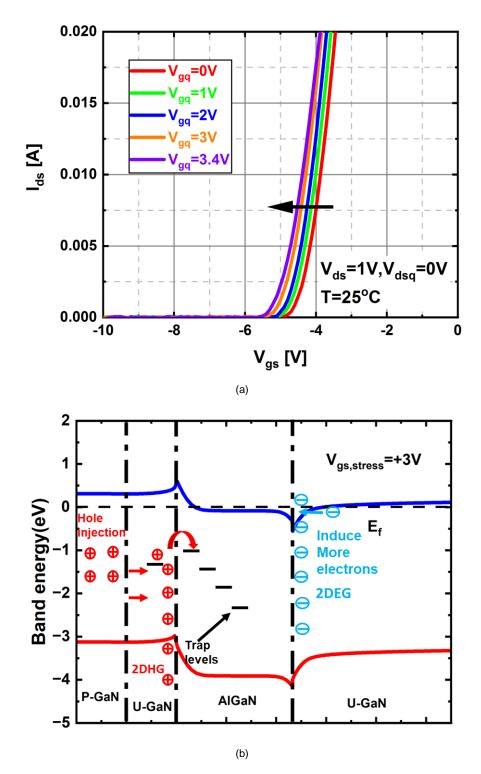

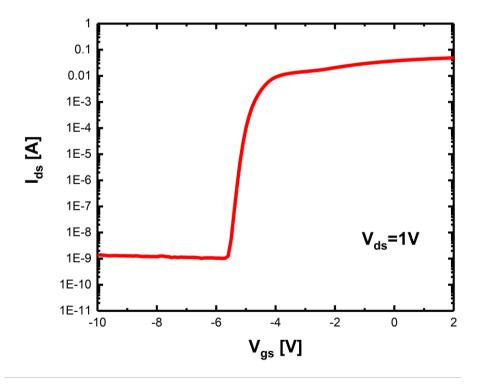

The shift in threshold voltages (V<sub>th</sub>) of 1.2 kV P-GaN ohmic-gate Normally-on Polarization Superjunction (PSJ) HFETs is reported for the first time. A comprehensive analysis of threshold voltage shifts and recovery processes under different gate stress voltages and temperatures is presented. Temperature effects on the V<sub>th</sub> shift are also evaluated. Compared with the P-GaN gate HEMTs, the Pulsed I<sub>d</sub>-V<sub>d</sub> results confirm that the current collapse induced by the Vth instability is relatively low in PSJ HFETs. Moreover, the V<sub>th</sub> shift in 1.2kV PSJ Schottky gate HFETs is also investigated.

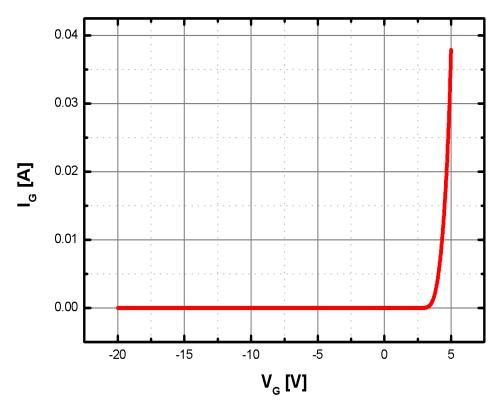

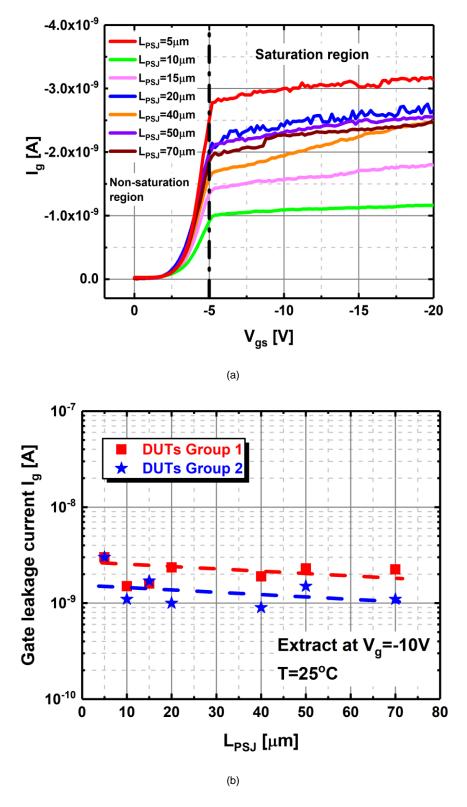

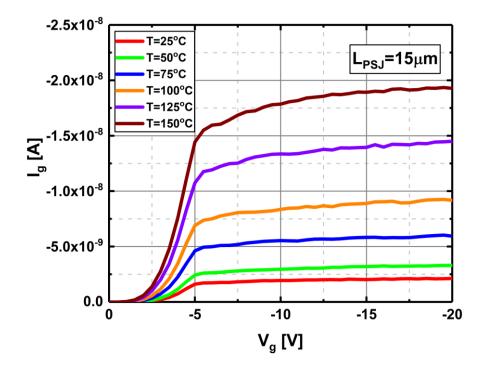

The characteristics of the P-type ohmic gate leakage current is also examined. And its unique saturation behaviour is presented and explored. Finally, it details how the leakage current operates in the saturation and non-saturation regions.

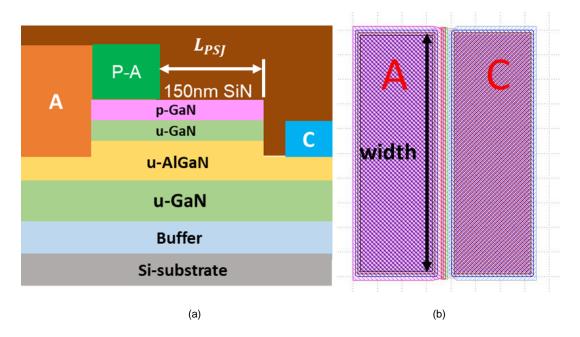

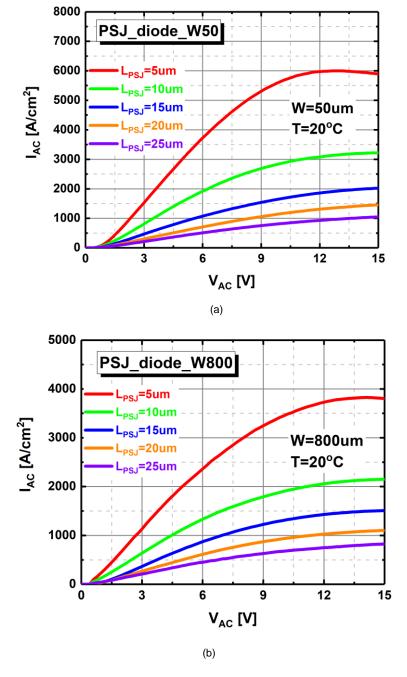

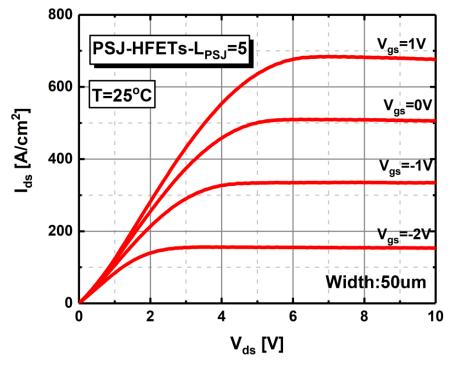

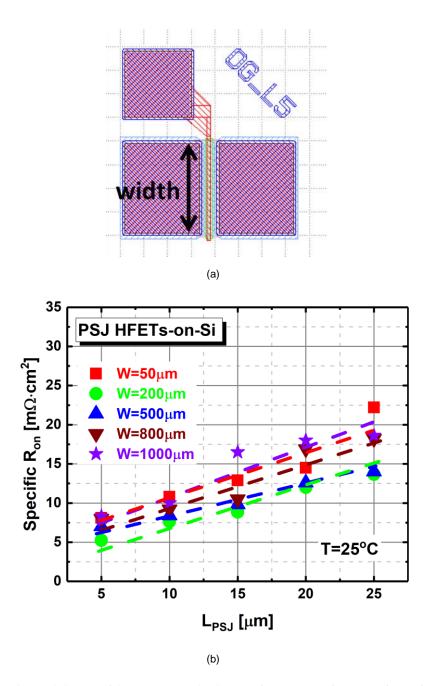

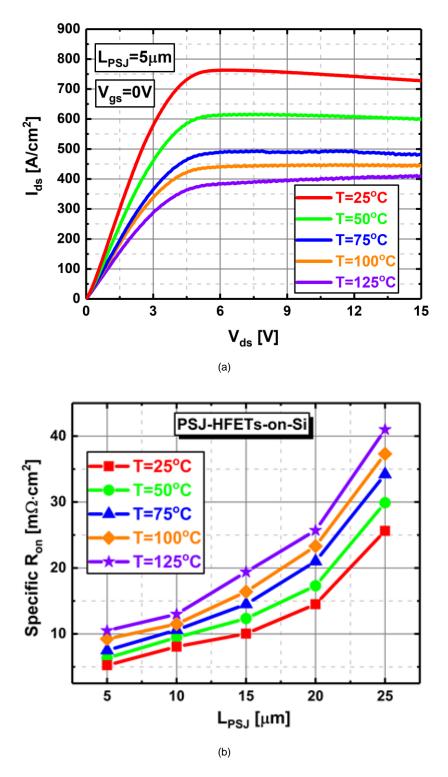

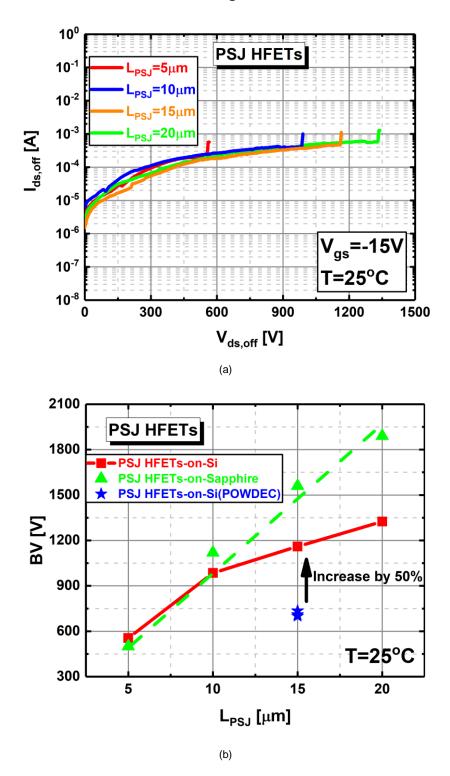

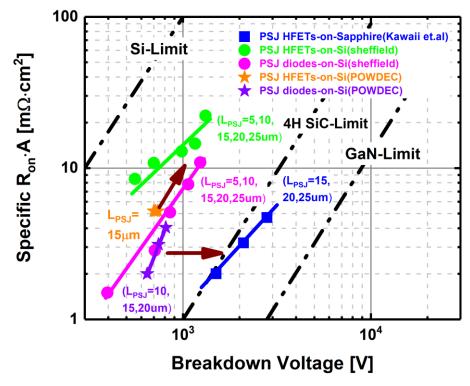

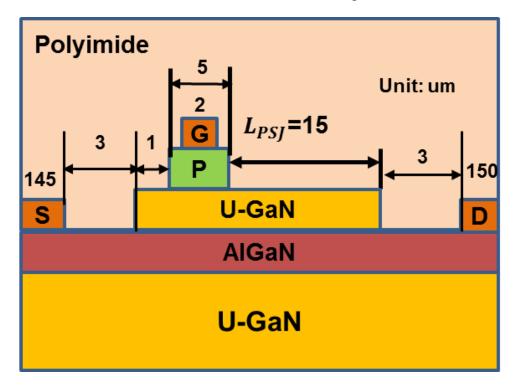

The fabrication process flow and electrical performances of the PSJ-on-Si power semiconductor devices at the University of Sheffield are firstly presented. It includes the on-state and breakdown characteristics of PSJ HFETs and PSJ hybrid diodes. Furthermore, the current density and specific on-state resistance are also studied as a function of the finger length, quantity and temperature.

# Contents

| Acknowledgements                                                     | ii  |

|----------------------------------------------------------------------|-----|

| Abstract                                                             | iii |

| Chapter 1. Introduction                                              | 1   |

| 1.1. Overview                                                        | 1   |

| 1.2. Introduction of Power semiconductor devices                     | 4   |

| 1.3. Thesis organisation                                             | 5   |

| Chapter 2. Background of Gallium Nitride (GaN) HFETs                 | 9   |

| 2.1. GaN Material Property                                           | 9   |

| 2.2. Substrates for GaN Power devices                                | 13  |

| 2.3. Polarisation Effects                                            | 17  |

| 2.3.1. Spontaneous Polarisation                                      | 18  |

| 2.3.2. Piezoelectric Polarisation                                    | 20  |

| 2.4. AlGaN/GaN heterostructures and the formation of 2DEG            | 23  |

| 2.4.1. Polarisation charge                                           | 23  |

| 2.4.2. Origin of 2DEG                                                | 28  |

| 2.5. Conventional AlGaN/GaN High Electron Mobility Transistor (HEMT) | 35  |

| 2.5.1. The operation principle of conventional AlGaN/GaN HEMTs       | 36  |

| 2.5.2. Introduction of field-plate technology                        | 39  |

| 2.5.3. Introduction of the RESURF concept                            | 43  |

| 2.5.4. Introduction of Si Superjunction                              | 46  |

| 2.6. GaN Polarisation Superjunction technology (PSJ)                 | 49  |

| 2.7. Current collapse                                            | 54               |

|------------------------------------------------------------------|------------------|

| 2.8. Summary                                                     | 58               |

| Chapter 3. Theoretical Analysis of the Sheet Density of 2DE      | G and 2DHG in    |

| Polarization Super-Junction Heterostructures                     | 60               |

| 3.1. Top u-GaN layer thickness                                   | 60               |

| 3.1.1. U-GaN/AlGaN/u-GaN heterostructures                        | 62               |

| 3.1.2. P-GaN/GaN/AlGaN/GaN Heterostructures                      | 68               |

| 3.2. The AlN nucleation layer thickness                          | 76               |

| 3.3. Summary                                                     | 79               |

| Chapter 4. Fabrication and Evaluation of PSJ-on-Si Power device  | es81             |

| 4.1. Design objective                                            | 81               |

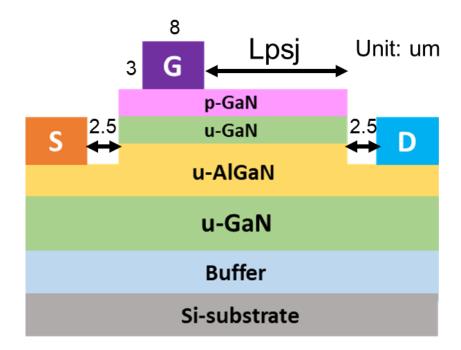

| 4.2. Device design information                                   | 82               |

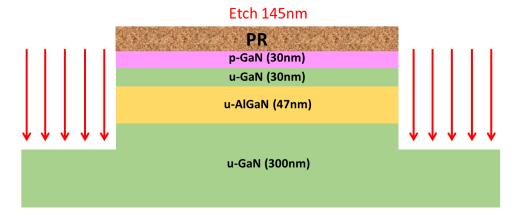

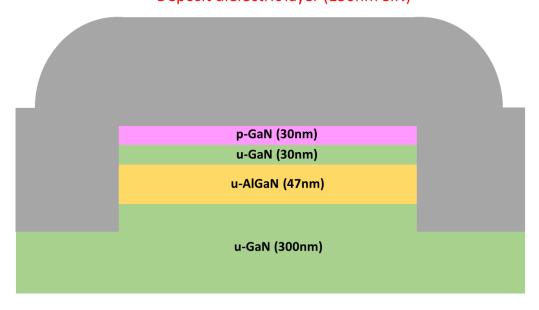

| 4.3. Device fabrication                                          | 83               |

| 4.4. Electric characterisation of fabricated PSJ-on-Si devices   | 83               |

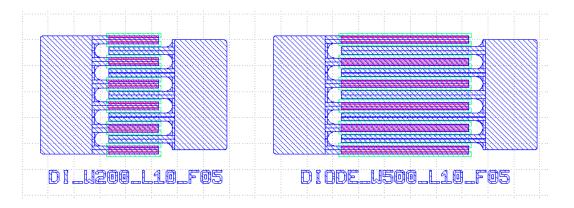

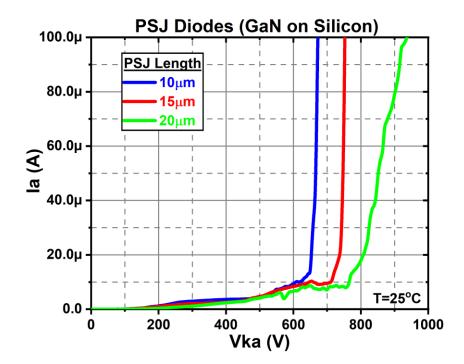

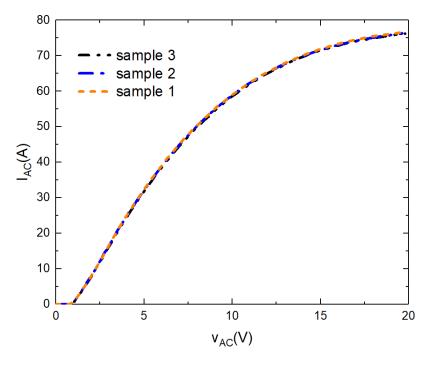

| 4.4.1. PSJ hybrid diodes (test structure)                        | 84               |

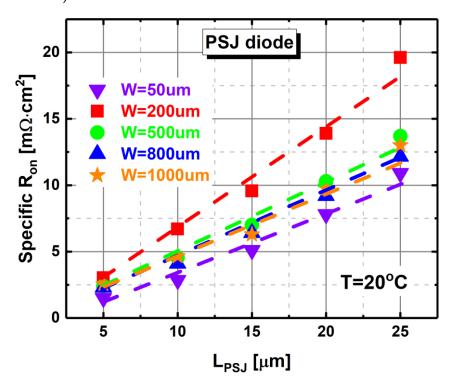

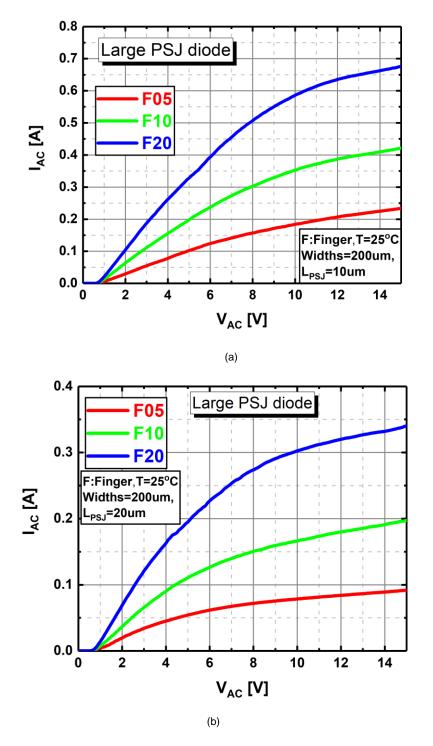

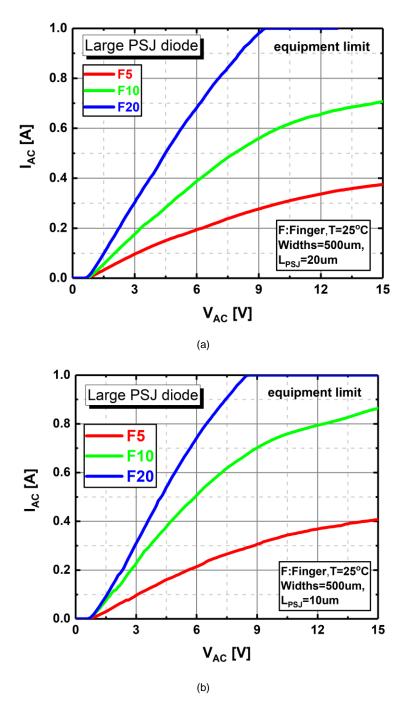

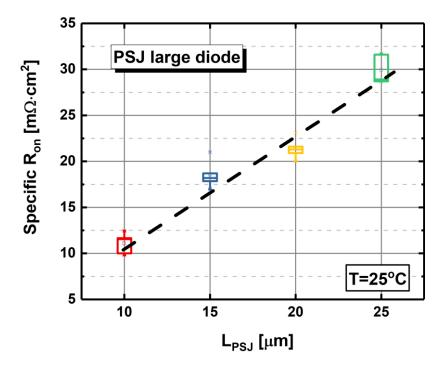

| 4.4.2. PSJ hybrid diodes(large-area)                             | 88               |

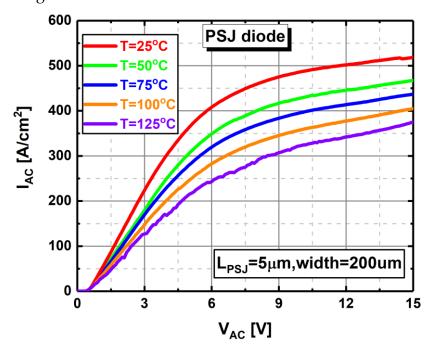

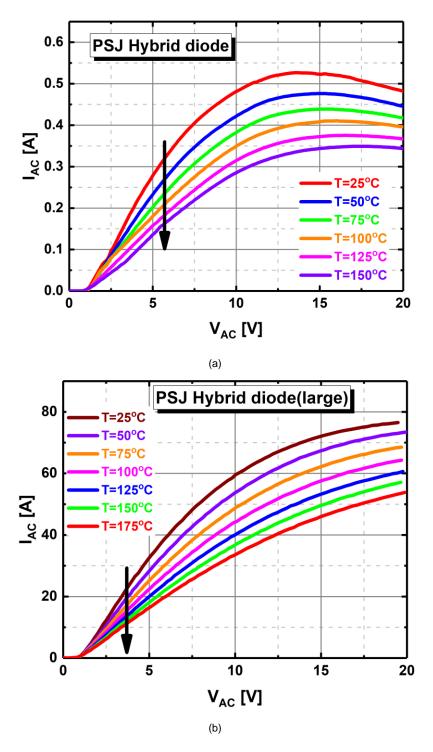

| 4.4.3. Temperature effects on PSJ hybrid diodes                  | 91               |

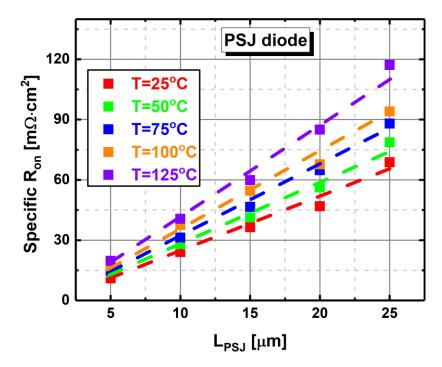

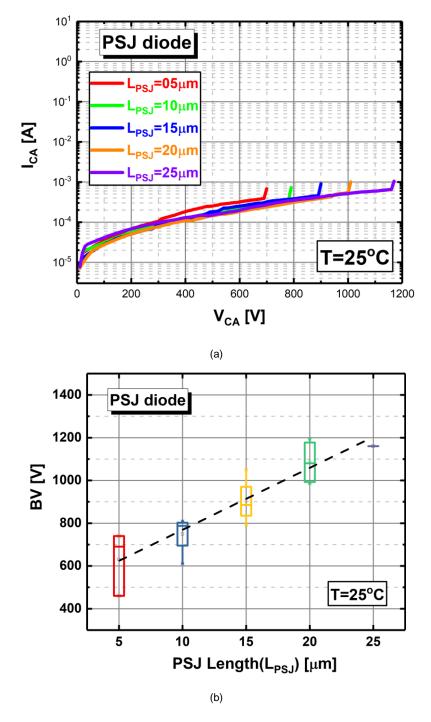

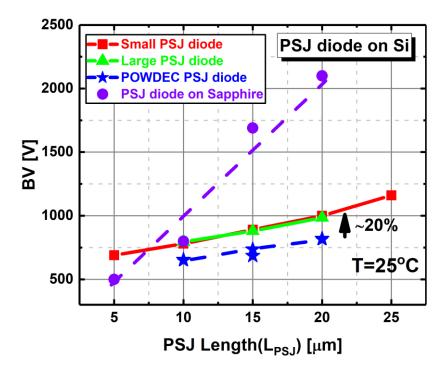

| 4.4.4. PSJ hybrid diode reverse blocking characteristics         | 93               |

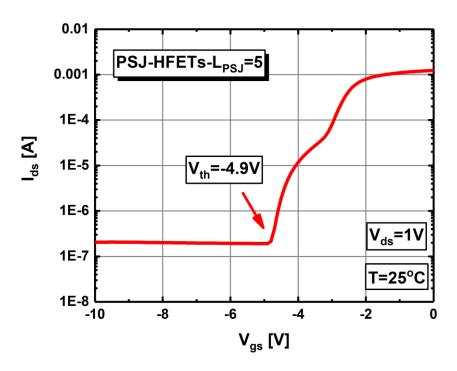

| 4.4.5. PSJ HFETs (I-V static characteristics)                    | 98               |

| 4.4.6. The Off-state Breakdown Voltage(BV) for PSJ HFETs         | 103              |

| 4.5. Summary                                                     | 106              |

| Chapter 5. Investigation of Shift in Threshold Voltages of 1.2kV | GaN Polarization |

| Superjunction (PSJ) HFETs                                        | 108              |

| 5.1. Threshold Voltage (Vth) shift in P-GaN gate PSJ HFETs       | 108              |

| 5.1.1. Introduction                                                        | 108       |

|----------------------------------------------------------------------------|-----------|

| 5.1.2. Device structure and dimensions                                     | 110       |

| 5.1.3. Pulse-mode measurement setup and conditions                         | 111       |

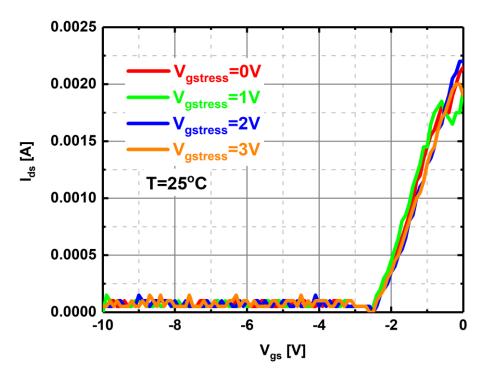

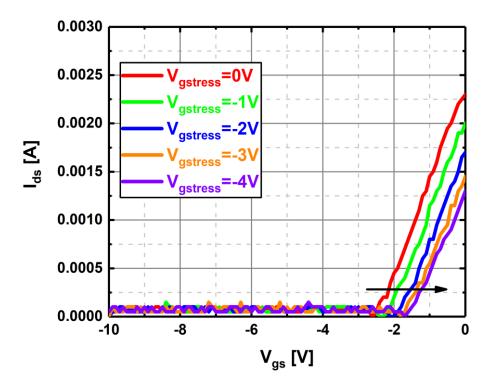

| 5.1.4. V <sub>th</sub> shift under positive gate stress voltages           | 113       |

| 5.1.5. Vth shift under negative gate stress voltages                       | 119       |

| 5.1.6. The Vth shifts under positive stress voltages as a function of terr | nperature |

|                                                                            | 123       |

| 5.2. Threshold Voltage (Vth) shift in Schottky gate PSJ HFETs              | 125       |

| 5.2.1. Devices structures, parameters and fabrication details              | 125       |

| 5.2.2. Vth shift under positive and negative gate stress voltage           | 126       |

| 5.3. Summary                                                               | 128       |

| Chapter 6. GaN Polarization Superjunction diode current saturation beha    | viour130  |

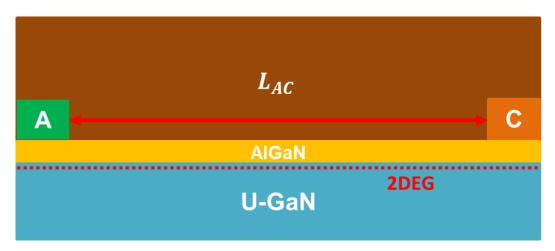

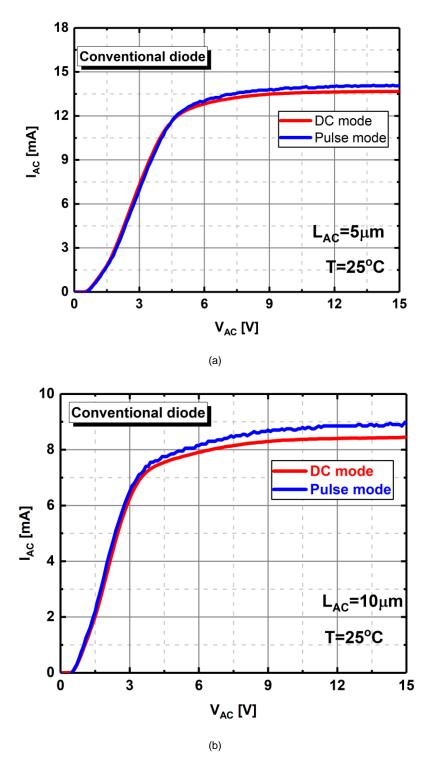

| 6.1. Current saturation behaviour in conventional AlGaN/GaN diode          | 130       |

| 6.1.1. Device structures and Measurement results                           | 130       |

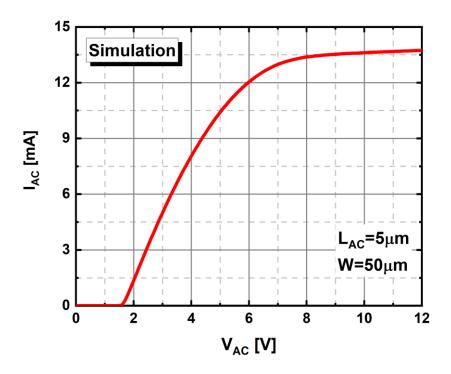

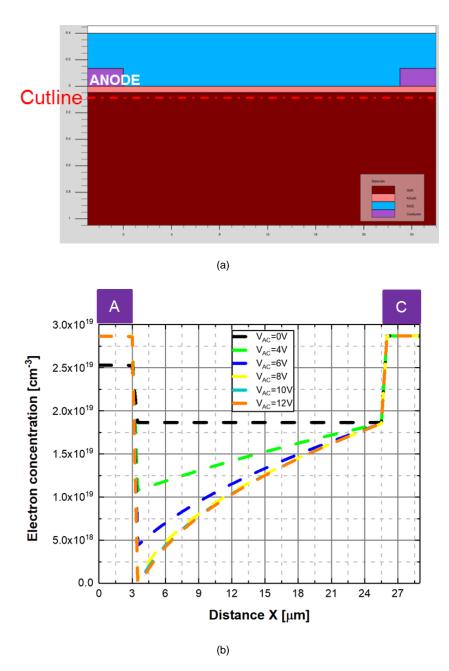

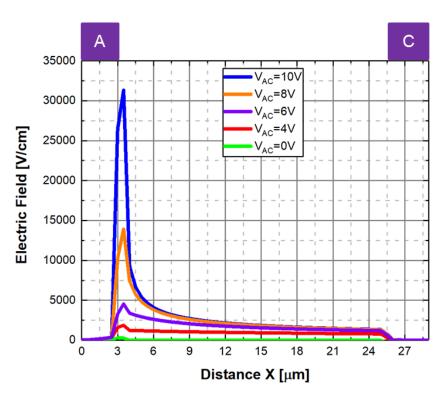

| 6.1.2. Simulation results and analysis                                     | 133       |

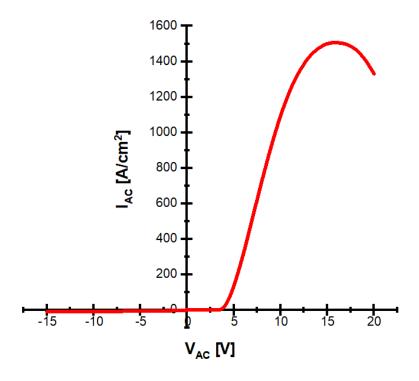

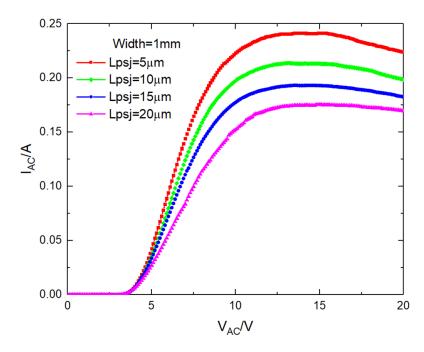

| 6.2. PSJ Hybrid diode current saturation behaviour                         | 136       |

| 6.2.1. Introduction                                                        | 136       |

| 6.2.2. Measurement results                                                 | 137       |

| 6.2.3. Simulation results and analysis                                     | 139       |

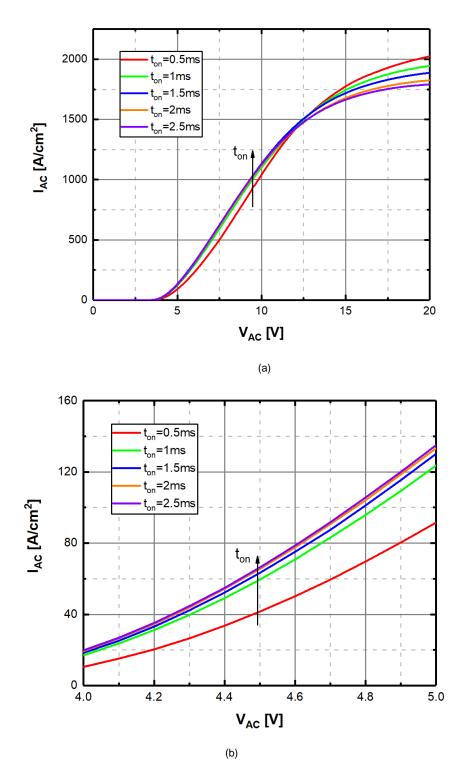

| 6.3. Current saturation behaviour in PSJ PiN diode                         | 144       |

| 6.3.1. Introduction                                                        | 144       |

| 6.3.2. Device structures and measurement results                           | 145       |

| 6.3.3. Conductivity modulation evaluation in PSJ PiN diode                 | 147       |

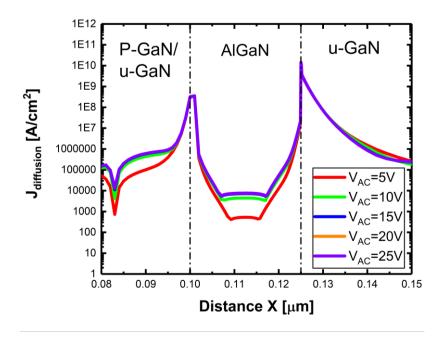

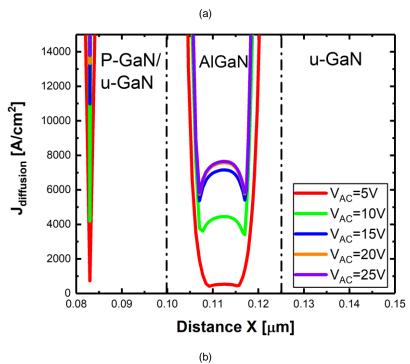

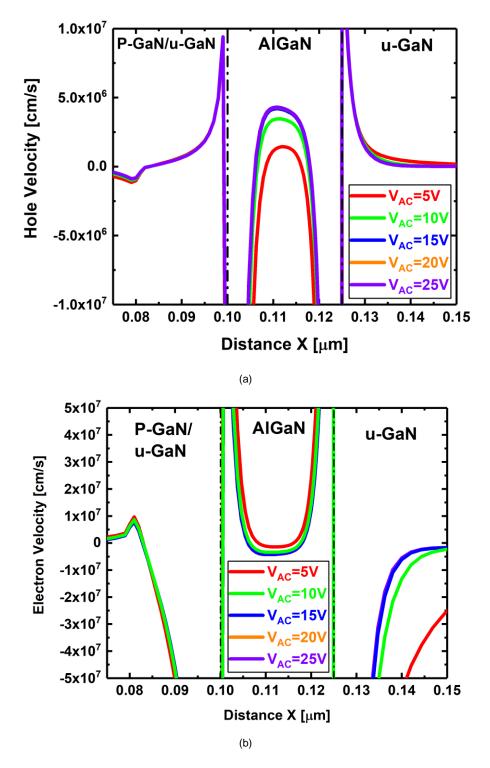

| 6.3.4. Trap effects on the current saturation                                       | 150       |

|-------------------------------------------------------------------------------------|-----------|

| 6.4. Summary                                                                        | 157       |

| Chapter 7. Gate leakage current mechanisms of PSJ HFETs                             | 159       |

| 7.1. Introduction                                                                   | 159       |

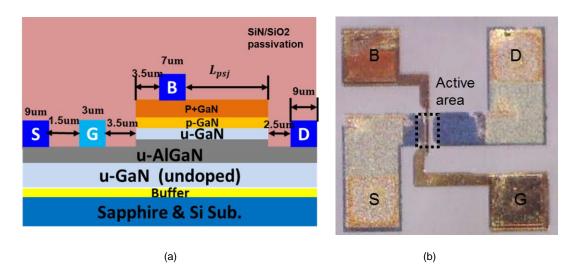

| 7.2. Device structures and parameters                                               | 161       |

| 7.3. Electric static characteristics of devices                                     | 162       |

| 7.4. Gate leakage current measurement results                                       | 162       |

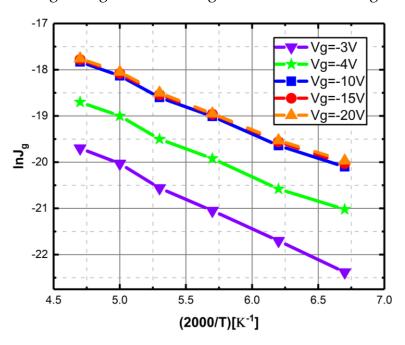

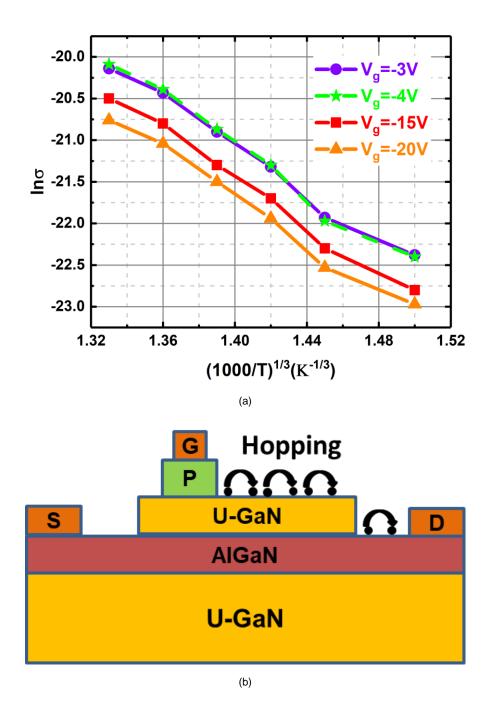

| 7.5. Mechanisms of gate leakage Current at the saturation region ( $V_g \le V_{th}$ | =-5V)164  |

| 7.6. Mechanisms of gate leakage current at the non-saturation region (Vg            | ≥Vth=-5V) |

|                                                                                     | 168       |

| 7.7. Summary                                                                        | 171       |

| Chapter 8. Conclusions and Future work                                              | 172       |

| 8.1. Conclusions                                                                    | 172       |

| 8.2. Future work                                                                    | 175       |

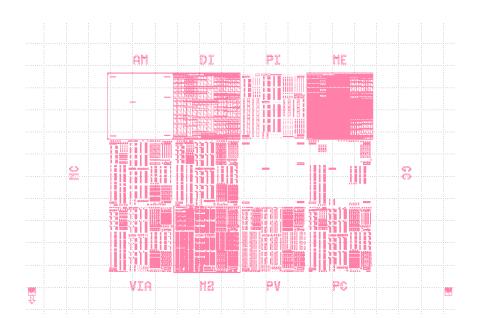

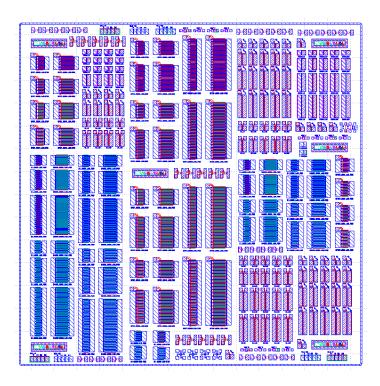

| Appendix-1                                                                          | 178       |

| Mask design                                                                         | 178       |

| Sample dicing size and cleaning preparation steps                                   | 181       |

| Fabrication process flow                                                            | 182       |

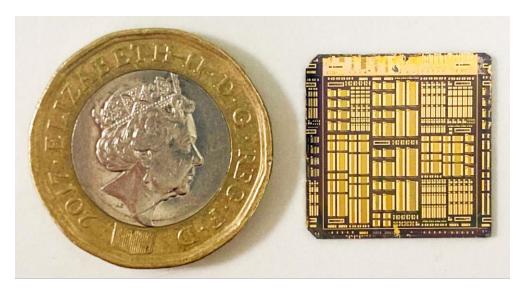

| Fabricated devices/sample                                                           | 187       |

| Appendix-2: References                                                              | 188       |

| Appendix-3: List of Figures                                                         | 207       |

| Appendix-4: List of Tables                                                          | 221       |

# Chapter 1. Introduction

#### 1.1. Overview

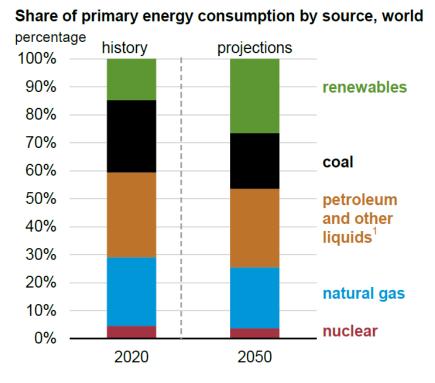

The International Energy Outlook 2021 states that total world energy consumption has grown from around 550 quadrillions (10<sup>15</sup>) British thermal units(Btu) in 2010 to about 600 quadrillions Btu in 2020 shown in Figure 1.1[3]. Although it dropped slightly during 2020 because of the pandemic of COVID-19 and climate change, the world's energy consumption is predicted to be back to the pre-pandemic level. It will keep increasing until 2050 due to economic and population growth[3]. However, as Figure 1.2 illustrates, the primary energy consumption composition is expected to be changed in 2050 [3]. The

# World energy consumption quadrillion British thermal units

Figure 1.1 World energy consumption: history and projection from 2010-2050 [3].

Figure 1.2 Share primary energy consumption by source in 2020 and the prediction in 2050[3].

renewable energy source is projected to increase from around 15% in 2020 to 25% in 2050. Still, the traditional fossil fuel, including coal, natural gas, petroleum and other liquids, will decrease due to the lowering of greenhouse gases emission and minimising the global warming effects.

However, renewable energy sources cannot be regarded as a reliable supply of energy to support economic growth and technological advancement. Moreover, due to the high expenses of equipment and transportation, the price of renewable energy is much higher than that of fossil fuel, causing more severe problems in economic growth and other social issues.

Energy efficiency improvement and waste reduction are hot topics because of the rising demand for energy and the anticipated shortage in the following decades. Electricity power, a renewable source, is widely used in power

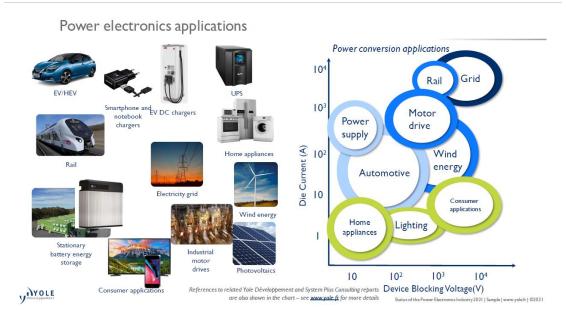

Figure 1.3 Power electronics applications[4].

electronic systems. Enhancing energy efficiency and reducing energy waste in power electronic systems are therefore essential

Power electronic systems have various applications due to the widespread and rapid advancement of electronic technology over the past few decades. Yole development reported the status of the power electronic industry applications in 2021[4]. According to the die current and the device blocking voltage of power electronics, the applications range from consumer applications, home appliances, and lighting to industrial motor drives, power supply, wind energy, automotive, rail, electricity grid, etc. [4].

## 1.2. Introduction of Power semiconductor devices

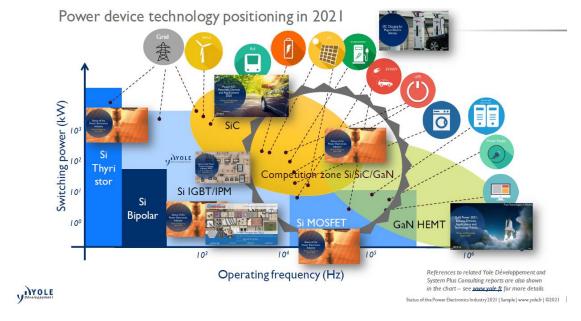

Power semiconductor devices play a critical role in power electronic systems. Due to the wide range of applications mentioned above, the devices are required to operate under different conditions to meet the various requirements. Figure 1.4 presents the positioning of the power semiconductor devices technology concerning the operating frequency in 2021[5]. Silicon(Si) power devices, including Si thyristor and IGBT (Insulated Gate Bipolar Transistor), are mainly operated under relatively low operating frequency (below 10<sup>4</sup> Hz) but relatively high switching power[5]. However, metal-oxide semiconductor field-effect transistors (Si MOSFETs) are employed at a relatively higher frequency.

Figure 1.4 Power device technology positioning in 2021[5].

Recently, Wide Band Gap (WBG) material-based, such as silicon carbide (SiC) and gallium nitride (GaN), power devices are emerging as competitive alternatives which are due to their inherent material properties. As Figure 1.4

illustrates, GaN-based power devices are gaining popularity because of their extremely fast switching speed and relatively low switching loss[5]. However, compared with Si and SiC-based power devices, GaN-based power devices are mainly utilised for low-power applications (the maximum rated voltage for commercial GaN power devices is below 650V). Therefore, the technology for enhancing the breakdown voltage for GaN power devices is becoming essential. GaN Polarisation Superjunction (PSJ) technology combines the polarisation effects and superjunction technology, significantly increasing the breakdown voltage of GaN power devices (over 2kV). All these advantages make GaN PSJ power devices the most competitive candidates for next-generation technology for GaN power devices.

However, as an emerging technology, more topics on the characterisation of GaN PSJ power devices are still under investigation to further understand their mechanisms and improve their performances. This thesis is devoted to exploring the impacts from the top u-GaN and AlN nucleation layer thickness on the sheet density of 2DEG and 2DHG, respectively, the performances of the PSJ power devices on Si substrates, PSJ diode current saturation behaviour and PSJ gate performance and reliability.

# 1.3. Thesis organisation

The structure of the thesis is as follows:

The background information about the current condition, energy consumption projections, and the use of power electronic devices are briefly introduced in Chapter 1.

GaN material physical characteristics and the basic idea of polarisation effects in AlGaN/GaN heterostructures are initially covered in chapter 2. Additionally, the origin of 2DEG and the fundamental electric properties of the GaN High Electron Mobility Transistor (HEMT) in the context of the application to power devices are presented. Moreover, examples of the device structures and operational principles in both the on-state and off-state are given. However, because of the uneven electric field distribution, conventional AlGaN/GaN HEMTs are unable to block the high voltage. Additionally, examples of the RESURF and Field-plate approaches for managing the electric field, frequently employed in conventional GaN power devices, are provided. Additionally, the operational principles of the PSJ Heterostructures Field effect transistors (HFETs) and diodes, as well as the polarisation Superjunction (PSJ) as a compensation idea for optimising the electric field distribution and boosting the breakdown voltage are discussed in detail.

Theoretical analysis of the 2DEG and 2DHG sheet densities in various PSJ heterostructures is covered in Chapter 3 as a function of the top u-GaN layer. Following the theoretical analysis approach and measurements, the effects of the SiO2 passivation layer, such as thickness and other impacts, on the density

of 2DEG and 2DHG are examined. Furthermore, the impacts of introducing the AlN nucleation layer in the PSJ heterostructures on the sheet density of 2DEG are also reported.

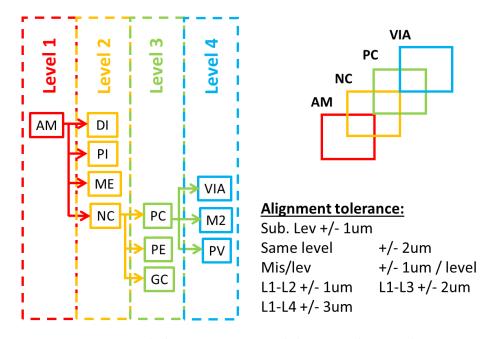

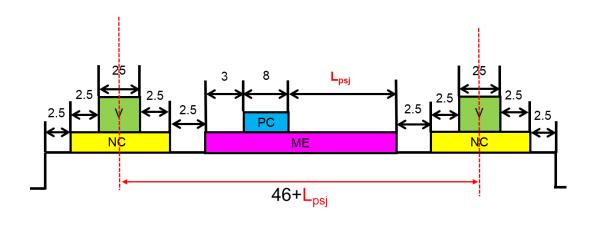

Chapter 4 describes the details of the PSJ-on-Si power devices fabricated at the University of Sheffield, including the fabrication process flow, alignment rules, mask design and electric performance. Also, the measured on-state performance and breakdown performances of PSJ HFETs and diodes are presented.

In chapter 5, the threshold voltage (V<sub>th</sub>) shift mechanisms of 1.2kV P-GaN gate PSJ HFETs are investigated based on the pulsed-mode measurement results under different gate stress voltages. Furthermore, the temperature effects on the shifts are also discussed. As a comparison, the V<sub>th</sub> shift performances are also investigated in PSJ Schottky gate HFETs.

In chapter 6, the PSJ diode current saturation behaviour is first reported, and their mechanism is investigated. The current saturation behaviour of the unipolar GaN power diodes, including the PSJ hybrid diode and conventional AlGaN/GaN diode, is discussed. Velocity saturation in the pinch-off region is the main cause of this phenomenon. However, the current saturation behaviour mechanisms in the bipolar PSJ PiN diode are different. The localised and negligible conductivity modulation, together with the trap effects, causes saturation behaviour.

In chapter 7, the gate leakage current mechanisms of P-GaN gate PSJ HFETs are reported and discussed in detail.

The study described in this thesis is concluded in Chapter 8, and future research and future research work are also discussed.

# Chapter 2. Background of Gallium Nitride (GaN) HFETs

The physical material properties of Gallium Nitride (GaN) are first mentioned in this chapter. The polarisation effects and the origin of 2DEG in the AlGaN/GaN heterostructures are then thoroughly explored. The operation principles and electrical characteristics of conventional AlGaN/GaN High Electron Mobility Transistors (HEMTs) are also introduced. The technologies for managing the electric field in power devices are also presented, including the field plate (FP), RESURF, and Superjunction (SJ) technologies. Finally, the concept and structure of GaN Polarisation of Superjunction (PSJ) are introduced and their advantages are explained.

# 2.1. GaN Material Property

One of the III-V wide bandgap semiconductor materials is gallium nitride (GaN) [6]. Table 21 lists some of the inherent Si properties as well as the key wide bandgap semiconductor features for Si, diamond, 4H-SiC, and GaN[7]. Wide bandgap semiconductor materials, such as 4H-SiC and GaN, can attain greater breakdown voltages than Si because they have a higher critical electric field [8]. Si, GaN, and diamond, which have high electron mobility, may have comparatively low on-state resistance and fast switching speed, indicating that

Table 2-2 Main figures of merit for WBG semiconductors compared with Si[9], [10]

| FOM                                        | Si | 4H-SiC | GaN  | Diamond |

|--------------------------------------------|----|--------|------|---------|

| BFOM                                       | 1  | 488    | 2414 | 8964    |

| $(\epsilon_r \cdot \mu \cdot E_c^3)$       |    |        |      |         |

| BHFOM                                      | 1  | 62     | 221  | 762     |

| $(\mu \cdot E_c^2)$                        |    |        |      |         |

| JFOM                                       | 1  | 366    | 1287 | 4322    |

| $(E_c \cdot v_{sat}/2\pi)_2$               |    |        |      |         |

| KFOM                                       | 1  | 4.0    | 1.6  | 31.5    |

| $(\lambda \cdot \sqrt{(vsat/\epsilon r)})$ |    |        |      |         |

| HMFOM                                      | 1  | 7.5    | 8    | 23.8    |

| $(E_c\sqrt{\mu})$                          |    |        |      |         |

| HCAFOM                                     | 1  | 65.9   | 61.7 | 220.5   |

| $(\varepsilon_r \sqrt{\mu} E_c^2)$         |    |        |      |         |

| HTFOM (λ/                                  | 1  | 0.6    | 0.1  | 1.7     |

| er · E <sub>c</sub> )                      |    |        |      |         |

they have low conduction and switching losses. The saturation velocities of GaN and SiC are almost double for Si, representing that they can operate at higher switching frequencies.

The critical parameters for assessing the performances for various purposes are the Figure of Merits (FOMs) for power devices, which mainly depend on the inherent material properties. The major FOMs of the semiconductor materials are presented in Table 2-1[9], [10]. Some of the critical indexes are introduced below. Baliga's Figure of Merit(BFOM), which is used to assess the conduction loss of power devices, is the product of on-state resistance and breakdown

voltage[11], [12]. The relative dielectric constant, electron mobility and critical electric field of the materials all affect this index. The product of the electric critical field and charge carrier saturation velocity is known as Johnson's figure of merit (JFOM).

Moreover, it is employed to calculate the maximum breakdown voltage and cut-off frequency. Baliga's high-frequency Figure of Merit, or BHFOM, assesses the switching loss of power field-effect transistors (FETs). KFOM is Keyes' FOM, which takes into consideration the thermal constraints on transistors' switching capabilities. Furthermore, several new FOMs are proposed to evaluate the power semiconductor devices by Alex Huang[13]. Huang's material figure of merit (HMFOM) is defined as the product of the critical electric field and carrier mobility, which is inversely proportional to the minimum total power loss. It takes into account both the switching losses and conduction losses[13]. Huang's device chip area figure-of-merit (HCAFOM) is inversely proportional to the optimal chip area. Higher HCAFOM represents the lower chip area[13]. Huang's thermal figure of merit (HTFOM) is used to evaluate the power devices' junction temperature rise under the given chip area and power losses[13].

GaN performs significantly better on BFOM, BHFOM, and JFOM than Si and SiC due to its excellent electrical material properties, which were previously described. However, the slight improvement in the KFOM of GaN indicates

that the thermal performances of GaN-based power devices have no apparent advantages over Si devices. According to HMFOM and HCAFOM, GaN is eight times lower on power loss than Si and 61.7 times smaller chip area than Si. The minimum HTFOM of GaN indicates that it has a higher junction temperature rise for operating similar conditions in these four materials[13]. Moreover, due these material properties, compared Si to MOSFETs(maximum 125 to 150°C), GaN high-electron-mobility transistors(HEMTs) can be operated at relatively higher temperatures(above 400-500°C) [14]-[16], which is a noteworthy benefit of GaN-based power devices [17].

# 2.2. Substrates for GaN Power devices

The market for commercial GaN power devices is currently dominated by lateral GaN power semiconductor devices. High-power GaN HEMTs operate at high voltages and simultaneously offer low on-state resistances.

The epitaxial crystal quality and the process significantly depend on the difference in the thermal expansion coefficients between the epitaxial layer and substrates. The increased dislocation density caused by the lattice mismatch between substrates and the GaN epitaxy layer possibly leads to a more significant leakage current under a high electric field [17]. It is detrimental to the static and dynamic electrical performances and the reliability of GaN power devices. GaN power devices can also function at high frequencies and temperatures because of the wide bandgap. As a result, GaN power device applications involving high voltage and high temperature also depend critically on the thermal constraints of the substrate [17].

GaN substrates have low thermal conductivity and no lattice mismatch, indicating low defect densities. The commercial market does not, however, favour expensive GaN materials. GaN heterostructures are subsequently produced epitaxially on foreign substrates [18]. The main substrates for GaN power semiconductor devices include sapphire, SiC, and silicon. According to the report[19], the first GaN transistors were grown on (0001) SiC and c-plane sapphire. Furthermore, due to the low costs of Si substrates, GaN-on-Si power

Table 2-3 properties of different Substrates for GaN power devices[7]

| Property                  | Sapphire            | SiC                 | Si                  | GaN           |

|---------------------------|---------------------|---------------------|---------------------|---------------|

| Lattice mismatch (%)      | 16                  | 3.1                 | -17                 | 0             |

| Linear thermal            | 7.5                 | 4.4                 | 2.6                 | 5.6           |

| expansion                 |                     |                     |                     |               |

| coefficient               |                     |                     |                     |               |

| $(\times 10^{-6} K^{-1})$ |                     |                     |                     |               |

| Thermal                   | 0.25                | 4.9                 | 1.6                 | 2.3           |

| conductivity (W           |                     |                     |                     |               |

| $cm^{-1}K^{-1}$           |                     |                     |                     |               |

| Cost                      | cheap               | expensive           | Cheap               | Very          |

|                           |                     |                     |                     | Expensive     |

| Dislocation density       | Low 10 <sup>8</sup> | Low 10 <sup>8</sup> | Low 10 <sup>8</sup> | $10^4 - 10^6$ |

| of GaN films grown        |                     |                     |                     |               |

| on                        |                     |                     |                     |               |

| substrate(optimized)      |                     |                     |                     |               |

| $(cm^{-2})$               |                     |                     |                     |               |

devices are becoming the leading choice for commercial GaN power devices. In Table 2-3 [7], the crucial characteristics of the various substrates, such as the dislocation density of GaN films produced on the substrate, thermal conductivity, lattice mismatch, and lattice thermal expansion coefficient are shown.

Threading dislocation density and significant lattice mismatch produce crystal defects, increasing the leakage current and trap states [17]. The dislocation densities of GaN films produced on Si, SiC, and sapphire substrates are about

10<sup>8</sup>, which is two orders of magnitude higher than GaN. Additionally, lattice mismatch for the epitaxially formed GaN layer (0001) on the c-plane sapphire and silicon substrate (111) is extremely high, at 16 and -17 percent, respectively. SiC substrates have the lowest lattice mismatch, with a value of just 3.1%.

The linear thermal expansion coefficient is another critical parameter for evaluating the epitaxial process's substrate effects. GaN layers differ significantly from Si or Sapphire substrates in terms of thermal expansion coefficient [20]–[22]. After the temperature dropped to room temperature, cracks began to occur in the GaN epitaxial layer on the substrate, notably for the thick GaN epitaxial films. It may also cause the generation of dislocations and defects along the GaN epitaxial layer.

GaN power devices work at rapid speeds and high-power densities, which results in significant heat generation. Heating effects degrade the current density and cause more power losses. As a result, another crucial factor is the thermal conductivity of the substrates. High substrate thermal conductivity helps the devices operate more effectively at high temperatures. SiC shows the highest thermal conductivity among three foreign substrates and becomes the best candidate for GaN power devices concerning thermal management. However, sapphire substrates have recently become more appealing for commercial use, including power integration applications and high-voltage

GaN power devices. The first GaN-on-sapphire power Integrated (IC) die was commercially available from Power Integrations in 2019 [23].

Moreover, Transphorm Inc. presented the first commercial 1200V GaN-on-sapphire power transistor with 99% efficiency power switching at ISPSD in 2022[24]. Even though the SiC substrate has a low lattice mismatch and good thermal conductivity, enabling it to be an ideal substrate for GaN high-power devices, the commercial market does not favour SiC due to its high cost. However, the sapphire substrate has lower manufacturing cost and is less influenced by temperature in manufacturing. These advantages make it one of the most competitive candidates for GaN power devices[24].

Although Transphorm Inc. has proved that GaN-on-sapphire shows good electrical performances and will be commercially available[25], the sapphire substrate is facing challenges. Low thermal conductivity and high lattice mismatch of sapphire substrates still need to be solved[24].

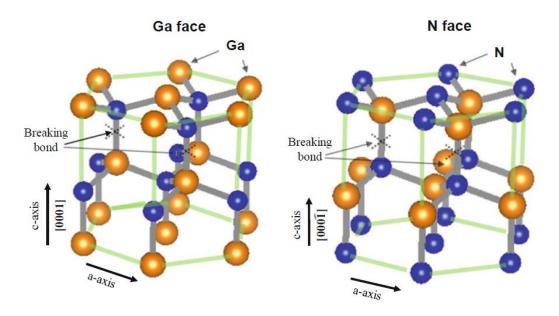

#### 2.3. Polarisation Effects

III-V compound semiconductor materials have wide applications in power, optoelectronic and RF-related semiconductor devices. The crystal formations of wurtzite, zinc blende and rock salt make up the three most prevalent III-V semiconductor materials. Furthermore, the wurtzite structure is the major crystal structure of the III-N(Nitride) semiconductors, including GaN, AlN, and InN [26]. The hexagonal close-packed (HCP) structure of wurtzite is depicted in the axial direction along the c-axis [0001] with the Ga- or N-face at the crystal's surface, respectively, as Figure 2.1 shows[7].

Figure 2.1 Wurtzite-type Hexagonal GaN crystal structure with Ga- or N-face at the surface of the crystal[7].

The chemical bond between Gallium and Nitride is ionic because the electronegativity of Ga and N atoms differs from one another. It demonstrates the reversed direction along the c-axis in the wurtzite structure with Ga- and N-face at the crystal surface, resulting in the various electrical properties in

GaN-based devices with Ga- and N-face. In III-nitrides semiconductors, there are two polarisation effects: spontaneous polarisation and piezoelectric polarisation [27].

## 2.3.1. Spontaneous Polarisation

Due to the difference in electronegativity between Ga and N atoms, polarisation results in a dipole leading to the spontaneous polarisation that occurred in the crystal structure of wurtzite GaN[27]–[29]. When an atom creates chemical bonds with other atoms, its ability to attract the shared electrons is known as electronegativity. In the GaN semiconductors, the electronegativity of nitrogen is higher than that of gallium. N atoms attract the shared electrons and show cationic (-) characteristics. Conversely, Ga atoms

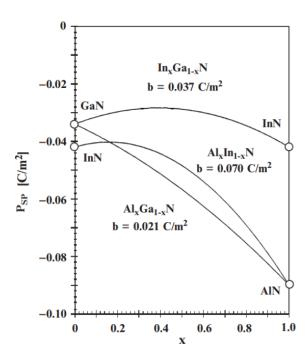

Figure 2.2 Spontaneous polarisation (Psp) coefficient in Al<sub>x</sub>Ga<sub>1-x</sub>N, In<sub>x</sub>Ga<sub>1-x</sub>N and Al<sub>x</sub>In<sub>1-x</sub>N as a function of Al mole fraction(x) [32].

show anionic characteristics. Therefore, electrical polarisation exists at a dipole across the chemical bonds [30]. GaN wurtzite crystal structure is not centrosymmetrical along the c-axis[31]. Thus, the polarisation at the dipoles from different orientations is neutralised inside the GaN material. However, the asymmetry of polarisation happens at the surface of GaN material, causing the net macroscopic polarisation, referred to as spontaneous polarisation (P<sub>sp</sub>).

Therefore, based on the prior explanation, the orientation of  $P_{sp}$  in the crystal structure of wurtzite GaN is parallel to the c-axis. GaN, AlN, and InN each have spontaneous polarisation coefficients of 0.029, 0.081, and 0.032  $C/m^2$ , respectively.

The expression of the spontaneous polarisation for  $Al_xGa_{1-x}N$ , which mostly depends on the mole fraction of Al(x), is [32][33]:

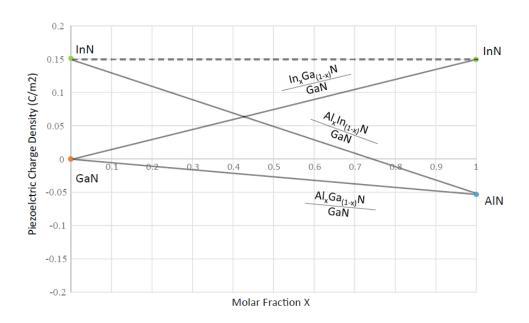

Figure 2.3 Theoretical calculation results of the piezoelectric polarisation charge density as a function mole fraction of Al or In in Al $_{\times}$ Ga1 $_{\times}$ N, In $_{\times}$ Ga1 $_{\times}$ N and Al $_{\times}$ In $_{1}$ XN[7].

$$P_{sp}(Al_xGa_{1-x}N) = -0.09x - 0.034(1-x) + 0.021x(1-x) C/m^2$$

(2.1)

Similar to this, Al mole fraction(x) and  $P_{sp}$  in AlxGa1-xN, InxGa1-xN, and AlxIn1-xN are also provided in Figure 2.2[32][33].

## 2.3.2. Piezoelectric Polarisation

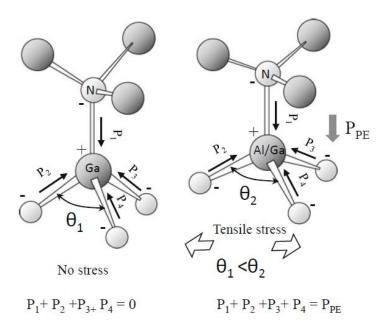

The mechanical stress or strain results in the polarisation effects and lattice mismatch because of the various lattice constants between different semiconductors. Thus the electric polarisation is named piezoelectric polarisation (Ppz). The mechanisms of piezoelectric polarisation are explained in Figure 2.4 [32].

As a result of a symmetrical tetrahedral crystal structure, the internal polarisation vectors ( $P_1+P_2+P_3+P_4$ ) between Ga and N atoms are equal to zero. However, due to the lattice mismatch, the tensile stress is generated in the

Figure 2.4 The polarisation field exists in the ionic bonds of the GaN tetrahedron structure with (right) and without (left) the mechanical stress[7].

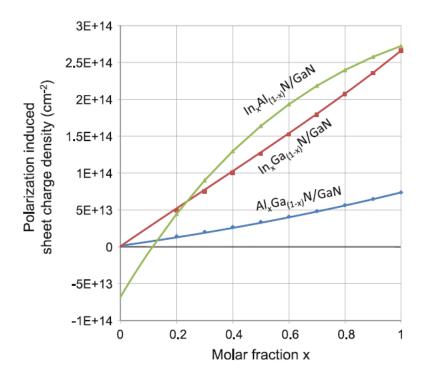

tetrahedral crystal structure of GaN. Therefore, as Figure 2.4 shows, when tensile stress is applied, angle 2 widens more than angle 1, resulting in a net polarisation field and an unbalanced polarisation electric field equivalent to P<sub>PZ</sub> (P<sub>1</sub>+P<sub>2</sub>+P<sub>3</sub>+P<sub>4</sub>= P<sub>PE</sub>) along [000-1]. On the contrary, in the case of N polarity, a similar net polarisation exists in the GaN tetrahedron, but the direction is reversed [0001] [7]. Figure 2.3 demonstrates the charge density caused by the piezoelectric polarisation of Al<sub>x</sub>Ga<sub>1-x</sub>N, In<sub>x</sub>Ga<sub>1-x</sub>N, and Al<sub>x</sub>In<sub>1-x</sub>N as a function of the mole fraction x [7].

In contrast, when a compressive strain is applied, angle 2 shrinks to a smaller value than angle 1, creating net polarisation in the [0001] direction for Ga polarisation and the [000-1] direction for N polarisation. [34].

F.Bernardini [10] reported that the expression of piezoelectric polarisation P<sub>PZ</sub> is:

$$P_{PZ} = 2\frac{a - a_0}{a_0} \left( e_{31} - e_{33} \frac{C_{13}}{C_{33}} \right) \tag{2.2}$$

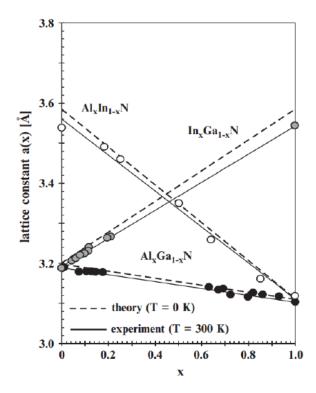

The material's lattice constants are represented by a and  $a_0$ , while the piezoelectric constants along the (x,y) and (z) directions are represented by  $e_{31}$  and  $e_{33}$ . The elastic constants are denoted by  $C_{13}$  and  $C_{33}$ . The piezoelectric polarisation constants of the GaN, InN and AlN binary semiconductor devices are displayed in Figure 2.5 [10][35].

However, for AlxGa1-xN, InxGa1-xN, and AlxIn1-xN, the lattice constant varies with the mole fraction (x) of metal (Al or In). From Figure 2.5, the relationship between the lattice constant and the mole fraction of Al or In is linear [9]. As a result, the piezoelectric polarisation follows equation (2) and is inversely proportional to the mole fraction of Al or In. The piezoelectric polarisation charge density in AlxGa1-xN, InxGa1-xN, and AlxIn1-xN is calculated as a function of the mole fraction of Al or In, assuming that they are all grown on a relaxed GaN layer[19][31]. The piezoelectric polarisation charge density for AlxGa1-xN/GaN exhibits a declining linear trend as the mole fraction of Al and In rises [7].

Figure 2.5 the theoretical and experimental lattice constant of Al<sub>x</sub>Ga<sub>1-x</sub>N, In<sub>x</sub>Ga<sub>1-x</sub>N and Al<sub>x</sub>In<sub>1-x</sub>N at T=0K and 300K, respectively[9].

## 2.4. AlGaN/GaN heterostructures and the formation of 2DEG

# 2.4.1. Polarisation charge

Following the previous discussions, it is clear that spontaneous and piezoelectric polarisation exists in III-V nitride heterostructures semiconductors. Ga- and N-face spontaneous and piezoelectric polarisation under various stress conditions are described in AlGaN/GaN heterostructures [31].

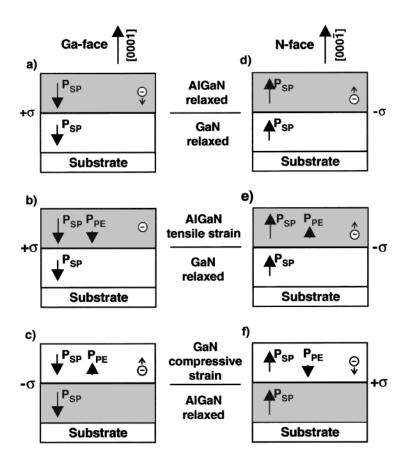

According to Figure 2.6, in AlGaN/GaN heterostructures with Ga face, the spontaneous polarisation in AlGaN and GaN layers is negative, indicating that

Figure 2.6 Spontaneous and piezoelectric polarisation with Ga-face and N-face induced sheet charge density under different conditions [35].

the polarisation vectors point toward the substrate [35]. In contrast, the spontaneous polarisation vectors in AlGaN and GaN layers have the opposite direction in N-face AlGaN/GaN heterostructures. It relies on the stress conditions, following the preceding concept of piezoelectric polarisation. When there is no stress between the AlGaN and GaN layer, there is no piezoelectric polarisation in the AlGaN/GaN heterostructures. When the tensile strain is delivered from the AlGaN layer to the relaxed GaN layer in the case of a Gaface, piezoelectric polarisation is created in the AlGaN layer.

Moreover, piezoelectric polarisation is parallel to spontaneous polarisation. On the other hand, when compressive-strained GaN is formed on the relaxed AlGaN layer, the antiparallel piezoelectric polarisation is detected in the AlGaN layer. However, piezoelectric and spontaneous polarisation have opposite directions if it switches from the Ga face to the N face.

The gradient of polarisation induces the sheet charge density ( $\sigma$ ) because it generates net polarisation between the AlGaN and GaN layers ( $\Delta P$ ). The following equation reported by O.Ambacher et al. [35]can express this relationship:

$$\sigma = \Delta P \tag{2.3}$$

$$\sigma = P(top) - P(bottom) \tag{2.4}$$

$$= [P_{sp}(top) + P_{PE}(top)] - [P_{sp}(bottom) + P_{PE}(bottom)]$$

$P_{sp}$  and  $P_{PE}$  denote spontaneous polarisation and piezoelectric polarisation, respectively.

In the AlGaN/GaN heterostructures, Equation (2.4) can be expressed by:

$$\sigma = P(AlGaN) - P(GaN)$$

$$= [P_{sp}(AlGaN) + P_{PE}(AlGaN)] - [P_{sp}(GaN)]$$

(2.5)

According to equation (2.5), the sheet polarisation charge density ( $\sigma$ ) is positive at the heterointerface. The free electrons are accumulated to balance the polarisation charge density. On the other hand, positive holes can be induced to achieve charge neutrality by the negative polarisation charge.

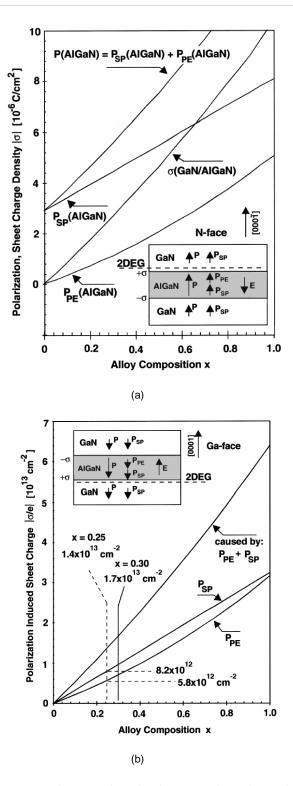

The calculation method can also be applied to double heterostructures GaN/AlGaN/GaN. The calculated sheet charge density as a function of the Al mole fraction in the N-face and Ga-face GaN/AlGaN/GaN heterostructures are depicted in Figure 2.7(a) and (b), respectively. The expression of the total polarisation sheet charge density for N-face GaN/ Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterostructures as a function of Al-content is [31]:

$$|\sigma(x)| = \left| \left[ P_{sp}(AlGaN) + P_{PE}(AlGaN) \right] - \left[ P_{sp}(GaN) \right] \right|$$

$$|\sigma(x)| = \left| 2 \frac{a(0) - a(x)}{a(x)} \left\{ e_{31}(x) - e_{33}(x) \frac{C_{13}(x)}{C_{33}(x)} \right\} + P_{SP}(x) - P_{SP}(0) \right|$$

(2.12)

For the Ga-face GaN/Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN, the spontaneous polarisation, piezoelectric polarisation, and total polarisation-induced sheet charge density are displayed as a function of Al-content(x) in Figure 2.7 (b) [31]. The calculated polarisation sheet charge density as a function of Al mole fraction in Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN, In<sub>x</sub>Ga<sub>1-x</sub>N/GaN and Al<sub>x</sub>In<sub>1-x</sub>N/GaN heterostructures are shown in Figure 2.8.

Figure 2.7 (a)The spontaneous, piezoelectric and total polarisation sheet charge density as a function of Al-content in the N-face GaN/ AlxGa1-xN/GaN heterostructures(b)the polarisation induced sheet charge density[31].

Moreover, the maximum sheet carrier concentration is expressed as a function

of Al content [36]:

$$n_{s}(x) = \frac{+\sigma(x)}{e} - \left(\frac{\epsilon_{0}\epsilon_{x}}{de^{2}}\right) \left[e\phi_{b}(x) + E_{F}(x) - \Delta E_{C}(x)\right]$$

(2.13)

Where e is the electronic charge and d is the barrier thickness of Al<sub>x</sub>Ga<sub>1-x</sub>N.

Furthermore,  $e\phi_b$  stands for the Schottky barrier of the Schottky gate contact.

The Fermi level and the conduction band offset are denoted by  $E_F$  and  $\Delta E_C$ , respectively.

Figure 2.8 Theoretical calculation results of the polarisation induced sheet charge density as a function of Al or In molar fraction(x) in Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN, In<sub>x</sub>Ga<sub>1-x</sub>N/GaN and Al<sub>x</sub>In<sub>1-x</sub>N/GaN heterostructures[36].

# 2.4.2. Origin of 2DEG

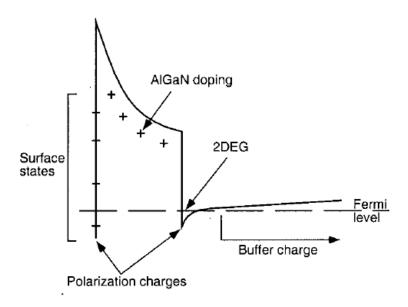

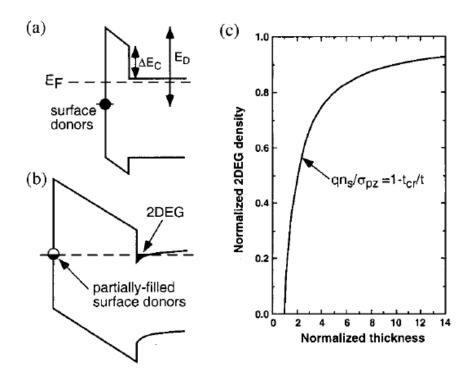

M.Asif Khan et al. initially discovered that undoped Al<sub>0.13</sub>Ga<sub>0.87</sub>N/GaN heterostructures contain two-dimensional electron gas (2DEG) with a sheet density of 2.6×10<sup>-12</sup> cm<sup>-2</sup> at 7 k [37]. Moreover,2DEG mobility was 834 cm<sup>2</sup>/Vs at room temperature [37]. With decrease in temperature, 2DEG mobility monotonically increased and gradually saturated at 2626 cm<sup>2</sup>/Vs at 77K [37]. At present, the surface-donor model is widely accepted as the main theory of the origin of 2DEG. J.P.Ibbetson et al. [38] formulated and then experimentally supported the theory of the origin of 2DEG in AlGaN/GaN HFETs. According to electrostatics theory, the surface states are relevant to the source of 2DEG. Figure 2.9 shows the AlGaN/GaN conduction band diagram with different space charge components:(1) negative charge due to 2DEG(n<sub>s</sub>);(2) polarisation-induced charges located at the AlGaN/GaN hetero-interface(σ<sub>PZ</sub>);(3)the

Figure 2.9 conduction band diagram of AlGaN/GaN HFET with different space charge components [38].

ionised-donors induced sheet charge in the AlGaN( $\sigma_{AlGaN}$ );(4)the ionised-surface-states induced charge( $\sigma_{surface}$ ); and,(5)buffer charge( $\sigma_{buffer}$ ). According to the theory of the polarization, the total polarization-induce charges composed by the a dipole contributes zero to the total space charge in the AlGaN/GaN heterostructures. Moreover, the magnitude of the buffer charge is assumed as low as possible in the well-designed FETs and can be neglected. Therefore, the space charges should follow the charge neutral principles, indicating that the 2DEG sheet density is equal to the sum of the  $\sigma_{surface}$  and  $\sigma_{AlGaN}$ . In the undoped AlGaN/GaN heterostructures,  $\sigma_{AlGaN}$  is zero, representing that sheet density of the 2DEG is dominated by the surface states. The idea argues that the ionised

Figure 2.10 schematic band diagram of the surface-donor model under different AlGaN thicknesses:(a)less than(b)more than the critical thickness. (C)The theoretical relationship between 2DEG density and AlGaN barrier thickness is based on the surface donor model[38].

donor or acceptor-like surface states have a significant influence on the 2DEG sheet density. This is called the surface-donor model.

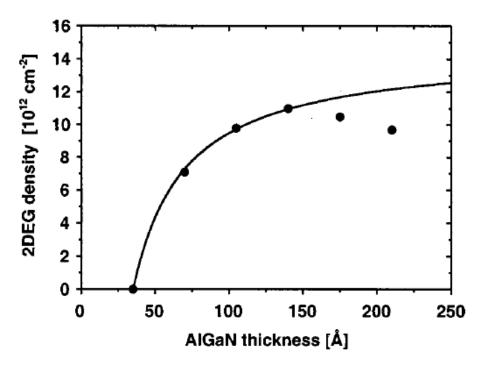

Figure 2.11 shows the measured and calculated 2DEG sheet density as a function of  $Al_{0.34}Ga_{0.64}N$  barrier thickness at room temperature [39].

Figure 2.10 demonstrates the relationship between the AlGaN barrier thickness and 2DEG sheet density [38]. Based on the surface donor model, electrons cannot transfer to the AlGaN/GaN interface when the surface donor energy is below the Fermi level, and the AlGaN barrier thickness is below the critical thickness. However, once it reaches the critical thickness, the surface donor energy hits the Fermi level, allowing electrons to move from the filled surface states to the AlGaN/GaN interface as illustrated in Figure 2.10 (b) [38].

Figure 2.11 demonstrates the relationship between 2DEG density and AlGaN thickness, including measured and calculated results [39]. When the AlGaN

thickness goes above the critical thickness, it is possible to see that 2DEG density increases (around 3nm) and then gradually saturates. This trend is

Figure 2.12 The relationship between 2DEG and 2DHG sheet density and carrier mobility as a function of GaN cap layer thickness in GaN/AlGaN/GaN double heterostructures [33].

Figure 2.13 schematic band diagram of (a) AlGaN/GaN heterostructures; GaN/AlGaN/GaN double heterostructures with a(b) thin GaN cap layer(C) thick GaN cap layer [39].

consistent with the outcome obtained based on the theory of the surface-donor model. However, other models, such as surface-pinning model, can also explain the data shown in Figure 2.11. And other questions in the surface donor model, for example, whether the surface donors are intrinsic or impurity-related, are still unknown. Therefore, although the surface-donor model is controversial and debatable, it is the widely accepted theory of the origin of 2DEG.

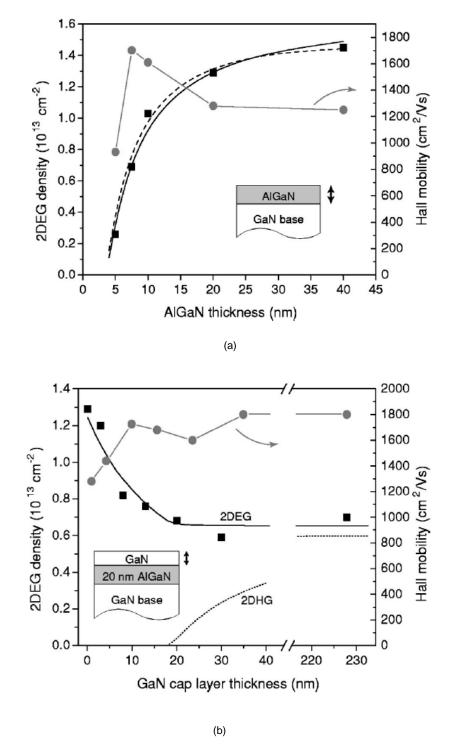

Heikman et al. also reported similar research findings, which also supported the theory of the surface donor model [39]. The 2DEG density and hall mobility is also provided as a function of AlGaN thickness in Figure 2.12(a) [39].

Moreover, GaN cap layer thickness impacts sheet density and hall mobility are also documented in Figure 2.12 (b) in GaN/AlGaN/GaN double heterostructures. As the thickness of the GaN cap layer increases, the density of the 2DEG density decreases, going from about 1.3×10<sup>13</sup> cm<sup>-2</sup> with no cap layer to  $0.7 \times 10^{13}$  cm<sup>-2</sup> with a 20nm GaN cap layer. The 2DEG sheet density reaches saturation at a thickness greater than 20nm. However, no 2DHG is seen when the GaN cap layer thickness is less than 17nm, and 2DHG density increases when the thickness is more than 17nm. The carrier hall mobility slightly decreases with the rise of the 2DEG sheet density. The reduction in mobility is caused by the increased coulomb scattering.

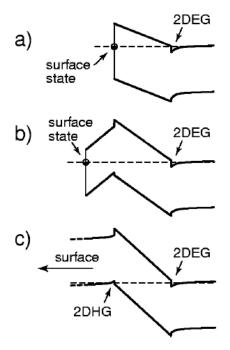

Figure 2.13 explains the reasons based on the surface donor model. In AlGaN/GaN heterostructures, donor states at the surface hold the Fermi level

Figure 2.14 2DEG sheet density as a function of Al composition of AlGaN in AlGaN/GaN heterostructures [40].

in place. When a GaN cap layer is grown on top of AlGaN/GaN heterostructures, negative polarisation charges are generated at the hetero-interface, raising the electric fields in the AlGaN layer and lowering the 2DEG density. As the GaN cap layer gets thicker, the valence band level rises. Until the thickness exceeds the critical thickness and the valence band energy reaches the Fermi level, 2DHG is formed at the GaN cap layer/AlGaN interface.

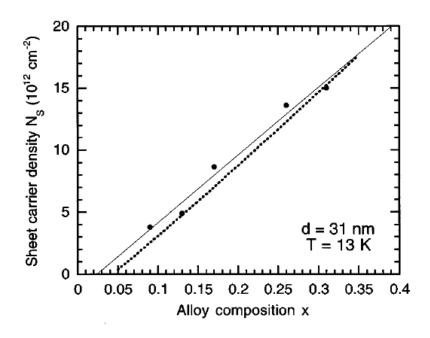

In addition, the 2DEG sheet density is also varied with the Al content of AlGaN and the relationship is reported in [40]. Figure 2.14 illustrates the linear relationship between 2DEG sheet densities and Al composition.

#### 2.5. Conventional AlGaN/GaN High Electron Mobility Transistor (HEMT)

Heterostructures based field-effect transistors were first invented through the MBE-grown doped GaAs/n-AlGaAs in 1980 [41]. Conventional AlGaAs/GaAs HEMTs are grown on the GaAs substrate. Additionally, it contains the n-type doped AlGaAs layer as well as the undoped AlGaAs space layer and GaAs layer. 2DEG is constrained at the AlGaAs/GaAs heterointerface. The n-doping concentration and the electronic states at the AlGaAs/GaAs interface potential have the most remarkable effects on the 2DEG concentration(roughly 1.0×10<sup>12</sup> cm<sup>-3</sup>)[42].

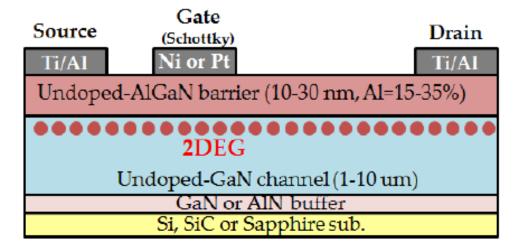

Conventional AlGaN/GaN HEMTs were firstly invented in 1993[43], [44]. Compared with the AlGaAs/GaAs HFETs, conventional AlGaN/GaN HEMTs have a simplified structure but have similar electrical characteristics. The diagram below depicts the schematic cross-section of the conventional AlGaN/GaN HEMTs in Figure 2.15 [45].

Figure 2.15 The schematic cross-section of conventional AlGaN/GaN HEMTs [45].

AlGaN/GaN HEMTs frequently use Si, SiC, or sapphire substrates. Above the substrate, a buffer layer made of GaN or AlN, an undoped GaN layer, and a barrier layer made of undoped AlGaN are all consecutively grown. On the AlGaN layer, there are three electrodes: the gate (G) contact forms the Schottky contact, while the source (S) and drain (D) contacts are Ohmic to the 2DEG. Due to the high mobility and high density of 2DEG, AlGaN/GaN HEMTs have low conduction and switching losses, making them one of the most appealing alternatives for power electronic applications.

#### 2.5.1. The operation principle of conventional AlGaN/GaN HEMTs

Conventional AlGaN/GaN HEMTs are lateral devices. 2DEG channel forms the conduction path when no gate biases are applied, representing that they are the normally-on devices. Therefore, the expression of V<sub>th</sub> in the conventional AlGaN/GaN HEMTs is [34]:

$$V_{th} = \phi_b - \frac{\Delta E_c}{e} - V_p - \frac{ed}{\varepsilon} (\sigma + N_B W_d)$$

(2.15)

Where  $\phi_b$  is the Schottky barrier height of the gate, $\Delta E_c$  denotes the conduction band offset, d is the total thickness of the AlGaN barrier layer, and  $\sigma$  denotes the interfacial polarisation charge.  $N_B$  and  $W_d$  denote the doping density in the bulk and depletion width in the channel, respectively.  $V_p = qN_dd_d^2/2\varepsilon$ , where  $N_d$  is the AlGaN barrier layer's donor concentration, and  $d_d$  is the doped thickness of the barrier layer.  $\varepsilon$  is the dielectric constant of the AlGaN barrier layer. Based on equation (2.15), the AlGaN barrier layer thickness, Al content

and the barrier height of the Schottky gate are varied to alter the 2DEG sheet density, which primarily determines the threshold voltage.

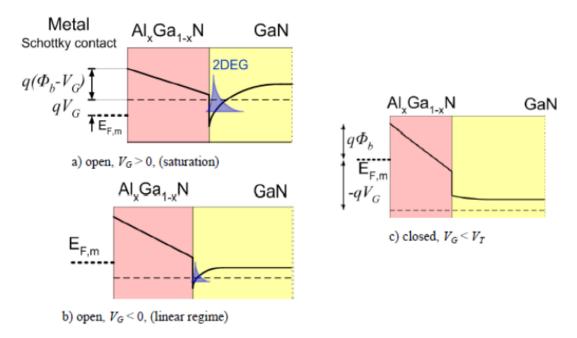

Figure 2.16 depicts the conduction band diagram of AlGaN/GaN HEMTs under different gate voltages [46]. Under the positive gate bias, the 2DEG channel is not depleted. When it becomes negative but higher than the threshold voltage, the conduction band are lifted, causing the reduction of 2DEG sheet density. However, when the gate voltage is lower than the threshold voltage, no quantum well can store 2DEG at the AlGaN/GaN interface when the conduction band is above the Fermi level.

Figure 2.16 conduction band diagram under different gate voltage(a)  $V_g$  is positive (b)0<Vg<V<sub>Th</sub> (C) Vg>V<sub>Th</sub> [46].

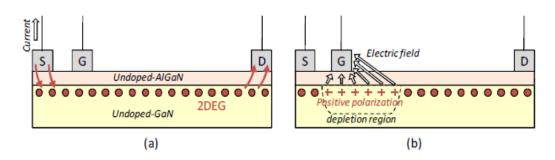

Figure 2.17 Schematic of a conventional HFET in (a) the ON-state and (b) the off-state[47].

Figure 2.17 explains the on-state and off-state operating principles of an AlGaN/GaN HEMT. Electrons flow through the 2DEG channel when the gate voltage rises beyond the threshold voltage. However, the 2DEG channel is depleted under the Gate region, disrupting the conduction path. Figure 2.17 (b) depicts the high electric field between positive polarisation charges in the depletion area and the gate electrode with negative biases causing the electric field to be crowded near the drain-side edge of the gate [47]. The electric breakdown of conventional AlGaN/GaN HEMTs occurs due to the high electric field peak exceeding the critical electric field. Therefore, enhancing the breakdown voltage is their main challenge for high-power applications.

## 2.5.2. Introduction of field-plate technology

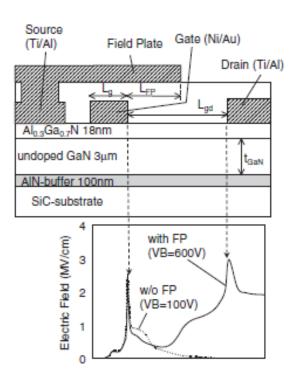

Several Field plate (FP) technologies are studied by W.saito et al. [48] for optimising the electric field management in AlGaN/GaN HEMTs to improve the inhomogeneous electric field distribution of the AlGaN/GaN HEMTs in the off-state. Single Field plate design (FP) was analysed in [48]. Several research also reports similar results of FP technology [49]–[53]. Figure 2.18 depicts the electric field distribution along the 2DEG channel with and without a single FP. The drain-side edge of the gate has a crowded electric field without using single FP technology, causing an extremely high electric field peak and low breakdown voltage (BV=100V). However, the highest electric field peak is

Figure 2.18 Cross-sectional structures of fabricated AlGaN/GaN HEMT with field plate structure (FP-HEMT) and electric field distribution along with the AlGaN/GaN interface layer with field plate (solid line) and without field plate (broken line)[54].

Figure 2.19 Comparison of electric field profile between single and double FP technology during off-state[54].

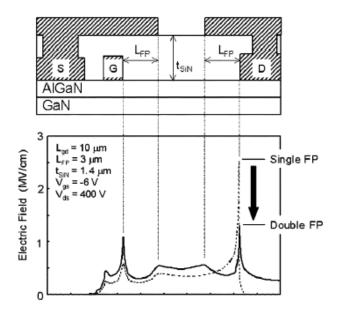

suppressed and shifted from gate to drain through FP design. Thus it optimises the electric field profile and enhances the BV from 100V to 600V. The single FP technique can increase not only breakdown voltage but also decrease gate leakage and hot electron generation[48]. Although the electric field peak of AlGaN/GaN HEMTs is somewhat flattened by the single FP design, the presence of these two peaks in the electric field profile suggests that the electric field distribution may be further optimised. Therefore, the double Field plate design was discussed in detail [54], which is thought to be a significant improvement in the breakdown voltage compared with the single FP design. Compared with the single FP technology, a drain field plate was added in the double FP design to suppress the high electric field peak at the drain, which is where the electric breakdown occurs in the single FP design GaN HEMTs.

Figure 2.19 presents the AlGaN/GaN HEMT cross-section with single and double FP technologies and also depicts the electric field distribution at  $V_{ds}$ =400V and  $V_{gs}$ =-6V. The electric field peak at the drain is successfully controlled once the drain field plate is introduced.

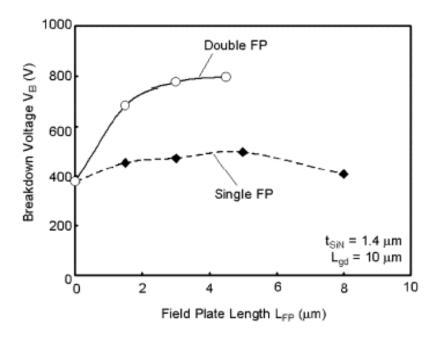

Figure 2.20 displays how the double FP method improves the breakdown voltage of the AlGaN/GaN HEMTs. Although the electric field profile of the Double FP design GaN HEMTs is far better, it is not the perfect box-shape distribution, indicating that the double FP technology is not ideal for enhancing the breakdown voltage. Meanwhile, the fabrication process becomes more complicated when increases the number of field plates in AlGaN/GaN HEMTs. Moreover, the single FP, multiple FP, and slant FP technologies are also suggested to lower the electric field peak and improve the electric field

Figure 2.20 The breakdown voltage of AlGaN/GaN HEMTs with single and double FP technology as a function of field plate length[54].

distribution at the off state, respectively, in [51], [52], [55]. Although the recently published FP designs are very effective at enhancing the breakdown voltage of AlGaN/GaN HEMTs, precisely controlling the thickness of the dielectric layer, which is crucial for lowering the electric field peak, is highly challenging [56].

## 2.5.3. Introduction of the RESURF concept

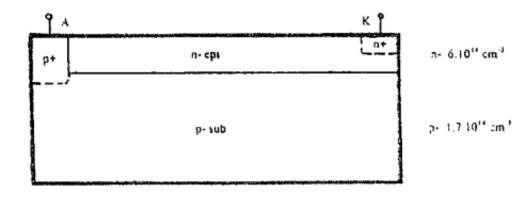

The concept of a reduced surface electric field (RESURF) was initially put forth by Appels and Vaes [57][58] for Silicon power devices. It is one of the most essential methods to optimise the electric field profile for lateral power devices. Figure 2.21 illustrates the lateral PN diode with RESURF technology[57][58]. Compared with conventional PN diode, the p+ region, a thin n-type epitaxial layer and n+ region are grown on a low-doped p-doped substrate.

Figure 2.21 The schematic cross-section of the PN diode with RESURF technology [57]

For a conventional diode, the depletion region is generated between the junction of the P+/ N- region. The electric field peak is close to the anode, and a triangle-shaped electric field profile is observed. With the increase in the reversed bias, the depletion region is extended laterally until the lateral surface breakdown happens.

However, due to the vertical n-epitaxial/p-substrate junction, RESURF technology enables the vertical (P-sub/N-epi) and lateral junction (P+/N-epi) to deplete simultaneously. It aims to make the vertical junction reach the critical

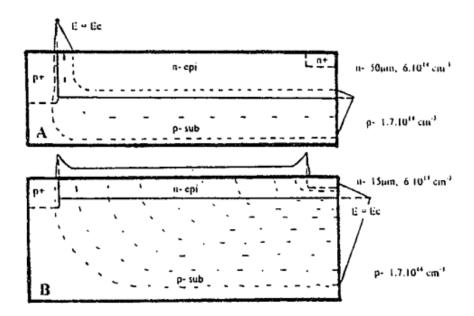

Figure 2.22 Th electric field distribution and potential lines in bulk and at the surface under various  $t_{epi}$ :(A) 50um at BV=370-470V;(B)for 15um at BV=1150V [57].

electric field before the lateral junction by precisely controlling the charge density of the n-epi, causing a larger lateral depletion region.

Moreover, it also discussed n-epi thickness influences on the blocking voltage performances of RESURF technology. Figure 2.22(A) shows the diode's electric field and potential distribution with a thicker n- region. Under these circumstances, the lateral junction reaches the critical electric field firstly, which represents the breakdown that firstly occurs at the surface P+/N- junction. However, when the thickness of the n-epi layer reduces from 50um to 15um, the P+/N- junction at the surface will be depleted until the depletion region approaches the N+ region, and the N-/P-substrate vertical junction will reach the critical electric field firstly. A larger lateral depletion region and symmetrical electric field profiles are obtained at the thickness equal to 15um.

It also found that the BV rises from 370-470V to 1150V when the n-epi thickness drops from 50um to 15um.

In conclusion, it was discovered that the N-epi layer's charge density would determine the blocking voltage performance of RESURF technology. To further optimise the high-voltage performances of RESURF power devices, double RESURF [57], [59], [60] and multiple/3D-RESURF technologies[61], [62] are investigated and discussed.

# 2.5.4. Introduction of Si Superjunction

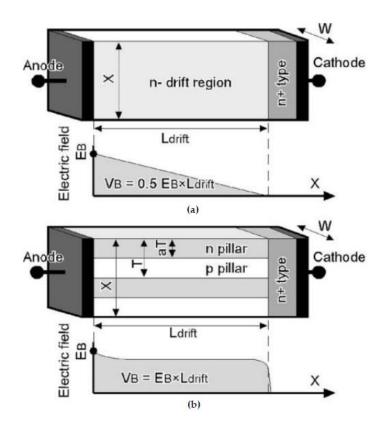

Superjunction (SJ) technology has been used in Si power devices for many years and is a mature technology. It helps silicon power devices overcome the Si material limit and reach remarkable results based on the charge balance concept in the drift region[62][63]. Compared with the conventional Si power devices, Si super-junction devices are composed of thin, highly doped N-pillar and P-pillar, as shown in Figure 2.23[64]. The Si power MOSFETs [65] and diodes[66] utilising the SJ technology were proposed and discussed.

As Figure 2.23(a) illustrates[64], with a rise in reversed bias, the depletion region of a typical diode extends from the anode to the cathode. The triangular-

Figure 2.23 Schematic cross-section and electric field profile of (a) Conventional diode (b) SJ diode [64]

shaped electric field is observed, and the peak is at the anode. Therefore, the doping concentration and thickness of the n-drift region are the key determinants of breakdown voltage [64]. Although the BV can be enhanced by reducing the N-doping concentration, the on-state resistance increases.

The specific on-resistance is defined as the resistance per unit area for the drift region[64]. As illustrated in Figure 2.23, in the vertical devices, such as power MOSFETs, the area of them is  $L_{drift} \times W$ .

Similarly, in the unipolar lateral devices, such as GaN HEMTs, the onresistance Ron can be expressed by [64]:

$$R_{on} = \frac{1}{qn\mu_n} \times \frac{L_{drift}}{WX}$$

Where L<sub>drift</sub> is the length of drift region, n is the carrier density,  $\mu_n$  is the carrier mobility, W is the width of devices. And the device area A is equal to  $L_{drift} \times W[64]$ .

Therefore, the specific on-resistance can be expressed by:

$$R_{on} \times A = \frac{1}{qn\mu_n} \times \frac{L_{drift}^2}{X}$$

And it can obtain the relationship between specific on-resistance and breakdown voltage:

$$R_{on}\times A \propto {V_B}^3$$

However, as Figure 2.23(b) illustrates, SJ diodes enable the depletion region to extend both laterally and vertically. Compared with the conventional diodes with the triangular field distribution, the drift region of the SJ diode exhibits a

flat electric field distribution, shown in Figure 2.23(b). The highly accurate doping control of the n-pillar and p-pillar is required to achieve charge balance conditions and deplete the drift region completely under the low reverse bias. Therefore, the flat and rectangular electric field profile can be observed in Si SJ power diodes under the relatively higher reverse bias.

Compared with conventional power devices, SJ technology can lower the onstate resistance and increase the breakdown voltage [65]. Thus it overcomes the Si material limit [62], [67].

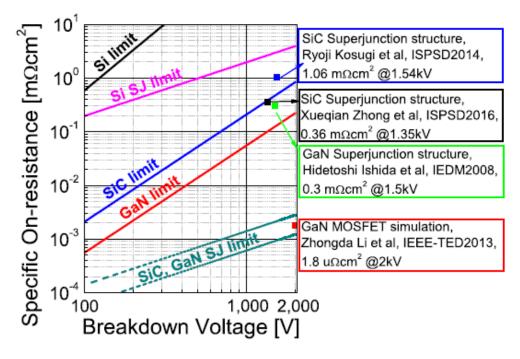

Figure 2.24 The trade-off relationship between specific on-state resistance and breakdown voltage for conventional Si, SiC, GaN and super junction for Si, SiC and GaN[65].

## 2.6. GaN Polarisation Superjunction technology (PSJ)

Because of doping difficulties, the GaN power devices cannot use the conventional Superjunction technology like the Si and SiC power devices. A. Nakajima et al. proposed Polarisation technology (PSJ), which combines the polarisation and charge balance concepts[64], and successfully realised it in GaN power devices in 2009 at the University of Sheffield.

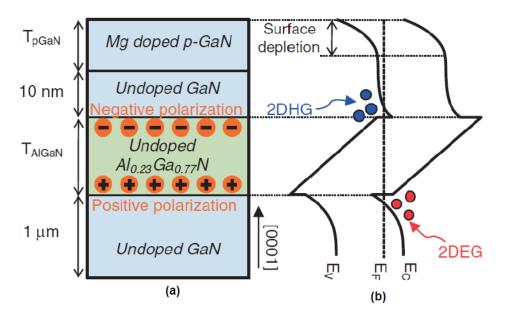

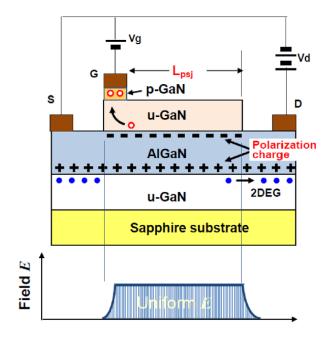

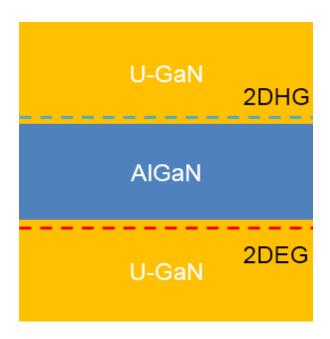

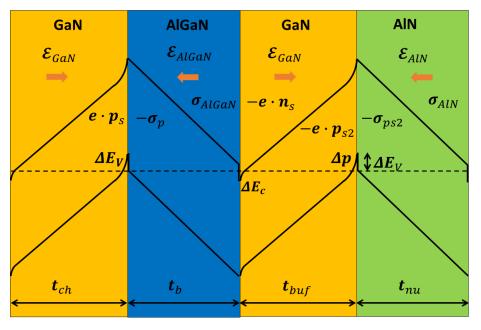

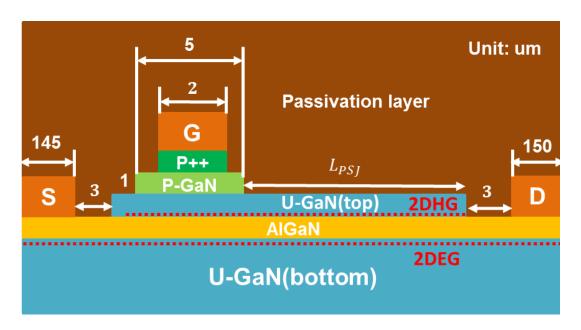

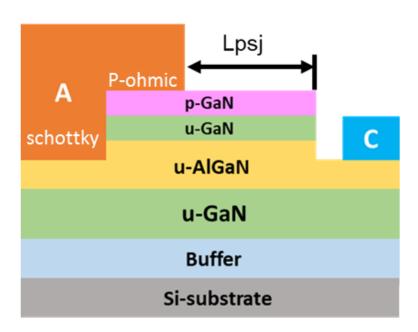

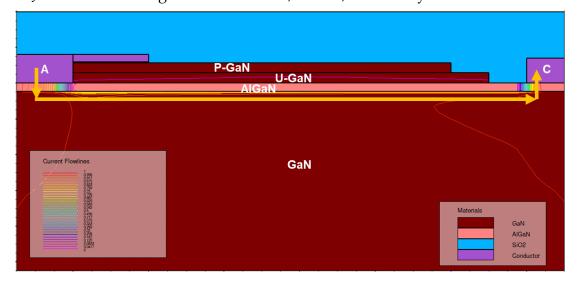

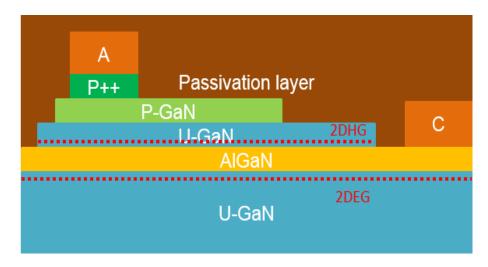

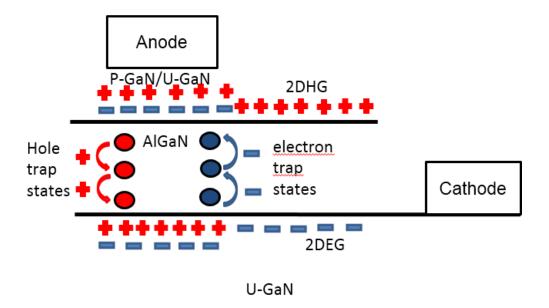

As Figure 2.25 illustrates, the Polarisation Super-junction (PSJ) HFET includes double heterostructures. Due to the polarisation effects, the high density of polarisation charge ( $\sigma_P$ =~ $10^{13}$  cm<sup>-2</sup>) is created in GaN/AlGaN/GaN heterostructures, causing the 2-dimension electron gases(2DEG) and 2-dimension hole gases(2DHG) to coexist between AlGaN/GaN and GaN/AlGaN interface, respectively[68]. Source, Gate, and Drain electrodes are all present in PSJ HFETs. Source and Drain make ohmic contact with 2DEG. P-type ohmic

Figure 2.25 Schematics of (a) layer structure and (b) band diagram[68].

gate assists the transportation of 2DHG during the switching process. The passivation details are not shown in [68]. Although the passivation details are not mentioned in the ref. [69], the composition of SiN, SiO<sub>2</sub> and polyimide are the main choices for the passivation in the PSJ HFETs.

In the conventional P-GaN HEMTs,P-type ohmic or schottky gate enables the devices to attain the normally-off function. However,due to the considerably thicker top u-GaN layer and AlGaN layer in PSJ HFETs, the P-type gate design cannot achieve the normally-off function in PSJ HFETs.

Figure 2.26 The cross-section and electric field distribution under the ideal condition of PSJ HFETs during off-state[69].

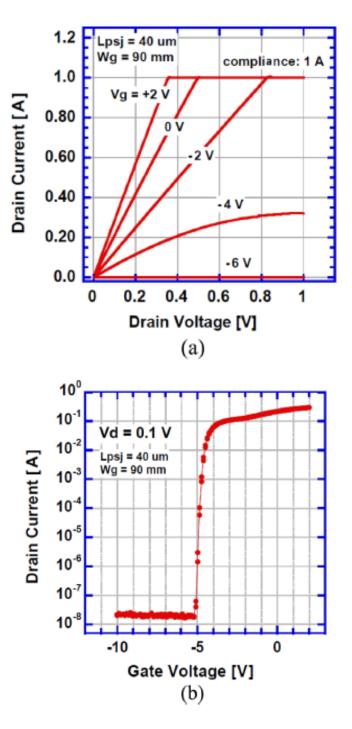

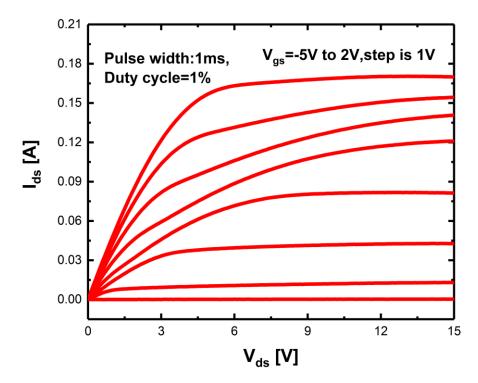

Similar to AlGaN/GaN HEMTs, when the drain bias is applied while the device is in the on-state, current flows through the 2DEG channel. Typical transfer and Id-Vd characteristics of PSJ HFETs are depicted in Figure 2.27 [69]. The Vth is around -5V, representing that they are normally-on devices. However, under

Figure 2.27 Typical (a)transfer characteristics and (b) Id-Vd characteristics of PSJ HFETs [69].

the off-state, as Figure 2.26 illustrates, 2DEG and 2DHG are discharged through the drain and gate, respectively, which achieves the ideal charge balance condition in the drift region (PSJ region). Therefore, the flat and box-shaped

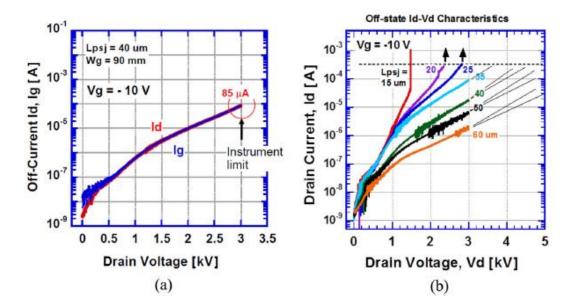

Figure 2.28 (a)Typical gate leakage(Ig) and drain leakage(Id) characteristics of Lpsj=40um (b) the breakdown characteristics as a function of PSJ Length during the off state of the PSJ HFETs with Wg=90mm. Furthermore, they are all measured at Vgs=-10V[69].

electric field profiles can be observed in the PSJ HFETs[69], significantly enhancing BV. Moreover, PSJ HFETs have a more simplified structure as compared to the field-plate design, representing that PSJ HFETs are less challenging for device fabrication, especially for high-voltage applications.

Figure 2.28(a) shows the off-state gate leakage current (Ig) and drain leakage current (Id) of PSJ HFETs at off-state.  $I_d$  and  $I_g$  are nearly identical, indicating that in PSJ HFETs, the leakage path is from the gate to the drain under off-state [69].

Figure 2.28(b) demonstrates how the PSJ Length affects the usual breakdown voltage of PSJ HFETs ( $L_{psj}$ ). The linear relationship between breakdown voltage (BV) and  $L_{psj}$  is presented in Figure 2.28(b), representing that BV grows linearly as the length of the PSJ drift region increases.

Compared with traditional Superjunction technology, Polarisation superjunction (PSJ) power devices do not require the precise doping control of the n-pillar and p-pillar. This is due to 2DEG and 2DHG being naturally and equally generated in the GaN/AlGaN/GaN double heterojunctions. Therefore, In the PSJ HFETs, the optimum charge balance condition and flat electric field distribution are easy to attain compared with the ideal Si Superjunction power devices. Due to the high density and mobility of 2DEG, PSJ HFETs can also attain low on-state resistance[70], indicating that they will not sacrifice the fast-switching speed, low conduction and switching losses. All these advantages enable GaN PSJ power devices to become the most competitive next-generation GaN power devices.

Nowadays, Schottky gate HFETs[47], diodes[71] and bi-directional devices[72] have been reported using the PSJ technology. More research on the design of GaN diodes using the PSJ concepts and technologies is discussed in[73]–[75].

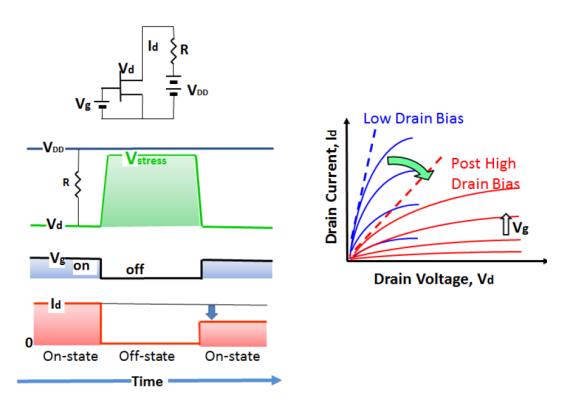

## 2.7. Current collapse

Current collapse, also referred to as the dynamic on-state resistance (R<sub>dynamic,dson</sub>) degradation, is a severe challenge for the conventional AlGaN/GaN HEMTs. This phenomenon occurs when devices are switched from off-state to on-state. The measurement setup and the switching waveform are shown in Figure 2.29[45]. The dynamic on-state resistance degrades in comparison to the static on-state resistance when the high drain-side stress voltage is applied at the off-state[45]. This effect will severely degrade the efficiency of the devices, increase the power losses and reduce the current-carrying capability during high switching speed and high voltage applications.

Figure 2.29 The switching waveform and circuit diagram for evaluating current collapse (left); Id-Vds characteristics of conventional HFETs(right) [45].

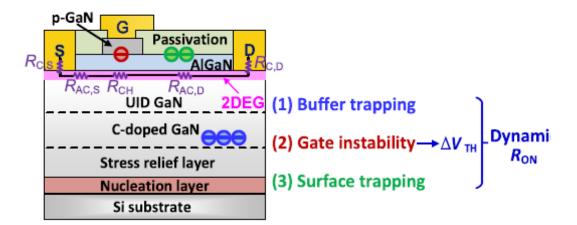

Current collapse originates from three main aspects: buffer trapping, surface trapping and gate instability[76].

Under the high  $V_{ds}$  stress during the off-state, the hot electrons which gained the high kinetic energy at the high-electric-field region are accelerated and trapped by the traps located at the surface or the buffer layer. When the devices switch from off-state to on-state, the trapped electrons cannot escape instantly from the traps because of the relatively long lifetime of traps, increasing the on-state resistance in comparison to the steady  $R_{on}$ . The increased dynamic  $R_{dson}$  can be recoverable if the time is sufficient after the stress is removed.

Surface trapping is caused by the surface traps along the interface of the passivation/AlGaN layer. The 2DEG is captured by the surface traps during the off-state, causing the increase of the dynamic Ron. The surface passivation, such

Figure 2.30 Schematic cross-section of conventional GaN-on-Si power HEMTs and the main factors for the current collapse[76].

as SiN, SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, can significantly lower the surface traps and effectively suppress the current collapse effects [77]. Alternatively, optimising the electric

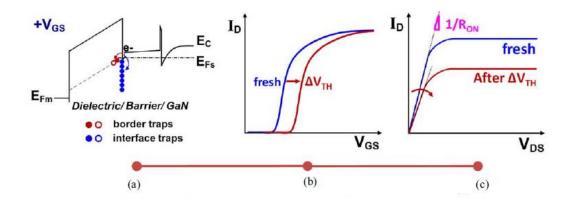

Figure 2.31 Gate-instability-induced dynamic R increase in the MIS-HEMTs (a) schematic of energy band diagram with the interface/border trapping mechanism under positive gate bias(b)positive  $V_{th}$  shift( $\Delta V_{th}$ )(c)degradation of  $R_{on}$  after  $\Delta V_{th}$ .

field profile is another method for mitigating the current collapse. FP technology can relax the electric field peak and minimise the impacts of current collapse effects[78], but it cannot completely solve this issue.

However, the buffer trapping has different mechanism. Due to the potential difference of the drain and substrate, the 2DEG will be escaped from the confined quantum well during the off-state and captured by the buffer traps, causing the increase of the dynamic Ron. The buffer trapping effects can be evaluated through back-gating measurements in GaN-on-Si power HEMTs[76]. Reducing the buffer defects during growth is an efficient way to mitigate this effect[79]. Figure 2.31 illustrates the gate instability induced by the current collapse in the MIS-HEMTs[80]. When the gate stress is applied, the border and interface traps capture the carriers, reducing the 2DEG density and producing a positive Vth shift. Therefore, dynamic Rds rise because they cannot

immediately react to the variable threshold voltage from the off-state to the onstate.

#### 2.8. Summary

In this chapter, GaN material properties are first introduced. Compared with Si, GaN is more advantageous in many aspects. Several Figures of Merits (FOMs) of Si, SiC and GaN, are discussed for different aspects. Substrate selection is also essential for GaN power devices. SiC and GaN substrate has better lattice properties than Si and Sapphire substrates. However, the low price of Si substrate is favoured by the commercial market.

Polarisation effects in AlGaN/GaN heterostructures are explored, including spontaneous and piezoelectric polarisation. Due to these polarisation effects, AlGaN/GaN heterointerface forms the high-density and high-mobility 2DEG, enabling AlGaN/GaN HEMTs to have low conduction loss and switching loss. The surface-state donor model, widely thought to be the origin of 2DEG, is also discussed in detail. The factors influencing the 2DEG sheet density, such as AlGaN layer thickness and Al mole fraction, are also presented. The device structure and the operation principle of Conventional AlGaN/GaN HEMTs are also introduced in detail.

Despite having a low on-state resistance, the breakdown voltage of AlGaN/GaN HEMTs is low due to ineffective electric field management. The typical methods for optimising the electric field distribution in the power devices include FP design, RESURF, and Superjunction technologies. For GaN power devices, polarisation superjunction technology is one of the most

effective ways to achieve flat and box-shaped electric field distribution. Due to the high density and mobility of 2DEG, GaN PSJ power devices have the potential to achieve the relatively lower conduction loss. Therefore, it can achieve low on-state resistance and high breakdown voltage simultaneously. These remarkable advantages of GaN PSJ power devices make them the most competitive next-generation power devices.

Current collapse, which significantly increases the power losses of the GaN power devices during the switching process, is also briefly reviewed. Surface trapping, buffer trapping and threshold voltage shift are the three main factors for this phenomenon.

# Chapter 3. Theoretical Analysis of the Sheet Density of 2DEG and 2DHG in Polarization Super-Junction Heterostructures

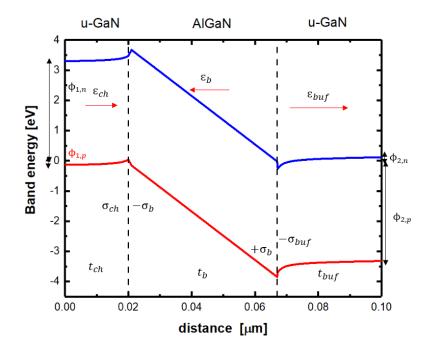

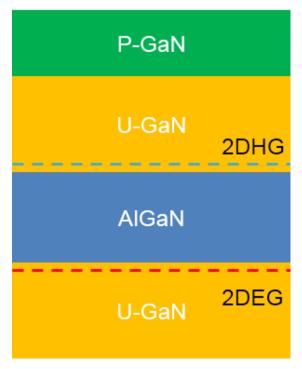

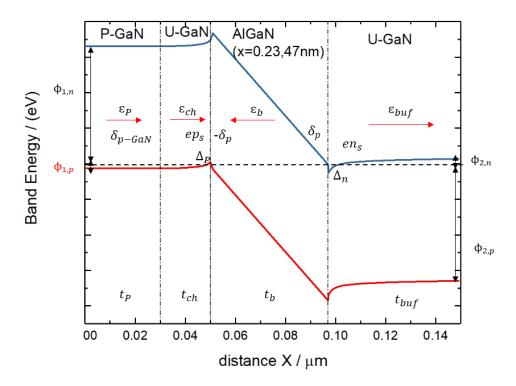

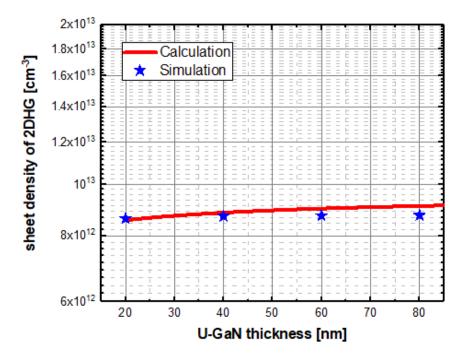

The main topic of this chapter is the theoretical analysis of the impacts of the top u-GaN layer and the AlN nucleation layer thickness on the sheet density of 2DEG and 2DHG in PSJ heterostructures. The simulation and experiment results are also included to compare and validate the conclusions of the theoretical study.

## 3.1. Top u-GaN layer thickness

Chapter 2 already briefly introduced that the sheet density of 2DEG mainly depends on the parameter of the Al $_{S}$ Gal $_{S}$ N barrier layer, including the thickness and Al mole fraction(x) Al $_{S}$ Gal $_{S}$ N[38], [39]. This chapter discusses how the top u-GaN layer affects the sheet density of 2DEG and 2DHG in the various PSJ heterostructures T. Prunty et al. [81] built the theoretical model of sheet density of 2DEG in AlGaN/GaN Heterostructures. Following a similar analysing method, Hahn et al. [82], [83]proposed the expression of the sheet density of 2DEG ( $n_{S}$ ) and 2DHG ( $p_{S}$ ) in the u-GaN/AlGaN/u-GaN heterostructures under different top u-GaN surface conditions. This model is built to analyse the relationship between the behaviours of threshold voltage Vth with the  $p_{S}$  in this article. Similarly, A. Kumar et al. [84] built the expression of the density of 2DEG and 2DHG in the GaN/AlGaN/GaN with SiO2 cap layer to investigate the threshold voltage behaviour in the P-channel GaN HEMTs

with MOS structures. Hongyang et al. [70]also analysed the 2DEG and 2DHG sheet density in PSJ heterostructures to investigate the on-state resistances in PSJ HFETs.

Although the surface donor model can be utilized to analyse the physical mechanisms of the origin of 2DEG, the expression of the sheet density of 2DEG and 2DHG cannot be obtained through it, because it neglected some components of the charges in the GaN/AlGaN/GaN heterostructures. Moreover, the possible generated charges in the PSJ heterostructures are different from the AlGaN/GaN heterostructures, causing the wrongly calculation of the sheet density of 2DEG and 2DHG. Therefore, in order to obtain the accurate expressions of them, the calculation method based on the band diagram is widely used at present.

#### 3.1.1. U-GaN/AlGaN/u-GaN heterostructures

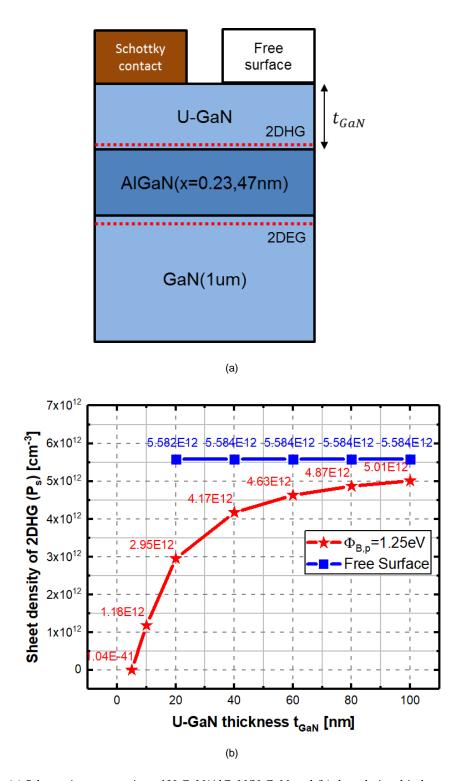

The expression for the density of 2DEG and 2DHG will be built first to consider the dependence on the u-GaN thickness via derivation in the u-GaN/AlGaN/u-GaN heterostructures shown in Figure 3.1.

Based on the band diagram illustrated in Figure 3.2, the expression of  $p_S$  and  $n_S$  obtained from Hahn's work is[83]:

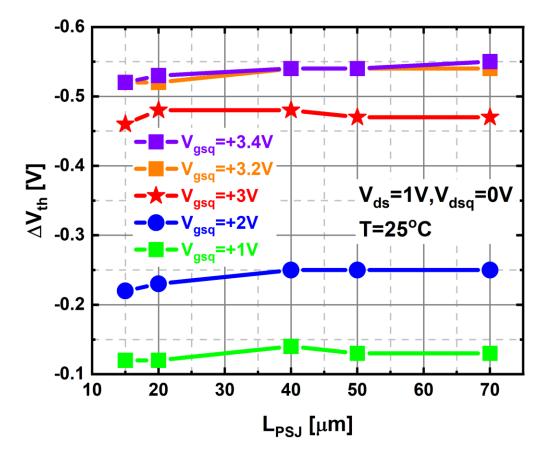

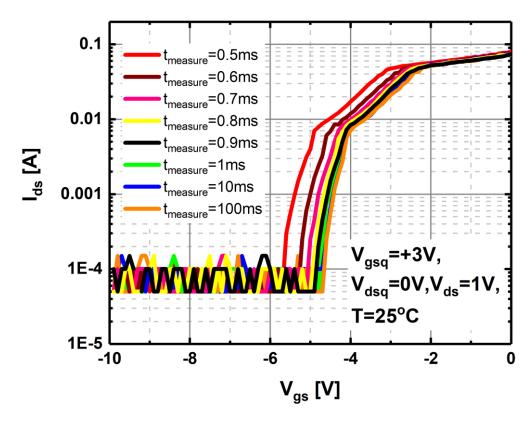

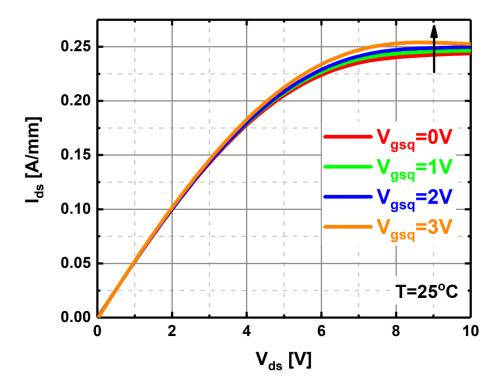

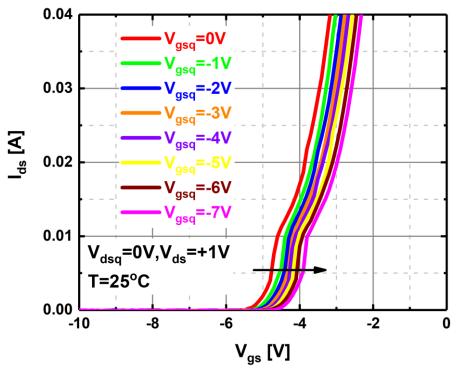

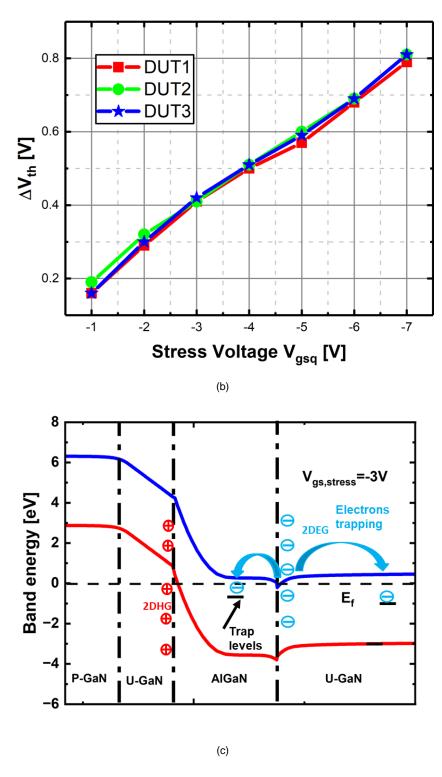

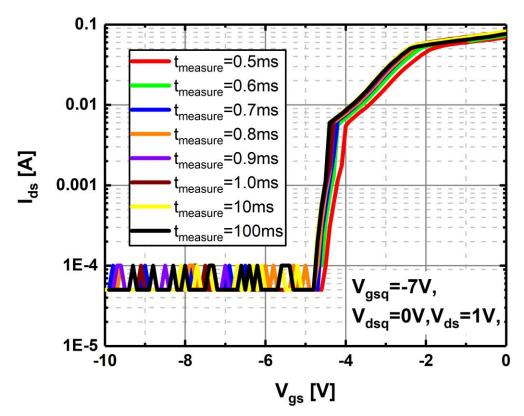

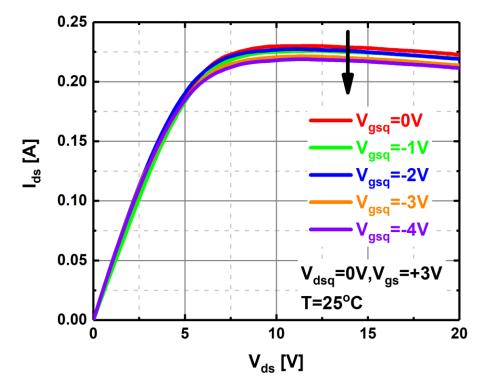

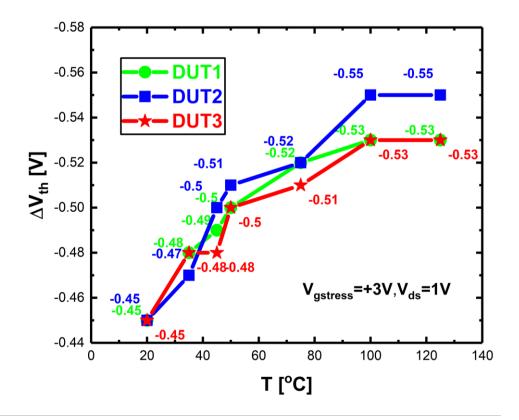

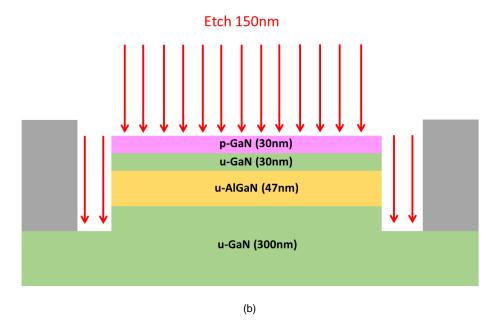

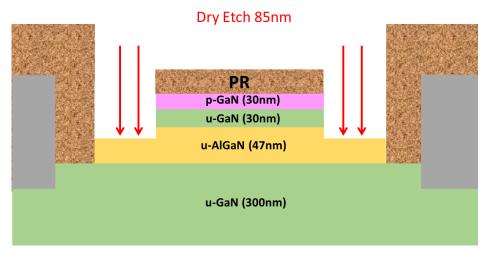

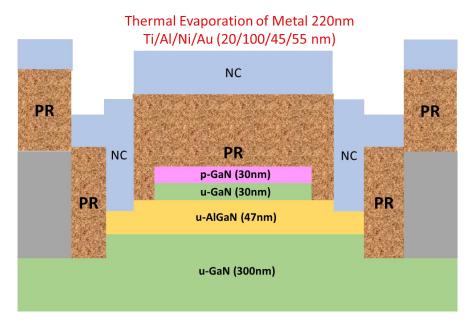

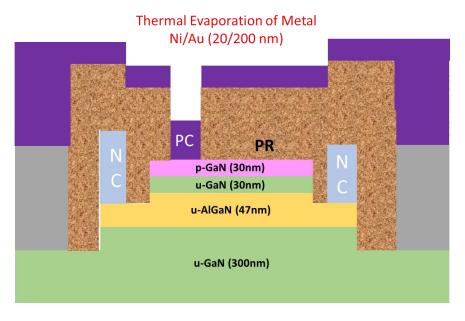

Figure 3.1 Schematic diagram of PSJ heterostructures (U-GaN/AlGaN/U-GaN).