## THE UNIVERSITY OF SHEFFIELD

Development of a Current Limiting Solid-State Circuit Breaker Based on Wide-Band Gap Power Semiconductor Devices for 400V DC Microgrid Protection

By

**Zhongying Wang**

A thesis submitted for the degree of Doctor of Philosophy in the Department of Electronic and Electrical Engineering The University of Sheffield

**June 2021**

#### **Abstract**

Popularity of DC distribution systems is increasing for many residential and industrial applications such as data centres, commercial and residential buildings, telecommunication systems, and transport power networks etc. Compared to AC systems, they have demonstrated higher power efficiency, less complexity, and more readiness of integrating with various local power sources and DC electronic loads. However, one of the major technical issues hindering this trend is the lack of effective DC fault protection devices/circuits. Although conventional electromechanical circuit breakers work well in AC systems, they are not suitable for DC systems due to their long response time (ranging from tens of milliseconds to hundreds of milliseconds). Such a long response time is far beyond the withstand time (typically tens of microseconds) of most power electronic devices in short-circuit operating conditions. In contrast, Solid-State Circuit Breakers (SSCBs) are able to offer ultrafast switching speed thanks to the modern power semiconductor devices which can turn off in microseconds or even in tens of nanoseconds. Furthermore, the ever-increasing fault current level in DC systems poses a significant mechanical and thermal stress on the whole DC system. Therefore, the desire for the protection devices with the feature of fast switching speed along with the current-limiting capability has prompted intensive research in this area over the last decade in both academia and industry. However, the relatively high conduction losses and limited short-circuit capability are two of the major drawbacks of SSCBs. With the growing maturity and increasingly commercial availability of Wide-Bandgap (WBG) semiconductor devices, a SSCB based-on WBG devices is a promising solution to alleviate the issues since WBG semiconductors have demonstrated superior material properties over the conventional silicon material such as lower specific on-resistance, higher junction temperatures and higher breakdown voltage.

This research aims to design and develop a WBG-based solid-state circuit breaker for a 400V DC microgrid application. To accomplish this task, this work starts with a comprehensive review of DC microgrid technology followed by an extensive review of the state-of-the-art DC circuit breakers. Then, to develop a circuit topology for the proposed SSCB, a practical current limiter is analysed, simulated, and evaluated. Based on this topology, the proposed SSCB is configured with a high-voltage normally-on Silicon Carbide Junction Field Effect Transistors (SiC-JFETs) cascading a low-voltage normally-off power MOSFET. This solution offers several advantages. For example, it does not require any additional sensing and tripping circuitry for

short-circuit protection and therefore has a fast response speed. Meanwhile, the use of power SiC JFETs tends to reduce the conduction losses and enhance the short-circuit robustness of SSCBs. In addition, it offers the feature of current limiting which could ease the thermal and mechanical stresses on the whole DC system. The operating process of the proposed SSCB is analysed and the analytical results are compared with the simulated results; In the end, a prototype SSCB has been built and evaluated for short-circuit protection in a 400V DC system. In addition, to effectively suppress the overvoltage at the turn-off of SSCBs, a novel hybrid snubber circuit has been proposed by taking into account the advantages offered by both conventional Resistor-Capacitor-Diode (RCD) snubbers and Metal-Oxide Varistors (MOVs). Finally, other functions of the proposed SSCBs including overload protection, over temperature protection and protection coordination have been investigated and some operating issues such as false tripping and SSCB reset have been addressed.

### **Acknowledgements**

I would like to take this opportunity to express my sincere thanks to everyone who has supported and encouraged me through this wonderful journey.

First and foremost, I would like to sincerely thank my supervisors Professor Shankar Ekkanath Madathil, Dr Mark Sweet and Dr Hongyao Long for guiding me through this research.

Secondly, I would like to thank Bourns Inc for providing me an opportunity of gaining insight of their amazing TBU products.

Special thanks will go to the enthusiastic young man Mr Alireza Sheikhan who thoroughly reviewed the thesis and perfected some drawings.

Appreciations will also go to our group members: Dr Kee Beom Nam, Dr Peng Luo, Mr Qiuyang Tan, Mr Hongyang Yan, Mr Yangming Du, Ms Gopika Narayanankutty, and Miss Sandy Tan for their help and friendship.

Finally, I would like to hugely thank my wife, my son, my parents and my siblings for their unwavering support through this journey of the highs and the lows. Without their unconditional love, I could not imagine I would be able to complete this research.

## **Table of Contents**

| Chaj | pter                    | 1 Introduction                                               | 1    |

|------|-------------------------|--------------------------------------------------------------|------|

| 1.1  | His                     | story of Competition between DC and AC technology            | 1    |

| 1.2  | Review of DC Microgrids |                                                              | 1    |

| 1.2  | 2.1                     | DC microgrid configuration                                   | 2    |

| 1.2  | 2.2                     | Voltage polarity                                             | 4    |

| 1.2  | 2.3                     | Grounding                                                    | 5    |

| 1.2  | 2.4                     | Voltage level standards applied for DC microgrids            | 8    |

| 1.3  | Bei                     | nefits of DC Power over AC Power                             | 8    |

| 1.4  | Cha                     | allenges of DC Power Protection                              | 10   |

| 1.5  | Fau                     | alt Protection Devices for DC Power Systems                  | 15   |

| 1.6  | Ob                      | jective of this Research                                     | 17   |

| 1.7  | Ma                      | in contributions of this research.                           | 18   |

| 1.8  | Ou                      | tline of the Thesis                                          | 19   |

| 1.9  | Lis                     | t of Publication                                             | 20   |

| 1.10 | Ref                     | ferences                                                     | 20   |

| Chaj | pter                    | 2 Review of DC Circuit Breaker Technologies                  | . 26 |

| 2.1  | Bas                     | sic Requirements and Main Parameters of a DC Circuit Breaker | 26   |

| 2.1  | 1.1                     | Requirements on a DC Circuit Breaker                         | 26   |

| 2.1  | 1.2                     | Technical parameters                                         | 26   |

| 2.2  | Ov                      | ercurrent Protection Process of a DC Circuit Breaker         | .27  |

| 2.3  | DC                      | Circuit Breaker Technologies                                 | 29   |

| 2.3  | 3.1                     | Electro-Mechanical Circuit Breakers (EMCBs)                  | 29   |

| 2.3  | 3.2                     | Solid-State Circuit Breakers (SSCBs)                         | .32  |

| 2.3  | 3.3                     | Hybrid Circuit Breakers (HCBs)                               | .33  |

| 2.4  | Rev                     | view of SSCBs/HCBs Based on Various Semiconductor Devices    | .35  |

| 2.4  | 1.1                     | SSCBs/HCBs based on Silicon power semiconductor devices      | .35  |

| 2.4  | .2 SSCBs/HCBs Based on Wide bandgap semiconductor devices             | 40 |  |

|------|-----------------------------------------------------------------------|----|--|

| 2.5  | Review of Fault Sensing Technique                                     | 45 |  |

| 2.6  | Conclusions                                                           |    |  |

| 2.7  | References                                                            | 47 |  |

| Chap | ter 3 Analysis of Transient Blocking Units                            | 53 |  |

| 3.1  | Introduction                                                          | 53 |  |

| 3.2  | Current-voltage Characteristics and Equations for FET devices         | 54 |  |

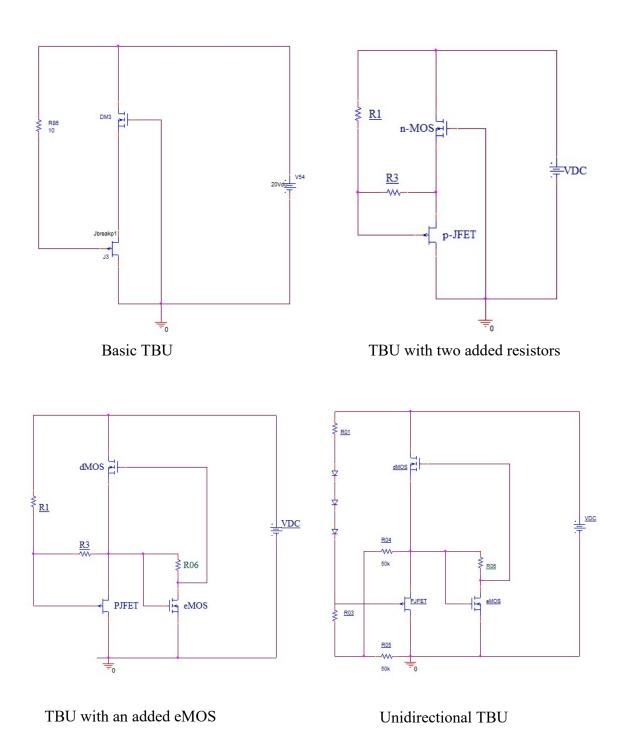

| 3.3  | Analysis of Static Operating Principle of the Basic TBU               | 56 |  |

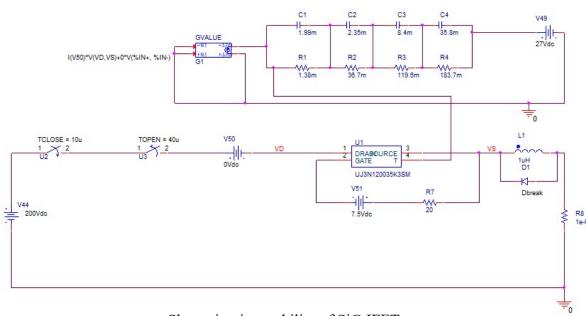

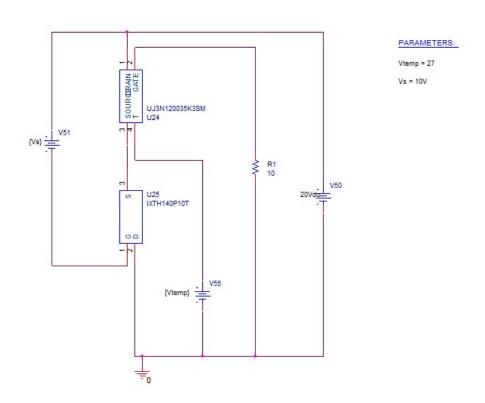

| 3.4  | Simulation Validation of the Basic TBU                                | 61 |  |

| 3.5  | Analysis of the Basic TBU with Two Added Resistors                    | 62 |  |

| 3.6  | Simulation Validation of the Basic TBU with two Added Resistors       | 65 |  |

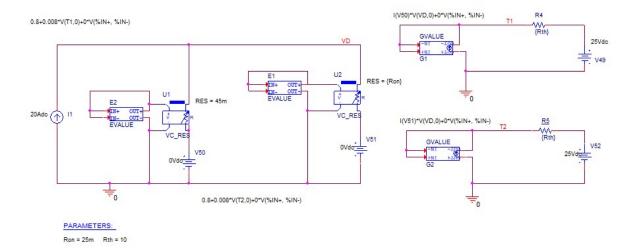

| 3.7  | Analysis of the Basic TBU with an Added Enhancement Mode MOSFET       | 66 |  |

| 3.8  | Simulation Validation of the TBU with an Added Enhancement MOSFET     | 73 |  |

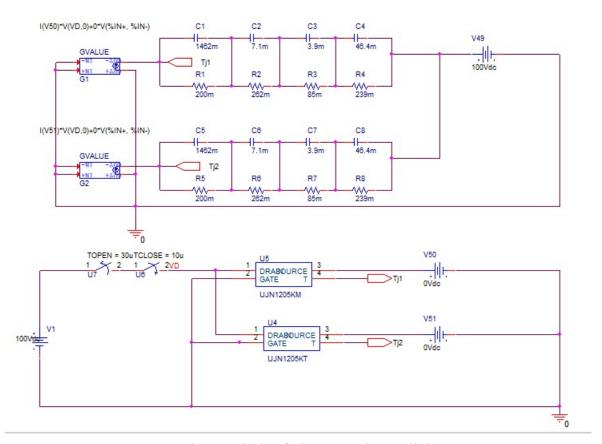

| 3.9  | Analysis of the TBU with Added Diodes (practical TBUs)                | 74 |  |

| 3.10 | Simulation and Experimental validation of the practical TBUs          | 79 |  |

| 3.11 | Conclusions                                                           | 87 |  |

| 3.12 | References                                                            | 87 |  |

| Chap | ter 4 Power semiconductor devices for the proposed SSCB               | 88 |  |

| 4.1  | Introduction                                                          | 88 |  |

| 4.2  | Device Requirement for the Proposed SSCB                              | 88 |  |

| 4.2  | .1 A typical low voltage 400V DC distribution system                  | 88 |  |

| 4.2  | .2 Functionalities of the proposed SSCB                               | 89 |  |

| 4.2  | .3 International Standards for DC Circuit Breakers                    | 90 |  |

| 4.2  | .4 Technical specifications for the proposed SSCB                     | 91 |  |

| 4.2  | .5 Calculation of maximum allowed on-Resistance for the proposed SSCB | 92 |  |

| 4.3  | Selection of Power Semiconductor Devices for the Proposed SSCB        | 93 |  |

| 4.3  | .1 Comparisons of wide bandgap materials over Silicon                 | 94 |  |

|      | ${f v}$                                                               |    |  |

|      |                                                                       |    |  |

| 4.3  | 3.2    | Commercial SiC power devices                                                 | ŀ        |

|------|--------|------------------------------------------------------------------------------|----------|

| 4.3  | 3.3    | Commercial GaN devices 95                                                    | 5        |

| 4.3  | 3.4    | Comparison of four commercial power semiconductor devices96                  | 5        |

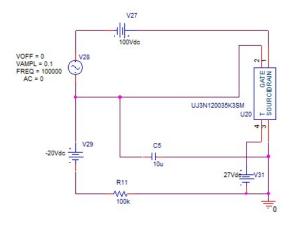

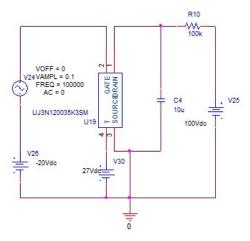

| 4.4  | Cha    | aracterisation and Development of SPICE model of 1.2kV SiC JFET106           | 5        |

| 4.4  | 4.1    | Static characterization and model development of 1.2kV SiC JFET106           | 5        |

| 4.4  | 4.2    | Dynamic characteristics and model development of 1.2kV SiC JFET106           | 5        |

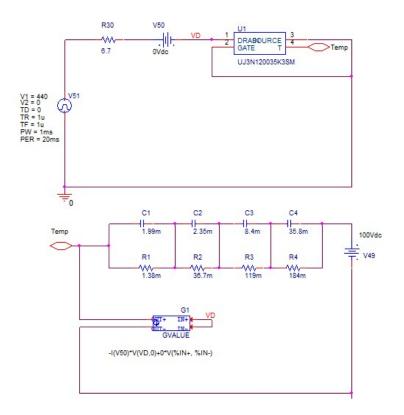

| 4.4  | 4.3    | Addition of junction temperature terminal Tj for SPICE model107              | 7        |

| 4.5  | The    | ermal Design                                                                 | )        |

| 4.5  | 5.1    | Introduction                                                                 | )        |

| 4.5  | 5.2    | Thermal parameters                                                           | )        |

| 4.5  | 5.3    | Thermal modelling                                                            | )        |

| 4.5  | 5.4    | Junction temperature analysis during normal operating condition of a SSCB112 | 2        |

| 4.5  | 5.5    | Junction temperature analysis during short-circuit operation117              | 7        |

| 4.6  | SiC    | JFETs in Parallel 118                                                        | 3        |

| 4.6  | 5.1    | Analysis of static operation of normally-on SiC JFETs in parallel118         | }        |

| 4.6  | 5.2    | Dynamic current unbalancing                                                  | 3        |

| 4.7  | Con    | nclusions                                                                    | 5        |

| 4.8  | Ref    | erences                                                                      | 5        |

| Chaj | pter : | 5 Transient Overvoltage Suppression Design13                                 | 31       |

| 5.1  | Intr   | oduction131                                                                  | l        |

| 5.2  | Rev    | view of Overvoltage Suppression Circuits for SSCB Applications131            | l        |

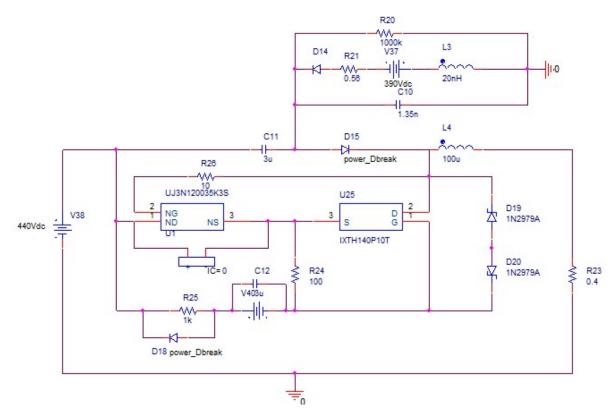

| 5.3  | Ana    | alysis of the Operating process of the Proposed Snubber Circuit139           | )        |

| 5.4  | Snu    | bber Design for Low Voltage DC SSCB Applications                             | <u>)</u> |

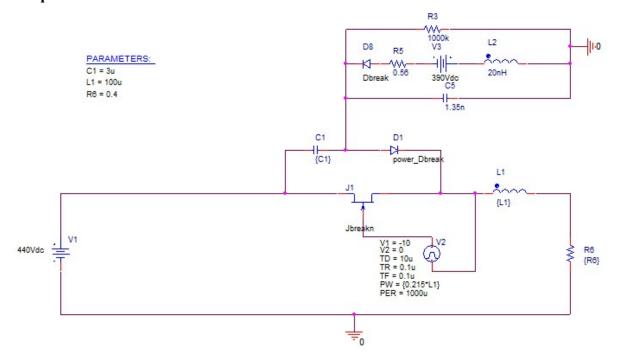

| 5.5  | Sim    | ulation Validation144                                                        | ļ        |

| 5.6  | Exp    | periment Validation                                                          | 5        |

| 5.7  | Disc   | cussions150                                                                  | )        |

| 5.8  | Con    | nclusions 153                                                                | ł        |

| 5.9  | References                                                                  | 154  |

|------|-----------------------------------------------------------------------------|------|

| Chap | oter 6 Development of a SSCB for Short-circuit Protection                   | 156  |

| 6.1  | Introduction                                                                | 156  |

| 6.2  | Short-circuit Protection Requirements                                       | 156  |

| 6.3  | Tripping mechanism in the literature                                        | 157  |

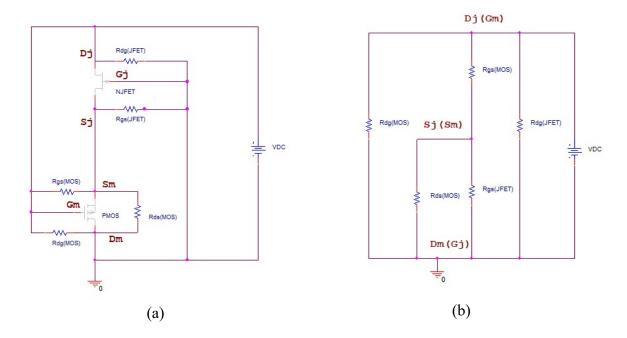

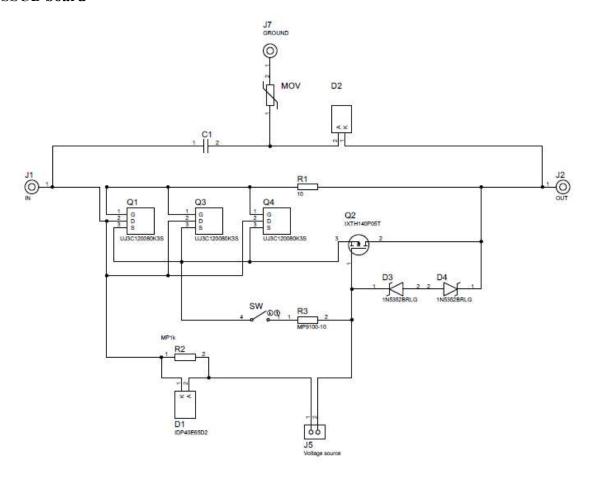

| 6.4  | Configuration of the circuit topology for SSCB application                  | 158  |

| 6.5  | Analysis of the Operating Principle of the Proposed SSCB                    | 161  |

| 6.6  | Simulation Validation of the Proposed SSCB                                  | 165  |

| 6.7  | Analysis of voltage stress of the proposed SSCB                             | 168  |

| 6.7  | 7.1 Analysis of voltage distributions in a static off-state                 | 168  |

| 6.7  | 7.2 Analysis of voltage distributions during turn-off transition of the SSC | B169 |

| 6.7  | 7.3 Simulation validation                                                   | 170  |

| 6.8  | Experiment Validation                                                       | 171  |

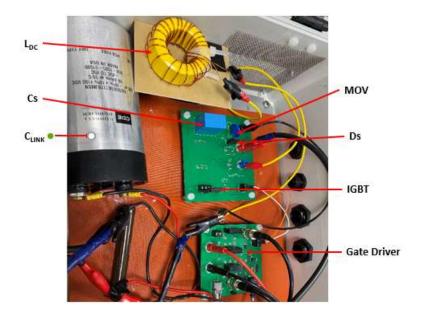

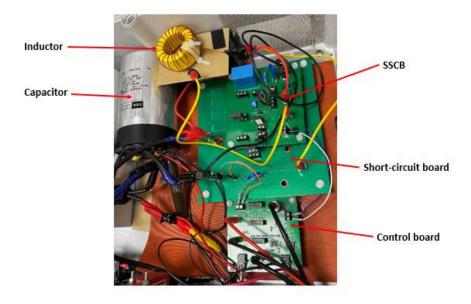

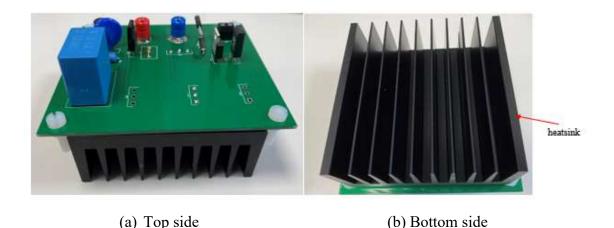

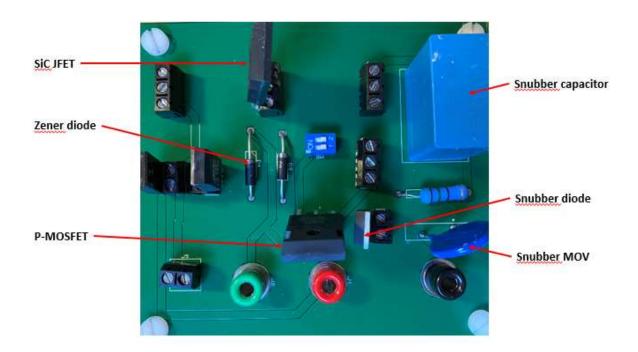

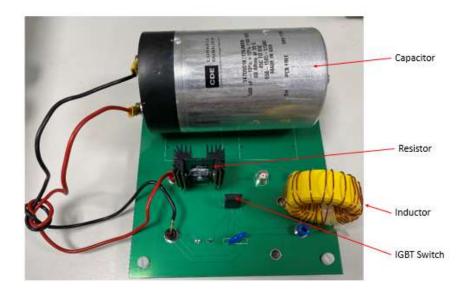

| 6.8  | 8.1 Experimental setup                                                      | 171  |

| 6.8  | Main components of the test bench                                           | 173  |

| 6.8  | 8.3 Experiment Results                                                      | 177  |

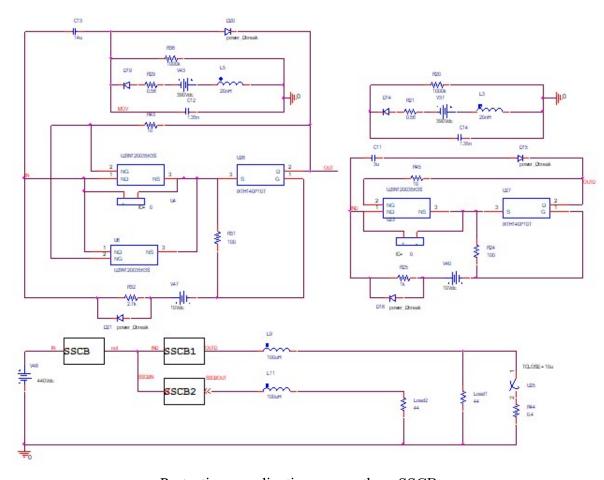

| 6.9  | Protection Coordination                                                     | 180  |

| 6.9  | P.1 Introduction                                                            | 180  |

| 6.9  | 9.2 Simulation validation                                                   | 182  |

| 6.9  | 9.3 Experimental validation                                                 | 184  |

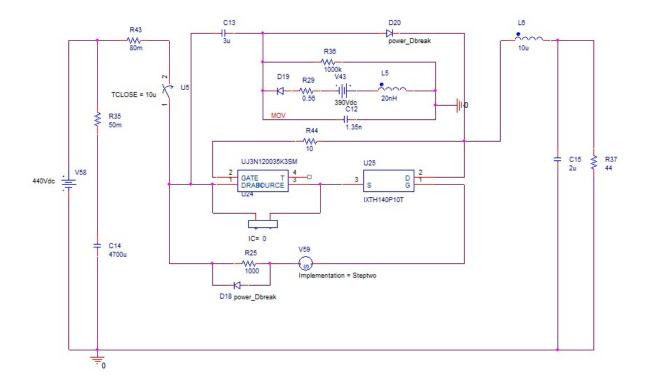

| 6.10 | Inrush Current Issue                                                        | 186  |

| 6.11 | SSCB Reset and Fail-Safe                                                    | 187  |

| 6.12 | Conclusions                                                                 | 188  |

| 6.13 | References                                                                  | 188  |

| Chap | oter 7 Overload and Over Temperature Protection                             | 192  |

| 7.1  | Introduction                                                                | 192  |

| 7.2  | Overcurrent Protection                                                      | 192  |

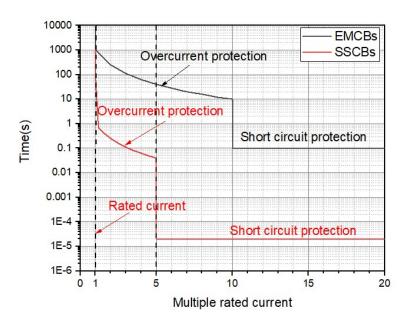

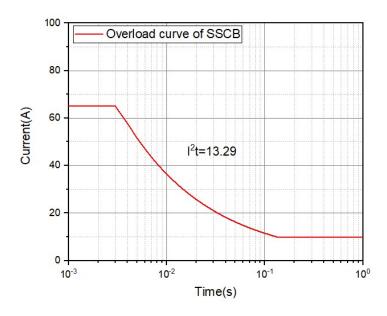

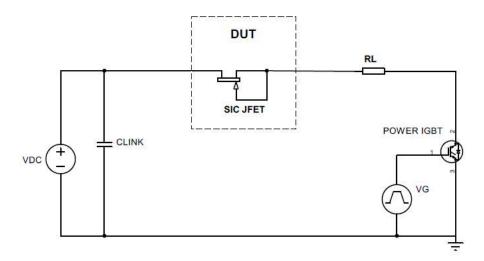

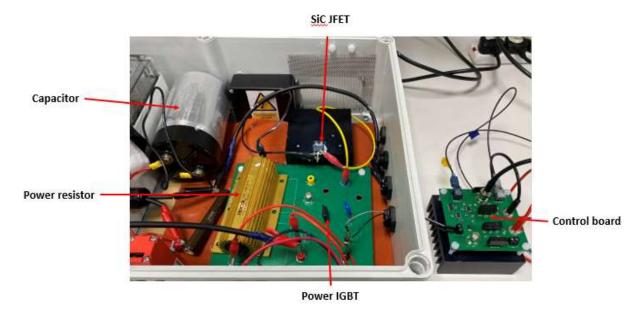

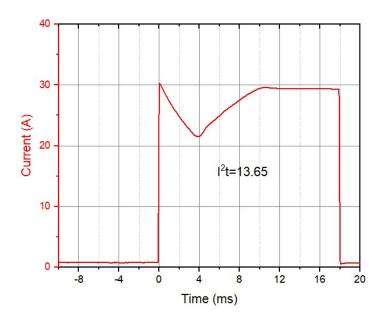

| 7.2  | .1    | Comparison of time-current tripping curves of SSCBs and EMCBs192           |

|------|-------|----------------------------------------------------------------------------|

| 7.2  | .2    | Design of I <sup>2</sup> t for the proposed SSCB                           |

| 7.2  | .3    | Experimental validation                                                    |

| 7.2  | .4    | Current sensing                                                            |

| 7.3  | Ove   | er Temperature Protection                                                  |

| 7.3  | .1    | Methods of junction temperature measurements                               |

| 7.3  | .2    | Selection of the TSEP for the proposed SSCB                                |

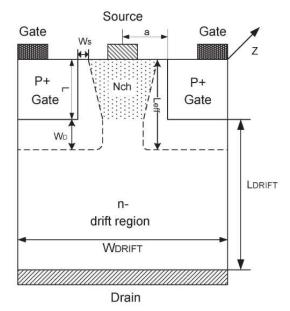

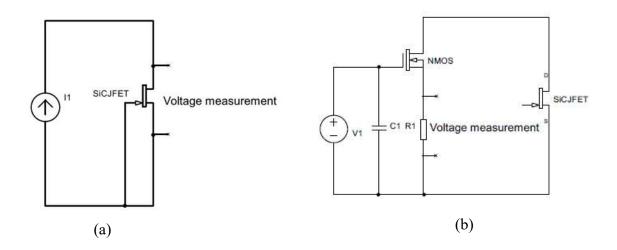

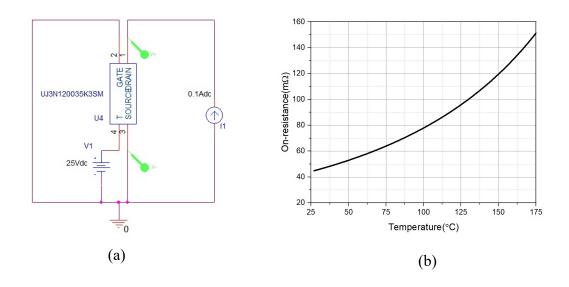

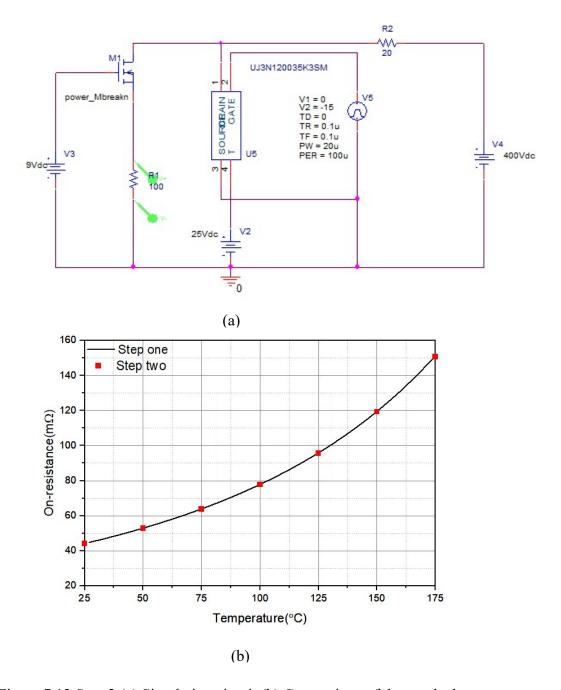

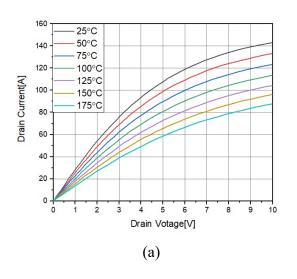

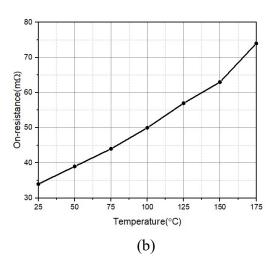

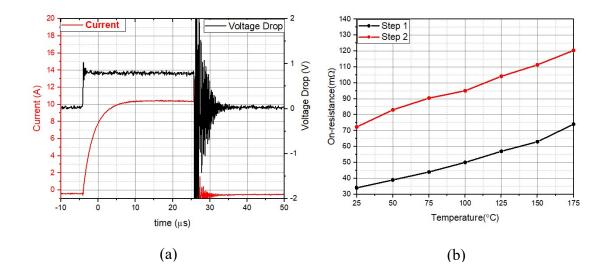

| 7.3  | .3    | On-resistance temperate dependency of a typical vertical power SiC JFET202 |

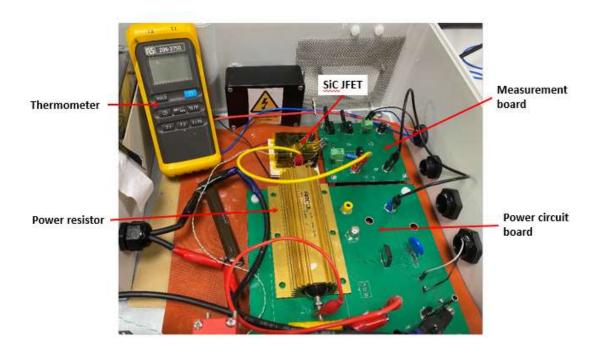

| 7.3  | .4    | Realization of real-time temperature measurements                          |

| 7.3  | .5    | Simulation validation                                                      |

| 7.3  | .6    | Experiment validation                                                      |

|      | 209   |                                                                            |

| 7.4  | Con   | clusions                                                                   |

| 7.5  | Refe  | erences                                                                    |

| Chap | ter 8 | 8 Conclusions and Future Work213                                           |

| 8.1  | Con   | clusions                                                                   |

| 8.2  | Futu  | are Work                                                                   |

| Appe | ndix  | A: Simulation Circuits in the Thesis217                                    |

| Appe | ndix  | B: Silicon Carbide Junction Field Effect Transistor SPICE Models223        |

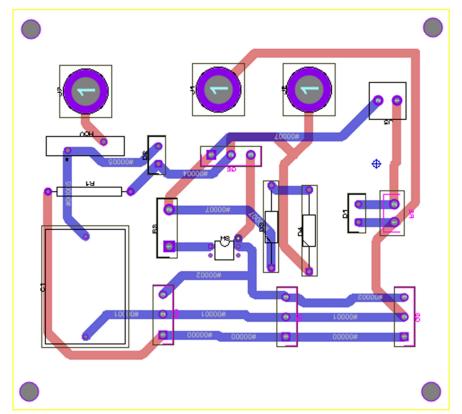

| Appe | ndix  | C: Schematic circuits and PCB layouts228                                   |

## **List of Figures**

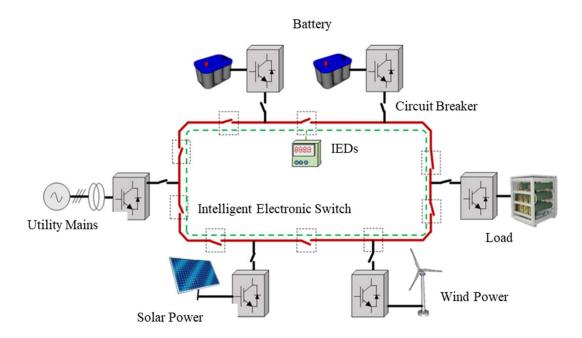

| Figure 1.1 Single bus Structure (adapted from [17])                                    | 2  |

|----------------------------------------------------------------------------------------|----|

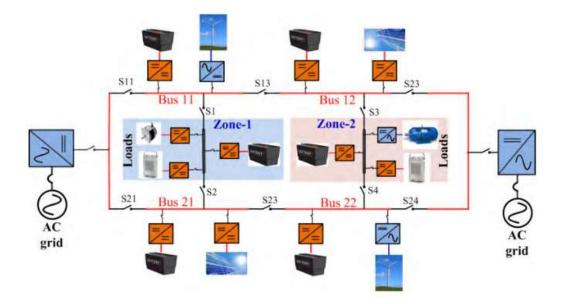

| Figure 1.2 Ring bus Structure of DC microgrids ([16])                                  | 3  |

| Figure 1.3 Zonal Structure of DC microgrids ([18])                                     | 4  |

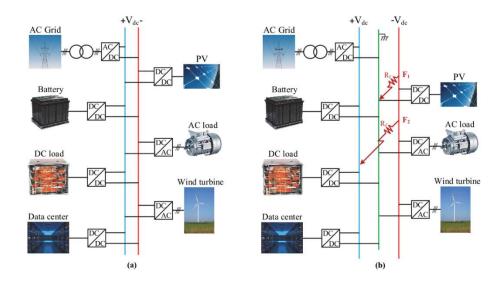

| Figure 1.4 DC voltage polarity (a) Unipolar (b) Bipolar ([19])                         | 4  |

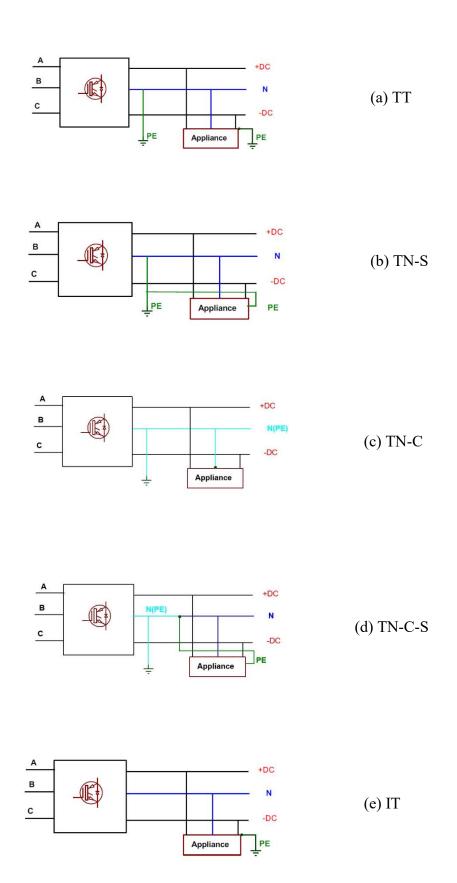

| Figure 1.5 DC grounding configurations (adapted from [22])                             | 7  |

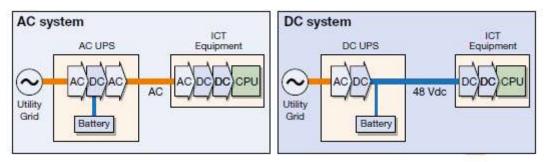

| Figure 1.6 Comparison of UPS installed in AC and DC system [31]                        | 9  |

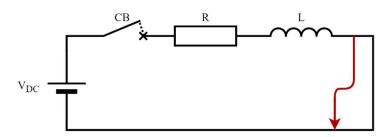

| Figure 1.7 Simplified equivalent circuit of a DC grid                                  | 12 |

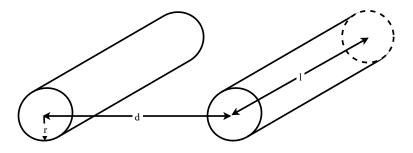

| Figure 1.8 Cross-section of the cable                                                  | 12 |

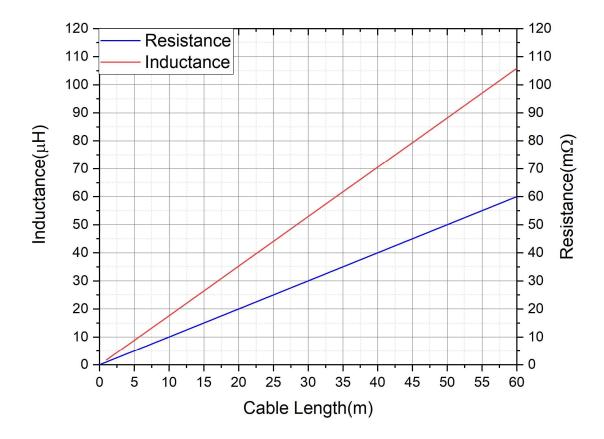

| Figure 1.9 Cable inductance and resistance against cable length                        | 14 |

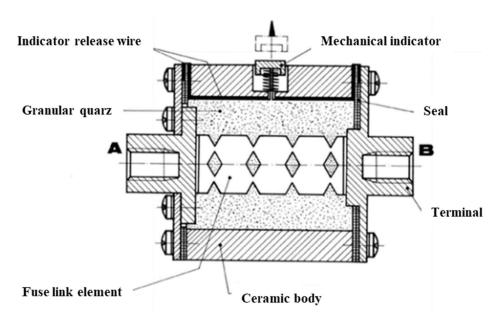

| Figure 1.10 Cross-section of a fuse [40]                                               | 15 |

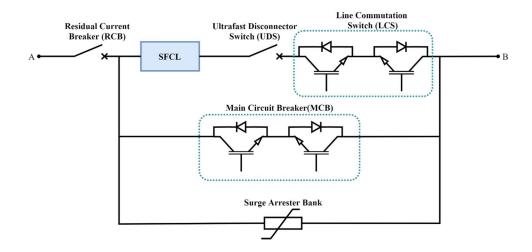

| Figure 1.11 Hybrid circuit breaker with superconductor (adapted from [47])             | 16 |

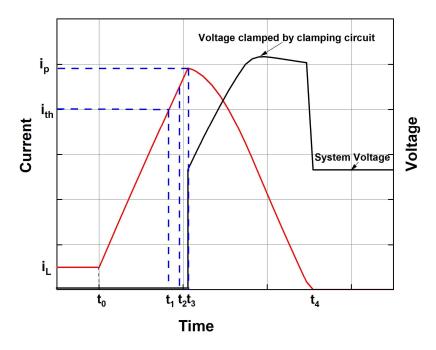

| Figure 2.1 Typical overcurrent protection process of a circuit breaker                 | 28 |

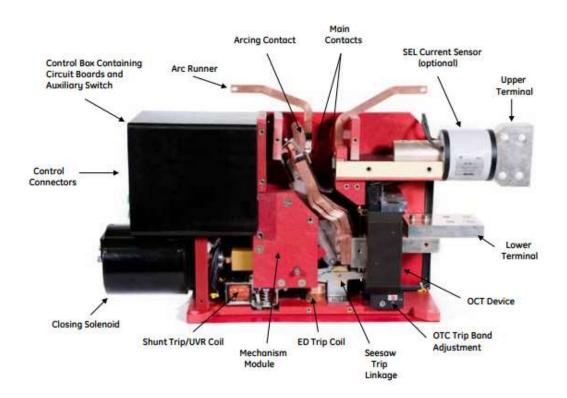

| Figure 2.2 DC circuit breaker anatomy [5]                                              | 29 |

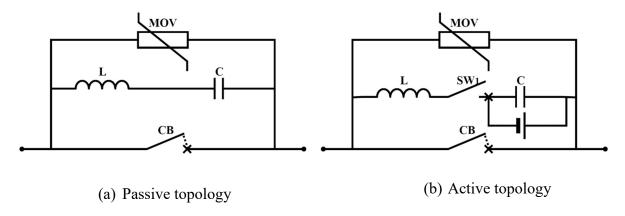

| Figure 2.3 Two topologies of DC EMCBs                                                  | 31 |

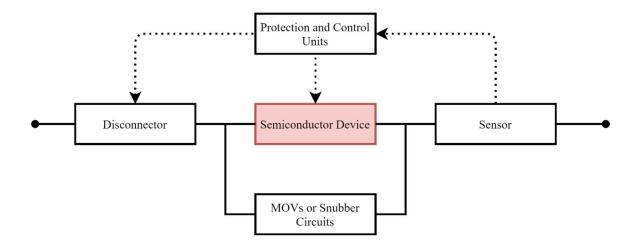

| Figure 2.4 Typical configuration of SSCBs                                              | 32 |

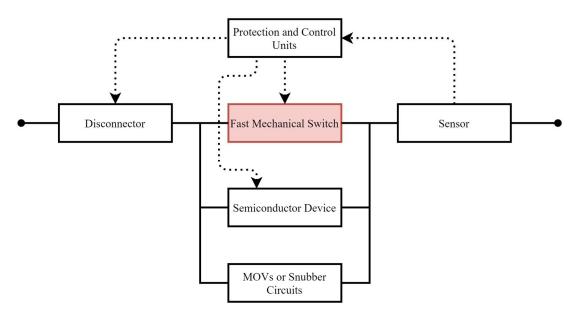

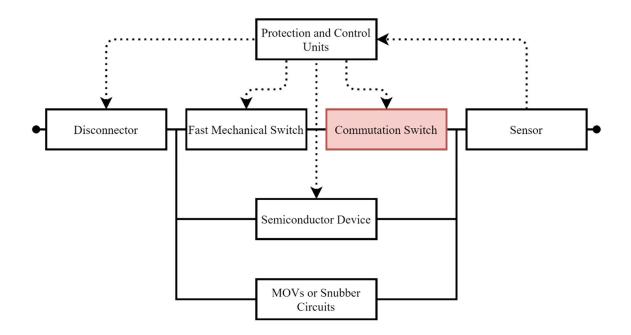

| Figure 2.5 Typical configuration of HCBs                                               | 33 |

| Figure 2.6 ABB Hybrid Circuit breaker (adapted from [10])                              | 34 |

| Figure 2.7 Thyristor based SSCB (adapted from [12])                                    | 36 |

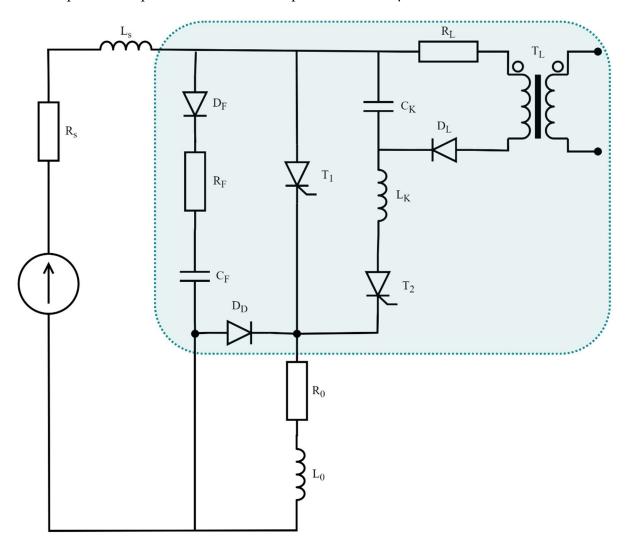

| Figure 2.8 Z-source circuit breaker [11]                                               | 37 |

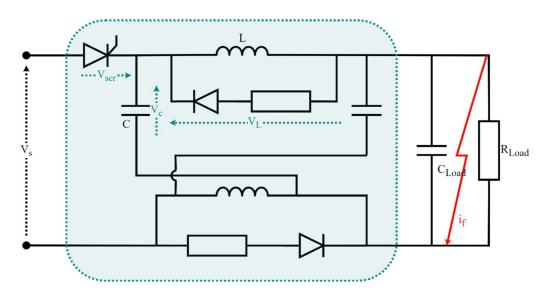

| Figure 2.9 MOSFET-based SSCB schematic circuit (adapted from [23])                     | 38 |

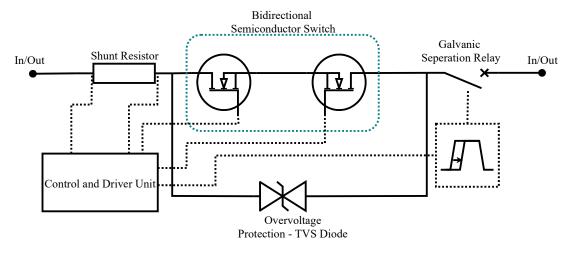

| Figure 2.10 IGBT based SSCB configuration [26]                                         | 39 |

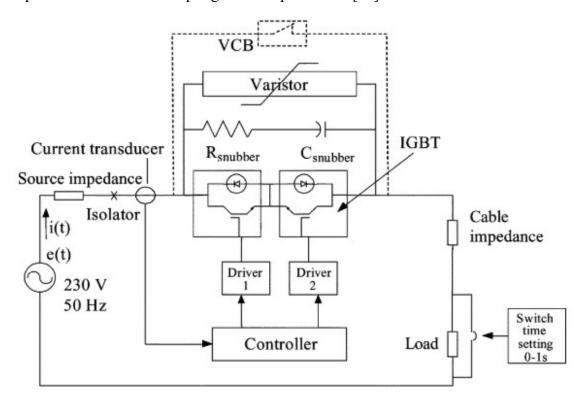

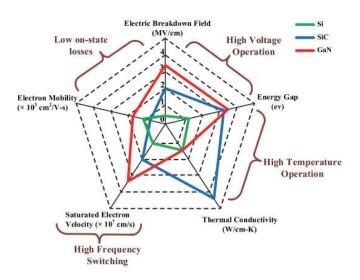

| Figure 2.11 Comparison of Si, SiC, and GaN material properties [30]                    | 40 |

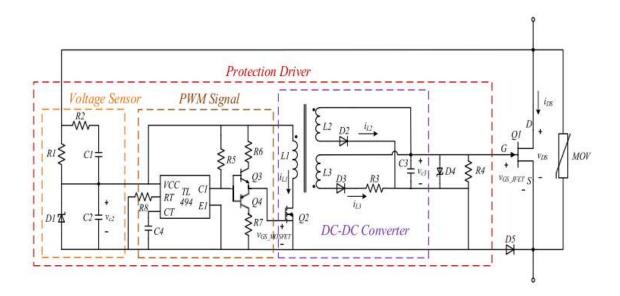

| Figure 2.12 schematic circuit of self-powered SSCB topology ([36])                     | 42 |

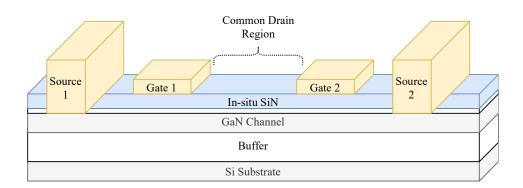

| Figure 2.13 cross-section of monolithic dual-gate bidirectional GaN switch (adapted to |    |

| Figure 2.14 a SSCB based on SiC MOSFETs [41]                                           |    |

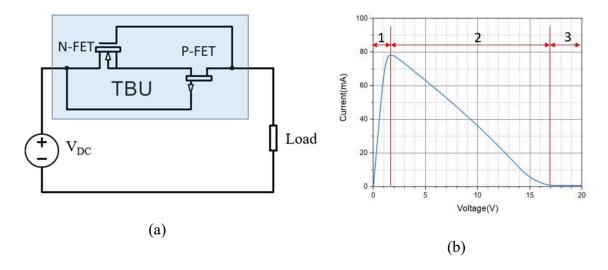

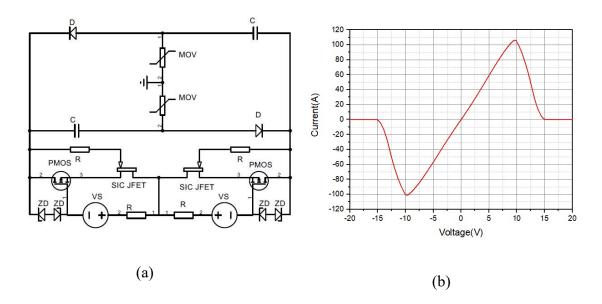

| Figure 3.1(a) Basic TBU circuit (b) Typical I-V of the TBU                             | 54 |

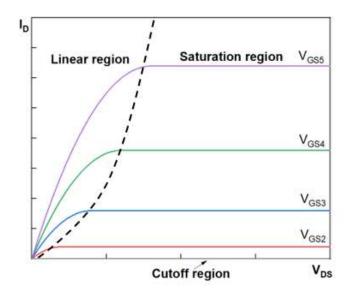

| Figure 3.2 I-V characteristics of a typical MOSFET                                     | 56 |

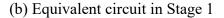

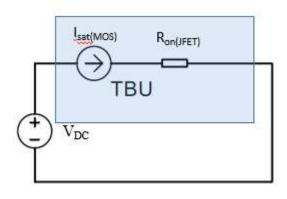

| Figure 3.3 Equivalent circuits of basic TBU in three stages                            | 57 |

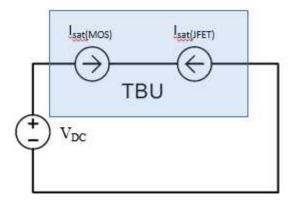

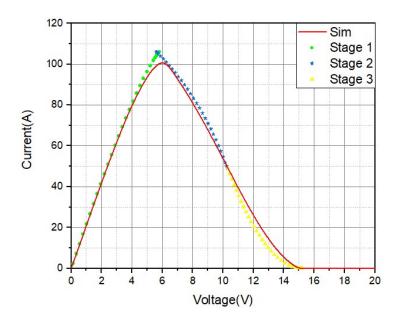

| Figure 3.4 Comparison of simulated and calculated I-V curve of the basic TBU           | 62 |

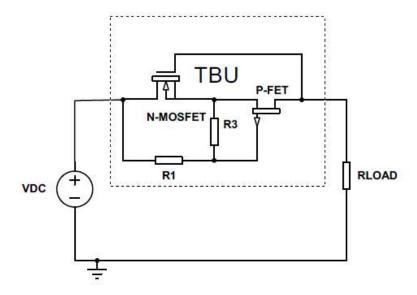

| Figure 3.5 Schematic of the basic TBU with two resistors                               | 63 |

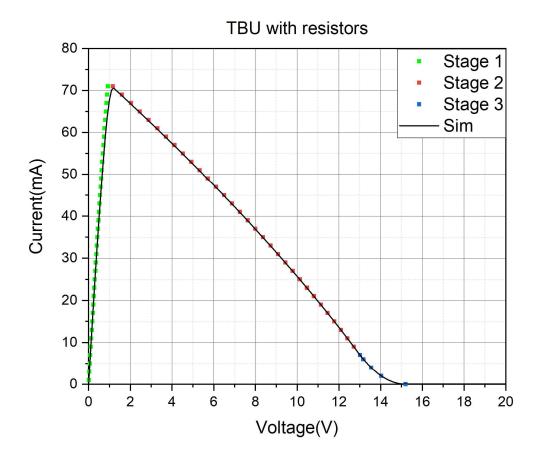

| Figure 3.6 Comparison of simulated and calculated I-V curves of the basic TBU wi          | th two  |

|-------------------------------------------------------------------------------------------|---------|

| resistors                                                                                 | 66      |

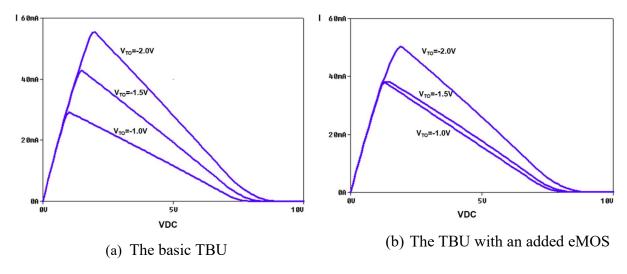

| Figure 3.7 Output current of the TBU with varied threshold voltage                        | 67      |

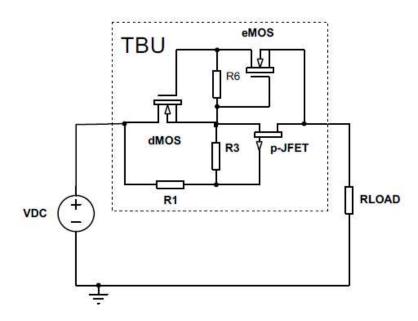

| Figure 3.8 TBU with added enhancement mode MOSFET                                         | 67      |

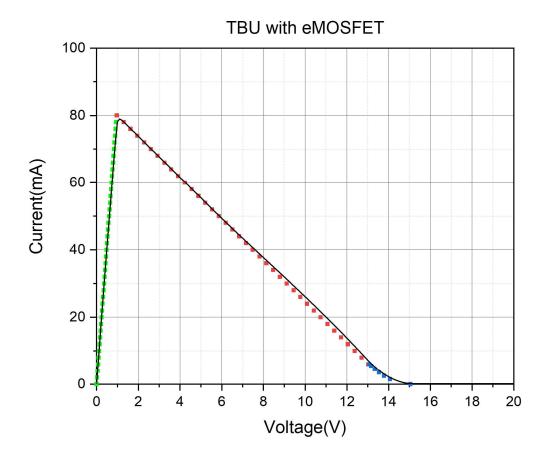

| Figure 3.9 Comparison of simulated and calculated I-V curve of the TBU with eMOS          | 74      |

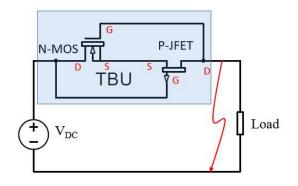

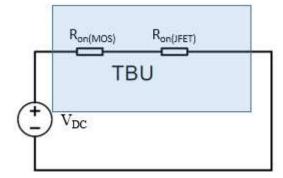

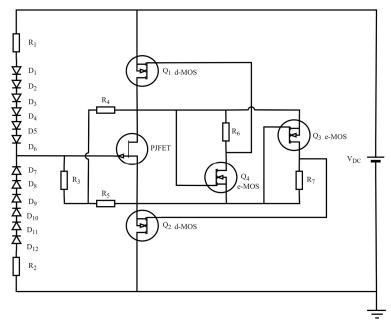

| Figure 3.10 Practical bidirectional TBUs                                                  | 75      |

| Figure 3.11 Practical TBUs [2]                                                            | 80      |

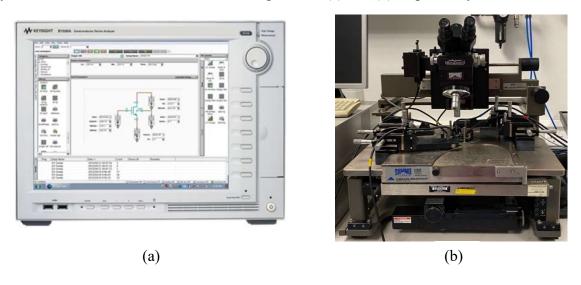

| Figure 3.12 (a) Device analyser B1500A (b) Probe Station                                  | 80      |

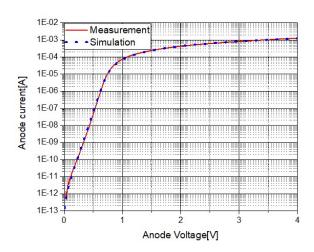

| Figure 3.13 Forward characteristic of the diode                                           | 81      |

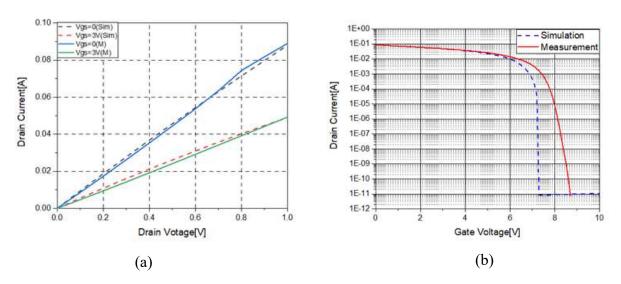

| Figure 3.14 (a) Output characteristics (b) Transfer characteristics of the pJFET          | 81      |

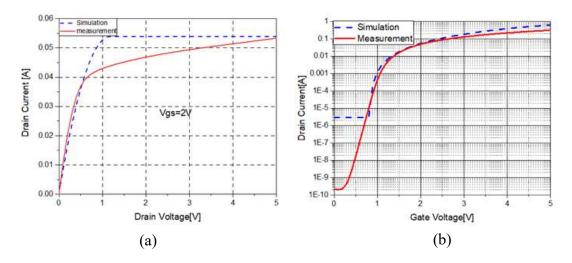

| Figure 3.15(a) Output characteristics (b) Transfer characteristics of the eMOS            | 82      |

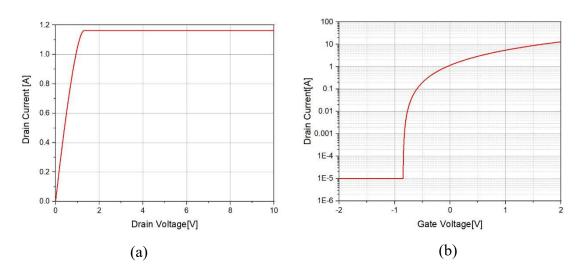

| Figure 3.16 (a) Output characteristics (b) Transfer characteristics of the dMOS           | 82      |

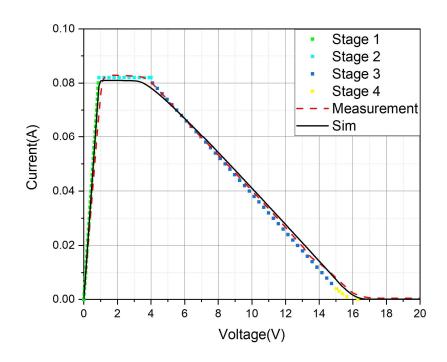

| Figure 3.17 Comparison of calculation, simulation and measurement for TBU-CA 250 50       | 084     |

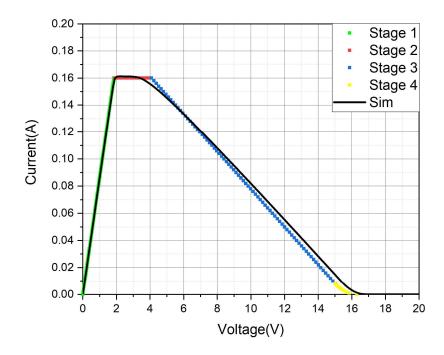

| Figure 3.18 Comparison of calculation, simulation and measurement for TBU-CA 650 10       | 0085    |

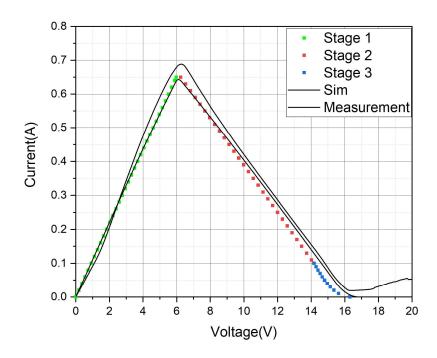

| Figure 3.19 Comparison of calculation, simulation and measurement for TBU-CA 850 50       | 0086    |

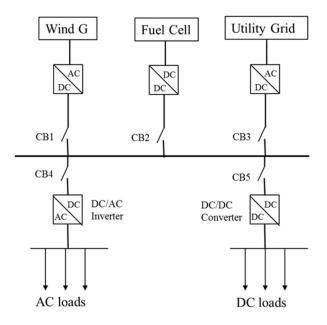

| Figure 4.1 A typical 400V DC distribution system (adapt from [1])                         | 88      |

| Figure 4.2 Functionalities of the proposed SSCB                                           | 89      |

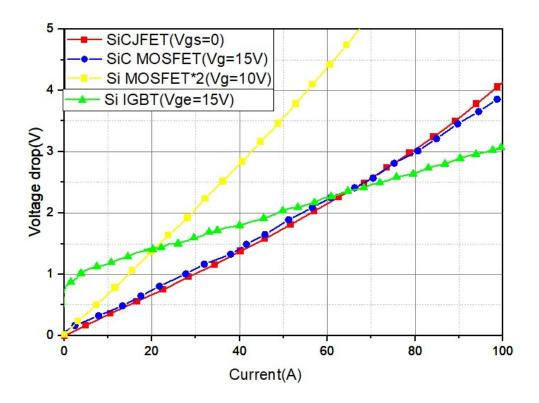

| Figure 4.3 Comparison of voltage drops of four candidate devices                          | 97      |

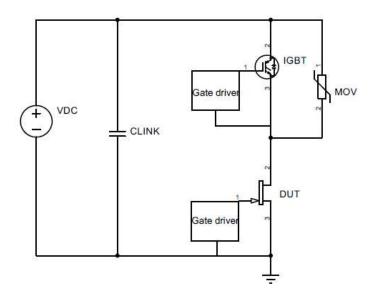

| Figure 4.4 The schematic circuit for short-circuit capability test                        | 99      |

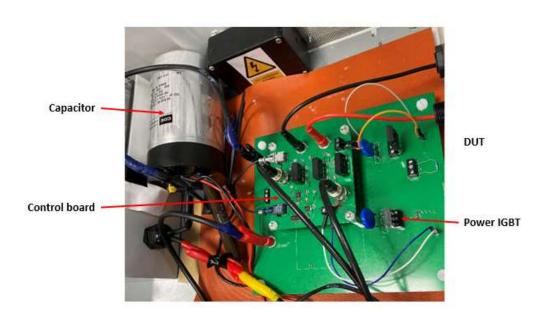

| Figure 4.5 Photo of the test bench                                                        | 99      |

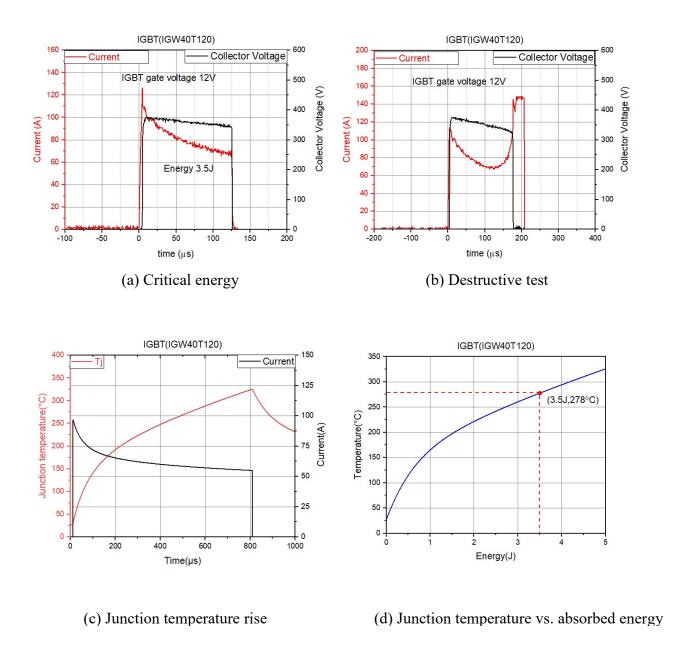

| Figure 4.6 Si IGBT Short-circuit capability                                               | 101     |

| Figure 4.7 SiC MOSFET short-circuit capability                                            | 102     |

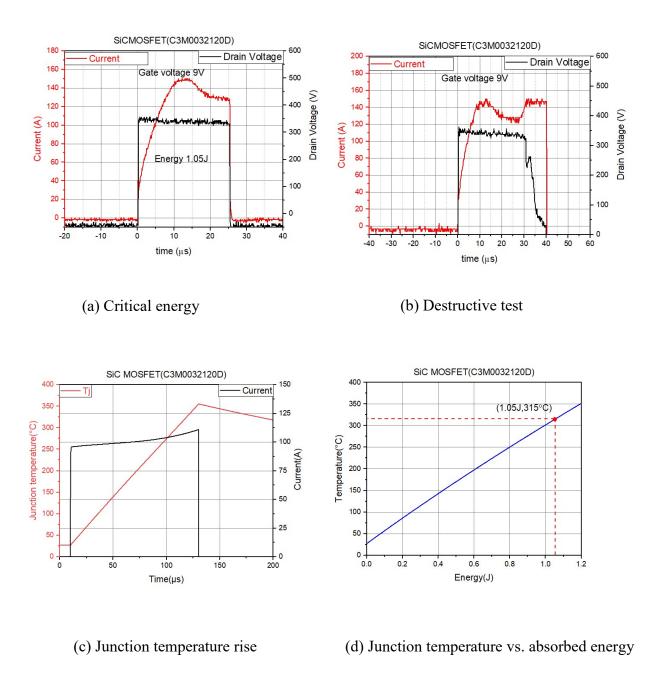

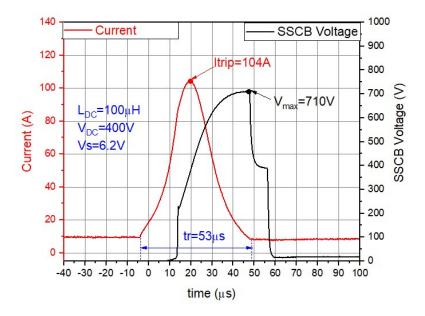

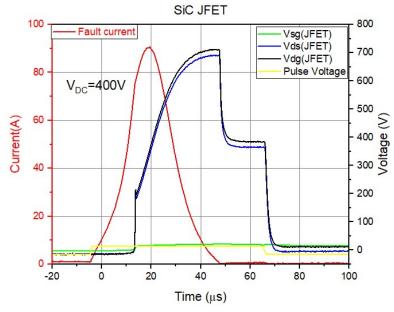

| Figure 4.8 Si MOSFET short-circuit capability                                             | 103     |

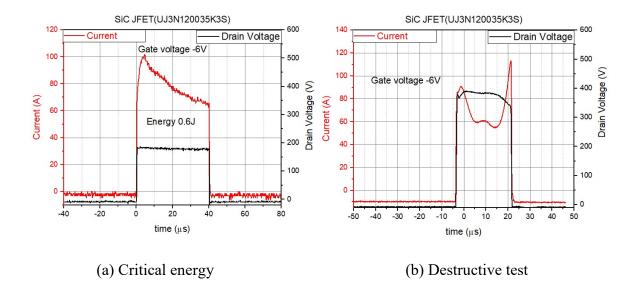

| Figure 4.9 SiC JFET short-circuit capability                                              | 104     |

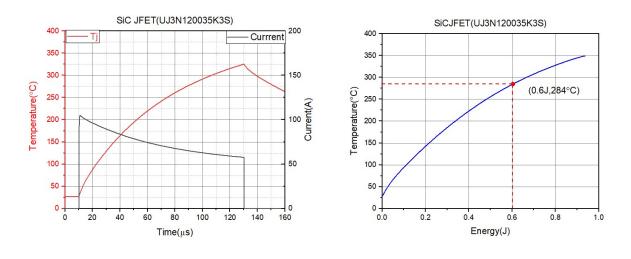

| Figure 4.10 Saturation characteristics under various temperatures and gate voltages       | 105     |

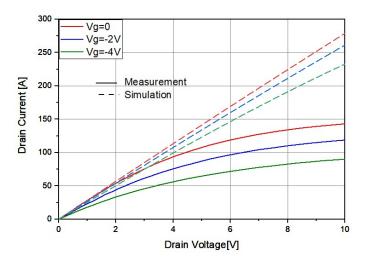

| Figure 4.11 Measurement against Simulated output characteristics of original SPICE m      | odel at |

| the room temperature                                                                      | 107     |

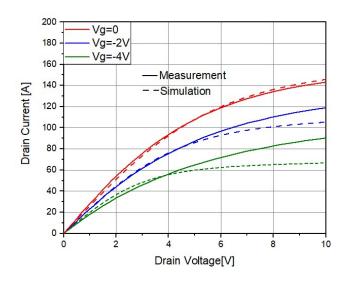

| Figure 4.12 Measurement against Simulated output characteristics of modified SPICE m      | odel at |

| the room temperature                                                                      | 107     |

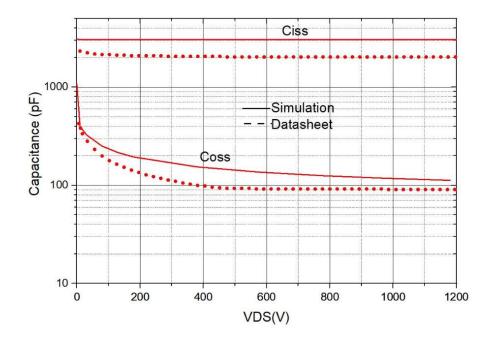

| Figure 4.13 C-V curves extracted from datasheet against simulated results of original     | SPICE   |

| model                                                                                     | 108     |

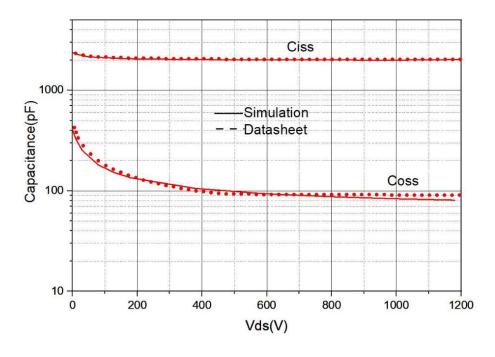

| Figure 4.14 C-V curves extracted from datasheet against simulated results of the modified | SPICE   |

| model                                                                                     | 108     |

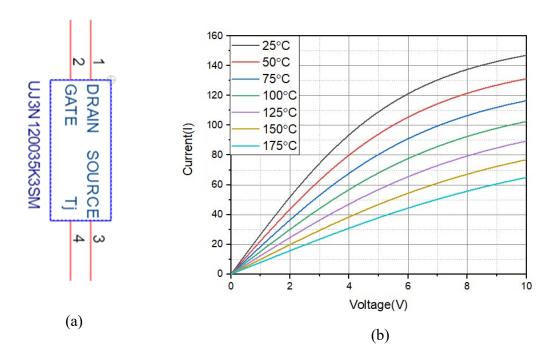

| Figure 4.15(a) Symbol of the modified SPICE model (b) Simulated output characteristics     | of the |

|--------------------------------------------------------------------------------------------|--------|

| modified SPICE model under various junction temperatures                                   | 109    |

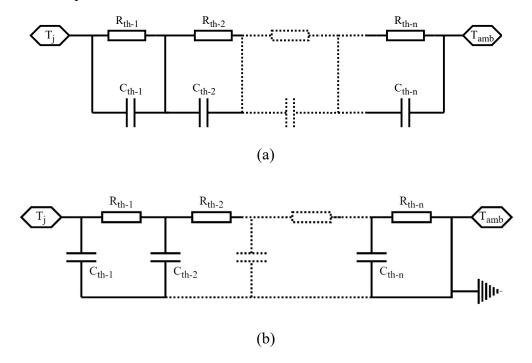

| Figure 4.16 (a) Foster model (b) Cauer model                                               | 111    |

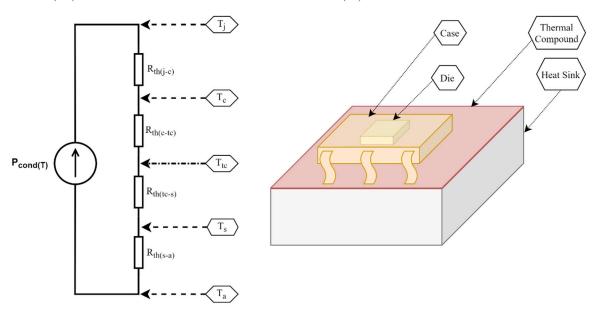

| Figure 4.17 Thermal equivalent circuit and schematic diagram of a typical device           | 112    |

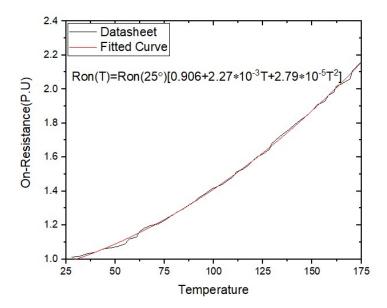

| Figure 4.18 Curve fitted on-resistance against temperature                                 | 113    |

| Figure 4.19 Heatsink with 1.4°C/W                                                          | 115    |

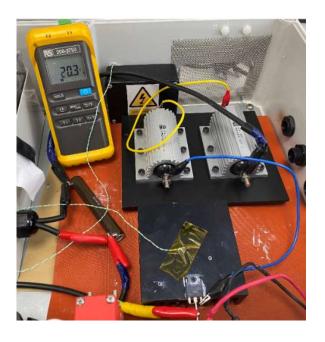

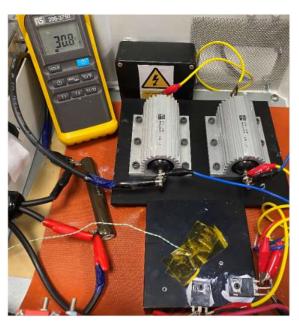

| Figure 4.20 Hardware of temperature measurement                                            | 116    |

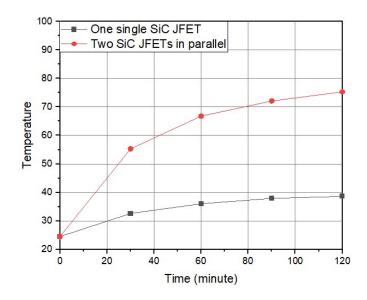

| Figure 4.21 Measured temperature under rated current                                       | 117    |

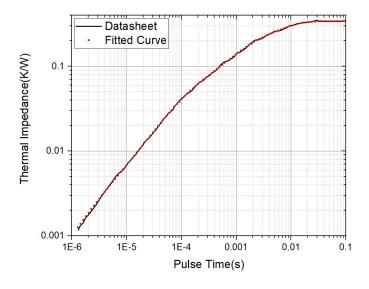

| Figure 4.22 Curve fitted Foster network impedance                                          | 117    |

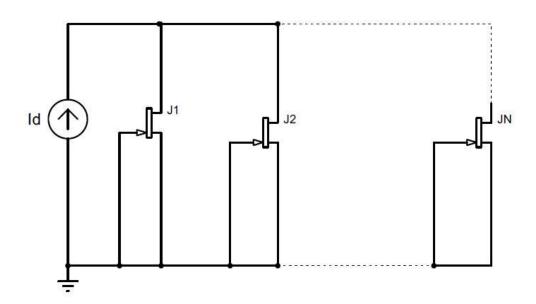

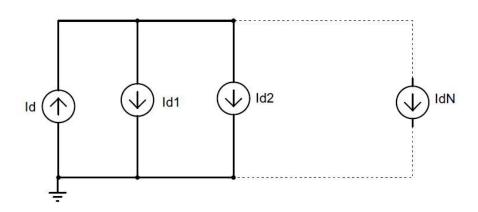

| Figure 4.23 SiC JFETs in parallel                                                          | 118    |

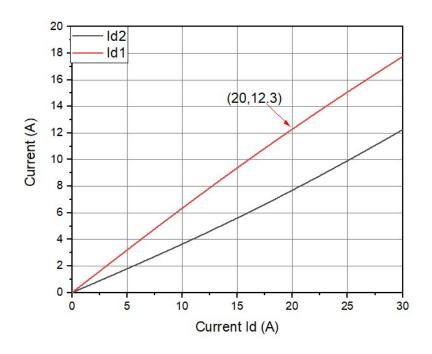

| Figure 4.24 Current sharing between two SiC JFETs in parallel                              | 122    |

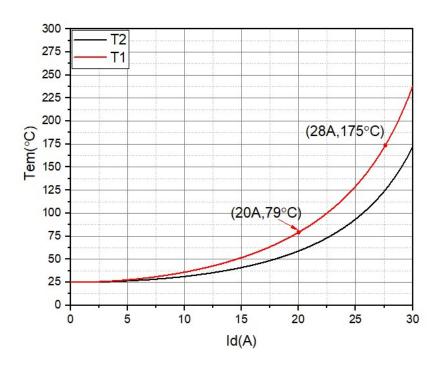

| Figure 4.25 Junction temperature vs. current                                               | 122    |

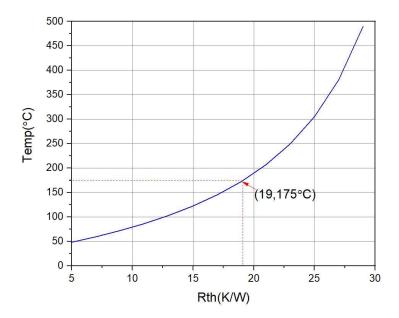

| Figure 4.26 Impact of thermal resistance on the junction temperature                       | 123    |

| Figure 4.27 Paralleling SiC JFETs operates in saturation region                            | 124    |

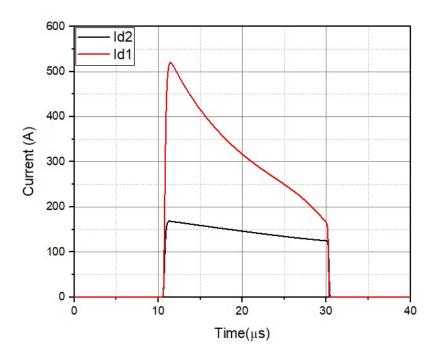

| Figure 4.28 Dynamic current sharing of two SiC JFETs in parallel                           | 125    |

| Figure 4.29 Junction temperatures of two paralleling SiC JFETs                             | 125    |

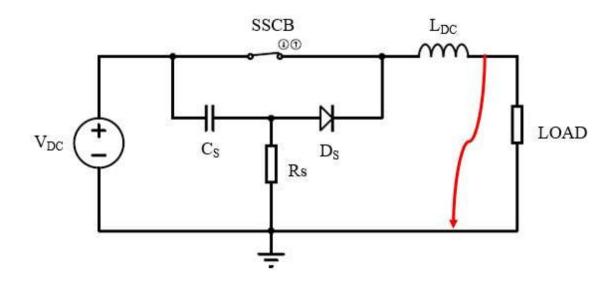

| Figure 5.1 Charge-discharge type RCD snubber                                               | 133    |

| Figure 5.2 Discharge-supressing type RCD                                                   | 134    |

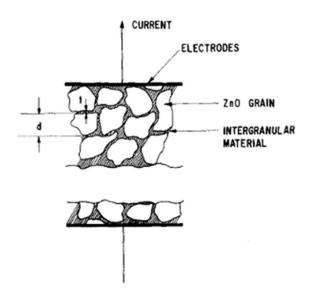

| Figure 5.3 Physical Structure of the MOV [11]                                              | 135    |

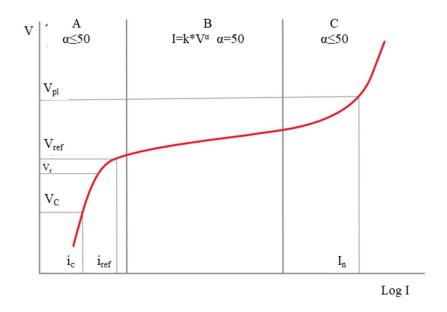

| Figure 5.4 Typical V-I characteristic of MOVs ([12])                                       | 136    |

| Figure 5.5 MOV as a snubber                                                                | 136    |

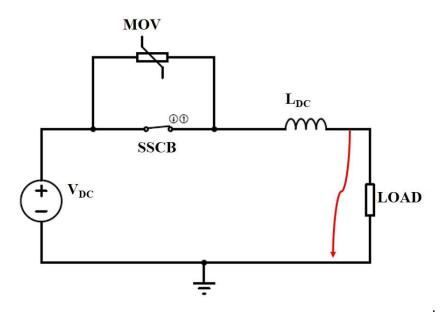

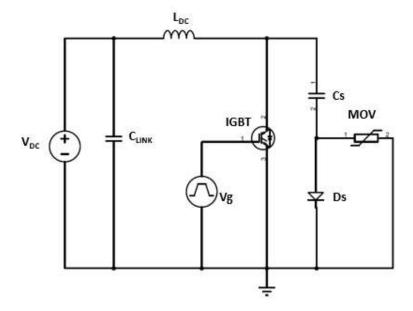

| Figure 5.6 Proposed snubber circuit                                                        | 137    |

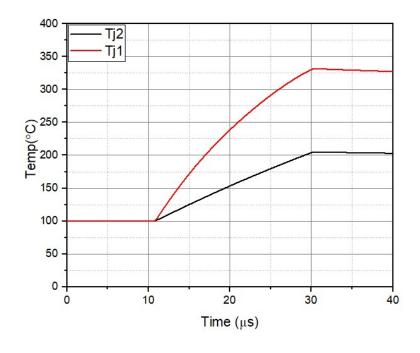

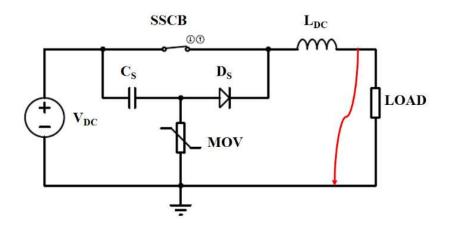

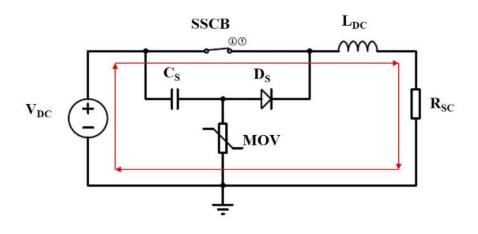

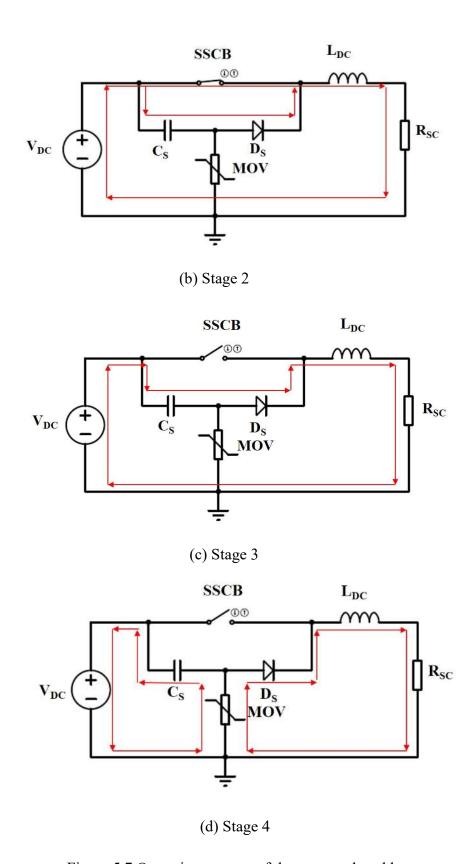

| Figure 5.7 Operating process of the proposed snubber                                       | 138    |

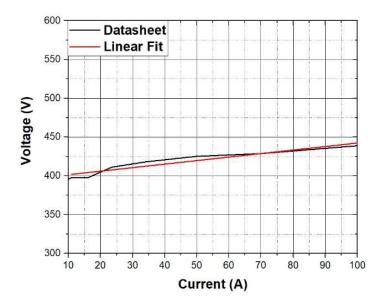

| Figure 5.8 MOV V-I characteristic and its linear fitted curve                              | 143    |

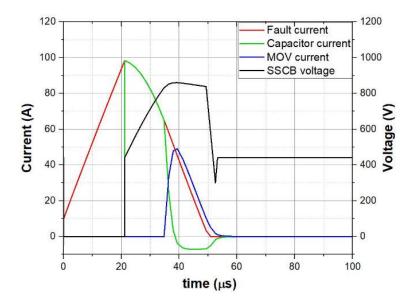

| Figure 5.9 Simulation waveforms                                                            | 145    |

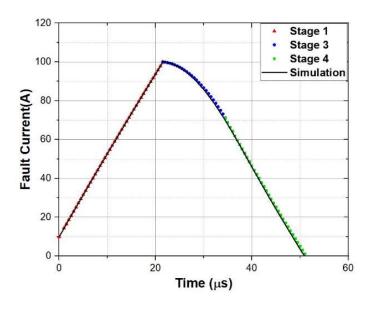

| Figure 5.10 Comparison of simulated and calculated fault current in each stage             | 145    |

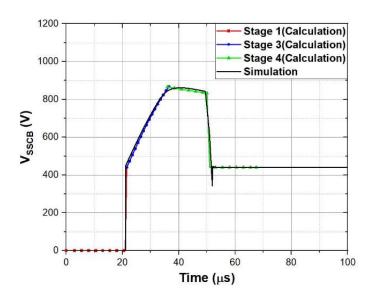

| Figure 5.11 Comparison of simulated and calculated voltage across SSCB in each stage       | 146    |

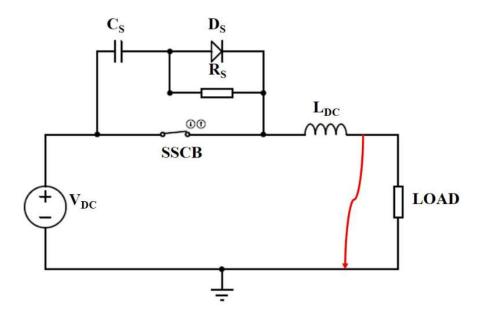

| Figure 5.12 Schematic of the snubber test bench                                            | 147    |

| Figure 5.13 Hardware of the experimental setup                                             | 147    |

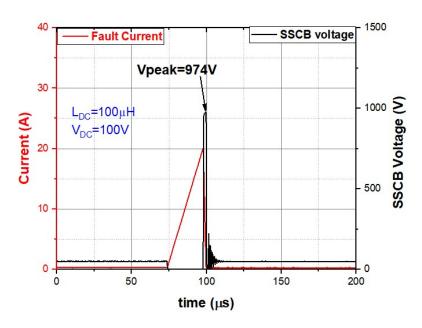

| Figure 5.14 Switching operation without and with the proposed snubber                      | 148    |

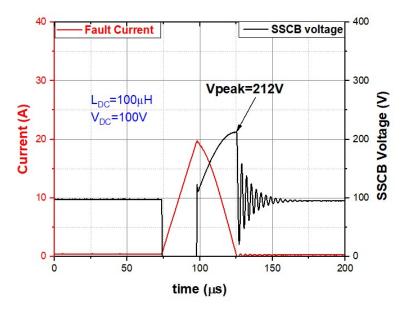

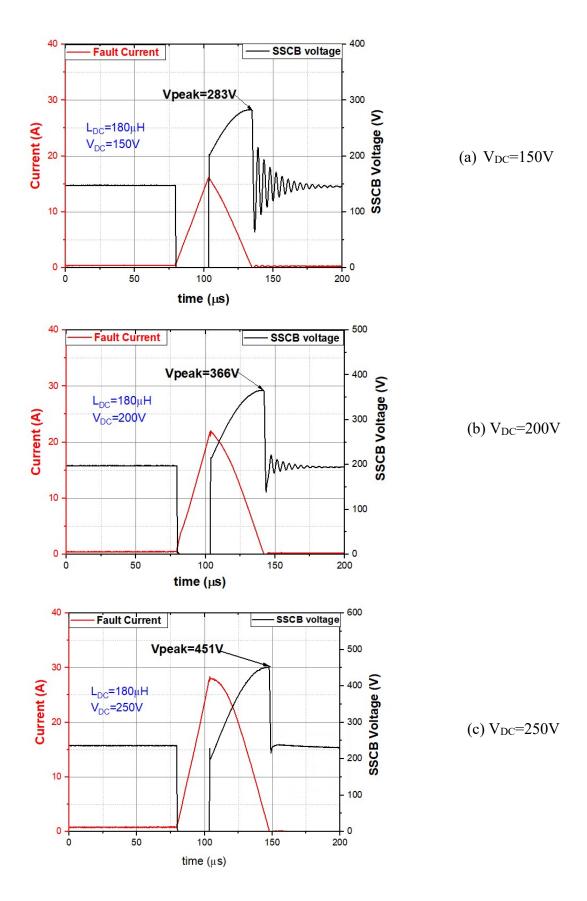

| Figure 5.15 Experimental Results with the proposed snubber                                 | 149    |

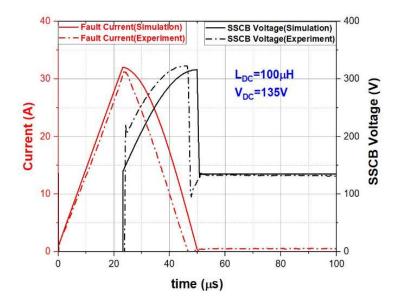

| Figure 5.16 Comparison of experiment and simulation results                                | 150    |

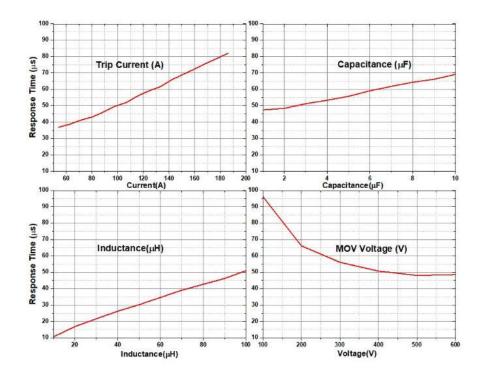

| Figure 5.17 Response time as a function of trip current, snubber capacitance, system induc | ctance |

| and MOV clamping voltage                                                                   | 151    |

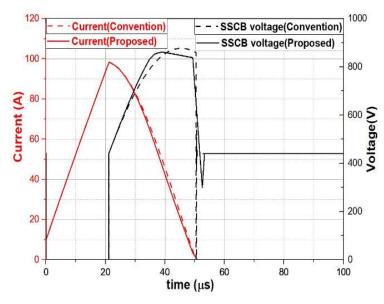

| Figure 5.18 Comparison of fault current and SSCB voltage                                           | 152        |

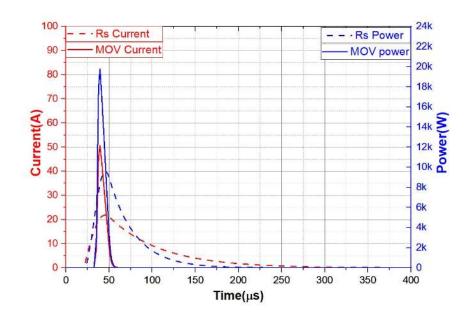

|----------------------------------------------------------------------------------------------------|------------|

| Figure 5.19 Comparison of current and power through Rs and MOV                                     | 153        |

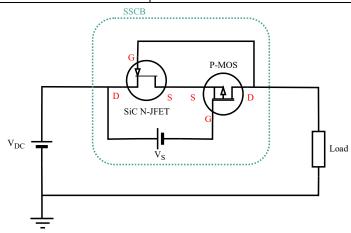

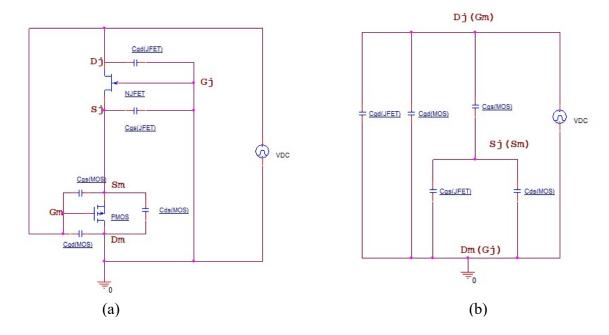

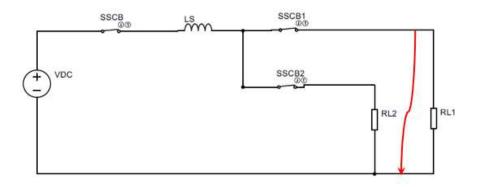

| Figure 6.1 Basic circuit topology for SSCB application                                             | 159        |

| Figure 6.2 Equivalent circuits of the proposed SSCB in each stage                                  | 160        |

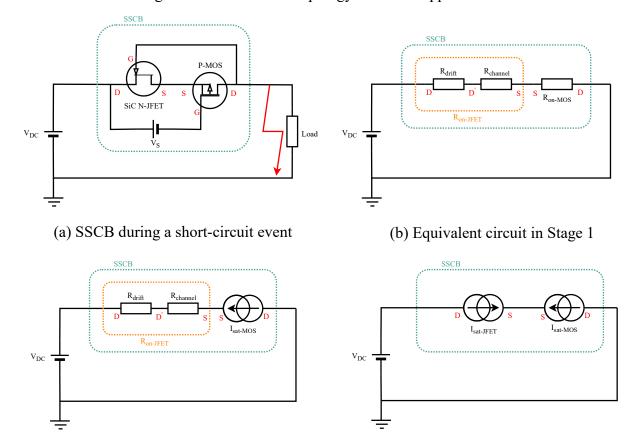

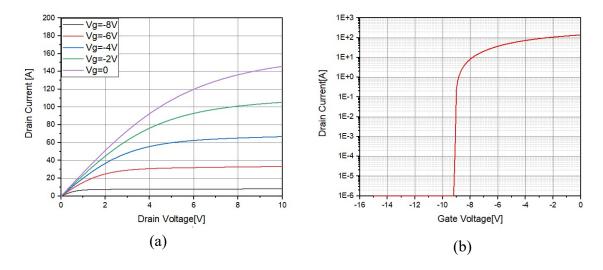

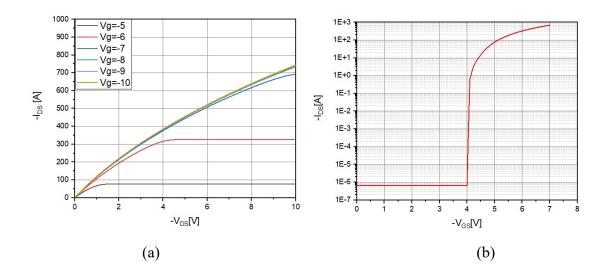

| Figure 6.3 SiC JFET (a) Output characteristic (b) Transfer characteristic                          | 165        |

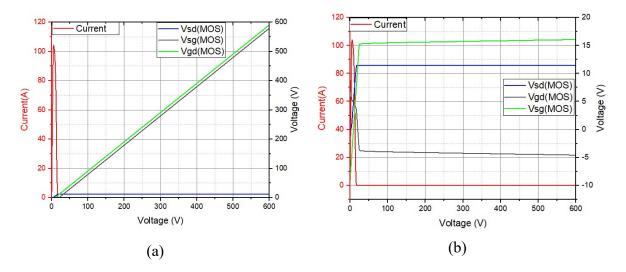

| Figure 6.4 P-MOSFET (a) Output characteristic (b) Transfer characteristic                          | 165        |

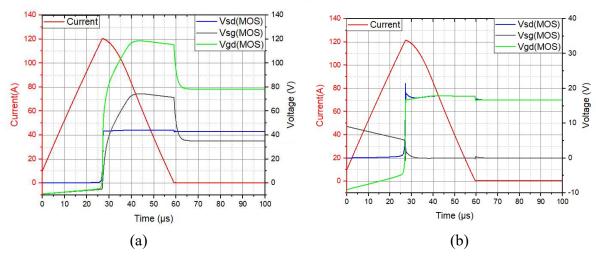

| Figure 6.5 Comparison of simulated and calculated results                                          | 166        |

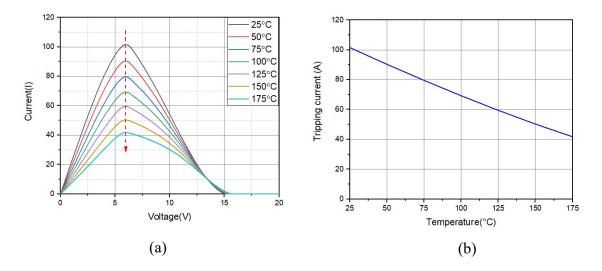

| Figure 6.6 (a) I-V curves under different junction temperatures (b) Tripping current vs            | Junction   |

| temperature                                                                                        | 167        |

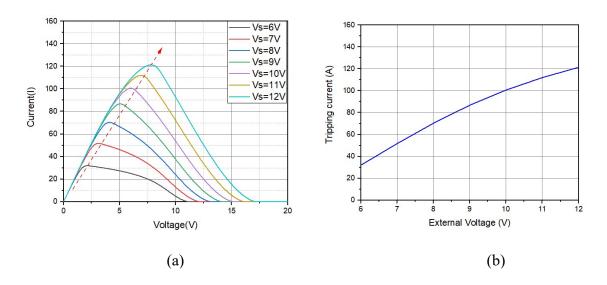

| Figure 6.7 (a) I-V curves under external voltages (b) Tripping Current vs External Volt            | age .167   |

| Figure 6.8 (a) Equivalent circuit of static off-state of the SSCB (b) Simplified equivale          | nt circuit |

|                                                                                                    | 169        |

| Figure 6.9 (a) Equivalent circuit of transient off-state of SSCB (b) Simplified circuit            | 170        |

| Figure 6.10 (a) Static voltages across MOSFET terminals without the Zener diodes (                 | (b) Static |

|                                                                                                    | 171        |

| Figure 6.11(a) Transient voltages across MOSFET terminals without the Zener di                     | odes (b)   |

| Transient voltages across MOSFET terminals with the Zener diodes                                   | 171        |

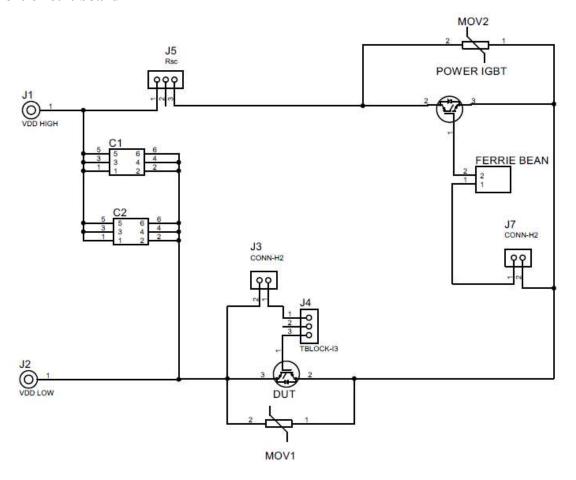

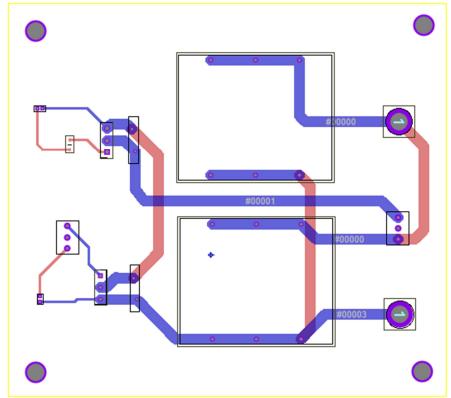

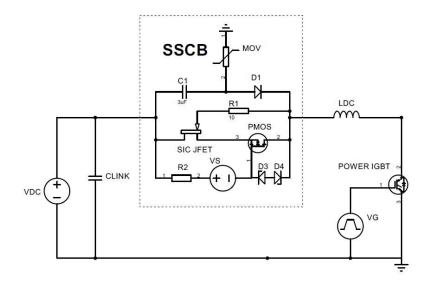

| Figure 6.12 Schematic of the short-circuit test circuit                                            | 172        |

| Figure 6.13 Hardware of short-circuit test                                                         | 172        |

| Figure 6.14 1000V DC power supply                                                                  | 173        |

| Figure 6.15 enclosed test box                                                                      | 173        |

| Figure 6.16 Pictures of the proposed SSCB                                                          | 174        |

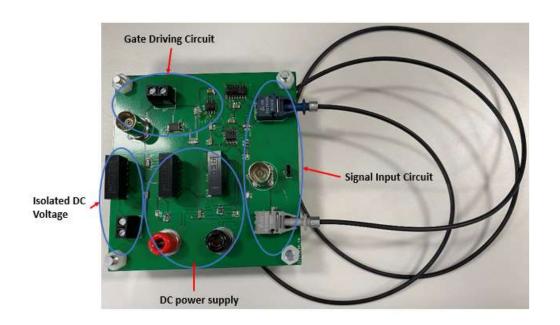

| Figure 6.17 Main components on the SSCB board                                                      | 174        |

| Figure 6.18 Short-circuit board                                                                    | 175        |

| Figure 6.19 Flow chart of gate driving circuit                                                     | 175        |

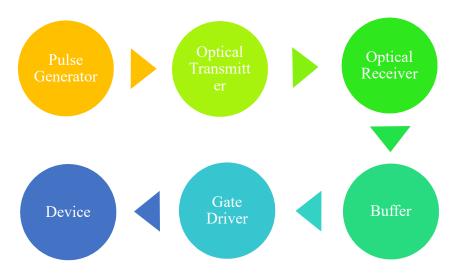

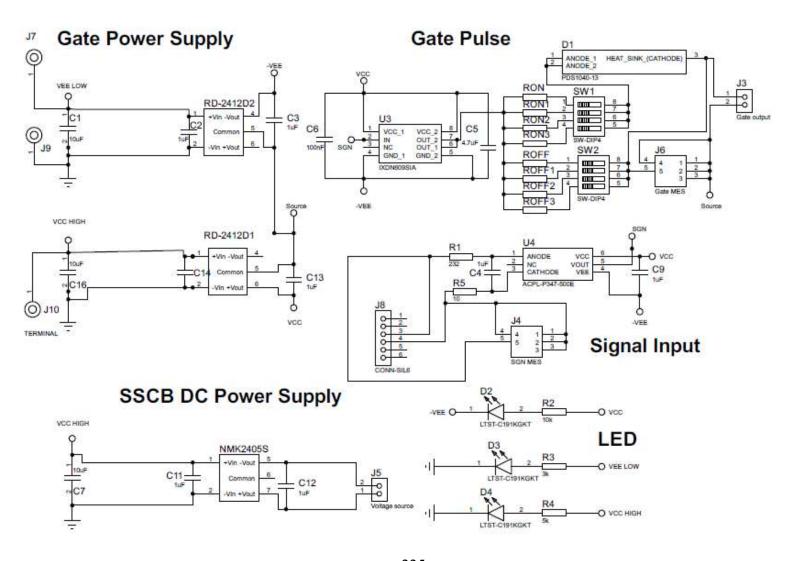

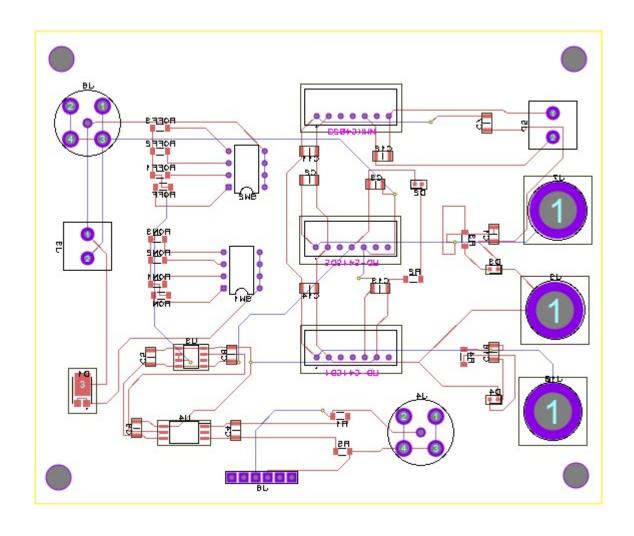

| Figure 6.20 Gate driving circuit board                                                             | 176        |

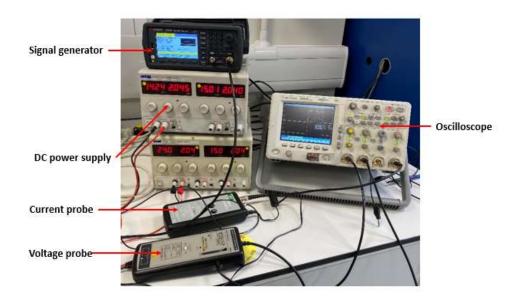

| Figure 6.21 Measurement instruments                                                                | 177        |

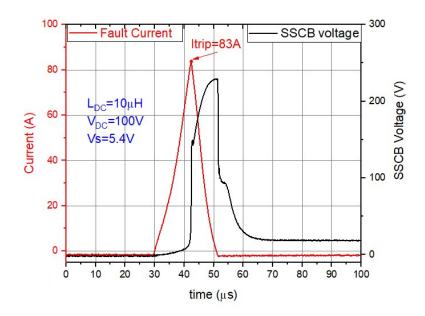

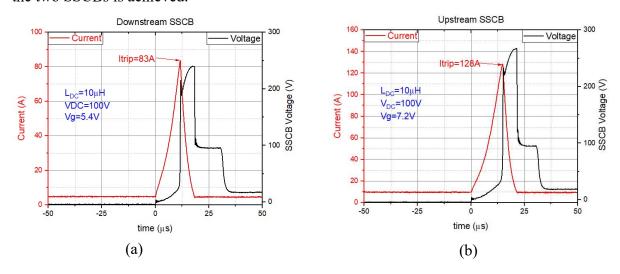

| Figure 6.22: Short-circuit test under the condition: $L_{DC}=10\mu H$ , $V_{DC}=100V$ and external | l voltage  |

| Vs=5.4V                                                                                            | 178        |

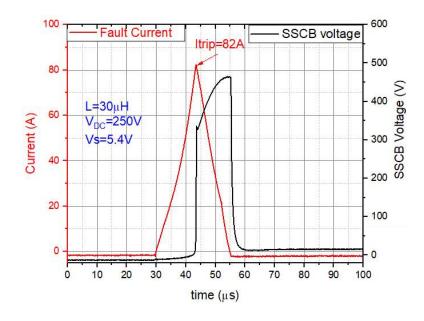

| Figure 6.23 Short-circuit test under the condition: LDC=30μH, VDC=250V and external                | ıl voltage |

| Vs=5.4V                                                                                            | 178        |

| Figure 6.24 Short-circuit test under the condition: LDC=30μH, VDC=250V and externa                 | ıl voltage |

| Vs=7 2V                                                                                            | 179        |

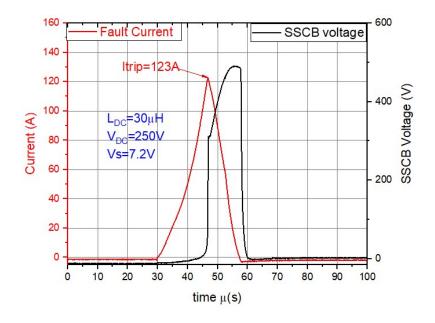

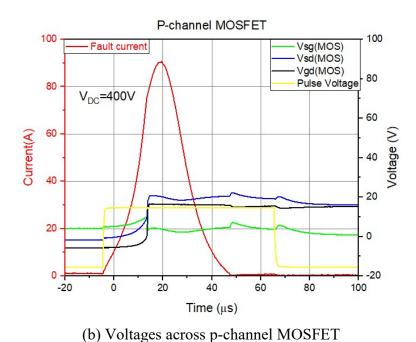

| Figure 6.25 Short-circuit test under the condition: LDC=100μH, VDC=400V and external externa | ernal |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| voltage Vs=6.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .179  |

| Figure 6.26 Voltage distribution after turn-off of the SSCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .180  |

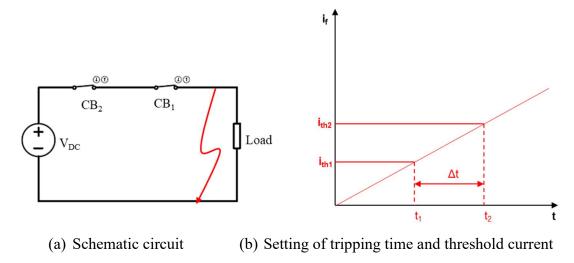

| Figure 6.27 Overcurrent protection coordination between SSCBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .181  |

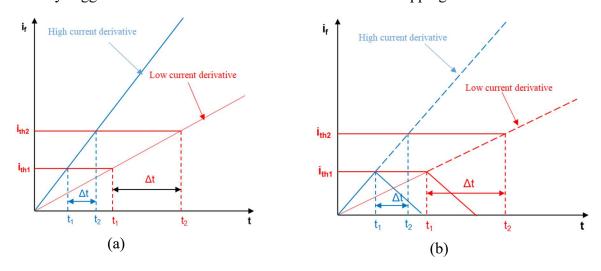

| Figure 6.28 Protection coordination (a) Conventional SSCBs (b) The proposed SSCBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .182  |

| Figure 6.29 Output characteristic of upstream SSCB (a) Static output (b) Transient output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .183  |

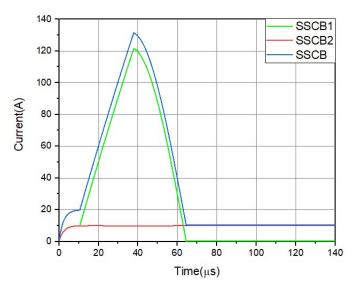

| Figure 6.30 Overcurrent protection coordination between SSCBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .183  |

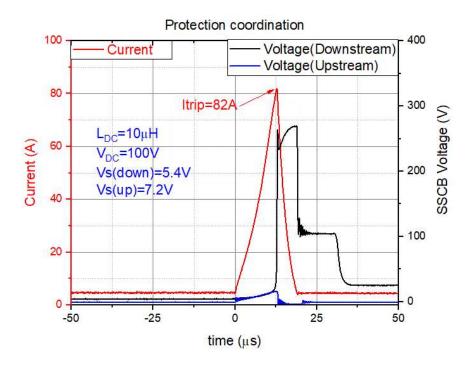

| Figure 6.31 Simulated overcurrent protection coordination between SSCBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .184  |

| Figure 6.32 Tripping currents of SSCBs (a) Downstream SSCB (b) Upstream SSCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .184  |

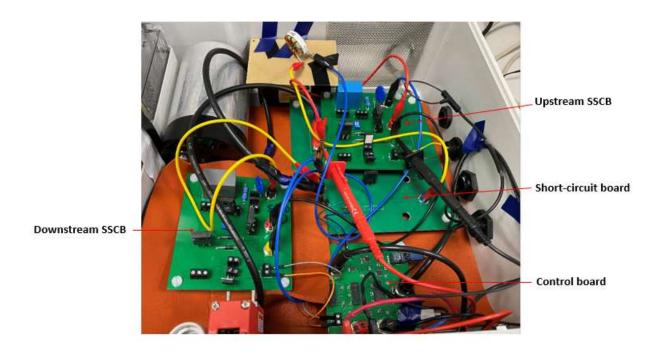

| Figure 6.33 Hardware of overcurrent protection coordination experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .185  |

| Figure 6.34 Protection coordination between two SSCBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .185  |

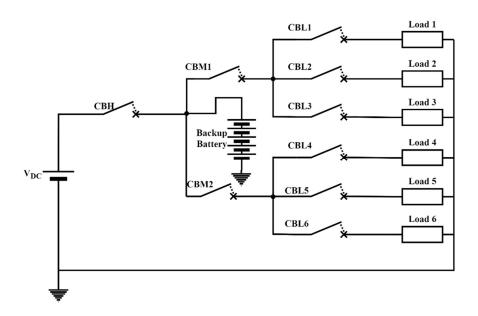

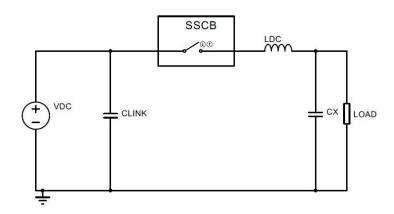

| Figure 6.35 Schematic of a DC system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .186  |

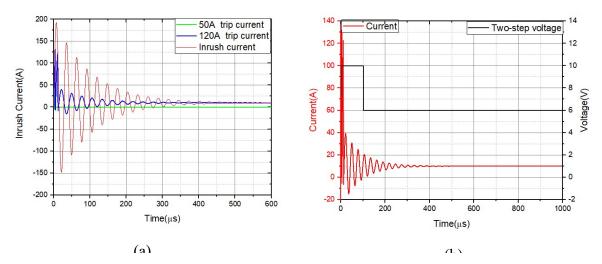

| Figure 6.36 Two-step solution (a) SSCBs with different tripping current (b) Load start-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .187  |

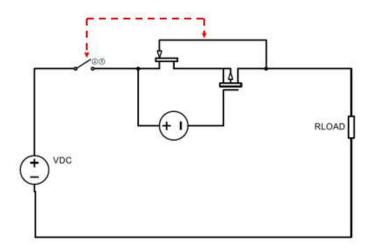

| Figure 6.37 SSCB reset and fail-safe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .187  |

| Figure 7.1 Typical trip curves of SSCBs and EMCBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .193  |

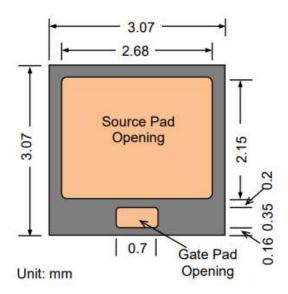

| Figure 7.2 Die Size of UJ3N120035K3S [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .195  |

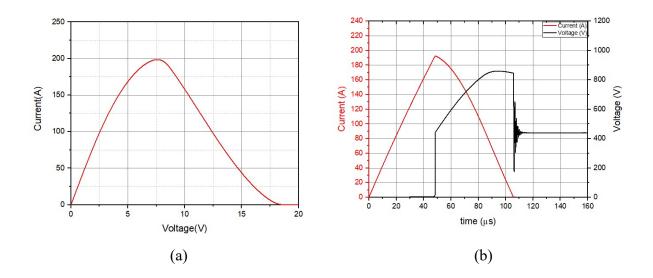

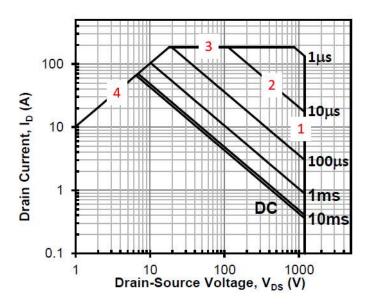

| Figure 7.3 SOA curve of UJ3N120035K3S [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .196  |

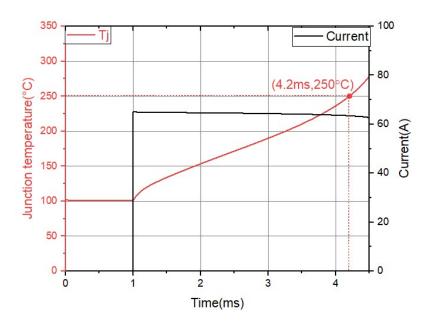

| Figure 7.4 Simulated junction temperature for a 65A pulsed current injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .197  |

| Figure 7.5 Overload curve for the proposed SSCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .197  |

| Figure 7.6 Schematic of the overload experimental setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .198  |

| Figure 7.7 Photo of the overload test bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .198  |

| Figure 7.8 Overload current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .199  |