# InAs avalanche photodiode linear array for low photon applications

Leh Woon Lim

A thesis submitted in fulfilment of the requirements for the degree of

Doctor of Philosophy

Department of Electronic and Electrical Engineering

The University of Sheffield

September 2020

# **Contents**

| List of I | Figures                                                            | V    |

|-----------|--------------------------------------------------------------------|------|

| List of T | Γables                                                             | ix   |

| Glossar   | y – List of Abbreviations                                          | X    |

| Glossar   | y – List of Symbols                                                | xii  |

| Acknow    | ledgments                                                          | XV   |

| Abstrac   | t                                                                  | xvi  |

| List of I | Publications                                                       | xvii |

| Chapter   | 1 Introduction                                                     | 1    |

| 1.1       | Light detection and ranging (LiDAR)                                | 1    |

| 1.1       | .1 Atmospheric LiDAR                                               | 1    |

| 1.1       | .2 Automotive LiDAR                                                | 3    |

| 1.2       | Infrared imaging                                                   | 8    |

| 1.3       | Telecommunication systems                                          | 9    |

| 1.4       | Literature review                                                  | 11   |

| 1.4       | .1 InAs                                                            | 11   |

| 1.4       | .2 Mercury Cadmium Telluride (MCT)                                 | 17   |

| 1.4       | .3 Other SWIR and MWIR APD materials                               | 20   |

| 1.5       | Motivation and thesis layout                                       | 24   |

| 1.6       | References                                                         | 26   |

| Chapter   | 2 Background Information                                           | 41   |

| 2.1       | Impact ionisation and avalanche gain                               | 41   |

| 2.2       | Avalanche excess noise                                             | 46   |

| 2.3       | APDs with low noise performance                                    | 47   |

| 2.3       | .1 Dead space effects in thin multiplication region                | 48   |

| 2.3       | .2 APDs employing impact ionisation engineering (I <sup>2</sup> E) | 49   |

| 2.4       | Ion implantation                                                   | 50   |

| 2.5     | Annealing                                                      | 52  |

|---------|----------------------------------------------------------------|-----|

| 2.6     | Edge breakdown in planar devices                               | 54  |

| 2.7     | Planar array design considerations                             | 56  |

| 2.8     | Reference                                                      | 59  |

| Chapter | 3 Experimental methodology                                     | 64  |

| 3.1     | Current-voltage measurement                                    | 64  |

| 3.2     | Capacitance-voltage measurement                                | 68  |

| 3.3     | Photomeasurements (responsivity and gain)                      | 71  |

| 3.3     | 3.1 Multiplication measurements                                | 73  |

| 3.4     | Temperature dependence (300K – 77K) studies                    | 74  |

| 3.4     | Low light level measurements                                   | 77  |

| 3.5     | Secondary Ion Mass Spectroscopy                                | 79  |

| 3.6     | References                                                     | 81  |

| Chapter | 4 Planar InAs photodiodes by 34 keV Be-ion implantation        | 82  |

| 4.1     | Fabrication of planar InAs diodes                              | 83  |

| 4.2     | Blanket Be-ion implanted mesa InAs diodes                      | 84  |

| 4.3     | Dopant profile by SIMS                                         | 86  |

| 4.4     | Be-ion implanted planar InAs diodes                            | 88  |

| 4.5     | Spatial uniformity of planar InAs photodiode                   | 90  |

| 4.6     | Lateral diffusion of Be dopants due to long annealing duration | 92  |

| 4.7     | Surface treatment processes on planar diodes                   | 96  |

| 4.8     | Conclusions                                                    | 100 |

| 4.9     | Reference                                                      | 101 |

| Chapter | 5 Mesa InAs and planar InAs linear arrays                      | 104 |

| 5.1     | Fabrication of mesa and planar linear arrays                   | 105 |

| 5.2     | Fabrication issues with mesa linear array                      | 108 |

| 5.2     | 2.1 Fabrication issues caused by SU-8                          | 108 |

| 5      | 5.2.2    | Optimised SU-8 passivation                                     | . 112 |

|--------|----------|----------------------------------------------------------------|-------|

| 5.3    | Cor      | mparison of mesa and planar InAs linear array photodiodes      | . 114 |

| 5      | .3.1     | Dark current comparisons                                       | . 114 |

| 5      | .3.2     | Responsivity at 1520 and 2004 nm comparisons                   | . 118 |

| 5.4    | Cor      | nclusions                                                      | .119  |

| 5.5    | Ref      | ferences                                                       | . 121 |

| Chapte | er 6 Lo  | ow light detection with planar InAs avalanche photodiode array | . 122 |

| 6.1    | Ter      | nperature dependence of current-voltage characteristics        | . 123 |

| 6.2    | Cal      | ibration of optical system                                     | . 128 |

| 6.3    | Gai      | in characteristics of APD array                                | . 130 |

| 6.4    | Lov      | w-light level measurements with linear APD array               | . 132 |

| 6.5    | Sm       | all area diodes with isolation trench design                   | . 138 |

| 6.6    | AP       | D array characteristics after thermal cycles                   | . 141 |

| 6.7    | Cor      | nclusion                                                       | . 142 |

| 6.8    | Ref      | ferences                                                       | . 144 |

| Chapt  | er 7 Co  | onclusion                                                      | . 146 |

| 7.1    | Fut      | ure work                                                       | 148   |

| 7      | .1.1     | Experimental work                                              | . 148 |

| 7      | .1.2     | Improvements to mask design                                    | .149  |

| 7      | 1.1.3    | Surface passivation of InAs APDs                               | . 151 |

| 7.2    | Ref      | ference                                                        | . 154 |

| Apper  | ndix A   | : Fabrication of InAs planar linear array                      | . 156 |

| Apper  | ndix B   | : Cleanroom fabrication methods and techniques                 | 161   |

| Cle    | aving a  | and 3 stage cleaning:                                          | . 161 |

| Pho    | otolitho | ography:                                                       | . 161 |

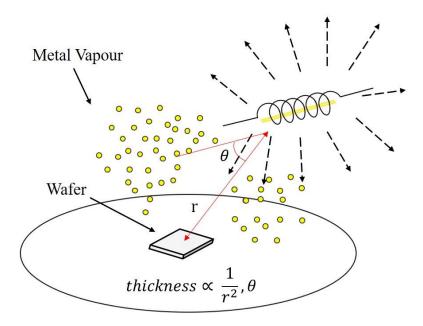

| Met    | tal dep  | osition and liftoff:                                           | . 164 |

| Che    | emical   | wet etching:                                                   | . 166 |

| Passivation:                                                             | 168        |

|--------------------------------------------------------------------------|------------|

| Dielectric deposition:                                                   | 168        |

| Plasma dry etching:                                                      | 170        |

| Packaging and bonding:                                                   | 171        |

| Appendix C: Standard operating procedure for Janis 2 low temperature pro | be station |

|                                                                          | 173        |

| Appendix D: Operating principle of a lock-in amplifier                   | 178        |

| Appendix E: Supplementary Results for Chapter 6                          | 180        |

# **List of Figures**

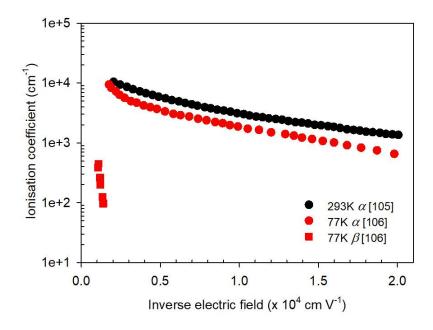

| Figure 1.1 Electron and hole ionisation coefficients of InAs at 293 [105] and 77 K        |

|-------------------------------------------------------------------------------------------|

| [106]                                                                                     |

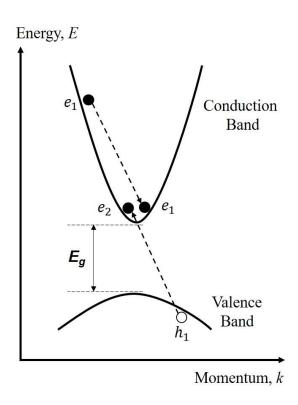

| Figure 2.1 E-k diagram of an impact ionisation initiated by an electron                   |

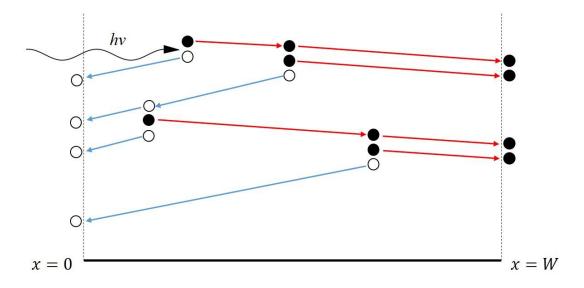

| Figure 2.2 Schematic diagram of a chain of impact ionisation events with initial          |

| carriers generated via absorption of a photon                                             |

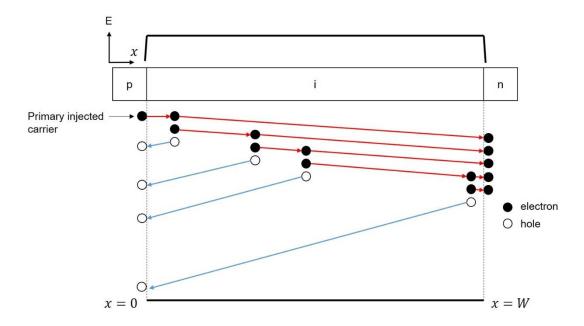

| Figure 2.3 An impact ionisation chain with pure electron injection and $\beta = 0$ 44     |

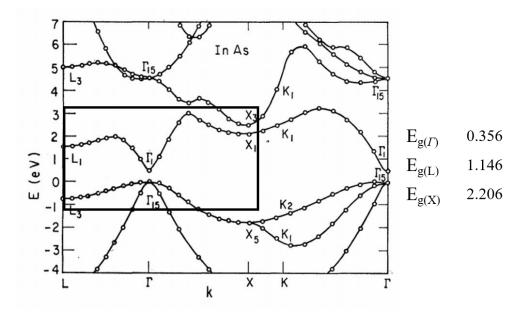

| Figure 2.4 The band structure of InAs [3] and valley separation energy with respect to    |

| the valence band maxima obtained from [4]45                                               |

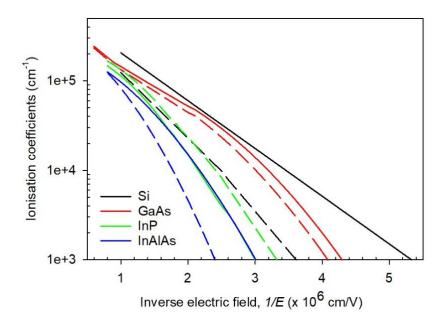

| Figure 2.5 Impact ionisation coefficients of key materials. Solid and dashed lines        |

| represent the electron and hole ionisation coefficients respectively                      |

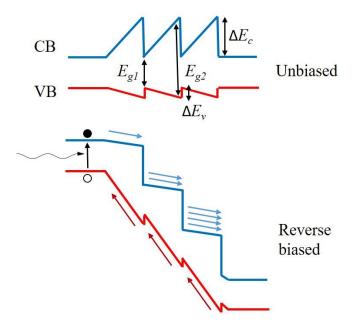

| Figure 2.6 The band diagram of the staircase APD concept under zero and reverse bias      |

| conditions                                                                                |

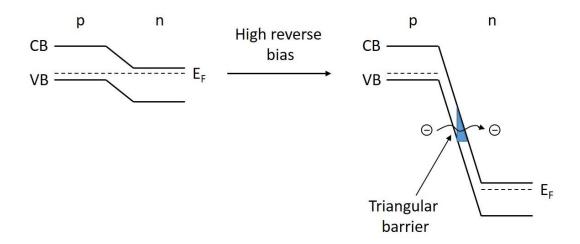

| Figure 3.1 Tunnelling in p-n junction with a triangular barrier under high reverse bias   |

| 67                                                                                        |

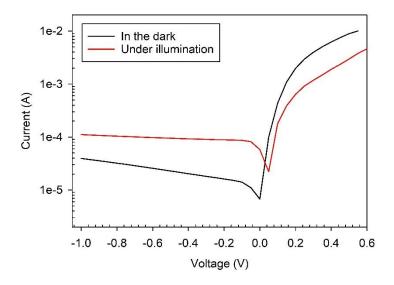

| Figure 3.2 Current-voltage characteristics of a photodiode in dark and illuminated        |

| conditions                                                                                |

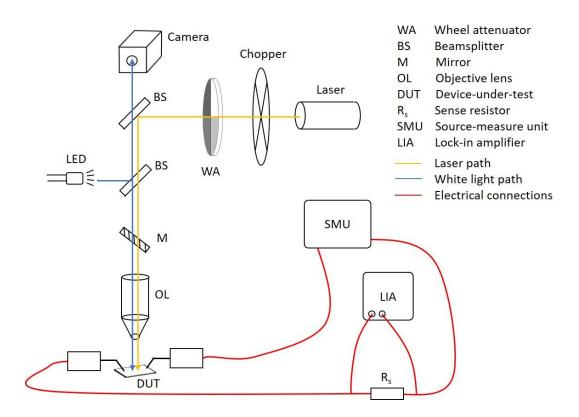

| Figure 3.3 Experimental setup for gain and responsivity measurements                      |

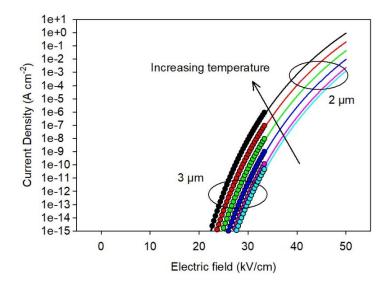

| Figure 3.4 Tunnelling current as a function of temperature from 300 to 77 K76             |

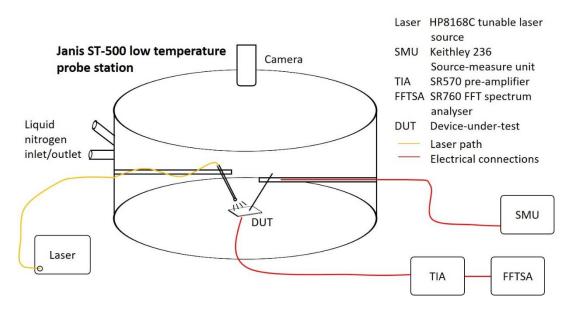

| Figure 3.5 Experimental setup using a liquid nitrogen cooled Janis probe station for      |

| temperature dependence and low signal measurements                                        |

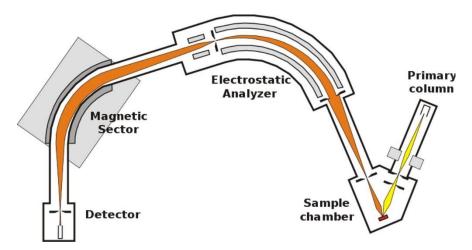

| Figure 3.6 Typical components in a SIMS instrument [12]. The primary ion path is          |

| denoted by the yellow areas while the path in orange represents the trajectory of         |

| secondary sputtered ions. The ions of interest of a specific charge and mass are isolated |

| before the detector by an applied electric field and magnetic field                       |

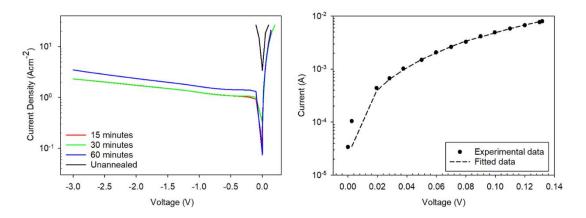

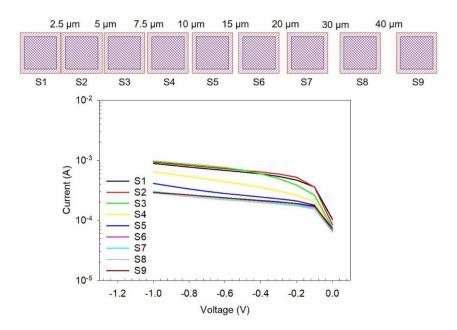

| Figure 4.1 Current density-voltage characteristics at room temperature of samples         |

| annealed at 500°C for different durations of 15, 30, 60 minutes and a control             |

| unannealed sample. (left) Forward current-voltage fitting to ideal Shockley diode         |

| equation of a 220 $\mu m$ diameter device from the 500°C, 15 minutes annealed sample.     |

| An ideality factor 1.14 and a series resistance of 6.3 $\Omega$ is obtained. (right)      |

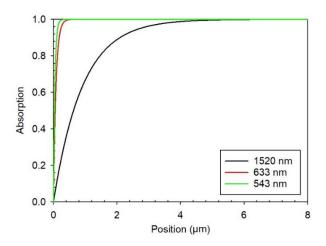

| Figure 4.2 Absorption profile of different wavelengths of light on InAs                   |

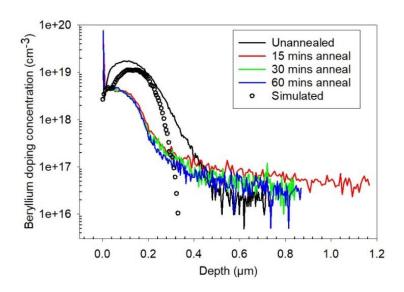

| Figure 4.3 Beryllium dopant concentration vs. depth of samples annealed for different     |

| durations. The simulation results using a 34 keV Be-ion energy is included 88             |

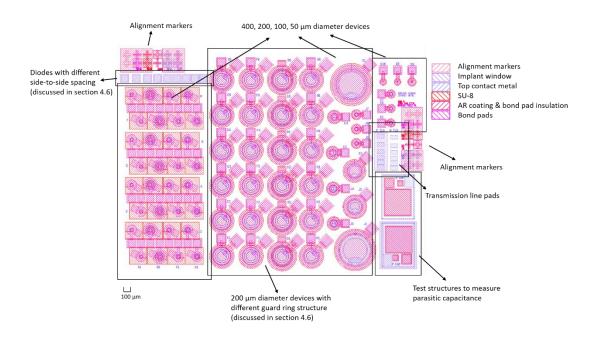

| Figure 4.4 Mask set used to produce planar InAs diodes with device sizes of 400, 200       |

|--------------------------------------------------------------------------------------------|

| and 100 μm diameter89                                                                      |

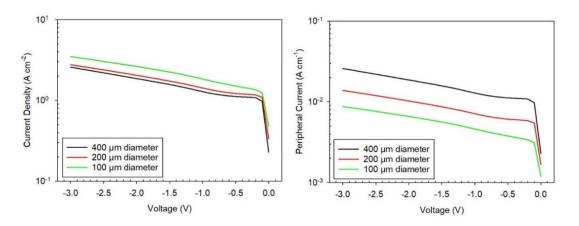

| Figure 4.5 Current density (left) and peripheral current (right) versus voltage for planar |

| InAs diodes of different sizes at room temperature                                         |

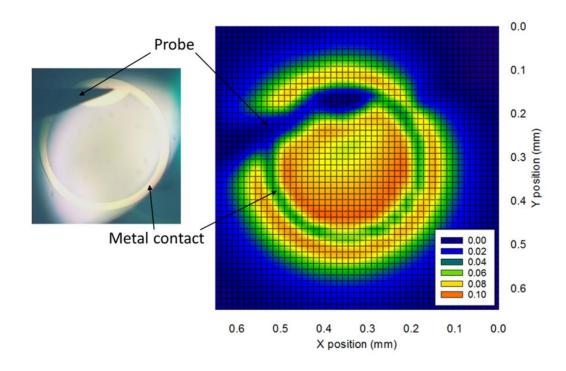

| Figure 4.6 Spatial variation of responsivity at -0.1 V at room temperature using an        |

| illumination wavelength of 633 nm on a 400 μm diameter diode91                             |

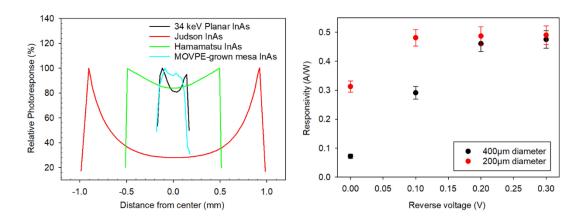

| Figure 4.7 Comparison of normalised spatial variation in photoresponse across the          |

| optical window of commercial, in-house mesa and planar (this work) InAs                    |

| photodiodes. (left) Responsivity at 1520 nm as a function of reverse bias with             |

| increments of 0.1 V. Error bars displayed are the standard deviation of the experiment.    |

| (right)                                                                                    |

| Figure 4.8 Variation in separation distance and the current-voltage characteristics at     |

| room temperature of a series of 9 adjacent diodes. Schematic of the array is shown and     |

| the dimensions for the square diode are 100 μm by 100 μm93                                 |

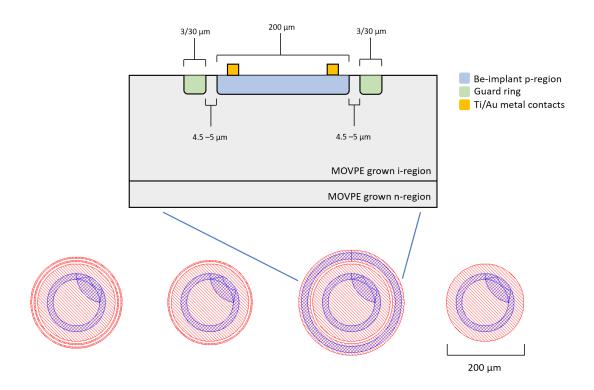

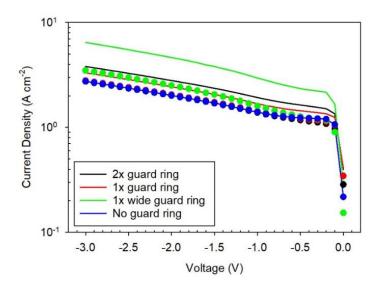

| Figure 4.9 200 µm diameter diodes with different guard ring designs and a cross            |

| sectional drawing of one of the 200 µm diameter diodes with wide guard rings 95            |

| Figure 4.10 Dark current density of 200 µm diameter diodes at room temperature with        |

| uncorrected (solid lines) and corrected (circles) areas                                    |

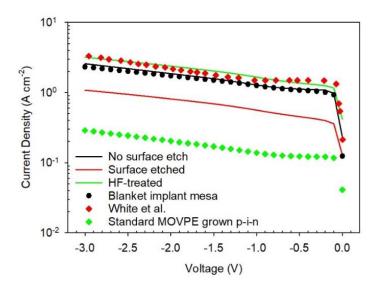

| Figure 4.11 Comparison of dark current densities at room temperature of InAs planar        |

| diodes with and without surface treatment. Results from previous planar InAs APDs          |

| by White et al. and standard MOVPE grown mesa InAs APDs as reference are                   |

| included97                                                                                 |

| Figure 4.12 Current-voltage characteristics at room temperature of 400 μm diameter         |

| diodes from samples with different surface etch depths with an unetched sample as          |

| reference 98                                                                               |

| Figure 5.1 Mask set for mesa (a) and planar (b) linear array as well as schematic (c) of   |

| two adjacent diodes from planar linear array mask                                          |

| Figure 5.2 Uniform high aspect ratio (roughly 1300 nm: 70 nm) features can be              |

| obtained easily with SU-8 2 on flat wafers                                                 |

| Figure 5.3 SU-8 2 tends to form tall bumps of varying heights around mesa boundaries.      |

| (left) SU-8 2 forms an uneven coating of tall features on mesa top and trenches at the     |

| base of mesa. (right)                                                                      |

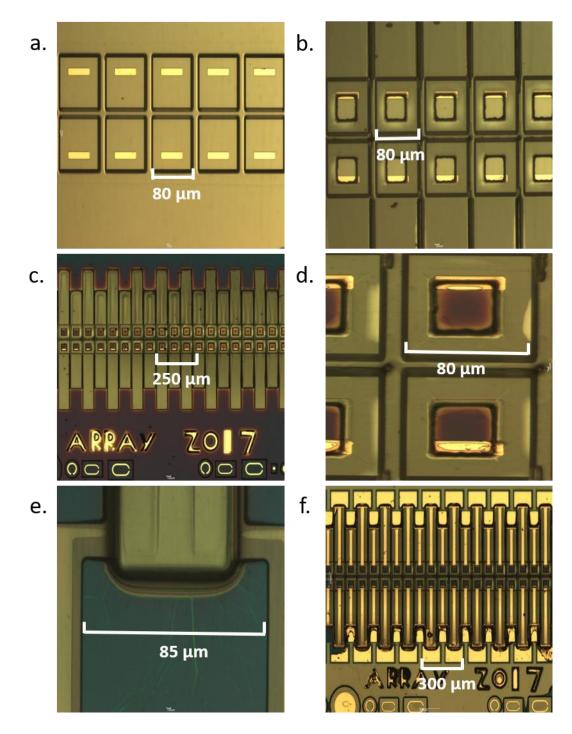

| Figure 5.4 Micrographs of MLA sample at various processing stages. (a) Formation of        |

| individual devices post wet etching. (b) Application of SU-8 by spin coating. (c)          |

| $200\ nm$ of $SiN_x$ deposition by PECVD. (d) Removal of dielectric on the contact metals  |

|--------------------------------------------------------------------------------------------|

| by reactive ion etching (RIE). (e) Alignment of photoresist prior to bond pad              |

| deposition. (f) Final step of bond pad deposition and liftoff                              |

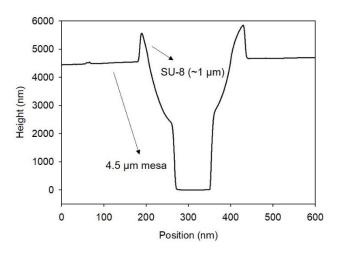

| Figure 5.5 Profilometer scan on a NEWPIN device after improved SU-8 passivation            |

| procedures                                                                                 |

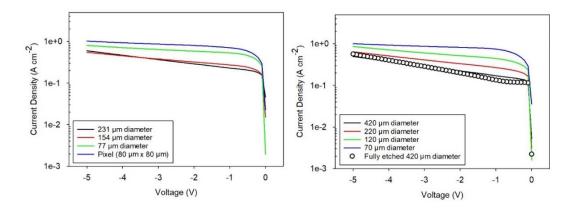

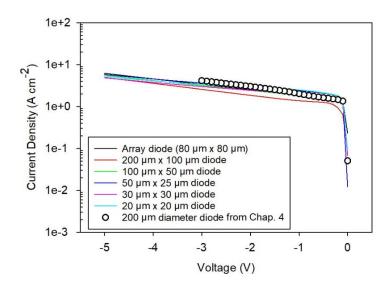

| Figure 5.6 Dark current densities of devices fabricated from MLA (left) and NEWPIN         |

| (right) mask                                                                               |

| Figure 5.7 Dark current density versus voltage plots for MLA (left) and PLA (right)        |

| devices                                                                                    |

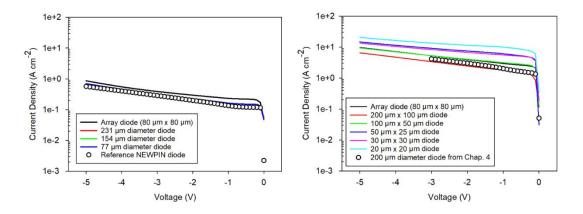

| Figure 5.8 Area-corrected (added 10 µm to each side) dark current density plots for        |

| PLA devices                                                                                |

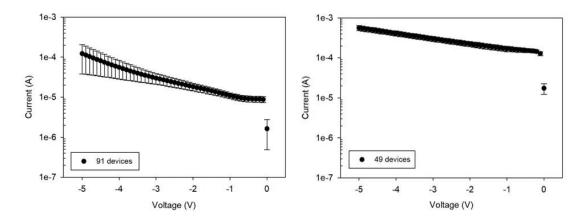

| Figure 5.9 Average dark current versus voltage plot for MLA (left) and PLA (right)         |

| devices. The standard deviation is presented as the error bars                             |

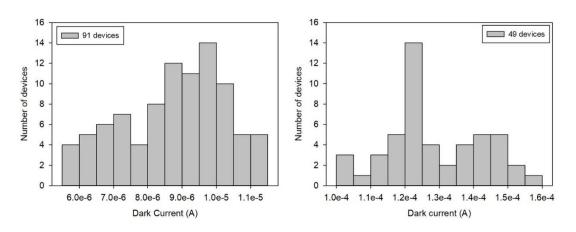

| Figure 5.10 The distribution of dark current at -0.1 V for the MLA (left) and PLA          |

| (right) sample                                                                             |

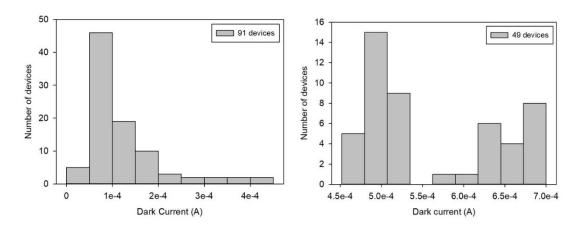

| Figure 5.11 The distribution of dark current at -5 V for the MLA (left) and PLA (right)    |

| sample                                                                                     |

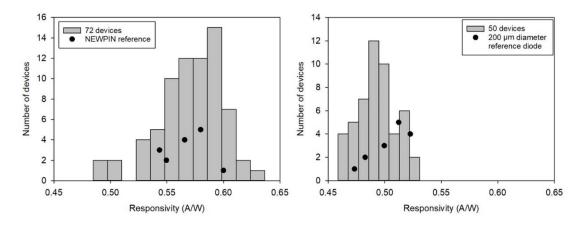

| Figure 5.12 Responsivity at -0.1 V with 1520 nm incident light for MLA (left) and          |

| PLA sample (right)                                                                         |

| Figure 5.13 Responsivity at -0.1 V with 2004 nm incident light for MLA (left) and          |

| PLA sample (right)                                                                         |

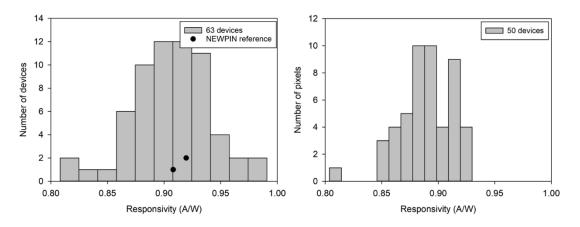

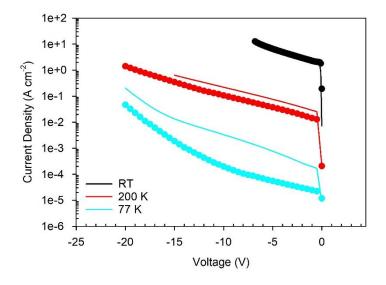

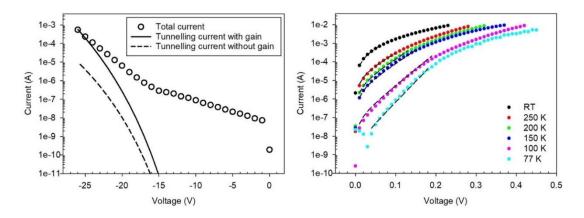

| Figure 6.1 Temperature dependence of dark current characteristics from room                |

| temperature to 77 K (left). Arrhenius plot of dark current at -0.5 V (right)               |

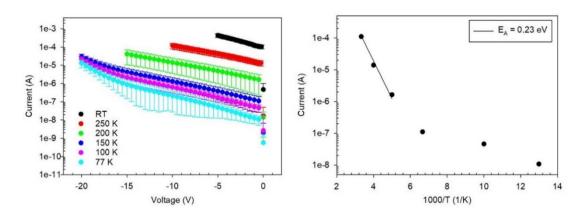

| Figure 6.2 Current density comparison between 80 by 80 $\mu m$ (solid lines) and 30 by     |

| $30\ \mu m$ (symbols). The different colours indicate the various temperature points $125$ |

| Figure 6.3 Fitting of the reverse dark current at high reverse biases to the band-to-band  |

| tunneling current in a p-i-n diode (left). Forward I-V as a function of temperature.       |

| Dashed lines show the region fitting to extract ideality factor. (right)                   |

| Figure 6.4 The fitted device temperature vs. cryostat temperature obtained from the        |

| temperature controller                                                                     |

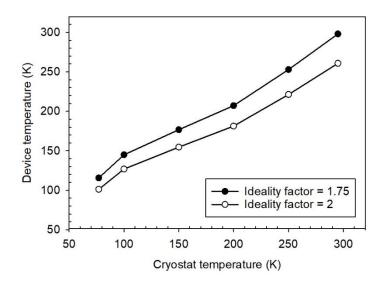

| Figure 6.5 The laser output power settings and its corresponding actual optical power      |

| exiting the fibre in the Janis probe station chamber                                       |

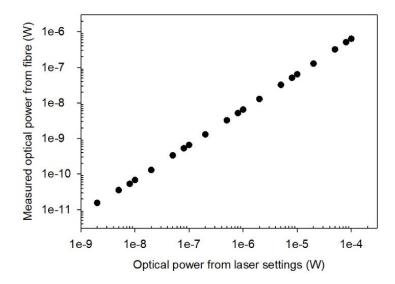

| Figure 6.6 The measured (left) gain at temperatures of 295, 200 and 77 K and the           |

| modelled gain at 295 and 77 K (right) using McIntyre's equation                            |

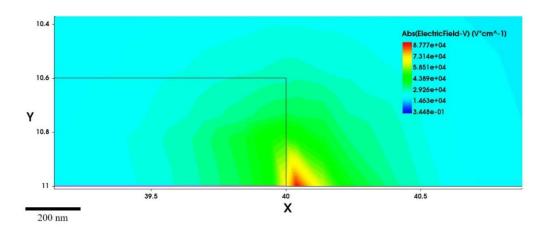

| Figure 6.7 Simulation of a planar InAs APD with an implant depth of 400 nm at a                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------|

| voltage bias of -10 V                                                                                                                 |

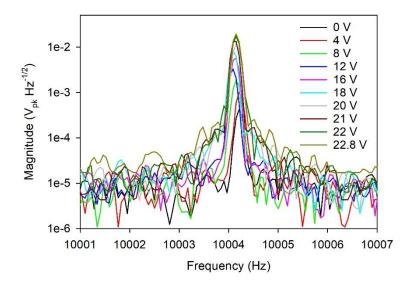

| Figure 6.8 The frequency response spectra at varying voltage biases at a fixed laser                                                  |

| injection power                                                                                                                       |

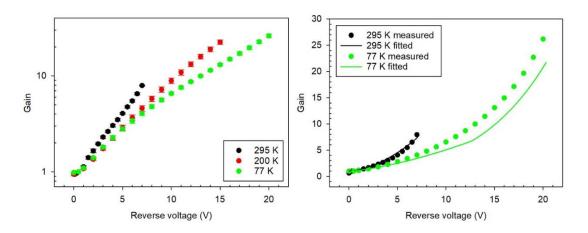

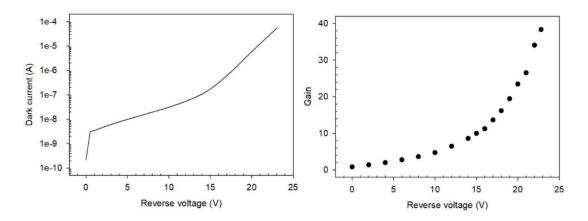

| Figure 6.9 Typical dark current (left) and gain (right) characteristics at 77 K of APDs                                               |

| tested                                                                                                                                |

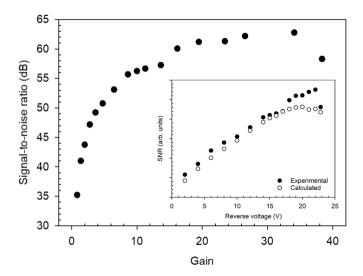

| Figure 6.10 The signal-to-noise ratio as a function of APD gain. The inset shows the                                                  |

| comparison between the SNR derived from spectrum analyser measurements and                                                            |

| calculated from equation 2.8, using the photocurrent, gain, dark current data presented in the previous sections and assuming $F = 2$ |

|                                                                                                                                       |

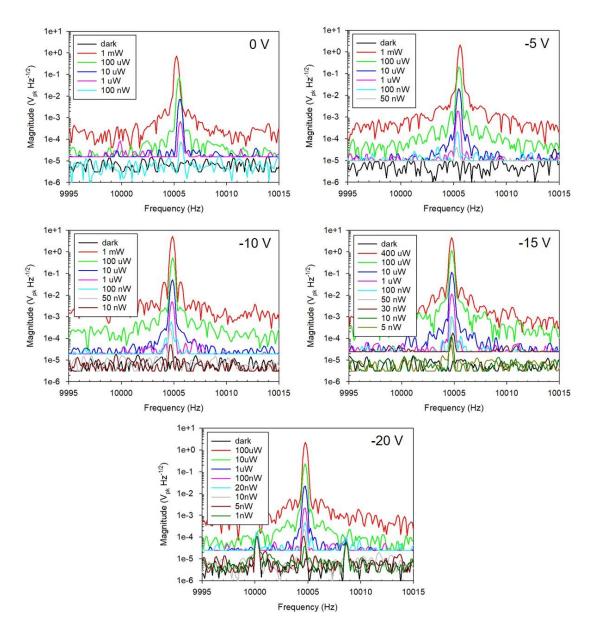

| Figure 6.11 The signal spectra at varying optical power level (as noted from the laser                                                |

| settings) with the operating voltage bias denoted at the top right corner of each plot                                                |

|                                                                                                                                       |

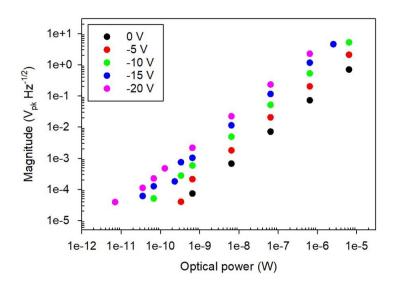

| Figure 6.12 The linearity of response to light at varying voltage bias                                                                |

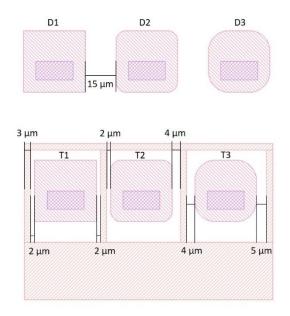

| Figure 6.13 Mini array of 3 small area diodes of 30 μm 30 μm with 15 μm spacing                                                       |

| (top). Detailed diode to trench spacing on mini array with isolation trench incorporated                                              |

| (bottom)                                                                                                                              |

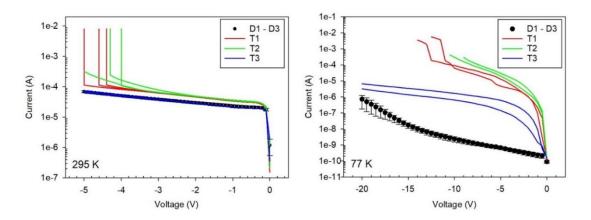

| Figure 6.14 Reverse current-voltage characteristics at room temperature (left) and                                                    |

| 77 K (right) of diodes from mini array with (D) and without (T) isolation trench 140                                                  |

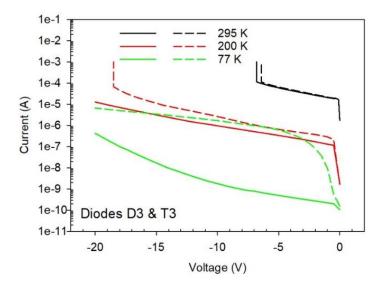

| Figure 6.15 Temperature dependence of current-voltage characteristics of selected D3                                                  |

| and T3 diodes                                                                                                                         |

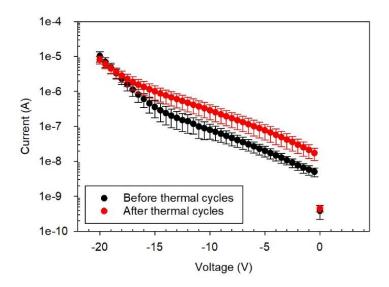

| Figure 6.16 Comparison of reverse current-voltage characteristics at 77 K before and                                                  |

| after multiple thermal cycles142                                                                                                      |

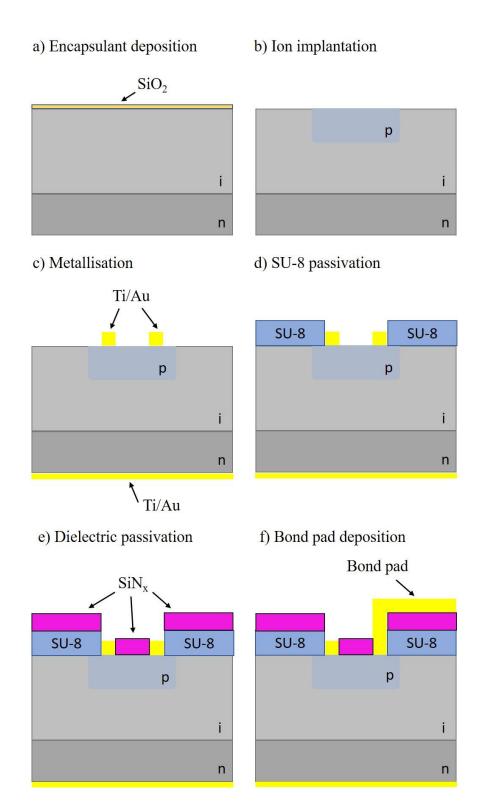

| Figure A.1 Schematic diagrams for several key steps in the fabrication of planar InAs                                                 |

| linear array diodes160                                                                                                                |

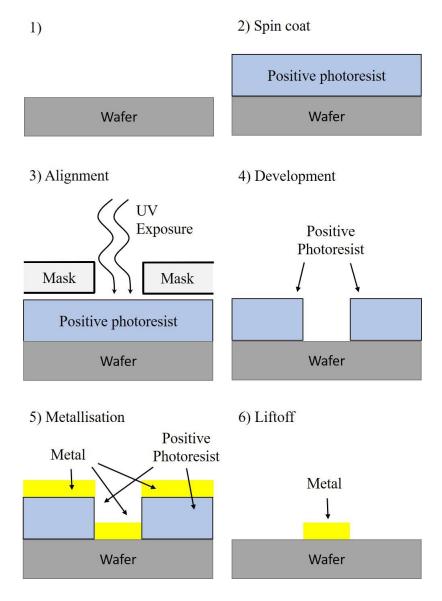

| Figure B.1 A standard photolithography procedure from spin coating to metal liftoff                                                   |

| on a wafer sample162                                                                                                                  |

| Figure B.2 A schematic diagram for a metal evaporation process                                                                        |

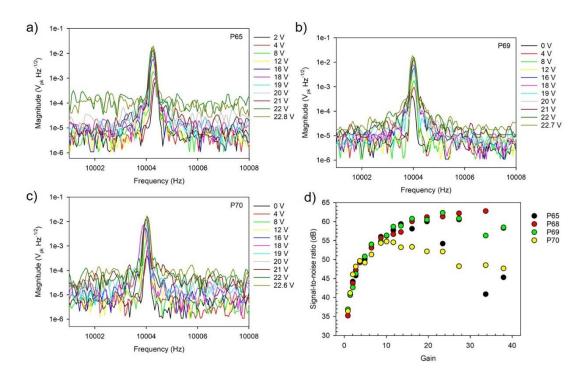

| Figure E.1 (a) – (c) Spectrum analyser plots with a fixed incident optical power at                                                   |

| varying voltage biases. (d) SNR vs gain plot where P68 is the data presented in chapter                                               |

| 6                                                                                                                                     |

## **List of Tables**

| Table 4-I Responsivity and external quantum efficiency of diodes from samples of      |

|---------------------------------------------------------------------------------------|

| different annealing duration                                                          |

| Table 4-II Corrected diameters (addition of guard rings) of 200 μm diameter diodes    |

| 95                                                                                    |

| Table 4-III A summary of etch durations in phosphoric acid mixture and sulphuric acid |

| mixture, the corresponding etch depth calculated from estimated etch rates and the    |

| responsivity at 0.2 V with 1520 nm wavelength light                                   |

| Table 5-I Details of linear array samples                                             |

| Table 5-II Comparison of old and improved SU-8 procedures                             |

| Table 6-I Comparison of dark current density of planar diodes at 0.5 V at different   |

| temperatures                                                                          |

| Table 6-II Details of mini arrays                                                     |

## Glossary - List of Abbreviations

ADAS Advanced driver assistance systems

APD Avalanche photodiode

BCB B-staged benzocyclobutene

BER Bit error rate

C-V Capacitance-voltage

DFT Discrete Fourier transform

DIAL Differential absorption LiDAR

DIW De-ionised water

DUT Device-under-test

e-APD Electron avalanche photodiode

EHP Electron-hole pair

FFT Fast Fourier transform

GBP Gain-bandwidth product

G-R Generation-recombination

HDVIP High-density vertically integrated photodiode

HF Hydrofluoric acid

I2E Impact ionisation engineering

ICP Inductively coupled plasma

ICPCVD Inductively coupled plasma chemical vapour deposition

I-V Current-voltage

LED Light-emitting diode

LIA Lock-in amplifier

LiDAR Light detection and ranging

LPE Liquid phase epitaxy

LWIR Long-wave infrared

MBE Molecular beam epitaxy

MCT Mercury cadmium telluride

MEMS Micro-electro-mechanical systems

MLA Mesa linear array

MOVPE Metalorganic vapour phase epitaxy

MPE Maximum permissible exposure

MWIR Mid-wave infrared

NFM Noise figure meter

NIR Near infrared

PECVD Plasma-enhanced chemical vapour deposition

PLA Planar linear array

RIE Reactive ion etching

RTA Rapid thermal annealing

SAGCM Separate absorption, grading, charge and multiplication

SAM-APD Separate absorption and multiplication avalanche photodiode

SCM Single carrier multiplication

SiPM Silicon photomultiplier

SIMS Secondary ion mass spectroscopy

SMU Source-measure unit SNR Signal-to-noise ratio

SPAD Single photon avalanche diode

SRH Shockley-Read-Hall

SWIR Short-wave infrared

TLM Transmission line measurement

ToF Time of flight

TRIM Transport of Ions in Matter

VCSEL Vertical cavity surface emitting laser

VLWIR Very long-wave infrared

# Glossary – List of Symbols

| $\boldsymbol{A}$            | Area of device/receiver                       |

|-----------------------------|-----------------------------------------------|

| A                           | Pre-exponential factor of Arrhenius equation  |

| α                           | Electron impact ionisation coefficient        |

| β                           | Hole impact ionisation coefficient            |

| $c_0$                       | Speed of light                                |

| $C_d$                       | Junction capacitance per unit area            |

| CMOS                        | Complementary metal-oxide-semiconductor       |

| $d_{p,n}$                   | Depletion width in p- and n-type material     |

| $D_{p,n}$                   | Diffusion constant of minority electron/hole  |

| $\Delta_{SO}$               | Spin-orbit split-off energy                   |

| $\Delta f$                  | Bandwidth                                     |

| $\Delta t$                  | lag/return time of returning laser pulse      |

| $E_A$                       | Activation energy                             |

| $E_g$                       | Band gap energy                               |

| $E_{th(e,h)}$               | Ionisation threshold energy for electron/hole |

| $\varepsilon_0$             | Vacuum permittivity                           |

| $\varepsilon_r$             | Relative permittivity of material             |

| $\mathcal{E}_{\mathcal{S}}$ | Material permittivity                         |

| ξ                           | Electric field                                |

| F(M)                        | Excess noise factor                           |

| G                           | Multiplication of a particular trial          |

| γ                           | Tunnelling parameter                          |

| h                           | Planck's constant                             |

| ħ                           | Reduced Planck's constant                     |

| $I_d$                       | Dark current                                  |

| $i_n^2$                     | Diode shot noise                              |

| $I_{ph}$                    | Photocurrent                                  |

| $I_{pri}$                   | Primary photocurrent                          |

| $i_{th}$                    | Thermal noise of amplifier                    |

| J                           | Current density                               |

Saturation current density  $J_0$  $J_{bulk}$ Bulk contribution dark current Current density due to Shockley-Read-Hall  $J_{SRH}$ Surface contribution dark current  $J_{surf}$ Current density due to tunnelling  $J_{tunn}$ k Ratio of hole to electron ionisation coefficient  $k_b$ Boltzmann's constant  $L_{p,n}$ Minority carrier diffusion length of minority electron/hole λ Wavelength  $\lambda_{off}$ Off-line wavelength  $\lambda_{on}$ On-line wavelength  $\lambda_{peak}$ Peak wavelength of blackbody source  $\ell$ Range to target gas species Μ Multiplication factor  $M_e$ Electron-initiated multiplication M(0)Pure electron injected multiplication M(x)Average total number of electrons and holes M(W)Pure hole injected multiplication  $m^*$ Effective carrier mass Ideality factor n  $N_{A.D}$ Acceptor/hole doping concentration  $N_B$ Background doping concentration  $n_i$ Intrinsic carrier concentration η Quantum efficiency External quantum efficiency  $\eta_{ext}$ Optical system efficiency  $\eta_{sys}$  $P_0$ Transmitted power from laser  $P_{opt}$ Incident optical power  $P_{rec}(\ell)$ Received signal power as a function of range Radius of device r R Responsivity  $R_{eq}$ Equivalent resistance at amplifier input

Theoretical maximum responsivity  $R_{ideal}$ Measured responsivity  $R_{meas}$  $R_s$ Series resistance Elementary charge q Carrier lifetime τ Atmospheric backscattering coefficient φ Т Temperature TLM Transmission line measurement Applied bias voltage  $V_{bias}$  $V_{bi}$ Built-in voltage  $V_r$ Reverse bias voltage Frequency of light ν

Depletion width

Extinction coefficient

W

χ

## Acknowledgments

I wish to express my heartfelt gratitude to Prof. Chee Hing Tan, Prof. Jo Shien Ng and Prof. John David for their teachings and mentorship throughout my Ph.D journey.

I wish to also thank members of the group, past and present, whom I am grateful to have known, specially Dr. Xin Yi, Yuchen Liu, Yuting Ji, Xiao Jin, Dr. Benjamin White, Dr. Jonathan Petticrew, Elizabeth Stark, Dr. Vladimir Shulyak, Dr. Simon Dimler, Dr. Yasaman Alimi, Jonathan Taylor-Mew, Tarick Osman, Dr. Robert Richards, Nicholas Bailey, Nada Adham, Mohammad Riduwan, Aina Baharuddin, Dr. Faezah Harun, Dr. Matthew Hobbs, Dr. Xinxin Zhou, Dr. Xiao Meng, Dr. Jeng Shuih Cheong, and Dr. Shiyu Xie.

I would also like to thank colleagues from the Nanoscience cleanroom specially Dr. Kean Boon Lee, Dr. Cai Yuefei, the technical staffs and Gordon.

A big thank you to my friends in Sheffield, Tee, Ara and Andy, without whom I cannot imagine. I want to thank my family for their support during these number of years I am away from home. Finally, I wish to thank my girlfriend for her unwavering love that got me through many difficult times over the years.

#### **Abstract**

Avalanche photodiodes (APDs) are used in photon-starved applications for their ability to amplify low levels of incoming signals. A special class of APDs, known as electron APDs (e-APDs), can significantly improve the signal-to-noise ratio of an optical receiver system due to single carrier multiplication and the lack of hole feedback. InAs is one of such material with a band gap of 0.36 eV which makes InAs an attractive material of choice for low photon, infrared applications such as LiDAR and active imaging. Conventional mesa structure InAs APDs face many problems such as lateral side etching and the need for sidewall passivation. Planar topology InAs APDs previously developed using a high energy ion implantation scheme have shown performance comparable to the mesa structure APDs.

In this thesis, planar InAs APDs with a shallow implant depth of 100 nm are investigated. Long duration anneals have been employed to promote dopant diffusion to form the p-type region. The dark current and responsivity of the planar APDs show improvement over as processed samples following a shallow surface etch, indicating the removal of surface damage induced by ion implantation.

Linear arrays of mesa and planar InAs APDs are fabricated and the array uniformity is evaluated to show that superior homogeneity of diode performance, from current-voltage and responsivity measurements, in the planar linear array. The challenges faced during semiconductor processing of mesa linear arrays are detailed and discussed to illustrate low device yield in mesa linear arrays.

Finally, the planar linear array is characterised in detail at the temperature range of 300-77 K. Good uniformity in dark current and gain characteristics are demonstrated at the temperatures measured. At 77 K, the signal-to-noise ratio increases with bias voltage (and gain) with a maximum of 62.8 dB at -22 V before the diode shot noise dominates. Current-voltage characteristics of the diode array before and after multiple thermal cycles show minimal degradation, highlighting the robustness of the fabricated planar array.

### **List of Publications**

#### **Journal Papers**

- **L. W. Lim**, P. Patil, I. P. Marko, E. Clark, S. J. Sweeney, J. S. Ng, J. P. R. David, and C. H. Tan, "Electrical and optical characterisation of low temperature grown InGaAs for photodiode applications", *Semicond. Sci. Technol.*, vol. 35, no. 9, 095031, 2020.

- X. Yi, S. Xie, B. Liang, **L. W. Lim**, J. S. Cheong, M. C. Debnath, D. L. Huffaker, C. H. Tan, and J. P. R. David, "Extremely low excess noise and high sensitivity AlAs0.56Sb0.44 avalanche photodiodes", *Nat. Photonics*, vol. 13, pp. 683-686, 2019.

- **L. W. Lim**, C. H. Tan, J. S. Ng, J. D. Petticrew, and A. B. Krysa, "Improved Planar InAs Avalanche Photodiodes With Reduced Dark Current and Increased Responsivity", *J. Lightw. Technol.*, vol. 37, no. 10, pp. 2375-2379, 2019.

- C. H. Tan, A. Velichko, **L. W. Lim**, and J. S. Ng, "Few-photon detection using InAs avalanche photodiodes", *Opt. Express*, vol. 27, no. 4, pp. 5835-5842, 2019.

- X. Yi, S. Xie, B. Liang, **L. W. Lim**, X. Zhou, M. C. Debnath, D. L. Huffaker, C. H. Tan, and J. P. R. David, "Demonstration of large ionization coefficient ratio in AlAs0.56Sb0.44 lattice matched to InP", *Sci Rep*, vol. 8, pp. 9107, 2018.

#### **Conference**

- X. Yi, S. Xie, B. L. Liang, **L. W. Lim**, D. L. Huffaker, C. H. Tan, and J. P. R. David, "Extremely low-noise avalanche photodiodes based on AlAs<sub>0.56</sub>Sb<sub>0.44</sub>", *SPIE Security* + *Defence 2020*, Edinburgh, UK, Sept 2020.

- X. Yi, S. Xie, B. L. Liang, **L. W. Lim**, D. L. Huffaker, C. H. Tan, and J. P. R. David, "High performance AlAs<sub>0.56</sub>Sb<sub>0.44</sub> avalanche photodiodes", *SPIE Photonics West* 2020, San Francisco, California, United States, Feb 2020.

- S. Xie, X. Yi, B. L. Liang, **L. W. Lim**, D. L. Huffaker, C. H. Tan, and J. P. R. David, "High speed and high sensitivity AlAs<sub>0.56</sub>Sb<sub>0.44</sub> avalanche photodiodes", *Asia Communication Photonics*, Chengdu, China, Nov 2019.

- L. W. Lim, M. Kesaria, I. P. Marko, P. Patil, E. Clarke, S. J. Sweeney, J. P. R. David, and C. H. Tan, "Optical and electrical performance of low temperature MBE-grown

- InGaAs and InGaAsBi photodetectors", 10th International Workshop on Bismuth-Containing Semiconductors, Toulouse, France, Jul 2019.

- D. L. Huffaker, S. Xie, X. Yi, B. L. Liang, **L. W. Lim**, C. H. Tan, and J. P. R. David, "Large ionisation coefficient ratio in AlAs<sub>0.56</sub>Sb<sub>0.44</sub> avalanche photodiodes", *Compound Semiconductor Week 2019*, Kasugano International Forum, Nara, Japan, May 2019.

- **L. W. Lim**, J. D. Petticrew, A. B. Krysa, J. S. Ng, and C. H. Tan, "Investigation of low energy Be implantation and annealing conditions in InAs avalanche photodiodes", *44th Freiburg Infrared Colloquium*, Freiburg, Germany, Mar 2019.

- X. Yi, S. Xie, B. L. Liang, **L. W. Lim**, X. Zhou, M. C. Debnath, D. L. Huffaker, C. H. Tan, and J. P. R. David, "Avalanche multiplication in AlAs<sub>0.56</sub>Sb<sub>0.44</sub>", *Asia Communications and Photonics Conference*, Hangzhou, China, Oct 2018.

- S. Xie, X. Yi, B. L. Liang, **L. W. Lim**, X. Zhou, M. C. Debnath, C. H. Tan, J. P. R. David, and D. L. Huffaker, "Breakdown voltages in AlAs<sub>0.56</sub>Sb<sub>0.44</sub> avalanche photodiodes", *UK Semiconductors*, Sheffield, UK, Jul 2018.

- **L. W. Lim**, J. D. Petticrew, A. B. Krysa, and C. H. Tan, "Investigation of low energy Be implantation in InAs photodiodes", *UK Semiconductor*, Sheffield, UK, Jul 2017.

- V. Shulyak, **L. W. Lim**, C. H. Tan, and J. S. Ng, "Sensitivity of High-Speed Optical Receivers with InAs Avalanche Photodiodes", *UK Semiconductor*, Sheffield, UK, Jul 2017.

## **Chapter 1 Introduction**

#### 1.1 Light detection and ranging (LiDAR)

Light detection and ranging is a metrological technique for distance measurement by illuminating a target or scene with laser light and detecting the reflected signal. LiDAR is particularly useful as a non-destructive tool to form 3-D environmental maps in geological or archaeological sites [1], [2], monitoring of foliage growth for crop maintenance and harvesting in agriculture [3] and atmospheric observations for metrological and climate research purposes [4], to name a few. With the advent of lasers, ranging experiments such as the measurement of the Earth-Moon distance has been conducted (ongoing to improve accuracies down to sub-millimetre resolution) by measuring the time taken for laser light from the Earth surface to arrive at and reflect from the Moon's surface [5]. The same method has also been used to profile the surface topography of the Moon [6].

#### 1.1.1 Atmospheric LiDAR

LiDAR systems used for remote atmospheric measurements can be influenced by aerosol particles, dust, water vapour, various gas molecules [7]. Interactions between laser light and atmospheric constituents can involve absorption [8] as well as elastic [9] and inelastic [10] scattering, leading to several LiDAR techniques that are effective for different applications. The first published use of LiDAR was for the purpose of measuring the height of clouds in 1946 [11]. Beginnings of the modern LiDAR technique started shortly after the invention of the ruby laser in 1960 [12] and subsequently used in atmospheric studies by Fiocco *et al.* in 1963 [13]. Since then, LiDAR systems and instrumentation has developed rapidly to cope with requirements to make the technique more accurate and sensitive.

With increasing concerns mounting over rising global temperatures and climate changes, the detection and monitoring of greenhouse gases and atmospheric pollutants are vital. LiDAR system development in observatories and satellites around the globe are used to measure, observe, and predict changes in the atmosphere. For example, NASA's continual involvement in the field of remote sensing has led to the development of the G-LiHT airborne imager [14]. The European space program, MERLIN, is a joint collaboration between France and Germany for atmospheric

methane monitoring [15]. Several ground-based observatories such as the ALOMAR in Norway [16], SIRTA site in Paris [17] and HALO in California [18] are used for taking vast LiDAR measurements of the atmosphere. The detection of toxic atmospheric gases such as CO<sub>2</sub>, CH<sub>4</sub>, and NO<sub>x</sub> has been long studied via optical means [19]. The molecular structure of a gas molecule gives rise to unique absorption characteristics at specific infrared wavelengths (or frequencies). This is due to the absorption of photons at these resonant frequencies that causes vibrational or rotational transitions in the molecules [20]. This leads to a characteristic infrared signature for different gas species which forms the basis of infrared absorption spectroscopy.

In LiDAR measurements, these known vibrational modes of different molecules are exploited by using laser light of specific wavelengths to interact with the gas of interest following the subsequent measurement to characteristic changes to the transmitted laser light. This has been well studied with many published works in the detection of trace concentration of gases in the atmosphere such as  $O_3$  at <3 µm [21], [22], CH<sub>4</sub> at 1.6 [23], [24] and 3.4 µm [25], CO<sub>2</sub> at 2 µm [26], [27] and 4.8 µm [28], N<sub>2</sub>O [29] and H<sub>2</sub>O [30]. The most commonly employed LiDAR technique for trace gas sensing is different absorption LiDAR (DIAL). The DIAL technique works by emitting two different wavelengths, one that is on the absorption line ( $\lambda_{on}$ ) of the target gas species and another away from the absorption line ( $\lambda_{off}$ ) as a reference signal. Both backscattered signals are collected at the receiver and the difference in power due to absorption gives a measure of the gas concentration [7]. The backscattered signal for a LiDAR system is governed by the following equation [31].

$$P_{rec}(\ell) = P_0 \eta_{sys} \frac{A}{\ell^2} \frac{c_0 \Delta t}{2} \varphi(\ell) \exp\left[\int_0^\ell -2\chi(l)dl\right]$$

(1.1)

where  $P_{rec}(\ell)$  is the received signal power as a function of range,  $P_0$  is the transmitted power from laser,  $\eta$  is the optical system efficiency, A is the area of the receiver,  $\ell$  is the range to the target gas species,  $c_0$  is the speed of light in air,  $\Delta t$  is the return time of the received laser pulse,  $\varphi$  and  $\chi$  is the atmospheric backscattering and extinction coefficient. The equation assumes only a single scattering element is present in the atmosphere, however in reality, there can be a number of trace gases as well as particles of various sizes present in the atmosphere, complicating the gas sensing analysis by DIAL.

Another widely used LiDAR technique for remote gas sensing applications is Raman LiDAR [32] which relies on the shift in frequency of laser light upon scattering inelastically (also known as Raman scattering) with the target gas. From a molecular point of view, light scattering occurs when photons of a particular excitation energy are absorbed and re-emitted. When the final energy level of the molecule is the same as the initial level and by extension, the re-emitted photon has the same energy as the incident photon (wavelength of light remains the same) but a different propagation direction, the scattering is considered elastic. Inelastic scattering occurs when the final state of the molecule is changed from the initial state. If the final molecular state is at a higher energy level, some of the photon energy is absorbed and the re-emitted photon will be of a lower energy, corresponding to a longer wavelength [33]. Again, the Raman phenomenon is specific to gas species therefore characteristic Raman spectra exist for different gas molecules. In comparison to the DIAL technique, Raman LiDAR signals are considerably weaker (for example water vapour Raman signals are four orders magnitude lower than backscattered signals [34]) and is therefore used for measuring gases at high concentrations. Furthermore, Raman LiDAR systems require intricate optics design to suppress any signal contamination from elastic backscattered signals [7]. Raman LiDAR, unlike the DIAL technique, can be performed using a wide range of wavelengths ranging from visible to NIR [35].

#### 1.1.2 Automotive LiDAR

While the effectiveness of LiDAR has been exploited in many areas, interest in employing LiDAR in the field of automotive applications has been rising in the past decade in the hope to achieve fully autonomous self-driving vehicles. Statistics have shown that in the United Kingdom, there were more than 100 thousand reported incidents of road casualties, with 1% of the listed resulting in death [36]. Modern cars have been outfitted with an increasing amount of electronics as part of various advanced driver assistance systems (ADAS) aimed at parsing road information, detecting early warning signs to alert drivers into taking precautionary measures, or to sometimes automatically apply direct countermeasures such as emergency braking for collision prevention [37]. ADAS such as blind spot detection, vehicular and pedestrian collision warnings, rear-view parking camera, in general enhances the driving experience and ensures driving, as a mode of transport, is safe for both the driver and other road users. These safety features installed on cars are enabled by a multitude of

sensors based on electromagnetic signals, image capture or ultrasound [38], [39]. Each technology is useful in its own domain but has limitations that require another method to complement. One such example is the use of optical cameras to identify traffic signage and imageries under daytime conditions but would falter under low light night time conditions. Between sensors, overlaps are sometimes necessary to ensure that all road information are accounted for to form a comprehensive map of the 3-D environment, which is essential to attain Level 5 autonomous vehicles, i.e. self-driving cars without need of any driver intervention.

Automotive LiDARs are mainly aimed at the identification of human or wildlife targets at least from a range of 100 metres (to account for the braking distance required when travelling at speed) and the detection and tracking of nearby vehicles. A commonality shared between LiDAR and long range radar is the range factor where both methods are able to identify large objects up to hundreds of metres away. However, a downside to radar is the poor angular resolution, limiting the ability to recognise relatively smaller objects such as humans at a distance away [40]. Distance information can be extracted from the time delay between the transmitted and received signals, using a simple relation of  $d = \frac{c_0 \cdot \Delta t}{2}$ , where d is the distance,  $c_0$  is the speed of light in air (as the transmission medium) and  $\Delta t$  is the travel time for a roundtrip, hence this method is also known as time-of-flight (ToF) LiDAR. The first demonstration of automotive LiDAR on a ground-based vehicle was a rotating disc unit that houses 64 lasers at DARPA's Grand Challenge in 2005, which was aimed at encouraging technological innovations and developments in the field of autonomous vehicles [41]. The inventors of that particular LiDAR module went on to establish Velodyne Lidar, the pioneering company in the automotive LiDAR industry and one of the most dominant in the current market. Commercially available Velodyne LiDAR units operate at a wavelength of 905 nm and uses a mechanical scanning method to provide a complete 360° horizontal field-of-view surrounding the vehicle.

Besides Velodyne, an increasing number of budding companies are tackling the automotive LiDAR industry, each with key aspects of technological innovation and individual approaches to improve LiDAR performance. To list a few, Luminar uses an illumination wavelength of 1550 nm coupled with a mechanical mirror beam steering system, AEye focuses on a software-based approach using an onboard artificial

intelligence to learn and adapt to ever-changing driving conditions and Ouster employs a flash illumination technique at a wavelength of 850 nm. There are others opting for more unconventional methods such as Baraja using tunable lasers and an optical prism to manipulate beam direction and Quanergy working on controlling the laser beam with optical phased arrays.

Only a narrow selection of wavelengths, namely 905, 940 and 1550 nm, are commonly used for automotive LiDAR. This is largely due to two reasons: one, the local minima in the solar spectrum reflected from the Earth's surfaces after attenuation through atmospheric water vapour [42]; and two, the availability of mature laser and detector technologies for a fully solid-state system. For comparison, the solar photon flux at the unconventional LiDAR wavelength of 850 nm is 2, 10 and 3 times higher than at 905, 940 and 1550 nm respectively [43]. It is argued in Ouster's case that the poor water vapour absorption at 850 nm can instead be advantageous to ensure consistent LiDAR performance in humid weather and foggy conditions. For near-infrared (NIR) LiDAR operation in the range of 850 – 940 nm, GaAs-based laser diodes and vertical cavity surface emitting lasers (VCSELs) are widely available while cheap, mature Si-based sensors can be used as detectors. Similarly, in the 1550 nm short-wave infrared (SWIR) wavelength, InP-based technologies are commercially available for laser diodes and photodetectors.

The choice of operation wavelength is weighed not only on the aspect of component cost (which heavily favours the shorter wavelengths) but also eye-safety considerations and thereby the performance. Eye safety poses an inherent limit to the maximum laser power a LiDAR system can output (and therefore the maximum range) since automotive LiDAR functions in environments where human eyes are exposed to laser light and infrared wavelengths cannot trigger eye-blinking reflexes. Exposure over the maximum permissible exposure (MPE), which is a function of laser power and exposure time, will cause retinal damage and therefore a method of mitigation is the use of short laser pulses. 1550 nm lasers are generally considered eye-safe as compared to 905 or 940 nm [44] which allows higher laser output powers for superior range performance. The dispersal, scattering and attenuation of laser light under harsh weather conditions such as foggy, rainy or snowy conditions can severely impact the transmittance of laser and degrade LiDAR performance [45]–[47]. Higher output

powers (up to 10 times more than shorter wavelength options) allowable on 1550 nm systems is therefore a more attractive choice under adverse weathers [48].

The emitted laser can be attenuated by both external factors and internal system imperfections from equation 1.1 [49], for example atmospheric transmission, target reflectivity, optics transmission efficiency and distance, such that the returning signal becomes extremely limited down to a few or even a single photon, necessitating the use of highly sensitive photodetectors such as avalanche photodiodes (APDs) [50], [51]. APDs are devices with an internal gain mechanism that is able to boost the received signal, thus increasing the signal-to-noise ratio (SNR) of a detection system. Furthermore, APDs can be operated in linear mode or Geiger mode, where the former produces signal amplification that is proportional to the applied voltage bias while the latter produces binary signals depending on the detection (or absence) of an incoming photon. Devices of the latter design are also sometimes known as single photon avalanche diodes (SPADs). For Si-based technologies, Si APDs and silicon photomultipliers (SiPM) [52] are used as the detector of choice for the NIR range while InGaAs-on-InP linear mode APDs and SPADs [53]–[55] are used in 1550 nm LiDAR systems, albeit at a higher cost than Si. Signal detection can be complicated in an automotive LiDAR system due to the exposure and detection of external ambient light sources from the environment (including laser light from other vehicular lasers and the Sun). Despite having narrow bandwidth bandpass filters incorporated to reject ambient light from background solar radiation, background photocurrent is unavoidable and depending on the detector field of view, size, and other factors, may contribute nWs (at 1.5 µm wavelength) of power into the detector [56], considering state-of-the-art InGaAs may only have dark currents in the range of nA (depending on the bias voltage) [57]. In the case of SPAD detectors, background signals can create false avalanche pulses that will hinder the correct detection of return signals [51]. Furthermore, reflected signals stronger than expected (either from retroreflectors on the road or a fast-moving vehicle crossing the laser path) can result in signal contamination or worse, damage to the detectors [58]. Hence, dedicated data processing units with signal identification and rejection algorithms are required as part of a LiDAR system [59].

Depending on the MPE to maintain eye safety standards and the laser pulse energy required for signal detection [60], the sensitivity required from the detector varies, going from the most sensitive SPADs to linear mode APDs and finally to unity gain

photodiodes. Considering the relation between operating wavelength and laser pulse energy, using higher power at 1550 nm wavelength signals (6 orders of magnitude higher MEP than 905 nm) also offers benefits in the choice of detector, allowing smaller area, large format arrays (advantageous for noise suppression) [61]. For example, a simple p-i-n InGaAs photodiode array (useful for their low dark current at low bias and lack of cooling hardware needed) has demonstrated a range of 51 m and 159 m using laser pulse energies of 300 µJ and 3 mJ respectively [62]. When comparing APD and SPAD performances for LiDAR, there are clear strengths and weaknesses of each option, some of which has been mentioned along the texts [51]. Admittedly, while both detector choices require some form of cooling for different reasons (reduced dark counts in SPADs and temperature stability of gain in APDs); in SPADs, the generated current pulses are more uniform than in APDs due to the stochastic nature of the avalanche process which also results in a long timing jitter. However, SPADs have a dead time after detection and APDs are advantageous in 3D ranging because the signal amplitude is proportional to the distance travelled by the return signal [51].

Hamamatsu features room temperature SiPM-based LiDAR sensor with a total of 2668 pixels and a pixel pitch of 25 µm, with a capacitance of 65 pF, 6% crosstalk and a dark count rate of 500 kHz [63]. Voxtel has demonstrated a 256 x 256 Si-based SPAD image sensor with pixel pitch of 30 µm, a low dark count rate of 55 Hz and a 0.4 V variation in breakdown voltage (of 18.75 V), though this is not yet commercially available [64]. The Voxtel portfolio also boasts arrays of sub-50 µm pixel pitch, high gain InGaAs-based APDs with array sizes up to 128 x 128 [65]. 1 x 16 SiPM linear arrays with pixel sizes of 10 µm by ON Semiconductors has capacitances of 59 pF, 25% crosstalk and dark count rate of 30 kHz [66]. Taking HgCdTe, another electron-APD material (discussed in more detail in Section 1.4) as a benchmark for comparison, HgCdTe APD arrays for LiDAR applications have been demonstrated [67]. The 4x4 array with a pixel pitch of 80 µm was reported to show uniform gain, quantum efficiency and dark current performances. When used in conjunction with a ROIC, bandwidths up to 7 MHz were obtained and the operating temperature is controlled by an integrated Stirling cooler, providing an integrated detector module. Similar to HgCdTe, InAs is also an electron-APD material with a narrow bandgap; while InAs in LiDAR applications have yet to be demonstrated, it is expected that in the future, with more development InAs APDs will achieve similar performances.

#### 1.2 Infrared imaging

Imaging in infrared wavelengths can provide information that is otherwise invisible, or hidden when using conventional visible light imaging systems. Furthermore, visible light imaging can become limited by the lack of an illumination source, such as imaging during nighttime. Visible light ranging from roughly 400 to 700 nm, is perceivable by the human eyes. Hence, it is no surprise that is the most common imaging wavelengths available to humans as information can be conveyed without any need of further interpretation. The first coloured still image was captured by James Clerk Maxwell back in 1861 [68], followed by the invention of coloured motion pictures roughly four decades later in 1899 by Edward Raymond Turner [69]. The analogue techniques, since then, have been replaced by solid-state technology and digital image processing methods. Beyond the visible light wavelengths is the infrared regime spanning from 700 nm up to 1 mm and is generally split into a number of bands: 1) the near-infrared band from 700 nm to 1.4 µm, 2) the short-wave infrared band from 1.4 to 3 µm, 3) the mid-wave infrared (MWIR) band from 3 to 8 µm, 4) the long-wave infrared (LWIR) band from 8 to 15 µm and 5) the very long-wave infrared (VLWIR) territory after 15 µm.

One form of infrared source, and perhaps the most prominent, is black-body radiation, that is a characteristic spectrum of electromagnetic radiation emitted by any object of a given temperature [70]. Black-body radiation is also sometimes known as thermal radiation due to the dependence on the object's temperature, where a higher temperature corresponds to a shorter peak wavelength, and is described by Planck's law [70]. These natural occurring infrared radiation can be detected such as in thermal imaging of the human body for temperature monitoring. The peak wavelength of a black-body source,  $\lambda_{peak}$ , is given by  $\lambda_{peak} = \frac{2.898 * 10^{-3}}{T} (\mu m)$ , where T is the temperature, from Wien's displacement law [71]. For the case of the human body temperature, the peak wavelength lies approximately at 9.5  $\mu$ m in the LWIR region which can be picked up by a microbolometer [72]. Disease diagnostics in biomedical applications from the black-body principle have been demonstrated, such as observing temperature gradients around acute inflammations in arthritic patients [73].

Unlike visible light imaging which is rendered useless in the absence of sunlight under night time conditions, SWIR imaging can function due to night illumination, otherwise known as nightglow, that has a peak emission around 1.6 µm [74]. Imaging can be performed by detecting nightglow reflections from objects in the scene [75], [76] or by actively illuminating the scene with a laser source and detecting the reflected signals [77], [78], akin to ToF LiDAR operation. When operating in the active sensing mode, gated viewing operation is normally employed where the camera is switched on with a delay after the laser pulse is sent. As a result, imageries from backscattered signals due to fog and dust are ignored and only signals from a set distance away will be registered [79]. An added advantage that infrared imaging possesses is the ability for infrared light to better penetrate through obscurants such as fog, smoke and haze over visible light [80]. Light traversing through an atmosphere laced with tiny particles can be scattered and dispersed, leading to low amounts of return signals and diminished image quality. This form of elastic scattering, Rayleigh scattering, has an inverse relation with the fourth power of wavelength and therefore can be mitigated by using longer wavelength light in the infrared regions [81]. Due to the lack of colour information in an infrared system, image formation instead requires extensive image processing algorithms to reconstruct the large amounts of data for image acquisition [82].

#### 1.3 Telecommunication systems

With the birth of optical fibres, long distance communication using electrical signals via copper telegraph cables were made obsolete. Today, a dense network of hundreds of undersea fibre optic cables form the backbone of modern telecommunications [cite undersea cable website]. Early generations of optical data transmission functioned at the wavelength range of 800 – 900 nm, using GaAs/AlGaAs based laser diodes and LEDs paired with Si detectors [83]. With improvements towards the manufacturing of high purity silica fibres [84], the operational wavelength shifted towards infrared wavelengths of 1.3 and 1.5 µm where the losses (due to absorption and scattering in silica) are the lowest. To meet increasing demands for high data rate, modern engineers utilise techniques such as wavelength division multiplexing (WDM) to combine signals of different (but closely spaced) wavelengths into a single optical fibre for

transmission. An optical communication system typically consists of laser diodes, modulators, (de-)multiplexer, optical fibres, photodetectors, and readout electronics.

The bandwidth of a photodetector is determined by the transit time, that is the time it takes for photogenerated carriers to exit the high field junction, and the RC time constant that arises from the diode series resistance and junction capacitance. For a fast response, the carriers are ideally absorbed in the depletion region where the built-in electric field is present. The junction capacitance is inversely proportional to the depletion width, which is dependent on the doping concentrations in a p-n diode. To minimise the capacitance, small area p-i-n detectors with a thick, low background doping concentration intrinsic region are used. This, however, compromises the carrier transit time by creating a larger distance for carriers to traverse and also a smaller light sensitive area. There are also trade-offs to be made with the detector quantum efficiency which require a long depletion width due to the exponential relation of light absorption. Hence, the design of photodetectors is complicated by a number of competing factors to consider. There are, therefore, a number of engineered methods to produce high speed photodiodes, namely the resonant cavity structure photodiode (increased quantum efficiency by reflecting unabsorbed light back into a thin depletion region) [85], the uni-travelling carrier photodiode (bandgap engineered to only allow electron drift) [86] and waveguide photodiodes (side-illuminated so that the direction of carrier movement and light propagation are different) [87]. Other than the aforementioned factors affecting the detector bandwidth, the bandwidth of APDs is also governed by carrier feedback and build up during the avalanche process where a higher gain generally increases the avalanche build up time and lowers the bandwidth [88].

For a typical photodetector-amplifier receiver system, utilising an APD over a p-i-n photodiode is more advantageous in improving the receiver sensitivity as the amplifier noise generally dominates over a p-i-n photodiode (discussed further in Section 2.2) [89]. There are a number of constraints that limit the sensitivity of an APD such as dark current, carrier ionisation rates and avalanche excess noise factor [90]. To assess the receiver sensitivity, it is common to evaluate the minimum signal power required to produce a bit error rate (BER) of typically,  $10^{-12}$ , where the BER refers to the probability of an incorrect measurement of "1" or "0" will be made. In order to satiate the rapid growth of transmission capacity, APDs capable of 25 Gb/s [91] and 50 Gb/s

[92] operation have been demonstrated. The most dominant material for telecommunications wavelength is InGaAs which has a bandgap energy of 0.75 eV at room temperature, corresponding to a cutoff wavelength of 1.7 μm which adequately covers the telecommunications bands from 1.3 to 1.6 μm. This provides a natural advantage to using InGaAs without incurring deficits (such as high dark currents) when using materials with narrower bandgap, for example InAs, that is able to cover a similar wavelength range. To circumvent the issue of high dark currents, one can reduce the active device area, typically to radii of 10 to 30 μm (which also carries along an added advantage of lowered junction capacitance suited for high speed operations), however, InAs devices with small dimensions have not yet been demonstrated. Another strategy to adopt InAs as telecommunications APD is to couple incoming signal through side illumination using an integrated packaging solution with lensed fibre since thick intrinsic region widths of up to 10 μm is generally sought for in InAs for high gain at low operating voltages.

#### 1.4 Literature review

Solid-state solutions are favoured in modern technologies for their compactness and mass-manufacturability. Imaging sensors made with CMOS technology are able to keep up with Moore's law, reducing in pixel sizes to allow a greater packing density [93]. In a modern digital camera, millions of pixels, each an individual semiconductor device, can be packed into an area less than 1 cm<sup>2</sup> [94]. Semiconductor devices are widely used in the aforementioned applications and in the heart of these systems, a light-sensitive photodetector is required.

#### 1.4.1 InAs

InAs is one such photodetector material from the III-V semiconductor family that is suitable and attractive for its narrow band gap of 0.36 eV, translating to a detection wavelength of 3.4 µm in the MWIR region. This section will mainly focus on InAs photodiodes and APDs, an extensive review on other facets of the InAs material can be found in Ref. [95].

One of the earliest report of InAs photodiode is by Lucovsky [96], where a p-n junction diode is formed via Cd diffusion into an n-type InAs with its forward and reverse current characteristics behaving as expected from conventional diode theory. Further

probing reveals the onset of avalanche multiplication at a reverse bias of -0.9 V in these InAs photodiodes, obtaining a multiplication factor of 10 at -10 V [97]. Fundamental properties such as the absorption coefficients at the InAs band edge as a function of donor and acceptor impurities were also investigated by Dixon and Ellis [98] as well as minority carrier diffusion lengths and surface recombination velocity in photovoltaic InAs p-n junctions by Mikhailova *et al.* [99]. Mikhailova went on to be the first to attempt to derive ionisation coefficients of InAs to show that indeed a relatively low electric field strength is needed to obtain carrier multiplication in InAs [100]. In the same work, it was also concluded that the hole ionisation coefficient is an order magnitude larger than the electron ionisation coefficient which is attributed to a resonance effect of holes in the spin-orbit split-off valence band.

Hereafter, developments in InAs photodiodes slowed down despite showing promise as a mid IR photodetector as compared to InSb which possesses a smaller band gap that covers the entire MWIR band. One reason perhaps, is due to the Fermi level lying above the conduction band minimum at InAs surfaces, resulting in an accumulation of electrons in the conduction band at the surface-bulk boundary [101]. These surface charges are thought to originate from an excess of anions, from antisite defects and dangling bonds, giving donor-like properties and contributing to excess electrons [102]. The phenomenon is observed in both In-rich and As-rich surfaces [103], [104] and detailed experimentally as well [105], [106]. This resulted in difficulties in producing practical InAs devices due to the lack of surface passivation techniques to remove these surface accumulation charges and suppress surface leakage currents. Lin et al. demonstrated suppressed leakage currents in unpassivated InAs p-i-n photodiodes as opposed to regular p-n junction photodiodes [107]. A further systematic study by the same authors with temperature dependent currentvoltage (I-V) characteristics revealed that an increasing i-layer thickness from 0 to 720 nm effectively suppresses tunnelling currents, explaining the advantages of p-i-n InAs diodes compared to a simple p-n junction [108]. Around a similar time period, Iwamura and Watanabe produced InAs p-n diodes by diffusion of Zn atoms [109] with a peak responsivity of 0.28 A/W at 3.2 µm but with dark currents roughly 100 times higher than in [108]. Zn-diffusion in InAs diodes were studied in [110], comparing the leakage currents as a function of diffusion temperature and time. Despite having poor diode characteristics and potentially surface-limited currents at low temperatures, the

work demonstrated an InAs array capable of detection of alpha particles. Several authors have also reported homojunction and heterojunction (with a lattice matched ptype InAsSbP grown on InAs substrate) InAs photodiodes while investigating the temperature dependent I-Vs, in particular trap-assisted tunnelling currents [111]–[113].

Dobbelaere *et al.* investigated InAs photodiodes grown heteroepitaxially on GaAs and GaAs-on-Si substrates in hopes of realising monolithic integration of InAs infrared detectors with read-out electronics [114]. Unsurprisingly, the device performance degrades due to large amounts of dislocations at the highly mismatched interface as compared to homoepitaxial InAs diodes. Even so, the authors demonstrated the monolithic integration of InAs photodiode with a GaAs MESFET in a separate publication [115]. Shi *et al.* also demonstrated high speed operation up to 20 GHz from Zn-diffused InAs photodiodes grown on semi-insulating GaAs substrates that is limited by the inherent electron transit [116]. Over the years, growth of InAs epilayers have been demonstrated via various techniques ranging from liquid phase epitaxy (LPE) [117] to molecular beam epitaxy (MBE) [118] and also metal-organic vapour phase epitaxy (MOVPE) [119].

The drought on InAs based detector research persisted until Marshall et al. demonstrated bulk-dominated leakage currents using a combination of etchants, namely phosphoric acid: hydrogen peroxide: de-ionised water (H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:DIW) in a 1:1:1 ratio followed by sulphuric acid: hydrogen peroxide: de-ionised water (H<sub>2</sub>SO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub>:DIW) in a 1:8:80 ratio (which will now be referred to as the standard etching recipe for InAs) [120]. Prior to this work, the same authors have also shown multiplication in a number of p-i-n and n-i-p InAs diodes where it was observed that multiplication due to electrons are larger than multiplication due to holes [121], directly in contrary to the reports by Mikhailova et al. in 1976 [100]. Further experimental work shows multiplication due to mixed injection of absorbed excitation light in the intrinsic region to be greater than hole initiated multiplication in n-i-p diodes [122] and the avalanche excess noise under pure electron injection condition to be less than 2 (the theoretical minimum according to McIntyre's ionisation theory [123] which will be further discussed in chapter 2) [124]. The latter is characteristic of single carrier multiplication (SCM), i.e. k = 0, where k is the ratio of hole  $(\beta)$  to electron (α) ionisation coefficient, which is also seen in HgCdTe APDs [125].

Theoretical calculations on impact ionisation in InAs by Monte Carlo methods have been performed separately by Brennan [126] and Satyanadh [127] where the parameterised electron ionisation coefficients from the former are similar to the experimental findings of Marshall. A series of p-i-n and n-i-p diodes characterised in [128] showed that electron impact ionisation is confined within the  $\Gamma$  valley due to the very low electric field required for multiplication and  $\beta$  is negligible in InAs within the studied range of electric field.

Figure 1.1 Electron and hole ionisation coefficients of InAs at 293 [105] and 77 K [106]

Single carrier multiplication promises several unique properties in e-APDs. Following multiplication theory in a device with uniform electric field, the multiplication due to electrons,  $M_e$  is given by  $M_e = \exp{(\alpha W)}$  where W is the depletion width. That is to say, multiplication scales exponentially with the depletion width at a given  $\alpha$ . In addition, the electron ionisation coefficient of InAs remains relatively constant under low electric field range as seen from Fig. 1.1, resulting in a strong dependence of multiplication on the depletion width. For a p-i-n diode, given a sufficiently low background carrier concentration in the intrinsic region, the APD gain will increase with the i-region thickness. This has been observed at room temperature [128] and at 77 K [129]. Interestingly, in [129], it was found that the electron ionisation coefficient has a positive temperature dependence, i.e. the obtainable multiplication at a given electric field is lower at reduced temperatures and this contradicts with other known III-V APDs. The absence of (or lack of) hole-initiated impact ionisation gives rise to

a more deterministic occurrence of impact ionisation, thereby generating lower avalanche excess noise and also removes any carrier feedback in the depletion width. The maximum avalanche build-up time, which is the total duration for all charges created by the avalanche process to leave the high field region, therefore has a maximum limit that is the sum of the transit time of electron and that of hole. Again, this is different from conventional APD materials where the device bandwidth is influenced by the avalanche gain [130]. Gain-independent bandwidth in InAs has been demonstrated in [131] where a gain-bandwidth product (GBP) of 580 GHz at a bandwidth of 3 GHz, the highest in any III-V APDs at the time, has been achieved. Ranging experiments at MWIR wavelengths also show picosecond time resolution [132], further attesting to short avalanche pulses in InAs. To obtain a large GBP for telecommunication applications using InAs APDs, there is likely a trade-off between the gain and bandwidth as the former relies on a long depletion width for a large buildup of avalanche carriers and the latter requires a distance as short as possible for carriers to exit. Recent sensitivity analysis on InAs APDs however, does point that at data rates of 10 and 25 Gb/s at 1550 nm wavelength, InAs APDs offer superior performance over InAlAs APDs but falter against Si/Ge alternatives at 1330 nm. To remain competitive, the dark current performance of InAs APDs requires further improvement [133].

To digress slightly, one main reason for the prominence of Silicon devices amongst the many different semiconductor materials is the ease to form SiO<sub>2</sub> layers as encapsulants for exposed semiconductor surfaces. Unfortunately for III-V compound semiconductors, the lack of a simple and effective method of passivation presents a major barrier to producing stable, robust practical devices. In InAs, oxide formation mechanisms are complicated by the fact that various composition of In<sub>x</sub>O<sub>y</sub>, As<sub>x</sub>O<sub>y</sub> and even ternary oxides of In-As-O can exist [134]. Following the works by Kim to suppress leakage currents in InAs/GaSb superlattice detectors [135], a passivation scheme using spin-coated SU-8 photoresist on InAs APDs was employed to give reduced leakage currents [136]. This allowed a systematic study on the temperature dependence of dark I-Vs, the analysis of dominant current mechanisms and the origin of said mechanisms [137], [138] along with detailed measurements on the temperature dependence of avalanche gain and excess noise in InAs [139]. An analytical band Monte Carlo model [140] developed to model impact ionisation in InAs explains that

the positive temperature dependence of avalanche gain in InAs is due to a more dominant effect temperature has on the ionisation threshold energy,  $E_{th}$ , than the that of phonon scattering. The reasoning given is that due to the large intervalley ( $\Gamma$ -L and  $\Gamma$ -X) separation energies in InAs, carriers capable of initiating impact ionisation (i.e. with energies exceeding the  $E_{th}$ ) are largely confined to low scattering  $\Gamma$  and L valleys which are influenced to a greater degree by increased  $E_{th}$  at reduced temperatures.

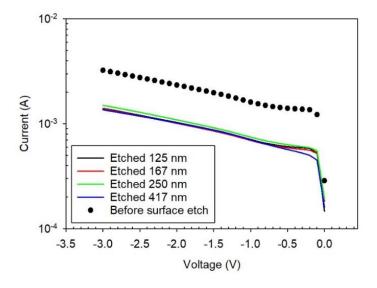

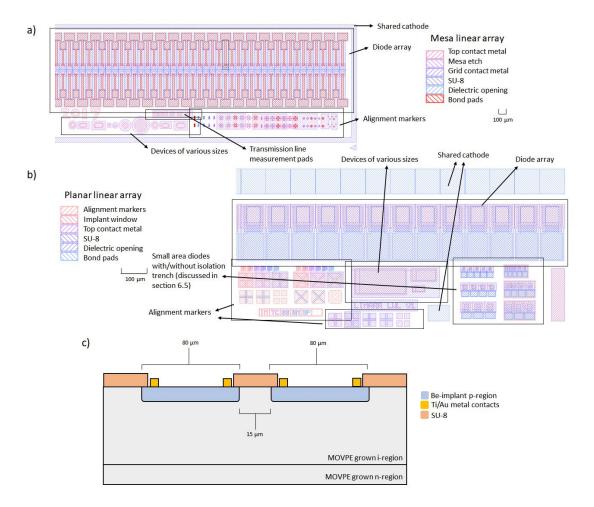

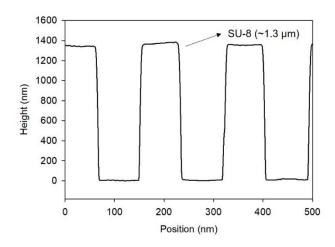

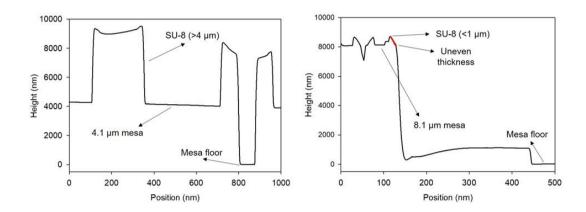

Separate from the Sheffield group, Bank's group in University of Texas has also demonstrated InAs APDs [141], [142] with similar gain and excess noise characteristics, proving that early work by Mikhailova *et al.* was anomalous. Monte Carlo simulations in [141] argues that due to decreased absorption of optical phonons at 77 K, carriers gain energy at a much slower rate. At the same time,  $E_{th}$  for impact ionisation, that is proportional to the band gap, increases at lower temperatures, hence the overall carrier multiplication decreases at reduced temperatures.