# Mapping of Real-time Applications on Network-on-Chip based MPSOCS

Paris Mesidis

Submitted for the degree of Master of Science (By Research)

The University of York,

Department of Computer Science

December 2011

## **Abstract**

#### Mapping of real time applications on real time NoC based MPSoCs

With the recent developments in semiconductor technology it becomes possible to integrate many different processing elements on single chip, this solution is known as a System-on-Chip (SoC). In such systems, the communication between the different components is also an important aspect. On-chip busses or point-to-point communications have been successfully used. However, as the number of elements increases, on-chip busses are not able to scale and quickly become a communication bottleneck. Packet-switched networks on chip (NoC) have been proposed as a solution for on-chip communication of SoC platforms overcoming many of the limitations of on-chip buses. An important design aspect in such a system is the relative placement of tasks on the processing elements of the platform so that some metrics of interest are optimised commonly referred to as the mapping problem. NoC platforms, because of the benefits that they introduce, will eventually be used in commercial embedded and realtime systems. Despite its significance to embedded systems industry and research communities, little research has been done on providing guarantees for hard real-time applications composed of multiple communicating components running over NoC platforms, in such systems both the computation and the communication between the components must complete within certain deadlines for the system to behave correctly. Application mapping has a direct impact on the interference patterns emerging on the platform where separate tasks and the communications between them interfere with each other when contending over shared resources. Even though a significant amount of research has been carried out on the mapping problem usually the aim is to optimise different metrics and reduce cost in terms of energy consumption. This work tries to solve the mapping problem from a real-time systems perspective, in such systems the overall correctness does not only depend on producing the correct output but also on the time required by the system to produce it, this requirement is most commonly expressed with the concept of a deadline which must always bound the response time of a computational task. Schedulability analysis refers to a set of analytical methods that are able to prove a set of tasks can meet their deadlines when sharing resources under a particular scheduling scheme. This work takes advantage of recent advancements on schedulability analysis that can guarantee the timeliness of tasks, as well as their communications, in distributed real-time systems which specifically run on network on chip platforms using wormhole routing, this analysis is used as a ranking function in a genetic algorithm that is able to evolve task mappings which allow all tasks and communication flows to meet their deadlines in all possible scenarios.

# **Table of Contents**

| 1 Introduction                                                          | 1  |

|-------------------------------------------------------------------------|----|

| 1.1 Introduction to NoC Systems and the Mapping Problem                 | 1  |

| 1.2 Problem Formulation                                                 | 4  |

| 1.3 Goals and Objectives                                                | 5  |

| 2 Network on Chip Platforms                                             | 6  |

| 2.1 System Architectures and modeling                                   | 6  |

| 2.2 Network on Chip Features                                            | 7  |

| 2.3 Network Layers                                                      | 8  |

| 2.4 Predictable Communication on NoC platforms                          | 11 |

| 2.5 Network on Chip Modelling                                           | 12 |

| 2.6 Summary                                                             | 13 |

| 3 Real-time Applications and Relevant Models                            | 14 |

| 3.1 Application Domains                                                 | 14 |

| 3.2 Application Modeling                                                | 15 |

| 3.3 Concurrent Models of computation                                    | 16 |

| 3.3.1 Dataflow Networks                                                 | 16 |

| 3.4 Meta-models                                                         | 19 |

| 3.5 Application Models and Analysis for Real-Time Systems               | 20 |

| 3.6 Schedulability Analysis for NoC traffic flows – An Analytical Model | 22 |

| 3.7 Summary                                                             | 24 |

| 4 Mapping Strategies                                                    | 26 |

| 4.1 Approaches to the Mapping Problem                                   | 26 |

| 4.2 Static Mapping                                                      | 27 |

| 4.2.1 Evolutionary Methods                                              | 27 |

| 4.2.2 Greedy Heuristic Methods                                          | 27 |

| 4.2.3 Unified Approaches                                                | 29 |

| 4.2.4 Generic Approaches                                                | 31 |

| 4.3 Dynamic Mapping                                                     | 33 |

| 4.3.1 Per single-task Mapping Methods                                   | 33 |

| 4.3.3 Resource Reserving Algorithms                                     | 38 |

| 4.4 Summary                                                      | 42 |

|------------------------------------------------------------------|----|

| 5 Mapping Algorithms for Hard Real-time Applications             | 44 |

| 5.1 Proposed Approach                                            | 44 |

| 5.2 Development Framework and Methodology                        | 45 |

| 5.3 Genetic Mapping of Hard Real-Time Applications               | 46 |

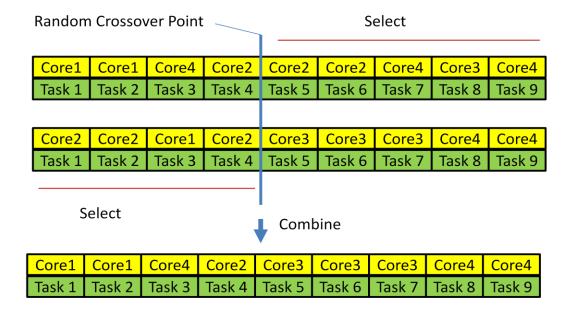

| 5.3.1 Genetic Algorithm                                          | 46 |

| 5.3.2 Route Selection                                            | 49 |

| 5.3.3 Priority Assignment                                        | 51 |

| 5.4 A Heuristic Mapping Algorithm                                | 52 |

| 5.5 Experimental Results                                         | 54 |

| 5.5.1 Input Application Models                                   | 54 |

| 5.5.2 Experimental Results using Custom Benchmarks               | 56 |

| 5.5.3 Experimental Results using Randomly Generated Applications | 63 |

| 6 Conclusions and Future Research                                | 82 |

| 6.1 Suggestions for Future research                              | 82 |

| 6.2 Conclusions                                                  | 84 |

#### **BIBLIOGRAPHY**

# List of Figures

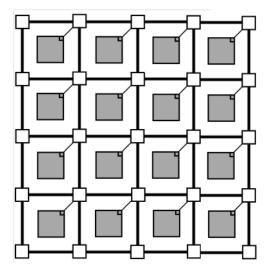

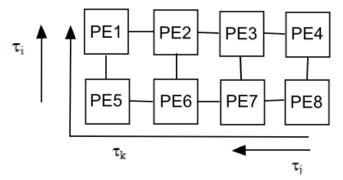

| Figure 1.1 A 4x4 NoC                                                                                                                                                                            | 2   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

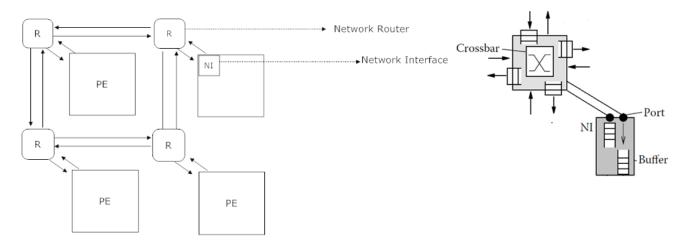

| Figure 2.1 A 2D mesh based NoC                                                                                                                                                                  | 7   |

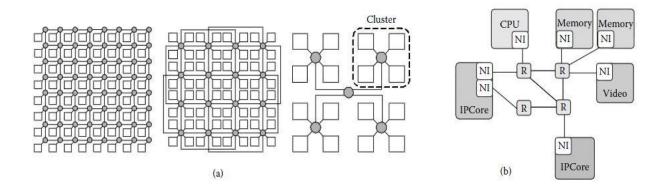

| Figure 2.2 Regular (a) and irregular (b) NoC topologies.                                                                                                                                        | 7   |

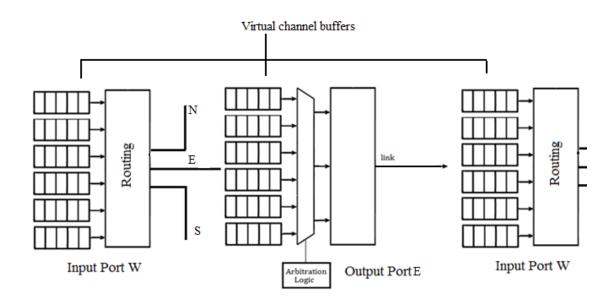

| Figure 2.3 Implementation of Virtual circuit using multiple buffers.                                                                                                                            | 9   |

| Figure 2.4 Message sub-components on a wormhole based NoC.                                                                                                                                      | 10  |

| Figure 2.5 Protocol stack for a wormhole based NoC                                                                                                                                              |     |

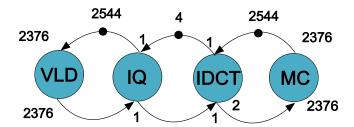

| Figure 3.1 Synchronous Dataflow. Token production/consumption rates.                                                                                                                            |     |

| Figure 3.2 The SDF graph of an H.236 decoder.                                                                                                                                                   |     |

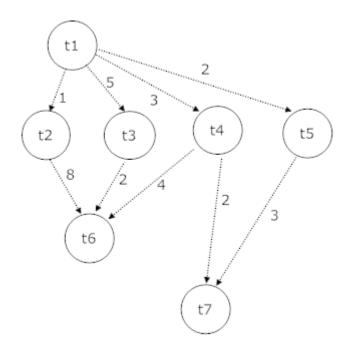

| Figure 3.3 A communication task graph.                                                                                                                                                          |     |

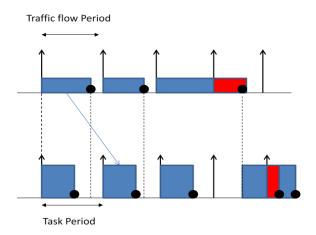

| Figure 3.4 Period and Release times of traffic flows and their receiving tasks.                                                                                                                 | 22  |

| Figure 3.5 Indirect interference between traffic flows $\tau_i$ and $\tau_j$ with different priorities                                                                                          | 24  |

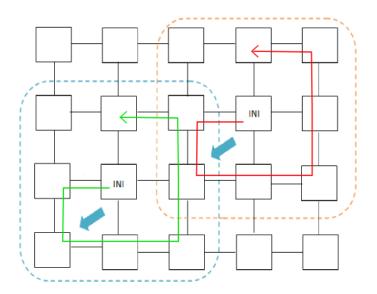

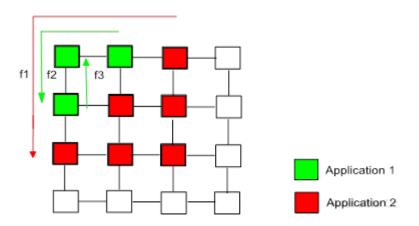

| Figure 4.1 Packing strategy for different applications sharing the same NoC.                                                                                                                    | 35  |

| Figure 4.2 Box bounding of search region for the mapping of task 3.                                                                                                                             | 37  |

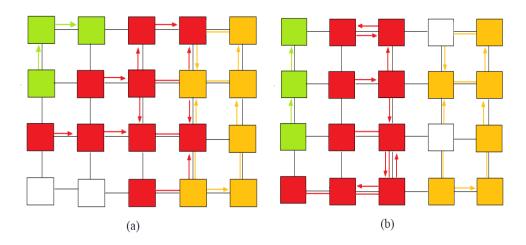

| Figure 4.3 Internal and external contention between traffic flows.                                                                                                                              | 39  |

| Figure 4.4 Mapping solutions for three different applications, (a) internal contention is minimised (b) extern                                                                                  | nal |

| contention is minimised                                                                                                                                                                         | 40  |

| Figure 5.1 Crossover Operator.                                                                                                                                                                  | 47  |

| Figure 5.2 (i)Mapping of Autonomous Vehicle application onto a NoC platform with 3x3 topology                                                                                                   | 56  |

| Figure 5.2 (ii)Mapping of Autonomous Vehicle application onto a NoC platform with 3x4 topology                                                                                                  | 57  |

| Figure 5.3 (i)Mapping of Autonomous Vehicle application onto a NoC platform with 4x4 topology                                                                                                   | 57  |

| Figure 5.3 (ii)Mapping of Autonomous Vehicle application onto a NoC platform with 4x5 topology                                                                                                  | 57  |

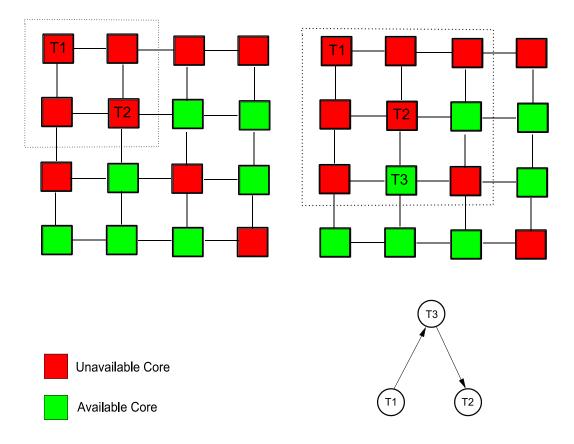

| Figure 5.4 (i)Mapping of Synthetic application onto a NoC platform with 4x4 topology                                                                                                            | 58  |

| Figure 5.4 (ii)Mapping of Synthetic application onto a NoC platform with 4x5 topology                                                                                                           | 58  |

| Figure 5.4 (iii)Mapping of Synthetic application onto a NoC platform with 5x5 topology                                                                                                          | 58  |

| Figure 5.5 Genetic Mapping of Synthetic application onto a NoC platform with 5x5 topology using the guid                                                                                        | led |

| mutation operator                                                                                                                                                                               | 59  |

| Figure 5.6 Genetic mapping of Synthetic application onto a NoC platform of size 5x5 using a                                                                                                     |     |

| combination of both guided and random mutation operators.                                                                                                                                       | 60  |

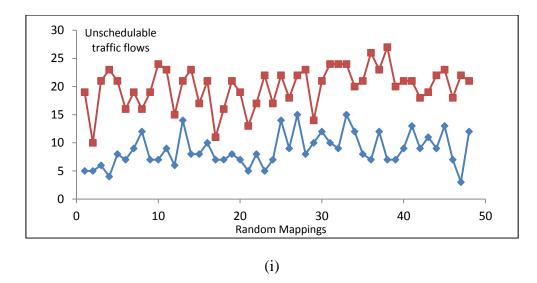

| Figure 5.7 Random mapping of the (i) Autonomous Vehicle and (ii) the Synthetic applications onto a                                                                                              |     |

| NoC platform of size 4x4 when the minimum contention routing algorithm is used                                                                                                                  | 61  |

| Figure 5.8 Random mapping of the (i) Autonomous Vehicle and (ii) the Synthetic applications onto a                                                                                              |     |

| NoC platform of size 4x4 when the proposed priority assignment algorithm is used                                                                                                                |     |

| Figure 5.9 Mapping of Synthetic application onto a NoC platform of size 4x4 using the genetic algorithm in                                                                                      |     |

| combination with the minimum contention route generator.                                                                                                                                        |     |

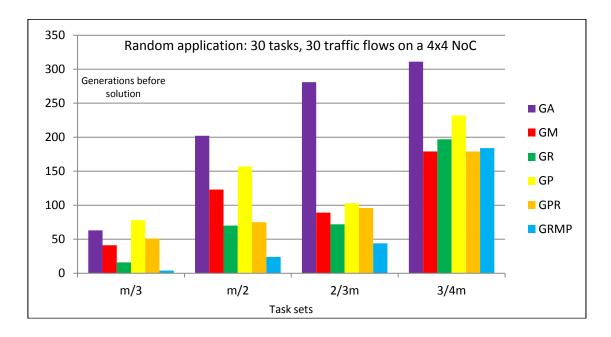

| Figure 5.10 (i) Mapping of random applications onto a NoC platform of size 4x4 using the different version                                                                                      |     |

| the genetic algorithm. The application is composed of 30 tasks and 30 traffic flows                                                                                                             |     |

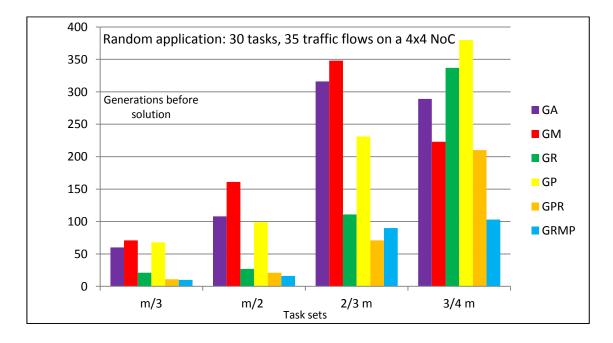

| Figure 5.10 (ii) Mapping of random applications onto a NoC platform of size 4x4 using the different version the genetic algorithm. The application is composed of 30 tasks and 35 traffic flows |     |

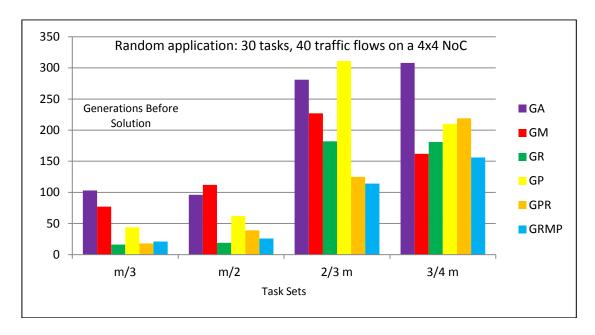

| Figure 5.10 (iii) Mapping of random applications onto a NoC platform of size 4x4 using the different version                                                                                    |     |

| the genetic algorithm. The application is composed of 30 tasks and 40 traffic flows                                                                                                             |     |

| Figure 5.10 (iv) Mapping of random applications onto a NoC platform of size 4x4 using the different version                                                                                     |     |

| the genetic algorithm. The application is composed of 40 tasks and 40 traffic flows                                                                                                             |     |

|                                                                                                                                                                                                 |     |

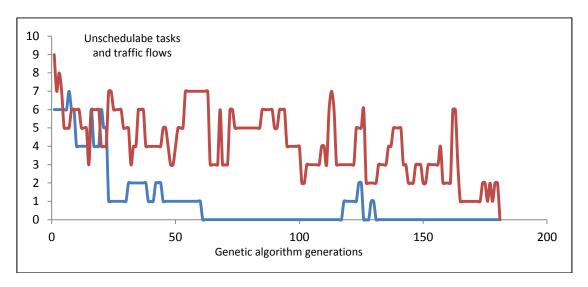

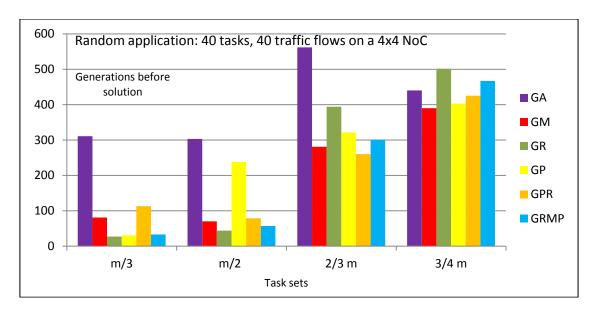

| Figure 5.11 (1) Mapping of random applications onto a INOC platform of size 4x4 using the different versions of                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| the genetic algorithm. The application is composed of 40 tasks and 40 traffic flows67                                                                                                            |

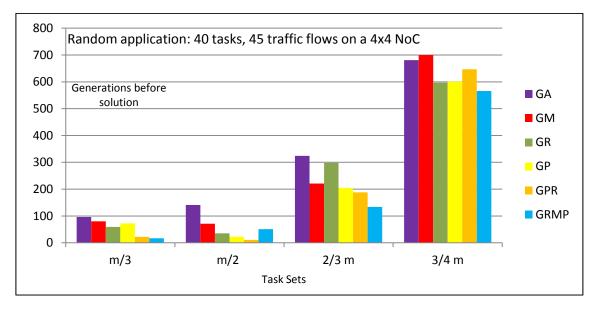

| Figure 5.11 (ii) Mapping of random applications onto a NoC platform of size 4x4 using the different versions of                                                                                  |

| the genetic algorithm. The application is composed of 40 tasks and 45 traffic flows67                                                                                                            |

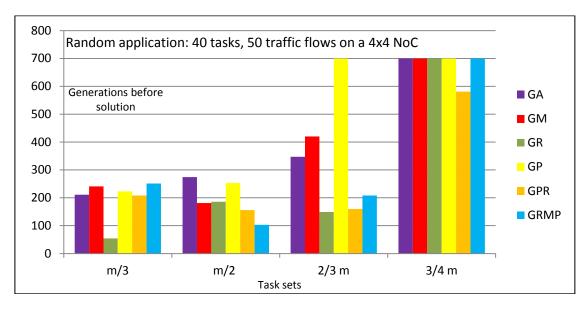

| Figure 5.11 (iii) Mapping of random applications onto a NoC platform of size 4x4 using the different versions of                                                                                 |

| the genetic algorithm. The application is composed of 40 tasks and 50 traffic flows                                                                                                              |

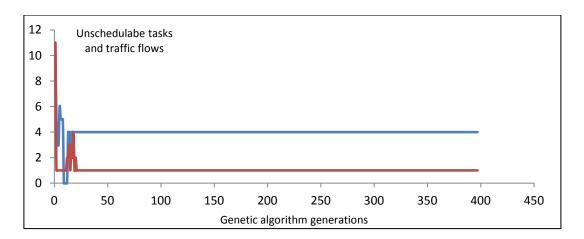

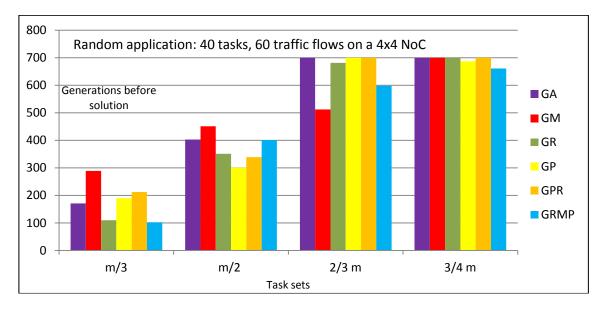

| Figure 5.11 (iv) Mapping of random applications onto a NoC platform of size 4x4 using the different versions of                                                                                  |

| the genetic algorithm. The application is composed of 40 tasks and 60 traffic flows                                                                                                              |

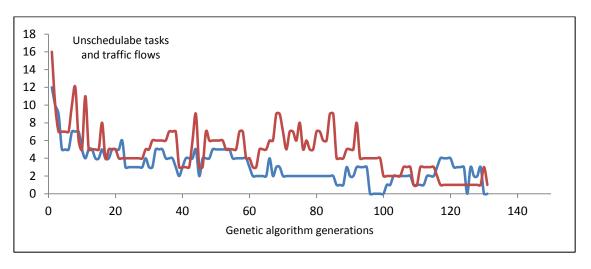

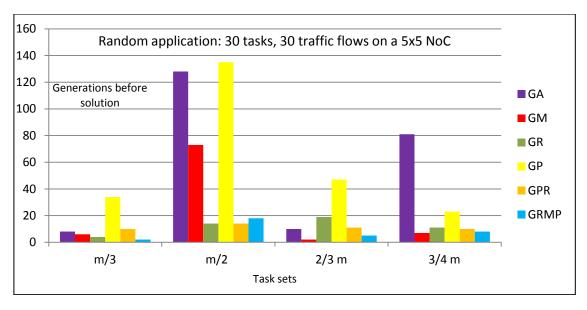

| Figure 5.12 (i) Mapping of random applications onto a NoC platform of size 5x5 using the different versions of                                                                                   |

| the genetic algorithm. The application is composed of 30 tasks and 30 traffic flows69                                                                                                            |

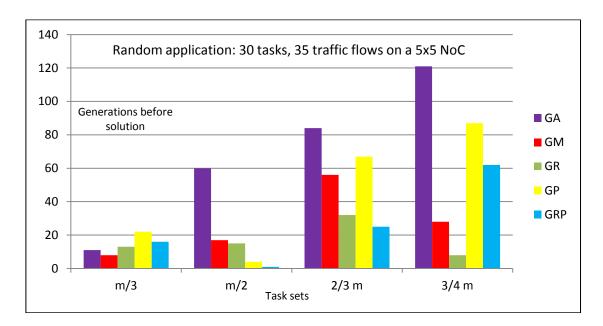

| Figure 5.12 (ii) Mapping of random applications onto a NoC platform of size 4x4 using the different versions of                                                                                  |

| the genetic algorithm. The application is composed of 30 tasks and 35 traffic flows69                                                                                                            |

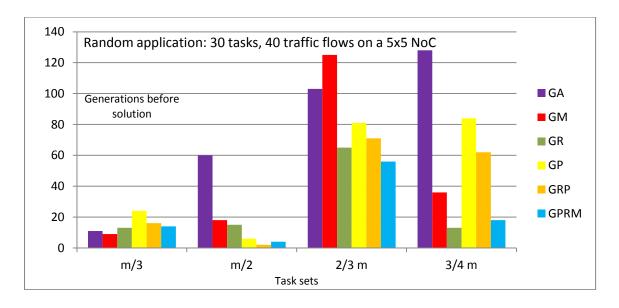

| Figure 5.12 (iii) Mapping of random applications onto a NoC platform of size 5x5 using the different versions of                                                                                 |

| the genetic algorithm. The application is composed of 30 tasks and 40 traffic flows70                                                                                                            |

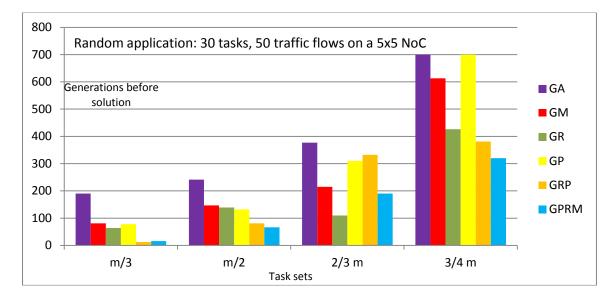

| Figure 5.12 (iv) Mapping of random applications onto a NoC platform of size 5x5 using the different versions of                                                                                  |

| the genetic algorithm. The application is composed of 30 tasks and 50 traffic flows70                                                                                                            |

| Figure 5.13 (i) Mapping of random applications onto a NoC platform of size 5x5 using the different versions of                                                                                   |

| the genetic algorithm. The application is composed of 40 tasks and 40 traffic flows71                                                                                                            |

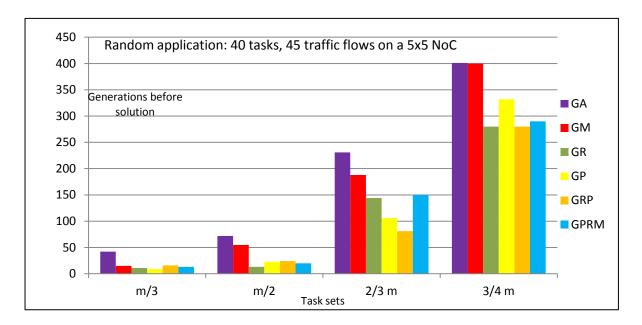

| Figure 5.13 (ii) Mapping of random applications onto a NoC platform of size 5x5 using the different versions of                                                                                  |

| the genetic algorithm. The application is composed of 40 tasks and 45 traffic flows71                                                                                                            |

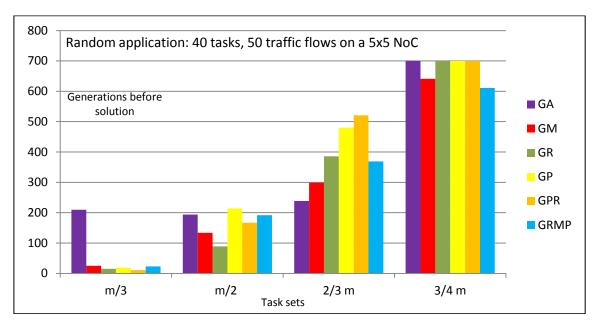

| Figure 5.13 (iii) Mapping of random applications onto a NoC platform of size 5x5 using the different versions of                                                                                 |

| the genetic algorithm. The application is composed of 40 tasks and 50 traffic flows72                                                                                                            |

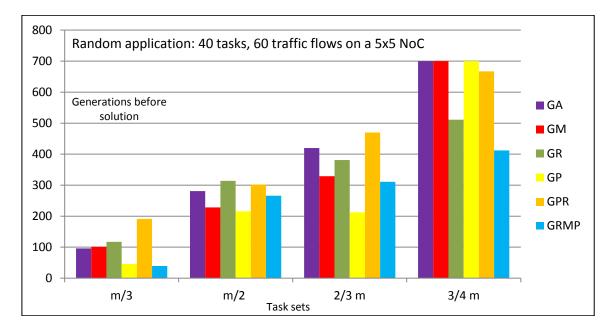

| Figure 5.13 (iv) Mapping of random applications onto a NoC platform of size 5x5 using the different versions of                                                                                  |

| the genetic algorithm. The application is composed of 40 tasks and 60 traffic flows72                                                                                                            |

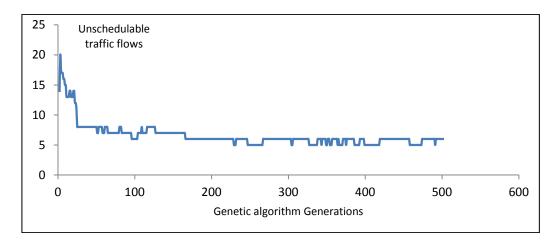

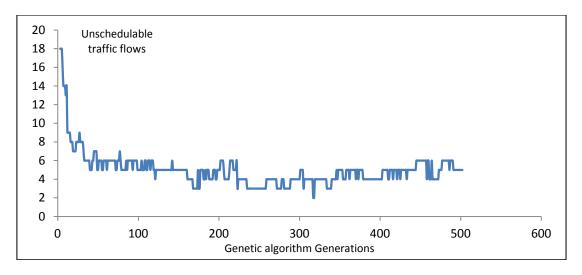

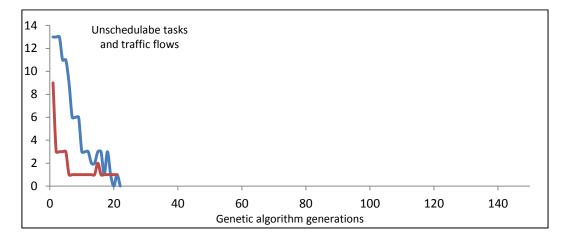

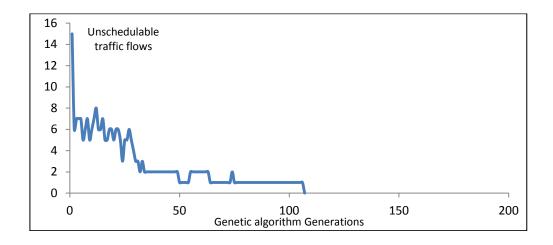

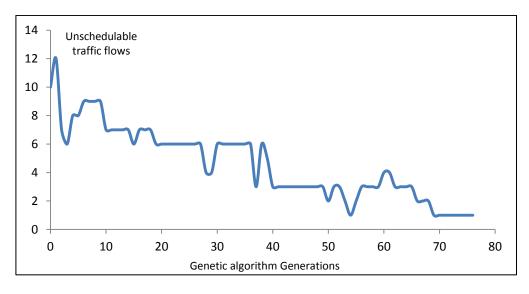

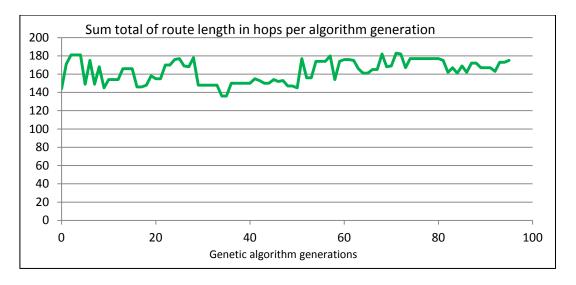

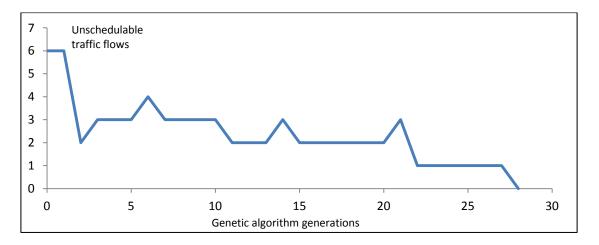

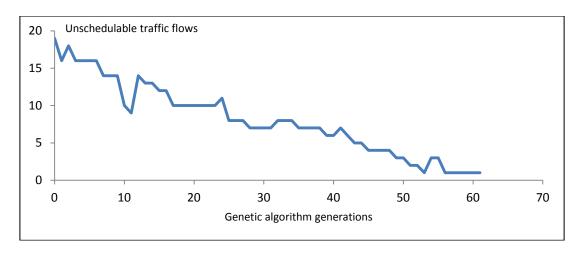

| Figure 5.14 (i) The evolution of the values of unschedulable traffic flows for the Autonomous Vehicle                                                                                            |

| application mapping on a 4x4 NoC74                                                                                                                                                               |

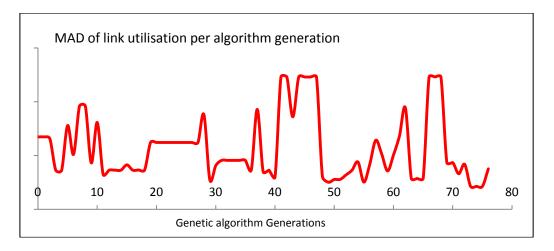

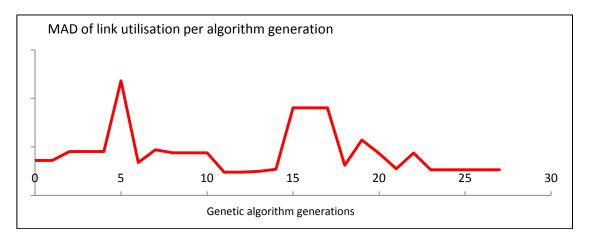

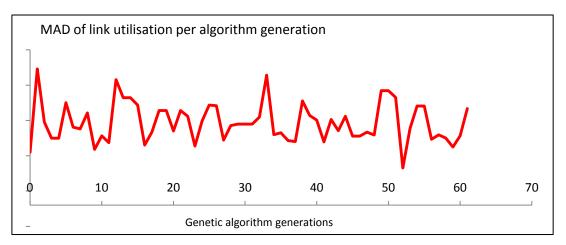

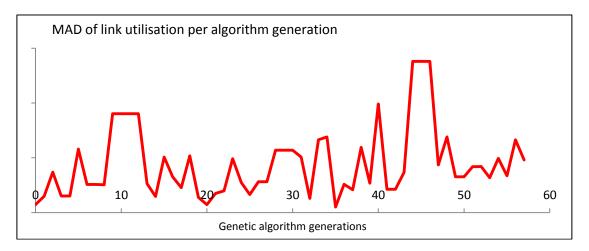

| Figure 5.14 (ii) The evolution of the values of the mean absolute deviation of the utilisation of the network links                                                                              |

| versus the genetic algorithm generations for the Autonomous Vehicle application mapping on a 4x4                                                                                                 |

| NoC                                                                                                                                                                                              |

| Figure 5.14 (iii) The evolution of the values of the mean absolute deviation of the utilisation of the network                                                                                   |

| links versus the genetic algorithm generations for the Autonomous Vehicle application mapping on a 4x4                                                                                           |

| NoC75                                                                                                                                                                                            |

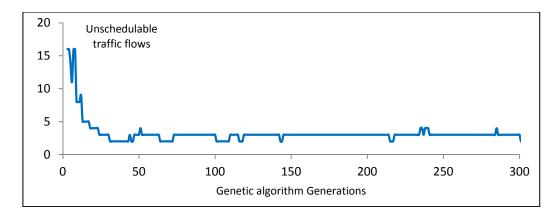

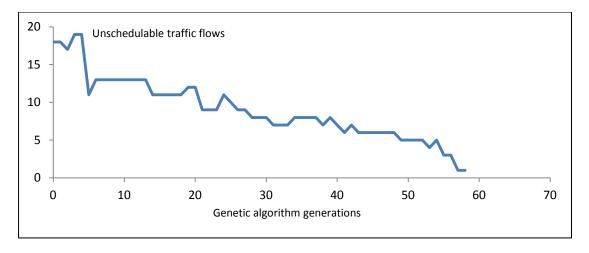

| Figure 5.15 (i) The evolution of the values of unschedulable traffic flows for the synthetic                                                                                                     |

| application mapping on a 4x5 NoC                                                                                                                                                                 |

| Figure 5.15 (ii) The evolution of the values of the mean absolute deviation of the utilisation of the network links                                                                              |

| versus the genetic algorithm generations for the synthetic application mapping on a 4x5 NoC                                                                                                      |

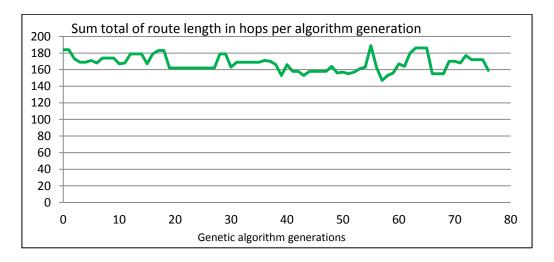

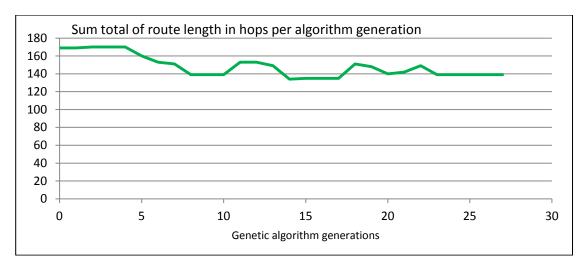

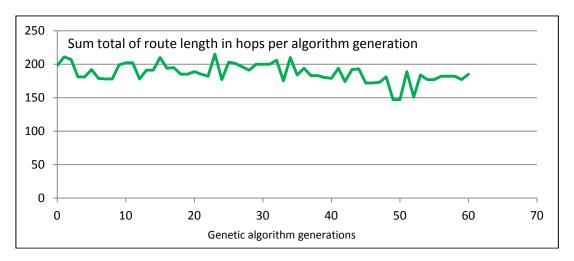

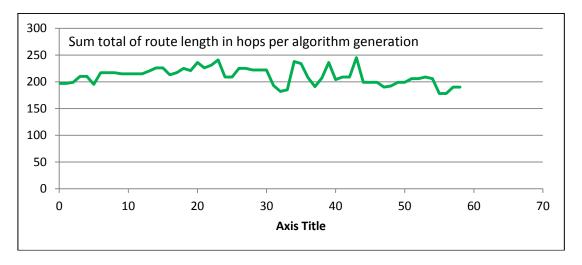

| Figure 5.15 (iii) The total sum of the route length over all traffic flows per generation of the genetic algorithm,                                                                              |

| values recorded for the mapping of the synthetic application on a NoC platform of size 4x5                                                                                                       |

| application comprising of 30 tasks and 35 traffic flows with an overall task utilization of 8 on a NoC platform of                                                                               |

| size 4x4                                                                                                                                                                                         |

| Figure 5.16 (ii) The evolution of the values of unschedulable traffic flows for the mapping of a random                                                                                          |

| application comprising of 30 tasks and 40 traffic flows with an overall task utilization of 8 on a NoC platform of                                                                               |

| size 4x4                                                                                                                                                                                         |

| Figure 5.16 (iii) The total sum of the route length over all traffic flows per generation of the genetic                                                                                         |

| algorithm, values recorded for the mapping of a random application comprising of 30 tasks and 35 traffic flows                                                                                   |

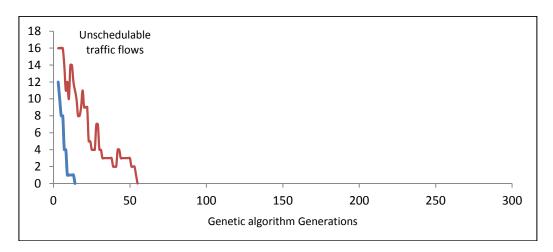

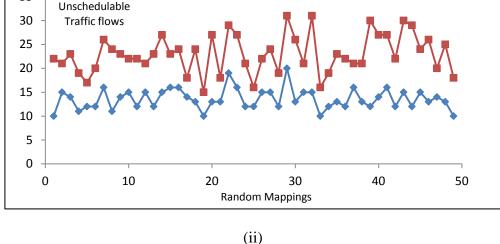

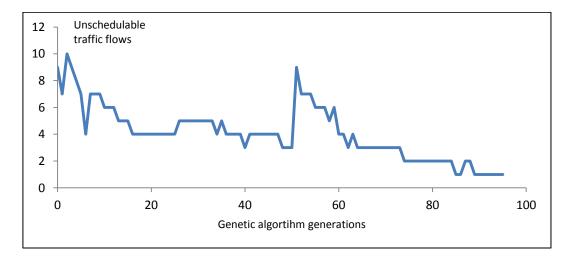

| Figure 5.17 (i) The evolution of the values of unschedulable traffic flows for the mapping of a random                                                                                           |

| application comprising of 30 tasks and 40 traffic flows with an overall task utilization of 8 on a NoC platform of                                                                               |

| size 4x479                                                                                                                                                                                       |

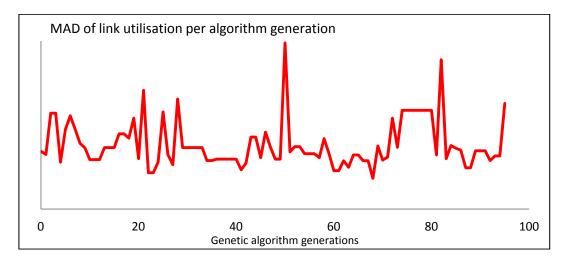

| Figure 5.17 (ii) The evolution of the values of the mean absolute deviation of the network link utilisation                                                                                      |

|                                                                                                                                                                                                  |

| versus the genetic algorithm generations for the mapping of a random application comprising of 30 tasks and 40 traffic flows with an overall task utilization of 8 on a NoC platform of size 4x4 |

| Figure 5.17 (iii) The total sum of the route length over all traffic flows per generation of the genetic algorithm values recorded for the mapping of a random application comprising of 30 tasks and 50 traffic flows with an overall task utilization of 8 on a NoC platform of 4x4 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

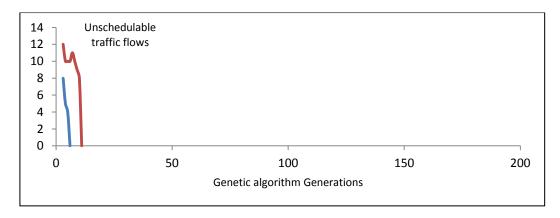

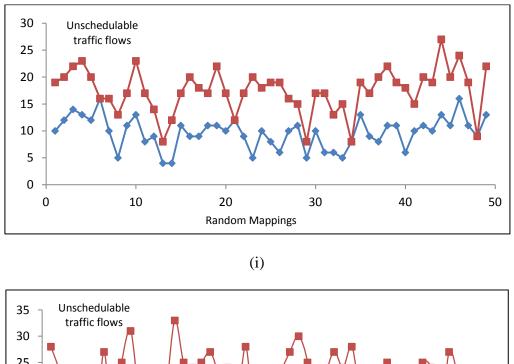

| Figure 5.18 (i) The evolution of the values of unschedulable traffic flows for the mapping of a random                                                                                                                                                                                |    |

| application comprising of 30 tasks and 50 traffic flows with an overall task utilization of 8 on a NoC platform size 4x4                                                                                                                                                              |    |

| Figure 5.18 (ii) The evolution of the values of the mean absolute deviation of the network link utilisation versu                                                                                                                                                                     | 1S |

| the genetic algorithm generations for the mapping of a random application comprising of 30 tasks and 50 traff                                                                                                                                                                         | ïc |

| flows with an overall task utilization of 8 on a NoC platform of size 4x4                                                                                                                                                                                                             | 80 |

| Figure 5.18 (iii) The evolution of the values of the mean absolute deviation of the network link utilisation vers                                                                                                                                                                     | us |

| the genetic algorithm generations for the mapping of a random application comprising of 30 tasks and 50 traff                                                                                                                                                                         | ïc |

| flows with an overall task utilization of 8 on a NoC platform of size 4x4                                                                                                                                                                                                             | 80 |

| Figure 5.18 (iv) The total sum of the route length over all traffic flows per generation of the genetic                                                                                                                                                                               |    |

| algorithm, values recorded for the mapping of a random application comprising of 30 tasks and 50 traffic                                                                                                                                                                              |    |

| flows with an overall task utilization of 8 on a NoC platform of size 4x4                                                                                                                                                                                                             | 80 |

# Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text.

Paris Mesidis

## Chapter 1

#### Introduction

#### 1.1 Introduction to NoC Systems and the Mapping Problem

Multiprocessor Systems-on-Chip (MPSoC) are SoC made of multiple processing elements (PEs). MPSoC is a relatively new technique and a new trend in VLSI design that has been made possible due to the advancements in IC technology. The primary advantages of SoC devices are lower costs, greatly decreased size, reduced power consumption and the ability to meet the increasing performance requirements of complex concurrent applications (real-time video, communications, control etc.). Such applications are inherently parallel and should take advantage of any available parallelism. As the computational demands of such applications increase they will no longer be supported as efficiently by single general purpose processors. Since MPSoC are SoC with multiple processing elements a communication infrastructure has to interconnect the PEs. Traditional on chip communication schemes such as buses could be used for MPSoC that consist of a few elements but as the number of PEs that can be integrated on such a system increases, due to advances in silicon technology, these communication schemes will not be able to scale well and issues like the power consumption of the system will impose limitations. So there is a need of a scalable communication infrastructure and a promising solution is found in the use of networks on chip (NoC). Network(s)-on-Chip (NoC) have emerged as a design that incorporates on-chip communication architectures that are scalable and provide a more efficient structure and better modularity than its predecessors [1, 2].

MPSoC may employ NoCs to integrate many different components such as multiple programmable processor cores of various types, specialized memories, and other intellectual property blocks (IPs) in a scalable way, giving rise to heterogeneous systems, alternatively the integrated components may be all similar resulting in homogeneous systems. Heterogeneous systems achieve better performance and lower power consumption because of the application specific components; this comes at the cost of reduced flexibility and reusability. Homogeneous architectures are more flexible and also more open to different techniques such as run time reconfiguration, task migration and fault tolerance because of their functional redundancy.

An important aspect of MPSoC design is the optimisation of the system so that the platform is fully utilized the advantages of MPSoCs. Given specific applications that can be subdivided into a set of tasks, that can be concurrent and communicating with each other, it is necessary to control task operation and system resources usage in order to better utilise the system. The mapping of the application tasks onto the PEs of the system consists of finding a placement for a set of tasks so that some specific requirements are met. The performance of a NoC system running such a highly parallel application is also communication-dependent and depends on task mapping in many ways such as overall execution time, energy consumption, packet latency, communication channel load, bandwidth reservation, and congestion levels; The mapping problem for NoC is to decide how to place the selected set of tasks onto the PEs of the network such that the metrics of interest are optimized.

In NoC architectures each processing element is connected to a router which is the actual interface to the rest of the network. Each router's work is to implement a routing policy by

accepting and forwarding each incoming packet, the architecture of the router depends on the switching policy which determines the manner that the packets are forwarded through the network so that the traffic flows can share the communication resources.

Figure 1.1 A 4x4 NoC

Applications running on MPSoC typically execute a varying number of tasks simultaneously, however at some point the number of tasks may exceed the available resources, requiring task mapping to be executed at runtime; more specifically the need to execute a new task may occur at run-time and with the current configuration the resources may be inadequate (paths connecting to master PE overloaded) so a remapping of some or all of the tasks may be necessary; in a simpler case a new task will have to be mapped somewhere on the available resources so that it's placement is optimal according to some criteria. Efficient solutions have been proposed for static mapping, static mapping defines a fixed placement and scheduling before the application is run where the application and its task set are known at design time. For this case approaches are used that can find better solutions since the time spent for finding such a solution at design time is not so important but obviously it is not appropriate for dynamic workloads.

The performance metrics mentioned above can usually be described in relation to the relative task placement so the task mapping problem, where the goal is to minimise some of these metrics, becomes similar to some well known NP-hard optimisation problems such as the quadratic assignment problem [3], [106] which is an especially hard instance of this class of problems [107] meaning that an algorithm that can solve this problem in polynomial time is unlikely to exist. The relation between different performance metrics is not always straight forward; a solution that optimises one may have adverse effects on another.

When formulating the mapping problem some properties of the system and underlying platform architecture must be known. These properties are also part of the assumptions in the problem definition, and hence they would affect the problem's complexity e.g. the ability for the PE's to execute more than one task. Additional properties such as the routing and switching policies of the network infrastructure would also play an important role in the way the problem is defined, and they could enable some analytical models that would help compute some of the metrics of interest; for example knowing the bandwidth capacity of a

system's communication links and that the specific routing algorithm is deterministic could give some deterministic bounds for communication delay and throughput, however more information would be required because this model does not take into consideration the delays due to contention of the shared network resources, this in turn could be modelled only by knowing the arbitration strategy of the system. A different approach would be to use some algorithm or policy based on intuition or some partial formulation (small subset) of the problem and use simulation to verify it, the feasibility of this approach would depend on the quality of the solution required and the determinism of the output.

The mapping procedure in any such system, affects many different parameters that may be conflicting, so for a system with real-time requirements (hard, soft) a mapping that would avoid task's and communication's deadline misses would be ideal, typically however such applications are found in the embedded systems domain where power consumption is an important issue as well, so a solution that satisfies both requirements becomes harder to find. Additionally in such a system, especially if the mapping takes place dynamically, the running time of the mapping algorithm itself could have a significant impact on the overall temporal behaviour of the system.

Next another important aspect of the problem solution is the way each solution proposed by a mapping algorithm is actually evaluated, this is typically done using an analytical model and in that case an accurate model is important, for example many mapping algorithms seem to use the average packet hop count (moves to adjacent routers) as a function that determines the power dissipated for communication and also the communication time cost, however packets may usually be queued in a congested system and have to reside somewhere for some time (which with smaller transistor sizes is power consuming as well) so hop count is not necessarily always a good measure. Alternatively simulation can be used to evaluate a solutions quality at the cost of speed. The inputs to the mapping problem, which are an application and a NoC platform have to be abstracted away because they are typically very complex objects however these abstractions must be at a level that all necessary information is included while the overall input is concise. For example the representation of an application through an application task graph is a sufficient way as it conveys all the important information for an application that the mapping algorithm needs to know such as communication/control dependencies and communication volume, any further constraints that need to be considered such as task deadlines, channel bandwidth etc. can be added as additional variables to the mapping problem. Mapping as explained above is an important aspect of the design as it may drastically influence the system performance. Many approaches and algorithms have been proposed in literature for the mapping problem based on different assumptions and trying to optimise different aspects of a system (e.g. energy-aware, congestion-aware), the quality of such algorithms would be measured in relation to their execution times and overall optimisation of the system also how well they can perform in various scenarios and how well they meet certain constraints of the system (real-time, bandwidth).

However testing such algorithms is not always easy because testing in the context of real applications is not flexible or otherwise would be very time consuming. Synthetic models can be used that model traffic and computation loads according to different classes of applications with worst case bounds or alternatively simulation based approaches with some well known applications since specific benchmarks have not yet been defined for those aspects of NoC design. The aim of this work is to review the existing literature relevant to the mapping problem and then examine this problem from a real-time system perspective where the timing aspects of a system are the most important.

#### 1.2 Problem Formulation

The mapping problem can be generally described as the problem of finding a topological placement of the application tasks onto the PEs of the system so that the metrics of interest are optimised. For an application that is partitioned into n tasks the problem of mapping those tasks on a network on chip with n processing elements would have n! possible solutions, the solution space factorially increases with the problem size so it is infeasible to exhaustively search it. The topological mapping of the application onto the NoC platform would obviously have an impact on the energy spent on the communication between the tasks and the communications latency as they are a function of the distance between the tasks. In some application domains, the communication volume between tasks can be very large and may be using the entire network link bandwidth; in this case a mapping that maps the tasks in a way so that the traffic on the network links does not exceed the bandwidth capacity of the network may be necessary. According to what metric the mapping problem is trying to optimise, the problem can be formulated differently, however most commonly the metrics and variables that formulate the problem are functions of distance and mapping becomes an instance of the NP-hard quadratic assignment problem [3]. This is the case when using the energy consumed on communication as a cost metric, as it is proportional to the distances between the communicating cores, also on such systems (NoCs) the energy spent on communication is a significant amount making it a popular metric in the relevant literature. The energy-aware formulation of the problem is described below to demonstrate a form that the problem may generally take.

The mapping problem in this case can be described as: For a set of communicating tasks where the communications and their volumes between them are known (described by a directed weighted graph G(T, C) and a set of cores with their positions on the network N(P, L) find a mapping function that maps tasks to cores  $f: T \to P$  so that:

Min

$$\{\sum_{\forall c,i,j} (c_i, c_j) * \frac{E}{bit} * (f(T_i), f(T_j))\}$$

(1)

Explaining the terms in the equation above:

- (c<sub>i</sub>, c<sub>j</sub>) A pair of communicating tasks

- $\frac{E}{bit}$  The energy that the system spends to communicate a bit per unit distance.

- (f(Ti), f(Tj)) The distance between the communicating tasks as a result of the mapping function f.

It can be seen that the goal is to minimise the sum of products between a cost function and weights. In this case the cost function is the energy that is consumed for a bit to travel unit distance (between adjacent routers) and the weights are the communication volume and the distance between two communicating tasks. Additional constraints may be added to the problem because of features of the platform architecture or the application. For example the problem above could have some additional constraints as it does in [4]:

$$\forall T_i \neq T_j, f(T_i) \neq f(T_j)$$

(2)

$$Bw(link) \ge \sum_{\forall Flow \ i,j} Bw(Flow \ i,j) * f(link, R \ i,j)$$

(3)

Where  $R_{i,j}$  is the set of links that make the route between i and j.

$$f(link, R_{i,j}) = \begin{cases} 1 & \text{if } link \in R_{i,j} \\ 0 & \text{otherwise} \end{cases}$$

(4)

The first constraint means that each processing core can only have one task running on it, which is a platform specific feature. The second constraint demands that the aggregated communication traffic on any link does not exceed the available bandwidth so that all the communication flows can be serviced. Any additional constraints may be added to the problem. In the case described above the goal of the problem is to minimise the quantity in (1) which depends on the distance the traffic has to traverse. This distance in turn depends on the path the packet has to traverse through the network which is determined by the system's routing algorithm. Because of this close relation, many authors have treated the topological mapping and path selection/ routing as one problem [4], [5]. In many instances it is suitable for NoCs to use deterministic minimal routing algorithms, because it becomes easy to calculate the path and distance of a specific traffic flow, and it also becomes possible to calculate the quantity in (1).

Whether there exists an accurate analytical model for this metric depends on how these features are implemented in this system. Finding good analytical models for different metrics in such systems is regarded as a difficult problem as well [6].

#### 1.3 Goals and Objectives

The main objective and scope of this work is to study the application mapping problem specifically from a distributed real-time systems perspective. In such systems the communications between real time tasks must complete within bounded time as well to ensure the correctness of the system, this is necessary as these communications contain data that the receiving tasks will need to operate on within bounded time. As a result this work will study the effects of task placement on both the timeliness of communication and computation in such systems. In order to do so it will be necessary to study solutions to this problem already proposed in a broader set of domains apart from real-time systems and also see what platforms and tools can be applied in this specific instance of the problem. Next utilising this knowledge we will be in a position to propose a solution to the problem based on evolutionary algorithms and finally evaluate it by producing experimental results and conclusions using an appropriate framework.

## Chapter 2

## Network on Chip Platforms

This chapter aims to provide a brief description of Network On Chip platforms by explaining some of the most important architectural characteristics and by giving an overview of the typical communication protocol stack. Next follows a review of current NoC platforms with regard to predictability, a concept central to real-time system analysis, and finally a review of methods which can be used to model such a system.

#### 2.1 System Architectures and Modelling

The advancement in microchip technologies has enabled many components to be integrated together and form large scale systems-on-chip (SoC). Typically the on-chip communication between the components of such systems has been bus-based or a mixture of buses and point-to point links. Communication on chips with few components ought to be fast and reliable while the computation aspect is usually is the performance limiting factor. With the technology scaling down and by adding more components onto a single chip this changes; while resources for computation (PEs, memory) mainly benefit from scaling down the communication infrastructure does not. In a highly interconnected multi core system the energy required for communication does not scale down well, the power consumed to drive the wires increases (wire resistance increases) and physical parameters of the wires become unpredictable because it becomes harder to produce uniform structures, thus in future deep submicron (DSM) designs, the interconnect medium will definitely affect performance [14]. In addition noise from crosstalk, delay variations and synchronisation failures between large numbers of components may cause transmission failures. As a result estimating delays accurately will become increasingly harder, and the transmission will be power consuming and inherently unreliable. For maximum flexibility and scalability, it is generally accepted that a move towards a shared, segmented global communication structure is needed [15]. This motivation led into a new approach which is a data-routing network that consists of communication links and routing nodes built on the chip, hence the name network on chip. Similar to macro network communication, the network on chip approach tries to provide scalability, performance and reliability as well as modularity. At the same time however networks on chip must exhibit less non determinism while having tight resource constraints (e.g. energy, area).

#### 2.2 Network on Chip Features

NoCs are packet switched multi hop networks. The processing elements access the network using point to point connections to the interface, and their packets are forwarded to their destinations by hoping through a number of routers. One of the basic characteristics of NoC is the topology which determines the layout and connectivity of the on chip components. Most NoCs implement regular network topologies that can be laid out on a 2D chip surface. These topologies are known as grid-based topologies. Torus, tree and irregular structures have also been proposed that may exploit different characteristics of the applications traffic patterns such as locality of traffic [36]; however mesh based topologies

are the most compatible in terms of simple routing algorithms, re-usability and scalability hence the most commonly used.

Figure 2.1 A 2D mesh based NoC.

Figure 2.2 Regular (a) and irregular (b) NoC topologies.

Networks on Chip can be designed in different ways, based on the network architecture and communication protocol used. Networks on chip can also be designed and described by using a layered model as it is done in macro networks, but in a much simpler fashion. The NoC design phase would involve designing a system specific architecture and a communication protocol/infrastructure that will be compliant with this architecture; hence according to these design decisions a protocol stack can be defined as in [1]. In macro networks the abstractions offered by the layered protocol allow communication between different systems. Networks on chip have the advantage that the system is composed from static elements so the communication protocol becomes simpler based only on the attributes of the specific system. Overall the network characteristics such as the communication mechanism, switching mode, and routing algorithm depend on the network topology and together they define the services provided by the NoC.

#### 2.3 Network Layers

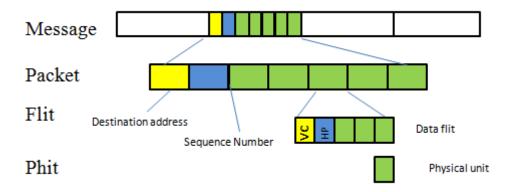

The lowest level in a typical communication stack is the physical layer where specific signalling techniques are implemented to provide the most fundamental service of lossless data transmission through the links; according to the signalling technique (encoding, synchronization) and the physical properties of the communication links a trade off between energy consumption and transmission errors is achieved; based on the specific signalling technique the energy spend on transmitting data can be calculated. At this level, the basic unit of data is a *phit* (physical unit), which is the minimum datagram of the system and the building block of packets and streams.

The layer above the physical layer would be the data link layer. The main role of this layer is to improve the reliability of the physical layer so that the system can operate at the required level. This can be done at the expense of energy and system complexity using error detection and correction protocols. The data link layer would also have to implement a policy that resolves contention between different traffic flows for the network resources (arbitration policy) so that no errors occur from simultaneously accessing the network. The layer above the data link layer, the network layer is responsible for end to end delivery of messages, in such a complex network which is composed of many links this layer has to address both the way the data will be transported through the network or in other words how the connection and transmission occurs between successive links and how routes are chosen between the source and destination of the data sent. The tasks mentioned above are those of switching and routing of data. The network interface (NI) decouples the processing core's functionality from the network and provides a well defined interface to the network layer.

The two main switching techniques are circuit and packet switching. In the case of circuit switching a path from the source to the destination of data is reserved prior to the transmission for the duration of the data transmission and is accessible only by this set of data; in this case there is no need for the data to be packetized. Circuit switching, however, is very inefficient in terms of link capacity utilisation and set-up latency unless used for long infrequent messages.

Packet switching overcomes the limitations of circuit switching by using packetized traffic. The data to be transmitted is divided into packets that also contain routing information. Typically the whole packets are buffered at each intermediate node before they are forwarded to the next (store-and forward); packet switching offers much higher utilization of the network resources and higher flexibility (production rates, arbitration schemes, out-of-order delivery) with respect to circuit switching, at the price of an increase in non-determinism and silicon area (switches, buffers) as each packet may experience queuing delays (residing on buffers). The disadvantage in the case of packet switching is the buffer space requirements, specifically flow control techniques that govern the way the packets use the buffering resources deal with this limitation. In order to overcome this limitation packet switching is further improved by using different flow control techniques as in cut-through switching. With this technique each packet can start leaving the switch on which it resides before the entire packet is present (received by the switch) hence reducing the buffer size requirements. In this way, however, the total resources a packet will occupy increase as it may occupy many switches at once. In the case where a packet is blocked, waiting on resources, it will occupy many resources itself which may cause other packets to block so the overall blocking caused by a packet's transmission increases hence the overall variance in traffic response times increases [1].

A further improvement on packet switching is achieved by wormhole switching; in this scheme each packet is divided into flow control *units* (*flits*) which are fixed size segments. Each packet has a header flit which traverses first and reserves a channel on each switch; the remaining flits will have the same route information as the header flit. Wormhole flow control works at the flit level and because it further divides packets into smaller chunks it reduces the required buffer spaces and the store and forward delay on each switch. Unfortunately the side effect of blocking in cut-through switching becomes even greater in wormhole switching as a stalled packet may occupy all the switches it spans (same as the number of flits).

This effect can be overcome by using resource sharing techniques like virtual channels. Virtual channels is a flow control method where many logical channels may be implemented sharing a single physical channel. This is achieved by having separate buffers for each logical channel. Hence with an overhead in silicon area and power more packets may share the network resources simultaneously which allows wormhole switching to become much more efficient. The number of virtual channels used is a design option based on the amount of traffic that needs to be supported. In such systems there is also the need to have a flow control mechanism that regulates the amount of traffic sent so that a receiver is not overwhelmed; in the case of wormhole switching this can be implemented using a credit based approach which can guarantee that data is only forwarded from a router to the next when there's enough buffer space to hold it otherwise it is blocked and may reside at the current VC buffer until space at the next hop node is available.

$\label{eq:continuous_problem} \textbf{Figure 2.3 Implementation of VC using multiple buffers.}$

Figure 2.4 Message sub-components for transmission on a wormhole based NoC.

The task of routing in the context of NoCs is that of determining the path of a message travelling from a source PE to destination PE. For this purpose many routing algorithms have been developed. Routing algorithms can be either deterministic or adaptive. Typically a routing algorithm would have a source and a destination core as inputs and it would produce a path between them. A deterministic algorithm will always produce the same path for the same inputs while the adaptive algorithm will take into account dynamic aspects of the system like congestion and silicon faults and may produce different paths each time in order to improve performance; another class of algorithms is the *flexible* routing algorithms, these algorithms are restricted to using only a subset of the network links from which they may choose a path according to some criteria. Because of the additional resources that adaptive algorithms would require (silicon area for more complex routers and energy to drive them) and the additional non-determinism they would introduce, they are not regarded a very suitable solution for NoCs (a comparison in [30]) and especially for systems with strict timing requirements. Most systems presented in literature use forms of source routing where the path of a packet is known before it is transmitted and each packet carries this information with it allowing for each network node to send it towards the right direction, this decision at every node does not require much logic if the routing scheme is simple.

Some properties of routing algorithms that are usually desirable for NoCs are minimality and freedom from deadlock and live lock, conditions caused by circular dependencies. The prominent strategy for avoiding deadlocks caused by routing paths in NoCs is by using certain routing algorithms which have the property that they do not produce paths that can cause a deadlock; deadlock is caused by cyclic dependencies on shared resources which in a network are the physical channels, the virtual channel scheme overcomes these dependencies by providing multiple channels [83] so different packets contend only for the network links. Minimal routing algorithms always produce a path that is of minimum hop distance between source and destination, this property is desirable in NoCs as many performance and cost metrics are proportional to the communication distance. For a detailed review and comparison of different NoC designs we refer the reader to [15].

Figure 2.5 Protocol stack for a wormhole based NoC.

### 2.4 Predictable Communication on Network on Chip platforms

The aspect of predictability is crucial from the perspective of real-time systems. In the packet switched schemes mentioned above packets still contend for shared resources such as the physical links (router output ports) of the network; this contention is the reason for the unpredictability of the network traffic, it can be resolved in many different ways providing flexibility and differentiated services, for example it can be done in a simple FIFO manner [30], where no distinction needs to be made between packets from different traffic flows or it can be based on time division multiplexing [32] where specific traffic flows can be assigned different time slices so that they never contend for the network links. Using this method traffic flows can have a guaranteed bandwidth and latency. A case where both of these schemes exist together on the same platform is that of the AEthereal network on chip [32], this system offers two classes of communication services that use the same infrastructure: guaranteed service (GS) where the communication flows have reserved time slots (TDM arbitration) and best-effort (BE) where the traffic flows use the unreserved time slots using FIFO arbitration; obviously in the later case no guarantees can be provided.

The TDM approach described earlier is characterized by resource reservation where traffic flows must set up paths on the network and reserve resources (time slots) at each node; this can be thought of as a virtual circuit implemented on top of a packet switched network. The advantage of such a scheme is that it can provide deterministic bounds for traffic parameters (latency, bandwidth) however this determinism comes at the cost of poor utilisation (especially for variable rate traffic) and runtime inflexibility furthermore TDM requires a highly synchronous system whereas NoC designs tend towards a GALS approach. A similar arbitration scheme is introduced in [31] which can overcome the limitations of the TDM approach but still providing bandwidth guarantees. This arbitration mechanism is again based on a virtual circuit scheme; each GS flow reserves a virtual channel on every node of the virtual circuit it establishes, then the access of all virtual channel buffers to the link is served at an equal rate, as a result the bandwidth guarantee for a GS flow will be the service rate of the reserved virtual channel (e.g. for 8 traffic flows it will be 1/8 of the total link bandwidth) [31]. This design together with credit based flow control is used in an asynchronous NoC design called MANGO. Other platforms use methods that do not fully utilise the packet switching capabilities of the NoC architecture but are still able to provide GS traffic and QoS guarantees, such a case is the Nostrum NoC [71] that sets up a form of virtual circuit for different nodes to communicate; the authors in [75] also propose a circuit switched communication network (SoCBUS) to provide hard real-time guarantees.

Another approach is priority based arbitration [34] [35] where higher priority packets may pre-empt lower priority ones accessing communication resources. Such an approach can provide guaranteed throughput to high priority traffic flows in a more efficient way as it does not reserve resources like the virtual circuit scheme does and can even allow analysis that estimates worst case end to end packet latency [33] which is suitable for hard real time systems. In the case where all traffic flows are equally important it may be hard to determine different priorities; furthermore for the relevant analysis to be applicable the system must again be static with fixed traffic and routes, a scheme similar to virtual circuit connections, even so it will be easier for system to reconfigure itself without suffering the penalty of virtual circuit set up times. In general the priority arbitration scheme seems to be much more flexible; both approaches however are able to provide the desired determinism for timecritical traffic flows. A comparison between the two schemes takes place in [67]. The priority arbitration scheme can also implement flow control techniques which improve the quality of service by using dynamic priorities as done in [74], improving the QoS cannot offer hard guarantees but can increase the performance in soft real-time systems. The QoS that a NoC platform can offer can be expressed with various parameters like availability, jitter, packet loss, and throughput.

One of the main challenges in the design of such a NoC system is the way the network resources are allocated such that the hard temporal requirements of GS traffic are satisfied while the system is not underutilised and the reserved resources are actually used. An approach trying to improve the overall utilisation of the NoC resources is used in the Aethereal NoC; this approach combines both GS and BE traffic flows where BE flows use the network resources when the GS flows are idle to avoid the low utilization, furthermore the BE traffic does not use the virtual circuit scheme so it is more flexible. The low utilization occurs because in real-time systems the resources are always reserved according to worst-case scenarios. Similarly in a priority based system packets with low priority and without hard deadlines may try and use the NoC along with higher priority packets as they will not affect their transmission.

#### 2.5 Network on Chip Modelling

An important step in the SoC design process is the modelling of the system, it is necessary as it helps the exploration of the design space as through modelling it is possible to evaluate various design trade-offs, it is also a means of evaluating a system in terms of performance and also validating the system in terms of requirements and constraints. A good model is also essential for evaluating the performance and cost trade-offs of different mappings. Modelling of complex MPSoCs and NoCs can be either analytical or simulation based, considering that simulation can happen at various levels of abstraction an analytical model is usually needed to abstract away the details of the lower levels.

A way to define different abstraction levels is based on time granularity. Finer time granularity implies lower levels of abstraction (more detailed) as it describes events that occur at smaller time periods hence given a certain duration it describes more states of the system. Using the clock cycle of the computation and communication components as a point of reference abstraction levels can be defined starting from cycle-accurate register transfer level or instruction set simulation level.

Running simulations at this level of abstraction is very time consuming as incorporating this level of detail for a large system would be computationally intensive, but it provides good accuracy in terms of the system behaviour. An RTL cycle- accurate model is used in

[37] in order to evaluate the power and delay in a NoC. Power and delay are first evaluated for even smaller components that make up the RTL components using circuit-physical level simulations and are then incorporated into the RTL blocks making the simulation even more accurate at the expense of running time.

Simulation at this level can be achieved using hardware description tools such as VHDL. An advantage of this level of simulation/modelling is that by incorporating monitors into the system design it becomes easy to obtain accurate figures for metrics that would otherwise be hard to measure (e.g. packet latency). At the other end models that abstract all the implementation details to the system level can be used of course at the cost of accuracy, such an abstract software model is implemented in [39] which models both a NoC and an RTOS managing its resources at system level, this model [40] aids in exploring the design space through different task mappings, RTOS policies and NoC protocols, using the calculated network latency (inaccurate) as a metric for the network performance.

Because of the particular complexity of NoCs, the simulation times at this accurate level are increasingly higher, so alternative solutions have been proposed such as FPGA-based emulation [40]. In such systems where communication between components is largely present it can be abstracted separately from computation in different levels according to which aspect needs to be simulated accurately and also which of the two aspects can be accurately described at higher levels of abstraction in order to speed up simulation time. A concept that works on this idea is that of transaction level models [41]. The basic characteristic of transaction level models is that they abstract away low-level details of the communication and model it as large granularity data transfers. This is done using the concept of channels to model communication where the transactions between computation elements take place through calls to the interface functions of the channels. Transaction level models use three degrees of time accuracy for both computation and communication and different abstraction levels are generated by possible combinations, the three degrees of time accuracy used are untimed, approximate-timed, and cycle-timed.

Cycle-timed computation/communication contains implementation and architecture details at all levels down to the register transfer level, a level that allows cycle-accurate estimation.

Approximate-timed computation/communication contains system-level implementation details and is the level that corresponds to the transaction level for communication; finally the un-timed computation/communication contains only the functionality of the system hiding away all the implementation details. The different abstraction levels can aid at different stages of the design flow in various systems however the more complicated the system architecture the greater the loss of accuracy of these models hence the ability of a TLM to accurately model systems depends on the system communication architecture/ protocols and the time granularity the model used. TLM has been successfully applied to NoC modelling [42], [43] giving significant improvements in simulation time and a small loss in accuracy. In [44] an approximate-timed TLM model of a network-on-chip using wormhole switching with priority pre-emptive virtual channel arbitration is proposed in order to reduce the simulation time and to obtain accurate packet latency figures, the time granularity instead of every clock cycle is the time instants when packets enter or exit the NoC nodes, experimental results showed that this approach achieved a significant speed-up (three orders of magnitude) with a small loss of accuracy (90%) compared to a cycle accurate simulation of the same system. A potentially useful application of this approach would be in cases where only the communication aspect of a design needs to be accurately simulated and the computation can be abstracted away in order to speed up simulation time.

#### 2.6 Summary

This chapter demonstrated some of the distinguishing characteristics of NoC platforms; also it provided a brief introduction to the different architectural variants that can be used each with different costs and benefits. Of specific interest are the different approaches used to provide predictable communications, reviewing the qualities of each aids this work with focusing on a platform type that will be more suitable to the achieve the desired result.

## Chapter 3

## Real – time Applications and Relevant Models

The goal of this chapter is to provide an overview of the real –time systems domain both from a soft and hard real-time perspective. It is necessary to clarify the requirements present in such systems so that they can then be related to the aspects of the mapping problem that we are trying to solve. Furthermore in this chapter models and tools that can be used to analyse the properties of interest for these systems are introduced.

#### 3.1 Application Domains

This research is mainly interested in reviewing the application mapping problem from a real-time system point of view; in real – time systems the correctness of a system does not only depend on it producing the correct results but also on the time it takes to produce them, so we are generally concerned about applications with real time requirements. An important distinction in real time systems is that of hard and soft real time systems. Soft real time applications are present in many areas such as multimedia and distributed and/or high performance computing, such systems are subject to temporal constraints however for these applications it is acceptable for some traffic to not be serviced correctly as long as the overall throughput maintains a certain level (quality of service). No absolute guarantee for the temporal behaviour of such systems is required, yet performance must be at a certain level on average. This allows the requirements to be expressed using statistical measures. Because of this flexibility such systems are termed as soft real-time.

Other types of applications, such as those found in the hard real-time domain, are not as flexible and require all computational tasks to meet their deadlines at all times [87]. In such a system the temporal requirements are expressed explicitly with deadlines. In general hard-real time systems cannot tolerate any deadline misses the occurrence of which may be catastrophic, for this reason all the aspects of the system need to be taken into consideration at design time so that guarantees may be provided; because of this inflexibility in such systems dynamic behaviour is undesirable unless it can be modelled as a state of the system that can be analysed at design time.

For streaming applications which are very common in various consumer systems the number of different modes that the system has to support is steadily increasing. These modes of operation could be either different combinations of a number of independent applications running on the same platform or various versions of an application's sub-systems where each may offer different services; for example in a video processing application different codec's could be used allowing for a trade-off between the quality of the image and the stream bit rate; we could treat those different scenarios as separate use cases. Each different use case will clearly have different requirements in terms of computation, storage and communication. In such an application the temporal requirements may be expressed in various terms such as throughput and end to end latency.

#### 3.2 Application Modelling

This section aims to list the ways that an application that consists of communicating concurrent tasks can be modelled so that it can be mapped on to a multiprocessor system. An important aspect of the mapping problem is the way the applications are modelled. Having an accurate model that conveys information about an application can either allow exploiting this information to reach a better solution quicker or can help validate solution reasoning about the application behaviour under different circumstances. By modelling an application the goal is to abstract the application's functionality regardless of implementation details by simplifying the information that is given about the task set, hence abstract it to a level so that only the information relevant to the problem at hand (mapping) is displayed. Applications that are likely to benefit from networks on chip are complex inherently parallel applications with many communicating subsystems and high computing power requirements mainly because their constraints on power consumption and size can be better met by on chip communication. A concurrent application or system in general is a set of interacting components and can be described by a concurrent model of computation, where this model would be the set of rules that determine the interaction between these components. A component of such a set could be a task, where a task could be defined as a computation that is executed by a processor in a sequential fashion. The use of a model of computation can help design an application and also describe and abstract an existing one. Many computational models have been introduced that describe computational systems e.g. Turing machines and finite state machines, however the need to efficiently exploit task level parallelism demands a concurrent model of computation that can model the dynamic aspects and the concurrent behaviour of the modelled applications. Such models of computation need to describe a concurrent system at such a level so that the non-determinism is minimized by taking into consideration all of the dynamical aspects.

#### 3.3 Concurrent Models of Computation

A distinction between concurrent models of computation can occur by the way they represent time and by whether the system is synchronous or asynchronous. A system's state or behaviour with respect to time can be determined at different granularity (continuous time/discrete time/ untimed). In timed models time is a reference against which all computation can be defined and measured where in untimed models there is only the notion of a logical sequence, in general there is a certain ordering of actions to ensure data precedences and causality but actions can also occur in parallel. Precedences and dependencies can be defined for each system through a concurrent MoC but are also interpreted differently according to it. The notion of the synchronous/asynchronous model has the typical meaning of a synchronous system where the concurrent tasks are synchronized centrally by a fixed rate clock while in asynchronous system the concurrent tasks synchronize through communication/events.

Concurrent models of computation give a set of rules that describe the interaction of communicating tasks. Those models can be represented in various ways, for example in the model of finite state machines, the behaviour of tasks can be described by state transition rules based on inputs for each individual task-machine (e.g. FSM composite model), multiple concurrent tasks may be executing independently or they can be interacting together asynchronously, in which case sets of state sequences (one set per task) can describe a certain system routine [7].

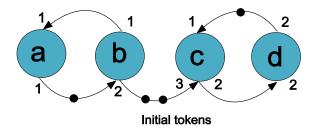

However such state-based models cannot explicitly express the rules of concurrency. A similar model is Petri-nets [8], in Petri-nets a computation can be modelled as a set of places/states and a transition between places, the system is also token based where tokens can move from one place to another when a state transition happens (fires). In turn a transition fires when there are enough tokens in its input place, since there can be many tokens Petrinets can model concurrency, and on a higher level tokens can represent different inputs (amount of data, control, external stimuli) again in an asynchronous untimed manner. These models can help with analysing the reachability and determinism of a task set however they do not incorporate information about execution times.