## **Social Insect-Inspired Adaptive Hardware**

Matthew Rowlings

Ph.D.

University of York

Electronic Engineering

September 2018

## Abstract

Modern VLSI transistor densities allow large systems to be implemented within a single chip. As technologies get smaller, fundamental limits of silicon devices are reached resulting in lower design yields and post-deployment failures. Many-core systems provide a platform for leveraging the computing resource on offer by deep sub-micron technologies and also offer high-level capabilities for mitigating the issues with small feature sizes. However, designing for many-core systems that can adapt to in-field failures and operation variability requires an extremely large multi-objective optimisation space. When a many-core reaches the size supported by the densities of modern technologies (thousands of processing cores), finding design solutions in this problem space becomes extremely difficult.

Many biological systems show properties that are adaptive and scalable. This thesis proposes a self-optimising and adaptive, yet scalable, design approach for manycore based on the emergent behaviours of social-insect colonies. In these colonies there are many thousands of individuals with low intelligence who contribute, without any centralised control, to complete a wide range of tasks to build and maintain the colony. The experiments presented translate biological models of social-insect intelligence into simple embedded intelligence circuits. These circuits sense low-level system events and use this manage the parameters of the many-core's Network-on-Chip (NoC) during runtime.

Centurion, a 128-node many-core, was created to investigate these models at large scale in hardware. The results show that, by monitoring a small number of signals within each NoC router, task allocation emerges from the social-insect intelligence models that can self-configure to support representative applications. It is demonstrated that emergent task allocation supports fault tolerance with no extra hardware overhead. The response-threshold decision making circuitry uses a negligible amount of hardware resources relative to the size of the many-core and is an ideal technology for implementing embedded intelligence for system runtime management of large-complexity single-chip systems.

## Contents

| A  | bstrac   | et      |                                            | 2  |

|----|----------|---------|--------------------------------------------|----|

| C  | onten    | ts      |                                            | 3  |

| Li | ist of l | Figures |                                            | 9  |

| Li | ist of [ | Fables  |                                            | 13 |

| A  | cknow    | vledgem | ients                                      | 14 |

| D  | eclara   | tion    |                                            | 15 |

| 1  | Intr     | oductio | 'n                                         | 16 |

|    | 1.1      | Overv   | iew                                        | 17 |

|    |          | 1.1.1   | Many-Core Systems                          | 18 |

|    |          | 1.1.2   | Many-Core Design Challenges                | 18 |

|    |          | 1.1.3   | Bio-Inspired Hardware                      | 20 |

|    |          | 1.1.4   | Social Insect Intelligence                 | 20 |

|    | 1.2      | Hypot   | heses                                      | 23 |

|    | 1.3      | Resear  | rch Contributions                          | 24 |

|    | 1.4      | Thesis  | Structure                                  | 24 |

| 2  | Cha      | llenges | of Large Scale VLSI Design                 | 26 |

|    | 2.1      | Overv   | iew                                        | 27 |

|    | 2.2      | Presen  | at and Upcoming Challenges in VLSI Devices | 28 |

|    |          | 2.2.1   | Future Technology Trends                   | 28 |

|    |          | 2.2.2   | Dennard Scaling and Dark-Silicon           | 29 |

|    |          | 2.2.3   | Device Variability                         | 33 |

|    |          | 2.2.4   | Device Degradation and Ageing              | 34 |

|    | 2.3      | Many-   | Core Systems                               | 35 |

|    |          | 2.3.1   | Network-on-Chip                            | 36 |

|    |          | 2.3.2   | The Many-Core Design Space                 | 39 |

|   | 2.4 | Autonomic Adaptive Systems                                  | 2 |

|---|-----|-------------------------------------------------------------|---|

|   | 2.5 | Existing Adaptive Hardware Platforms                        | 6 |

|   | 2.6 | Summary                                                     | 0 |

| 3 | Lar | ge Scale Social Insect Systems 5.                           | 2 |

|   | 3.1 | Overview                                                    | 3 |

|   | 3.2 | Intelligence Capabilities of an Individual                  | 3 |

|   |     | 3.2.1 Colony Size versus Individual Capabilities            | 3 |

|   |     | 3.2.2 Neural Complexity                                     | 5 |

|   |     | 3.2.3 Hardware System Implications                          | 7 |

|   | 3.3 | Social Insect Intelligence Models for Task Allocation       | 8 |

|   |     | 3.3.1 Overview of Intelligence Models for Task Allocation 5 | 8 |

|   |     | 3.3.2 Hardware System Implications                          | 2 |

|   | 3.4 | Other Aspects of Social Insect Task Performance             | 3 |

|   |     | 3.4.1 Ratio of Working versus Resting Ants                  | 3 |

|   |     | 3.4.2 Polymorphism                                          | 6 |

|   |     | 3.4.3 Hardware System Implications                          | 7 |

|   | 3.5 | Hardware System Translation                                 | 8 |

|   | 3.6 | Summary                                                     | 0 |

| 4 | The | Centurion Many-Core System 7                                | 2 |

|   | 4.1 | Overview                                                    | 3 |

|   | 4.2 | Centurion Overview                                          | 4 |

|   | 4.3 | Router Design                                               | 6 |

|   |     | 4.3.1 NoC Packet and Routing Modes                          | 7 |

|   |     | 4.3.2 Data Channels                                         | 3 |

|   |     | 4.3.3 Router Configuration Port                             | 7 |

|   |     | 4.3.4 Deadlock Avoidance                                    | 0 |

|   |     | 4.3.5 Router Switch and Controller                          | 3 |

|   | 4.4 | Processing Element Design                                   | 6 |

|   |     | 4.4.1 Processing Core                                       | 7 |

|   |     | 4.4.2 Network Interface                                     | 3 |

|   | 4.5 | Embedded Intelligence Using PicoBlaze                       | 4 |

\_\_\_\_

|   | 4.6 | Advan     | ced Features of the NoC                                                                 | 7        |

|---|-----|-----------|-----------------------------------------------------------------------------------------|----------|

|   |     | 4.6.1     | Dynamic Node Clock Rates                                                                | 7        |

|   |     | 4.6.2     | Local Thermal Sensing                                                                   | 1        |

|   | 4.7 | FPGA      | Implementation                                                                          | 2        |

|   |     | 4.7.1     | Node Implementation                                                                     | 2        |

|   |     | 4.7.2     | NoC Layout                                                                              | 4        |

|   |     | 4.7.3     | Experiment Controller                                                                   | 5        |

|   |     | 4.7.4     | Clocking Structure                                                                      | 7        |

|   |     | 4.7.5     | Floorplanning                                                                           | 3        |

|   |     | 4.7.6     | Hardware Resources                                                                      | 3        |

|   |     | 4.7.7     | Software Development                                                                    | 3        |

|   | 4.8 | Summ      | ary                                                                                     | 5        |

| _ | ТΙ  | <b>CC</b> |                                                                                         | <i>,</i> |

| 5 |     | U         | urable Intelligence Array 120                                                           |          |

|   | 5.1 |           | 127                                                                                     |          |

|   |     | 5.1.1     | Role of the CIA   128     Designing Designing Determined with the CIA   120             |          |

|   | 5.0 | 5.1.2     | Designing Decision Pathways with the CIA                                                |          |

|   | 5.2 |           | gurable Intelligence Unit       131         The last last last last last last last last |          |

|   |     | 5.2.1     | Thresholder         132                                                                 |          |

|   |     | 5.2.2     | Internal Routing                                                                        |          |

|   |     | 5.2.3     | Level Output Option                                                                     |          |

|   | 5.0 | 5.2.4     | Placement and Configuration                                                             |          |

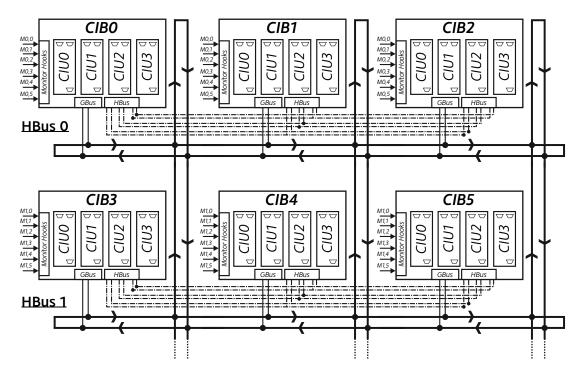

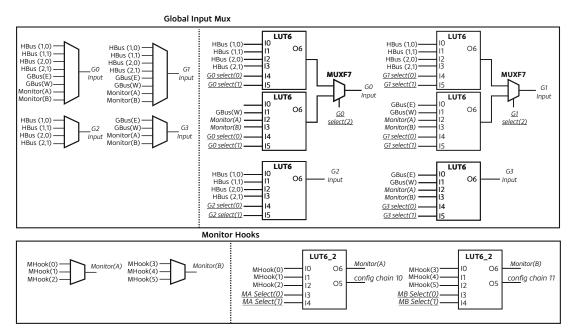

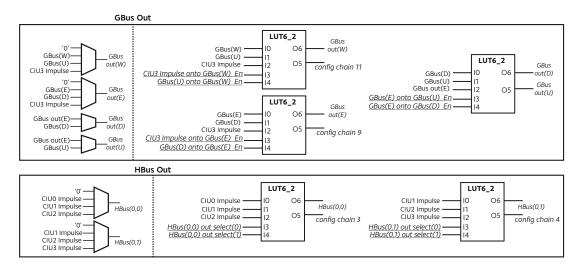

|   | 5.3 | -         | gurable Intelligence Block                                                              |          |

|   |     | 5.3.1     | Inter-CIB Routing                                                                       |          |

|   |     | 5.3.2     | Intra-CIB Routing                                                                       |          |

|   |     | 5.3.3     | Placement and Configuration                                                             |          |

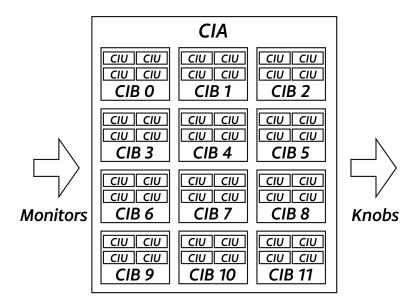

|   | 5.4 |           | gurable Intelligence Array 149                                                          |          |

|   |     | 5.4.1     | Array Layout                                                                            |          |

|   |     | 5.4.2     | CIA Hardware Resource Requirements and Scalability 15                                   |          |

|   |     | 5.4.3     | Monitors                                                                                |          |

|   |     | 5.4.4     | Knobs                                                                                   |          |

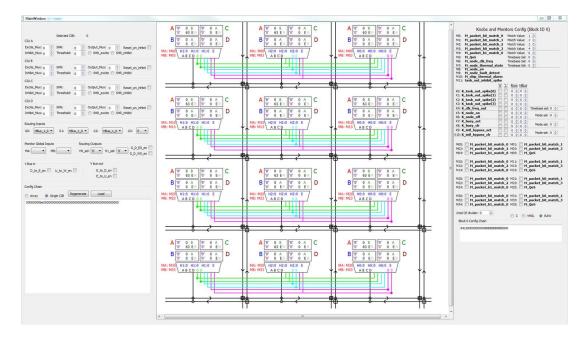

|   |     | 5.4.5     | Configuration                                                                           |          |

|   | 5.5 | Summ      | ary                                                                                     | 1        |

| 6 | Soci | al Insec | et Inspired Many-Core                                         | 162  |

|---|------|----------|---------------------------------------------------------------|------|

|   | 6.1  | Overvi   | iew                                                           | 163  |

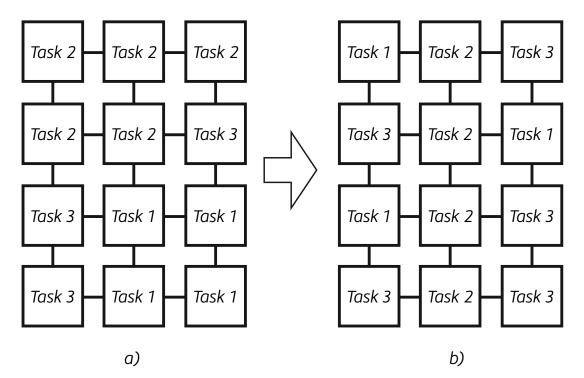

|   | 6.2  | Experi   | mental Benchmark Applications                                 | 163  |

|   |      | 6.2.1    | Experiment Settings                                           | 165  |

|   | 6.3  | Experi   | ment 1: Performance of System without Embedded Intelligence   | 167  |

|   |      | 6.3.1    | Description                                                   | 167  |

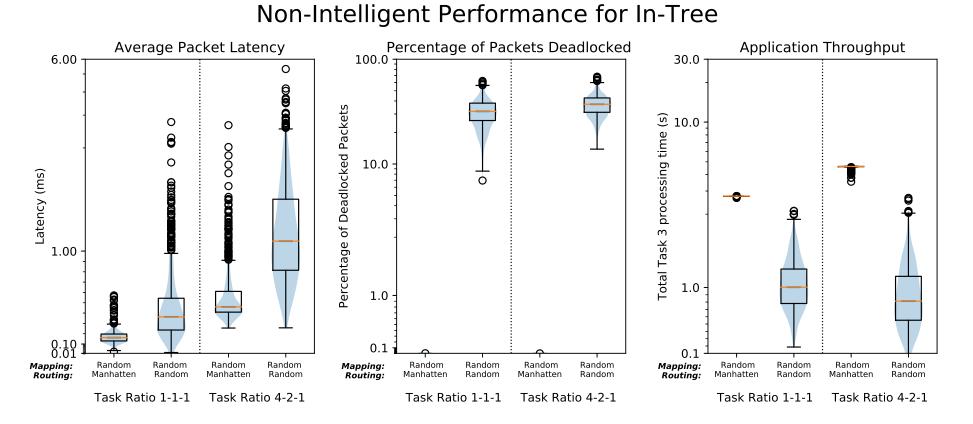

|   |      | 6.3.2    | Experiment 1.1 In-Tree                                        | 168  |

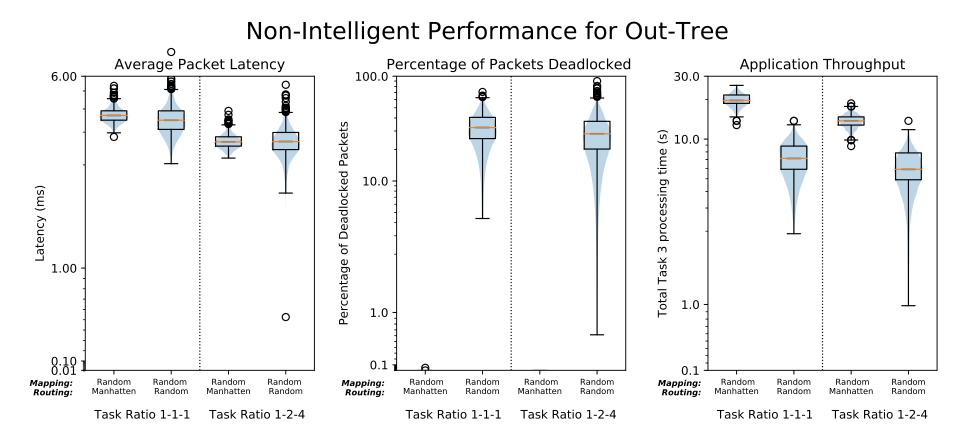

|   |      | 6.3.3    | Experiment 1.2 Out-Tree                                       | 170  |

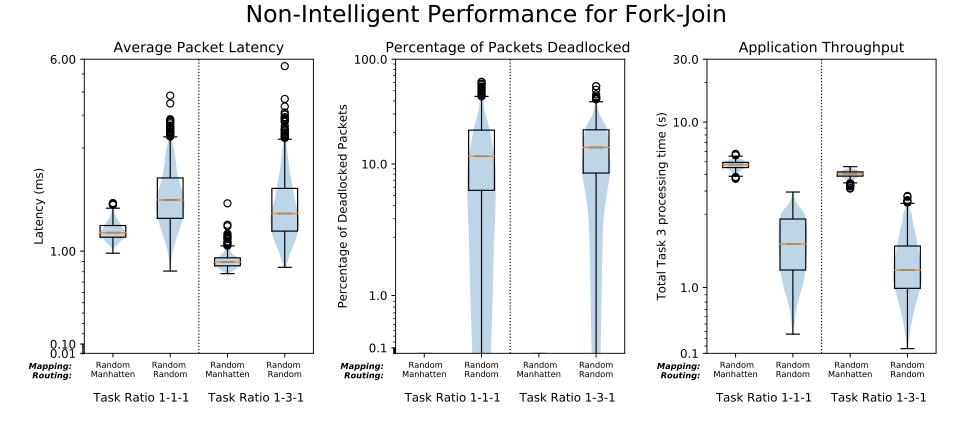

|   |      | 6.3.4    | Experiment 1.3 Fork-Join                                      | 172  |

|   |      | 6.3.5    | Review                                                        | 174  |

|   | 6.4  | Experi   | ment 2: Adaptive Task Allocation using the Interaction Net-   |      |

|   |      | work I   | ntelligence Model                                             | 175  |

|   |      | 6.4.1    | Biological Inspiration                                        | 175  |

|   |      | 6.4.2    | Experiments Overview                                          | 175  |

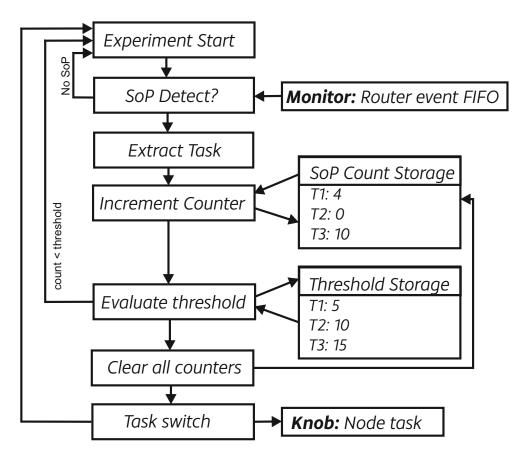

|   |      | 6.4.3    | Intelligence Implementation                                   | 177  |

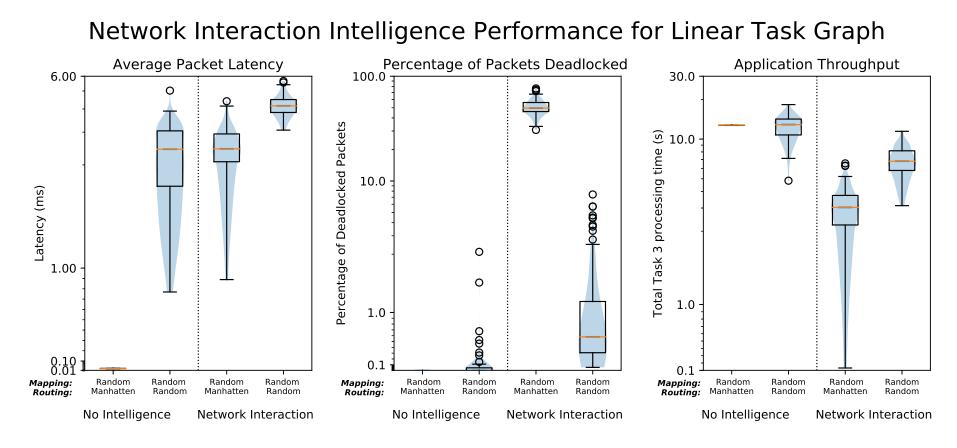

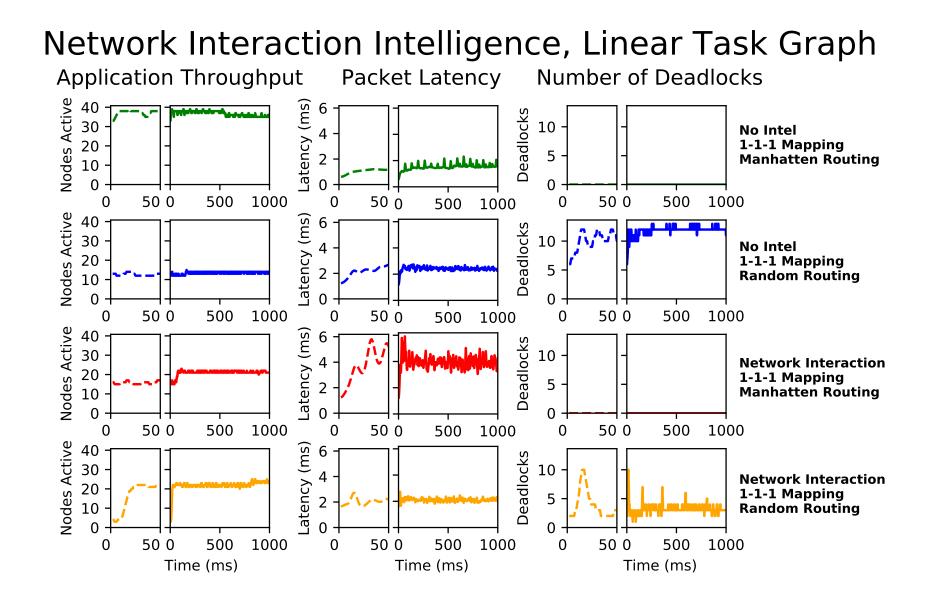

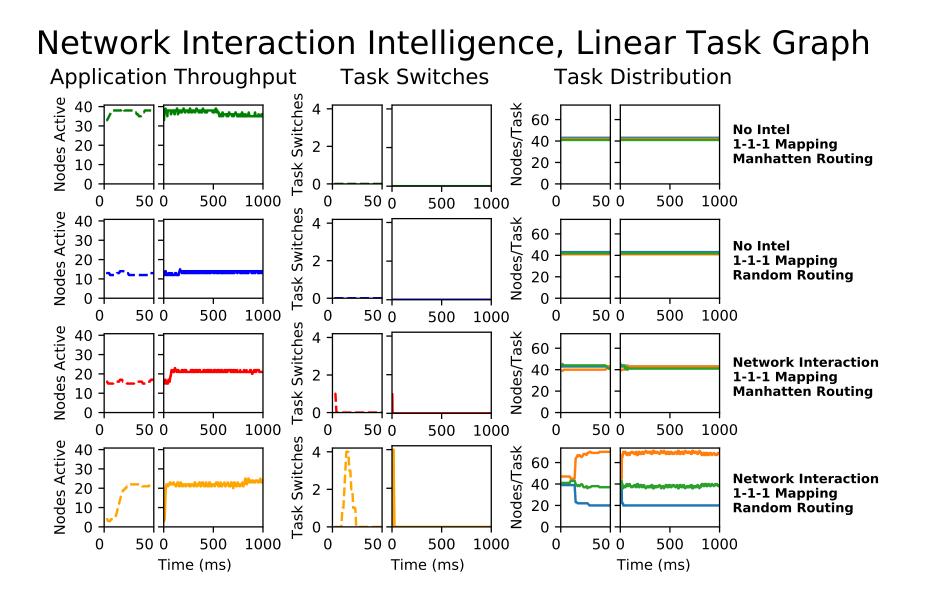

|   |      | 6.4.4    | Experiment 2.1: Interaction Network Model - Linear Task Graph | n179 |

|   |      | 6.4.5    | Experiment 2.2: Interaction Network Model - In tree           | 184  |

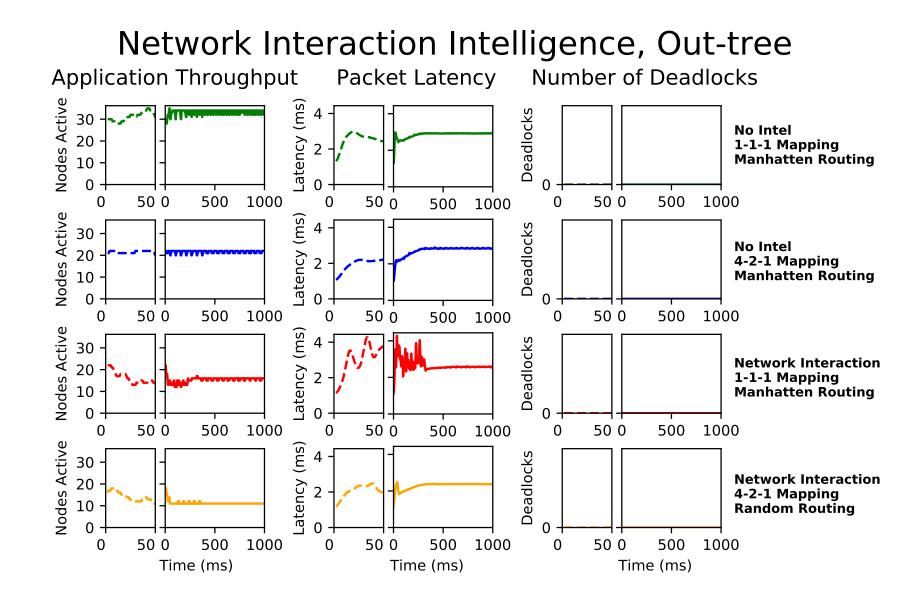

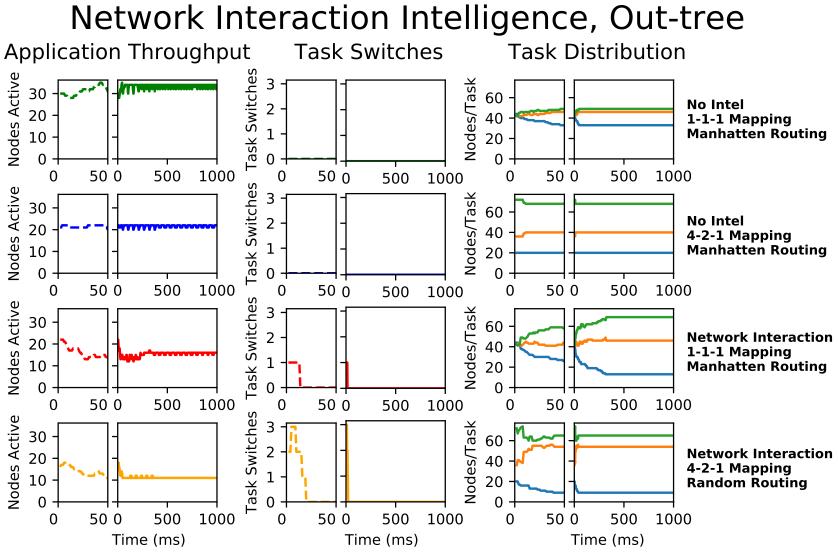

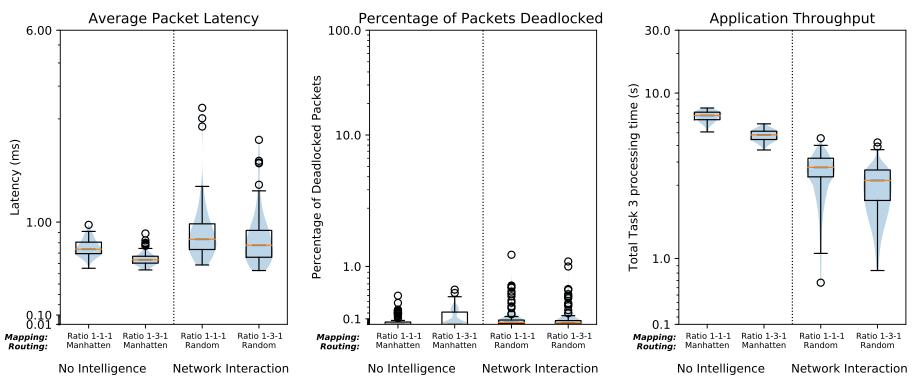

|   |      | 6.4.6    | Experiment 2.3: Interaction Network Model - Out tree          | 188  |

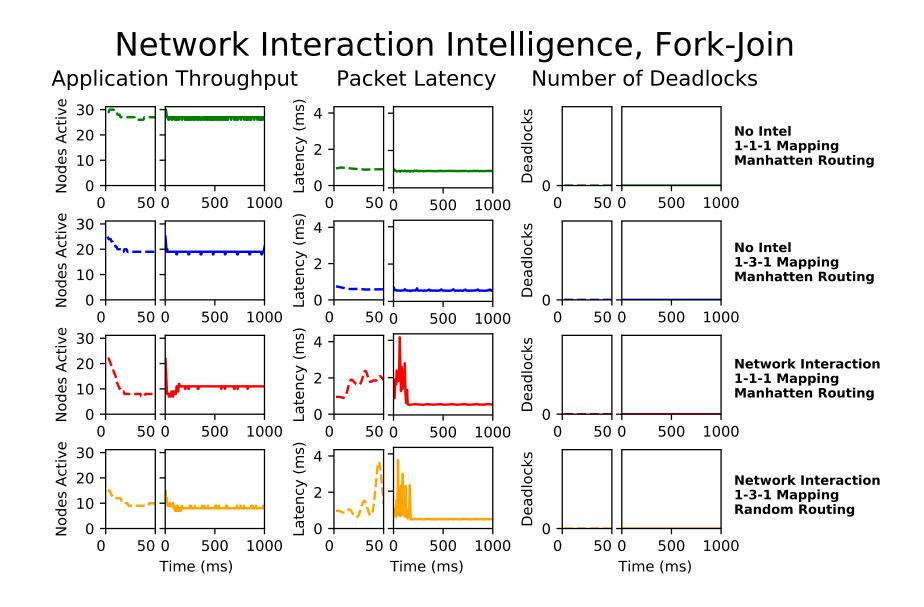

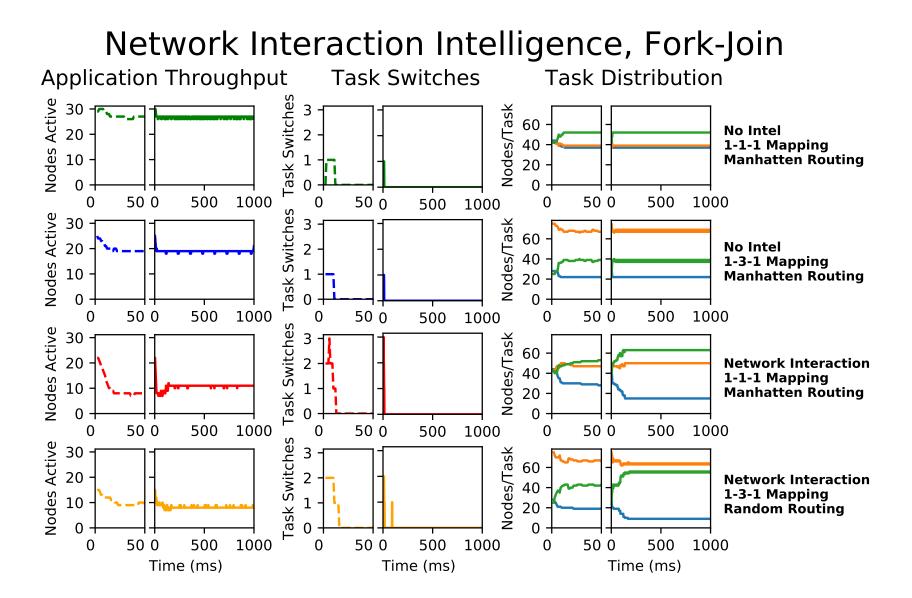

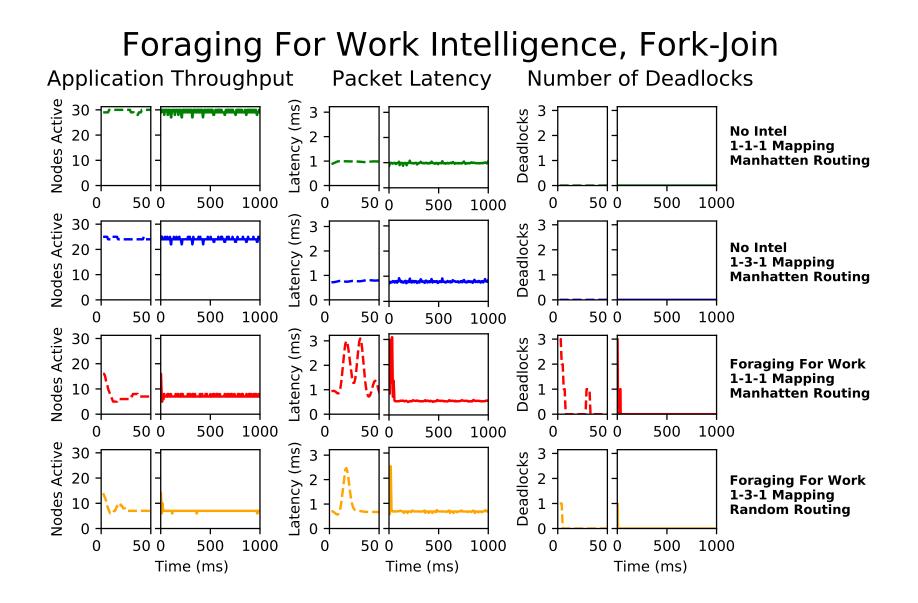

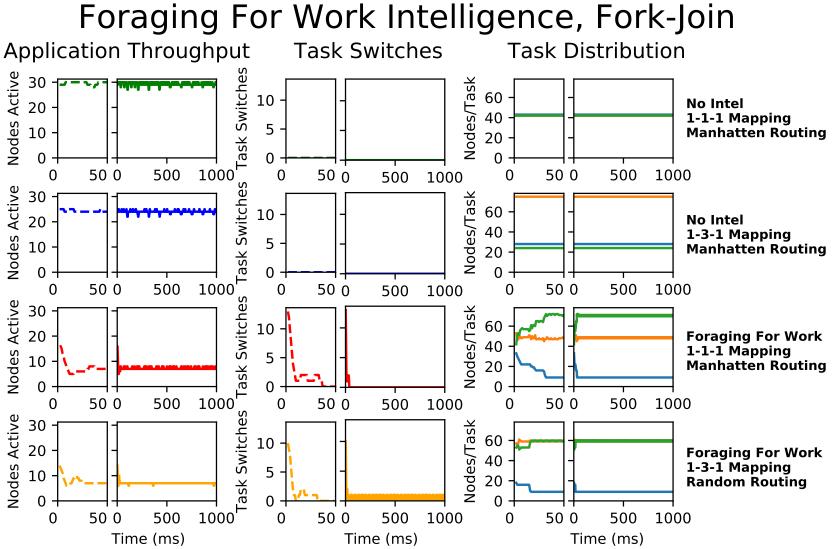

|   |      | 6.4.7    | Experiment 2.4: Interaction Network Model - Fork Join         | 192  |

|   |      | 6.4.8    | Review                                                        | 196  |

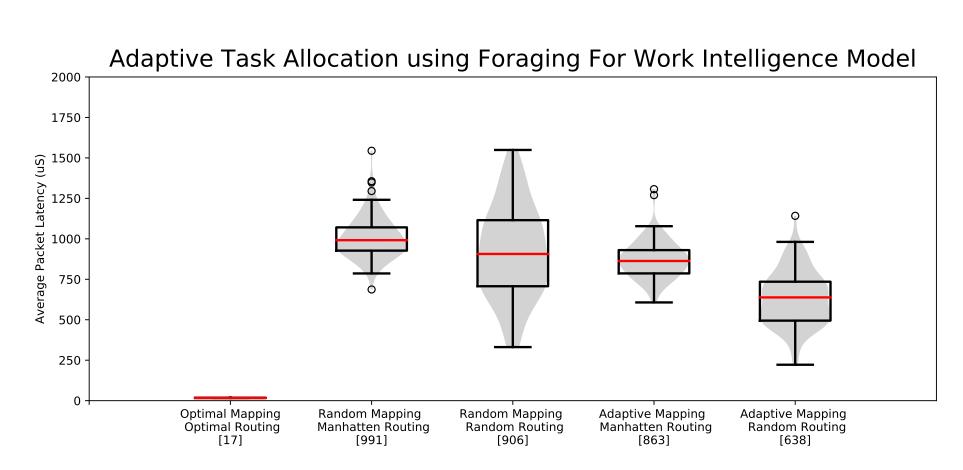

|   | 6.5  | Experi   | iment 3: Adaptive Task Allocation with the Foraging For Work  |      |

|   |      | (FFW)    | ) Model                                                       | 197  |

|   |      | 6.5.1    | Biological Inspiration                                        | 197  |

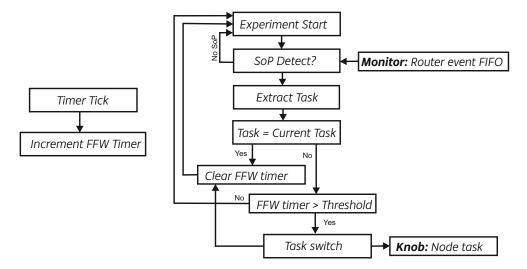

|   |      | 6.5.2    | Experiments Overview                                          | 197  |

|   |      | 6.5.3    | Intelligence Implementation                                   | 197  |

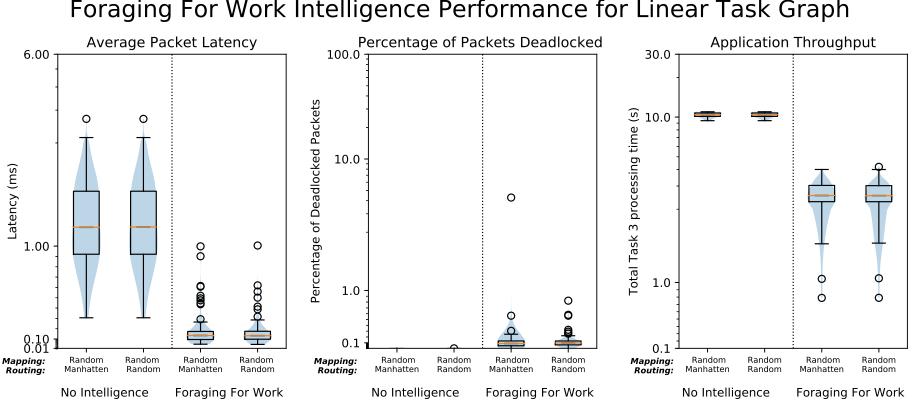

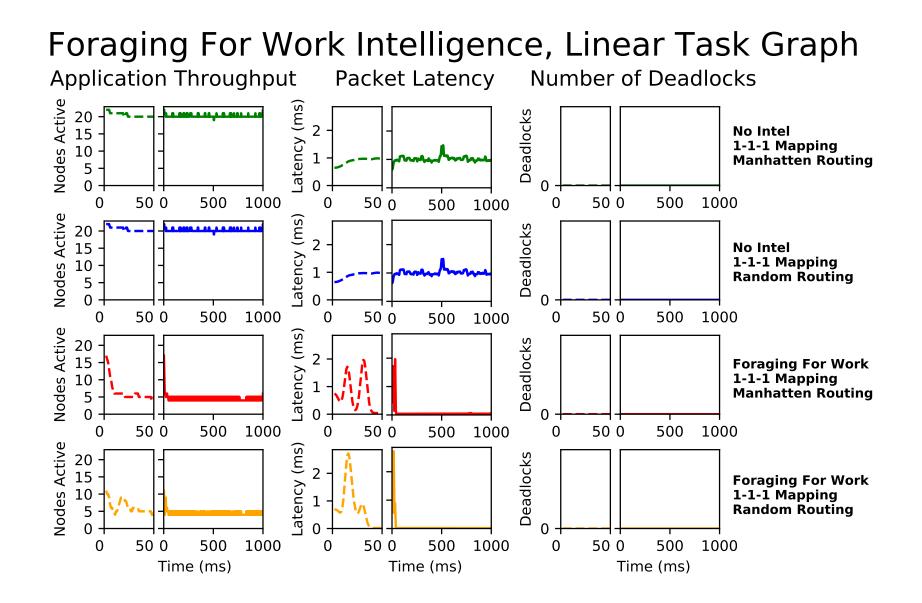

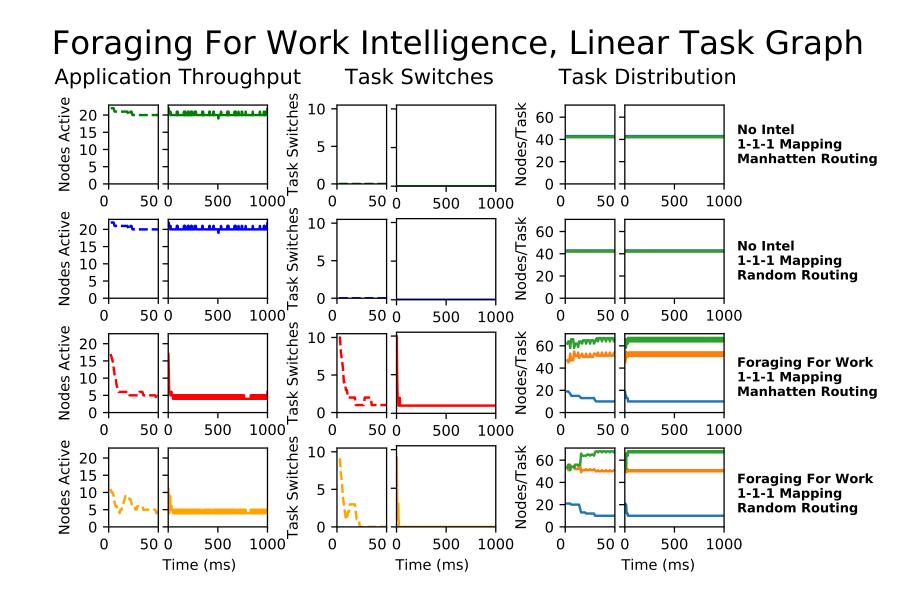

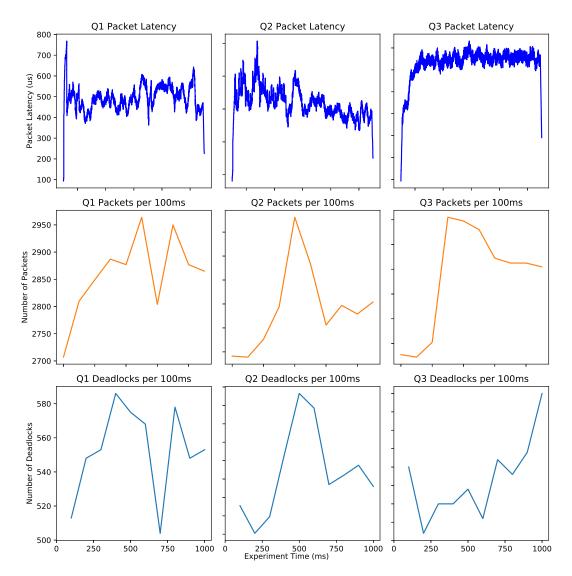

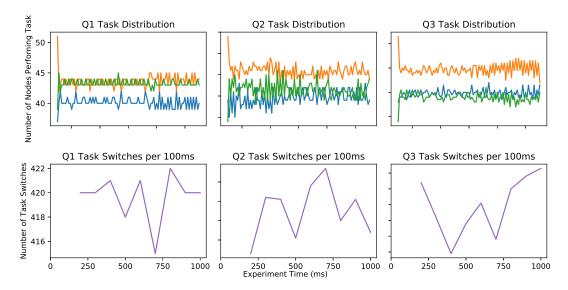

|   |      | 6.5.4    | Experiment 3.1: Foraging For Work - Linear Task Graph         | 199  |

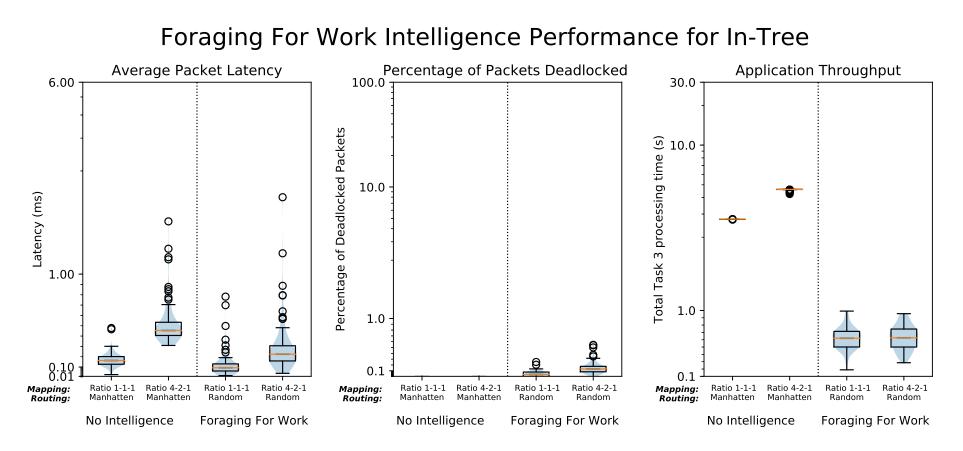

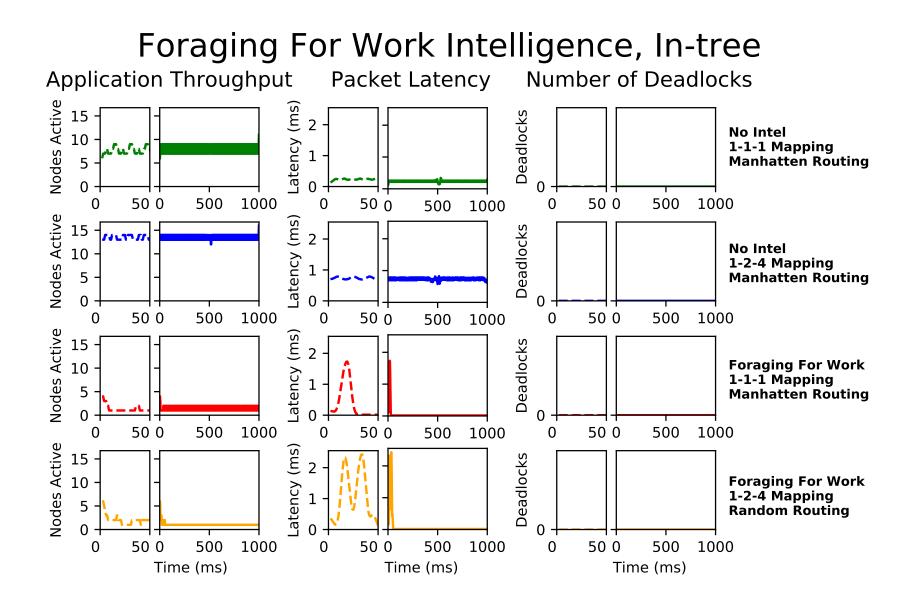

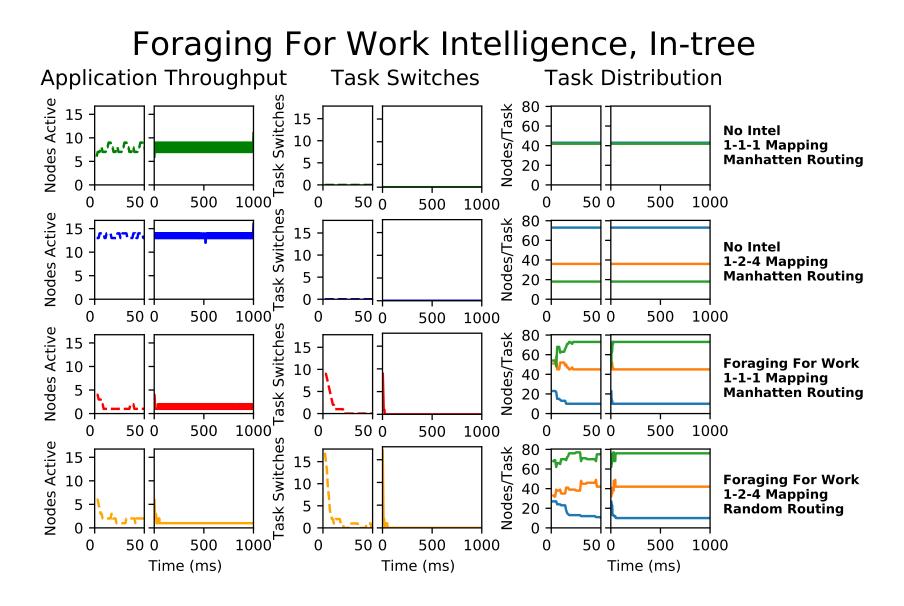

|   |      | 6.5.5    | Experiment 3.2: Foraging For Work - In tree                   | 203  |

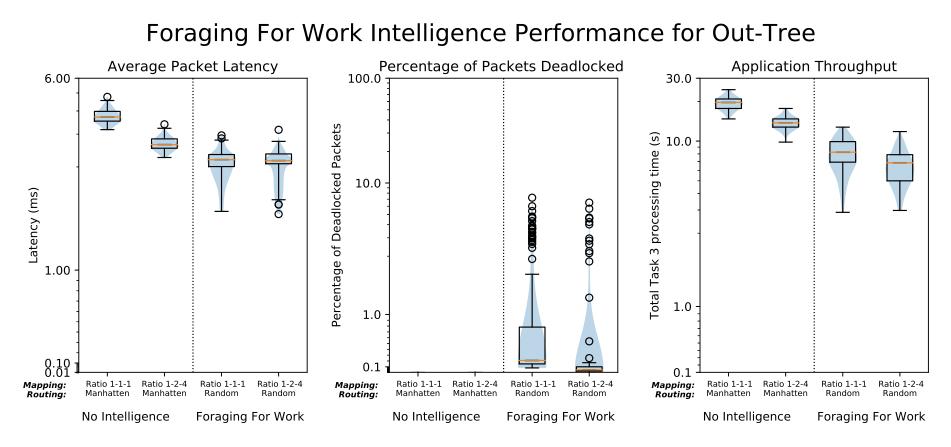

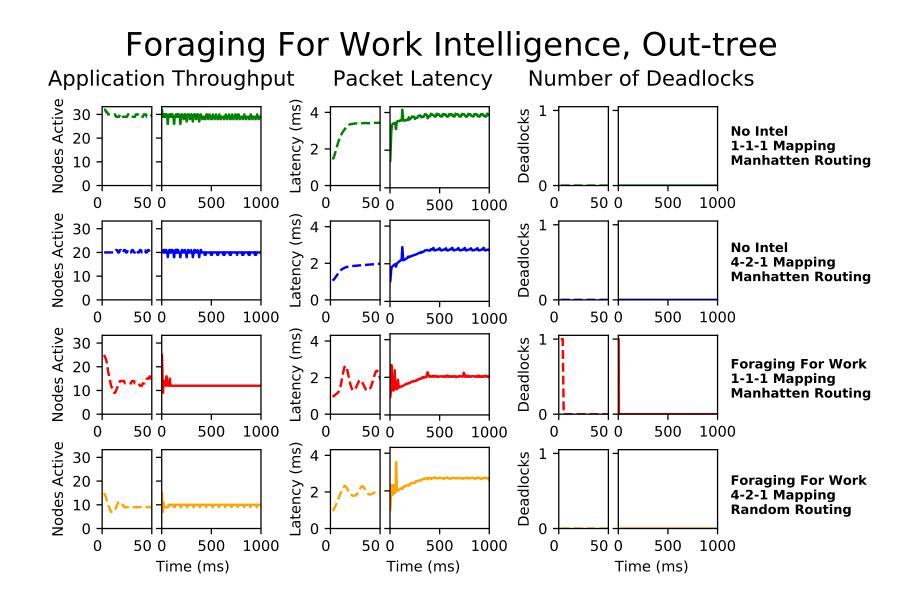

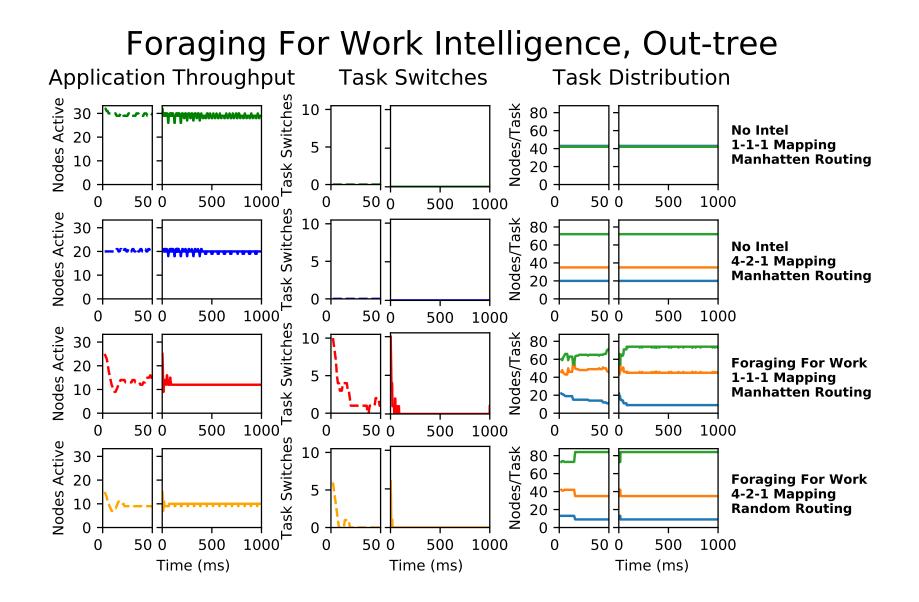

|   |      | 6.5.6    | Experiment 3.3: Foraging For Work - Out tree                  | 207  |

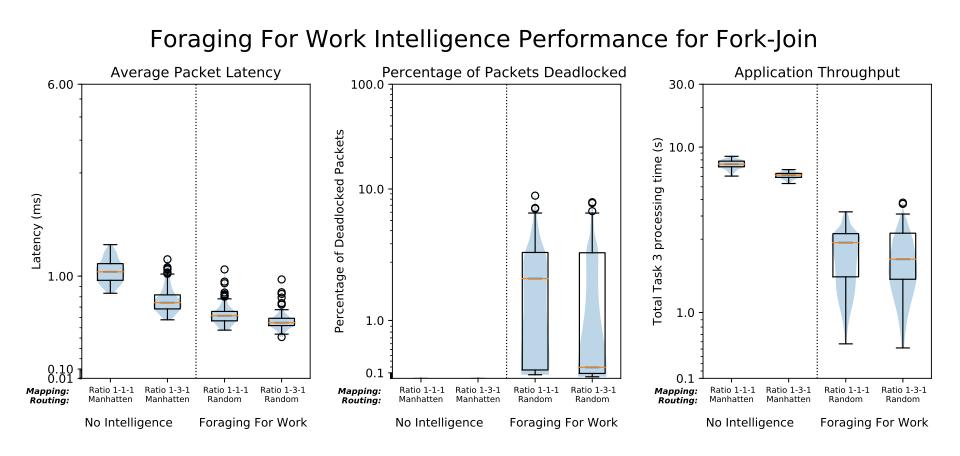

|   |      | 6.5.7    | Experiment 3.4: Foraging For Work - Fork Join                 | 211  |

|   |      | 6.5.8    | Review                                                        | 215  |

|   | 6.6  | Experi   | ment 4: Self-Regulation of Task 1 Nodes                       | 216  |

|   |      | 6.6.1    | Biological Inspiration                                        | 216  |

\_\_\_\_

|   |     | 6.6.2   | Experiments Overview                                          | 216 |

|---|-----|---------|---------------------------------------------------------------|-----|

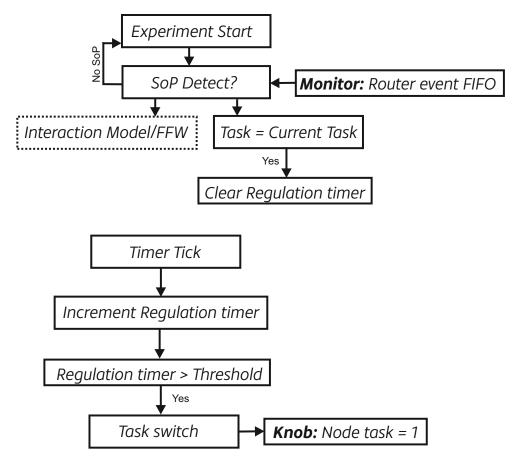

|   |     | 6.6.3   | Intelligence Implementation                                   | 216 |

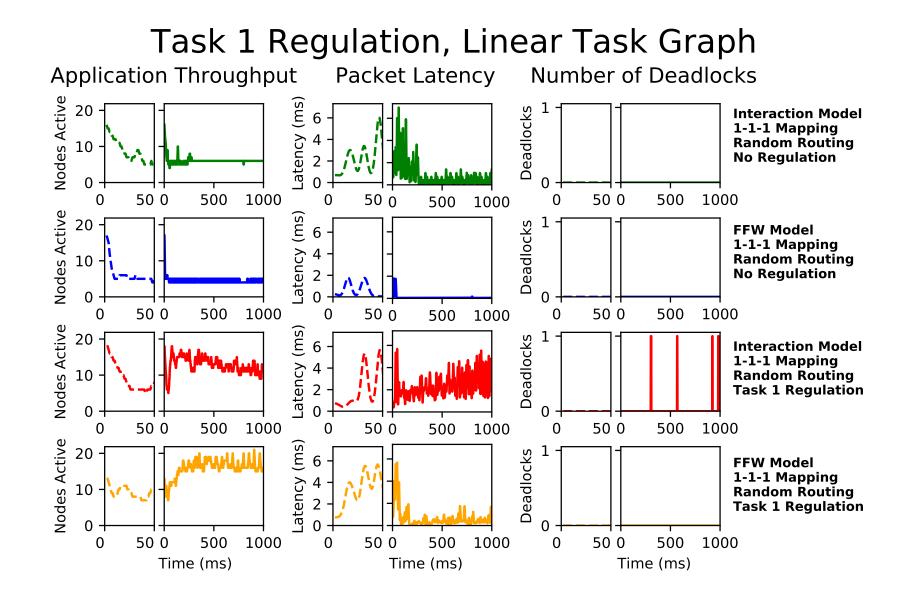

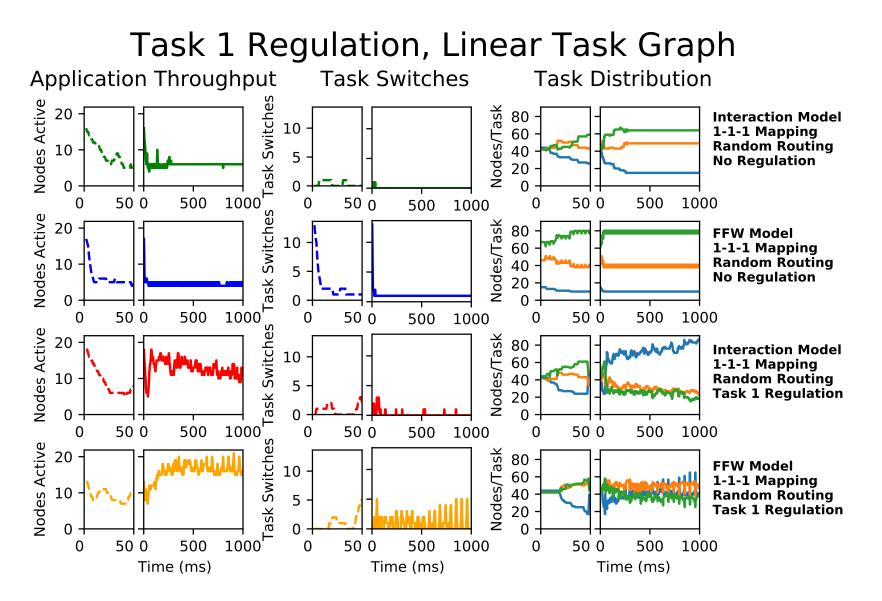

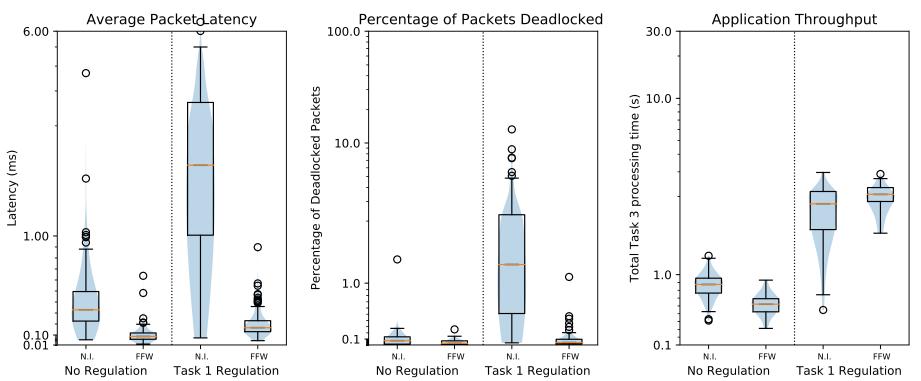

|   |     | 6.6.4   | Experiment 4.1: Self-Regulation - Linear Task Graph           | 218 |

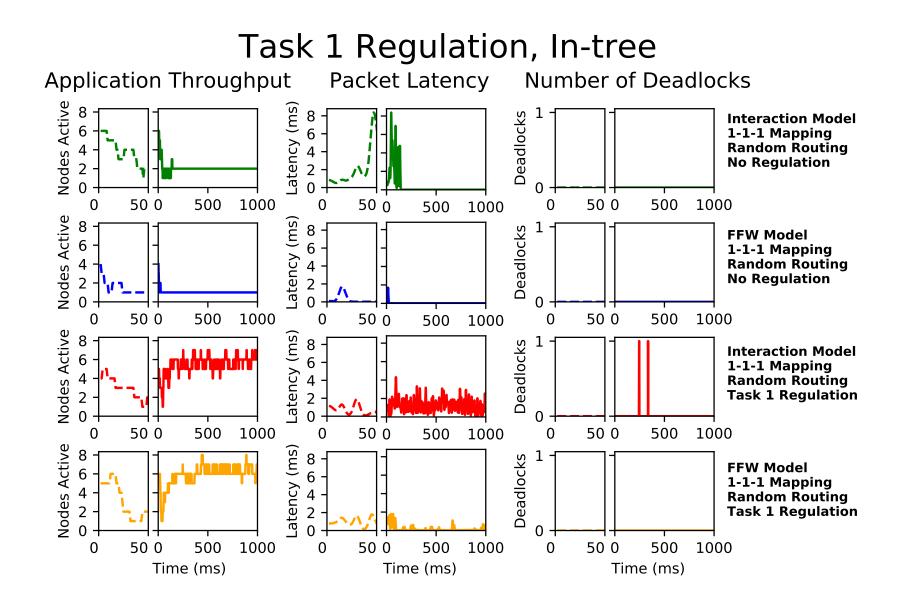

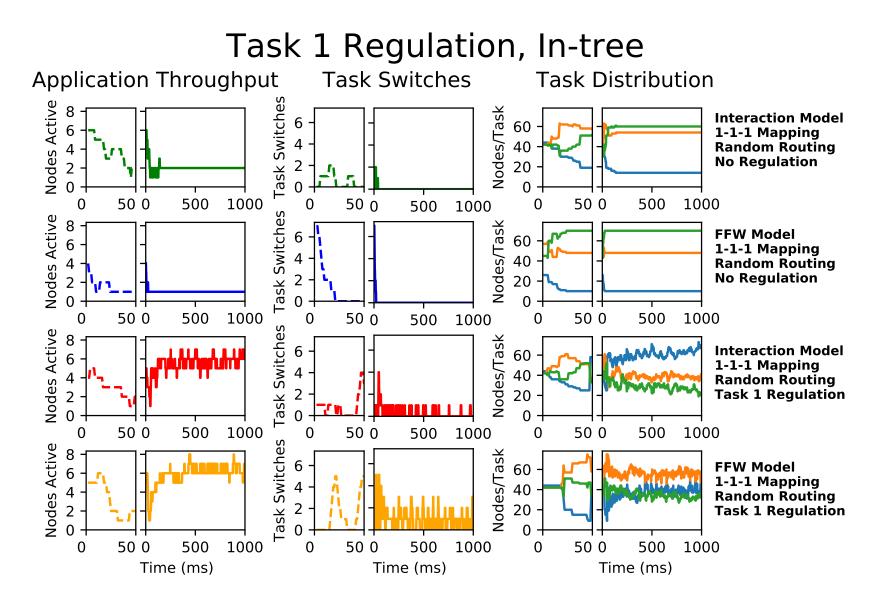

|   |     | 6.6.5   | Experiment 4.2: Self-Regulation - In tree                     | 222 |

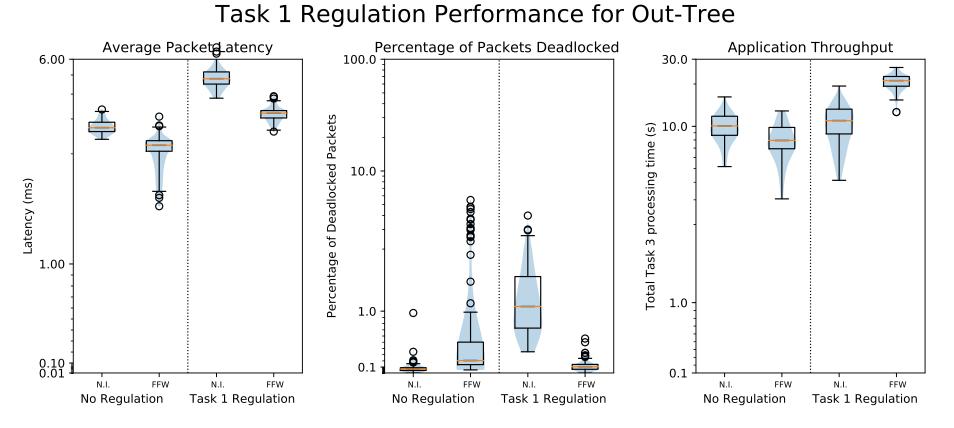

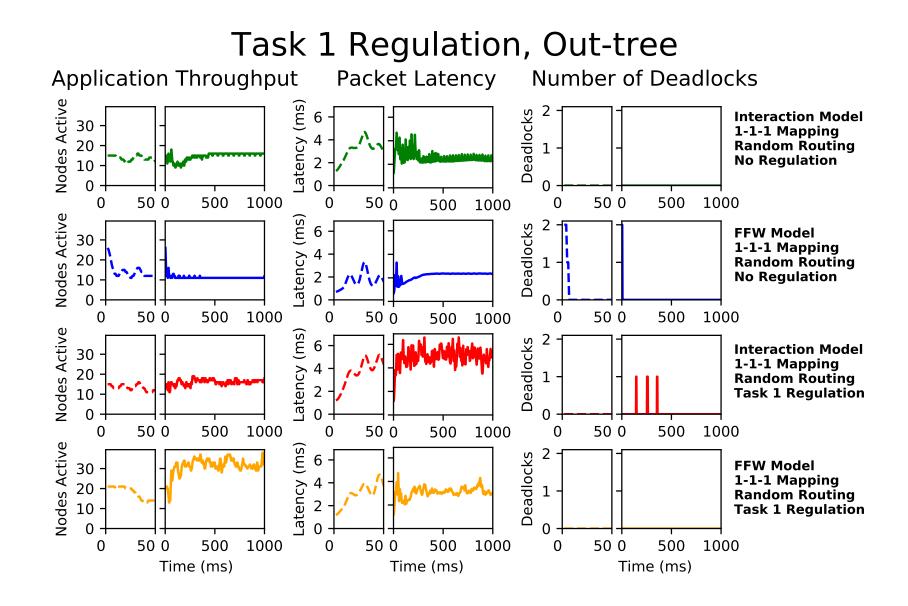

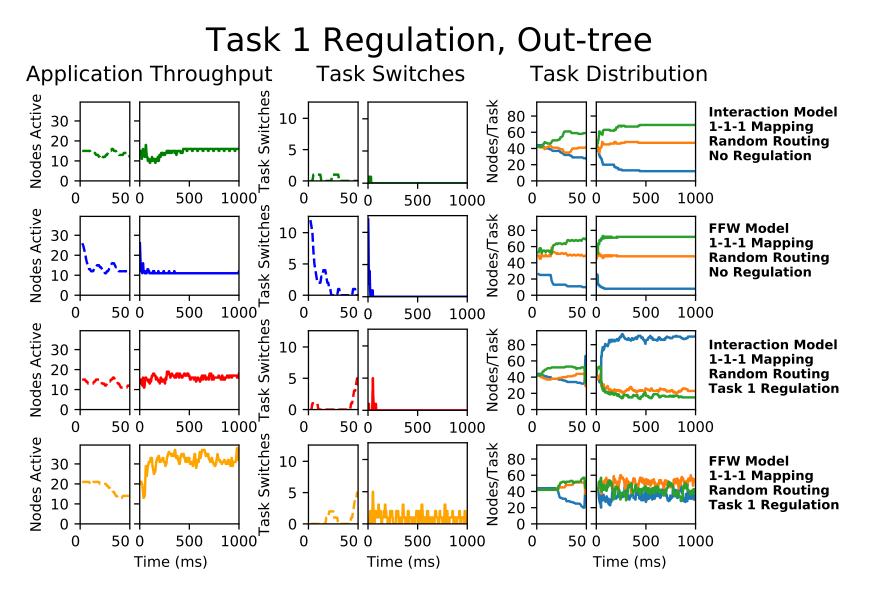

|   |     | 6.6.6   | Experiment 4.3: Self-Regulation - Out tree                    | 226 |

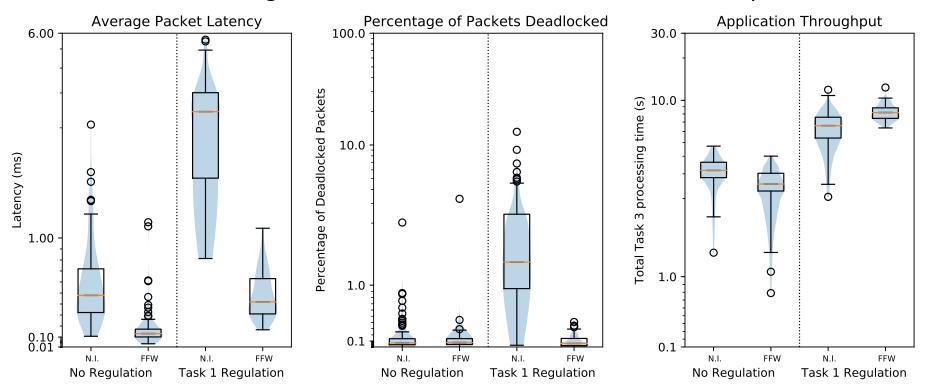

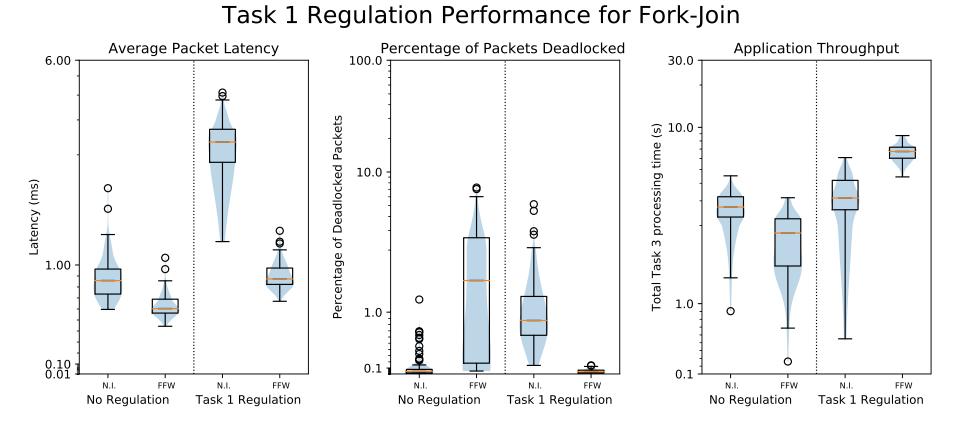

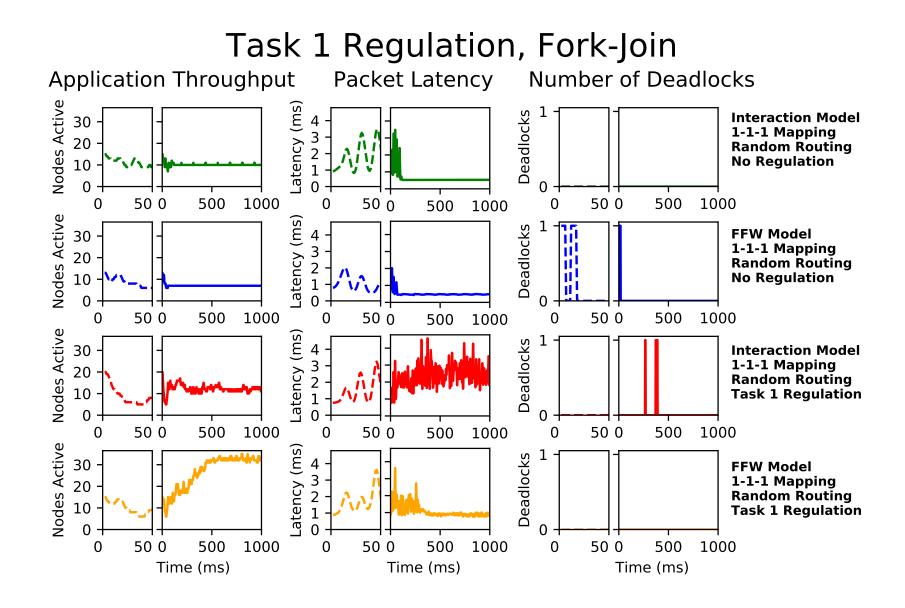

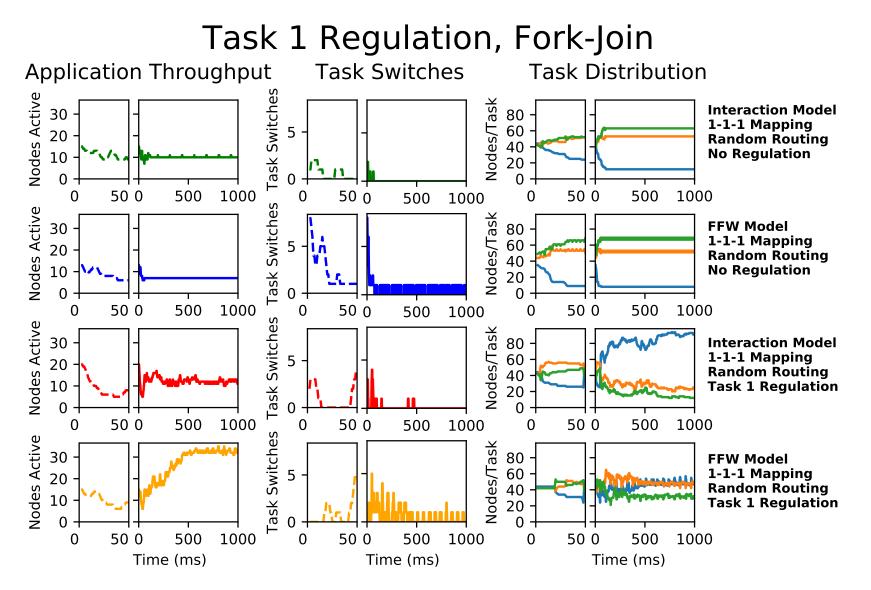

|   |     | 6.6.7   | Experiment 4.4: Self-Regulation - Fork Join                   | 230 |

|   |     | 6.6.8   | Review                                                        | 234 |

|   | 6.7 | Summ    | ary                                                           | 235 |

| 7 | Ada | ptive M | lany-Core Investigation                                       | 238 |

| - | 7.1 | -       | iew                                                           |     |

|   | 7.2 |         | ment 5: Fault Tolerance                                       |     |

|   |     | 7.2.1   | Biological Inspiration                                        |     |

|   |     | 7.2.2   | Experiment Overview                                           | 240 |

|   |     | 7.2.3   | Intelligence Implementation                                   | 241 |

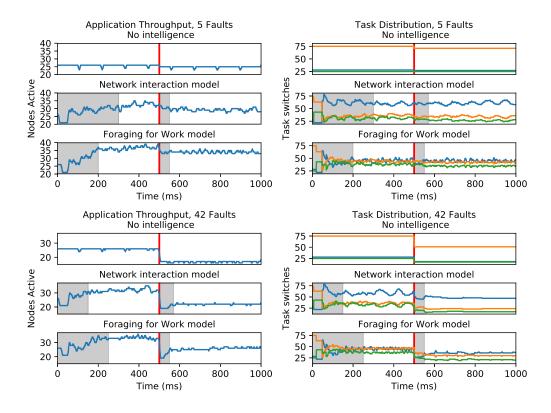

|   |     | 7.2.4   | Experiment 5.1: Fault Injection                               | 241 |

|   |     | 7.2.5   | Review                                                        | 244 |

|   | 7.3 | Experi  | ment 6: CIA Implementation of the Interaction Network Intel-  |     |

|   |     | ligence | e Model                                                       | 245 |

|   |     | 7.3.1   | Experiment Overview                                           | 245 |

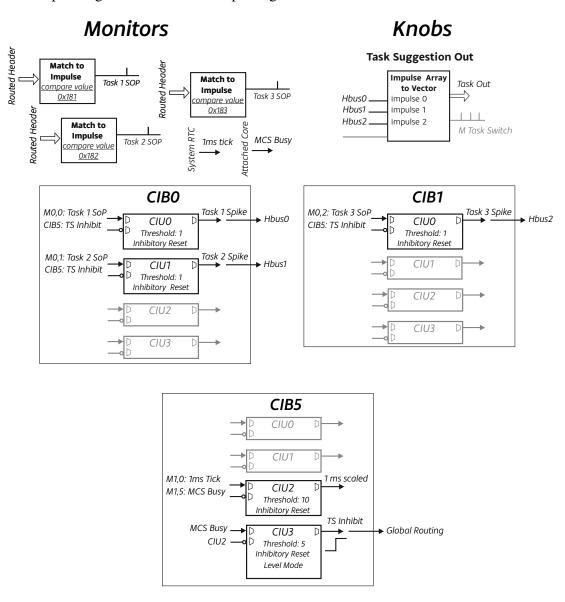

|   |     | 7.3.2   | Knobs and Monitors                                            | 245 |

|   |     | 7.3.3   | CIA Configuration                                             | 246 |

|   |     | 7.3.4   | Experiment 6: Interaction Network Intelligence Model          | 247 |

|   |     | 7.3.5   | Review                                                        | 251 |

|   | 7.4 | Experi  | ment 7: CIA Implementation of the Foraging For Work (FFW)     |     |

|   |     | Model   |                                                               | 252 |

|   |     | 7.4.1   | Experiment Overview                                           | 252 |

|   |     | 7.4.2   | Knobs and Monitors                                            | 252 |

|   |     | 7.4.3   | CIA Configuration                                             | 253 |

|   |     | 7.4.4   | Experiment 7.1: Foraging For Work Intelligence Model          | 254 |

|   |     | 7.4.5   | Review                                                        | 258 |

|   | 7.5 | Experi  | ment 8: Experiment Performance of Intelligence Array Relative |     |

|   |     | to Clo  | ck Frequency                                                  | 259 |

|    |       | 7.5.1        | Experiment Overview                                        | 259 |

|----|-------|--------------|------------------------------------------------------------|-----|

|    |       | 7.5.2        | Experiment 8.1: Underclocking the Intelligence to 50kHz    | 260 |

|    |       | 7.5.3        | Review                                                     | 263 |

|    | 7.6   | Summa        | ary                                                        | 265 |

| 8  | Con   | clusions     |                                                            | 267 |

|    | 8.1   | Summa        | ary                                                        | 268 |

|    |       | 8.1.1        | Social-Insect Inspired Adaptive Task Allocation            | 268 |

|    |       | 8.1.2        | Effectiveness of the Centurion Platform                    | 270 |

|    |       | 8.1.3        | Implementation of Decision Pathways using the CIA          | 271 |

|    |       | 8.1.4        | Autonomous System Evaluation                               | 271 |

|    |       | 8.1.5        | Overall Conclusions                                        | 273 |

|    | 8.2   | Further      | Work                                                       | 275 |

|    |       | 8.2.1        | Potential Centurion Developments                           | 275 |

|    |       | 8.2.2        | Further Experiments with the Social Insect Models          | 277 |

|    |       | 8.2.3        | Future Development of Decision Pathways based on the CIA . | 277 |

| Ар | pend  | ices         |                                                            | 279 |

| A  | Devi  | ce Cloc      | k Domain Mapping                                           | 280 |

| B  | Floo  | rplanni      | ng Figures                                                 | 284 |

| Re | feren | ferences 287 |                                                            |     |

# **List of Figures**

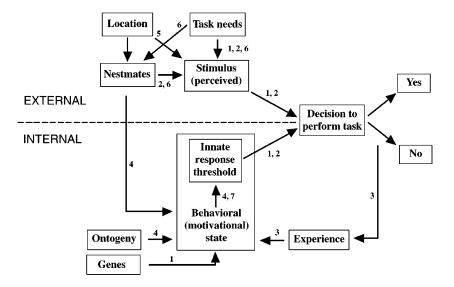

| 3.1  | Task Decision Factors                                     | 59 |

|------|-----------------------------------------------------------|----|

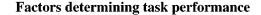

| 4.1  | General overview of the Centurion 16x8 many-core          | 75 |

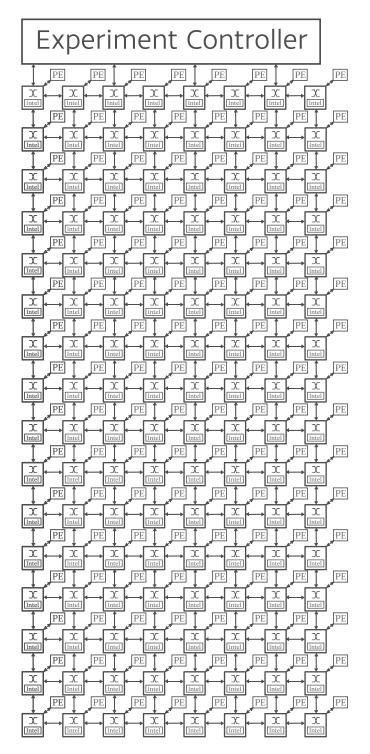

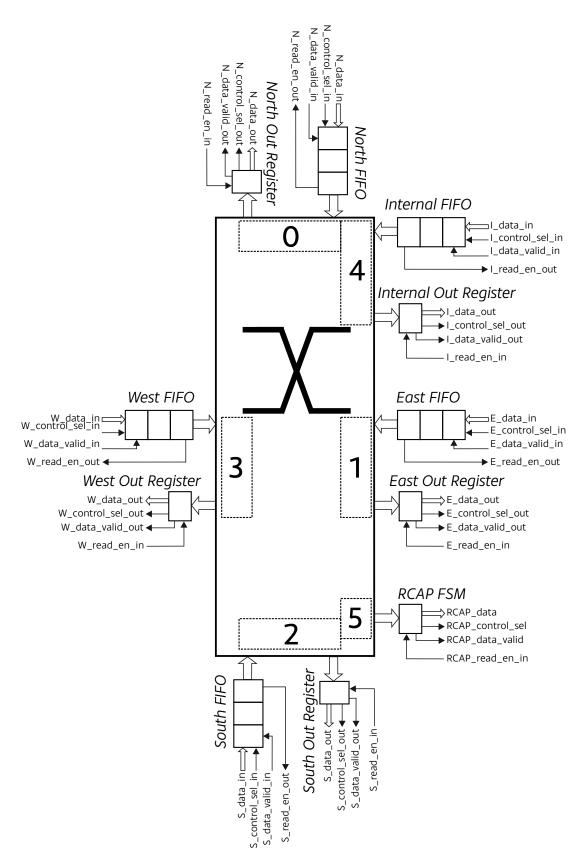

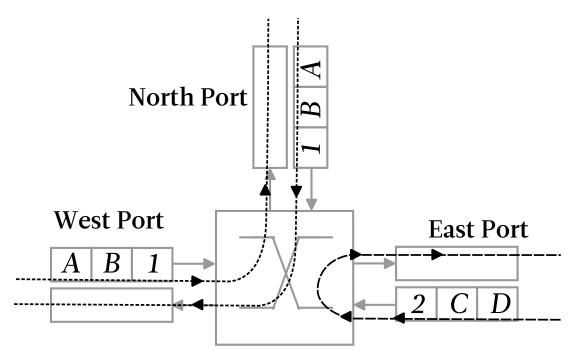

| 4.2  | The Centurion 5-channel NoC router                        | 77 |

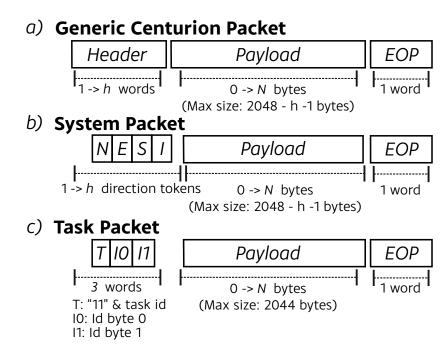

| 4.3  | Centurion Packet Structure                                | 79 |

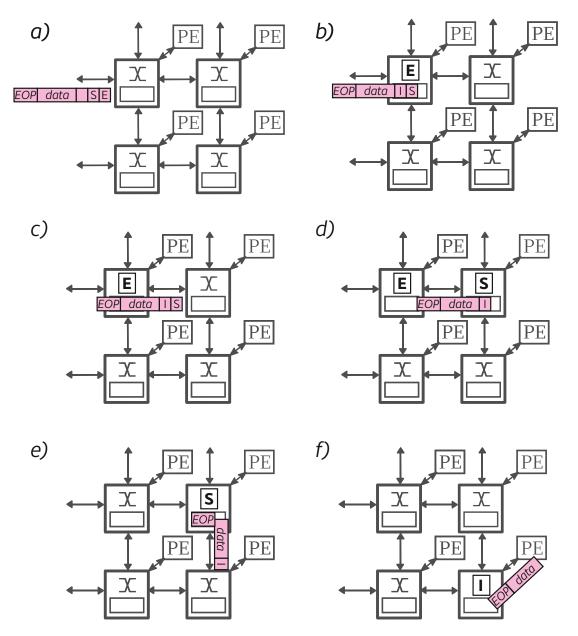

| 4.4  | Example of System packet routing                          | 81 |

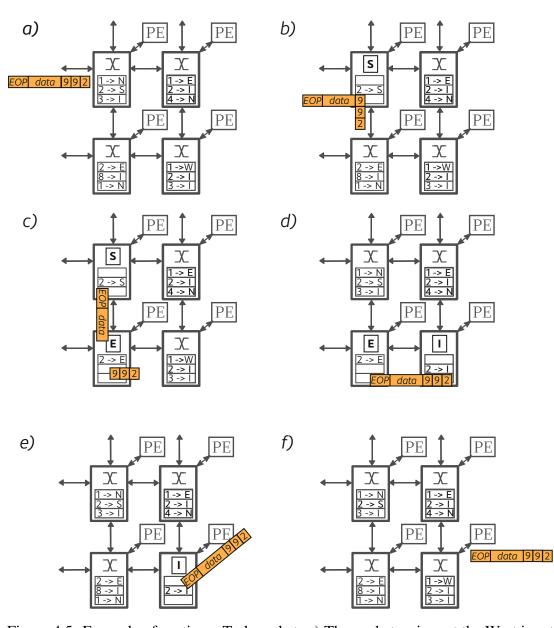

| 4.5  | Example of Task packet routing                            | 82 |

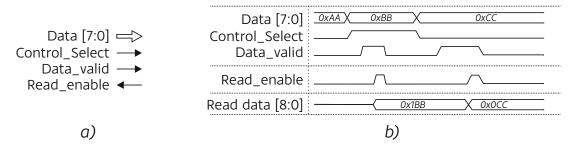

| 4.6  | Data Transmission Signals                                 | 84 |

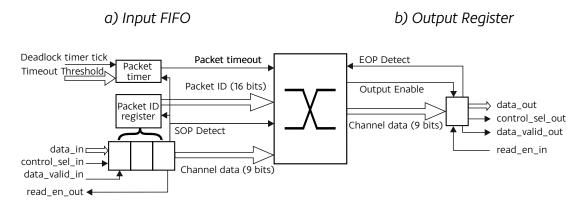

| 4.7  | A Single Centurion Data Channel                           | 85 |

| 4.8  | Arrangement of Data Channels in the Router                | 86 |

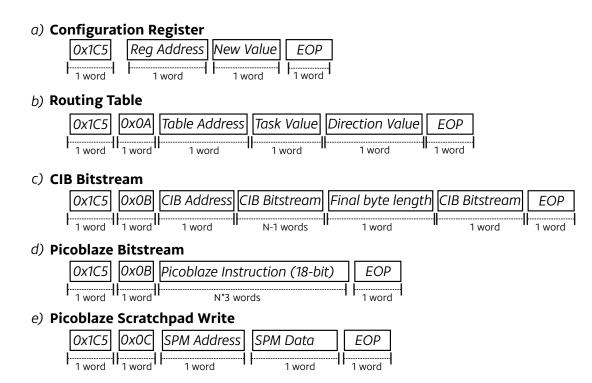

| 4.9  | Structre of Centurion RCAP Packets                        | 88 |

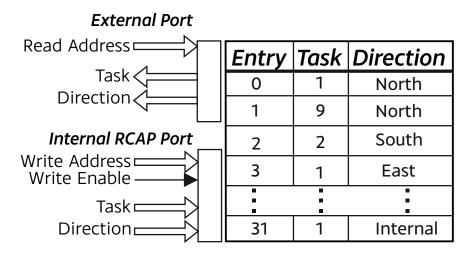

| 4.10 | Structure of the Routing Table                            | 90 |

| 4.11 | Example of Deadlock Detection and Handling                | 92 |

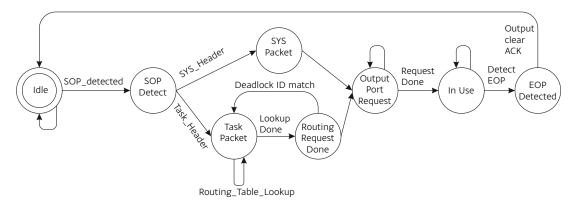

| 4.12 | Router Input Channel FSM                                  | 93 |

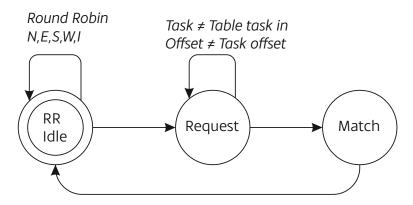

| 4.13 | Routing Table Request FSM                                 | 95 |

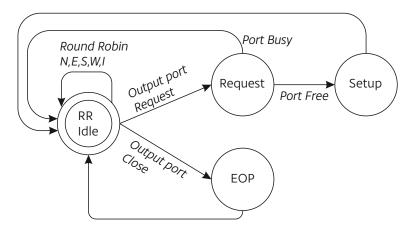

| 4.14 | Output Port Request FSM                                   | 95 |

| 4.15 | Arrangement of the Centurion Processing Element           | 99 |

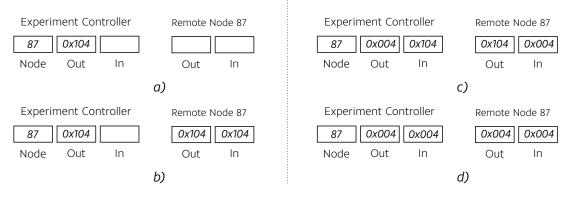

| 4.16 | Example of the Node Debug Interface                       | 03 |

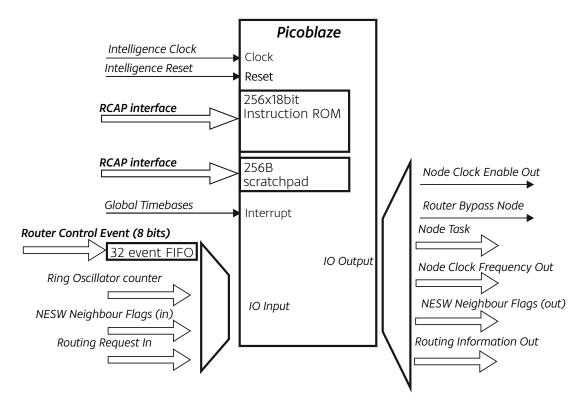

| 4.17 | Picoblaze Hardware Design                                 | 06 |

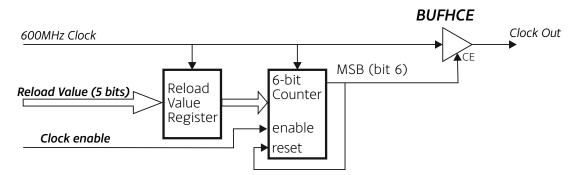

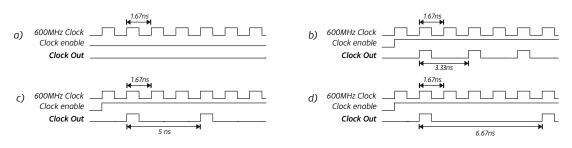

| 4.18 | Dynamic Clock Divider Design                              | 08 |

| 4.19 | Example Waveforms of the Divided Clock                    | 10 |

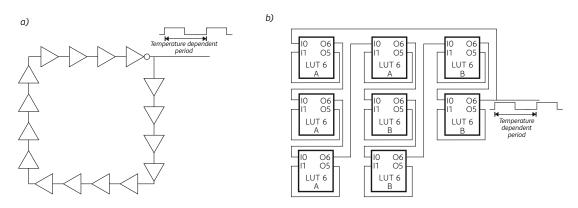

| 4.20 | A 16-stage Ring Oscillator used for Temperature Sensing 1 | 12 |

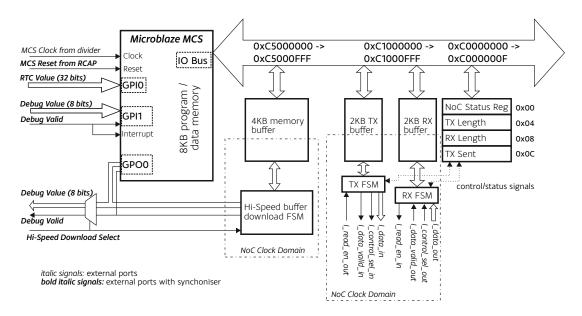

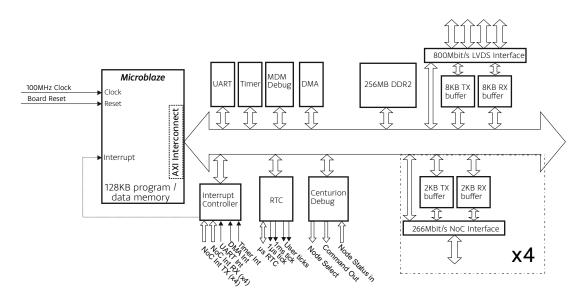

| 4.21 | Architecture of the Experiment Controller                 | 16 |

| 4.22 | Clock Regions of the xc6vlx760                            | 17 |

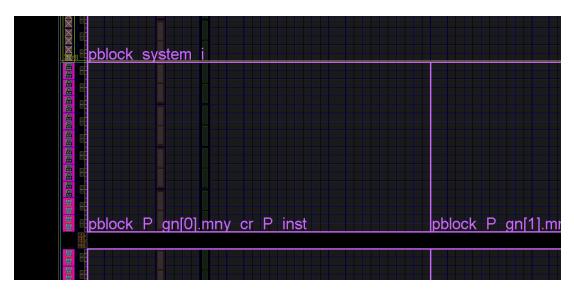

| 4.23 | Node Partition Layout                                     | 20 |

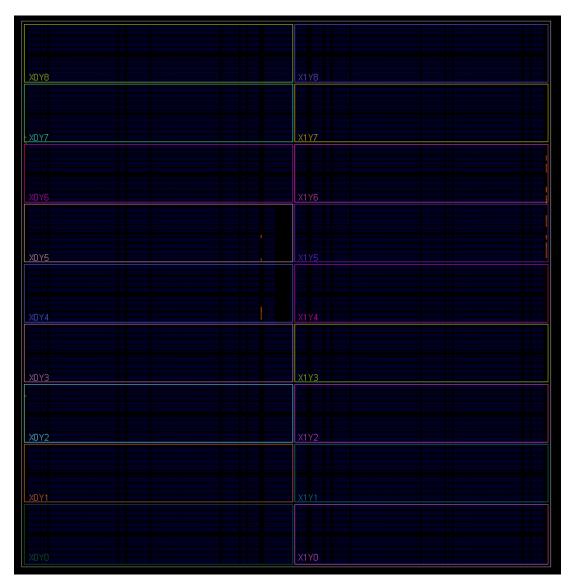

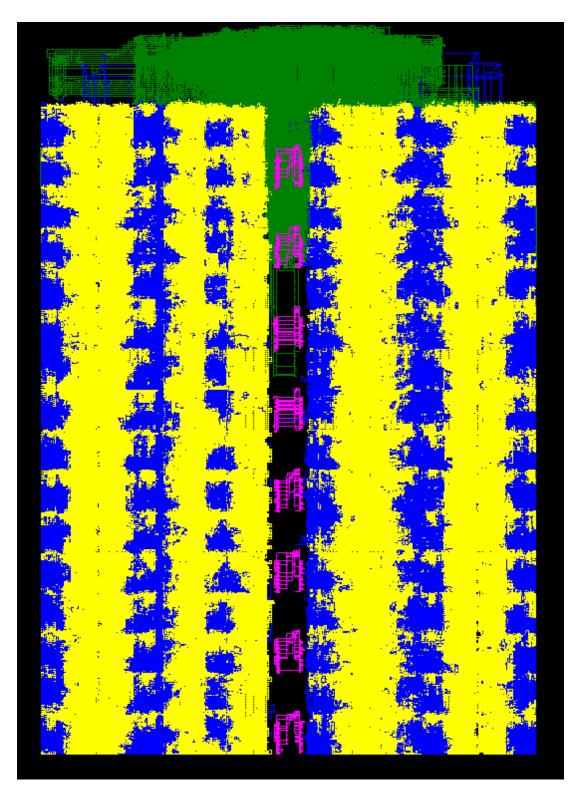

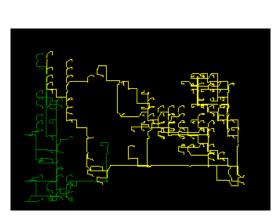

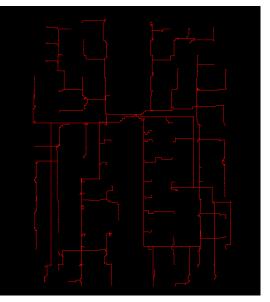

| 4.24 | Overview of all Centurion Partitions on the FPGA Device 1 | 21 |

| 4.25 | Post-Implementation Floorplan of Centurion                | 22 |

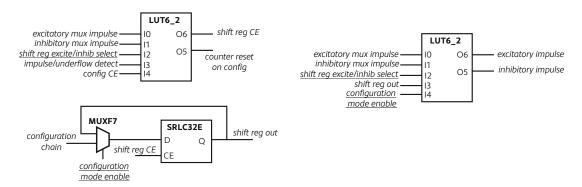

| 5.1  | General Overview of the CIA                               | 27 |

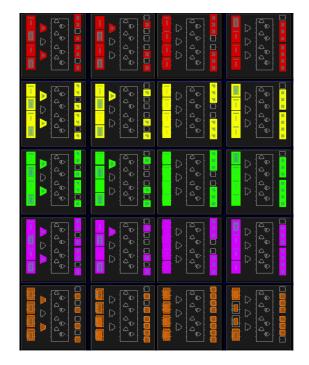

| 5.2  | Screenshot of CIA Programming Tool                        | 31 |

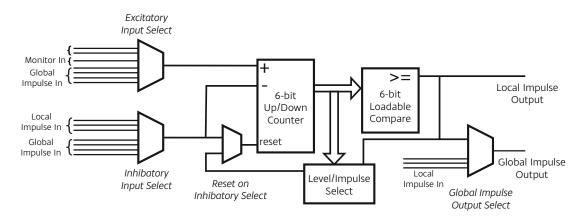

| 5.3  | General overview a single CIU                  | 132 |

|------|------------------------------------------------|-----|

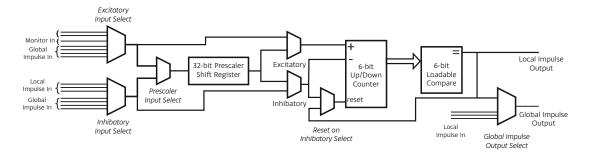

| 5.4  | LUT optimised 6-bit Counter for the CIU        | 133 |

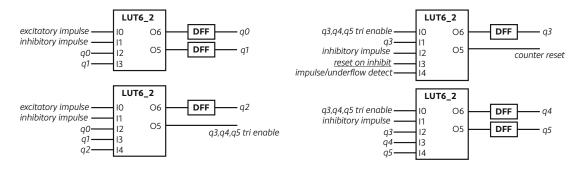

| 5.5  | LUT optimised 6-bit Match Unit for the CIU     | 134 |

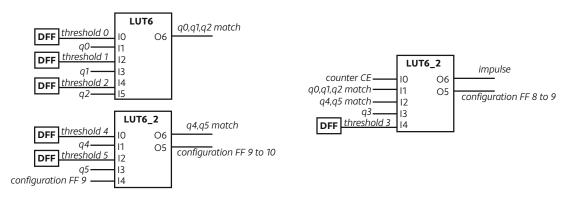

| 5.6  | CIU Prescalar Implementation                   | 135 |

| 5.7  | LUT Implementation of the CIU Input Muxes      | 136 |

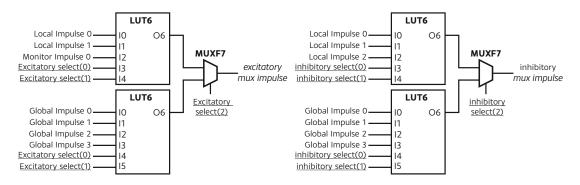

| 5.8  | Overview of the Level CIU Variant              | 138 |

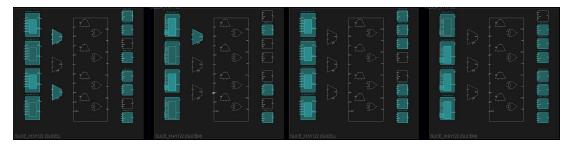

| 5.9  | LUT Translation of a CIU Tile                  | 138 |

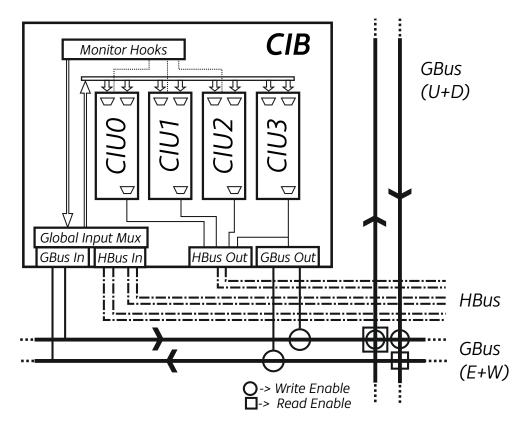

| 5.10 | Overview of a CIB Tile                         | 140 |

| 5.11 | Overview of CIB Global Routing Resources       | 141 |

| 5.12 | CIB Input Multiplexors and LUT Implementation  | 144 |

| 5.13 | CIB Output Multiplexors and LUT Implementation | 145 |

| 5.14 | LUT Translation of the CIB Router              | 146 |

| 5.15 | LUT Translation of the CIB Tile                | 147 |

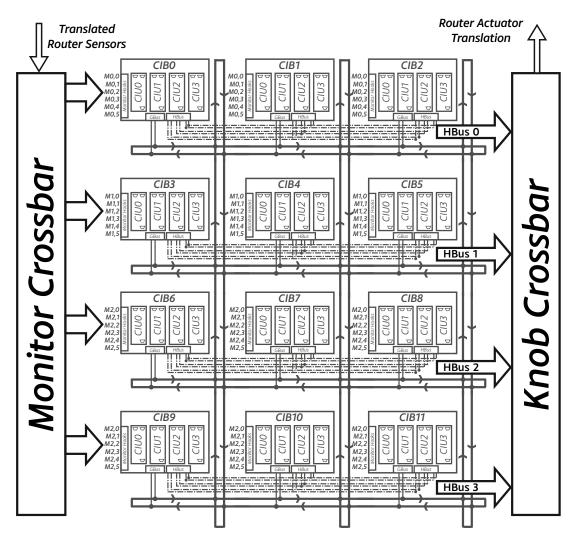

| 5.16 | Overview of the 4x3 CIA                        | 150 |

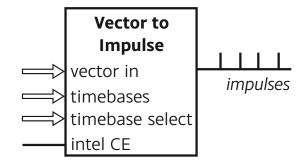

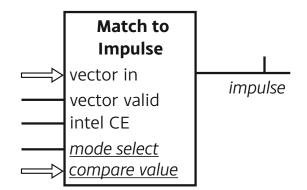

| 5.17 | Monitor Translator: Vector to Impulse          | 155 |

| 5.18 | Monitor Translator: Match to Impulse           | 155 |

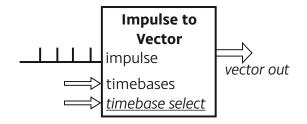

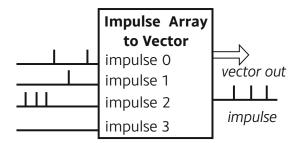

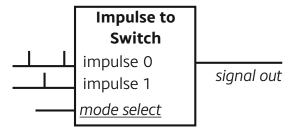

| 5.19 | Knob Translator: Impulse to Vector             | 157 |

| 5.20 | Knob Translator: Impulse Array to Vector       | 158 |

| 5.21 | Knob Translator: Impulse to Switch             | 158 |

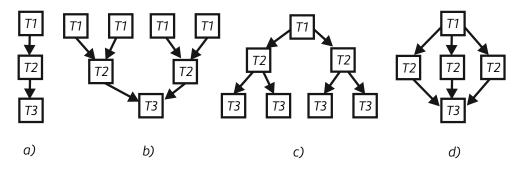

| 6.1  | Test Task Graphs for Experiments               | 163 |

| 6.2  | Results of Experiment 1.1                      | 169 |

| 6.3  | Results of Experiment 1.2                      | 171 |

| 6.4  | Results of Experiment 1.3                      | 173 |

| 6.5  | Task Allocation Experiment Concept             | 176 |

| 6.6  | Interaction Model Software Design              | 178 |

| 6.7  | Results of Experiment 2.1                      | 180 |

| 6.8  | Packet Analysis for Experiment 2.1             | 182 |

| 6.9  | Task Switching Analysis for Experiment 2.1     | 183 |

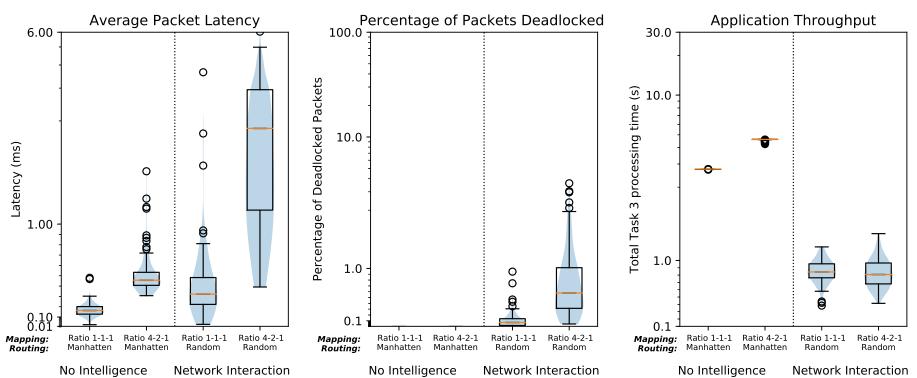

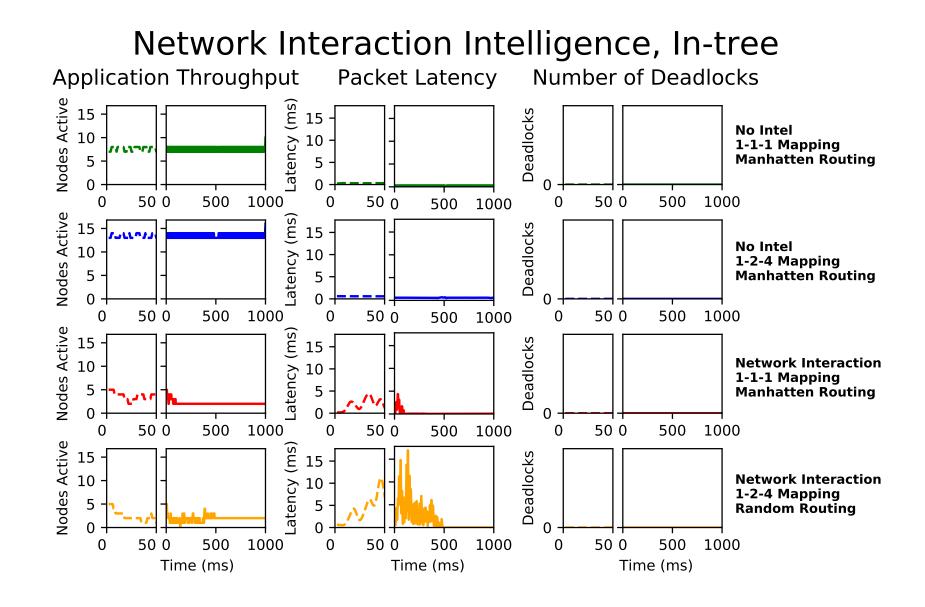

| 6.10 | Results of Experiment 2.2                      | 185 |

| 6.11 | Packet Analysis for Experiment 2.2             | 186 |

| 6.12 | Task Switching Analysis for Experiment 2.2     | 187 |

| 6.13 | Results of Experiment 2.3                      | 189 |

| 6.14  | Packet Analysis for Experiment 2.3         | 190 |

|-------|--------------------------------------------|-----|

| 6.15  | Task Switching Analysis for Experiment 2.3 | 191 |

| 6.16  | Results of Experiment 2.4                  | 193 |

| 6.17  | Packet Analysis for Experiment 2.4         | 194 |

| 6.18  | Task Switching Analysis for Experiment 2.4 | 195 |

| 6.19  | Foraging For Work Software Design          | 198 |

| 6.20  | Results of Experiment 3.1                  | 200 |

| 6.21  | Packet Analysis for Experiment 3.1         | 201 |

| 6.22  | Task Switching Analysis for Experiment 3.1 | 202 |

| 6.23  | Results of Experiment 3.2                  | 204 |

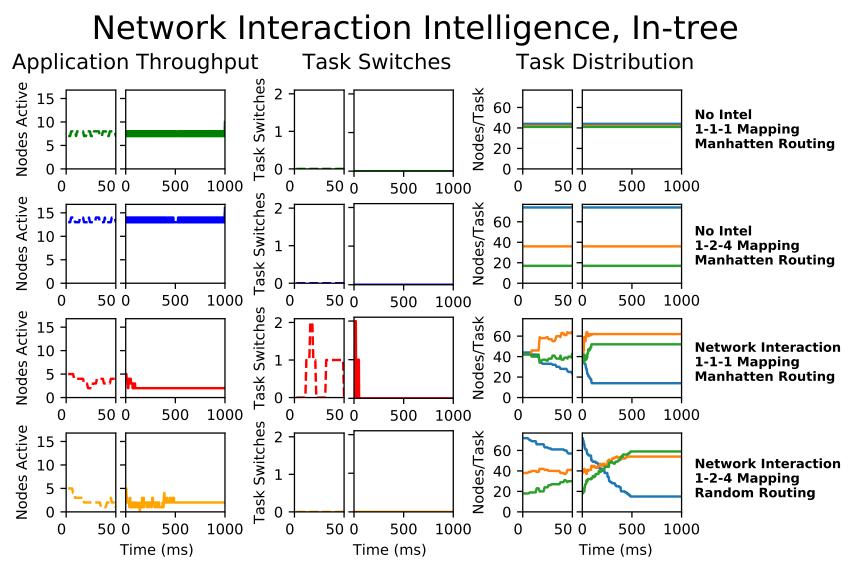

| 6.24  | Packet Analysis for Experiment 3.2         | 205 |

| 6.25  | Task Switching Analysis for Experiment 3.2 | 206 |

| 6.26  | Results of Experiment 3.3                  | 208 |

| 6.27  | Packet Analysis for Experiment 3.3         | 209 |

| 6.28  | Task Switching Analysis for Experiment 3.3 | 210 |

| 6.29  | Results of Experiment 3.4                  | 212 |

| 6.30  | Packet Analysis for Experiment 3.4         | 213 |

| 6.31  | Task Switching Analysis for Experiment 3.4 | 214 |

| 6.32  | Self-Regulation Model Software Design      | 217 |

| 6.33  | Results of Experiment 4.1                  | 219 |

| 6.34  | Packet Analysis for Experiment 4.1         | 220 |

| 6.35  | Task Switching Analysis for Experiment 4.1 | 221 |

| 6.36  | Results of Experiment 4.2                  | 223 |

| 6.37  | Packet Analysis for Experiment 4.2         | 224 |

| 6.38  | Task Switching Analysis for Experiment 4.2 | 225 |

| 6.39  | Results of Experiment 4.3                  | 227 |

| 6.40  | Packet Analysis for Experiment 4.3         | 228 |

| 6.41  | Task Switching Analysis for Experiment 4.3 | 229 |

| 6.42  | Results of Experiment 4.4                  | 231 |

| 6.43  | Packet Analysis for Experiment 4.4         | 232 |

| 6.44  | Task Switching Analysis for Experiment 4.4 | 233 |

| 7.1   | Results of Experiment 5                    | 242 |

| · • ± |                                            |     |

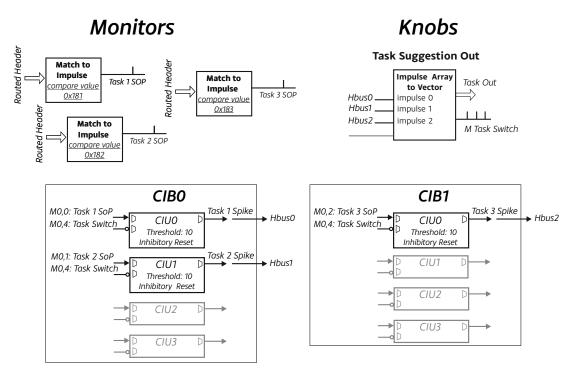

| 7.2         | Layout of the CIA for the Interaction Network Intelligence Model | 246 |

|-------------|------------------------------------------------------------------|-----|

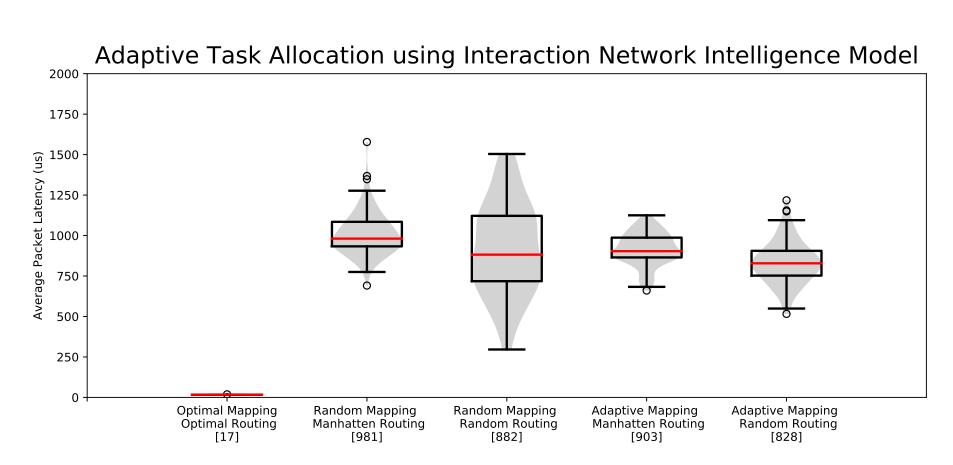

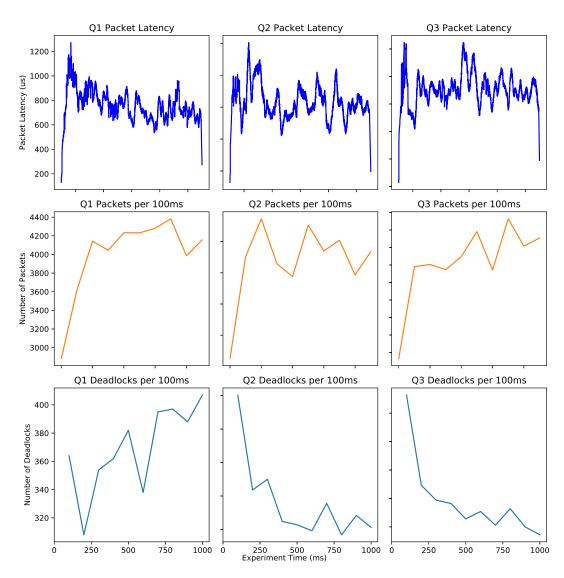

| 7.3         | Results of Experiment 6                                          | 248 |

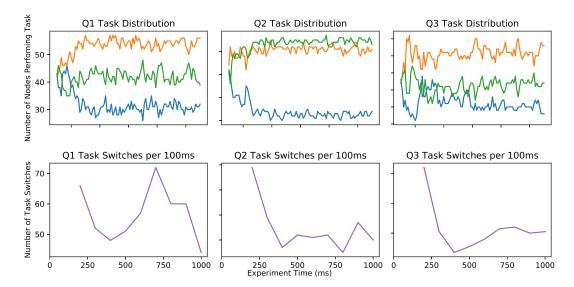

| 7.4         | Packet Analysis for Experiment 6                                 | 250 |

| 7.5         | Task Switching Analysis for Experiment 6                         | 251 |

| 7.6         | CIA Configuration for the FFW Model                              | 254 |

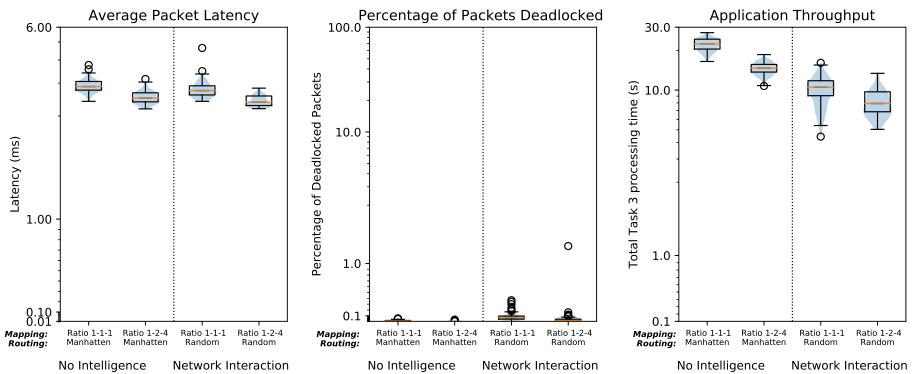

| 7.7         | Results of Experiment 7                                          | 256 |

| 7.8         | Packet Analysis for Experiment 7                                 | 257 |

| 7.9         | Task Switching Analysis for Experiment 7                         | 258 |

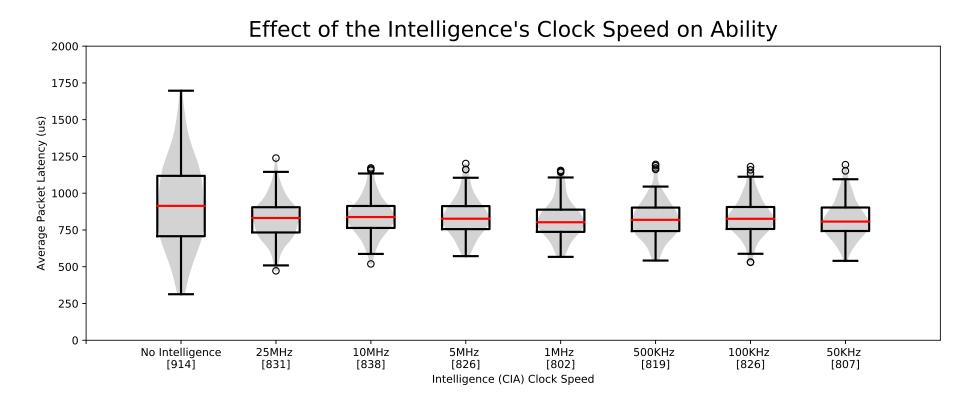

| 7.10        | CIA Frequency Sweep with Interaction Network Model               | 261 |

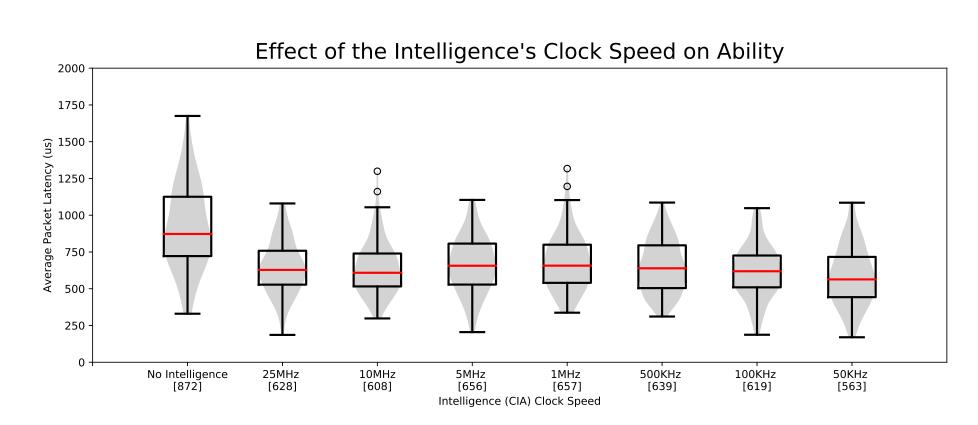

| 7.11        | CIA Frequency Sweep with FFW Model                               | 262 |

|             |                                                                  |     |

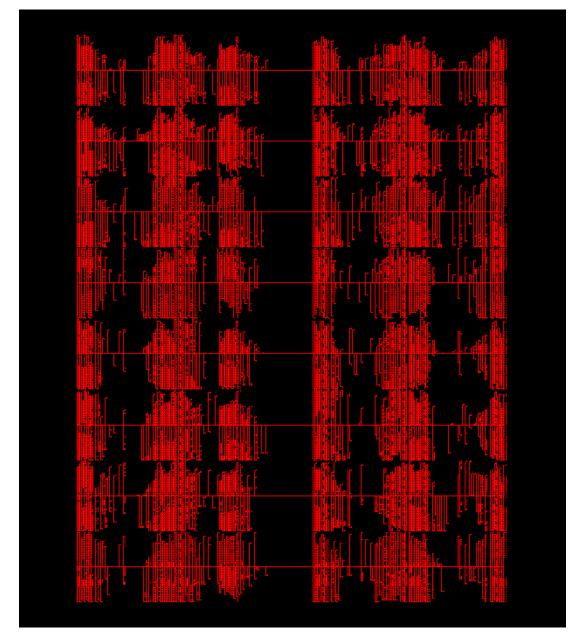

| <b>B</b> .1 | Post-Implementation view of Three Centurion Nodes                | 284 |

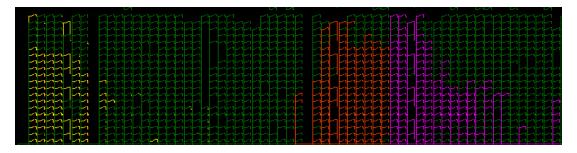

| B.2         | Distribution of Clock Divider-Sourced Clock Nets                 | 285 |

| B.3         | Centurion Reset Architectures                                    | 286 |

# **List of Tables**

| 2.1  | Survey of existing adaptive hardware platforms           | 49  |

|------|----------------------------------------------------------|-----|

| 3.1  | Translation between Bio Inspired Model and HW Model      | 70  |

| 4.1  | Centurion Control Tokens                                 | 78  |

| 4.2  | Register Map of the RCAP                                 | 89  |

| 4.3  | Parameters for Generating the Microblaze MCS             | 98  |

| 4.4  | Hardware Resource Requirements of the Processing Element | 98  |

| 4.5  | Possible Frequencies of the Clock Divider                | 109 |

| 4.6  | Resource Requirements of a Single Centurion Node         | 113 |

| 4.7  | Breakdown of Resource Requirements for a Centurion Node  | 114 |

| 4.8  | Total Hardware Resource Requirements                     | 123 |

| 4.9  | Address Map of the Nodes                                 | 124 |

| 4.10 | Address Map of the Experiment Controller                 | 124 |

| 5.1  | Structure of CIU Configuration Bitstring                 | 139 |

| 5.2  | Structure of CIB Configuration Bitstring                 | 148 |

| 5.3  | Hardware Resources required by the CIA                   | 152 |

| 5.4  | List of CIA Monitors and their Translation Units         | 156 |

| 5.5  | List of CIA Knobs and their Translation Units            | 159 |

| 5.6  | Structure of CIA Configuration Bitstring                 | 160 |

| 6.1  | Application Model Settings                               | 166 |

| 7.1  | Baseline Performance without Fault Injection             | 243 |

| 7.2  | Fault Tolerance Performance                              | 243 |

| 7.3  | Distribution of Workload in Experiment 6                 | 249 |

| 7.4  | Deadlock Figures for each Configuration of Experiment 6  | 249 |

| 7.5  | Distribution of Workload in Experiment 7                 | 255 |

| 7.6  | Deadlock Figures for each Configuration of Experiment 7  | 257 |

| A.1  | Clocking Resources used per Clock Region                 | 280 |

## Acknowledgements

Many thanks to my supervisors Dr. Martin Trefzer and Prof. Andy Tyrrell for all of their support, guidance and many interesting discussions throughout the duration of the PhD process. I'd also like to thank all of my family for their understanding and patience when I kept talking about ants through all of these years. Likewise to the friends in the Department who have provided many enjoyable pub and climbing sessions during my time at York.

This work would not have been possible without the continuous dedication, assistance and encouragement provided by the SCR coffee machine. And also by Sarah. Thank you to you both.

## Declaration

I declare that this thesis is a presentation of original work and I am the sole author. This work has not previously been presented for an award at this, or any other, University. All sources are acknowledged as References. The research presented in this thesis features in a number of the author's publications listed below:

- Matthew Rowlings, Andy M. Tyrrell, Martin A. Trefzer. *Embedded Social Insect-Inspired Intelligence Networks for System-level Runtime Management* in: *Design Automation and Test in Europe (DATE)*, March 2020

- Matthew Rowlings, Andy M. Tyrrell, Martin A. Trefzer. *Hardware Implementation of Social-Insect-Inspired Adaptive Many-Core Task Allocation* in: *IEEE Symposium Series on Computational Intelligence (SSCI)*, December 2016

- Matthew Rowlings, Andy M. Tyrrell, Martin A. Trefzer. *Hardware Implementation of Social-Insect-Inspired Adaptive Many-Core Task Allocation* in: *IEEE Symposium Series on Computational Intelligence (SSCI)*, December 2016

- Matthew Rowlings, Andy M. Tyrrell, Martin A. Trefzer. Social-Insect-Inspired Adaptive Task Allocation for Many-Core Systems in: IEEE World Congress on Computational Intelligence (WCCI 2016), July 2016

- Matthew Rowlings, Andy M. Tyrrell, Martin A. Trefzer. Social-Insect-Inspired Networking for Autonomous Fault Tolerance in: IEEE Symposium Series on Computational Intelligence (SSCI), December 2015

- Matthew Rowlings, Andy M. Tyrrell, Martin A. Trefzer. Social-insect-inspired networking for autonomous load optimisation in: Procedia CIRP 38, pages 259-264

# **Chapter 1**

\_\_\_\_

# Introduction

### 1.1. Overview

The advancement of silicon implementation technologies has recently reached a stage in its development where integrated circuit performance and cost has revolutionised the use of, capabilities of and number of electronic devices that we use during our day-to-day lives. The improvements in transistor densities, switching frequencies and lower power consumption of integrated circuits over the last decade now allows us to use complex embedded systems in more and more applications; from advanced medical devices to the high-power embedded computing requirements of autonomous vehicles.

However, as state-of-the-art device technologies come ever-closer to the atomic scale, challenges intrinsic to deep sub-micron fabrication emerge [1][2]. Engineers are required to include large design tolerances to ensure that their designs will not fail after it leaves the manufacturing line, confounded by the device variability challenges that mean a design that works comfortably within specifications on one silicon die may not work on the die created on the next wafer [3]. Unfortunately as feature sizes get smaller, these problems are only going to be of more importance as design margins tighten and very small scale variations of the silicon wafer become the overriding concern [4][5]. Thus the fundamental unit of the digital designer's toolkit, the transistor, is becoming less and less reliable with more variation in its key behavioural properties.

Whilst engineering suffers from such unreliable and varied fundamental blocks, some of the great feats of natural systems have been found to be due to inherent variability and unreliability within the building-blocks of biological systems [6] [7] [8] [9] [10]. There are clearly some value for engineering systems in such processes that biology has developed to overcome and exploit these low level problems. With a suitable model extracted and translated from particular biological processes, there is no reason that engineered systems could not also adapt to variation and cope with faults in their constituent parts.

#### 1.1.1. Many-Core Systems

Hardware co-processors typically provide a performance improvement as well as reduced power (and thus thermal) load compared to a general propose processor implementation. The hardware co-processor model also scales well with parallel problems and so has been used heavily in high performance, embarrassingly parallel applications such as graphics pipelines. Many-core systems [11][12] aim to take this approach to an architectural level whereby lots of heterogeneous hardware accelerators (or processing cores with hardware accelerators attached) are connected together with levels of specialism such that the resulting task architectures distributes thermal and power load across the die and reducing the occurrence of processing "hotspots".

As well as Dark Silicon [13][14], many-cores can also be used to tackle the issue of device variability and post-manufacture failures through the use of the classic fault-tolerance technique N-modular redundancy. With several copies of the same co-processor within the many-core architecture, it is easily seen that the tasks undertaken by a under-performing or failed core (due to device variation or a post-manufacture fault due to device degradation) can be undertaken by another co-processor of the same type located at a different geometric area of the die that may not suffer from the same inherent silicon characteristics.

### 1.1.2. Many-Core Design Challenges

Whilst many-core architectures seem well poised to tackle the previously discussed problems, they also bring a large number of different complex issues when designing systems for such an architecture. Many-core architectures tend to be organised in a grid-like fashion on the die with a Network-on-Chip (NoC) used to interconnect the co-processors, also known as Processing Elements (PE). A NoC has many similarities with standard computer networking but tends to be simpler with more deterministic workings. Starting from a grid of PEs, a many-core designer would need to determine: 1) The task (or co-processor) that each PE is specialised for

- The thermal/power budget of this task, which may limit what tasks the adjacent

PEs can undertake

- The expected data throughput of this task, including the thermal requirements on the NoC local to the PE

- A list of tasks/PEs that this node will need to communicate with before, during or after data processing, including specific throughput requirements

2) A routing strategy that connect tasks that need to communicate together, with throughput and thermal requirements on the NoC paths met

- Analysis of alternative/redundant routing paths and how these affect the calculation of each data-transfer pathway in the task graph

- Choice of routing protocol. This will impact the routing paths, some protocols require significant buffering or less deterministic routing strategies

- Analysis, prediction and elimination of any deadlock or livelock scenarios within the chosen NoC routing strategy

3) Consider fault scenarios that will change the balance of tasks in the many-core due to PE failure or the performance of the NoC (e.g. a link that may fail, or a link that has to reduce throughput due to unexpected thermal environment)

- This will require re-analysis of all the previous parameters for the different fault scenarios or environmental changes

This is a huge amount of analysis that scales exponentially with not only the number of nodes in the many-core, but also with the number of tasks mapped to it. If many-core is going to be the platform that allows us to fully utilise future silicon devices then not only must it support a huge number of processing elements, but we must also be able to use it in a multi-application environment. Despite these problems, we see some aspects of many-core design already being used in embedded systems [15], and it is a active research field with lots of outstanding challenges [16][12].

### 1.1.3. Bio-Inspired Hardware

The huge number of interacting design parameters of a many-core system has many similarities with complex systems found within biology. Natural optimisation methods such as evolution and development have emerged as biology's way of navigating very high-dimensional pareto-front tradeoffs. Using biological inspiration in electronic systems design has been a mature research area for many years now. Despite this, we have not seen an uptake of using biologically inspired models to solve problems in hardware design for the commercial electronics world. There are many reasons for this gap, but the following are some of the main factors:

- Cost of implementing the biological model in hardware is high and non-scalable [17]

- An advance in technology has rendered the problem the biological inspiration solves as redundant [18]

- The biological model is difficult to validate against a set of requirements [19]

- Difficulty integrating the systems application with the biological model [20] [21]

As designing for many-core systems allows a degree of abstraction away from the digital substrate with the design challenges at a much higher level, this opens the possibility of a different bio-inspired approach than the traditional "building-blocks" up approach seen in many bio-inspired research projects. The model of a processing element communicating with other processing elements via the NoC opens up a link with many highly-scalable biological models.

#### **1.1.4. Social Insect Intelligence**

Large social insect colonies also require a wide range of important tasks to be undertaken to build and maintain the colony and in most nests there are many thousands of workers available to offer their assistance to ensure the expansion and survival of the colony. However, there is a crucial equilibrium between the number of workers performing each task that must not only be maintained but must also continuously adapt to sudden changes in environment and colony need. What is most fascinating is that social insects can sustain this balance without any centralised control and with colony members that have relatively little intelligence when considered on their own. Due to this simplicity and evident scalability it would seem that social insects have evolved an interesting scalable approach to task allocation that could be applied to very large many-core systems.

When evaluating a bio-inspired hardware system there are several implementation possibilities and abstractions to chose from. In this work, relevancy to near-future hardware platforms was considered a priority. Device densities have reached a stage where large amounts of computing power are available per chip, this is reflected in the recent rise of high-performance consumer embedded systems (e.g. smartphones [22]). Therefore, it is felt that applicability to modern systems is highly important. This motivates the creation of a large-scale many-core system as part of this work. The emphasis on applicability to hardware systems also drives the implementation and evaluation of the biological models. These models could be evaluated using simulation models, starting from biologically "true" models and refining them such that they can be applied to the hardware system. However there are two reasons for not following this route:

- (a) The biological models for social-insect intelligence are relatively new, a consolidated model is not available [23] and the research into these models is active. Modelling techniques used for the biological models that this work takes inspiration from are not coherent across the models, with Kauffman networks [24], oscillatory dynamics models [25] and Markov chains [26] being used. Further work would be required in this field to use a direct implementation of the biological models as a starting point for the embedded intelligence.

- (b) Simulation of the biological models would also require simulation of the manycore system. One millisecond of a behavioural simulation of a 128-core Centurion takes around 1 hour to complete and so running an experiment of one second (as used in the experiments in this thesis) would have taken a large number of days to complete. As each experiment consists of averaging from a large number (100 in most experiments) of initial parameters, experiments would take an infeasible amount of time. Therefore an abstraction of the many-core would

also be required for simulation. Architecture of efficient large-scale processor simulations abstract the cores to tasks running on a CPU or cluster (for example [27]). This requires precise modelling of communication structures between nodes (critical due to the use of wormhole routing between nodes) and also a modelling of time to allow frequency scaling of cores to be supported. The intended low level hardware signals that the embedded intelligence hooks into will need to be extracted, abstracted and then integrated into the biological simulation model. Understanding how to achieve this becomes more difficult as the many-core abstraction level increases, which is a direct counter to the need of a high node abstraction level for simulation scalability purposes. Modelling of the NoC could also help with gaining accuracy in the simulation model, at the cost of adding overhead to the simulation time. There are many NoC developments and simulation models [28]. When the constraints of proven large scalability and a hardware implementation are applied to a survey of existing NoC developments [28], only three NoCs out of the 60 evaluated had both been implemented for FPGA or ASIC (to ensure applicability to near-future technologies) and supported over 50 processing cores (to prove scalability).

Therefore, in this work simulation is not used as the primary evaluation method. All inputs and outputs of the embedded intelligence interact directly with hardware signals. This has the benefit of:

- A shorter experiment runtime, an experiment of one second only takes one second to run and around 250ms to collect the data and set up the next experiment run.

- No issues with simulation-reality gaps or need to prove correctness of a simulation model to the target hardware platform that it is simulating.

- A hardware-suitable implementation of the biological model is enforced that does not require complex operations that are hardware-resource expensive (e.g. large matrices, solving of differential equations, floating point arithmetic).

- Direct manipulation of low-level hardware signals. This is inherently a hardwareresource efficient approach, allowing support of the largest number of cores pos-

sible.

• A hardware platform with unique access to low-level many-core signals that can be used be other many-core research experiments without the effort of configuring, deploying and debugging a NoC that is not designed for low-level manipulation of its control signals.

Smaller simulations were used during development of the models using behavioural simulation of a 24 core Centurion, however the results of these not presented as the intelligence models developed for them are used in the hardware experiments that are presented in the thesis.

### **1.2.** Hypotheses

The work presented in this thesis establishes how many-core systems can be made more robust by using emergent self-organisation based on the decision pathways of individuals of social-insect colonies. The intelligence is ensured to be hardware efficient by taking inspiration from a simple biological model and through research study using a large-scale hardware platform typical of near-future many-core systems.

In this thesis I propose and evaluate a new source of biological inspiration for digital electronic systems based on the following hypothesis:

**Hypothesis:** Embedded social insect intelligence models derived from studies of the social insects can exhibit highly-scalable adaptive behaviours suitable for managing complex digital electronic systems.

With the following supporting sub-hypotheses:

Sub Hypothesis 1: Models of task allocation in social insect colonies provide appropriate inspiration for enabling self-organising task mappings for many-core systems. Sub Hypothesis 2: The decision making processes of individual social insects can inspire embedded intelligence circuitry that allow run-time self-optimisation of digital sub-systems to be achieved.

### **1.3. Research Contributions**

During the undertaking of this work the following research contributions have been made to the field of digital electronics:

- The creation of *Centurion* many-core system a 128-node many-core platform for experimenting with large scale many-core systems in hardware.

- The design of the *Configurable Intelligence Array*, a novel artificial intelligence hardware platform based on simplified aspects of spiking neural networks but highly optimised for efficient FPGA and digital circuit implementations.

- Selection and Evaluation of two reference task allocation models from the biological literature and understanding of their strengths and weaknesses when applied in an artificial emergent environment.

- Methodologies for converting response-threshold based artificial intelligent behaviours into forms that are suitable for embedding in modern digital systems.

## 1.4. Thesis Structure

This thesis consists of eight chapters and is structured as follows:

- Chapter 2 gives an outline of the trends of modern VLSI design and summarises the problems that are expected to arise in the medium term that could spell the end of the device size and performance scaling that we have been accustomed to over the last few decades. It also introduces many-core systems and autonomic computing as potential design solutions to these problems.

- Chapter 3 explores the biological literature to gain understanding on how social insect colonies are organised and describes the key biological models created to capture the adaptive properties of large social insect colonies.

- Chapter 4 introduces the *Centurion* 128-node many-core platform designed for the experiments presented in this thesis and describes its FPGA implementation.

- Chapter 5 is a second implementation chapter that covers the design of the *Configurable Intelligence Array*, which is then embedded within Centurion and used to implement the social insect-inspired models.

- Chapter 6 presents the results of experiments that validate the emergent behaviour of the social insect intelligence when used to control aspects of the Centurion platform.

- Chapter 7 expands on the adaptive behaviour goals of investigated in Chapter 6 with a fault injection experiment and shows how adaptive behaviours can be implemented using the Configurable Intelligence Array.

- Chapter 8 reviews the social-insects as a source of bio-inspiration for adaptive systems and suggests improvements and further work that could be undertaken with the models, Centurion and the Configurable Intelligence Array.

# **Chapter 2**

# **Challenges of Large Scale VLSI Design**

### 2.1. Overview

The continuous advancement of semiconductor based technologies has enabled many digital electronic engineering paradigms as transistor densities and power consumption improved over time with each new technology. Today, this allows digital engineers to build complex *Systems-on-Chips (SoCs)*, comprised of hundreds of digital sub-systems, all integrated together into one silicon die. It has been a relatively fast-paced transformation period, driven by the unrelenting Moore's law [29], that has seen large shifts in digital system design methodology as each step forward allowed designers to use a higher level of complexity and abstraction. This has resulted in engineers advancing from a transistor-to-transistor design based on hand drawn circuit diagrams, to the specification description based EDA tool flows that we enjoy today, within only a few decades.

However, this advancement of digital hardware has been focused sharply on siliconbased transistors and these have fundamental physical properties (e.g. leakage current [30], heat dissipation) that at certain technology sizes will start to affect how many transistors can be integrated into a chip. In general the smaller the transistor the more such properties become a fundamental limitation to the density and performance of silicon-based transistors, resulting in our classical route of technological advancements eventually grinding to a halt. Dennard Scaling [31] was the first of these properties to fail and has forced a change in the design of complex VLSI systems, with many other limitations likely to be hit in the near future if digital hardware with silicon-based transistors prevails . Modern design paradigms such as *Many-Core Systems* built on *Networks-on-Chip (NoCs)* promise new ways of overcoming imminent limitations, but with the penalty of an extremely costly (indeed almost prohibitive) increase in design complexity.

This chapter will introduce the problems that current and near-future deep sub-micron VLSI technologies will need to overcome to realise the next generation of high-performance digital electronic systems. Hardware implementation device trends and challenges are explored in Section 2.2. Many-Core Systems and their design challenges are then introduced in Section 2.3. Finally, Section 2.4 will introduce the *Autonomic Computing*

paradigm as a means of tackling these challenges.

### 2.2. Present and Upcoming Challenges in VLSI Devices

#### 2.2.1. Future Technology Trends

As we start to reach silicon's fundamental physical and performance limits, research into the next-generation digital device technologies has focussed on either finding a replacement for silicon as an implementation technology or using the silicon fabric in novel ways to extract more performance per device. This is a broad and speculative field and so the 2015 reporting of the *International Technology Roadmap for Semiconductors (ITRS)*[32] and the 2018 reporting of the follow up group *IEEE International Roadmap For Devices and Systems (IRDS)* [33] provide a useful summary of the medium-term challenges that the technology presented in this thesis aims to address.

The ITRS and IRDS reports are produced to detail upcoming challenges in the semiconductor industry and are prepared by representative experts from several industrial bodies including: European Semiconductor Industry Association, Japan Electronics and Information Technology Industries Association, Korean Semiconductor Industry Association, Semiconductor Industry Association and Taiwan Semiconductor Industry Association [32]. Therefore it can be considered a reliable indicator of the problems that the semiconductor industry feel are most important to tackle. The ITRS/IRDS reports consider a wide range of consumer application uses: from high-performance data centre use, low-power IoT applications and also requirements of future mobile devices that strike a tough balance between power and embedded high-performance [34] [1]. Most of the sub-reportings summarise that in the medium term many electronics fields will require either a replacement for CMOS technologies or use of CMOS technologies in advanced ways. They predict that the growth of use cases and demand for ever more computation power will continue for at least the next 20 years and so these medium term challenges are likely to be required and will drive research directions for the foreseeable future.

The following summaries explore some of the most pressing challenges for digital VLSI systems.

#### 2.2.2. Dennard Scaling and Dark-Silicon

Recently we have reached a fundamental transistor size where Dennard scaling starts to break down [13]. Previously the threshold voltage of the transistors on the die would scale together with the supply voltage, allowing the supply voltage to drop with each process generation. However, now the supply or threshold voltage cannot be dropped without simultaneously increasing either the transistor delay or leakage [11], forcing the supply voltage through each recent process generation to be fixed. This has dire consequences when combined with the scaling in transistor density as the power required by the chip will increase exponentially with each generation, to the point that we cannot provide the power required to switch all the transistors on a chip at their maximum frequency or even remove the thermal energy produced by this switching [35].

This limitation has been dubbed *Dark Silicon* and has been highlighted as a crucial problem for the semiconductor industries, with predictions claiming that at an 8nm process over 50% of a chip may need to be powered off to act as thermal buffering [13]. Further analysis in [36] suggests that this figure can be reduced with DVFS management. Their experiments show that between features sizes and, even with a 40% Dark Silicon overhead at 8nm, the performance benefits of a smaller feature size outweigh the Dark Silicon overhead when overall system performance is considered. These results however are dependant on a thermal analysis and use of DFVS, this will be application specific and requires extra design analysis and runtime management which may not scale to very large systems. Designs are starting to use 7nm processes and the evaluation presented in [37] implemented a 64-core design using a 7nm FinFET technology. The results aligned with the predictions of [13], using highperformance FinFETs (Super-Threshold) and a 15W power budget it was found that the system had a Dark Silicon overhead of 64% (i.e. only 36% of the design cores could be run at full speed at once). If lower performance, but more power-efficient, Near Threshold FinFETs were used then this overhead improved to 19%.

Consequently, several research directions have emerged to tackle the Dark Silicon problem, of which many-core systems are one of them [11][12]. Four possible directions for Dark Silicon mitigation have been outlined in [14]:

- 1. Smaller dies: By reducing the number of transistors per die the overall power and thermal requirements of the die can be reduced. However this approach neglects the fact that the area of the die is a fundamental requirement for heat dissipation performance and so the frequency of operation is then limited, increasingly an issue as transistor density (and therefore the intensity of hotspots) increases. This approach is also restricted in cost savings as the design costs will remain largely the same, if not increasing due to the need to fit the design into a smaller area. This could even require several chips to achieve the required functionality, practically reversing the trend to fit complex systems within on chip with the effect of increasing system power consumption and unnecessary overheads such as greater off-chip communication channels (requiring more IO pads and more complex PCB layouts).

- 2. Part-time logic: Whilst Dark Silicon is important for maintaining power and thermal constraints, it should be emphasised that the silicon does not have to be completely unused all the time and can instead be used for circuitry that is of either low frequency operation or of infrequent use. Through the use of techniques such as clock gating and Dynamic Voltage and Frequency Scaling (DVFS), the energy consumption of specific parts of the chip can be controlled. This has seen some application in modern multi-cores as a "turbo" function where the frequency of some cores is scaled back to allow another core to run at a higher frequency. By careful scheduling of the application or scheduling the use of DVFS it is also possible to move some of the problem to the temporal domain; parts of the system are run at full performance until the thermal capacity of the chip is reached at which point the performance is reduced until the chip has had time to cool. This technique also favours assigning large parts of the chip to memories such as caches, as only a small subset of the memory is accessed (and therefore active) at any one time giving a high "darkness" per square millimetre when compared to computational logic despite being operated at its maximum

frequency. However few applications will benefit from just a de-facto increase in cache resources so a vast amount of silicon will have to be left dark and is thus wasted.

- 3. Specialised co-processors: An elaboration of the previous technique is to utilise the dark silicon for specialised co-processors. The co-processors consist of specialised hardware accelerators that perform a specific operation with far greater performance and energy efficiency than the general purpose processor. They are also clock gated and may support DVFS, allowing them to be disabled when not in use. Execution switches between a general purpose processor and the coprocessors (possibly many copies of the same for a parallel application) in such a way that the most efficient core for a particular operation is always used. Unused cores are switched off resulting in a reduction in total switching capacitance for a particular operation, this is in contrast with the previous approach where the aim is to minimise energy use through frequency and voltage management. This approach makes full use of unused dark silicon and it can be envisioned that systems will consist of hundreds or thousands of tiny co-processors residing in otherwise wasted silicon resources. Some care will be required at the design stage to ensure that energy savings are not compromised by inefficient communication between the cores and new programming tools will be required to shield the underlying complexity of the many-core away from the programmer without jeopardising the potentially great improvements offered by co-processor driven architectures.

- 4. New material or silicon breakthrough: The final hope for combating dark silicon comes from changes in the silicon platform itself, a possible move is away from MOSFET technologies due to their fundamental limits on leakage current at room temperature. Two candidate technologies highlighted in [14] are tunnel-FETs (TFETs) and Nanoelectromechanical system (NEMS) switches, both of which offer significantly better leakage performance. However these processes also have their limitations: TFETs are unsuited to be applied to high performance circuitry due to lower on-currents and NEMS technology suffers from slow switching times. This limits their immediate integration into chips, but

they are a key focus of future semiconductor fabrication research and may indeed find niche applications.

From this survey it is clear that Dark Silicon is going to be a significant problem that we must overcome if we are still going to reap the benefits of increasing transistor density. Unless new materials or breakthroughs at the physical layer are made, it is almost certainly going to fundamentally change the way we design complex digital systems; indeed with the adaptation of many-core it could be said that this change has already started to happen. Out of the above directions, it seems that the first is not only rather bleak in terms of future innovation but it is also not particularly scalable or future proof. It will raise the cost of systems, introduce longer engineering times and limit the amount of complexity we can achieve within a system.

In contrast, the fourth direction is the most encouraging in terms of a more holistic solution of the issues regarding dark silicon and indeed the ITRS highlights novel fabrication substrates such as graphene and spin materials as of significant research interest in their Emerging Research Materials [38] and Emerging Research Devices [39] summaries from 2013. Alternative silicon based technologies are explored in the Process Integration, Devices and Structures summary (also from 2013) [40], with a focus on sub 10nm technologies and three-dimensional architectures; but with also a strong focus on improving reliability and other fabrication scaling issues. The 2018 IRDS Metrology report [41] shows that the field has evolved slightly with the challenges focussing on both sub-7nm technology and also larger feature sizes. Implementation of 3D structures (e.g. finFETs) is a key element of the report and so a large focus of this report covers device measurement and feature implementation verification for 3D structures. This shows that whilst building these structures at feature sizes of 10nm is feasible, managing and verifying yield is still a large challenge despite introduction of new fundamental structures. The report also introduces the idea that research into AI predictions of yield using models of a process combined with process parameters and measurement points could be used to predict die measurements that cannot be taken for scale reasons.

The broad range of research directions suggested by the ITRS (shown in the *Executive Summary* of all ITRS assessments [34] [1]) suggests that it is not clear what silicon's

replacement will be or indeed when it will disrupt silicon's dominance. Therefore, the principal method for a medium-term approach to tackling dark silicon should be through the second and third research directions [42].

#### **2.2.3.** Device Variability

This problem is exaggerated when another major problem affecting modern semiconductors is considered, namely fabrication related issues such as *process variability* and *manufacturing defects*. During fabrication it is impossible to keep the physical characteristics of all transistors and interconnections consistent across the chip and so some local variation in performance occurs. As the size of transistors continuously shrinks these margins become more significant to the point that it becomes inevitable that some parts of a chip will be out of stable operating range for a given operating environment whilst other parts may be well within their margins. No two dies are the same and so this variability is seen not only across the billions of transistors on the chip, but then again across the millions of chips produced in a manufacturing run. Therefore a detailed characterisation of the maximum operating parameters of each individual chip is not possible as this would require exhaustive testing (of all potentially critical paths) under a huge range of operating conditions to expose all possible faults.

Consequently the technique of *binning* [43] is now a common practice of the semiconductor manufacturers; each device is evaluated with a simple test depending on the operating feature required and then device guarantees are based on the performance of this test. For example a microprocessor manufacturer may bin their products based on the maximum frequency at which they can operate without faults, this may be well below the design maximum frequency of the device but it would allow a device to still be sold in spite of a lower performance; this is far better from a yield perspective than disposing of all under-performing chips. However, binning is clearly limited by the binning metric used to evaluate it and may still require very large reductions in performance of many devices in a production run to get a reasonable yield. Variability issues are only going to get worse with smaller fabrication processes; and so the reduction of performance may be so severely limiting that little of the advantage offered by a new process may actually be exploited by the device. Also the binning metric does not scale well with the many-core approach taken to combat dark silicon, in both terms of testing time and effectiveness of binning; with hundreds of cores on the chip it only takes one under-performing core to render the whole device destined for a poor device binning even if all other cores work perfectly well at their maximum performance, drastically limiting the yield of potential for high performing devices [3]. Thus it does not seem that binning is a sustainable approach to tackling variation for very large scale many-cores with thousands of processing elements.

#### 2.2.4. Device Degradation and Ageing

A further challenge that has only relatively recently started to affect device yield is faults induced post-manufacture by transistor ageing and electromigration. These defects are surveyed in [44] (presented in an IEEE magazine), where three mechanisms for transistor ageing are identified: hot-carrier injection which increases the threshold voltage of the transistor (and thus limits the maximum switching speed); bias temperature instability which also increases the threshold voltage and oxide breakdown which will break down the transistor dielectric over time, eventually leading to a complete catastrophic failure of the transistor. Electromigration however occurs in the tracks between transistors: the accidental drifting of atoms with electrons causes the tracks to thin, increasing the resistance to the point that an open track may occur. As these permanent faults are impossible to mitigate through manipulation of controllable parameters (i.e. voltage, temperature), we will also need to mitigate ageing effects geometrically at runtime; analysis at time of manufacture is not longer sufficient. This has been done in the past with *N*-modular redundancy, where N copies of each processing unit exist on the device and their outputs are used to vote and thus can both detect faulty modules and provide a correct output. However the voter can still be subject to the permanent faults introduced here and if the processing unit is of high performance then the total power required by the redundancy scheme will be multiplied by N, with severe dark silicon implications. Thus, we shall either need to rely on cold spares which would be advantageous for dark silicon but could potentially be quite wasteful depending on system granularity, or utilise the adaptive nature of reconfigurable device technologies such as Field Programmable Gate Arrays (FPGAs).

### **2.3.** Many-Core Systems

To tackle these issues when designing for high-density silicon devices, we can change our design paradigm to manage the complexity of having so much computation onchip whilst also managing co-dependent design constraints to ensure as much as the circuity on the device as possible is operating within design limits. As highlighted by the ITRS reports, a level of abstraction of interest is at the data-processor level and is encapsulated by the field of Many-Core Systems. These are large SoCs consisting of a high number of processing cores but implemented with a more generic architectures and processing cores than specialist high-core-count SoCs such as graphics cards or dedicated algorithm accelerators. The More than Moore 2018 IRDS report [2] predicts many-core systems as the only way to achieve performance targets assuming incremental improvement of the thermal and power density of dies. The report predicts a 4.0GHz maximum mobile processor speed by 2025 with this speed getting worse as technologies reduce in size (due to increased impact of parasitics), to the point where the average frequency of a CPU in a mobile SoC will be 700MHz by 2034. To counteract this the number of processing cores is increased, reaching 194 GPU cores and 170 CPU cores for a mobile SoC by 2034. A modern mobile SoC, for example the Apple A13 [22], consists of six CPU cores (two at 2.65GHz, four running significantly slower) and four GPU cores. The expansion of this SoC to the IRDS processing core densities will require a large shift in the design of software, hardware and run-time management to use the large number of processors effectively.

Many-core computing has been of research interest for many years within the parallel computation research field, a field that has steadily become more integrated with hard-ware research as the increasing transistor density allows more and more parallel computation to take place within a single chip. In an attempt to tackle engineering problems such as scalability, many parallel architectures have been proposed and evolved over the years including: systolic arrays[45], wavefront arrays [46], hypercubes [47] and stream processors [48]. However the prominent architecture for modern *on-chip* many-core systems is the *Network on Chip* (*NoC*) [49][50], an interconnection scheme based on conventional networking where routers and channels are provided for com-

munication between nodes. A large number of node topologies, interconnect options and constraint optimisations are possible [16] (IEEE transactions on Computer-Aided Design of Integrated Circuits and Systems), giving the hardware engineer a powerful platform for implementing systems that could be adapted to meet various Dark Silicon criteria or tolerance to ageing effects via redundancy.

This flexibility comes with its own engineering caveats however, as the large number of parameters will require problem and system analysis to ensure that systems implemented within NoCs fit their requirements and may necessitate the need for heuristical approaches [51][52][53] to optimise the design space. This approach also suffers as such analysis is traditionally done at design time and so cannot be adapted should the operating conditions or properties of the chip change during operation (e.g. due to ageing effects). Whilst it would be possible to generate either a design that can operate over a range of operating environments or several different designs that can be switched in/out at run time, the multi-objective optimisation required for the system analysis tends to be computationally expensive. This would make it impossible to undertake this analysis online at runtime and would require a extensive amount of offline analysis; with the potential of storing a huge number of different configurations and parameters for all possible operating conditions that the system may be expected to work correctly for. The following sub-sections will explore this design space and show why managing these parameters is important for effective, scalable many-core design. Factors the influence the physical hardware implementation of a many-core (only Network-on-Chip implementations are considered in this thesis due to their ease of scalability) are discussed first and then the higher-level algorithmic design parameters and processes.

#### 2.3.1. Network-on-Chip

Network-on-Chip (NoC) is a modern digital design paradigm enabled by the recent generation of high-density VLSI fabrics that supports a large number of data processing resources, using a network to interconnect the processing resources [49][50]. Whilst taking a large amount of inspiration from traditional networking, there are some significant design differences due to the fact that NoCs are implemented within a single chip. Network topology for example is more focused towards layouts that are better suited to tiling across a die using protocols and channels that require less storage overhead than current computer networking protocols and physical implementations. The authors in [16] (IEEE transactions on Computer-Aided Design of Integrated Circuits and Systems) have conducted a large survey of NoC design techniques and highlighted problems that need attention, whilst the authors of [54] (ACM Computing Surveys) and also in [55] summarise key design points in NoC design and discuss some example designs. The following summaries use these papers to provide a brief explanation of the role of each component of NoC design and tradeoffs that can be made with each component.

#### **NoC Packets and Routing**

The majority of data transmission methods for NoCs fall into either *circuit switched* or packet switched schemes. These relate to the amount of data that is moved in a transaction and whether the routing information is located within the packet. Packet switched networks will contain the required routing control information within the packet and the packet can only exist at one router at a time (aside from during a transmission transaction), requiring ample buffer storage to allow each router to be able to store an entire packet. Circuit switching on the other hand reserves a path for the packet, with the routing information typically leading the data. This requires minimal buffering per router channel (just the routing data), but it does mean a packet can span several routers and data channels. This clearly results in a tradeoff between amount of memory required for buffering at each router and the amount of interference on a routing path on the networking; indeed wormhole routing, the most common form of circuit switched routing for NoCs, is very susceptible to deadlock [56]. The authors of [57] claim that, generally, for larger packets in lower-load applications that circuit switched communication should be used for NoCs; with packet switching performing better in high-load, small packet applications. They also show the extra area cost of packet switched routing, with their synthesised packet switched router requiring nearly five times the area than their circuited switched router.

#### **NoC Routers**

The router tends to be the most complex element in the NoC. Much like a conventional network router its role is to connect routers to each other, connect the processing node(s) to a router and to support the communication protocol(s) that run on top of the NoC hardware. At the heart of the router is the switch that connects input data channels to output data channels. The router requires a control unit that uses an arbitration policy and connection rules (sometimes encoded within a *routing table*) to determine which input channels should be connected to which output channels via the switch. As exemplified in [58], the design of the router will reflect heavily on the system in which the NoC is to be used and the communication demands of the applications running on the NoC, especially with systems requiring support for both "guaranteed" and best-effort traffic. The AETHEREAL NoC [59] for example supports a sophisticated timeslot arbitration and so has a complex switch controller within its design, resulting in a large amount of control logic required for the router and memory resources required for the various timeslot queues.

#### **Data Channels**

Physical wires that carry the data connect the routers to each other. This may seem a trivial part of the NoC design, but the number, width and length of these wires can contribute significantly to the operating envelope of the chip, with [54] suggesting that as technologies shrink, the influence of crosstalk, power supply noise and wire capacitance will prove a real challenge to NoC interconnect, likely requiring the use of error protection methods on the interconnections with future technologies. This problem is even more applicable to any global signals or other lengthy signals with highfanout due to the large number of signal repeaters on the wire, so designs suitable for high scalability will require minimal use of such signals. High-speed serial communication has been successful in conventional networking to alleviate these problems, although their use within NoCs is limited due to the extra area required by the fast serialiser/deserialiser pairs [60] and the increased thermal load of the fast serial clock. NoCs will help in this regard as the grid structure ensures that long wires will not be needed in the design (the longest performance limiting wires will be those between NoC routers) and the regular grid structure can give an efficient cross-talk and thermal analysis as once one tile is analysed the resultant model could be tiled across the die.

#### **2.3.2.** The Many-Core Design Space