Spread Spectrum system analysis, development, and testing, in a multipath UHF radio environment.

Terence Bayes

Submitted in accordance with the requirements for the degree of PhD.

The University of Leeds

Department of Electrical and Electronic Engineering

January 1989

Direct Sequence Spread Spectrum systems presently find use in navigation and military communication systems. In recent years, however, interest has also been shown in the potential of such systems for Land Mobile Radio applications. In particular the broadband Spread Spectrum signal would be useful in combating the effects of narrowband fading experienced in the UHF radio environment.

In addition, vast improvements in the performance of digital integrated circuits is leading to the concept of the all-digital radio receiver. One such device made feasible by progress in miniaturisation is the Digital Matched Filter.

This work examines the operation of the Digital Matched Filter. It's applicability to Direct Sequence Spread Spectrum Systems is studied with a view to the possible implementation of such schemes in the Land Mobile Radio environment. Emphasis is placed on achieving maximum utilisation of the Digital Matched Filter resource. Information obtained from Digital Matched Filters in a complex baseband receiver is shown to assist rapid code synchronization, RF carrier recovery, and measurement of the multipath transmission channel profile.

A practical transmitter/receiver pair is described, and the results obtained suggest that future designers of Direct Sequence Spread Spectrum receivers may obtain benefits from the Digital Matched Filter approach, particularly in the area of rapid code synchronization.

## **ACKNOWLEDGEMENTS**

I would like to extend special thanks to the following for their assistance during the course of this work:

Professor Peter Lawrenson and Professor Michael Howes, as heads of the Department of Electrical and Electronic Engineering, for their permission to use the facilities of the department.

Professor Peter Matthews for supervising the project, and providing much appreciated help and advice during the period of study and during the preparation of this thesis.

The Science and Engineering Research Council for providing financial support.

The Home Office Directorate of Telecommunications for providing funds for the project.

My wife, Sharon, for her patience during the preparation of this thesis.

# CONTENTS

| 1 | INT  | RODUCTION                                         | 1  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | History of the project                            | 1  |

|   | 1.2  | Background to the problem                         | 2  |

|   | 1.3  | Terminology used                                  | 3  |

|   |      | References                                        | 8  |

| 2 | THE  | DIGITAL MATCHED FILTER                            | 10 |

|   | 2.1  | Introduction                                      | 10 |

|   | 2.2  | DMF operation                                     | 11 |

|   | 2.3  | DMF output statistics                             | 18 |

|   |      | 2.3.1 Approximation for chip error probability    |    |

|   |      | with hard limiting                                | 18 |

|   |      | 2.3.2 Approximation for DMF output - Bernoulli    |    |

|   |      | trials                                            | 21 |

|   |      | 2.3.3 DMF output - Code in phase                  | 28 |

|   |      | 2.3.4 DMF output - Code out of phase              | 30 |

|   |      | 2.3.5 Noise only                                  | 32 |

|   | 2.4  | Detection criterion                               | 33 |

|   |      | 2.4.1 Code selection                              | 33 |

|   |      | 2.4.2 Effect of modulation                        | 33 |

|   |      | 2.4.2.1 Sequence inversion keying                 | 33 |

|   |      | 2.4.2.2 On-off keying                             | 34 |

|   | 2.5  | Effect of quantization on DMF performance         | 37 |

|   | 2.6  | Conclusions                                       | 44 |

|   |      | References                                        | 46 |

| 3 | COMI | PLEX BASEBAND RECEIVER                            | 58 |

|   | 3.1  | Introduction                                      | 58 |

|   | 3.2  | Receiver mixers                                   | 60 |

|   | 3.3  | Lowpass filters                                   | 63 |

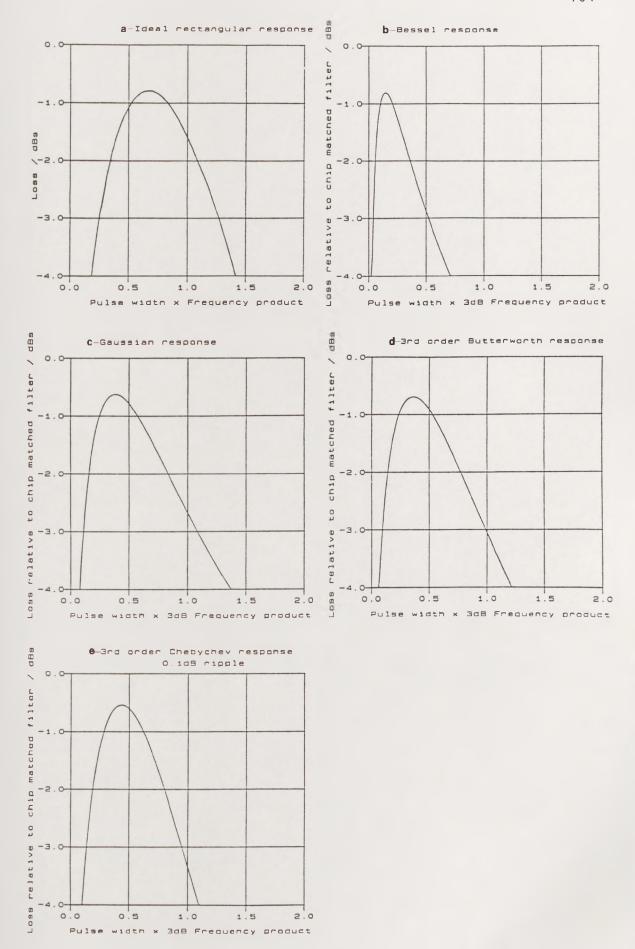

|   |      | 3.3.1 Choice of frequency response characteristic | 64 |

|   |      | 3.3.2 Effect of filtering on correlation          | 64 |

|   |      | 3.3.2.1 Correlation of lowpass noise samples      | 64 |

|   |      | 3.3.2.2 Correlation of lowpass signal             |    |

|   |      | samples                                           | 67 |

|   |      | 3.3.3 Cutoff frequency and noise equivalent bandwidth | 69  |

|---|------|-------------------------------------------------------|-----|

|   |      | 3.3.4 Filter loss relative to ideal chip matched      | 09  |

|   |      | filter                                                | 70  |

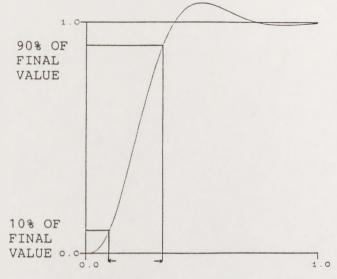

|   |      | 3.3.5 Filter phase and step response                  | 75  |

|   |      | 3.3.6 Choice of practical lowpass filter              | 78  |

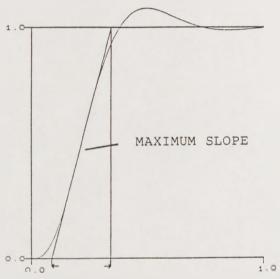

|   | 3.4  | RF local oscillator and system clock relationship     | 80  |

|   |      | Sample and hold and A/D converters                    | 83  |

|   |      | Digital matched filter                                | 84  |

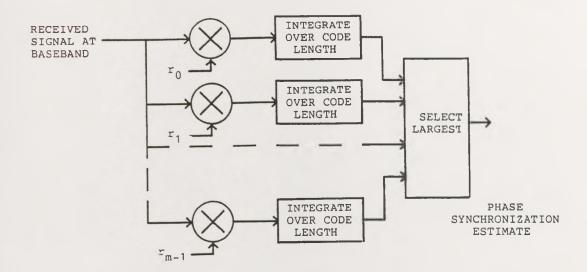

|   |      | Combining algorithm                                   | 84  |

|   |      | Conclusions                                           | 92  |

|   |      | References                                            | 96  |

| 4 | SYNO | CHRONIZATION TECHNIQUES                               | 110 |

|   |      |                                                       |     |

|   | 4.1  | Introduction                                          | 110 |

|   | 4.2  | Synchronization and tracking schemes                  | 111 |

|   |      | 4.2.1 Code synchronization acquisition                | 111 |

|   |      | 4.2.2 Code tracking                                   | 116 |

|   |      | 4.2.3 RF recovery                                     | 118 |

|   | 4.3  | Digital synchronization system                        | 119 |

|   |      | 4.3.1 DMF receiver code synchronization               |     |

|   |      | acquisition                                           | 120 |

|   |      | 4.3.1.1 Threshold detection on average                |     |

|   |      | algorithm output                                      | 123 |

|   |      | 4.3.1.2 Average of number of threshold                |     |

|   |      | crossings                                             | 124 |

|   |      | 4.3.1.3 Single threshold crossing with                |     |

|   |      | binary integration                                    | 129 |

|   |      | 4.3.2 Digital tracking and RF recovery loops          | 139 |

|   | 4.4  | System study of control of a DMF based DSSS           |     |

|   |      | receiver                                              | 141 |

|   |      | 4.4.1 Conditions for code synchronization             | 145 |

|   |      | 4.4.2 Ability to achieve RF synchronization           | 148 |

|   |      |                                                       | 153 |

|   | 4.5  | Conclusions                                           | 155 |

|   |      | References                                            | 159 |

| 5 | PROT | TOTYPE DIRECT SEQUENCE SYSTEM                         | 172 |

|   |      |                                                       |     |

5.1 Introduction

172

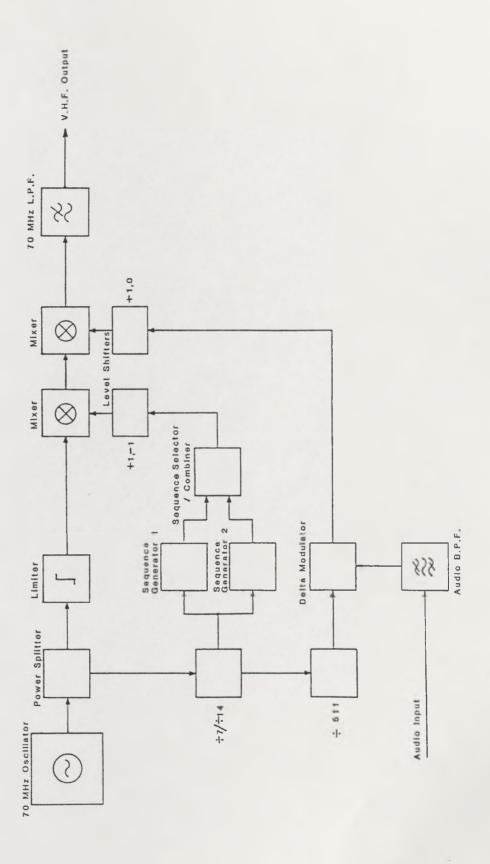

| 5.2  | Protot | type direct sequence transmitter            | 173 |

|------|--------|---------------------------------------------|-----|

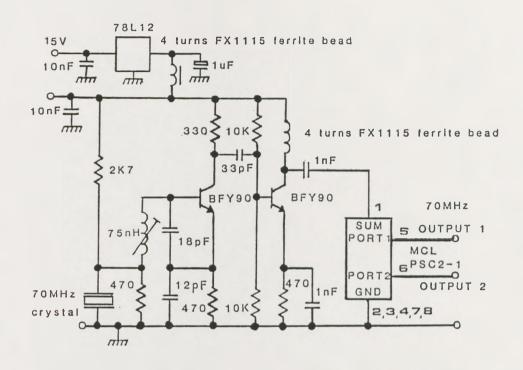

|      | 5.2.1  | 70 MHz oscillator and system clock          |     |

|      |        | generator                                   | 174 |

|      | 5.2.2  | Code generators                             | 175 |

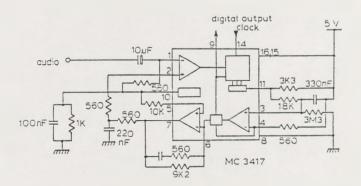

|      | 5.2.3  | Audio encoder                               | 176 |

|      | 5.2.4  | Delta modulator clock and synchronization   |     |

|      |        | generator                                   | 178 |

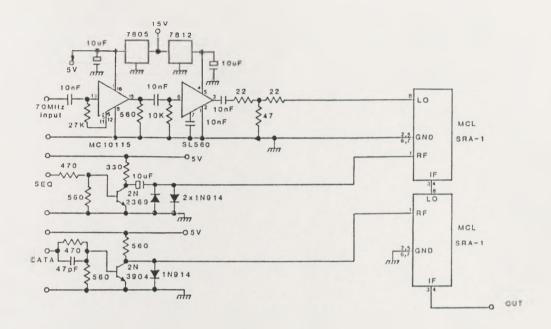

|      | 5.2.5  | 70 MHz limiter and mixer module             | 179 |

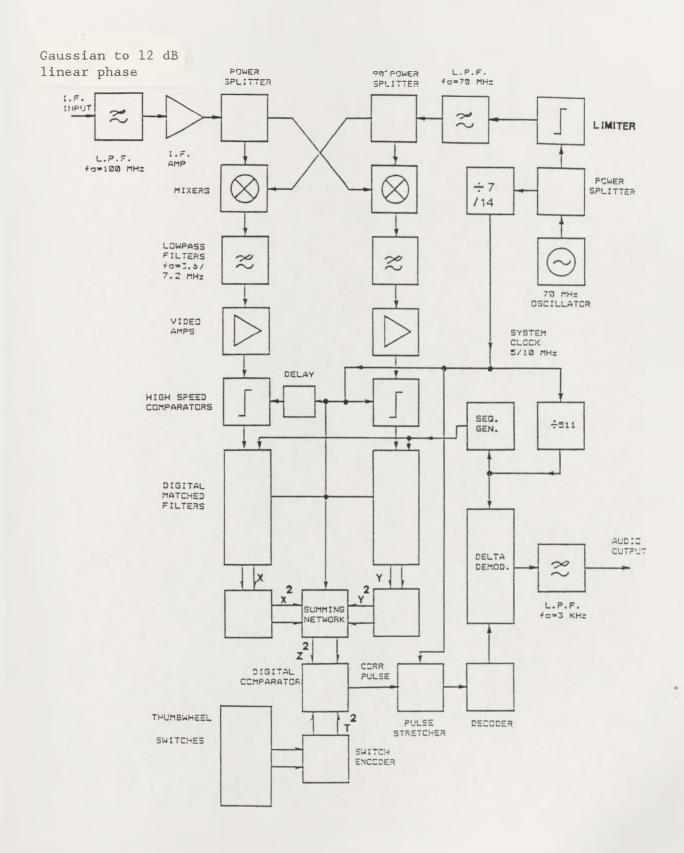

| 5.3  | Protot | type DSSS receiver                          | 181 |

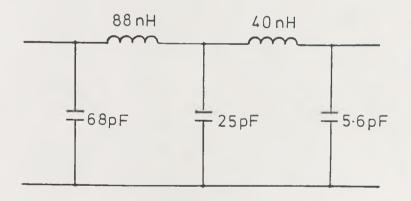

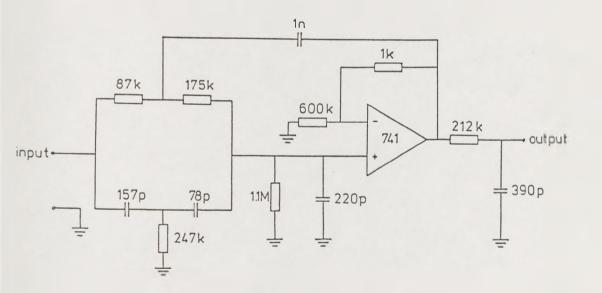

|      | 5.3.1  | IF lowpass filter and amplifier             | 183 |

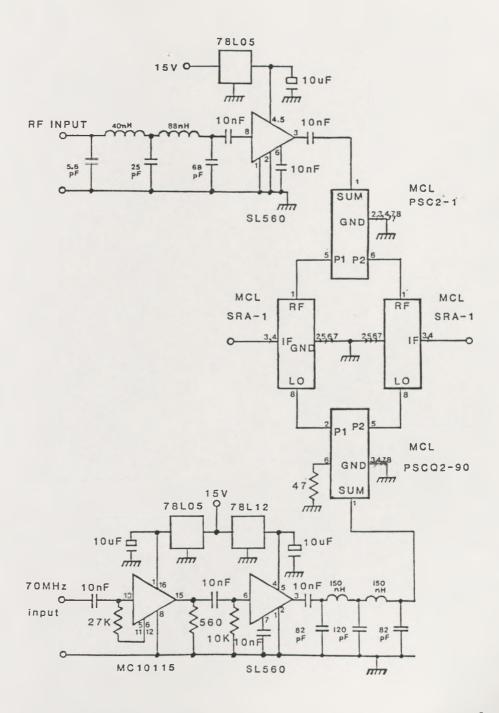

|      | 5.3.2  | 70 MHz oscillator and system clock          |     |

|      |        | generator                                   | 183 |

|      | 5.3.3  | Power dividers and IF mixers                | 183 |

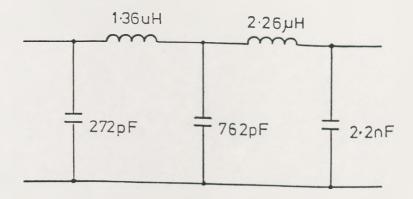

|      | 5.3.4  | Baseband lowpass filters and video          |     |

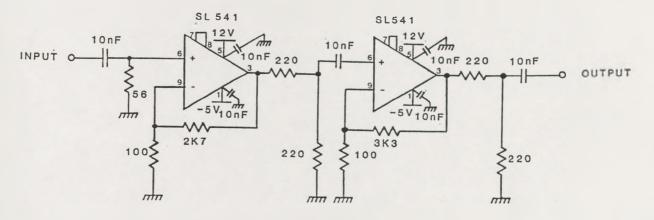

|      |        | amplifiers                                  | 184 |

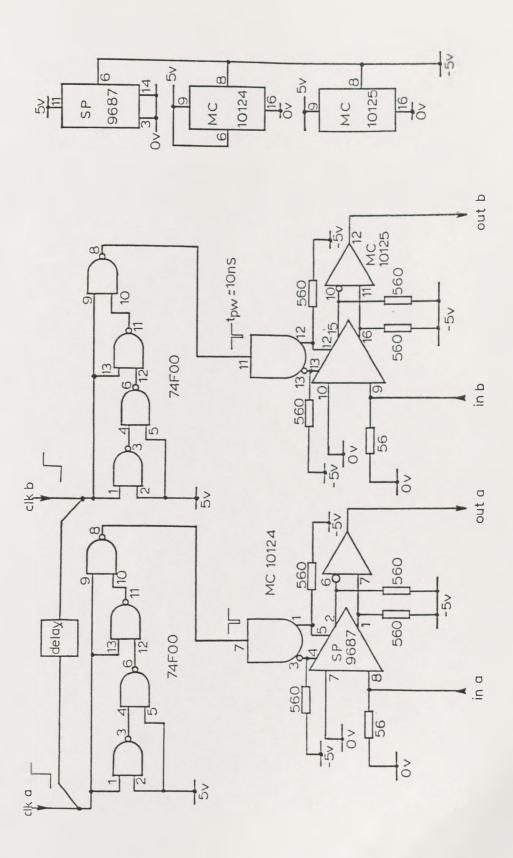

|      | 5.3.5  | High speed comparators                      | 184 |

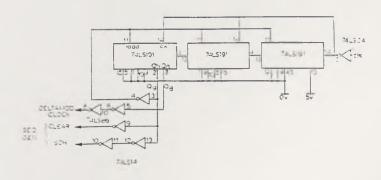

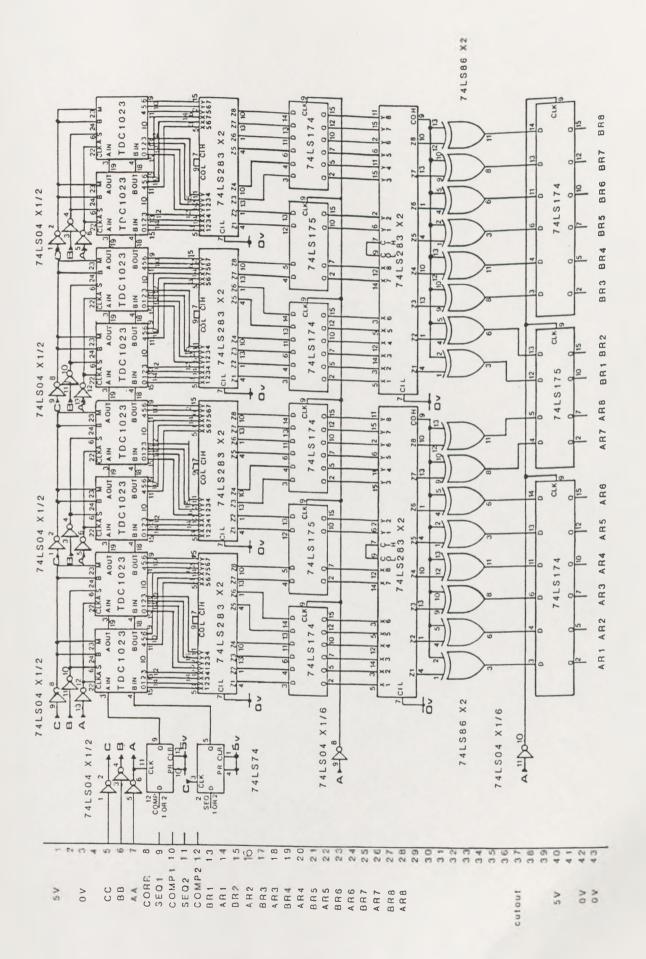

|      | 5.3.6  | Digital matched filters and arithmetic      |     |

|      |        | functions                                   | 185 |

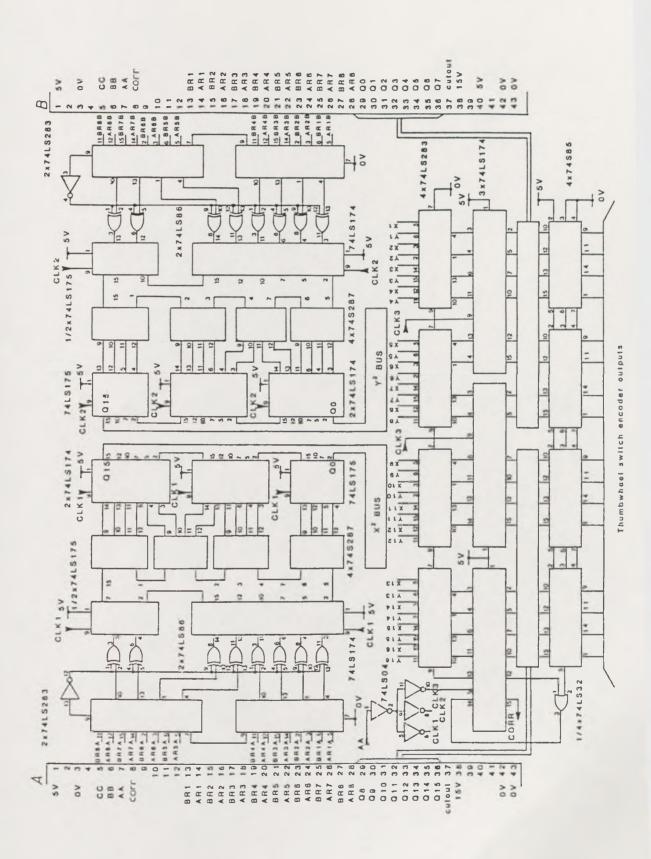

|      | 5.3.7  | Thumbwheel switch encoder                   | 189 |

|      | 5.3.8  | Digital comparator                          | 190 |

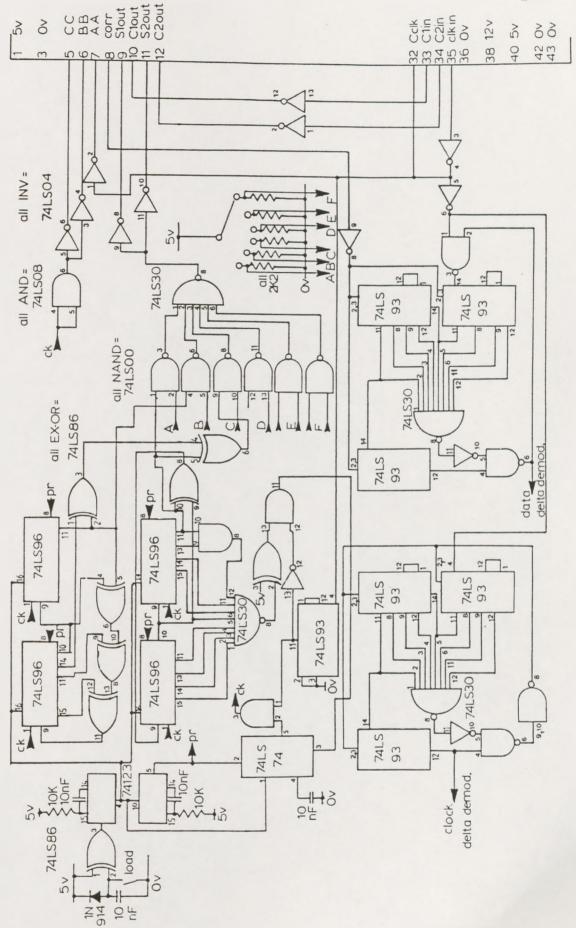

|      | 5.3.9  | Correlation processor and delta demodulator |     |

|      |        | clock generator                             | 191 |

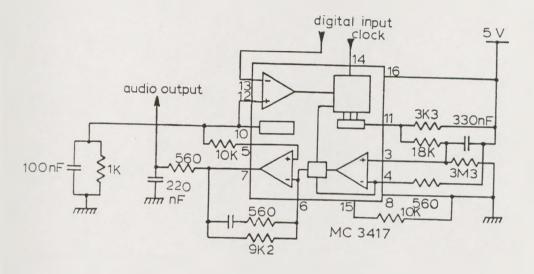

|      | 5.3.10 | ) Delta demodulator and lowpass filter      | 192 |

|      | 5.3.11 | Receiver sequence generator                 | 192 |

| 5.4  | Conclu | isions                                      | 192 |

|      | Refere | ences                                       | 195 |

|      |        |                                             |     |

| PRAC | CTICAL | RESULTS                                     | 211 |

|      |        |                                             |     |

| 6.1  | Introd | duction                                     | 211 |

| 6.2  | Broadh | pand noise generator                        | 211 |

| 6.3  | Chip e | errors                                      | 214 |

| 6.4  | Symbol | l errors                                    | 217 |

| 6.5  | DMF ou | atput probability distribution              | 219 |

| 6.6  | Multip | path propagation measurements               | 222 |

| 6.7  | Examin | nation of algorithm mean output             | 232 |

| 6.8  | Probab | oility algorithm exceeds thresholds         | 235 |

| 6.9  | Conclu | sions                                       | 237 |

|      |        |                                             |     |

6

7 CONCLUSIONS 254

# TABLES AND FIGURES

| Table : | 2 – 1 | Mathematical operations required to solve (2-9) and (2-10) | 15  |

|---------|-------|------------------------------------------------------------|-----|

| mahla ' | າ າ   | Voltage transfer function for 3 bit                        | 13  |

| Table : | 2-2   | quantizer                                                  | 41  |

| Table 2 | າ າ   | Minimum and maximum loss due to multibit                   | -21 |

| lable . | 2-3   | quantization                                               | 41  |

|         |       | quantizacion                                               | 7.1 |

| Table : | 3 – 1 | Practical lowpass filter responses, ratio of               | •   |

|         |       | noise equivalent bandwidth to 3dB bandwidth                | 70  |

| Table : | 3-2   | Practical lowpass filter responses,                        |     |

|         |       | normalized risetime                                        | 78  |

|         |       |                                                            |     |

| Table ' | 4 – 1 | Probability that algorithm output exceeds                  |     |

|         |       | threshold                                                  | 126 |

| Table · | 4-2   | Mean number of synchronization searches,                   |     |

|         |       | single threshold crossing with binary                      |     |

|         |       | integration                                                | 134 |

| Table   | 4 – 3 | Mean number of synchronization searches,                   |     |

|         |       | single threshold crossing with 1 and 4                     |     |

|         |       | binary integrators                                         | 137 |

| Table   | 6 – 1 | Predicted and measured DMF outputs with                    |     |

|         | ,     | multipath components                                       | 228 |

|         |       |                                                            |     |

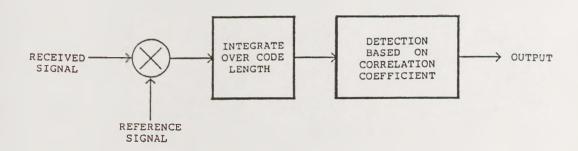

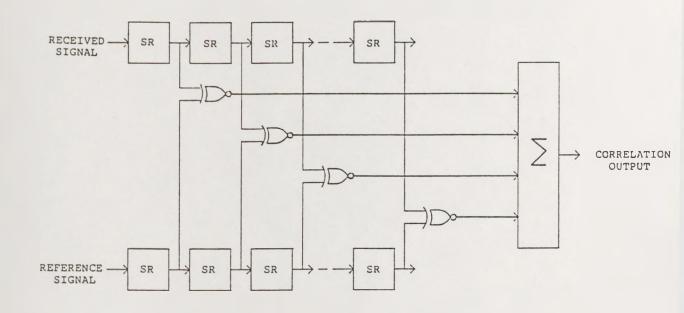

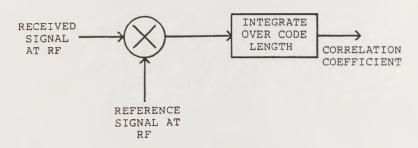

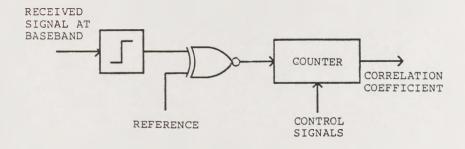

| Figure  | 2-1   | Correlation Detector                                       | 48  |

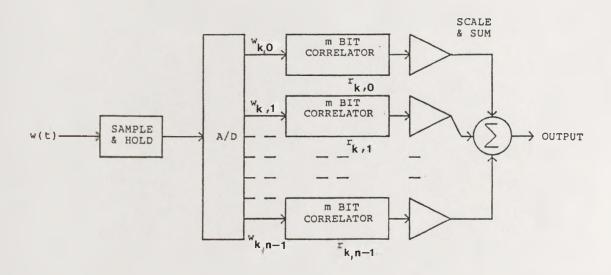

| Figure  | 2-2   | m by n bit Digital Correlator                              | 48  |

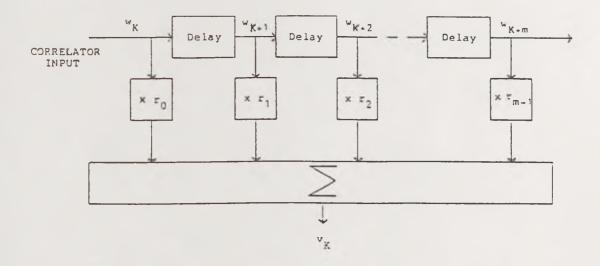

| Figure  | 2-3   | Canonical form of Binary Correlator                        | 49  |

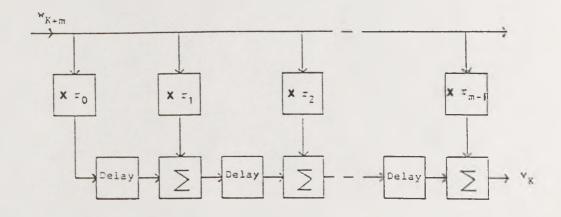

| Figure  | 2 – 4 | Binary Correlator with pipelined adders                    | 49  |

| Figure  | 2-5   | Binary Correlator Implementation                           | 50  |

| Figure  | 2-6   | Implementation of Binary Correlator from                   |     |

|         |       | expression (2-10)                                          | 50  |

| Figure  | 2-7   | Gaussian probability density function                      | 51  |

| Figure  | 2-8   | Cumulative Gaussian probability function                   | 51  |

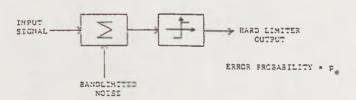

| Figure  | 2-9   | Hard limiter                                               | 51  |

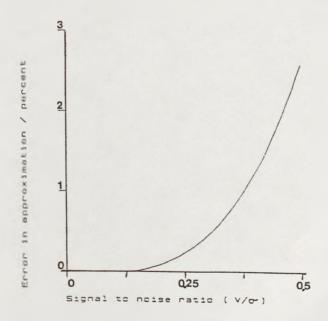

| Figure  | 2-10  | Error due to approximtion (2-21)                           | 51  |

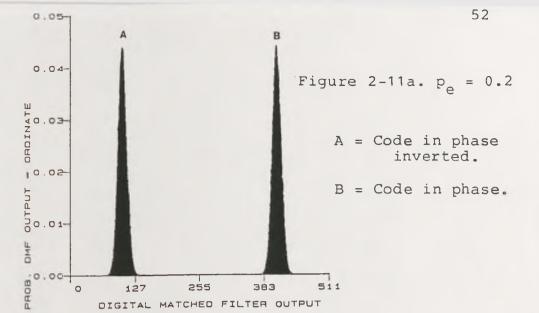

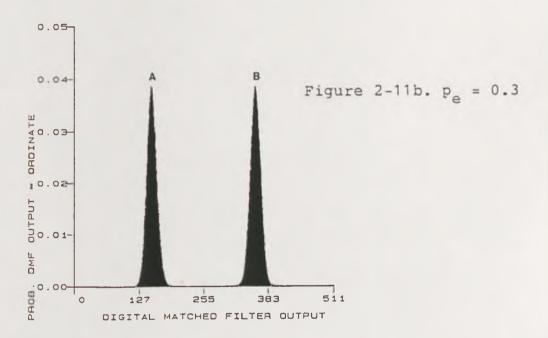

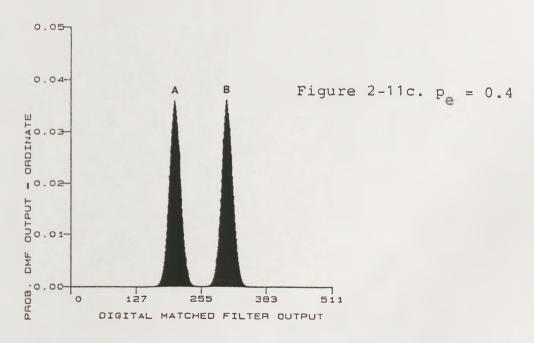

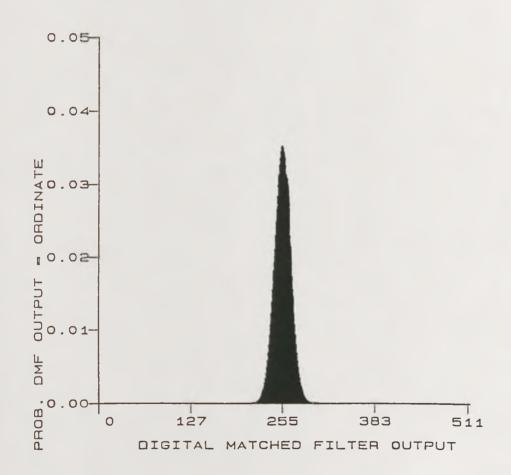

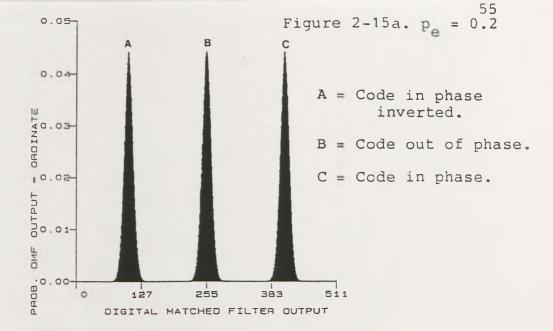

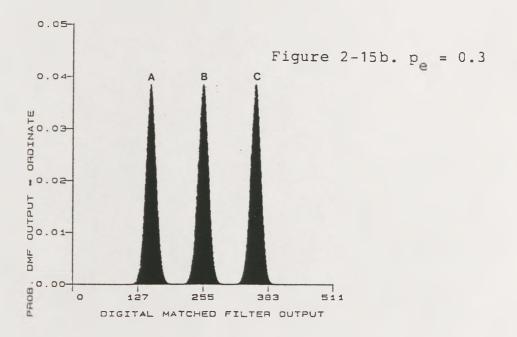

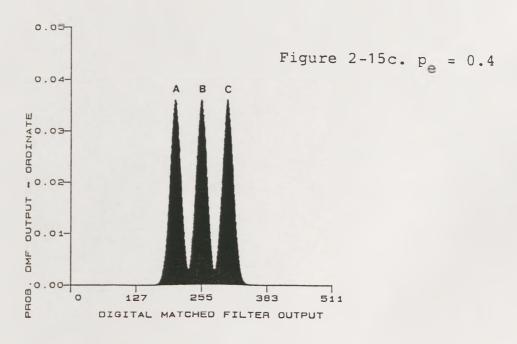

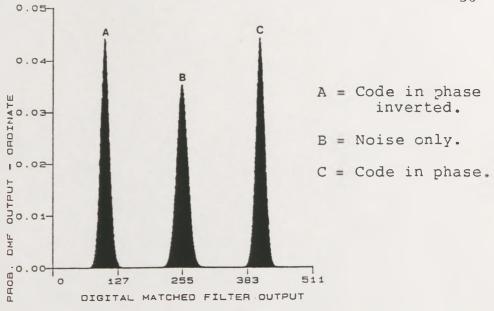

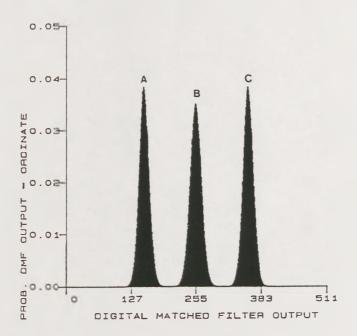

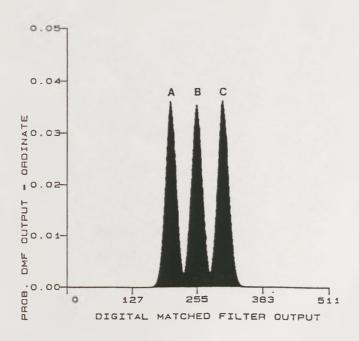

| Figure  | 2-11  | DMF output PDFs                                            | 52  |

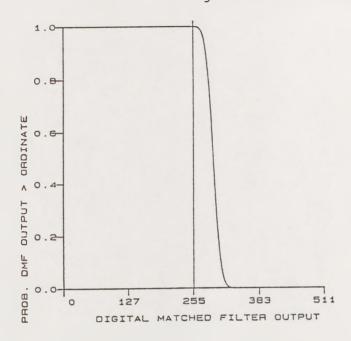

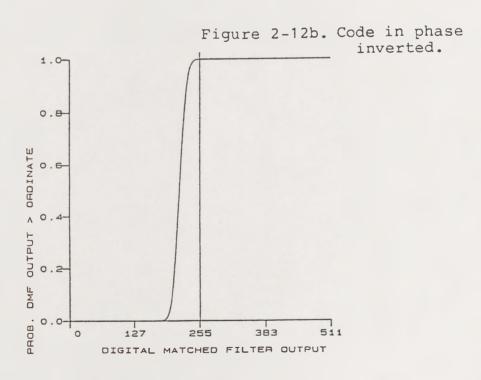

| Figure  | 2-12  | Cumulative PDF of DMF output                               | 53  |

| Figure | 2-13  | Autocorrelation function of practical code       |     |

|--------|-------|--------------------------------------------------|-----|

|        |       | for optimum detection                            | 54  |

| Figure | 2-14  | DMF output PDF, noise only case                  | 54  |

| Figure | 2-15  | DMF output PDF for code in phase and code        |     |

|        |       | out of phase cases                               | 55  |

| Figure | 2-16  | DMF output PDF for code in phase and noise       |     |

|        |       | only cases                                       | 56  |

| Figure | 2-17  | Effect of quantization threshold on              |     |

|        |       | processing gain loss for constant input snr      | 57  |

|        |       |                                                  |     |

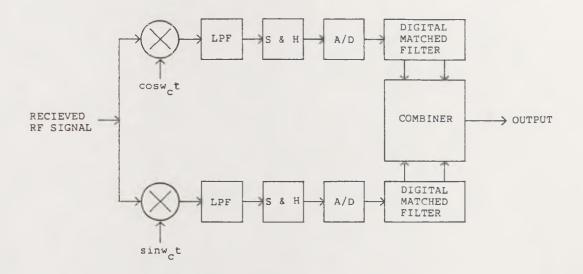

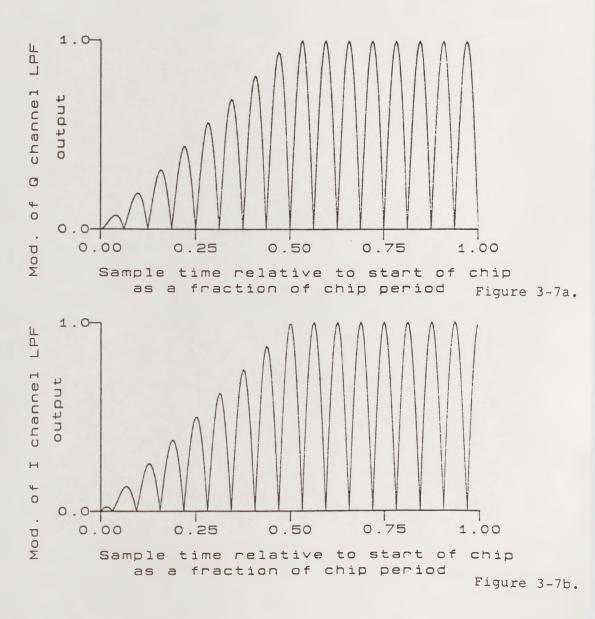

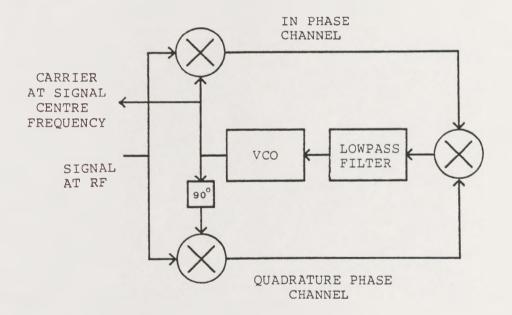

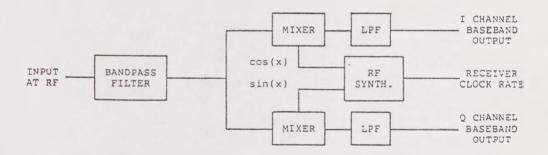

| Figure | 3 – 1 | Complex Baseband Receiver                        | 98  |

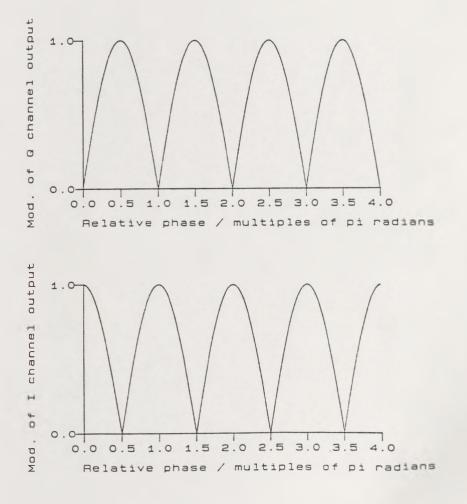

| Figure | 3-2   | Modulus of I and Q channel outputs with          |     |

|        |       | varying relative RF carrier phase                | 98  |

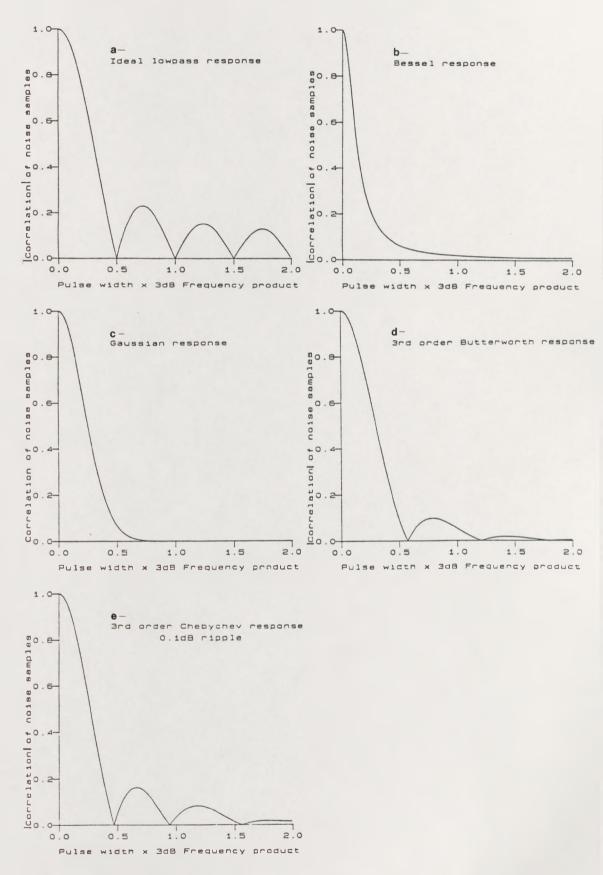

| Figure | 3-3   | Modulus of correlation of lowpass noise          |     |

|        |       | samples for test filters                         | 99  |

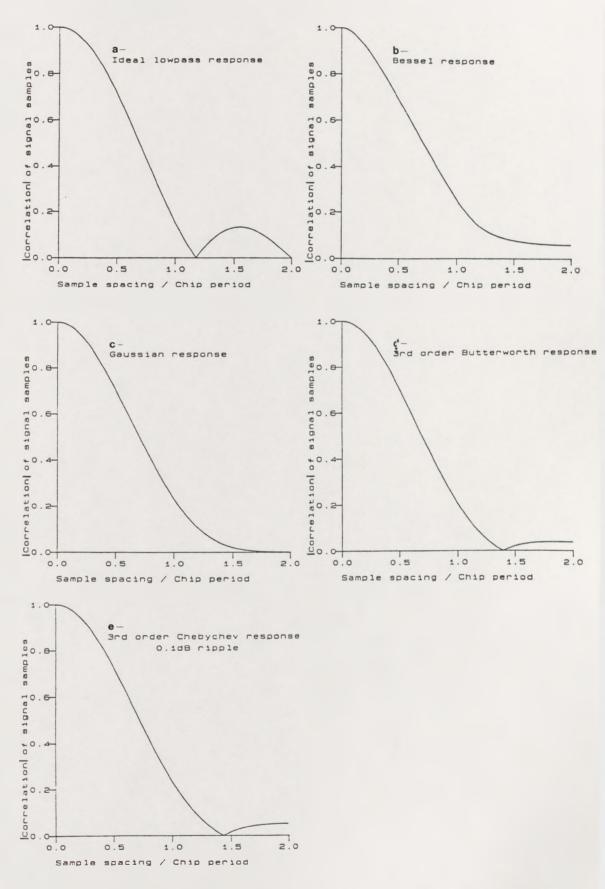

| Figure | 3-4   | Modulus of correlation of lowpass signal         |     |

|        |       | samples for test filters                         | 100 |

| Figure | 3-5   | Loss relative to ideal chip matched filter       |     |

|        |       | for test filters                                 | 101 |

| Figure |       | Lowpass filter risetime definitions              | 102 |

| Figure | 3-7   | Lowpass filter risetime superimposed on          |     |

|        |       | mixer output null pattern                        | 103 |

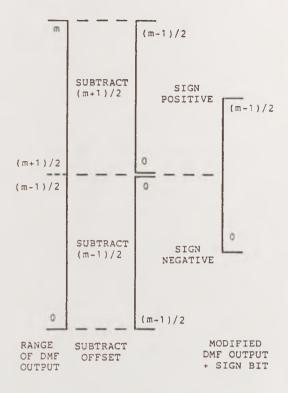

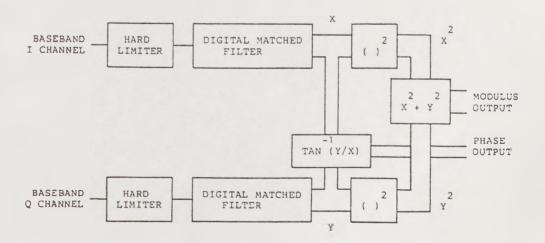

| Figure |       | Algorithm to modify DMF output                   | 104 |

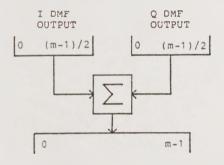

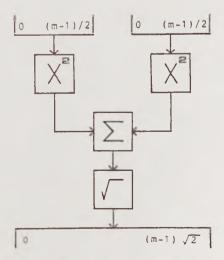

| _      |       | DMF combining algorithms                         | 104 |

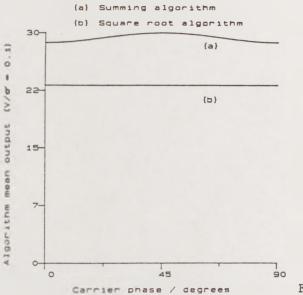

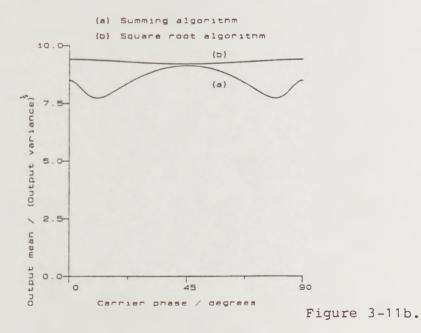

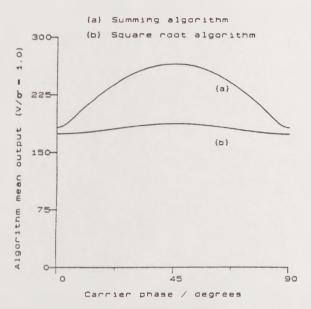

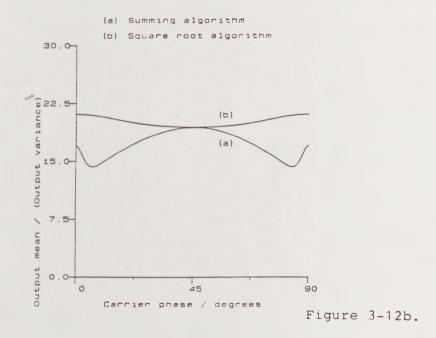

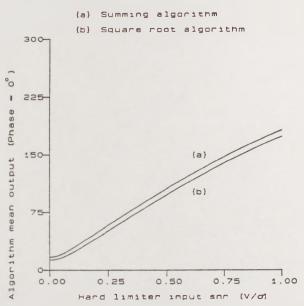

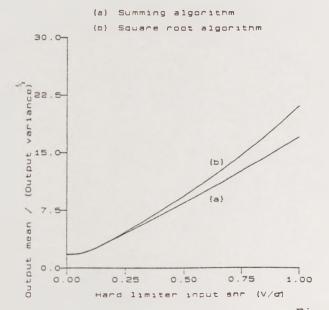

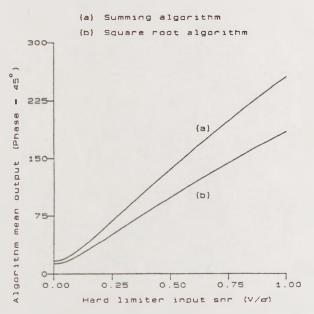

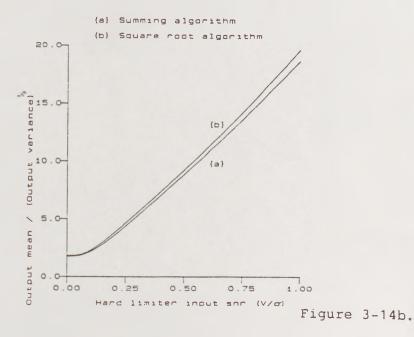

| Figure | 3-10  | Output statistics for algorithms, constant       |     |

|        |       | snr, varying phase                               | 105 |

|        |       | Output statistics for algorithms, V/o=0.5        | 106 |

| _      |       | Output statistics for algorithms, $V/\sigma=1.0$ | 107 |

| Figure | 3-13  | Output statistics for algorithms,                |     |

|        |       | increasing snr, constant phase (0 degrees)       | 108 |

| Figure | 3-14  | Output statistics for algorithms,                |     |

|        |       | increasing snr, constant phase (45 degrees)      | 109 |

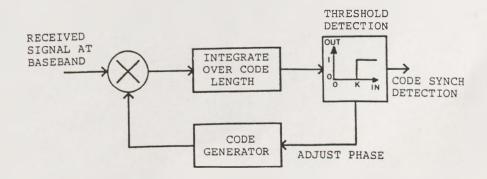

| Figure | 4-1   | Maximum likelihood detector                      | 161 |

| _      |       | Active correlator                                | 161 |

| _      |       | Digital correlator                               | 161 |

|        |       | Stepping correlator                              | 161 |

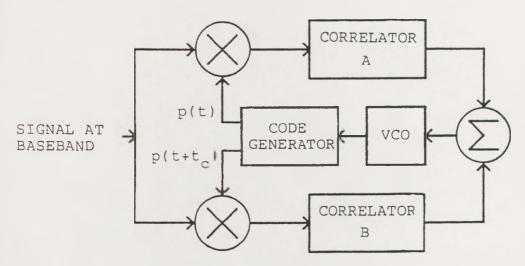

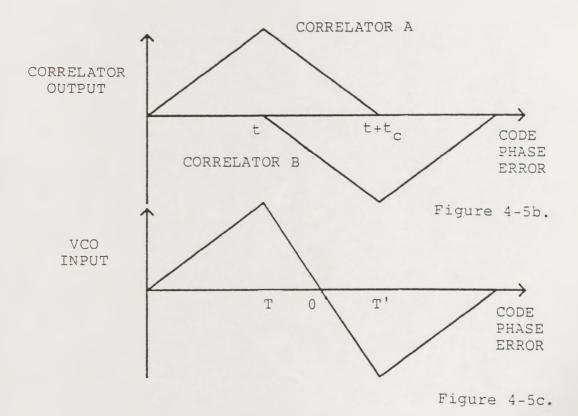

| _      |       | Delay lock loop                                  | 162 |

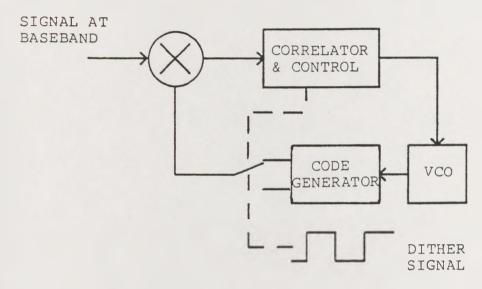

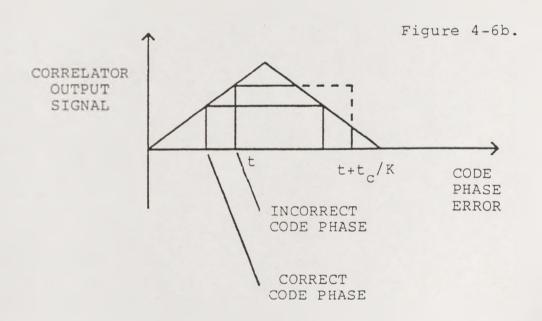

|        |       | Dither loop                                      | 163 |

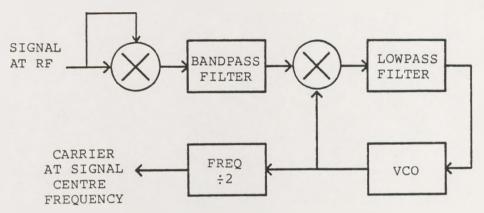

| _      |       | RF recovery loops                                | 164 |

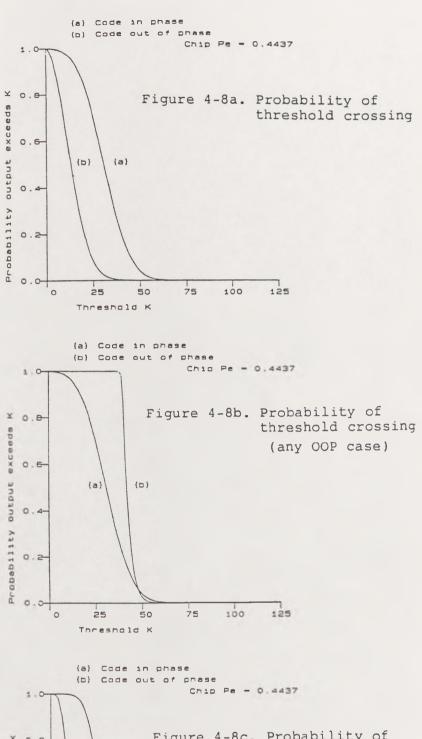

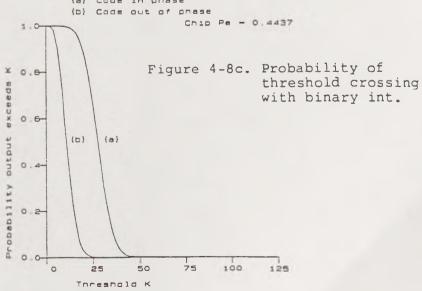

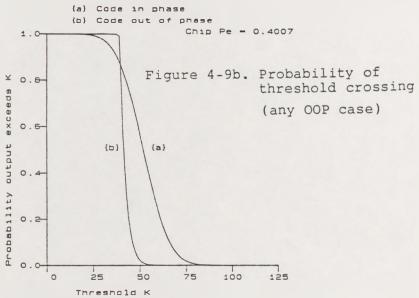

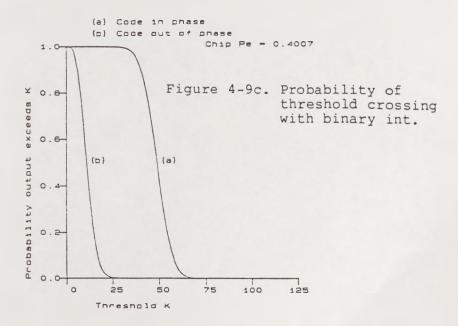

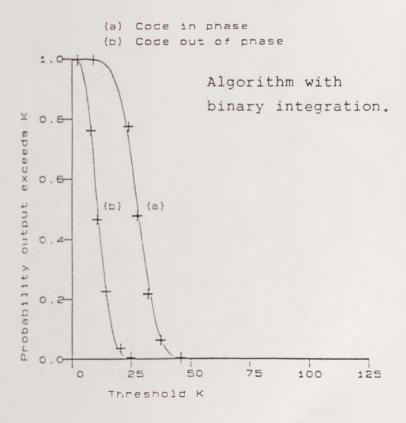

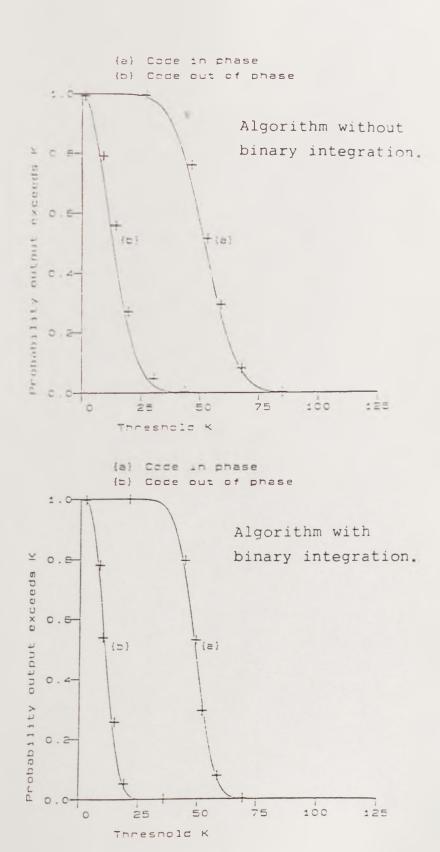

| Figure | 4-8     | Algorithm output probabilities, $p_e = 0.4437$ | 165  |

|--------|---------|------------------------------------------------|------|

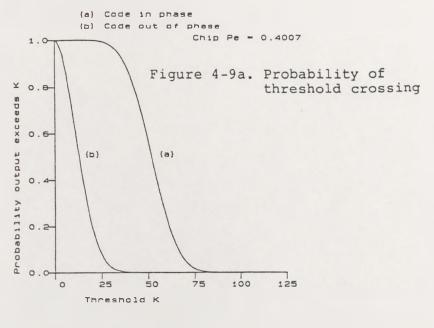

|        |         | Algorithm output probabilities, $p_0 = 0.4007$ | 166  |

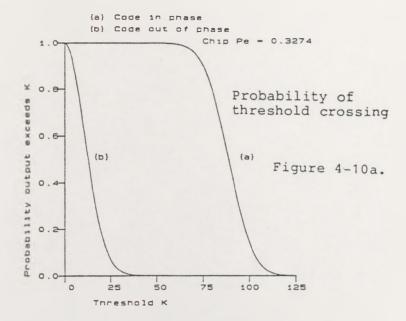

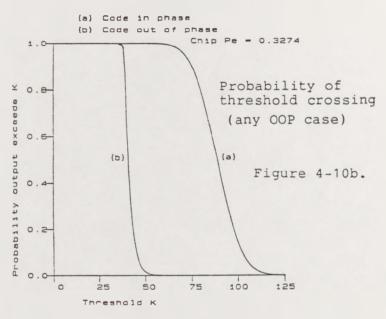

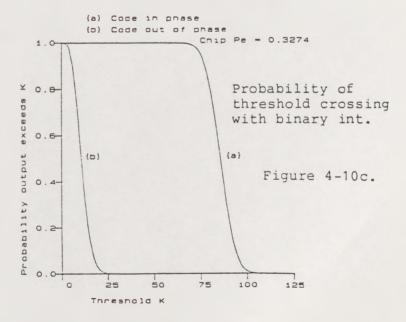

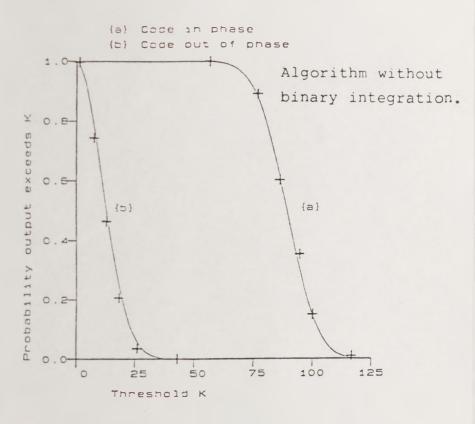

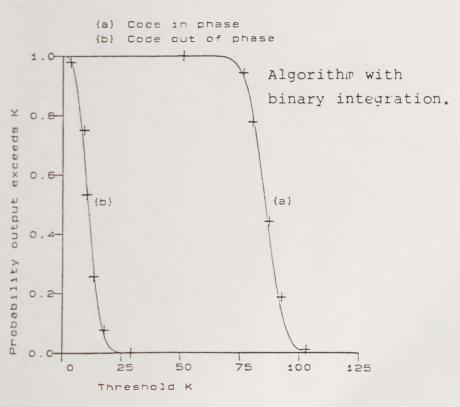

| Figure | 4-10    | Algorithm output probabilities, $p_e = 0.3274$ | 167  |

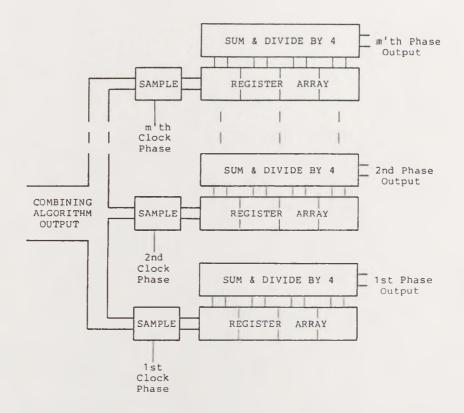

| Figure | 4-11    | Production of average algorithm output         | 168  |

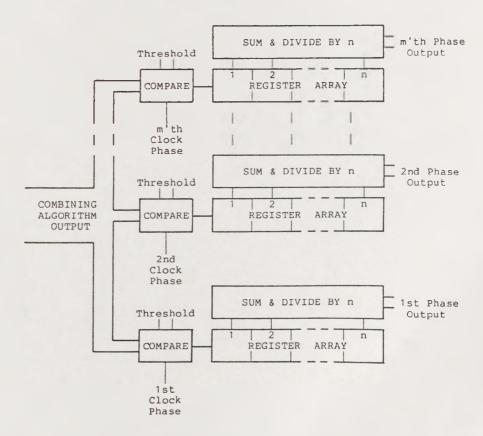

| Figure | 4-12    | Production of sum of threshold crossings       | 168  |

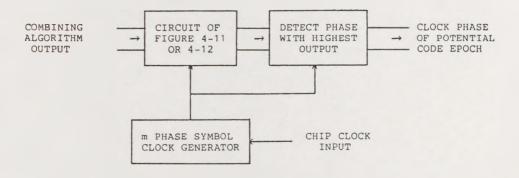

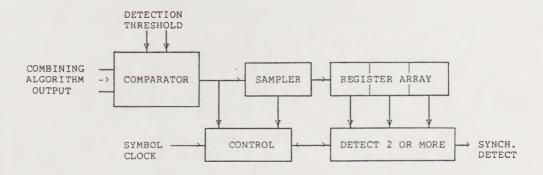

| Figure | 4-13    | Code epoch detection                           | 169  |

| Figure | 4 – 1 4 | Code synchronization detection by single       |      |

|        |         | threshold crossing with binary integration     | 169  |

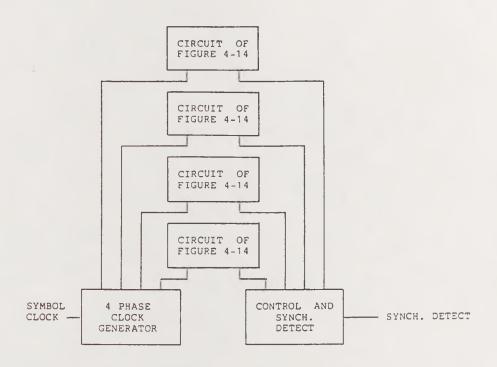

| Figure | 4-15    | Code synchronization detection by 4 single     |      |

|        |         | threshold crossing detectors with binary       |      |

|        |         | integration                                    | 170  |

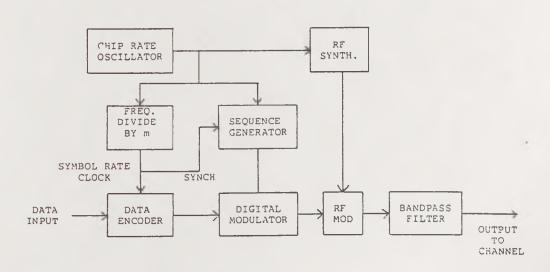

| Figure | 4-16    | DSSS Transmitter block diagram                 | 170  |

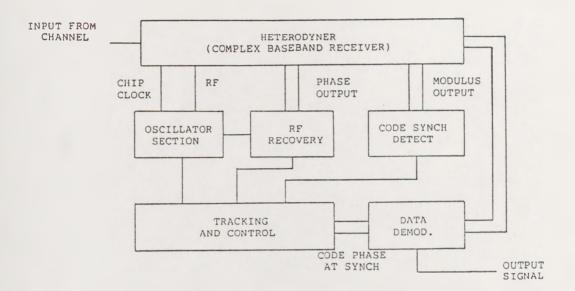

| Figure | 4 – 1 7 | DSSS receiver block diagram                    | 171  |

| Figure | 4-18    | DSSS receiver RF down conversion section       | 171  |

| Figure | 4-19    | DSSS receiver baseband section                 | 171  |

| Figure | 5-1     | Practical DSSS transmitter block diagram       | 197  |

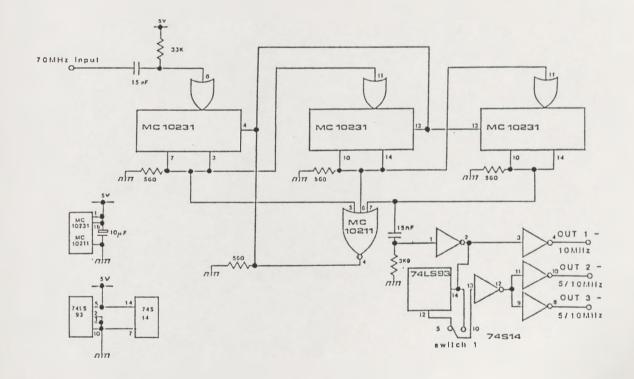

| Figure | 5-2     | 70 MHz oscillator                              | 198  |

| Figure | 5-3     | 70 MHz divider and system clock generator      | 198  |

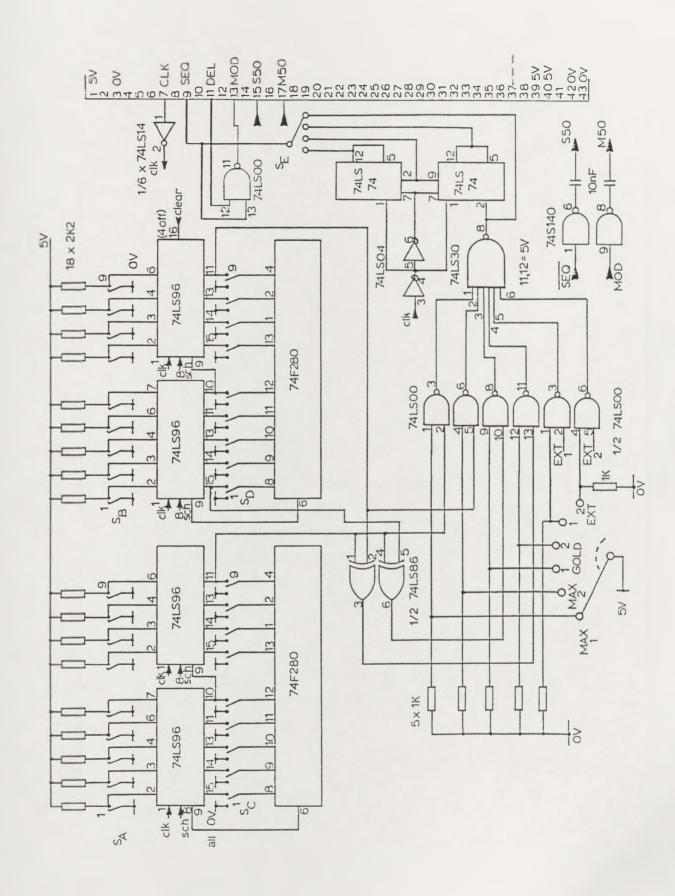

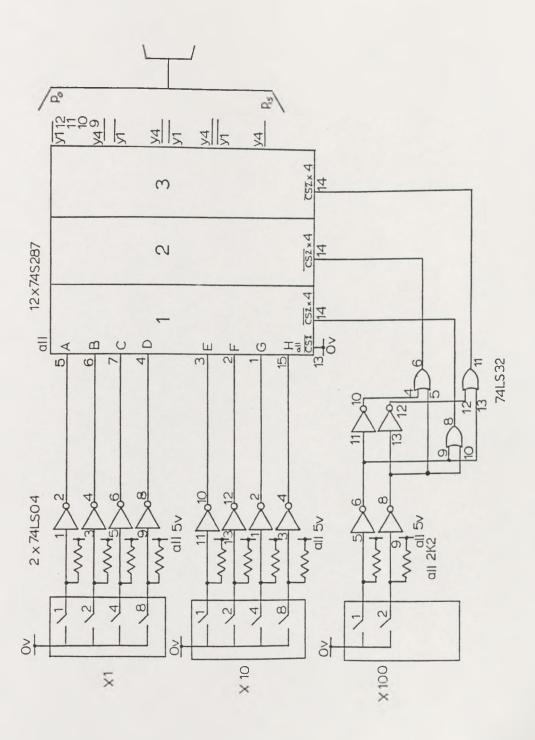

| Figure | 5-4     | Transmitter code generator                     | 199  |

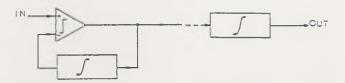

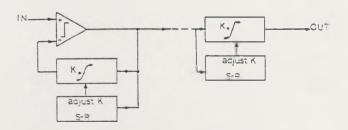

| Figure | 5-5     | Delta modulation                               | 200  |

| Figure | 5-6     | CVSD modulator                                 | 200  |

| Figure | 5-7     | CVSD clock and synchronization generator       | 201  |

| Figure | 5-8     | Transmitter IF modulator section               | 201  |

| Figure | 5-9     | IF lowpass filter                              | 201  |

| Figure | 5-10    | Practical DSSS receiver block diagram          | 202  |

| Figure | 5-11    | Receiver input filter and complex baseband     |      |

|        |         | converter                                      | 203  |

| Figure | 5-12    | Baseband lowpass filter                        | 204  |

| Figure | 5-13    | Video amplifier                                | 204  |

| Figure | 5-14    | High speed comparators                         | 205  |

| Figure | 5-15    | Digital matched filter                         | 206  |

| Figure | 5-16    | Matched filter combiner, arithmetic            |      |

|        |         | functions, and digital comparator              | 207  |

| Figure | 5-17    | Thumbwheel switch threshold encoder            | 208  |

| Figure | 5-18    | Correlation pulse processor, CVSD demodulate   | or   |

|        |         | clock generator, and receiver sequence         | 0.00 |

|        |         | generator                                      | 209  |

| _      |         | CVSD demodulator                               | 210  |

| Figure | 5-20    | CVSD demodulator audio lowpass filter          | 210  |

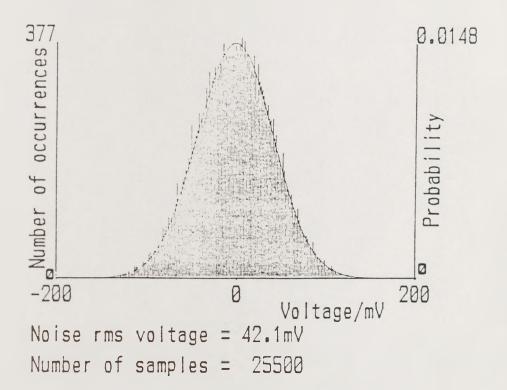

| Figure | 6 – 1 | Noise generator amplitude probability      |     |

|--------|-------|--------------------------------------------|-----|

|        |       | distribution                               | 242 |

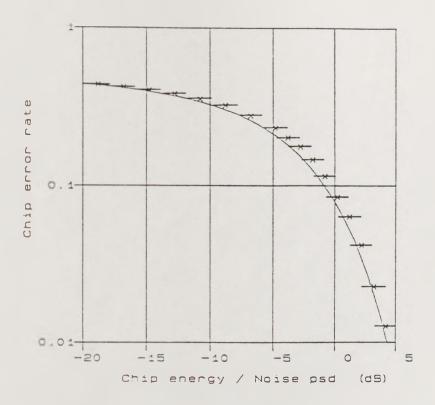

| Figure | 6-2   | Measured chip error rate                   | 243 |

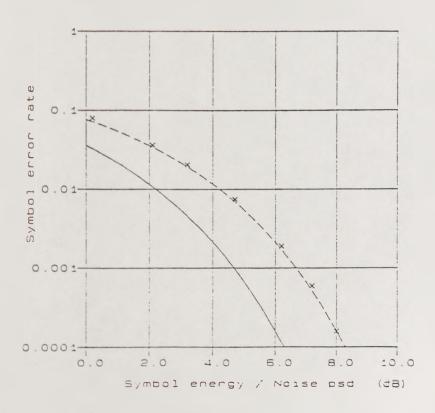

| Figure | 6-3   | Measured symbol error rate                 | 243 |

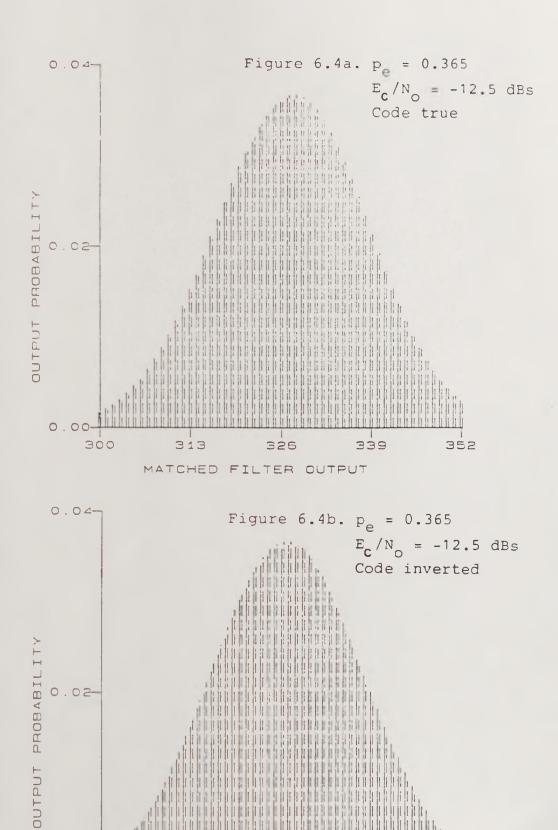

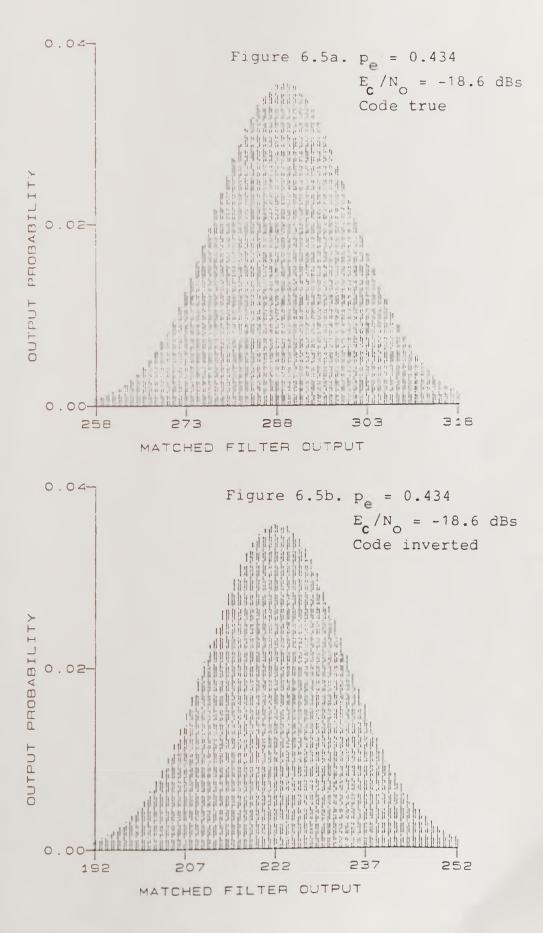

| Figure | 6-5   | DMF output probability distribution,       |     |

|        |       | $p_{e} = 0.365$                            | 244 |

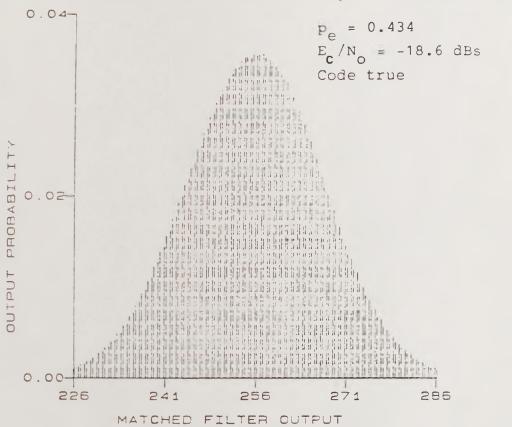

| Figure | 6-6   | DMF output probability distribution,       |     |

|        |       | $p_{e} = 0.434$                            | 245 |

| Figure | 6-5   | DMF output probability distribution,       |     |

|        |       | code out of phase and noise only           | 246 |

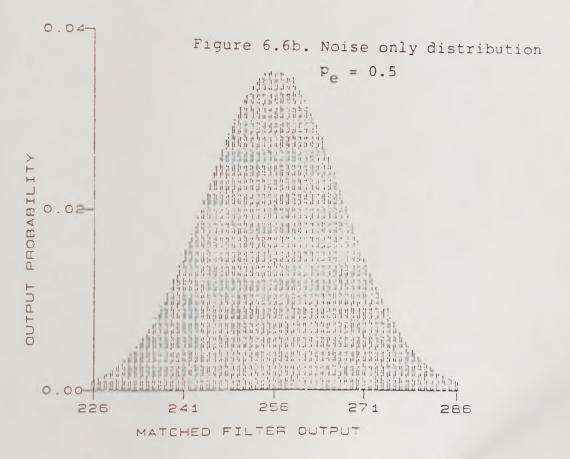

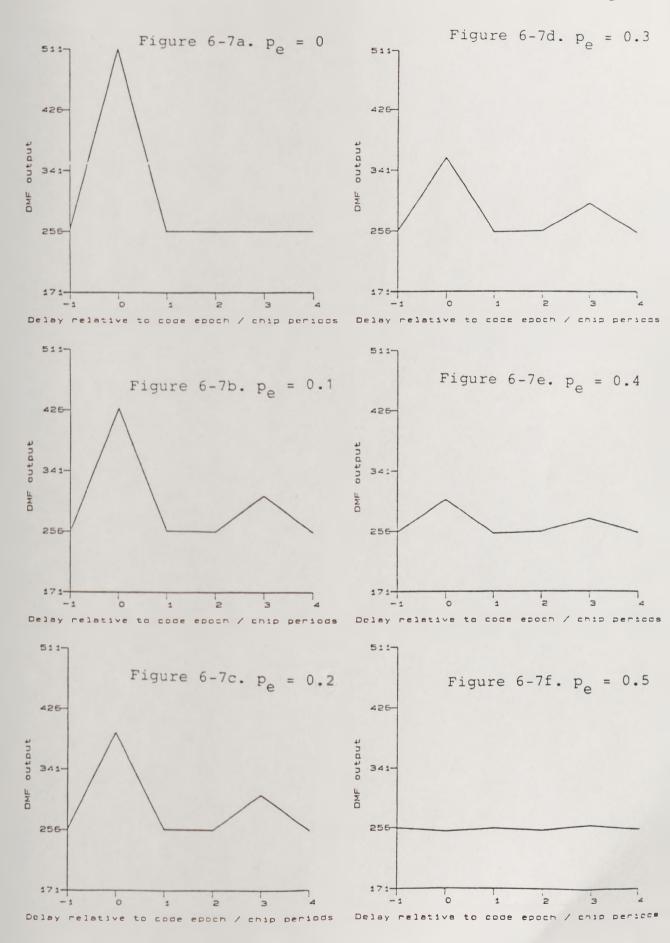

| Figure | 6-7   | DMF mean output against delay with delayed |     |

|        |       | path 6dB below main path, delayed path not |     |

|        |       | inverted                                   | 247 |

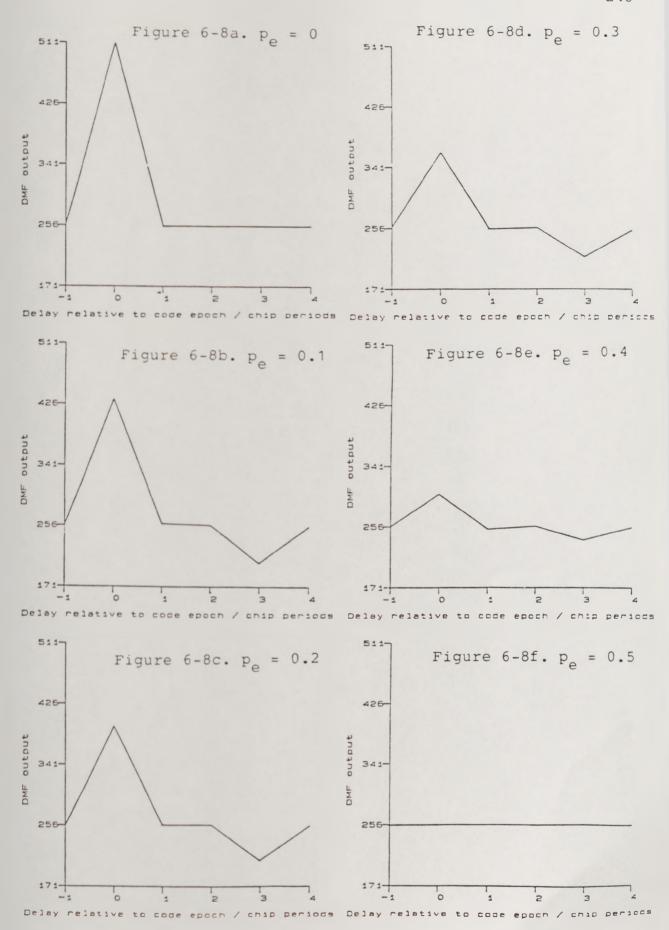

| Figure | 6-8   | DMF mean output against delay with delayed |     |

|        |       | path 6dB below main path, delayed path     |     |

|        |       | inverted                                   | 248 |

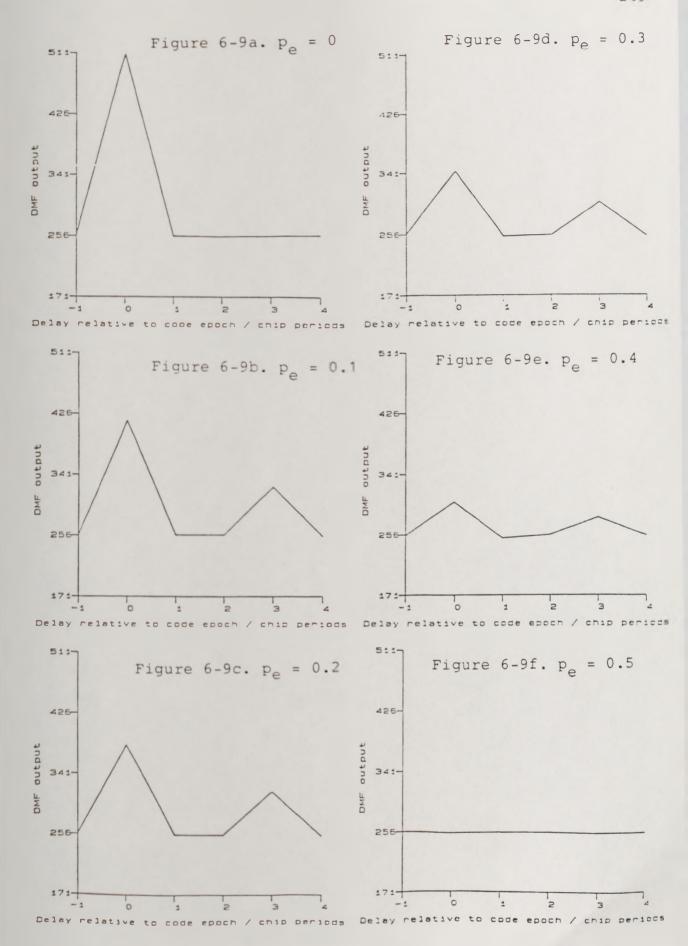

| Figure | 6-9   | DMF mean output against delay with delayed |     |

|        |       | path 3dB below main path, delayed path not |     |

|        |       | inverted                                   | 249 |

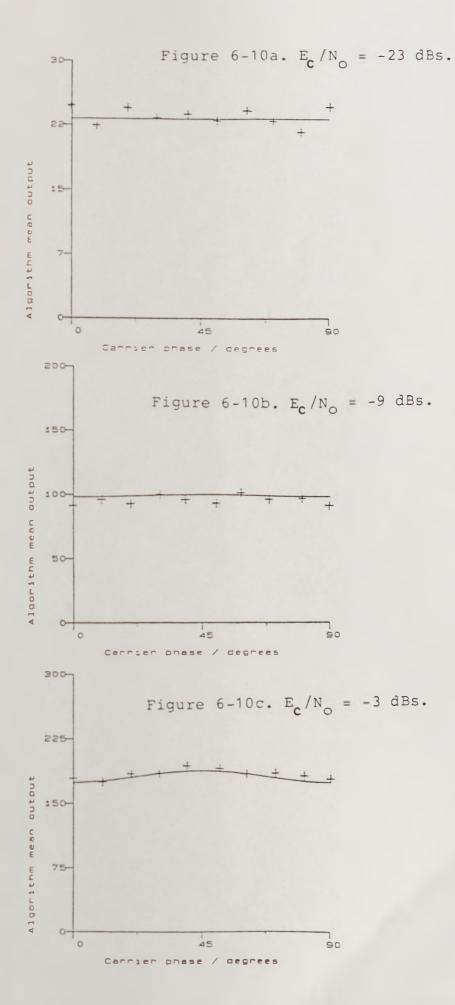

| Figure | 6-10  | Square root algorithm mean output against  |     |

|        |       | relative carrier phase                     | 250 |

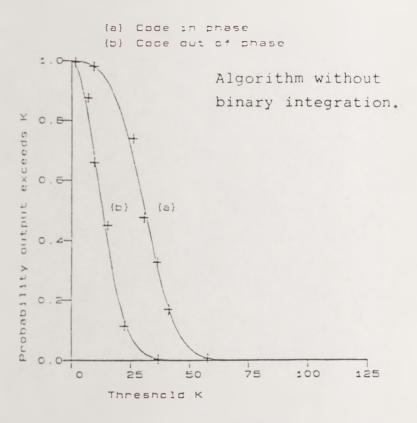

| Figure | 6-11  | Probability algorithm exceeds threshold    |     |

|        |       | output, $p_e=0.4437$                       | 251 |

| Figure | 6-12  | Probability algorithm exceeds threshold    |     |

|        |       | output, p <sub>e</sub> =0.4007             | 252 |

| Figure | 6-13  | Probability algorithm exceeds threshold    |     |

|        |       | output, p <sub>e</sub> =0.3274             | 253 |

#### ABBREVIATIONS

ADC Analogue to Digital convertor AWGN Additive White Gaussian Noise

BCD Binary Coded Decimal

BPSK Bipolar Phase Shift Keying Code Division Multiple Access **CDMA**

Central Processor Unit CPU

CVSD Continuously Variable Slope Delta modulator

8 Dirac delta function

dB Decibel

Digital Matched Filter DMF Digital Signal Processing DSP

Direct Sequence Spread Spectrum DSSS

Emitter-Coupled Logic ECL

HF High Frequency

Ι In phase

Intermediate Frequency IF

Land Mobile Radio LMR

LSI Large Scale Integration

Most Significant Bit MSB

OOK On Off Keying

Probability that x is true Prob(x)

Programmable Read Only Memory **PROM**

PSK Phase Shift Keying Quadrature phase 0

RARASE Recursion Aided Rapid Acquisition by

Sequential Estimation

Rapid Acquisition by Sequential Estimation RASE

RECT(x) Rectangular function

RF Radio Frequency

SIK Sequence Inversion Keying

SINC(x)Sin(x)/x

Signal to noise r.m.s. voltage ratio snr

TDMA Time Division Multiple Access Transistor-Transistor Logic TTL

Ultra High Frequency UHF

VCO Voltage Controlled Oscillator VLSI Very Large Scale Integration

t | ≤ 1 / 2 otherwise

#### CHAPTER 1

## INTRODUCTION

# 1.1 HISTORY OF THE PROJECT

The investigation of Direct Sequence Spread Spectrum (DSSS) systems began at Leeds in 1978 in collaboration with the Home Office Directorate of Telecommunications. The resulting broad paper study [MATTHEWS P.A. and BAJWA A.S 1979] identified the lack of published information in the public domain on the subject of practical DSSS systems. It concluded that there was a need for practical investigation into DSSS schemes, before further consideration could be given to the application of such techniques to the Land Mobile Radio (LMR) environment.

The work continued with a further study assessing the likely user capacity of such a scheme in a mobile radio system [DRURY 1981]. Whilst the user capacity did not compare favourably with proposed narrowband analogue schemes [FRENCH 1979], [TURIN 1984], the DSSS approach offered the potential advantage of some immunity to the problems of multipath fading. Further being a digital modulation scheme it naturally provided the facility for the inclusion of system control data alongside the digitized analogue 'message'. Drury concluded that the need to provide synchronization at the receiver would be a serious limitation of the active form of receiver correlation if long sequences were applied.

A further study then began in 1981, to investigate the application of Digital Matched Filters (DMFs) to receiver correlation, again in collaboration with the Home Office. The intention of the design was to avoid the need for synchronization by the use of matched filtering techniques, and to perform field trials on the system.

The study continued with support from the Home Office until March 1984, at which point several problems had been identified. The most serious problem was the requirement for receiver synchronization, a feature which had been considered undesirable at the specification stage. Furthermore difficulties in achieving operation at the desired chip rate had indicated the need for careful redesign, and highlighted potential problems in cascading short DMFs in an attempt to match to long code sequences.

Despite these difficulties it was felt that a detailed study of a receiver structure would be worthwhile, with particular emphasis on identifying losses incurred by the receiver due to non-ideal operation, and the possibility of achieving more rapid synchronization than could be achieved by an active correlator. This information could then be applied to the operation of a DSSS system in the LMR environment.

### 1.2 BACKGROUND TO THE PROBLEM

There is much literature on the subject of DSSS systems, and there has been interest in the topic since the early 1950's, following the pioneering work of Shannon. Areas of frequent interest are code properties e.g. [GOLD 1967], [SARWATE 1984], and spectral efficiency e.g. [GARDNER and ORR 1979], [HUI 1984]. In contrast few practical systems have been described, and this is indeed noticeable on the topic of practical implementations utilising the DMF as the correlation element.

At the commencement of the work in 1983 no references to practical DMF based DSSS receivers could be found. During 1984 two descriptions were given, [ASH 1984], and [SKAUG 1984], with a further paper on an analogue implementation presented by [YAMADA, DAIKOKU and USUI 1984]. The implementation described by Skaug did not include details of how the synchronization and tracking

functions were achieved as the work concentrated largely on the performance of the system in an HF radio environment. The receiver described by Ash used a delay lock loop as the synchronization scheme, a technique associated with active correlator designs and well documented as such.

Such an implementation is a somewhat inefficient use of the DMF as it does not provide a more rapid synchronization acquisition than can be achieved by the analogue delay lock loop. Clearly there was a requirement to investigate methods of obtaining rapid synchronization acquisition in DMF based DSSS receivers. This property could produce an increase in the favour of DSSS systems incorporating DMFs, which could lead to reduced system costs by the adoption of Large Scale Integration (LSI) techniques and volume sales.

One particular area in which an enhancement in synchronization performance would be a desirable property is burst transmission, particularly useful in covert applications or systems operating on an interference limited basis.

## 1.3 TERMINOLOGY USED

Where possible terminology has been chosen in accordance with that generally used in the literature. The meaning of terms used throughout this work is given here in the form of a brief introduction to Direct Sequence Spread Spectrum systems.

The term spread spectrum is taken to mean a signal which has been encoded in a manner such as to introduce considerable redundancy in the signal prior to transmission, and hence a considerable expansion in transmission bandwidth than is necessary to accommodate the signal prior to spreading. Compared to an equivalent power non-spread spectrum signal the spread spectrum signal will

be received at a lower snr, but over a wider bandwidth. This is a direct attempt to achieve improved utilisation of a transmission channel in terms of the maximum attainable channel capacity, as indicated by the work of Shannon (see for example [CARLSON 1975] pp350 to 371). Shannon's fundamental theorem states that the capacity of a channel to transmit information is a function of the channel bandwidth and the received snr. The information reception be made at an arbitrarily low error rate. constant transmission rate, bandwidth expansion allows a decrease in transmitted power. Alternatively a reduction in transmission bandwidth must be accompanied by an increase in transmitted power. The exchange is approximately exponential, see for example [CARLSON 19751 for excellent description, in favour of increasing bandwidth.

DSSS scheme direct bandwidth expansion is In а achieved by replacing each bit of digital message data by a sequence of 'm' bits, or 'chips'. The m bits constitute the 'code' sequence, or code, and are generally chosen from a set of orthogonal or nearly orthogonal codes. orthogonality is generally achieved by selecting binary codes which have low cross correlation properties. The digital message information is transmitted by modulation of the code sequence, most frequently by Sequence Inversion Keying (SIK). In this modulation scheme a code sequence is sent to represent a message bit equal to a logical true (1), and the code sequence logically inverted is sent to represent a message bit equal to a logical false (0). In this work a modulated code of length m is termed a message 'symbol'.

The received signal sequence can be correlated against the local reference code sequence to provide a detection capability. In this work the correlation process is performed by the Digital Matched Filter (DMF). A receiver can discriminate between a set of sequences received in the same bandwidth provided it has knowledge of the transmitted code sequence and the time of arrival of the end of the

code sequence. The property of signal discrimination is termed 'processing gain', and is a direct result from Shannon's law. If the receiver has knowledge of the transmitted code then each received data bit can be added coherently. The signal voltages will add directly, whereas the noise components will add on a power basis, since these will not be coherent. A net improvement in signal to noise ratio is achieved, by a factor 10log(m) dB, and this is the familiar expression for processing gain.

To utilise the processing gain a knowledge of the transmitted code must be accompanied by knowledge of the time of arrival of the end of the code, such that correlation of the m received chips can be correctly made with the m reference chips. Knowledge of the time of arrival of the code start or end is termed 'code synchronization', and forms a considerable part of the work presented in this thesis. It is apparent from the above discussion that lack of code synchronization prevents access to the DSSS processing gain, and much effort has been spent in this area for this reason.

In terms of the operation within the DMF, code synchronization can be expressed in terms of the relative phase of the received code with the reference code. The code phase is the offset between a pair of identical codes in terms of the number of chips distance between them. This may be visualised as the state of a received code in a DMF relative to a static reference code. A code in phase condition occurs when the received code has a phase of 0 chips relative to the reference code. This is the condition required for code synchronization and only occurs at 1 of m possible code phases. Alternately code out of phase is all conditions where a received code does not have a phase of 0 chips relative to the reference code, and naturally occurs for m-1 code phases.

Finally signal to noise ratios (snrs) are quoted in terms of signal voltage amplitude to noise voltage rms

(V/ $\sigma$ ) or chip energy to noise power density (E<sub>C</sub>/N<sub>O</sub>). Where comparisons are made Bipolar Phase Shift Keying (BPSK) modulation is assumed and the relationship

$$E_{c}/N_{o} = 10\log(v^{2}/2\sigma^{2})$$

is assumed [CARLSON 1975].

## 1.4 SCOPE OF THE THESIS

Chapter 2 investigates the internal workings of the DMF and its performance in a statistical sense. The approximate loss incurred by using a single level of quantization is derived.

In chapter 3 the elements required to augment two DMFs in a complex baseband receiver are studied, with emphasis placed on the losses incurred by practical implementations. Choice of lowpass filters is shown to be a complex but important aspect of receiver design. New work is presented in the area of DMF output combining algorithms, and it is shown that an estimate of the received snr can be obtained.

Chapter 4 covers the important topic of receiver synchronization, with a summary of present techniques. New techniques for achieving rapid synchronization are given. These make maximum use of the information available from the DMFs.

Construction of a practical transmitter/receiver pair is described in chapter 5 and potential problem areas are identified. The descriptions and circuits presented indicate that there is still some way to go in terms of miniaturisation before hand held DSSS receivers are a practicality.

Chapter 6 presents the results obtained from the

practical receiver. Measurements have been made in the presence of noise in support of the ideas presented in chapters 2, 3, and 4.

Finally chapter 7 draws together the results to conclude the potential of rapid acquisition techniques in DSSS systems which use the DMF.

### REFERENCES

- ASH C.P. 'Digital implementation of a narrowband satellite receiver', IEE Proceedings., Vol 131 Pt. F, No.6 October 1984, Pp 570 to 576

- CARLSON A.B 'Communication Systems', McGraw-Hill electrical and electronic engineering series, 1975.

- DRURY D. 'Direct sequence spread spectrum techniques for land mobile radio applications', 1981, PhD Thesis, University of Leeds.

- FRENCH R.C. 'The effect of fading and shadowing on channel reuse in mobile radio', IEEE Trans. VT-28 (3), 1979, pp171-181.

- GARDNER C.S. and ORR J.A. 'Fading effects on the performance of a spread spectrum multiple access communication system', IEEE Trans. Com-27, 1979, pp143-149.

- GOLD R. 'Optimal binary sequences for spread spectrum multiplexing', IEEE Trans. IT-13, 1967, pp619-621.

- HUI J.Y.N. 'Throughput analysis for code division multiple accessing of the spread spectrum channel', IEEE Vol. SAC-2, No. 4, 1984, pp482-486.

- MATTHEWS P.A. and BAJWA A.S. 'Spread spectrum signalling in Home Office radio schemes', 1979, Phase 1 Final Report, Home Office Directorate of Telecommunications, Agreement No DT 122/180/12.

- SARWATE D.V. 'Mean square correlation of shift register sequences', IEE Proc. Vol. 131 Part F No. 2, 1984, pp 101-106.

- SKAUG R. 'Experiment with spread spectrum modulation on an HF channel', IEE Proc. Vol. 131 Part F No. 1 1984, pp 87-91.

- TURIN G.L. 'The effects of fading on the performance of direct sequence CDMA systems', IEEE Vol. SAC-2 No. 4, 1984, pp 597-603.

- YAMADA K. DAIKOKU K. and USUI H. 'Performance of portable radio telephone using spread spectrum', IEEE Vol. COM-32 No. 7, 1984, pp 762-768.

#### CHAPTER 2

## THE DIGITAL MATCHED FILTER

## 2.1 INTRODUCTION

The main emphasis of this work is the study of the application of digital matched filters with single bit quantization to a DSSS system. There are several reasons for the adoption of such an approach, for example the minimization of receiver hardware, complexity, and cost. However general expressions defining the process of digital matched filtering (or digital correlation) will be determined for the general case of a length m bit by width n bit DMF. The single bit DMF (n=1) will then be studied in detail as a special case.

This chapter discusses the theoretical operation of a DMF and gives a formal definition for this. The single-bit (2-level) DMF is studied in detail and the output statistics for this filter are evaluated when the input data stream is corrupted with AWGN. Suitable approximations for the DMF output will be formulated as these are required later. A new approach to the calculation of the loss incurred by the DMF relative to the ideal matched filter is investigated for several levels of quantization. The results obtained are compared with those of other authors [BRUNO 1970], [TURIN 1976], [BAIER and BAIER 1984]. This technique can be used to extend the analysis beyond the limiting case of a data stream corrupted in AWGN provided the probability of quantizer level occupancy can be determined from the noise statistics.

## 2.2 DMF OPERATION

It was shown in chapter 1 that the main processing operation performed by a DSSS receiver is correlation. The primary function of the signal processing section of the receiver is to calculate the correlation between the received signal w(t) and the reference signal r(t) stored or generated in the receiver, such that a detection decision can be made with a finite error probability, figure 2-1.

We begin the analysis by observing that the reference signal r(t) is periodic with period R, where R=mT, m is the number of chips in a given code, and T is the chip period. Therefore the correlation may be performed over one period R of r(t) and can be defined as

$$v(y) = \int_{0}^{R} r(t) w(t-y) dt$$

(2-1)

It has been shown [STREMLER 1977] that the processes of correlation and matched filtering are related and therefore we begin by expressing the appropriate matched filtering operation as

$$v(t) = \int_{0}^{R} r(R-y) w(t-y) dy \qquad (2-2)$$

We may now consider a digital approach to the matched filtering operation by taking sampled and quantized versions of r(t) and w(t) where  $r_k=r(kT)$  and  $w_k=w(kT)$  are

samples of r(t) and w(t) at t=kT respectively, T is the chip period, and k is an integer. In most applications m will be equal to the number of samples in the reference signal r(t). This may not be the case for applications such as ranging, where accurate chip alignment is required. In this case multiple samples of a chip may be required resulting in a proportional increase in the length of the matched filter.

Now (2-2) may be expressed in terms of the sampled quantities

$$v_{k} = \sum_{i=0}^{m-1} r_{k-i} w_{k-i}$$

(2-3)

where m is the code length.

We may write  $r_k$  as a j bit number such that

$$j-1$$

$$2r_{k} = \sum_{q=0}^{j-1} r_{k,q} 2^{-q}$$

(2-4)

and  $w_k$  as an n bit number such that

The coefficients  $r_{k,g}$  and  $w_{k,h}$  take on the values +1,-1 only, and further  $r_k$  and  $w_k$  are restricted to lie in the range {+1,-1}. Therefore for the sampled and quantized signal and reference the expression (2-3) may be written

$$v_k = \sum_{i=0}^{m-1} \begin{cases} j-1 & n-1 \\ \sum_{k-i,g} z^{-g} \begin{cases} \sum_{k-i,h} w_{k-i,h} & 2^{-h} \end{cases} \end{cases}$$

(2-6)

$$= \sum_{h=0}^{n-1} \left\{ \sum_{g=0}^{j-1} 2^{-(g+h)} \left\{ \sum_{i=0}^{m-1} r_{k-i,g} w_{k-i,h} \right\} \right\} (2-7)$$

The full implementation of (2-7) would require a j bit by n bit by m bit correlator structure.

Such a scheme is practical in the sense that digital correlation leads directly to a bit-slice approach to implementation [CHRISTIE 1986]. However (2-7) defines the most general case of a quantized signal data stream correlated against a reference which has a set of coefficients  $\mathbf{r_k}$  which may each take on any value in the range  $0..2^{j-1}$ . It has been shown [HOLMES 1982] that for optimum correlation the reference code should be filtered in a manner identical to the filtering imposed on the transmitted code by transmitter, channel, and receiver filtering. Therefore the coefficients chosen for  $\mathbf{r_k}$  should represent the effect of this filtering on the reference code. The transfer functions of the transmitter and receiver filters can be determined but in practice the overall transfer function of the required filtering process

is not likely to be known at the receiver. This is due to the time varying response of the channel [STREMLER 1977]. Therefore the analysis proceeds with the assumption that reference code filtering is not practical.

We may thus write (2-4) as  $\{r\} = \{+1,-1\}$ . The reference can therefore be written in the same form as the transmitted code prior to modulation

$$r(t) = \sum_{j=0}^{m-1} d_j \cdot y(t-jT)$$

$$(2-8)$$

where

$$d_j = \{+1,-1\}$$

for  $j = \{0,..,m-1\}$

and  $y(t) = 1$  for t in the range  $0$ . T

Having simplified (2-4) and (2-5) it is now possible to simplify (2-7) giving

$$v_{k} = \sum_{h=0}^{n-1} \left\{ \sum_{i=0}^{m-1} r_{k-i,0} w_{k-i,h} \right\}$$

(2-9)

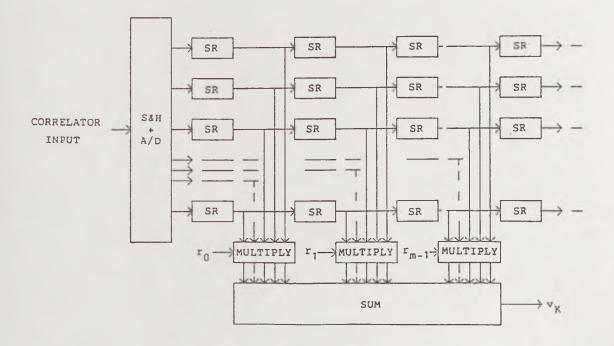

It can be seen from (2-9) that the correlation result is formed from a scaled summation of n separate length m correlations, shown schematically in figure 2-2. Since the reference coefficients are not a function of h the order of summation may be reversed giving

$$v_{k} = \sum_{k=1,0}^{m-1} r_{k-i,0} \sum_{h=0}^{m-1} w_{k-i,h}$$

(2-10)

It is interesting to observe the difference in computational effort required to evaluate (2-10) relative to the evaluation of (2-9). Assuming that a summation of y elements requires y additions we may calculate the computational effort required by observing that (2-9) is n sets of m multiplications and m additions with a further n additions for the final summation and (2-10) is m sets of additions and 1 multiplication with a further m additions for the final summation. This gives the results of table 2-1.

TABLE 2-1 Mathematical operations needed to solve (2-9) and (2-10)

| Equation        | ation (2-9) |         |

|-----------------|-------------|---------|

| Additions       | n.(m+1)     | m.(n+1) |

| Multiplications | m.n         | m       |

In general multiplication of digital numbers is more computationally intensive than addition since multiplication is usually performed by a series of addition and shift operations. It would seem, therefore, that the calculation of (2-10) is preferable to that of (2-9) on the basis of computational complexity. However to test this hypothesis it is necessary to consider the way in which the

operations of addition and multiplication might be performed by a digital correlator. The summation over m in a length m bit by width n bit correlator can be performed canonically by an array of n adders, each with m inputs. This approach is likely to suffer from speed limitations at high bit rates [CHRISTIE 1986]. Figure 2-3 shows one of the n sections required for a full implementation.

Alternatively a pipelined approach can be adopted resulting in the need for n by m adders, figure 2-4, where the number of inputs per adder depends on the position the pipeline but reaches a maximum of only 9 bits for a 511 bit correlator. This is a much more realisable technique and has been adopted in practical devices [TRW 1980], [MEDL 1986]. Initially the operation of multiplication appears more complicated than that of addition. However close examination of (2-9) shows that the multiplication of  $r_{k-i,0}$  by  $w_{k-i,h}$  is simply the multiplication of two single bit numbers. By suitable scaling of r and w, and accounting for a resulting offset in v, it is possible to multiplication operation by replace the exclusive-NOR function. This simplifies the implementation section of the considerably, and one corresponding to the input stream  $W_{k-1,1}$ is shown in figure 2-5. Since only single bit data is being correlated only a single bit shift register is required for each element of w.

The final correlation result is calculated by taking a weighted sum of the outputs from each section of the correlator corresponding to each element of w. Therefore the evaluation of (2-9) can be performed by an array of n single bit correlators of length m followed by a suitable adder. Now the evaluation of (2-10) requires an array of m adders of width n plus suitable pipelined adders to form the result, figure 2-6. This is clearly a less efficient solution. Therefore correlator implementation according to the order of operations of (2-9) is more efficient than that of (2-10) despite the apparent number of

multiplications required. This is because the multiplications of (2-9) reduce to single bit multiplications. Further the binary representation of these numbers allows these multiplications to be implemented as the simple exclusive-NOR function. This is not the case in (2-10) where a single bit number must be multiplied by an n bit number.

Finally we consider the practical implications of taking a single bit approximation to w(t). For this case n=1, and (2-9) and (2-10) become

$$v_{k} = \sum_{i=0}^{m-1} r_{k-i,0} w_{k-i,0}$$

(2-11)

It is interesting to observe that under this condition the theoretical limitation on the range of allowable values for w(t) is removed, since  $w_{k,h}$  is determined simply by the sign of w(t). Further if it is necessary to constrain w(t) to lie in the range  $\{+1,-1\}$  then a knowledge of the expected amplitude of w(t) must be assumed at the receiver. This is necessary such that the quantization levels may be determined, or automatic gain control implemented. The effectiveness of the receiver may thus be restricted and it will be shown that the potential performance improvement due to multibit quantization may not always be achieved in practice. This is particularly serious during the critical stage of synchronization, where it is unlikely that the receiver will have knowledge of the received snr.

It will be shown in section 2.5 that the additional expense and complexity of a multibit DMF structure may be wasted by incorrect choice of quantization levels for a given input snr. Although the single bit DMF may never

quite achieve the performance of the multibit DMF the relative performance loss is surprisingly low.

One advantage of the single bit DMF, therefore, is the removal of the need for automatic gain control of the received signal w(t).

In summary it can be seen that the function of the DMF is to approximate the operation of an analogue matched filter, or correlator. This is achieved by performing summations of the signal and reference in sampled and quantized form. The DMF is constructed from an array of shift registers and adders. The number and complexity of the required adders is reduced by a parallel approach. This reduces many of the necessary addition operations to the simpler Exclusive-NOR operation.

## 2.3 DMF OUTPUT STATISTICS

We now examine the statistics of DMF operation. This will allow an estimation to be made of the performance of the DMF based DSSS receiver when signals are received in the presence of noise. This is important since DSSS systems are generally operated at low received snrs, either due to the desire for signal concealment, or as a result of operation at interference limited levels in overlay schemes.

# 2.3.1 APPROXIMATION FOR CHIP ERROR PROBABILITY WITH HARD LIMITING

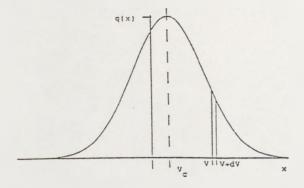

We begin by examining the statistics of chip decisions. The Gaussian probability density function for a bipolar binary signal of equally likely amplitudes of  $^{+V}_{\rm C}$  and  $^{-V}_{\rm C}$  in bandlimited AWGN of zero mean and variance  $^{2}_{\rm C}$  is given by [PAPOULIS 1984]

$$q(V) = e^{-(V-V_c)^2/2\sigma^2} / ((2\pi)^{1/2} \sigma)$$

(2-12)

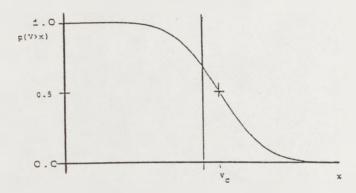

This is the probability that the instantaneous voltage will be in the range V to V+dV, figure 2-7. The cumulative distribution function, figure 2-8, or the probability that the instantaneous voltage will be less than some value x is given in normalised form as

$$Q(V_{e}) = \int q(x) dx \qquad (2-13)$$

This then gives the error probability for a hard limiter operating under the given conditions, with  $x=V_{_{\hbox{\scriptsize C}}}$ , and decision threshold set to 0 volts, figure 2-9, giving

$$Pr(chip error) = Q(V_{C}/\sigma)$$

(2-14)

The integral of (2-13) cannot be evaluated in closed form and therefore numerical techniques or tables are necessary to evaluate the function, [CARLSON 1975]. The function Q(V) is identical to the complementary error function, Erfc(V) [STREMLER 1977].

It is generally desirable to operate spread spectrum systems at low received snrs where advantage can be taken of the potential processing gain of the receiver. Consequently the expected value of  $V/\sigma$  at the receiver will be less than 1, and under this condition we may approximate the function Q(V).

By substitution we obtain

$$Q(V) = (2\pi)^{-1/2} \int_{V}^{\infty} e^{-y^2/2} dy$$

(2-15)

Since terms in the expansion of  $e^{x}$  cannot be evaluated at infinity it is necessary to introduce the error function

$$erf(K) = (2/\pi)^{1/2} \int_{0}^{K} e^{-t^2} dt$$

(2-16)

which is related to the function Q(K) by

$$Q(K) = (1 - erf(K/2^{1/2}))/2$$

(2-17)

Expanding (2-16) in terms of  $e^{-t^2}$  gives [PAPOULIS 1984]

erf(K) =

$$2e^{-K^2}/\pi^{1/2} \sum (2^n K^{2n+1})/(1.3...(2n+1))$$

(2-18)

$$= 2e^{-K^2}/\pi^{1/2} (K + 2K^3/3 + 4K^5/15 + ...)$$

$$= 2K/\pi^{1/2}$$

(2-19)

for small K. Therefore from (2-14), (2-17), and (2-19) we obtain

Pr(chip error) =

$$1/2(1-(2/\pi)^{1/2}K)$$

(2-20)

$$= 1/2 - K/(2\pi)^{1/2}$$

(2-21)

The error due to using this approximation compared to an accurate numerical technique is shown in figure 2-10 for V/ $\sigma$  in the range 0 to 0.5, (E<sub>C</sub>/N<sub>O</sub> less than -9dB for BPSK modulation). In this range the error is less than 3 percent.

# 2.3.2 APPROXIMATION FOR DMF OUTPUT - BERNOULLI TRIALS

We now extend the analysis to consider the case of m binary trials. Each trial is assumed independent but the error probability is constant for all trials. Such an event is generally termed a Bernoulli trial [PFEIFFER and SCHUM 1973]. We assume without loss of generality that the desired outcome is a string of m ones. If we now assign an error probability,  $p_e$ , to each event and further assume that  $p_e$  remains constant throughout m trials then we may calculate the pdf of the possible outcomes from the Binomial theorem [PAPOULIS 1984]

$$Pr(result=K) = C p_e^{K} (1-p_e)^{m-K}$$

$$K$$

(2-22)

where

$$m$$

$C = m!/((m-K)!K!)$

$K$

For detection we are interested in finding the probability that the result exceeds a value K. Therefore from (2-22) we define the discrete output probability of an outcome K as

$$Pr(result=K) = b(m,K,p_e)$$

(2-24)

Whence

$$Pr(result < K) = \sum b(m, K-1, p_e)$$

(2-25)

K-1

j=0

$$= B(m, K-1, p_e)$$

(2-26)

Further the probability that the result exceeds K is found by subtraction from unity, this being the total cumulative probability, giving

$$Pr(result>K) = 1 - B(m,K,p_e)$$

(2-27)

Again in (2-24) and (2-26) the numerical evaluation of factorials and summations becomes cumbersome, particularly for large values of m. However these functions may be approximated in a form more convenient for direct evaluation. Introducing the notation  $p=p_e$ ,  $q=1-p_e$ , it can be shown [PAPOULIS 1984] that if mpq>1 then

$$p^{K} q^{(m-K)} = e^{-(K-mp)^{2}/(2mpq)}$$

(2-28)

for K in the neighbourhood  $(mpq)^{1/2}$  of mp. For p in the range of practical interest (0.3 to 0.5) this will imply large m.

Equation (2-28) is an application of the DeMoivre-Laplace theorem, and is based on Stirling's approximation

$$m! = m^m e^{-m}/(2mm)^{1/2}$$

(2-29)

Returning to the definitions of (2-12) and (2-13) in normalized form we have

$$q(y) = e^{-y^2/2}/(2\pi)^{1/2}$$

(2-30)

and

$$Q(x) = \int_{x} q(y) dy \qquad (2-31)$$

We can equate terms from (2-12), (2-28) and (2-30) to show that for 0.3

$$C p^{K}q^{(m-K)} \approx (mpq)^{-1/2} q((K-mp)/(mpq)^{1/2})$$

(2-32)

Therefore using (2-32) in (2-22) the evaluation of the probability that the result is K for a given value of  $p_{\rm e}$  is reduced to the evaluation of the normal curve. Further

$$Pr(K1 < K < K2) = \sum_{K=K1}^{m} C p^{K} q^{(m-K)}$$

$$(2-33)$$

K2

K=K1

$$= (mpq)^{1/2} \sum q((K-mp)/(mpq)^{1/2})$$

(2-34)

Now since the curve

$$q((K-mp)/(mpq)^{1/2}) = e^{-(K-mp)^2/2mpq}$$

(2-35)

is nearly constant over a unit interval for mpq>1 the area in that interval is approximately equal to the ordinate, therefore

K2

$$\sum_{q((K-mp)/(mpq)^{1/2})} = \int_{q((K-mp)/(mpq)^{1/2})} dK \quad (2-36)$$

$$K=K1 \quad K1$$

$$= Q((K2-mp)/(mpq^{1/2})) - Q((K1-mp)/(mpq^{1/2}))$$

(2-37)

If the lower limit is zero then it can be shown [PAPOULIS 1984] that the second term of (2-37) is 0 giving

$$B(m,K,p_e) = Q((K-mp_e)/(mp_e(1-p_e)))$$

(2-38)

An improved approximation can be found by expressing q(K) as the incremental slope of Q(K) rather than it's derivative.

Putting

$$M = (mpq)^{1/2}$$

we obtain

$$q(K) = M \{Q((K+0.5)/M) - Q((K-0.5)/M)\}$$

(2-39)

and therefore

$$\sum_{K}^{m} q^{(m-K)} \approx Q((K2+0.5-mp)/M) - Q((K1-0.5-mp)/M)(2-40)$$

K = K1

Again if K1=0 it can be shown that

$$B(m,K,p_e) = Q((K+0.5+mp)/M)$$

(2-41)

The similarity between the functions (2-12) and (2-38) can be investigated by evaluating the mean and variance for the Binomial distribution.

For this we have

$$\operatorname{Mean}(K) = \sum_{K} K C p^{K} q^{(m-K)}$$

$$K=1$$

(2-42)

$$= \sum_{K=1}^{K} \frac{m!}{(m-K)!K!} p^{K} q^{(m-K)}$$

(2-43)

$$m-1$$

=  $mp \sum_{j=0}^{m-1} C_{p^{j} q^{(m-j)}} (2-44)$

where j=K-1, from which

m

$$Mean(K) = mp (2-45)$$

since the summation of (2-44) is equal to 1.

Similarly the variance may be determined

$$Variance(K) = \sum_{K=1}^{m} K^{2} C p^{K} q^{(m-K)}$$

$$(2-46)$$

which by a similar method gives

Variance(K) = mpq

(2-47)

### 2.3.3 DMF OUTPUT - CODE IN PHASE

The previous discussion introduced the output pdf of a trial of m independent binary events or Bernoulli We may now consider the probability of a decisions. particular output from an m bit DMF for an input data code, where the data is a hard-limited estimate of a known binary code in AWGN, figure 2-9. First we consider the case where the sampled data in the on-line (received signal) register (figure 2-5) of the DMF is in alignment with the fixed reference register data. This condition is generally termed 'code in phase', or the code 'epoch'. We may evaluate the probability of a specific output value from the DMF for a given snr at the hard-limiter input by using expressions (2-21) and (2-24) of the previous section. The actual form of the code, that is the number of ones and their positions, is not relevant to this part of the argument since each data element is assumed to be independent of all others, and their value (zero or one) is based on the any chip probability that is in error from corresponding element in the reference register. The in phase case is, therefore, a straighforward Bernoulli trial of m independent events. If SIK data modulation is used then, in the absence of noise or interfering signals and hence hard-limiter errors, the expected output from the DMF will be m for a data symbol 1 received and 0 for a data symbol O received, since in this case the data will be inverted. With a known input snr, and thus known chip error probability, the output pdf is Binomially distributed about the mean values  $m(1-p_a)$  for a data 1 received, and about

mp<sub>e</sub> for a symbol 0 received, figure 2-11. The pdfs of figure 2-11 are "mirror-images" about the mid-point m/2. This is simply due to the definitions designating a symbol 1 or 0 received.

If a symbol 1 is received but the pdf calculated on the number of chip disagreements rather than agreements then the resulting distribution is identical to that for a symbol 0 received but calculated on the basis of the number of chip agreements. Clearly the average ordinate or mid-point of these two, figure 2-11, is the value m/2, irrespective of the values of m or  $p_e$ . Now since the mean values are  $m(1-p_e)$  and  $mp_e$  it can be seen that as  $p_e$  is reduced the distributions move away from the mid-point. As  $p_e$  is increased towards 0.5 the distributions move towards the mid-point, figures 2-11a, 2-11b, 2-11c. To determine if a symbol 1 or 0 is present in the on-line register we need a measure of discrimination between the two cases. To do this we examine the cumulative distribution of (2-27) rather than the discrete distribution of (2-24).

This is illustrated in figure 2-12 for a 511 bit DMF with chip error probability of 0.42 (E<sub>C</sub>/N<sub>O</sub>=-17 dB for BPSK modulation). The results show that for either symbol in the on-line register the cumulative probabilities rapidly approach zero, above a given ordinate for the in phase case, and below a given ordinate for the out of phase case. Further since the discrete pdfs are known to be symmetrical with corresponding amplitudes spaced a distance  $m(0.5-p_0)$  from the mid-point m/2 the cumulative probabilities must also be symmetrically identical, with corresponding amplitudes spaced at  $2m(0.5-p_e)$ . Clearly if we know that the current DMF output corresponds to a symbol alignment (either symbol 1 or symbol 0) then it is only necessary to decide if the DMF output is greater than or less than m/2 to make the optimum detection estimate of a symbol 1 or 0. This will give minimum symbol error probability in the presence of chip errors, assuming equally likely symbols. Whilst this result may appear

obvious it can only be applied to the case where the symbol in the on-line register is known to be in alignment with the reference symbol, that is the symbol decision instant is code-synchronized. It will be shown that this has serious implications for the available processing gain available from the DMF during synchronization.

## 2.3.4 DMF OUTPUT - CODE OUT OF PHASE

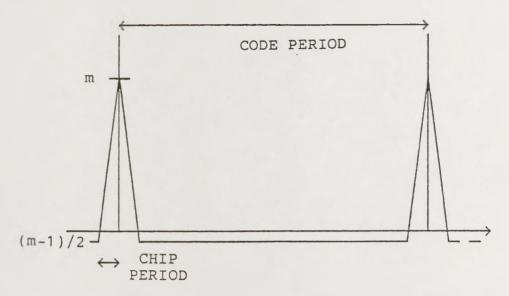

For a binary code of m elements there are m-1 out of phase conditions between on-line and reference registers. In the absence of chip errors the DMF output will be determined by the out of phase autocorrelation function of the code. Values for some codes have been evaluated [GOLD 1967], [GOLOMB 1967], [BEALE 1982], but for the sake of clarity the discussion will be restricted at this stage to codes with uniform out of phase autocorrelation properties, figure 2-13. In particular the codes considered (m-sequences) have a uniform out of phase autocorrelation value of -1, that is there is one more disagreement than agreement between the on-line and reference registers. This assumes a chip error probability of 0.

For a practical m-sequence of length m (where  $m=2^K-1$ , K is an integer) the error free out of phase condition will result in (m+1)/2 disagreements and (m-1)/2 agreements between on-line and reference registers. For a given value of  $p_e$  the pdf corresponding to the out of phase condition is similar in shape to that for the in phase condition. However the pdf is centred about the out of phase autocorrelation value, that is the shape of the pdf is determined by the value of  $p_e$  but the mean is always equal to the out of phase autocorrelation value. The mean can be evaluated by considering the length m code to consist of a pair of sub-sequences, sequence x of length (m+1)/2 corresponding to disagreements, and sequence y of length (m-1)/2 corresponding to agreements. Since the chips are assumed independent the sequence pair can be considered

independently on a statistical basis. Therefore considering the mean of each sequence we have from (2-45)

Mean number of agreements in

$$x = (m+1) p_e/2$$

(2-48)

Mean number of agreements in

$$y = (m-1)(1-p_e)/2$$

(2-49)

since  $\mathbf{p}_{\mathbf{e}}$  is common to both sequences. The resulting mean is found by addition giving

Mean output =

$$(m-1) (1-p_0)/2 + (m+1) p_0/2$$

$$= (m-1)/2 + p_e$$

$$=$$

m/2 (2-50)

since  $p_e = 0.5$ .

The pdfs corresponding to in phase and out of phase conditions are shown in figures 2-15a to 2-15c for lowering snr values. The out of phase case appears as the centre distribution in 2-15a to 2-15c, the in phase case with code true appears to the right of the out of phase case, and for comparison the in phase case with code inversion appears to the left of the out of phase case. This shows that the pdfs are similar in shape but does not take into account the m-1 occurrences of the out of phase condition for each in phase condition. From the above it can be seen that if a symbol decision is made on the DMF output when the code is out of phase and with a decision threshold of m/2 then the symbol error probability will be approximately 0.5. This is the case for all values of  $p_{\rm e}$ , assuming that m is much greater

than pe.

Finally for the out of phase condition the variance is given by

Total variance =

$$1/2$$

( Variance(x) + Variance(y) ) (2-51)

which from (2-47) gives

Total variance =  $1/2 ((m-1)p_eq_e + (m+1)p_eq_e)$

$$= mp_e q_e \tag{2-52}$$

where  $q_e = 1-p_e$ . Hence the variance is the same as for the in phase case.

# 2.3.5 NOISE ONLY

If the input snr to the hard limiter of figure 2-9 is reduced to 0 (noise only) then from (2-22) the DMF output pdf is

$$m$$

Pr(Output=K) = C  $(0.5)^{m}$  (2-53)

since  $p_e = q_e = 0.5$

Clearly this is not changed by the code phase since the signal is zero, or by the noise amplitude providing this is greater than zero but not greater than would be acceptable

in a practical implementation. The mean value of this distribution is again  $m(1-p_e)=m/2$ , as for the out of phase case. Similarly the variance is  $mp_eq_e$ . The DMF output pdf for the noise only case is shown in figure 2-14. This does not vary with absolute noise level, within practical limits, provided the signal level is 0, since the resulting chip error probability will always be 0.5.

#### 2.4 DETECTION CRITERION

#### 2.4.1 CODE SELECTION

From the previous discussions and diagrams it can be seen that a knowledge of the time at which the code is in phase (code epoch) is necessary for the correct sampling of the DMF output, to minimize the symbol error probability, and hence optimize data demodulation. For the code out of phase condition the cumulative distribution is similar to that for the noise only case. The discrete probability distribution for the in phase case is approximately centred about the value  $m(1-p_e)$  whilst that for the noise only case is centred about the value m/2. If a code is selected which has an out of phase autocorrelation value close to m/2 then the out of phase discrete probability distribution is also centred about the value m/2. Such codes are often termed 'pseudonoise' codes.

### 2.4.2 EFFECT OF MODULATION

## 2.4.2.1 SEQUENCE INVERSION KEYING

We now consider the effect of SIK modulation on the DMF output probability distribution. It has been shown that for a sequence inversion the DMF output distribution is reversed. For the out of phase condition the probability of correctly detecting a symbol 1 or 0 will be identical if

the decision threshold is set to the out of phase autocorrelation value, assuming equally likely symbols. For the in phase case the optimum threshold value is that which minimizes the probability of symbol errors under the same conditions. It can be seen from figures 2-11 and 2-12 that this must be the value m/2 by symmetry. Therefore to give an equal symbol error probability for the in phase case (regardless of the symbol) we must choose a symbol decision threshold at the DMF output of m/2. Furthermore to produce identical cumulative probabilities for the out of phase condition we must choose a code with an out of phase correlation value of m/2, for all code phases. In practice m may be an odd number and it may be necessary to choose a code with an out of phase autocorrelation value of (m-1)/2. The autocorrelation function of such a code, figure 2-13, is optimum in the sense that it maximizes the distance DMF output between code in phase and code out of phase values in the absence of noise, and with noise present is still optimum in the sense that it maximises the ratio of in phase to out of phase autocorrelation values for any particular DMF output K whilst still accounting for the two possible in phase cases due to modulation. modulation it is essential that such a code be used in order to obtain the maximum processing gain from the DMF.

### 2.4.2.2 ON-OFF KEYING

We now turn our attention to an alternative modulation scheme, ON-OFF keying (OOK), which may be useful in certain applications. With ON-OFF keying a sequence is transmitted to represent a symbol 1 and no sequence (no energy transmission) represents a symbol 0. If we assume coherent RF demodulation but assume an arbitrary phase offset of 0 or 180 degrees then the in phase probability distribution will be identical to the in phase case for SIK modulation as discussed. As we have no prior knowledge of the phase offset and assuming that phase offsets of 0 or 180 degrees are equally likely then the probability that the DMF output

probability distribution has mean  $m(1-p_0)$  is equal to the probability that the output probability is equal to  $\ensuremath{\text{mp}}_{e}.$  Both cases, therefore, would need to be interpreted as receiving a symbol 1. For a symbol 0 received the DMF output probability distribution would be identical to that the noise only case. The three probability distributions are shown in figures 2-16a to 2-16c for comparison with figures 2-15a to 2-15c, using the same probabilities for the code in phase case corresponding diagrams in 2-16 as used in 2-15. Again the in phase case with code true appears as the rightmost distribution for each value of snr, the in phase case with code inverted as the leftmost distribution, but the out of phase case has been substituted by the noise only case and appears as the centre distribution for each value of snr.

For the OOK case the optimum decision threshold is not m/2, but somewhere between m/2 and m, or m/2 and 0. Thus two decision thresholds must be accounted for and it is apparent that exceeding the upper threshold or failure to exceed the lower threshold defines a symbol one received, and failure to exceed the upper combined with exceedance of the lower threshold defines a symbol zero received, at the code epoch in the case of a symbol one received, and at an assumed code epoch (no signal received) in the case of a symbol zero received. Therefore the maximum distance between decisions of symbol ones and zeros has been drastically reduced and hence the sensitivity or processing gain of the DMF will also be lost.

A first order estimate of a possible choice of decision threshold is now given, the argument assumes a symbol 1 received as a positive DMF output.

For low snrs the DMF output pdfs for noise only and code in phase conditions are assumed to be similar in shape, only differing by their respective mean values. If the pdfs are similar then the cumulative pdfs will also be similar in shape, again only differing by the mean values

at which the respective curves reach the value 0.5. Therefore the probability of making a symbol decision error for the noise only case is the probability that the DMF output exceeds some threshold x, and for the symbol 1 case the error probability is the probability that the DMF output will be equal to or less than the threshold x. The optimum choice of threshold must be that which makes these two error probabilities equal, and assuming the DMF pdfs curves are equal in shape for noise and symbol 1 cases, then the value x will be the mid-point between the two pdfs. For noise only the mean DMF output was shown to be m/2, and for the code in phase condition it was shown to be  $m(1-p_0)$ .

Therefore the threshold x is the mean of these,

Threshold =

$$m(3/4 - p_e/2)$$

(2-54)

Similarly it can be shown that if the symbol 1 is received such as to cause a negative DMF output then the threshold value should be set to

Threshold =

$$m(1/4 + p_e/2)$$

(2-55)

This result highlights two serious problems with this type of modulation scheme. Firstly the choice of threshold is dependent upon the value of  $\mathbf{p}_{e}$  and hence the received snr, this is unlikely to be known by the receiver prior to synchronization. Secondly the distance between deciding a symbol 1 and a symbol 0 received has been reduced by a factor of 2 and the resultant symbol error rate increased accordingly.

The problem is examined further in chapter 4 where the problem is addressed in terms of the performance of the DMF during code synchronization acquisition.

The main difference between the effect of OOK and SIK modulation on the DMF output probabilities has been introduced. Clearly if SIK modulation is used it is essential to maintain phase coherence between the transmitter and receiver local oscillators. If OOK modulation is used this condition can be relaxed to some extent at the expense of system sensitivity.

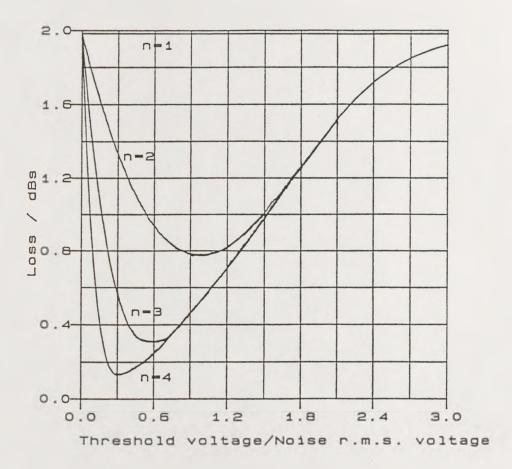

### 2.5 EFFECT OF QUANTIZATION ON DMF PERFORMANCE

The analysis of DMF performance for various quantization levels has been performed by several authors, e.g. [BRUNO 1970] for multilevel quantization, [TURIN 1976] and [BAIER and BAIER 1984] for single level quantization. An alternative technique is developed here, based on the statistics of the input samples. The samples are considered to belong to a sufficiently large set such that the probability of occupancy of a particular quantization level is determined solely by the probability density function of the input signal plus noise. The mean and variance of the quantizer output are then determined. The loss due to quantization can then be found by comparing these with the mean and variance at the output of the ideal matched filter.

It was shown in Chapter 1 that under ideal conditions and using the appropriate matched filter the processing gain available to a spread spectrum receiver is 10log(m) dBs where m is the code length. We now consider the loss of processing gain due to quantization, since the DMF is an approximation to the ideal matched filter.

From the definition of processing gain

$$PG = (mean snr)_{output} / (mean snr)_{input}$$

(2-56)

it can be seen that we must examine the quantizer output statistics before the mean and variance can be determined. These will be independent of the DMF length, m, provided m is sufficiently large such that the quantizer input probability distribution can be considered to be equal to the expected or average probability distribution. This condition is also necessary when considering chip error probabilities since these are also assumed to be average error probabilities.

We begin by defining the mean and variance as in (2-42), (2-46) where

$$Mean(k) = \sum_{k=1}^{L} k p(k)$$

(2-57)

$$Var(k) = \sum_{k=1}^{L} k^2 p(k)$$

(2-58)

for an event with L outcomes, and probability of occurrence p(k) for each unique outcome. For an n bit quantizer there are  $2^n$  unique output states, giving  $L = 2^n$ .

Now if uniform and bipolar quantization (table 2-2) is assumed (2-57) and (2-58) cannot be applied directly since positive quantizer outputs are in the range 0 to n-1, and negative outputs are in the range -1 to -n. However without loss of generality the quantizer outputs can be assigned a new 'index' for k and an average weight,  $W_k$ , associated with each index. The new index is incorporated in table 2-2 for clarity.

Thus the mean may be written as

n

n

$$Mean(k) = \sum_{k=-n} W_k p(k)$$

$$k=-n$$

$$k \neq 0$$

(2-59)

$$= \sum_{k=1}^{\infty} W_{k} p(k) + W_{-k} p(-k)$$

(2-60)

and putting V(k) = (W(k) - Mean) the variance becomes

$$Var(k) = \sum_{k=1}^{\infty} (v_k)^2 p(k) + (v_{-k})^2 p(-k)$$

(2-61)

It now only remains to formulate the error probabilities p(k). From figures 2-7 and 2-8 it can be seen that, assuming a rectangular pulse in AWGN, it is only

necessary to evaluate the normal curve at the appropriate quantization levels and by subtraction the average error probabilities can be found for each interval. However the probability associated with a given quantization interval for a given input snr is clearly determined by the choice of interval width, or quantization threshold,  $V_t$ . Therefore, using (2-60) and (2-61), the expression (2-56) has been evaluated for a range of quantization levels, figure 2-17, relative to a constant input snr of -17 dBs. Examining figure 2-17 in detail shows that a constant loss of almost 2 dBs can be expected from single-bit quantization (hard-limiting), whereas for 2 or more levels of quantization a minimum loss can be achieved for a particular choice of quantization threshold, table 2-3.

TABLE 2-2

Voltage transfer function for 3-bit quantizer

Uniform input and output quantization

| Input Voltage<br>(Vin) / Volts | Output | Index<br>k | Weight<br><sup>W</sup> k |

|--------------------------------|--------|------------|--------------------------|

| Vin > 3Vt                      | 3      | 4          | 3.5                      |

| 3Vt > Vin > 2Vt                | 2      | 3          | 2.5                      |

| 2Vt > Vin > Vt                 | 1      | 2          | 1.5                      |

| Vt > Vin > 0                   | 0      | 1          | 0.5                      |

| 0 > Vin > -Vt                  | -1     | -1         | -0.5                     |

| -2Vt > Vin > -2Vt              | -2     | -2         | -1.5                     |

| -3Vt > Vin > -3Vt              | -3     | -3         | -2.5                     |

| -4Vt > Vin                     | - 4    | -4         | -3.5                     |

| Quantization level/bits | Minimum<br>loss/dB | Maximum<br>loss/dB |

|-------------------------|--------------------|--------------------|

| 1                       | 1.98               | 1.98               |

| 3                       | 0.78<br>0.30       | 1.98<br>1.98       |

| 4                       | 0.09               | 1.98               |

This shows that a loss of only 2 dBs is incurred by the hard limiter based DMF, whereas a very good approximation to the ideal matched filter can be achieved with quantization of only 3 or 4 levels. The penalty of multibit quantization is increased DMF complexity and cost. Furthermore to obtain the minimum loss of table 2-2 the optimum quantization threshold must be known at the quantizer. This assumes that the input snr is known.

In general, during synchronization acquisition the received snr is unlikely to be known and the potential benefit of multibit quantization may not be realised in practise. For the single bit DMF the quantization loss is constant, and therefore independent of received snr. Figure 2-17 shows that the loss for multibit quantization at V =0 is identical to that for the hard-limiter, regardless of the number of quantization levels. This can be seen intuitively since as V, approaches 0 the width of the quantization interval approaches 0, and hence the probability of occupancy also approaches 0. Therefore the only significant contribution to the mean and variance of the quantizer output in (2-60) and (2-61) respectively is for k=+n or k=-n, and these values correspond to outputs from the most significant bit. Clearly this is equivalent to the hard-limiter case and accounts for the curves of figure 2-17 approaching 2 dBs as V, approaches 0. Similarly for low snrs it can be seen that as V, becomes large relative to  $V_{in}$  then contributions to the quantizer output mean and variance can only be due to the least significant bit, since this is the only likely level of occupancy. Again this approximates the hard-limiter case, and explains why the curves of figure 2-17 approach 2 dBs as V, becomes large relative to Vin.

In chapter 3 it is shown that the received snr can be measured by a complex baseband receiver based on single-bit DMFs. This could prove useful in a multibit DMF receiver where such information could be used to set up optimum quantization levels and hence allow the multilevel DMF to

operate under optimum conditions. In such a scheme the quantization threshold could be set to zero, allowing the DMF to operate in single bit mode. The received snr could then be measured, and the optimum quantization threshold determined from this. The DMF based on multibit quantization could then be operated under optimum conditions.

Finally from (2-60) we have for the hard-limiter

Mean(output) = 1

$$p(1) - 1 p(-1)$$

(2-62)

$$= 1 (1-p_e) - 1 (p_e)$$

$$= 1 - 2 p_{e}$$

(2-63)