## Novel Approaches to Power Efficient GaN and Negative Capacitance Devices

A thesis submitted for the degree of

Doctor of Philosophy

By:

Ashwani Kumar

December 2018

Department of Electronic and Electrical Engineering

The University of Sheffield

#### **Acknowledgement**

I would like to express my sincerest gratitude and appreciation to my supervisor, Prof. Maria Merlyne De Souza for everything, starting from offering me the opportunity to join her team, to her valuable guidance, support, and encouragement during the course of my doctoral research.

I would like to acknowledge ENIAC-JU project E2SG for funding the first year of my research. A special thanks to Ms. Sara Gawthorpe, Ms. Hilary Levesley, Ms. Frances G. Bright, Ms. Dianne Webster, Dr. Kevin Jackson, Dr. Nathan Porter, Mr. Fahmi Mohammad, and Ms. Kim Brechin who have helped me regarding the departmental formalities.

I want to thank the past and present members of our team: Premlal Pillai, Mirza Rasheduzzaman, Asiel N. Corpus-Mendoza, Nagaditya Poluri, and Xiaoyao Song for their support and a good company.

I wish to thank my property owners, Dr. Piya Gamage and Susila Gamage, and their friend Dr. Rohan Tittagala, who helped me with moving in and getting settled in Sheffield, and are one of the humblest and kindest persons I have met.

Finally, I am grateful to my mother Ms. Omwati and my late father Mr. Prathvi Singh, for their hardships and being a constant source of inspiration for me. My final thanks goes to my siblings for their inestimable support and continual encouragement over the years.

Ashwani Kumar

#### **List of Publications**

#### **Journals:**

- A. Kumar, P. B. Pillai, X. Song, and M. M. De Souza, "Negative Capacitance beyond ferroelectric switches," <u>ACS Applied Materials and Interfaces</u>, vol. 10, no. 23, pp. 19812–19819, May 2018.

- P. B. Pillai, A. Kumar, X. Song, and M. M. De Souza, "Diffusion-Controlled Faradaic Charge Storage in High-Performance Solid Electrolyte-Gated Zinc Oxide Thin-Film Transistors," <u>ACS Appl. Mater. Interfaces</u>, vol. 10, no. 11, pp. 9782–9791, Mar. 2018. DOI: 10.1021/ACSAMI.7B14768.

- 3. **A. Kumar** and M. M. De Souza, "Impact of channel thickness on the performance of an E-mode p-channel MOSHFET in GaN," *Appl. Phys. Lett.*, vol. 112, no. 15, pp. 153503-1–153503-4, Apr. 2018.

- H. Amano *et al.*, "The 2018 GaN power electronics roadmap," <u>J. Phys. D. Appl.</u>

<u>Phys.</u>, vol. 51, no. 16, pp. 163001-34–163001-35, Apr. 2018.

- 5. **A. Kumar** and M. M. De Souza, "Modelling the threshold voltage of p-channel enhancement-mode GaN heterostructure field-effect transistors," *IET Power Electron.*, vol. 11, no. 4, pp. 675–680, Apr. 2018.

- A. Kumar and M. M. De Souza, "An E-Mode p-Channel GaN MOSHFET for a CMOS Compatible PMIC," <u>IEEE Electron Device Lett.</u>, vol. 38, no. 10, pp. 1449– 1452, Oct. 2017.

#### **Conferences:**

1. J. Zhou, **A. Kumar**, and M. M. De Souza, "Influence of an underlying 2DEG on the performance of a p-channel MOSHFET in GaN," *International Workshop on Nitride Semiconductors* (IWN 2018), Kanazawa, Japan. Nov 2018.

- 2. **A. Kumar** and M. M. De Souza, "On the Dynamic characteristics of Ferroelectric and Paraelectric FETs," *Proc of the 2<sup>nd</sup> Electron Devices Technology and Manufacturing* (EDTM 2018), Kobe, Japan. Mar 2018 (Oral Presentation).

- 3. **A. Kumar** and M. M. De Souza, "Enhancement mode p-channel devices for GaN CMOS," *International Conference on Optimisation of Electrical & Electronic Equipment Aegean Conference on Electrical Machines* (OPTIM-ACEMP 2017), Brasov, Romania, May 2017.

- A. Kumar and M. M. De Souza, "Mechanism of Turn-Off Operation in E-mode pchannel MOSHFET in GaN," *UK Semiconductors* (UKS 2017), Sheffield, United Kingdom, July 2017 (Oral Presentations, Session G-O-8, 12 Jul 2017).

- 5. **A. Kumar** and M. M. De Souza, "Extending the bounds of performance in E-mode p-channel GaN MOSHFETs," *Proc of the 62<sup>nd</sup> International Electron Devices Meeting* (IEDM 2016), Dec. 2016, pp. 7.4.1-7.4.4.

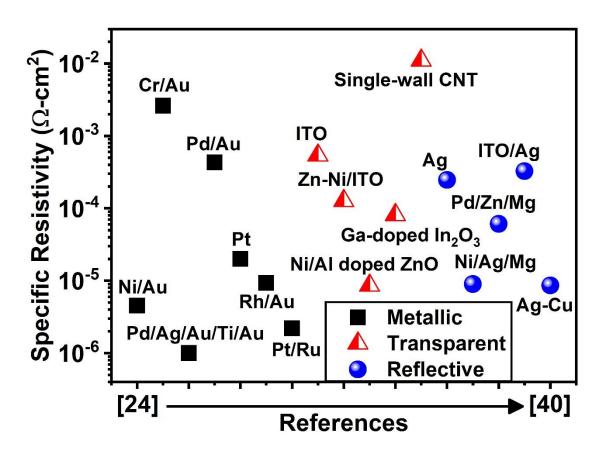

- A. Kumar, P. B. Pillai, and M. M. De Souza, "Comparative Characteristics of High Performance ZnO Thin Film Transistors," 6<sup>th</sup> International Symposium on Transparent Conductive Material (TCM 2016), Platanias-Crete, Greece, Oct 2016 (Oral Presentation, Session 14B, 13 Oct 2016).

- A. Kumar and M. M. De Souza, "Theoretical Modelling of 2DEG and 2DHG in III-Nitride based heterostructures" *Proc of the 13<sup>th</sup> International Seminar on Power Semiconductors* (ISPS 2016), Prague, Czech Republic, Sep 2016 (Poster Presentation, 1 Sep 2016).

- 8. **A. Kumar** and M. M. De Souza, "Theoretical modelling of 2DHG in Oxide/GaN/AlGaN/GaN heterostructures," *UK Semiconductors* (UKS 2016), Sheffield, United Kingdom, July 2016 (Poster Presentations, Session G-P-14, 6 Jul 2016).

#### **Abstract**

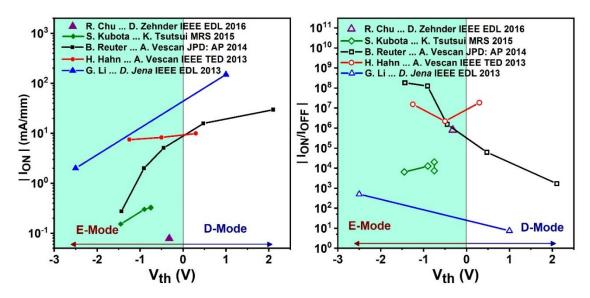

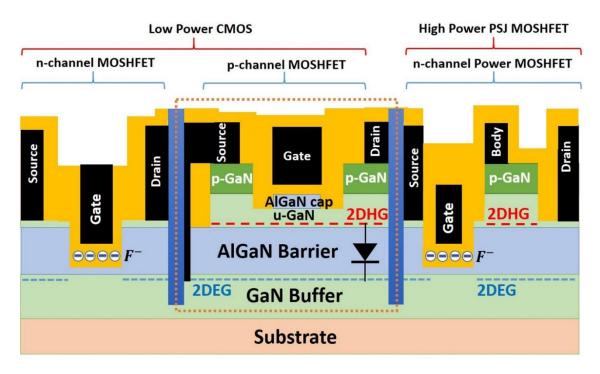

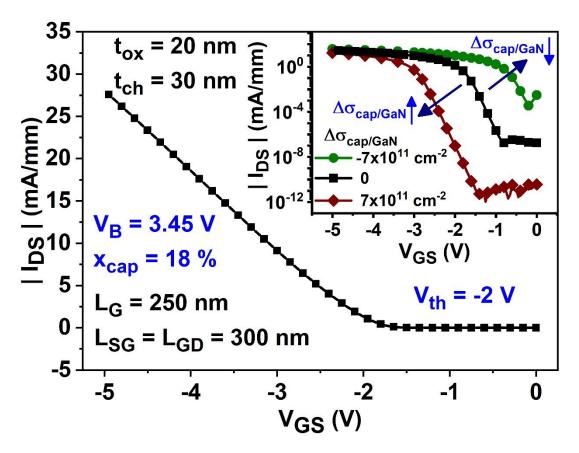

Recent emergence of data-driven and computation hungry algorithms has fuelled the demand for energy and processing power at an unprecedented rate. Semiconductor industry is, therefore, under constant pressure towards developing energy efficient devices. A Shift towards materials with higher figure-of-merit compared to Si, such as GaN for power conversion is one of the options currently being pursued. A minimisation in parasitic and static power losses in GaN can be brought about by realising on-chip CMOS based gate drivers for GaN power devices. At present, p-channel MOSHFETs in GaN show poor performance due to the low mobility and the severe trade-off between  $|I_{ON}|$  and  $|V_{th}|$ .

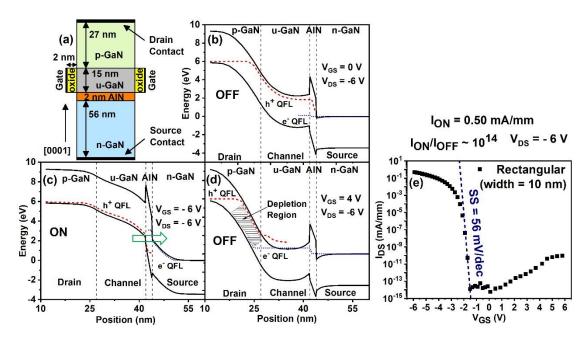

For the first time, it is shown that despite a poor hole mobility, it is possible to improve the on-current as well as minimise  $|I_{ON}|$  -  $|V_{th}|$  trade-off, by adopting a combination of techniques: using an AlGaN cap, biased two-dimensional electron gas, and shrinking source-gate and gate-drain access region and channel lengths. As part of this work, a novel vertical p-channel heterojunction tunnel FET (TFET) utilising polarisation induced tunnel junction (PITJ) is also explored, which unlike common TFETs, shows non-ambipolar transfer characteristics and a better electrostatic control over the tunneling region via the gate.

Meeting the ever-increasing demand for computation would require continuous scaling of transistor physical dimensions and supply voltage. While a further reduction in physical dimension is expected to come from adopting a vertical integration scheme, scaling in supply voltage would require achieving sub-60 mV/dec of subthreshold swing. The two common approaches to achieve this are TFETs and negative capacitance

(NC) FETs, where the NC operation is commonly associated with ferroelectric materials.

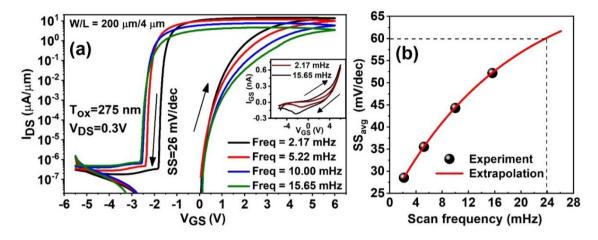

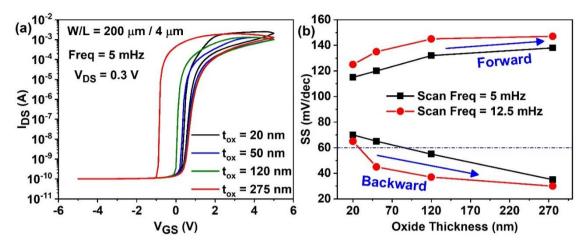

This work develops a model to explain sub-60 mV/dec, observed in  $Ta_2O_5/ZnO$  thin-film-transistors, which is governed by the motion of oxygen ions inside  $Ta_2O_5$ , leading to NC under dynamic gate bias sweep.

### **Table of Contents**

| Chapter 1 Introduction                                              | 1  |

|---------------------------------------------------------------------|----|

| 1.1. Overview                                                       | 1  |

| 1.2. Making Power Conversion Energy Efficient                       | 1  |

| 1.3. Satisfying Growing Demand for Computation                      | 5  |

| 1.3.1. Achieving subthreshold swing below <b>60</b> <i>mV/dec</i>   | 6  |

| 1.3.2. Beyond Von Neumann Architecture                              | 8  |

| 1.4. Objective of This Work                                         | 11 |

| 1.5. Outline of the Thesis                                          | 11 |

| 1.6. References                                                     | 13 |

| Chapter 2 MOSFET and Steep-Switching Devices                        | 16 |

| 2.1. Operation of A Metal-Oxide-Semiconductor (MOS) FET             | 16 |

| 2.1.1. Body Factor of a MOS                                         | 17 |

| 2.1.2. Boltzmann Limit and Subthreshold Operation of a MOSFET       | 19 |

| 2.2. Sub-60 mV/dec Switching, Body Factor, and Negative Capacitance | 21 |

| 2.3. Operation of a TFET                                            | 23 |

| 2.4. Physics of Ferroelectric Materials                             | 25 |

| 2.4.1. Equivalent Series R-C Circuit Model                          | 29 |

| 2.5. Operation of a FE-FET                                          | 30 |

| 2.6. Operation of a PE-FET                                          | 33 |

| 2.7. Summary                                                        | 34 |

| 2.8. Reference                                                        | 35     |

|-----------------------------------------------------------------------|--------|

| Chapter 3 Fundamentals of GaN and Heterostructure Devices             | 38     |

| 3.1. Why GaN?                                                         | 38     |

| 3.2. Polarisation and Polarisation Sheet Charge                       | 39     |

| 3.3. Polarisation Effects in AlN/GaN and Their Alloys                 | 40     |

| 3.4. Polarisation Induced Two Dimensional Carrier Gases               | 44     |

| 3.5. Operation of MOS in GaN Heterostructures                         | 47     |

| 3.5.1. Threshold Voltage Expression and C-V Characteristics           | 48     |

| 3.6. Achieving Normally-Off Operation in n-channel MOSHFET            | 50     |

| 3.7. Summary                                                          | 52     |

| 3.8. Reference                                                        | 52     |

| Chapter 4 Modelling the Threshold Voltage for p-channel E-mode GaN HF | ETs.57 |

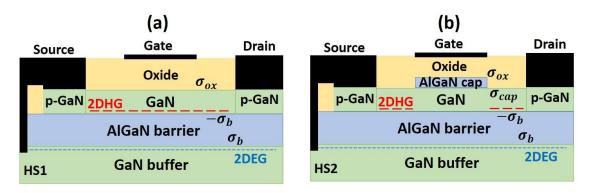

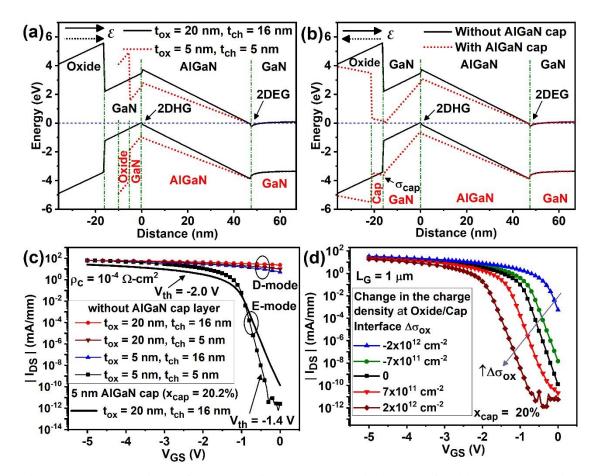

| 4.1. Simulation Model and Heterostructures                            | 59     |

| 4.2. Derivation of Threshold Voltage Expression                       | 65     |

| 4.2.1. Conventional Heterostructure                                   | 65     |

| 4.2.2. Alternate Heterostructure with an AlGaN Cap                    | 67     |

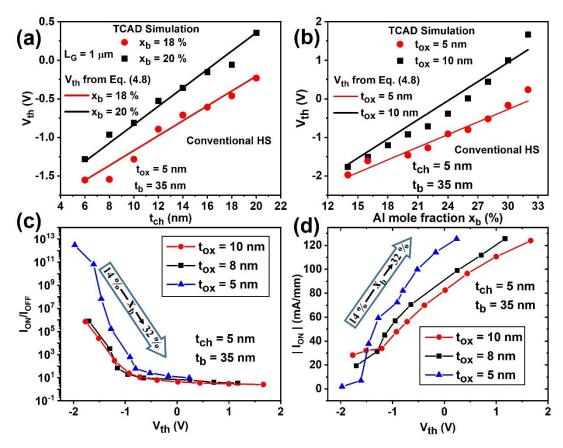

| 4.3. Analysis of the Conventional Heterostructure p-Channel MOSHFET   | 69     |

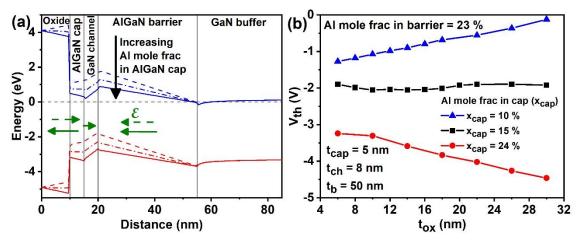

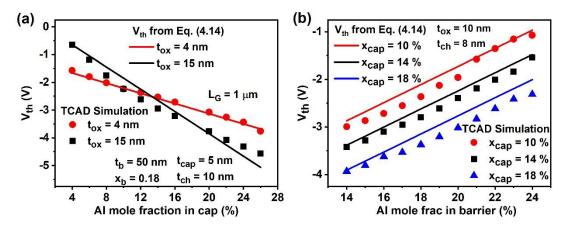

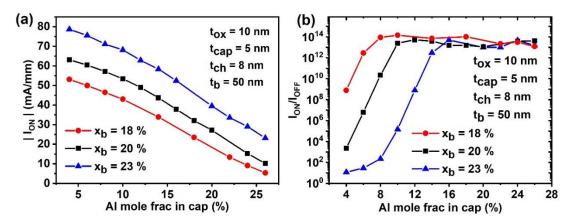

| 4.4. Analysis of the Alternate Heterostructure p-Channel MOSHFET      | 74     |

| 4.5. Summary                                                          | 82     |

| 4.6. References                                                       | 83     |

| Chapter 5 An E-Mode P-Channel GaN MOSHFET for a CMOS Compatible       | e PMIC |

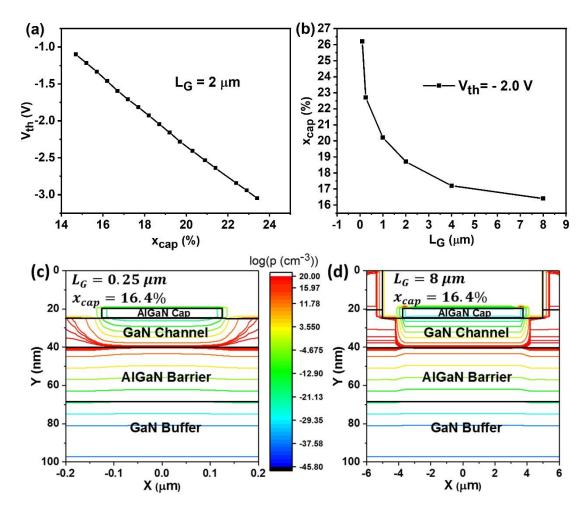

|                                                                       |        |

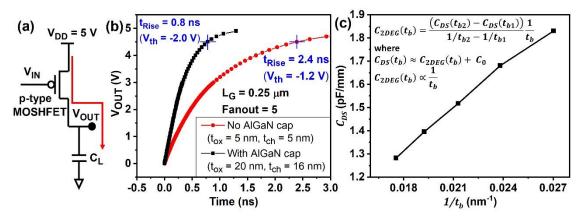

| 5.1. Introduction                                                | 88            |

|------------------------------------------------------------------|---------------|

| 5.2. Methodology and Settings                                    | 91            |

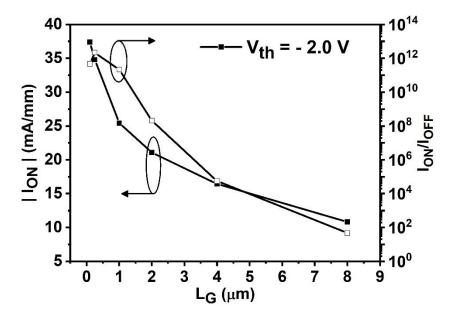

| 5.3. Impact of Gate Length on Performance                        | 91            |

| 5.4. Impact of Channel Thickness on the Performance of an E-Mo   | ode p-Channel |

| MOSHFET in GaN                                                   | 98            |

| 5.5. Summary                                                     | 103           |

| 5.6. References                                                  | 104           |

| Chapter 6 A Non-ambipolar p-channel GaN Heterostructure Tunnel I | ET with high  |

| on/off ratio                                                     | 108           |

| 6.1. Introduction                                                | 108           |

| 6.2. Modelling Tunneling Transport                               | 110           |

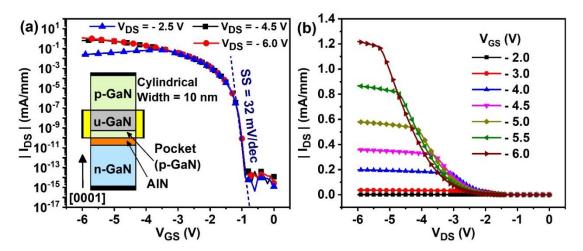

| 6.3. Non-ambipolar Operation of P-Channel GaN HTFET              | 112           |

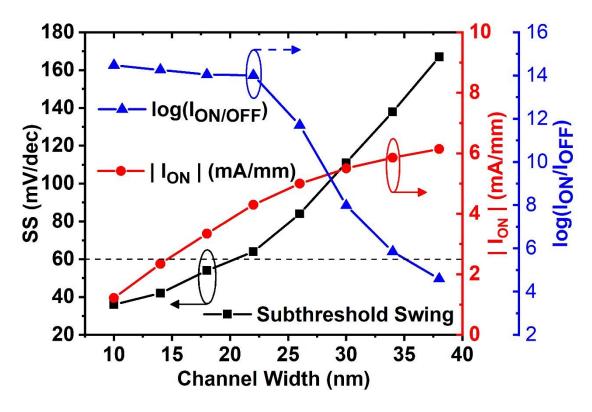

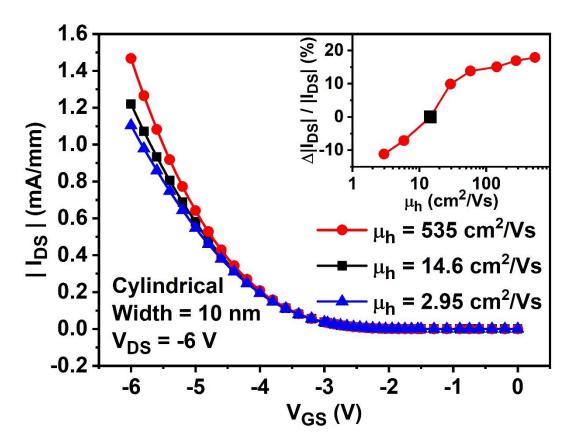

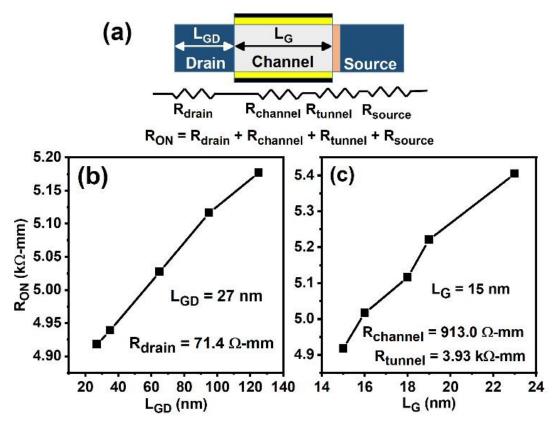

| 6.4. Optimised Cylindrical P-Channel GaN HTFET                   | 114           |

| 6.5. Analysis of Tunnel Distance                                 | 118           |

| 6.6. Summary                                                     | 120           |

| 6.7. References                                                  | 121           |

| Chapter 7 Negative Capacitance beyond Ferroelectric Switches     | 125           |

| 7.1. Introduction                                                | 125           |

| 7.2. Results                                                     | 129           |

| 7.3. Summary                                                     | 144           |

| 7.4. References                                                  | 146           |

| Chapter 8 Conclusions and Future Work                            | 151           |

| Aj | ppendix                 | 155 |

|----|-------------------------|-----|

|    | 8.2. Future Work        | 152 |

|    | 8.1. Concluding Remarks | 151 |

#### **Chapter 1 Introduction**

#### 1.1. OVERVIEW

The international demand for energy is on a constant rise. This is in part due to the staggering growth of economy in developing nations such as India, China, and in Africa that is resulting in expansion of industrial, transportation, commercial sectors and human consumption. A recent explosion in data-driven and compute-hungry techniques, such as deep learning and cryptocurrency mining constitutes another major part of higher demand for energy. The aggregate energy consumption in mining bitcoins, a form of cryptocurrency, is currently at a whopping 73 TWh, surpassing the energy consumption of entire countries such as Czech Republic or Austria [1]. Owing to an increasing demand for data-driven services, energy consumption of data centres in U.S. alone is estimated to be 73 PWh by 2020 according to Lawrence Berkeley National Laboratory [2], thereby underscoring the urgent need for efficient energy systems.

#### 1.2. Making Power Conversion Energy Efficient

Owing to a well-established manufacturing base, various forms of power converters, AC/AC, AC/DC, DC/AC, or DC/DC, have traditionally relied upon silicon as the basic semiconductor for power devices. However, it is apparent that more efficient semiconductors are required for sustainable development of society. Table 1.1 highlights the electronics and thermal properties along with different figure-of-merits (FOMs) of some of the promising semiconductor materials for power applications.

Table 1.1. Electronic properties of different materials, data obtained from [3]–[6], hole mobility values for GaN in bulk and 2DHG are from [7], [8], and FOM parameters are from [9], [10], respectively.

| Parameters                                      | Description                  | Si                   | 4H-SiC               | GaN                        | Diamond               |

|-------------------------------------------------|------------------------------|----------------------|----------------------|----------------------------|-----------------------|

| $\varepsilon_r$                                 | Dielectric coefficient       | 11.7                 | 9                    | 10                         | 5.5                   |

| $E_G(eV)$                                       | Band gap                     | 1.1                  | 3.26                 | 3.39                       | 5.45                  |

| $n_i (cm^{-3})$                                 | Intrinsic carrier density    | $1.5 \times 10^{10}$ | $8.2 \times 10^{-9}$ | $1.9\times10^{-10}$        | $1.6 \times 10^{-27}$ |

| $v_{sat} (10^7  cm/s)$                          | Electron saturation velocity | 1                    | 2                    | 2.5                        | 2.7                   |

| $\mu_n$ (cm <sup>2</sup> /Vs)                   | Electron mobility            | 1350                 | 900                  | 1200 (Bulk)<br>2000 (2DEG) | 2200                  |

| $\mu_p  (\mathrm{cm^2/Vs})$                     | Hole mobility                | 450                  | 50                   | 81 (Bulk)<br>43 (2DHG)     | 1600                  |

| $\mathcal{E}_{br}(MV/cm)$                       | Breakdown electric field     | 0.3                  | 2.0                  | 3.3                        | 5.6                   |

| $\lambda(W/cmK)$                                | Thermal conductivity         | 1.5                  | 4.5                  | 1.3                        | 20                    |

| BFOM $(\varepsilon_r \mu_n \mathcal{E}_{br}^3)$ | Baliga's FOM                 | 1                    | 500                  | 2414                       | 8964                  |

| HMFOM $(\sqrt{\mu_n}\mathcal{E}_{br})$          | Huang's materials FOM        | 1                    | 8                    | 15                         | 28                    |

Both the FOMs in the above table have been normalised with respect to Si. Here BFOM is equivalent to the inverse of the conduction loss with specific area, therefore is relevant to those cases where the switching loss is dominated by conduction loss. Whereas HMFOM, which is the inverse of total loss, also includes the switching losses during charging and discharging of the input capacitance of the power transistor.

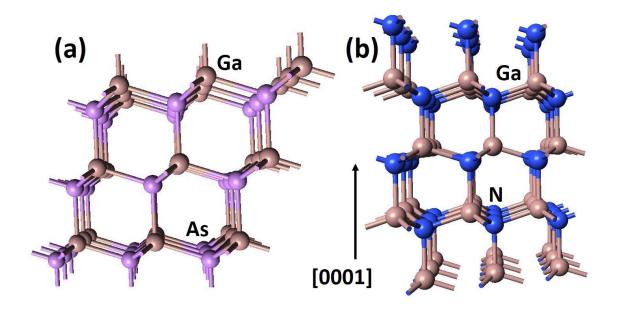

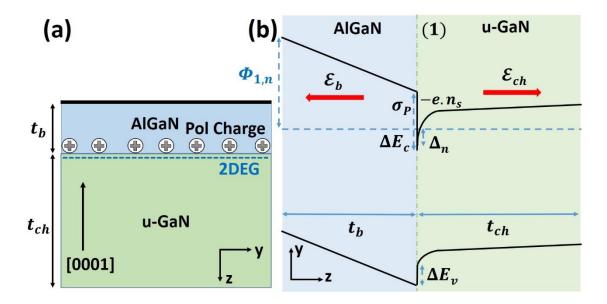

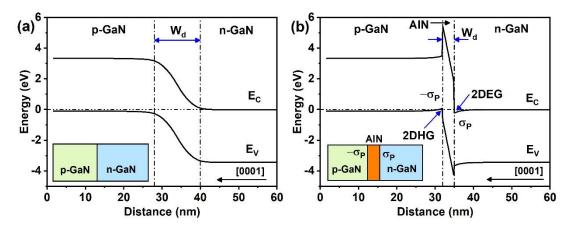

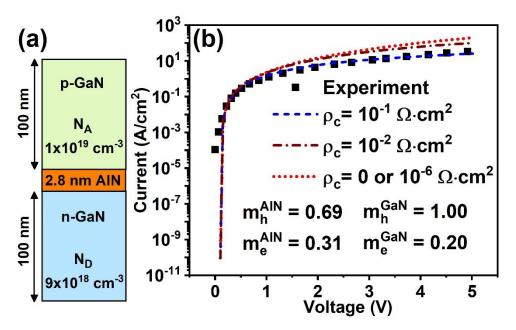

Among the materials listed in Table 1.1, GaN is particularly unique, because of its polarisation properties that lead to formation of two-dimensional electron and hole gases (2DEG and 2DHG) with high sheet density  $\sim 10^{13}~cm^{-3}$  without applying any external bias. In addition, despite having a bulk electron mobility smaller than Si, the 2DEG in GaN exhibits an electron mobility of  $2000~cm^2/Vs$ ,  $\sim 50$  % higher compared to Si. As observed by M. Shur *et al.* [11] in their theoretical analysis, a better suppression of the piezoelectric scattering, resulting from a high concentration of electron gas and a reduction of ionized impurity scattering in the absence of doping are responsible for the high mobility of the 2DEG. Mobility is therefore primarily limited by polar optical

phonon scattering. On the other hand, such a theoretical study of hole mobility of 2DHG in GaN is still non-existent. The values listed in Table 1.1 for the hole mobility in bulk and 2DHG are the best experimental values observed to date. As a result of this highly conducting 2DEG along with higher breakdown electric field and saturation velocity means that GaN devices can operate at higher voltages and frequency at a fraction of the size of silicon power devices.

In high frequency power conversion, increasing the frequency reduces the size and volume of various other circuit elements in the system, such as transformers, filters and inductors. This helps to reduce the weight, bill of materials and thereby the cost of power systems. Increasing the frequency of operation in power MOSFETs, however leads to a rise in switching loss, as

$$Loss \propto \frac{\sqrt{f}}{FOM} \tag{1.1}$$

Since FOM remains fixed for a given material, Eq. (1.1) indicates a material with higher FOM becomes necessary to suppress the increase in loss as the frequency of operation becomes higher.

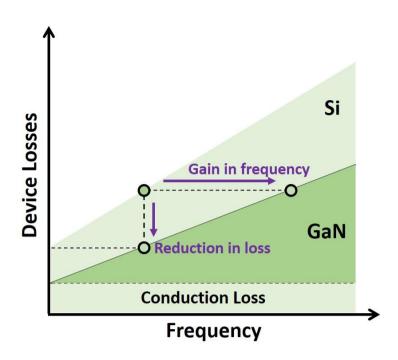

Fig. 1.1 elucidates device losses in Si and GaN with respect to frequency. Owing to the much higher BFOM in GaN compared to Si, GaN based devices facilitate smaller conduction losses. Moreover, the rise in device loss with frequency occurs at a smaller rate in GaN than Si, owing to a higher HMFOM. This makes GaN devices inherently advantageous in efficiency despite the higher frequency in comparison to silicon as indicated in this figure.

Fig. 1.1. Comparison of device losses, conduction and switching losses, for GaN and Si.

Table 1.1 also shows that the material properties and FOM of diamond far exceed the properties of Si or GaN. However, owing to economic reasons and difficulty in achieving n-type doping in diamond, the commercialisation of diamond based power devices is not expected any time soon.

One downside of GaN power devices is that currently the gates of these devices are driven by Si based CMOS, located discretely, though more recently GaN ICs based on n-type logic gate drivers have also come into the market [12]. This lack of integrated CMOS gate driver introduces chip-to-chip delay and parasitic inductance to the gate drive loop, resulting in slow operation with higher loss and instability. A further improvement is required by integrating power device and CMOS based gate driver on the common GaN chip to harness the full material benefits of GaN.

However, the mobility of holes in GaN remains poor,  $7.8 - 81 \, cm^2/Vs$  in bulk [7] and  $10 - 43 \, cm^2/Vs$  for 2DHG [8] at room temperature, which severely degrades the performance of monolithic CMOS in GaN [13], thereby prohibiting applications of GaN based logic and CMOS for driving power converters. Novel solutions are therefore

required to improve hole mobility or realise a p-channel device with a higher hole mobility material heterogeneously integrated with GaN.

#### 1.3. SATISFYING GROWING DEMAND FOR COMPUTATION

Besides electrical power conversion in all its forms, a large fraction of energy consumption accrues from the demand for computation. This has historically been made possible by Moore's law, which states that the number of transistors on an integrated chip doubles approximately every 2 years [14]. Moore's law has served both as a motivation and guide for semiconductor industry in setting targets for the next generation of transistors. As a result, the size of the transistors became smaller, which led to an increase in their performance, whilst reducing the cost of manufacture.

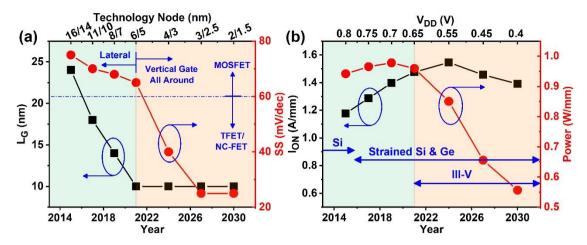

The targets for feature size along with other physical and electrical characteristics for each of the technology nodes are dictated by the International Technology Roadmap for Semiconductors (ITRS), which has successfully predicted the evolution of transistor properties over the few decades. Figs. 1.2 (a) and (b) show the forecast for physical gate length  $L_G$ , subthreshold swing (SS), the on-current  $I_{ON}$ , and maximum power consumption (supply voltage  $V_{DD} \times I_{ON}$ ), for each technology node up to 2030, according to ITRS Executive Reports, 2015 [15]. By the year 2021,  $L_G$  is expected to shrink to 10 nm, at which point, a further scaling in  $L_G$  will not be possible until the next decade due to adverse short-channel effects and higher channel leakage current. A further scaling of physical dimension is expected to come from adopting a vertical gate all around device structure.

Fig. 1.2. Targets for the (a) gate length, sub-threshold slope, (b) on-current and power over the next decade, as predicted by ITRS 2.0, Executive Summary 2015 [15].

Despite a higher on-current, a reduction in power is expected due to scaling of supply voltage and a reduction in subthreshold swing. After year 2021, two important technological shifts become necessary for ensuring high performance even at lower  $V_{DD}$ :

- Employing tunneling or negative capacitance phenomena to bring SS below

mV/dec

- 2. Realising beyond von Neumann architectures at hardware level

#### 1.3.1. Achieving subthreshold swing below 60 mV/dec

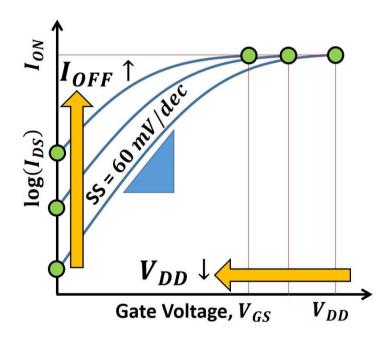

In a conventional MOSFET, due to Boltzmann distribution of carriers, a change in the carrier density in a semiconductor channel is limited to  $\sim \exp(q\Psi_s/kT)$  with respect to the surface potential  $\Psi_s$ , which results in a drain current unable to change by more than an order of magnitude for a change in surface potential by 60~mV. This implies that for a given  $I_{ON}$  and at a fixed SS, a reduction in the supply voltage comes at a cost of a higher off-current  $I_{OFF}$ , leading to an off-state power consumption, as shown in Fig. 1.3. Therefore, reducing SS beyond this limit of 60~mV/dec in conventional MOSFET becomes crucial for the continued scaling of supply voltage and power consumption. Tunnel FETs (TFETs), where the transport of carriers between source and drain is enabled by quantum mechanical band-to-band tunneling over a potential barrier, have

been demonstrated to overcome this limit. Nevertheless, the performance of these transistors has been historically poorer than their CMOS counterparts [16], which is due to tunneling that introduces additional series resistance in the source and drain path. To date, the best reported electrical characteristics have been achieved in a vertical nanowire InAs/GaAsSb/GaSb TFET, showing an on-current of 0.31 *mA/mm* at 60 *mV/dec* of SS [17]. In addition to poor on-current, TFETs also suffer from ambipolarity, which refers to their inability to remain in off-state for one of the polarities of the applied gate bias, further restricting their applicability in complementary logic [18].

Fig. 1.3. Schematic of transfer characteristics for a MOSFET showing that scaling of the supply voltage causes the off-current to become higher.

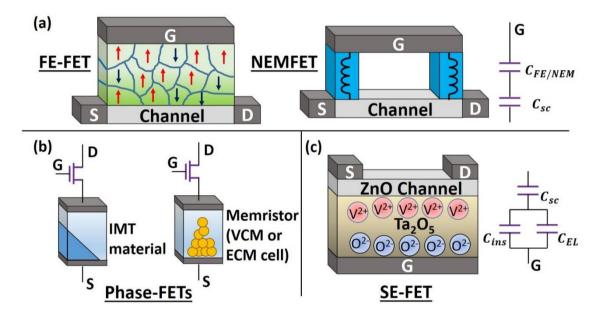

Ferroelectric FETs (FE-FETs) and other negative-capacitance FETs provide an alternative approach to lower SS below 60 mV/dec. In these FETs, the gate dielectric in the transistor is replaced by a material with inherent instability, i.e. exhibiting a two-valley energy profile rather than a parabolic energy profile, observed in ordinary dielectric. Owing to this instability, the resulting insulator capacitance becomes negative for a range of applied gate bias. This produces an amplification in the potential at the

surface of the semiconductor relative to the applied gate bias, leading to steeper draincurrent characteristics

#### 1.3.2. Beyond Von Neumann Architecture

The von Neumann framework, where the memory and processing units are physically separated from each other, has been the underlying architecture behind contemporary high level programming languages, where variables in the program represent memory locations, algebraic and logical operations describe a single or a set of instructions to be performed by the processing unit, control statements mimic jump instructions, and assignment statements are a representation of fetch and store operations. Despite its prevalent use, this architecture has many limitations, such as information is processed sequentially, the speed at which any logic or algebraic operation can be performed remains limited to the maximum speed at which the data can be transferred between memory and processing units, which also leads to a significant loss of power in data transfer, where a small operation needs to be performed over a large amount of data. The time delay caused by data transfer between the memory and processor introduces a bottleneck on the maximum speed in this architecture referred to as memory wall [19].

Many avenues have been proposed and developed to surpass the limitations of von Neumann computing. Fig. 1.4 shows a chart of approaches based upon how information is processed, as reported by IRTS in [20]. These can be broadly divided into "Program-Centric" and "Data-Centric", which can be further decomposed depending upon whether the outcome of a calculation is deterministic or non-deterministic. "Program-Centric" refers to the processors which take a program as an input, which contains a set of instructions provided by a designer and execute these instruction on the available input to generate an output. As shown, a Program-Centric framework can be sub-divided into von Neumann architecture, where instructions are executed from a stored program in a

sequential order, and non-von Neumann architectures, where instructions can be executed in parallel, for instance in field-programmable gate array (FPGA) or the same device is utilised to carry out both processing and storage, such as in a memristor [21], which exhibits a state dependent resistance.

| Program-Centric (performance and components dictated by designer) |                   |                                                                                                                                                                                               | Data-Centric (performance and/or components influenced by the data that is passed through the system)              |                                                                                                                                                                                                     |  |  |  |

|-------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| -                                                                 | Von Neumann Nor   |                                                                                                                                                                                               |                                                                                                                    | n-Von Neumann                                                                                                                                                                                       |  |  |  |

| Memor                                                             | y Processor       | Non-VN Processor<br>(including less-than-reliable VN)                                                                                                                                         | Trained off-line                                                                                                   | Trained in-line                                                                                                                                                                                     |  |  |  |

| CMOS Non-                                                         | CMOS CMOS Non-CMO | S CMOS Non-CMOS                                                                                                                                                                               | CMOS Non-CMOS                                                                                                      | CMOS Non-CMOS                                                                                                                                                                                       |  |  |  |

| SRAM  DRAM  DRAM  Flash  TCAM  NV  cross for S-: M-S              | bars<br>SCM,      | Active FPGA Interconnect  Coarse-Grained Reconfigurable Architectures  Analog oscillators computing  Accelerators (multimedia, etc.)  Probabilistic computing  Quantum computing  Approximate | Execution of pre-trained ANN True Ohmic North Weave  Associative computing  ML Accelerators (Convolution, SVM, ML) | Analog computing (w/ Flash)  New learning algorithms (unsupervised, reinforcement)  HTM  Crossbars for STDP  Supervised ANN learning  Crossbars for backprop  Probabilistic Learning  Bayesian  RBM |  |  |  |

Fig. 1.4. Different categories for computing architecture, as published by ITRS in [20].

On the other hand, a Data-Centric approach, also a non-von Neumann computing framework, uses available input data to learn and extract meaningful features that have proven to be useful in performing a variety of tasks, such as summarising news or reports, categorising documents, recognising objects in an image, performing semantic analysis, processing natural language or recognising speech, and generating responses. Brain inspired artificial neural networks (ANN) [22] have recently surpassed the limitation of other traditional approaches based on either von Neumann or non-von Neumann architectures. Deep neural networks with multiple stacked layers of neurons have

recently achieved significant improvements in the accuracy in these tasks, matching or even outperforming human-level accuracy in some of the complex world problems such as image and speech recognition [23], [24], autonomous driving [25], and medical diagnosis [26]. Further improvements in the accuracy, in deep networks require aggressively increasing the depth and size of these networks, demonstrating a need for ever-increasing computational capacity and large volume of memory required to store the analogue strength (weights) of a synapse connecting the neurons.

In the state-of-the-art deep networks, the number of weight parameters are usually of the order of millions [27], However, Si based CMOS implementation of ANNs with SRAM as the synaptic memory places a severe limitation on the maximum available on-chip memory. Moreover, this approach also consumes a large amount of power due to the continuous data transfer between memory and processing units during the operation.

In an alternative hardware platform, non-volatile memory (NVM) with analog or multi-state memory capabilities have been proposed for providing weight storage [28]. NVM typically consists of a memristor, realised using different approaches such as: phase change materials [29], formation/rupture of a conducting filament/bridge [30], magnetic tunnel junction [31], ferroelectric materials [32] or ferroelectric tunnel junction [33]. Compared to six-transistor (6T) cell in a typical SRAM, the one-transistor-one-resistor (1T1R) cell in NVM permits realisation of potentially higher density memory storage, removing the need for off-chip memory to store large number of weights. Currently, the research in this area has focused upon realising networks of synaptic devices, with connectivity and power consumption equivalent of a human brain, which consists of  $10^{10}$  synapses yet only consumes  $\sim 10 W$  [34]. The following section introduces the fundamentals of such neural networks and discusses one of the widely used learning algorithms to train these networks.

#### 1.4. OBJECTIVE OF THIS WORK

The focus of this work is two-fold. First, assessing the limits of performance of a p-channel device in GaN that is highly desired for the realisation of a complementary switch in GaN that can provide an integrated gate drivers for GaN power devices. Here we explore GaN heterostructures based lateral FET and a vertical tunnel FET, employing a polarisation induced tunnel junction. The second major contribution focuses on new physics of negative capacitance, beyond ferroelectric FETs. This is demonstrated by developing novel theory that explains steep switching in solid-electrolyte  $Ta_2O_5/ZnO$  thin-film transistors (TFTs), as part of this work.

#### 1.5. OUTLINE OF THE THESIS

The thesis is organised as follows:

In this Chapter 1 the need for energy-efficient devices and a growing demand for processing speed is introduced. Currently available solutions to meet these demands beyond 2021 are discussed. Finally, the role of this work in addressing these challenges is presented.

In the introductory Chapters 2 and 3, the operation of MOSFET and various techniques to overcome the 60 *mV/dec* limit of SS, via band-to-band tunneling, negative capacitance, are presented to provide the reader a background on the theory of Tunnel FETs and negative capacitance FETs. In Chapter 3, the physics of GaN, operation of metal-oxide-semiconductor (MOS) in GaN heterostructures, and approaches to realise normally-off operation in n-channel GaN heterostructure devices are discussed.

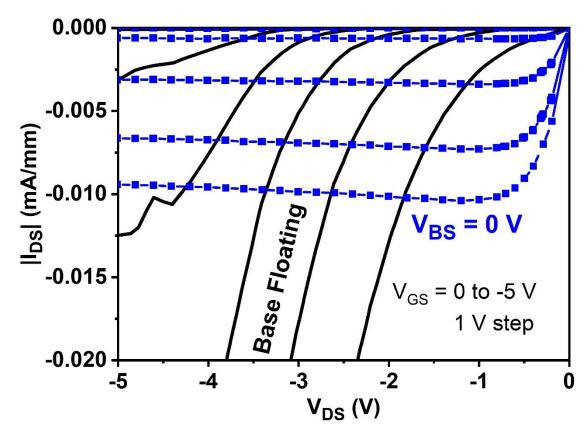

In Chapters 4 and 5 the limitations of conventional p-channel enhancement mode (E-mode) GaN MOS heterostructure FET (MOSHFET) are discussed. A modified p-channel device with an AlGaN cap for overcoming and extending the performance of these

devices is proposed. It is revealed in Chapter 4 that the device with the AlGaN cap suffers from higher leakage current as the thickness of the channel increases. Utilisation of a biased 2DEG along with an AlGaN cap is demonstrated to resolve this issue.

Chapter 6 introduces a novel p-channel vertical TFET in GaN that relies upon polarisation properties of GaN for its tunneling operation. From TCAD simulations, it is shown that this device, unlike conventional TFETs, does not suffer from ambipolarity in the transfer characteristics. The presented device also shows promise for achieving a much smaller tunnel distance with a better control than is possible in conventional TFETs.

In Chapter 7, a novel physics based model that explains sub-60 mV/dec of switching in a  $Ta_2O_5/ZnO$  solid-electrolyte FET is developed. It is shown that the motion of mobile oxygen ions inside  $Ta_2O_5$  ions under a dynamic gate bias sweep causes the capacitance across  $Ta_2O_5$  to become negative, leading to sub-60 mV/dec of switching.

In Chapter 8, concluding remarks are presented and future directions for this work are discussed.

#### 1.6. REFERENCES

- [1] "Bitcoin Energy Consumption Index Digiconomist." [Online]. Available: https://digiconomist.net/bitcoin-energy-consumption. [Accessed: 01-Dec. 2018].

- [2] A. Shehabi, S. J. Smith, N. Horner, I. Azevedo, R. Brown, J. Koomey, E. Masanet, D. Sartor, M. Herrlin, and W. Lintner, "United States Data Center Energy Usage Report," 2016.

- [3] U. K. Mishra, Shen Likun, T. E. Kazior, and Yi-Feng Wu, "GaN-Based RF Power Devices and Amplifiers," *Proc. IEEE*, vol. 96, no. 2, pp. 287–305, Feb. 2008. DOI: 10.1109/JPROC.2007.911060.

- [4] M. S. Shur, *Handbook Series on Semiconductor Parameters Volume 1*. 1996. DOI: 10.1142/2046-VOL1.

- [5] C. Claeys and E. Simoen, *Germanium-Based Technologies*. 2007. DOI: 10.1016/B978-0-08-044953-1.X5000-5.

- [6] A. Elasser and T. P. Chow, "Silicon carbide benefits and advantages for power electronics circuits and systems," *Proc. IEEE*, vol. 90, no. 6, pp. 969–986, Jun. 2002. DOI: 10.1109/JPROC.2002.1021562.

- [7] M. Zhong, J. Roberts, W. Kong, A. S. Brown, and A. J. Steckl, "p-type GaN grown by phase shift epitaxy," *Appl. Phys. Lett.*, vol. 104, no. 1, p. 012108, Jan. 2014. DOI: 10.1063/1.4861058.

- [8] B. Reuters, H. Hahn, A. Pooth, B. Holländer, U. Breuer, M. Heuken, H. Kalisch, and A. Vescan, "Fabrication of p-channel heterostructure field effect transistors with polarization-induced two-dimensional hole gases at metal–polar GaN/AlInGaN interfaces," *J. Phys. D. Appl. Phys.*, vol. 47, no. 17, p. 175103, Apr. 2014. DOI: 10.1088/0022-3727/47/17/175103.

- [9] N. Kaminski, "State of the art and the future of wide band-gap devices," in 2009 13th European Conference on Power Electronics and Applications, Sep. 2009.

- [10] A. Q. Huang, "New Unipolar Switching Power Device Figures of Merit," *IEEE Electron Device Lett.*, vol. 25, no. 5, pp. 298–301, May 2004. DOI: 10.1109/LED.2004.826533.

- [11] M. Shur, B. Gelmont, and M. Asif Khan, "Electron mobility in two-dimensional electron gas in AIGaN/GaN heterostructures and in bulk GaN," *J. Electron. Mater.*, vol. 25, no. 5, pp. 777–785, May 1996. DOI: 10.1007/BF02666636.

- [12] D. Kinzer, "GaNFast<sup>TM</sup> Power ICs Enable Breakthroughs in Adapter Performance," *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2018. [Online]. Available: https://www.navitassemi.com/wp-content/uploads/2015/03/APEC-2018-Ind-Session-Semiconductors-Dan-Kinzer-3-7-18.pdf. [Accessed: 10-Dec. 2018].

- [13] R. Chu, Y. Cao, M. Chen, R. Li, and D. Zehnder, "An Experimental Demonstration of

- GaN CMOS Technology," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 269–271, Mar. 2016. DOI: 10.1109/LED.2016.2515103.

- [14] G. E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, no. 8, pp. 114–117, 1965. DOI: 10.1109/JPROC.1998.658762.

- [15] International Technology Roadmap for Semiconductors (ITRS), "Executive Reports 2015," *ITRS*. [Online]. Available: http://www.itrs2.net/itrs-reports.html. [Accessed: 10-Dec. 2018].

- [16] H. Lu and A. Seabaugh, "Tunnel Field-Effect Transistors: State-of-the-Art," *IEEE J. Electron Devices Soc.*, vol. 2, no. 4, pp. 44–49, Jul. 2014. DOI: 10.1109/JEDS.2014.2326622.

- [17] E. Memisevic, J. Svensson, M. Hellenbrand, E. Lind, and L.-E. Wernersson, "Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/decade and Ion =  $10~\mu$ A/ $\mu$ m for Ioff = 1~nA/ $\mu$ m at Vds = 0.3~V," in 2016 IEEE International Electron Devices Meeting (IEDM), Dec. 2016, p. 19.1.1-19.1.4. DOI: 10.1109/IEDM.2016.7838450.

- [18] D. B. Abdi and M. J. Kumar, "Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain," *IEEE J. Electron Devices Soc.*, vol. 2, no. 6, pp. 187–190, 2014. DOI: 10.1109/JEDS.2014.2327626.

- [19] W. A. Wulf and S. A. McKee, "Hitting the memory wall: implications of the obvious," *ACM SIGARCH Comput. Archit. News*, vol. 23, no. 1, pp. 20–24, Mar. 1995. DOI: 10.1145/216585.216588.

- [20] International Technology Roadmap for Semiconductors (ITRS), "Beyond CMOS (Emerging Research Devices)," *ITRS*, 2015.

- [21] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 7191, pp. 80–83, May 2008. DOI: 10.1038/NATURE06932.

- [22] K. L. Priddy and P. E. Keller, *Artificial Neural Networks: An Introduction*. SPIE press, 2005.

- [23] O. Russakovsky, J. Deng, H. Su, J. Krause, S. Satheesh, S. Ma, Z. Huang, A. Karpathy, A. Khosla, M. Bernstein, A. C. Berg, and L. Fei-Fei, "ImageNet Large Scale Visual Recognition Challenge," *Int. J. Comput. Vis.*, vol. 115, no. 3, pp. 211–252, Dec. 2015. DOI: 10.1007/S11263-015-0816-Y.

- [24] W. Xiong, J. Droppo, X. Huang, F. Seide, M. Seltzer, A. Stolcke, D. Yu, and G. Zweig, "The microsoft 2016 conversational speech recognition system," in 2017 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Mar. 2017, pp. 5255–5259. DOI: 10.1109/ICASSP.2017.7953159.

- [25] C. Chen, A. Seff, A. Kornhauser, and J. Xiao, "DeepDriving: Learning Affordance for Direct Perception in Autonomous Driving," in 2015 IEEE International Conference on

- Computer Vision (ICCV), Dec. 2015, pp. 2722–2730. DOI: 10.1109/ICCV.2015.312.

- [26] A. Esteva, B. Kuprel, R. A. Novoa, J. Ko, S. M. Swetter, H. M. Blau, and S. Thrun, "Dermatologist-level classification of skin cancer with deep neural networks," *Nature*, vol. 542, no. 7639, pp. 115–118, Feb. 2017. DOI: 10.1038/NATURE21056.

- [27] G. Huang, Z. Liu, L. van der Maaten, and K. Q. Weinberger, "Densely Connected Convolutional Networks," in 2017 IEEE Conference on Computer Vision and Pattern Recognition (CVPR), Jul. 2017, pp. 2261–2269. DOI: 10.1109/CVPR.2017.243.

- [28] T. Chang, Y. Yang, and W. Lu, "Building neuromorphic circuits with memristive devices," *IEEE Circuits Syst. Mag.*, vol. 13, no. 2, pp. 56–73, 2013. DOI: 10.1109/MCAS.2013.2256260.

- [29] J. Lin, A. Annadi, S. Sonde, C. Chen, L. Stan, K. V. L. V Achari, S. Ramanathan, and S. Guha, "Low-Voltage Artificial Neuron using Feedback Engineered Insulator-to-Metal-Transition Devices," pp. 2–5, 2016.

- [30] S. Menzel, U. Bottger, M. Wimmer, and M. Salinga, "Physics of the Switching Kinetics in Resistive Memories," *Adv. Funct. Mater.*, vol. 25, no. 40, pp. 6306–6325, 2015. DOI: 10.1002/ADFM.201500825.

- [31] A. Jaiswal, A. Agrawal, and K. Roy, "In-situ, In-Memory Stateful Vector Logic Operations based on Voltage Controlled Magnetic Anisotropy," *Sci. Rep.*, vol. 8, no. 1, pp. 1–12, 2018. DOI: 10.1038/S41598-018-23886-2.

- [32] Z. Fan, J. Chen, and J. Wang, "Ferroelectric HfO2-based materials for next-generation ferroelectric memories," *J. Adv. Dielectr.*, vol. 06, no. 02, p. 1630003, Jun. 2016. DOI: 10.1142/S2010135X16300036.

- [33] A. Chanthbouala, V. Garcia, R. O. Cherifi, K. Bouzehouane, S. Fusil, X. Moya, S. Xavier, H. Yamada, C. Deranlot, N. D. Mathur, M. Bibes, A. Barthélémy, and J. Grollier, "A ferroelectric memristor," *Nat. Mater.*, vol. 11, no. 10, pp. 860–864, 2012. DOI: 10.1038/NMAT3415.

- [34] D. Kuzum, R. G. D. Jeyasingh, and H. S. P. Wong, "Energy efficient programming of nanoelectronic synaptic devices for large-scale implementation of associative and temporal sequence learning," *Tech. Dig. - Int. Electron Devices Meet. IEDM*, pp. 693– 696, 2011. DOI: 10.1109/IEDM.2011.6131643.

#### **Chapter 2 MOSFET and Steep-Switching Devices**

This introductory chapter is dedicated to device operation and evolution of the metal-oxide-semiconductor (MOS) field effect transistor (FET) that forms a basis of discussion in subsequent chapters. Sections 2.1 & 2.2 introduce the physics of operation of a MOSFET and conditions for achieving sub-60 mV/dec switching. This leads on to properties of steep-switching devices, Tunnel FET (TFET), Ferroelectric FET (FEFET), and Paraelectric FET (PE-FET) discussed in sections 2.3 – 2.6, which will serve as a basis for chapters 6 and 7. Finally, section 2.7 provides a summary of this chapter.

#### 2.1. OPERATION OF A METAL-OXIDE-SEMICONDUCTOR (MOS) FET

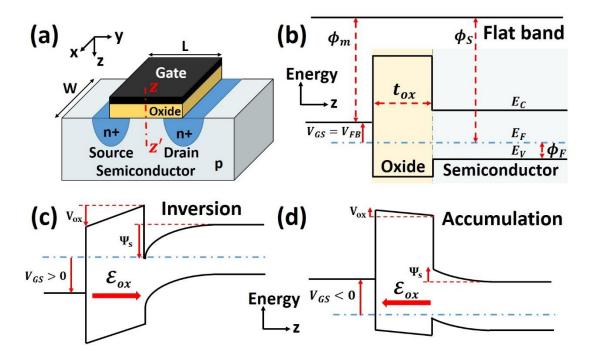

Fig. 2.1 (a) presents a schematic of a conventional n-channel MOSFET with a device width of W and channel or gate length L, fabricated on an acceptor-doped or p-type semiconductor. The two heavily donor-doped or n+-type regions define the source and drain, whereas the region in between forms the channel. Since the channel is p-type, it acts as a barrier between the n-doped source and drain. Hence applying a bias across drain and source  $V_{DS}$  does not produce a current through the device. An oxide separated gate is employed to electrostatically control the density of electrons within the channel. The band diagrams along the intercept Z - Z' are displayed in Figs. 2.1 (b)-(d) under various bias conditions of the gate. Fig. 2.1 (b) shows the band diagrams in flat band condition, where  $\phi_m$  and  $\phi_S$  indicate the work functions of metal and semiconductor, while  $\phi_F$  is the energy of the Fermi level with respect to the valence band of the semiconductor. In the flat band condition, the electric field within the oxide and semiconductor becomes zero. A gate bias  $V_{GS}$  equal to the difference of work functions  $\phi_m - \phi_S = \phi_{ms}$ , also referred as flat band voltage  $V_{FB} (= \phi_{ms})$ , is required to achieve this condition.

Fig. 2.1. (a) Schematic of an n-channel metal-oxide-semiconductor FET (MOSFET). The energy band diagrams along Z - Z' directions in (b) flat band, (c) inversion, and (d) accumulation conditions, respectively.

#### 2.1.1. Body Factor of a MOS

If a positive gate bias is applied, the energy of the Fermi level in the gate reduces by  $eV_{GS}$ , leading to a reduction in the energy of the conduction and valence bands in oxide and semiconductor, with part of the applied bias dropping across the oxide  $V_{ox}$  and the remaining as surface potential  $\Psi_S$  at the surface of the semiconductor, as shown in Fig. 2.1 (c). This can be expressed as

#### 2.1 (c). This can be expressed as

$$V_{GS} = \phi_{ms} + V_{ox} + \Psi_s \tag{2.1}$$

If a positive  $V_{GS}$  is applied such that the energy difference between the conduction band and Fermi level at the surface remains larger than  $\phi_F$ , the energy difference between the valence band and Fermi level under flat band condition (see Fig. 2.1 (b)), the carriers in the channel remain depleted. This corresponds to the depletion condition.

To determine the change in gate bias required to produce a unit change in the surface potential  $(dV_{GS}/d\Psi_S)$ , also referred as body factor m, we differentiate both side of Eq.

(2.1) with respect to  $\Psi_s$

$$m = \frac{dV_{GS}}{d\Psi_{S}} = 1 + \frac{dV_{ox}}{d\Psi_{S}} = \frac{1}{1 - \frac{dV_{ox}}{dV_{GS}}}$$

(2.2)

Where  $d\phi_{ms}/d\Psi_s=0$  since  $\phi_{ms}$  is a constant. As seen from Figs. 2.1 (c) and (d), since for a regular gate oxide both  $V_{ox}$  and  $\Psi_s$  always change in the same direction,  $dV_{ox}/d\Psi_s$  in the above equation always remains >0, which leads to m>1, indicating that the change in  $\Psi_s$  remains smaller than that in the gate bias.

At a certain positive gate bias, the energy of the bands at the surface of the semiconductor drops such that the energy difference between the conduction band and Fermi level becomes less than  $\phi_F$ , causing this region to become n-type. Since the surface of the semiconductor transforms from p-type, consisting of holes, to an n-type with a layer of electrons, this condition is referred to as inversion. As shown in Fig. 2.1 (c), a further increase in positive gate bias leads to the conduction band at the surface of the semiconductor sinking below the Fermi level, which leads to the formation of an equantum well, resulting in a two-dimensional confinement of electrons. Since an equal but positive charge is also created at the gate, this makes the entire metal-oxide-semiconductor stack to act as a capacitor, referred as MOS capacitor.

At a certain positive gate bias, the conduction band at the surface of the semiconductor sinks below the Fermi level, causing the formation of an e- quantum well, leading to a two-dimensional confinement of electrons. Since the channel transforms from a p-type semiconductor, consisting of holes, to n-type with a sheet of electrons, this condition is referred to as inversion. Since an equal but positive charge is also created at the gate, this makes the entire metal-oxide-semiconductor stack to act as a capacitor, referred as MOS capacitor.

In inversion, the sheet of electrons at the channel interface forms an electrical path

between n+ doped source and drain, thereby switching the device in the on-state. At this point, an application of  $V_{DS}$  results in  $I_{DS}$ , depending upon the density of the carriers in the channel. On the other hand, an application of negative bias on the gate raises the energy of the valence band inside the channel, bringing it closer to Fermi level, as shown in Fig. 2.1 (d), which results in an accumulation of holes at the surface of the semiconductor. Since in this mode, the channel remains p or p+, it obstructs any flow of electrons between the n+-doped source and drain regions and the device continuous to remains in off-state. Further explanations on the physics of MOS can be found in textbooks [1], [2].

#### 2.1.2. Boltzmann Limit and Subthreshold Operation of a MOSFET

In the depletion and weak inversion conditions, since the electron concentration in the channel remains small, the carrier transport is dominated by the diffusion of electrons from source to drain region, which can be described as [2]

$$I_{DS} \propto -D_n \frac{dN}{dt} \propto \frac{N(0) - N(L_G)}{L_G}$$

(2.3)

Where  $D_n$  is the diffusion coefficient for the electrons, N(0) and  $N(L_G)$  are the sheet carrier densities at source and drain edges of the gate. N(0) can be shown to have an exponential dependence upon the surface potential at the semiconductor, as  $N(0) \propto \exp(q\Psi_s/k_BT)$ , where  $k_B$  is Boltzmann constant, T is the temperature, and q is the elementary charge, while  $N(L_G)$  is described as  $N(0)\exp(-qV_{DS}/k_BT)$ . Substituting the values for N(0) and  $N(L_G)$  in Eq. (2.3), yields

$$I_{DS} \propto \exp\left(\frac{q\Psi_s}{k_B T}\right) \left(1 - \exp\left(-\frac{qV_{DS}}{k_B T}\right)\right) \approx \exp\left(\frac{q\Psi_s}{k_B T}\right)$$

(2.4)

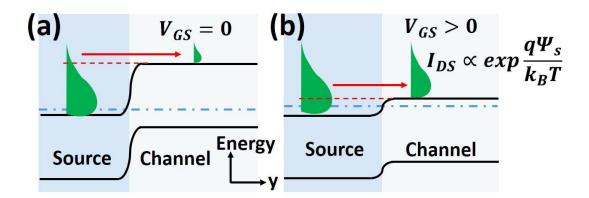

This exponential dependence upon the surface potential can also be interpreted from the band diagrams depicted in Figs. 2.2 (a) and (b) at zero and positive gate biases, respectively. At zero gate bias, the channel acts as a potential barrier for the carriers in the source region and prevents their diffusion across the channel, as indicated in Fig. 2.2 (a). However, as the gate bias is increased, a resulting increase in surface potential  $\Psi_s$  in the channel reduces the energy of conduction and valence bands in the channel (see Fig. 2.1 (c)), leading to a lowering of the barrier and a corresponding increase in the diffusion of the carriers, thus producing an exponential rise in the drain current, as shown in Fig. 2.2 (b).

Fig. 2.2. The band diagrams in source and channel regions of the semiconductor along the oxide/semiconductor interface for (a) zero and (b) positive gate bias.

Taking the logarithm of both sides of Eq. (2.4) and differentiating with respect to  $\Psi_s$ , yields

$$\frac{d\log_{10}I_{DS}}{d\Psi_{S}} \approx \frac{q}{2.3 k_{B}T} \tag{2.5}$$

Taking the reciprocal of the above equation

$$n = \frac{d\Psi_s}{d\log_{10}I_{DS}} \approx \frac{2.3 k_B T}{q}$$

(2.6)

where n, which is a measure of the change in  $\Psi_s$  required to produce a decade of change in  $I_{DS}$ , is defined as the transport factor. From the above equation, the transport factor is approximately equal to  $2.3 k_B T/q$ , referred to as the *Boltzmann limit*, indicating that at room temperature n cannot be smaller than  $60 \ mV/dec$ . This suggests that in the case of a thermionic emission a change of  $60 \ mV$  in  $\Psi_s$  is required to produce a decade

of change in the drain current.

From a knowledge of the body factor and transport factor, the subthreshold swing (SS), which is defined as the change in the gate bias required to produce a decade of change in the drain current,  $dV_{GS}/dlog_{10}I_{DS}$ , can be expressed as [3]

$$SS = \frac{dV_{GS}}{d\log_{10}I_{DS}} = \frac{dV_{GS}}{d\Psi_{S}} \frac{d\Psi_{S}}{d\log_{10}I_{DS}} = m \times n$$

(2.7)

As observed from Eqs. (2.2) and (2.6), m > 1 and  $n \approx 60 \, mV/dec$  at room temperature, therefore, it follows from Eq. (2.7) that SS always remains greater than  $60 \, mV/dec$  in a conventional MOSFET. This places a fundamental limit upon the operation of a MOSFET and leads a higher drain leakage current as the supply voltage is reduced, as discussed in Fig. 1.3 of Chapter 1.

# 2.2. Sub-60 MV/DEC SWITCHING, BODY FACTOR, AND NEGATIVE CAPACITANCE

Overcoming the limit of  $60 \, mV/dec$  of subthreshold swing of a Metal–Oxide–Semiconductor Field Effect Transistor (MOSFET) is accepted as the next evolution of CMOS scaling projected for future logic devices [3]–[5]. One of the two main approaches to achieve SS smaller than  $60 \, mV/dec$  is to reduce n below  $60 \, mV/dec$ . This can be obtained by adopting a fundamentally different transport mechanism, such as band-to-band quantum mechanical tunneling in tunnel FETs (TFETs), instead of thermionic emission in a MOSFET as discussed in the next section.

The second method to achieve  $SS < 60 \, mV/dec$  is to enhance the coupling of the gate to the semiconductor such that the body factor m, becomes less than unity. Factors governing the value of the body factor can be understood from the relationship between the applied gate and channel surface potential, which in its simplest form is given as

$$V_{GS} = \phi_{ms} + \frac{Q_{ch}}{C_{ins}} - \frac{Q_{ox}}{C_{ins}} + \Psi_s$$

(2.8)

where  $\phi_{ms}$  represents the work function difference between the gate and semiconductor,  $C_{ins}$  is the unit area capacitance of the gate insulator,  $Q_{ox}$  is the sheet charge density at the interface of the oxide and the semiconductor, and  $Q_{ch}$  is the sheet charge density in the semiconductor. Taking the derivative of Eq. (2.8) with respect to  $\Psi_s$  gives

$$\frac{dV_{GS}}{d\Psi_S} = \frac{d\phi_{ms}}{d\Psi_S} + \frac{d}{d\Psi_S} \left(\frac{Q_{ch}}{C_{ins}}\right) - \frac{d}{d\Psi_S} \left(\frac{Q_{ox}}{C_{ins}}\right) + 1 \tag{2.9}$$

In the case of a conventional MOSFET as  $\phi_{ms}$ ,  $C_{ins}$  and  $Q_{ox}$  are constants, the above equation reduces to

$$m = \frac{dV_{GS}}{d\Psi_S} = 1 + \frac{1}{C_{ins}} \frac{dQ_{ch}}{d\Psi_S} = 1 + \frac{C_{dep}}{C_{ins}} \ge 1$$

(2.10)

where  $dQ_{ch}/d\Psi_s$  in the subthreshold regime is the depletion capacitance  $C_{dep}$ . In terms of voltage across the oxide, the body factor can be written as

$$m = \frac{1}{\frac{d\Psi_S}{dV_{GS}}} \Rightarrow m = \frac{1}{\frac{d(V_{GS} - \phi_{ms} - V_{ox})}{dV_{GS}}} \Rightarrow m = \frac{1}{1 - \frac{dV_{ox}}{dV_{GS}}}$$

(2.11)

Since for a regular dielectric material as the gate insulator,  $C_{ins}$  and  $C_{dep}$  are always non-negative, body factor from Eq. (2.10) always remains greater than 1, leading to a subthreshold swing  $> 60 \, mV/dec$ . It follows from Eq. (2.11), an m > 1 results in  $0 < dV_{ox}/dV_{GS} < 1$  i.e. a change in the voltage across the dielectric is always smaller than the change in applied gate bias and remains in-phase with  $V_{GS}$ . On the other hand, in a FE-FET, where a ferroelectric material is utilised as the gate dielectric,  $C_{ins}$  is replaced with  $C_{FE}$ , which can become negative, as will be shown in section 2.4, resulting in m < 1, or equivalently  $SS < 60 \, mV/dec$  [6].

#### 2.3. OPERATION OF A TFET

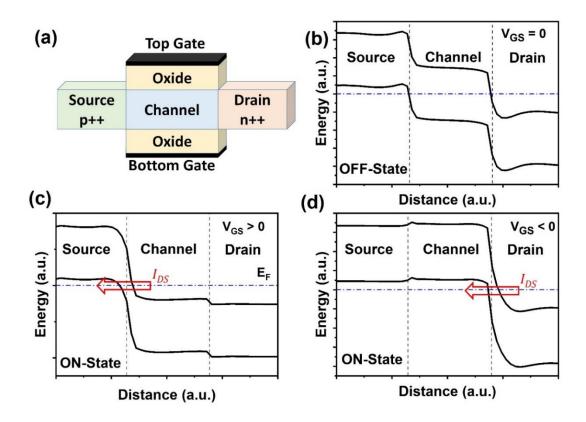

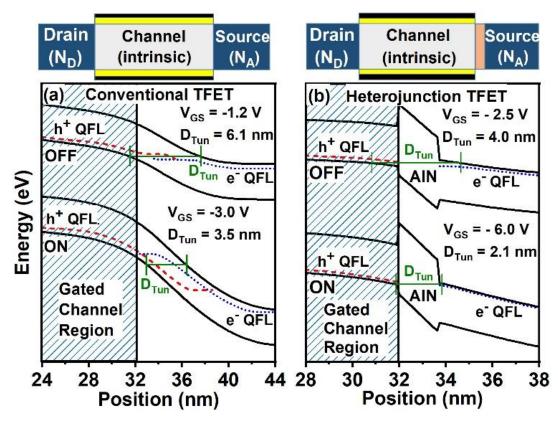

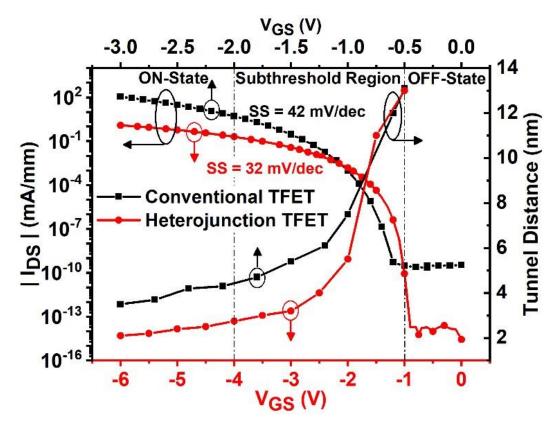

Unlike MOSFETs where the source to drain path consists of n-p-n or p-n-p doped semiconductor regions for n-type and p-type devices, TFETs employ a p-i-n or n-i-p doped semiconductor structure, where source and drain regions are doped degenerately of opposite polarity, as depicted in Fig. 2.3 (a). At zero gate bias, due to presence of the intrinsic channel, a bias across source and drain  $V_{DS}$  does not result in any drain-current and the device remains in the OFF-state, as seen from the band diagram in Fig. 2.3 (b). An application of a positive gate bias lowers the energy of valence and conduction bands in the channel region, which causes an overlap of the conduction band in the channel with the valence band in the source region across a small distance, typically less than 10 nm. This enables the carriers in these regions to tunnel between these bands across the potential barrier introduced by the bandgap, via a band-to-band quantum mechanical tunneling (BBT), as indicated by the red arrow in Fig. 2.3 (c). Therefore, the device switches to the ON-state, and allows conduction, upon the application of  $V_{DS}$ . Fig. 2.3 (d) shows the band diagram for a negative gate bias that raises the energy level of bands in the channel region. As marked by a red arrow in this figure, a similar overlap between the valence band in the channel and conduction band in drain facilitates BBT between these regions, and causes the device to turn-on. Therefore, unlike MOSFETs which are non-ambipolar (i.e. turn-on either with positive or negative gate bias only) TFETs are ambipolar devices and can be turned on via non-zero gate bias in either direction of the bias. Ambipolarity is one of the main challenges with TFETs that leads to a higher leakage and makes their operation unreliable in CMOS logic applications.

Fig. 2.3. (a) Schematic of typical double gate TFET, and the typical band diagrams at (b)  $V_{GS} = 0$ , (c)  $V_{GS} > 0$ , and (d)  $V_{GS} < 0$ .

Since the transport in a TFET is provided by BBT, fundamentally different from MOSFET, the device can potentially achieve a transport factor n (Eq. (2.6)) below  $2.3k_BT/q$ , bringing SS below  $60 \, mV/dec$ . The tunneling probability  $T_{WKB}$  across a potential barrier of height  $\mathcal{V}(x)$  can be described under a Wentzel-Kramers-Brillouin (WKB) approximation as [2]:

$$\mathcal{T}_{WKB} \approx \exp\left(-2\int_{0}^{D_{Tun}} |\kappa(x)| dx\right)$$

(2.12)

where,  $D_{Tun}$  is the band-to-band tunneling distance and  $|\kappa(x)| = \sqrt{2m^*V(x)/\hbar}$  is the absolute value of the wave vector of carriers of effective mass  $m^*$  inside the tunnel barrier. It can be observed from Eq. (2.12) that the tunneling probability, responsible for the current in the device, decays exponentially with  $D_{Tun}$ . Consequently, the drain current in TFETs has been historically worse than in CMOS. Table 2.1 summarises the

reported experimental results for minimum SS and the corresponding ON-current  $I_{ON}$  for the TFETs achieving SS <  $60 \, mV/dec$ . Whereas, the highest drain-current TFET with SS still below  $60 \, mV/dec$  has been reported to be in the range of  $1 - 10 \, \mu A/mm$  [7], orders of magnitude lower than the desired  $\sim 1 \, A/mm$ . Therefore, attempts are being made to shrink  $D_{Tun}$ , by incorporation of a highly doped pocket in the channel, which increases the field at the point of tunneling [8]. In addition, semiconductor materials with dissimilar bandgaps, e.g. heterostructures of III-V compound semiconductors and their alloys, have been utilised to lower the barrier height, which have demonstrated a significant improvement in SS over Si-TFETs [9].

Table 2.1. Experimental results for TFETs with subthreshold swing below  $60 \, mV/dec$ .

| Reference                               | Material System      | $SS_{min}$ | $I_{ON}$ (mA/mm) |

|-----------------------------------------|----------------------|------------|------------------|

| Reference                               | Wiateriai System     | (mV/dec)   | with $SS_{min}$  |

| J. Appenzeller et al. 2004 [10]         | Carbon-nanotube      | 40         | 0.01             |

| W. Y. Choi et al. 2007 [11]             | Silicon              | 53         | ~10              |

| T. Krishnamohan <i>et al.</i> 2008 [12] | Strained-Ge/Si       | 50         | 0.1              |

| K. Tomioka et al. 2012 [13]             | Si/InAs Nanowire     | 21         | 1                |

| L. Knoll et al. 2013 [14]               | Strained-Si Nanowire | 30         | 10               |

| E. Memisevic <i>et al.</i> 2016 [9]     | InAs/GaAsSb/GaSb     | 48         | ~20              |

#### 2.4. Physics of Ferroelectric Materials

The approach of including a layer of ferroelectric material between the gate and semiconductor channel is another potential way for reducing the operating voltage in CMOS, as discussed in chapter 1. The unique negative capacitance phenomenon in a ferroelectric can provide voltage amplification at the semiconductor channel that can lead to a body factor less than unity, resulting in the subthreshold swing of transfer

characteristics beyond that conceivable in conventional MOSFETs. In this section, we will review the properties of Ferroelectric materials, the two phases of these materials, namely ferroelectric (below Curie temperature) and paraelectric (above Curie temperature), describe the negative capacitance, R-C circuit equivalent models for these materials, and how they affect the operation of an FET, when employed as a gate oxide.

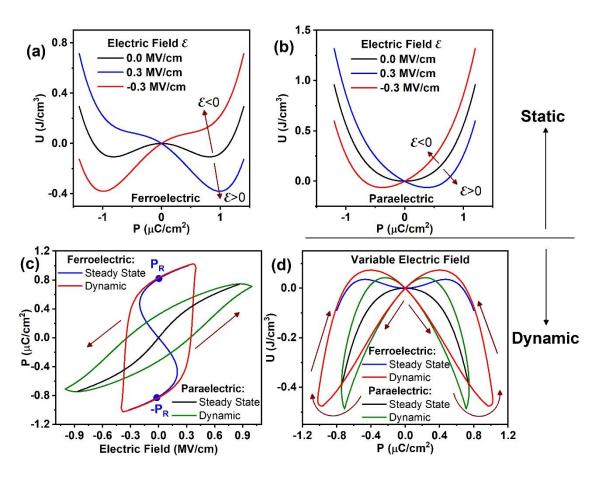

Ferroelectric materials consist of domains of electric dipoles, which can respond to and change their direction of polarisation according to the applied external bias. Unlike ordinary dielectrics where the free energy density U follows a quadratic relationship with respect to the sheet charge density that appears across its terminals, the free-energy density in a typical ferroelectric material is described by a polynomial equation as [15]

$$U = \alpha P^2 + \beta P^4 + \gamma P^6 - P \mathcal{E} \tag{2.13}$$

Where  $\alpha(=1/\varepsilon_r\varepsilon_0)$  is equivalent to the inverse of the dielectric permittivity from the common relationship between electric field  $\mathcal{E}$  and polarisation,  $\beta$  and  $\gamma$  are material dependent constants,  $\mathcal{E}$  is the electric field, and P is the sheet charge density due to polarisation. In a ferroelectric,  $\alpha$  remains less than zero, which results in two local minima from Eq. (2.13), positive and negative spontaneous polarisation states [16], as shown in Fig. 2.4 (a) at  $\mathcal{E}=0$ . Therefore, without an external electric field, a ferroelectric contains a remnant polarisation  $P_R$ , corresponding to one of the minima in U-P curve.  $\alpha$  in a ferroelectric material exhibits temperature dependence, which following the Curie-Weiss law ( $\varepsilon_r = \mathcal{C}/(T-T_{ph})$ ), can be described as [16]

$$\alpha = \frac{T - T_{ph}}{\varepsilon_0 C} \tag{2.14}$$

C is the Curie constant,  $T_{ph}$  is equal to or lower than the Curie temperature. While the temperature is less  $T_{ph}$ ,  $\alpha$  remains negative, and the material exhibits the ferroelectric phase. However, as the temperature exceeds  $T_{ph}$ , the increase in thermal energy disrupts

the alignment of the electric domains in the material, leading to a loss of polarity in the absence of an external electric field, which corresponds to the paraelectric phase, with  $\alpha$  greater than zero. U vs. P for a paraelectric material reduces to a single valley energy profile, with a minimum at P=0 when electric field is zero, as shown in Fig. 2.4 (b). Therefore, unlike ferroelectrics, paraelectrics do not contain any remnant polarisation in the absence of an electric field.

In the presence of an electric field, however, these curves become tilted due to the dependence of U upon  $\mathcal{E}$  in Eq. (2.13), as indicated by the brown arrows in Figs. 2.4 (a) & (b), resulting in one of the minima to become more favourable in the case of a ferroelectric, or causing the minimum to shift from the origin for the case of a paraelectric, leading to a development of finite polarisation.

Fig. 2.4. Simulated energy profiles, U for (a) the ferroelectric and (b) paraelectric phases as a function of polarisation, P at different electric fields. (c) Comparison of P vs. electric field for

FE and PE in steady state and under the dynamic sweep of the electric field with a frequency of 50 MHz, and (d) corresponding U vs. P for ferroelectric and paraelectric where the electric field changes as shown in (c). Here,  $\alpha = -3.2 \times 10^{11} cm/F$  for ferroelectric and  $3.2 \times 10^{11} cm/F$  for paraelectric, while  $\beta$  and  $\gamma$  of  $6.8 \times 10^{23} cm^5/FC^2$  and 0 for both ferro- and paraelectrics are used.

The dynamic behaviour of ferroelectric or paraelectric under continuously varying E is described by the Landau-Khalatnikov (L-K) equation as [17]

$$\rho \frac{dP}{dt} = -\frac{dU}{dP} \tag{2.15}$$

Substituting U from Eq. (2.13) leads to the desired relationship between  $\mathcal{E}$  and P

$$\rho \frac{dP}{dt} = -2\alpha P - 4\beta P^3 - 6\gamma P^5 + \varepsilon \tag{2.16}$$

where  $\rho$  is a damping coefficient associated with the material, which determines the switching rate or a hysteresis in the dynamic behaviour of a ferroelectric material. P vs.  $\mathcal{E}$  from Eq. (2.15) in the steady state i.e. (dP/dt=0) and under dynamic  $\mathcal{E}$  are plotted in Fig. 2.4 (c). In the steady state, the P vs.  $\mathcal{E}$  curve in ferroelectric exhibits an 'S' shaped characteristic with a negative-slope  $(dP/d\mathcal{E} < 0)$  around the origin, which is an unstable region, and causes the polarisation to settle into one of two residual states at  $\mathcal{E}=0$ , marked by  $\pm P_R$  in Fig. 2.4 (c). P vs.  $\mathcal{E}$  in a paraelectric does not show such a region with negative slope. Therefore, P remains zero at zero electric field. This dissimilarity however, vanishes under a dynamic sweep, where both ferro- and para- electrics show non-zero P at  $\mathcal{E}=0$ , giving rise to an anti-clockwise hysteresis. This hysteresis arises because the term  $\rho$  dP/dt in Eq. (2.16) slows down the maximum rate of change in P, introducing a delay in the change in P with respect to a change in the electric field. This leads to a non-zero polarisation at zero electric field with an anti-clockwise hysteresis. Fig. 2.4 (d) compares the U vs. P characteristics of both materials in steady state and dynamic conditions, as electric field changes according to that shown in Fig. 2.4 (c). Fig.

2.4 (d) further confirms the similarity of the two materials under dynamic operation.

## 2.4.1. Equivalent Series R-C Circuit Model

Since the parallel plate capacitance of a layer of dielectric is related to its stored energy density as  $C = \left(t \frac{d^2 U}{dQ^2}\right)^{-1}$ , where t is the layer thickness or distance between the electrodes, we can apply the same procedure to obtain an expression for the unit-area capacitance of a ferroelectric or paraelectric  $C_{F/P}$ , while substituting U from Eq. (2.13) with  $\mathcal{E}$  equals to zero, which leads to

$$C_{F/P}^{-1} = t(2\alpha + 12\beta Q^2 + 24\gamma Q^4)$$

(2.17)

where P is expressed as the sheet charge density Q that appears across the terminals of insulator of thickness t. Since the double derivative of any given curve becomes negative wherever the curve becomes convex (a local maximum),  $C_{F/P}$  becomes negative, where U vs. P in Fig. 2.4 (a) shows a maximum (see black curve around origin). This also corresponds to the region of P vs.  $\mathcal{E}$  plot in Fig. 2.4 (c), where its slope becomes negative.

Utilising Eq. (2.17), it is possible to construct an equivalent non-linear RC circuit from Eq. (2.16) [15]. If V is the bias applied across an insulator of thickness t, substituting  $\mathcal{E} = V/t$ , Q = P, and  $C_{F/P}$  from Eq. (2.17) into Eq. (2.16)

$$V = \rho t \frac{dQ}{dt} + \int \frac{dQ}{C_{F/P}} = RI + \int \frac{dQ}{C_{F/P}}$$

(2.18)

Eq. (2.18) represents a series non-linear RC circuit with  $R = \rho t$  with  $C_{F/P}$  described according to Eq. (2.17). Owing to the delay introduced by this series RC circuit, originating from the finite response of polarisation with respect to external electric field, we observe a remnant polarisation for a paraelectric in Fig. 2.4 (c) under dynamic electric field. However, an important distinction is that while in a paraelectric, the non-linear

capacitor, always remains positive, it can become negative for a ferroelectric in a certain range of operation, owing to  $\alpha < 0$  for this material.

### 2.5. OPERATION OF A FE-FET

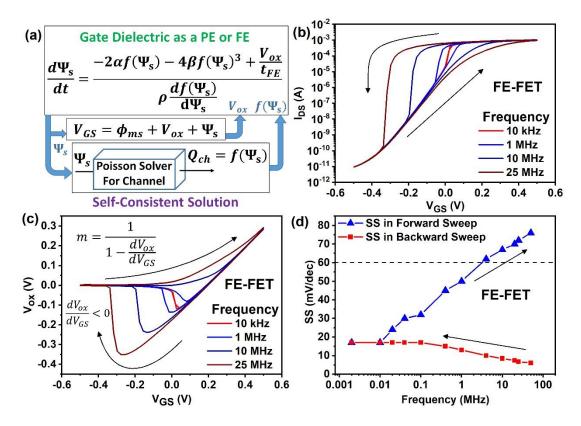

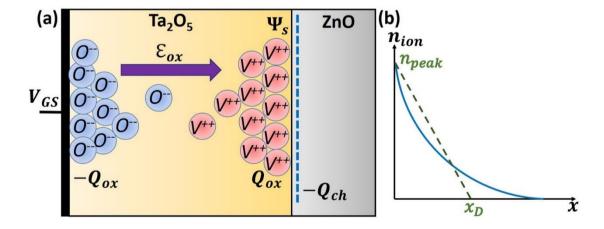

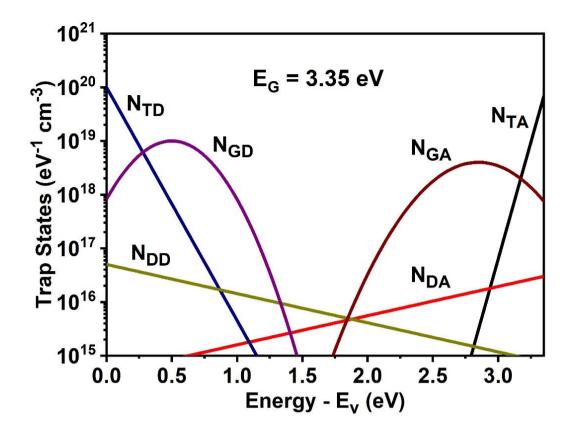

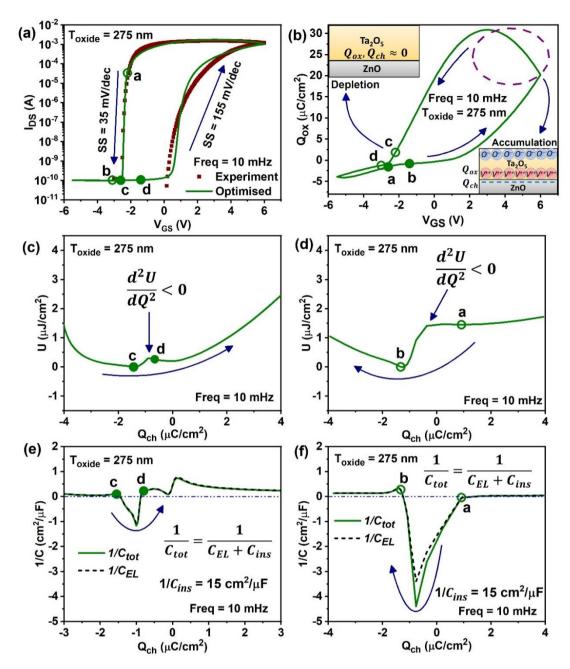

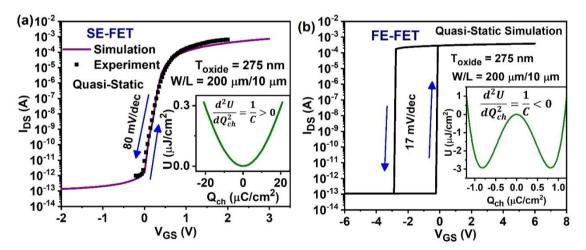

A flow diagram for simulating the dynamic characteristics for either FE- or PE- FET is illustrated in Fig. 2.5 (a). At a given gate bias, first a value of  $\Psi_s$  is guessed, and the corresponding sheet charge density in the channel  $Q_{ch}$  is obtained by solving the one-dimensional Poisson equation along with the density of carriers, which is determined by integrating the density of states in the channel together with the potential dependent Fermi-Dirac distribution of carriers within the channel. This procedure can be summarised as  $Q_{ch} = f(\Psi_s)$ , as shown in Fig. 2.5 (a). The values for  $Q_{ch}$  and  $V_{ox}$  (=  $V_{GS} - \phi_{ms} - \Psi_s$ ) are substituted into L-K equation (Eq. (2.16)) to generate a new value for  $\Psi_s$ , which is used in the subsequent calculation of  $Q_{ch}$ . This process is repeated until the change in  $\Psi_s$  becomes smaller than some desirable tolerance. For each of the applied gate bias point, the entire procedure is repeated to obtain the final value for  $Q_{ch}$ . From the converged values of  $Q_{ch}$ , the drain current  $I_{DS}$  is obtained simply as:

$$I_{DS} = \mu \frac{W}{L} Q_{ch} V_{DS} \tag{2.19}$$

where  $\mu$  is the mobility of carriers in the semiconducting channel, W and L are the width and length of the device, and  $V_{DS}$  is the drain to source bias. The results for  $I_{DS}$  from Eq. (2.19) of an FE-FET at different scan frequencies of gate bias are plotted in Fig. 2.5 (b). Owing to the instability in the FE, steep switching is observed during both the forward and backward sweeps of gate bias. It has been explained in the literature by a sudden change in the polarisation state of the FE that causes a change in the density of carriers in channel and results in amplification [18]. At low frequency, the slope  $dV_{OX}/dV_{GS}$  becomes less than zero during both directions of the sweep of  $V_{GS}$ , resulting

in a body factor m < 1, according to Eq. (2.11). At higher frequency, the counterclockwise hysteresis in the transfer characteristics of the device follows from the ferroelectric properties, observed in Fig. 2.4 (c), following the L-K equation. The increase in the hysteresis with frequency arises from the finite time taken by the ferroelectric domains to respond to the changing electric field, controlled by  $\rho$  in Eq. (2.16). A high remnant polarisation in the ferroelectric maintains the surface potential of the channel  $\Psi_s$  during the reverse sweep, while the majority of the reduction in applied gate voltage is dropped across the ferroelectric,  $V_{ox}$ , which thereby achieves a minimum in Fig. 2.5 (c). However, as the gate voltage is further reduced, a change in the state of polarisation leads to a depletion in the channel and a corresponding reduction in  $\Psi_s$ , while  $V_{ox}$  increases to its initial value. This increase in  $V_{ox}$  during a reduction of  $V_{GS}$  leads to  $dV_{ox}/dV_{GS} < 0$ , thereby producing m < 1 from Eq. (2.11). Fig. 2.5 (d) reveals a SS < 60 mV/dec at low frequency in both the forward and backward directions of  $V_{GS}$ . With an increase in frequency, the increase in the width of the hysteresis in the transfer characteristics becomes larger. As a result, SS during the forward sweep degrades, increasing above 60 mV/dec at a frequency of ~3 MHz, while in the backward sweep, it becomes as low as  $\sim 5 \, mV/dec$ . Employing a ferroelectric material to boost the SS does not always guarantee a sub-60 mV/dec operation. Since a ferroelectric affects the body factor, the amplification depends upon the performance of the underlying MOSFET via the factor  $n = d \log I_{DS} / d\Psi_s$ . Moreover, the observed SS in FE-FETs can fluctuate owing to non-idealities such as multi-domain ferroelectricity, diverse polarisation [19] or gate leakage [20].

Fig. 2.5. (a) A flow diagram showing the self-consistent coupling of the L-K equation with the semiconductor channel for computing the drain current in FE- or PE- FET. (b) Simulated transfer characteristics, (c) voltage across the ferroelectric gate insulator  $V_{ox}$  vs. the applied gate bias  $V_{GS}$  at different frequency of gate bias sweep. (d) SS vs. scan frequency in both directions of gate bias sweep for a ferroelectric FET (FE-FET). A sub-60 mV/dec switching is present at low frequency (where hysteresis virtually disappears). At higher frequency, the width of the hysteresis increases and the switching becomes more gradual because of the finite rate of change in the polarisation controlled by the parameter  $\rho$  in Eq. (2.16). where  $\alpha$ ,  $\beta$ ,  $\gamma$ , and  $\rho$  of  $-3.2 \times 10^{11} cm/F$ ,  $6.8 \times 10^{23} cm^5/FC^2$ , 0, 3000  $\Omega$  cm are used.

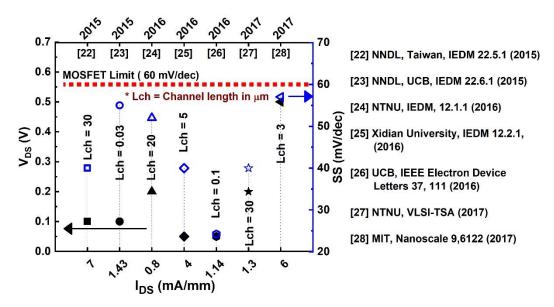

Fig. 2.6 highlights reported results in ferroelectric FETs meant for mainstream CMOS applications. Many of these are based on devices with long channel lengths, while the drain current does not exceed 6 mA/mm, at least 3 orders of magnitude lower than the accepted benchmark ( $\sim 1 A/mm$ ).

Fig. 2.6. Recent experimental results of reported ferroelectric FETs for CMOS applications. [21]–[27]

#### 2.6. OPERATION OF A PE-FET

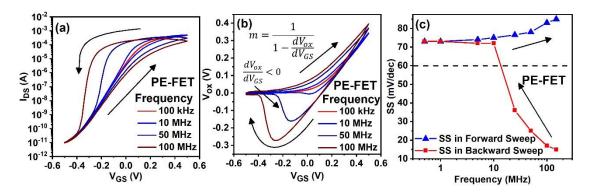

The operation of a paraelectric (PE) –FET can also be simulated in a similar fashion to a FE-FET by simply replacing the ferroelectric by a paraelectric (PE) material. The transfer characteristics of a PE-FET, plotted in Fig. 2.7 (a), show no steep-switching at low scan frequency of  $V_{GS}$ , but the slope of the drain-current becomes steeper during the backward sweep as the frequency is increased. Further investigation of the  $V_{ox}$  vs.  $V_{GS}$  in Fig. 2.7 (b) reveals that at low frequency, the slope  $dV_{ox}/dV_{GS}$  remains positive, resulting in m > 1. At higher frequency,  $dV_{ox}/dV_{GS}$  turns negative only in the backward sweep, leading to m < 1 (Eq. (2.11)). Fig. 2.7 (c) indicates that the SS remains greater than 60 mV/dec at low frequency in both forward and backward directions of  $V_{GS}$  sweep, but become less than 60 mV/dec in the backward sweep as the frequency of gate bias sweeps exceeds 12 MHz (for this value of  $\rho$ ). As we observed, the capacitance for a PE in Eq. (2.17) always remains greater than zero, implying that the observed sub-60 mV/dec of switching originates from a different mechanism. In fact, owing to the equivalent series R-C circuit representation of L-K equation in Eq. (2.18), the

paraelectric insulator introduces a delay in propagating the variations in  $V_{GS}$  to the surface of the semiconductor, causing a phase difference between  $V_{GS}$  and  $\Psi_s$ . Due to this phase difference, the change in  $\Psi_s$  becomes greater than the corresponding change in  $V_{GS}$  at high frequency, that is  $dV_{GS}/d\Psi_s < 1$ , or equivalently  $dV_{ox}/dV_{GS} < 1$ , from Eq. (2.2) since  $\Psi_s = V_{GS} - \phi_{ms} - V_{ox}$ . Consequently, sub-60 mV/dec switching in the dynamic characteristics of PE-FETs is possible via an equivalent R-C type behaviour represented by an equivalent circuit based on the L-K equation during the backward scan of the gate bias depending upon the frequency.

Fig. 2.7. (a) Simulated transfer characteristics of a PE-FET with gate scan frequency (b) Voltage across the paraelectric gate insulator  $V_{ox}$  vs. the applied gate bias  $V_{GS}$ , and (c) SS vs. frequency of gate bias sweep in forward and reverse directions for a PE-FET. No steep-switching at low frequency is present in either forward or backward direction of sweep. At a scan frequency >  $15 \, MHz$ , the device shows a  $SS < 60 \, mV/dec$  in the backward sweep for chosen parameters, where  $\alpha$ ,  $\beta$ ,  $\gamma$ , and  $\rho$  of  $3.2 \times 10^{11} cm/F$ ,  $6.8 \times 10^{23} cm^5/FC^2$ , 0, and  $3000 \, \Omega \, cm$  are used.

## 2.7. SUMMARY

In this chapter, we have reviewed the operation of MOSFET, physics of steep switching devices such as a tunnel and ferroelectric FET (TFET and FE-FET) and their distinction from paraelectric FETs. We have demonstrated that under dynamic conditions the energy well profiles of FE-FETs and PE-FETs can be somewhat indistinguishable, but the frequency dependence of the SS is a useful method of identifying the physics of operation of these two FETs. These concepts will provide a foundation for the discussion

of this work in the subsequent chapters.

#### 2.8. REFERENCE

- [1] Y. Taur and T. H. Ning, *Fundamentals of Modern VLSI Devices*. Cambridge University Press, 2002. DOI: 10.1109/LED.2004.837581.

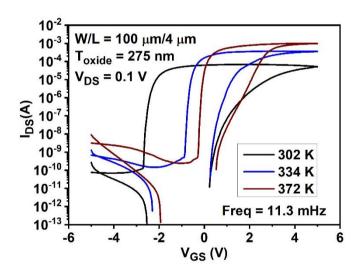

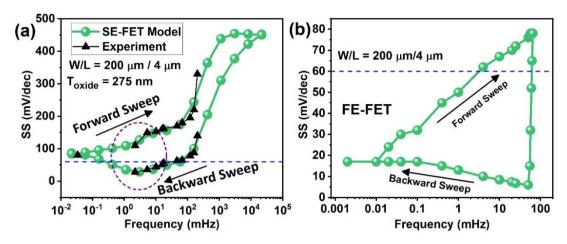

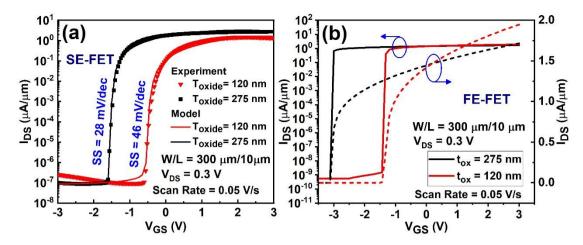

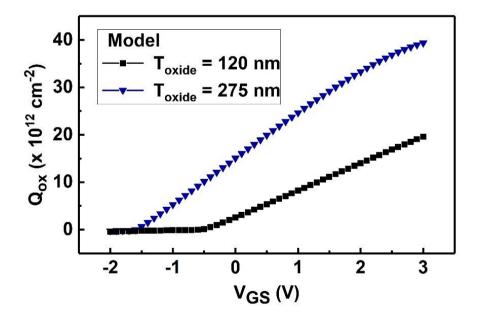

- [2] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*. John Wiley & Sons, 2006.