# EMC Performance of Field Programmable Gate-Arrays: Effects of I/O Standards and Attributes on the Radiated Emissions Spectrum

Mark Andrew Boden

**Master of Science Research**

**University of York**

**Electronic Engineering**

**June 2017**

## **Abstract**

This research investigates what impact the I/O standards & attributes of a Field Programmable Gate Array have on the radiated emissions spectrum. FPGAs are used in countless digital applications. The use of a Spartan-6 FPGA gives a good representation of a general device with Xilinx being the market leader in supplying FPGAs for a variety of industries. The logic standard, drive strength and edge rate are examined for their impact on that radiated emissions produced. Digital integrated circuits are a well-known and documented source of Electromagnetic Interference due to the fast transitions of period signals. A practical and theoretical understanding of the behaviour of clock signals in the time and frequency domains has been established. The impact of phenomena such as overshoot and ringing from practical signals has been considered for its impact on the emissions spectrum and how this deviates from the theoretical expectations. Logic standard, drive strength and edge rate have been assessed comparatively to determine their influence of peak emissions produced. Of the logic standards tested the LVTTL standard recorded the highest level of EMI across all I/O logic standards approximately 4dB higher than the equivalent CMOS standards. The LVTTL standard recorded the largest variation in emissions across the available I/O driver settings with approximately a 14dB increase from the minimum to maximum I/O driver settings. The LVCMOS logic standards recorded on average across the 3.3 volts, 2.5 volts, 1.8 volts, 1.5 volts and 1.2 volts logic, a maximum change to EMI of approximately 10dB from the minimum to maximum driver settings. Each category of the variable I/O driver settings has been assessed independently to assess the level of change to emissions produced. Average levels of EMI produced under each I/O driver setting have also been obtained and presented to give engineers and designers an indication of how decisions made within the design process can influence the level of emissions produced. It is hoped that this research will provide as a useful tool when designing with programmable integrated circuits such as the Spartan-6 FPGA and the potential EMC impact on the radiated emissions spectrum.

# Contents

| A  | bstract | ıct                                                      | 2  |

|----|---------|----------------------------------------------------------|----|

| C  | ontent  | nts                                                      | 3  |

| Fi | gures.  | S                                                        | 7  |

| Ta | ables   |                                                          | 11 |

| Ε¢ | quation | ons                                                      | 12 |

| Α  | cknow   | wledgments                                               | 14 |

| D  | eclarat | ation                                                    | 15 |

| 1  | Intr    | troduction                                               | 16 |

|    | 1.1     | EMI from Digital Circuits & Systems                      | 16 |

|    | 1.1.    | 1.1 EMI from Practical Signals                           | 18 |

|    | 1.2     | Historical Review of EMC Studies of Integrated Circuits. | 21 |

|    | 1.3     | FPGA Overview                                            | 23 |

|    | 1.3.    | 3.1 FPGA Basic Architecture                              | 23 |

|    | 1.3.    | 3.2 FPGA LVCMOS & LVTTL Logic Standards                  | 25 |

|    | 1.3.    | 3.3 FPGA Output Buffer Circuit Overview                  | 25 |

|    | 1.3.    | 3.4 Logic Family Comparison                              | 26 |

|    | 1.4     | Overview of Thesis                                       | 28 |

| 2  | Circ    | rcuit for Testing - Architecture & Design                | 29 |

|    | 2.1     | Hardware Design Overview                                 | 29 |

|    | 2.1.    | 1.1 Board Power                                          | 31 |

|    | 2.1.    | 1.2 Voltage Regulators                                   | 31 |

|    | 2.1.    | 1.3 Expansion Headers                                    | 32 |

|    | 2.2     | Measurement Architecture                                 | 33 |

|    | 2.2.    | 2.1 Signal Integrity Measurement Traces                  | 33 |

|    | 2.2.    | 2.2 Measurement Instrument Protection                    | 34 |

|    | 2.2.    | 2.3 DC Blocking Capacitor                                | 34 |

|    | 2.2.    | 2.4 Attenuator                                           | 35 |

|    | 2.2.    | 2.5 Capacitor Attenuation                                | 36 |

|    | 2.2.    | 2.6 Emissions Traces                                     | 38 |

|    | 2.3     | VHDL Code Design                                         | 38 |

|    | 2.3.    | 3.1 MSCR-001 VHDL Cores & Primitives                     | 39 |

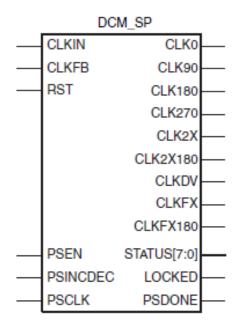

|   | 2.3. | 2 DCM – Digital Clock Manager (FREQ_CHANGE)    | 39 |

|---|------|------------------------------------------------|----|

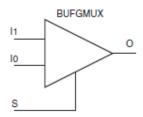

|   | 2.3. | 3 BUFGMUX (CLOCK_MUX)                          | 40 |

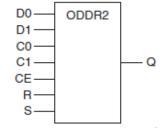

|   | 2.3. | 4 ODDR2 (HP2_PIN_2 & SMA_SIG2)                 | 40 |

|   | 2.4  | VHDL Code Overview                             | 40 |

| 3 | Sign | nal Testing – Signal Generator                 | 42 |

|   | 3.1  | Testing Overview                               | 42 |

|   | 3.1. | 1 Source Signals                               | 43 |

|   | 3.1. | 2 Time Domain Analysis Test Setup              | 43 |

|   | 3.1. | 3 Frequency Domain Analysis                    | 44 |

|   | 3.1. | 4 Results Processing MATLAB                    | 45 |

|   | 3.2  | Signal 1 & 2 Time and Frequency Domain Results | 46 |

|   | 3.2. | 1 Time Domain Analysis                         | 46 |

|   | 3.2. | 2 Frequency Domain Analysis                    | 47 |

|   | 3.2. | 3 Theory v Practical Curve Comparison          | 49 |

|   | 3.3  | Signal 3 - 6 Time and Frequency Domain Results | 50 |

|   | 3.3. | 1 Time Domain Analysis                         | 50 |

|   | 3.3. | 2 Frequency Domain Analysis                    | 52 |

|   | 3.3. | 3 Theory v Practical Curve Comparison          | 55 |

|   | 3.4  | Signal Generator Testing Conclusion            | 57 |

| 4 | Sigr | nal Integrity Testing - MSCR-001 PCB           | 59 |

|   | 4.1  | Spartan 6 I/O Attributes                       | 59 |

|   | 4.2  | Test Plan & Setup                              | 59 |

|   | 4.2. | 1 Time & Frequency Domain Set-Ups              | 60 |

|   | 4.2. | 2 Time Domain Test Equipment                   | 61 |

|   | 4.2. | 3 Frequency Domain Test Equipment              | 61 |

|   | 4.3  | Overview of Testing - MSCR-001 PCB             | 62 |

|   | 4.3. | 1 LVTTL Testing                                | 62 |

|   | 4.3. | 2 LVTTL Theory v Practical Analysis            | 68 |

|   | 4.3. | 3 LVCMOS33 Testing                             | 69 |

|   | 4.3. | 4 LVCMOS33 Theory v Practical Analysis         | 73 |

| 5 | MS   | CR-001 – Radiated Emissions Testing            | 76 |

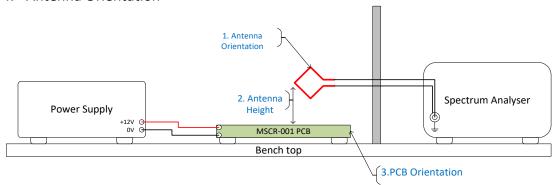

|   | 5.1  | Test Setup                                     | 76 |

|   | 5.1. | 1 Test Equipment                               | 77 |

| 5.  | 1.2    | Spectrum Analyser Settings                | 77  |

|-----|--------|-------------------------------------------|-----|

| 5.  | 1.3    | Test Procedure                            | 77  |

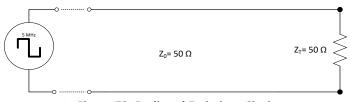

| 5.  | 1.4    | Radiated Emissions PCB Configuration      | 78  |

| 5.  | 1.5    | Order of Testing                          | 78  |

| 5.2 | Re     | sults Anomalies and Equipment Limitations | 79  |

| 5.3 | Lo     | gic Standard Testing                      | 80  |

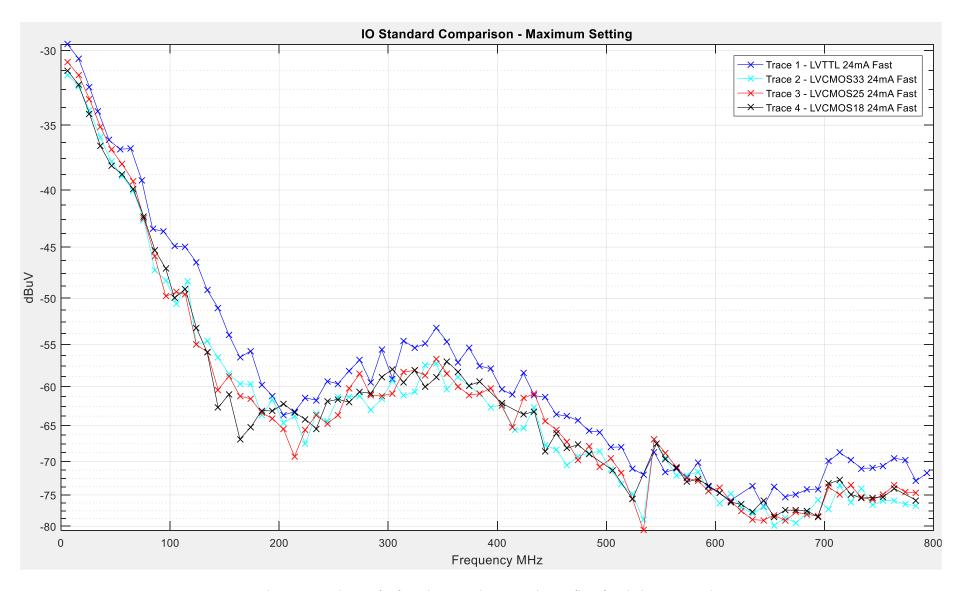

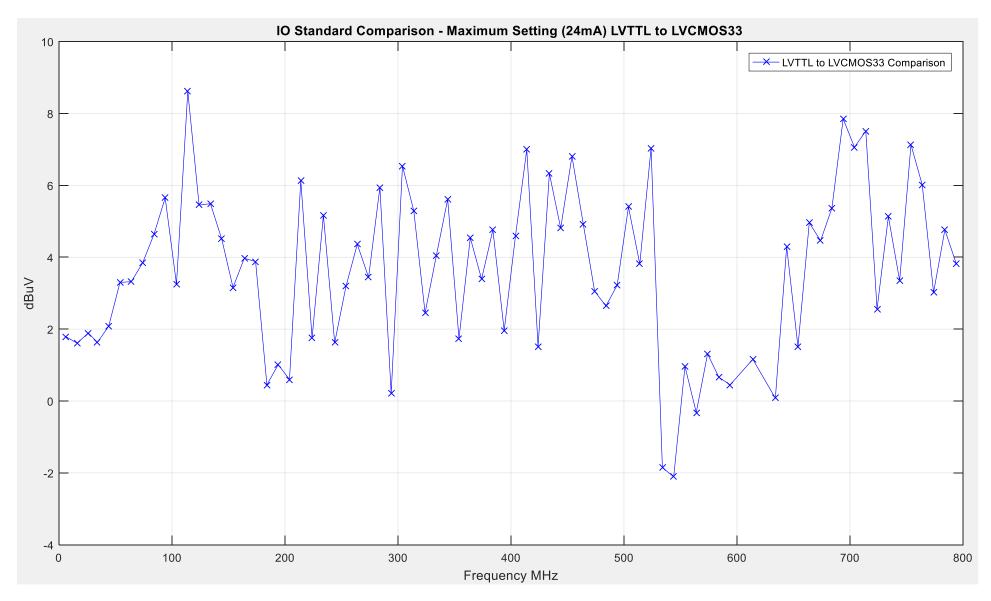

| 5.  | 3.1    | Comparison One – Maximum Settings         | 80  |

| 5.  | 3.2    | Comparison Two – Default Settings         | 87  |

| 5.  | 3.3    | Comparison Three – Minimum Settings       | 96  |

| 5.  | 3.4    | I/O Standard Testing Conclusion           | 105 |

| 5.4 | Dri    | ive Strength Testing                      | 107 |

| 5.  | 4.1    | LVTTL Drive Strength Testing Results      | 107 |

| 5.  | 4.2    | LVCMOS33 Drive Strength Results           | 119 |

| 5.  | 4.3    | LVCMOS25 Drive Strength Results           | 131 |

| 5.  | 4.4    | LVCMOS18 Drive Strength Results           | 143 |

| 5.  | 4.5    | LVCMOS15 Drive Strength Results           | 155 |

| 5.  | 4.6    | LVCMOS12 Drive Strength Results           | 165 |

| 5.  | 4.7    | Drive Strength Testing Conclusion         | 174 |

| 5.5 | Ed     | ge Rate Comparison                        | 176 |

| 5.  | 5.1    | Edge Rate Testing Overview & Results      | 176 |

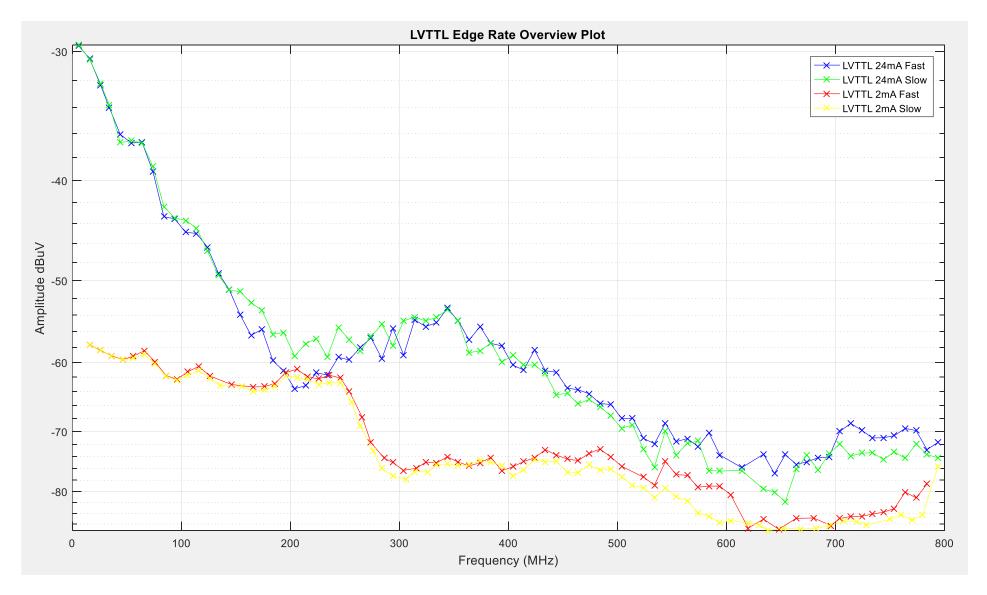

| 5.  | 5.2    | LVTTL Edge Rate Results                   | 176 |

| 5.  | 5.3    | LVCMOS33 Edge Rate Results                | 183 |

| 5.  | 5.4    | LVCMOS25 Edge Rate Results                | 190 |

| 5.  | 5.5    | LVCMOS18 Edge Rate Results                | 197 |

| 5.  | 5.6    | LVCMOS15 Edge Rate Results                | 204 |

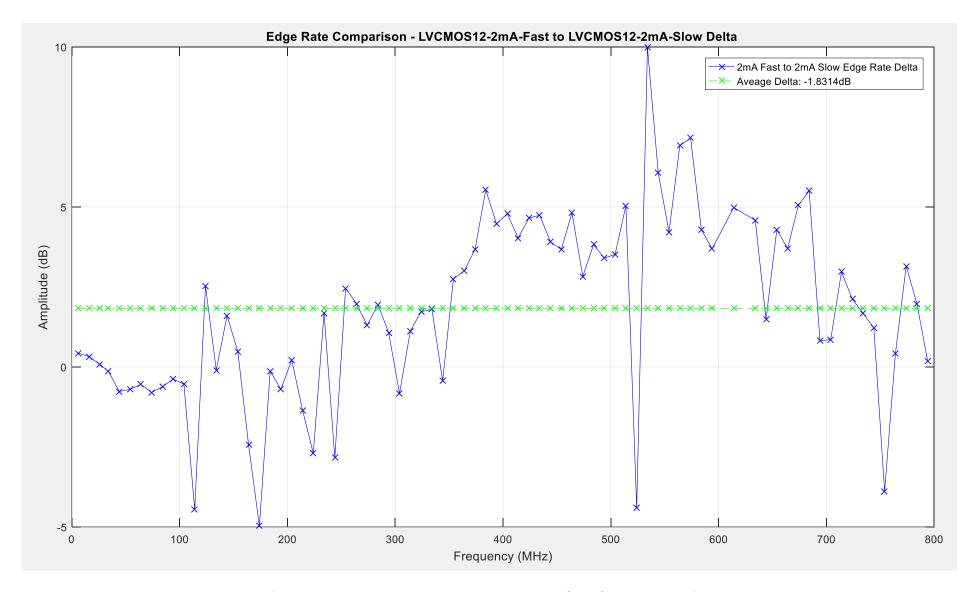

| 5.  | 5.7    | LVCMOS12 Edge Rate Results                | 211 |

| 5.  | 5.8    | Edge Rate Testing Conclusion              | 218 |

| Ra  | adiate | ed Emissions Reference Levels             | 220 |

| 6.1 | Te     | sting Overview                            | 220 |

| 6.  | 1.1    | LVTTL Emissions Overview                  | 220 |

| 6.  | 1.2    | LVCMOS33 Emissions Overview               | 221 |

| 6.  | 1.3    | LVCMOS25 Emissions Overview               | 221 |

| 6.  | 1.4    | LVCMOS18 Emissions Overview               | 222 |

6

|    | 6.1.5     | LVCMOS15 Emissions Overview | 222 |

|----|-----------|-----------------------------|-----|

|    | 6.1.6     | LVCMOS12 Emissions Overview | 223 |

| 7  | Conclu    | sions                       | 224 |

| ,  | 7.1 Fu    | rther Research              | 226 |

| Ар | pendix    |                             | 227 |

|    | Appendix  | ¢ A1                        | 228 |

|    | Appendix  | ¢ A2                        | 238 |

|    | Appendix  | ¢ A3                        | 246 |

|    | Appendix  | ¢ A4                        | 251 |

|    | Appendix  | ¢ A5                        | 256 |

|    | Appendix  | ¢ A6                        | 259 |

|    | Appendix  | ¢ A7                        | 261 |

| Ac | ronyms    |                             | 263 |

| Re | ferencing | 7                           | 264 |

# **Figures**

| Figure 1: Properties of a Clock Waveform [5], [6]                  | 17 |

|--------------------------------------------------------------------|----|

| Figure 2: Frequency Domain Behaviour of a Periodic Signal [5], [6] | 18 |

| Figure 3: L-C-R Circuit Example                                    | 19 |

| Figure 4: L-C-R Step Response                                      | 19 |

| Figure 5: L-C-R Frequency Response [9]                             | 20 |

| Figure 6: FPGA Architecture Overview [21]                          | 23 |

| Figure 7: Basic Logic Element [21]                                 | 24 |

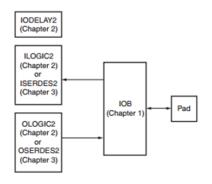

| Figure 8: FPGA I/O Block Overview [23]                             | 24 |

| Figure 9: SPARTAN-6 FPGA I/O Block [22]                            | 25 |

| Figure 10: Output Buffer Circuit [27]                              | 25 |

| Figure 11: Logic Family Timeline [26]                              | 26 |

| Figure 12: MSCR-001 Hardware Architecture                          | 29 |

| Figure 13: MSCR-001 PCB Overview                                   | 30 |

| Figure 14: MSCR-001 Board Power                                    | 31 |

| Figure 15: MSCR-001 Expansion Header                               | 32 |

| Figure 16: FPGA Expansion Port Nets                                | 32 |

| Figure 17: SMA FPGA I/O Connection                                 | 33 |

| Figure 18: SMA Power Plane Connection                              | 33 |

| Figure 19: DC Blocking Capacitor                                   | 34 |

| Figure 20: DC Blocking Capacitor Impedance [31]                    | 35 |

| Figure 21: Attenuator Circuit                                      | 35 |

| Figure 22: Capacitor Equivalent Circuit                            | 36 |

| Figure 23: Attenuator Equivalent Circuit                           | 37 |

| Figure 24: Capacitor Attenuation                                   | 37 |

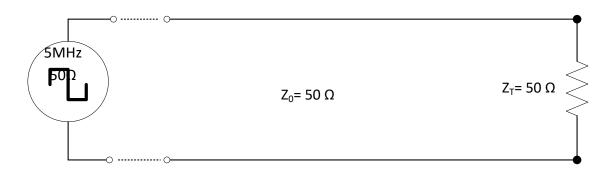

| Figure 25: Terminated I/O Signal pins                              | 38 |

| Figure 26: DCM Primitive [33]                                      | 39 |

| Figure 27: BUFGMUX Primitive[33]                                   | 40 |

| Figure 28: ODDR2 Primitive [22]                                    | 40 |

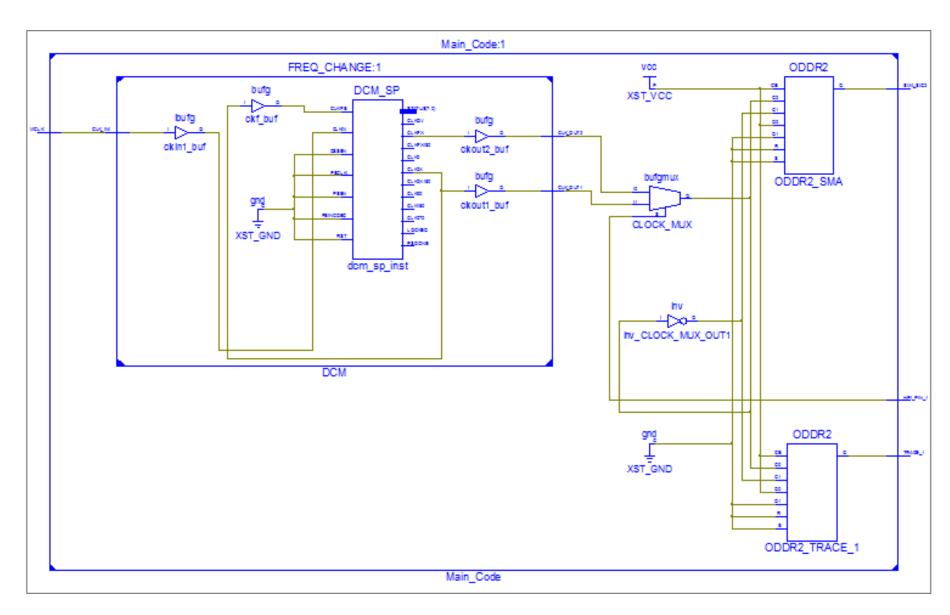

| Figure 29: VHDL Code RTL Schematic                                 | 41 |

| Figure 30: Time Domain Test Setup - Signal Integrity Testing       | 43 |

| Figure 31: Time Domain Testing Photograph - Signal Generator       | 43 |

| Figure 32: Frequency Domain Test Setup Signal Integrity Testing    | 44 |

| Figure 33: Frequency Domain Testing Photograph - Signal Generator  | 45 |

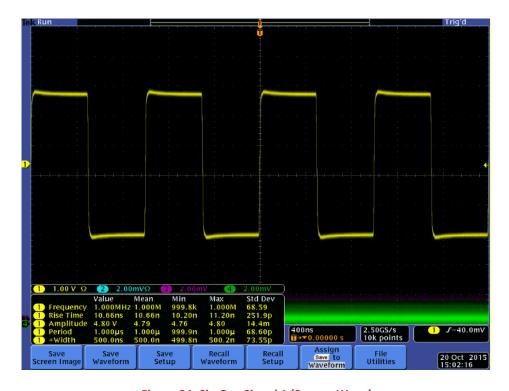

| Figure 34: Sig Gen Signal 1 (Square Wave)                          | 46 |

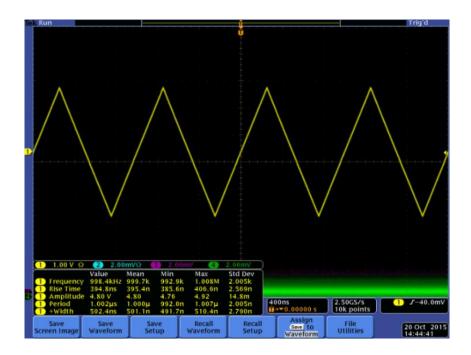

| Figure 35: Sign Gen Signal 2 (Triangle Wave)                       | 47 |

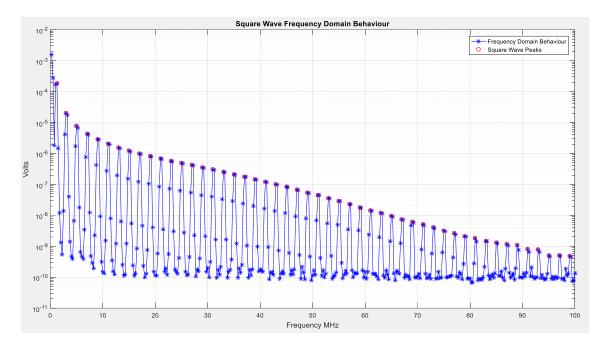

| Figure 36: Signal 1 (Square Wave) - Frequency Domain Response      | 48 |

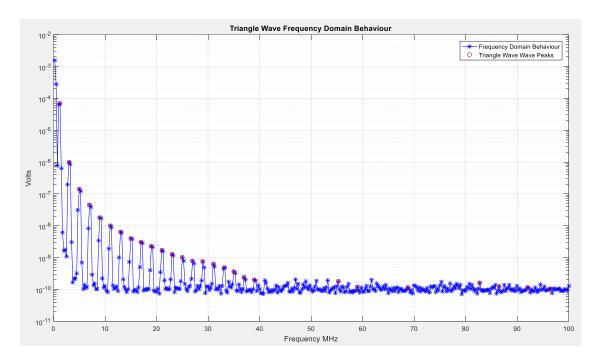

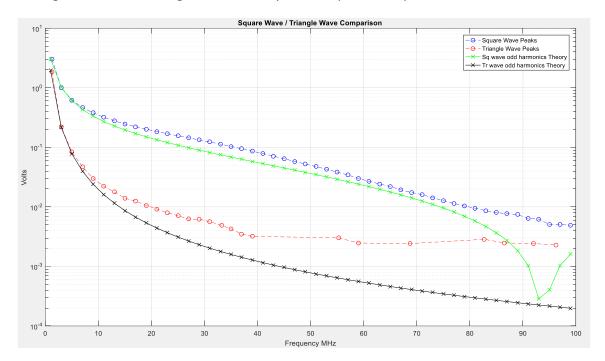

| Figure 37: Signal 2 (Triangle Wave) - Frequency Domain Response    | 48 |

| Figure 38: Square Wave and Triangle Wave (Practical & Theory)      | 49 |

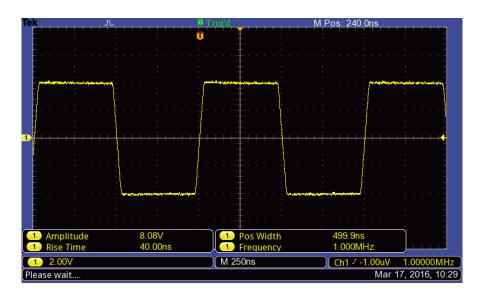

| Figure 39: Signal Generator Square Wave 10nS Rise Time             | 51 |

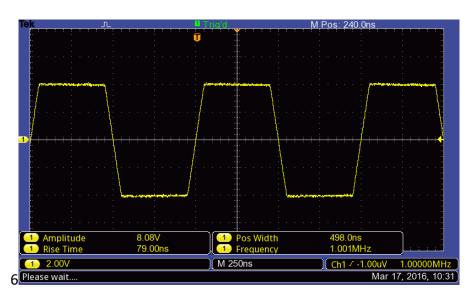

| Figure 40: Signal Generator Square Wave 20nS Rise Time             | 51 |

| Figure 41: Signal Generator Square Wave 40nS Rise Time                                  | 51   |

|-----------------------------------------------------------------------------------------|------|

| Figure 42: Signal Generator Square Wave 80nS Rise Time                                  | 52   |

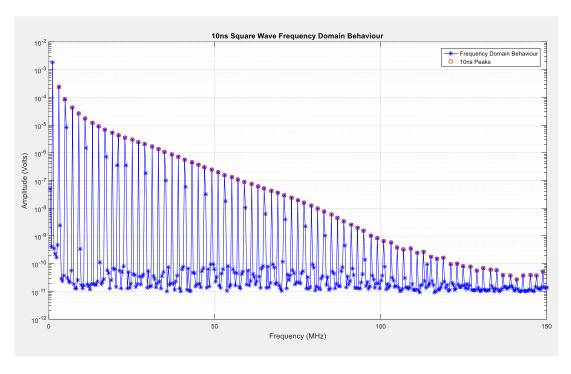

| Figure 43: Signal Generator Square Wave 10nS Rise Time Frequency Domain Behaviour       | 52   |

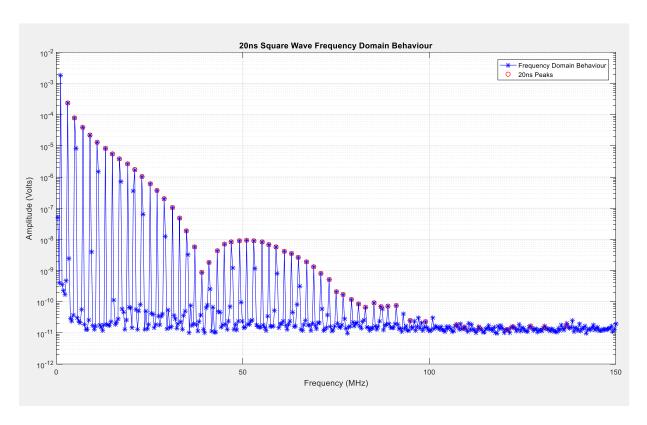

| Figure 44: Signal Generator Square Wave 20nS Rise Time Frequency Domain Behaviour       | 53   |

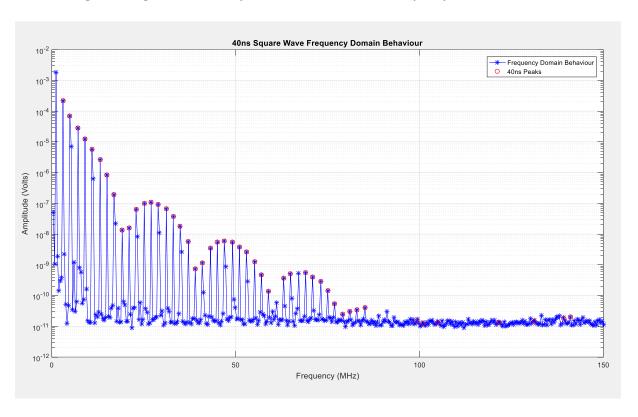

| Figure 45: Signal Generator Square Wave 40nS Rise Time Frequency Domain Behaviour       | 53   |

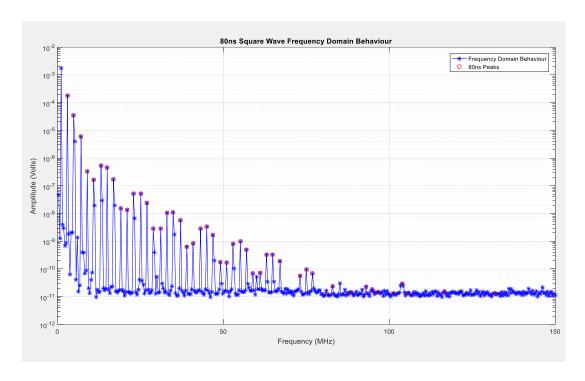

| Figure 46: Signal Generator Square Wave 80nS Rise Time Frequency Domain Behaviour       | 54   |

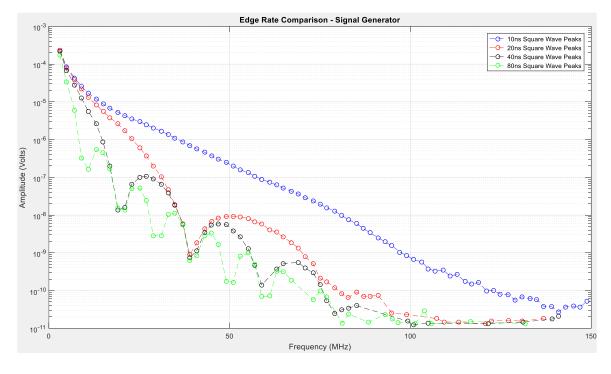

| Figure 47: Signal Generator Square Wave Peak Harmonic Level Comparison                  | 54   |

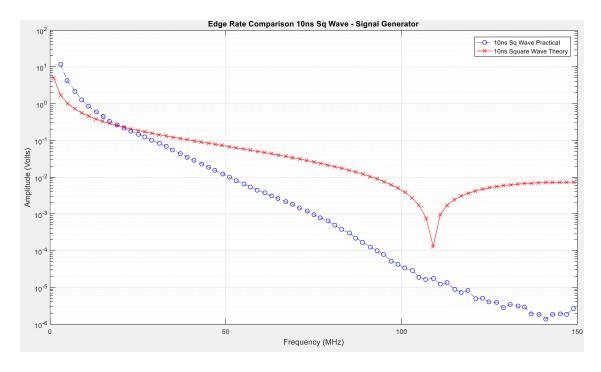

| Figure 48: 10ns Square Wave Practical & Theoretical Curves                              | 55   |

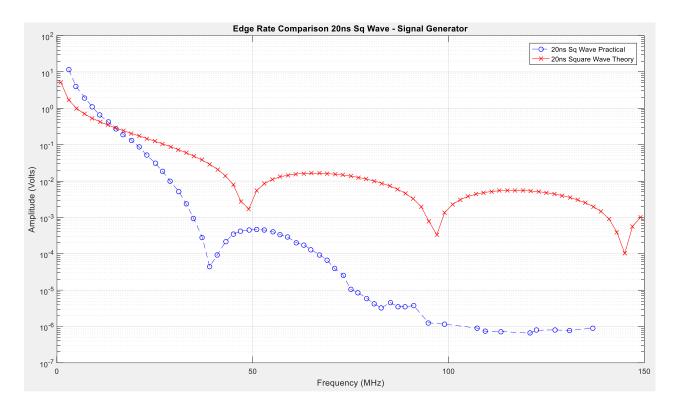

| Figure 49: 20ns Square Wave Practical & Theoretical Curves                              | 56   |

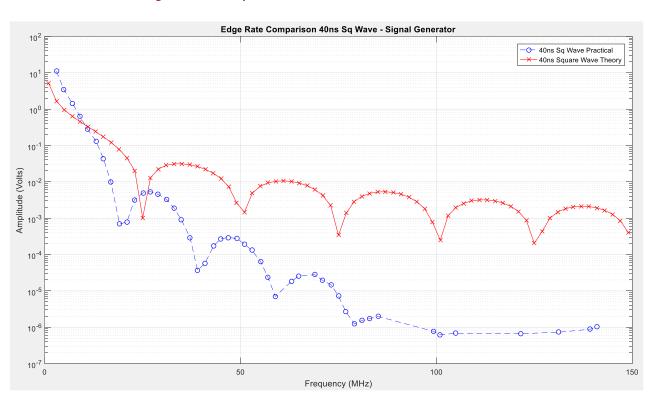

| Figure 50: 40ns Square Wave Practical & Theoretical Curves                              | 56   |

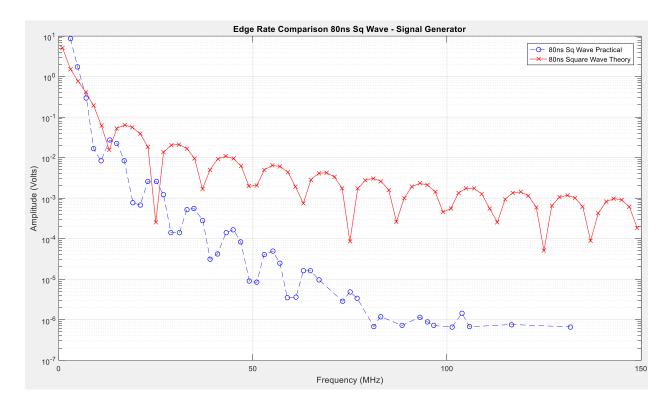

| Figure 51: 80ns Square Wave Practical & Theoretical Curves                              | 57   |

| Figure 52: Time & Frequency Domain Test Setup MSCR-001                                  | 60   |

| Figure 53: Time & Frequency Domain Test Setup Photograph                                | 60   |

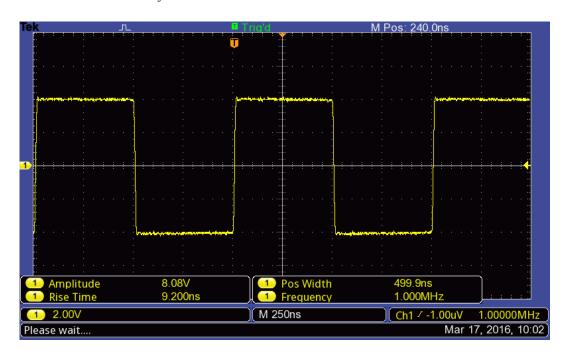

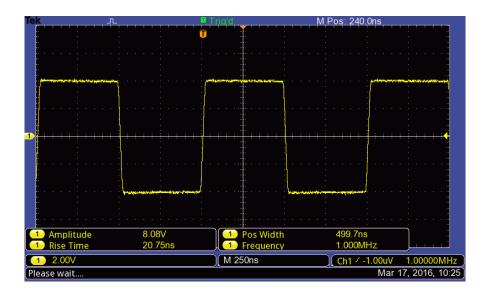

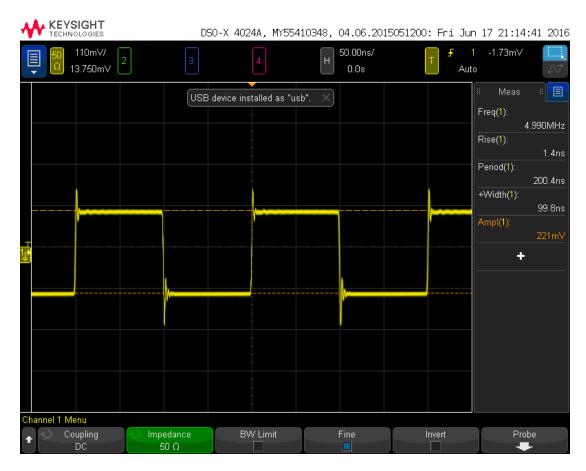

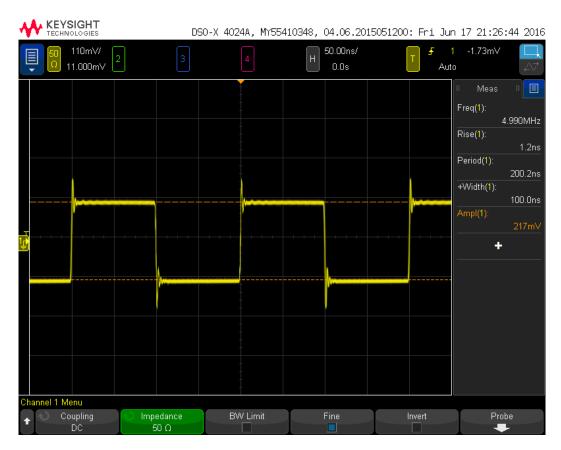

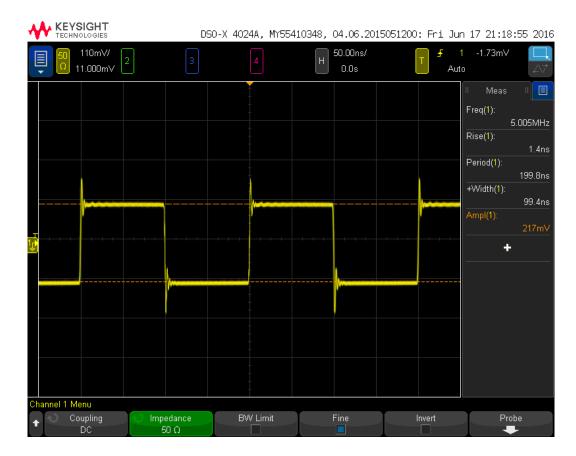

| Figure 54: LVTTL-24mA-Fast Time Domain Behaviour                                        | 62   |

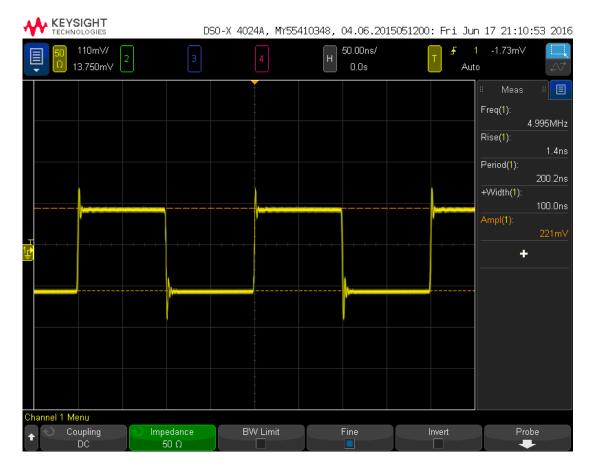

| Figure 55: LVTTL/24mA/Slow Time Domain Behaviour                                        | 63   |

| Figure 56: LVTTL/2mA/Fast Time Domain Behaviour                                         | 63   |

| Figure 57: LVTTL-2mA-Slow Time Domain Behaviour                                         | 64   |

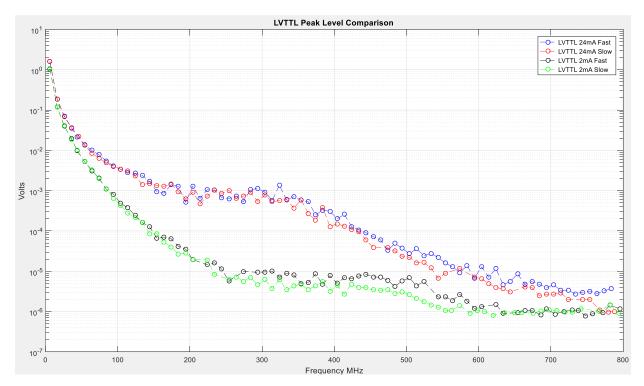

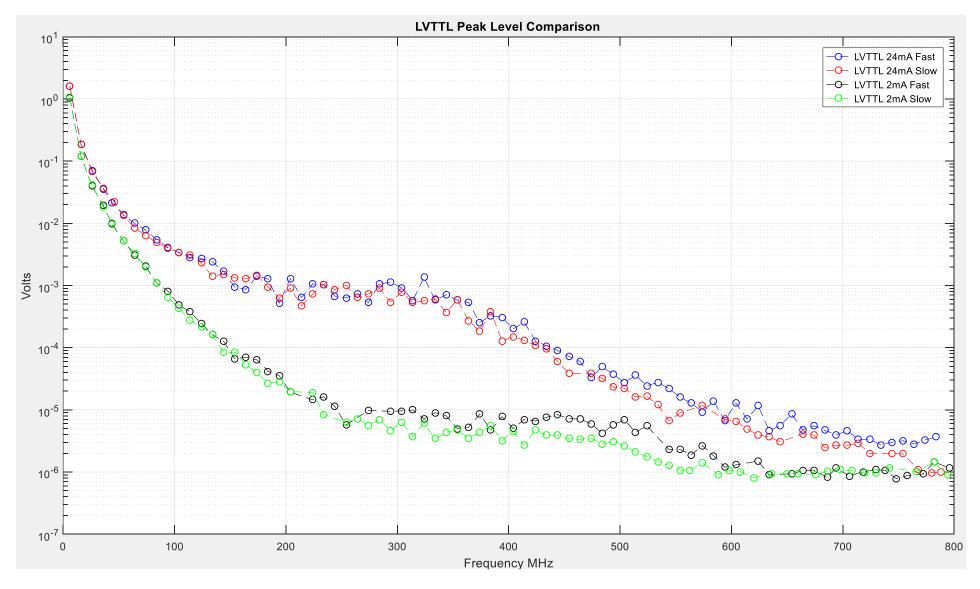

| Figure 58: Peak Level Comparison FPGA LVTTL Signals                                     | 65   |

| Figure 59: Peak Level Harmonic Comparison FPGA LVTTL Signals                            | 67   |

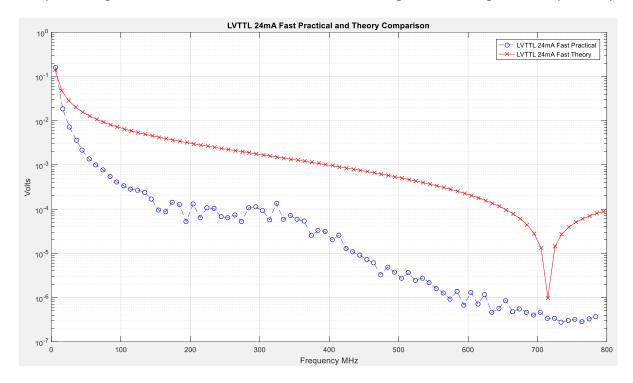

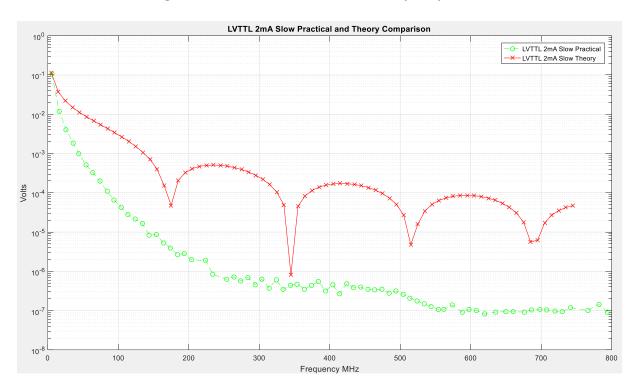

| Figure 60: LVTTL-24mA-Fast Practical v Theory Comparison                                | 68   |

| Figure 61: LVTTL-2mA-Slow Practical v Theory Comparison                                 | 68   |

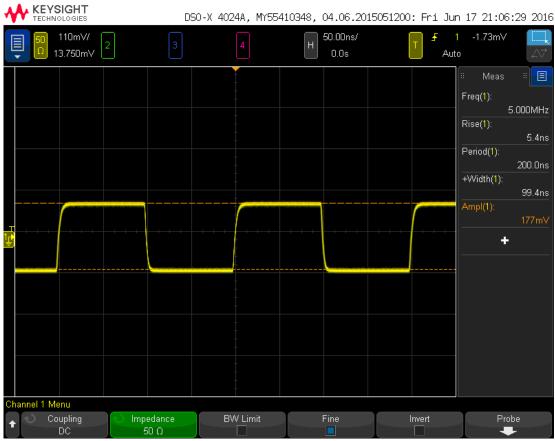

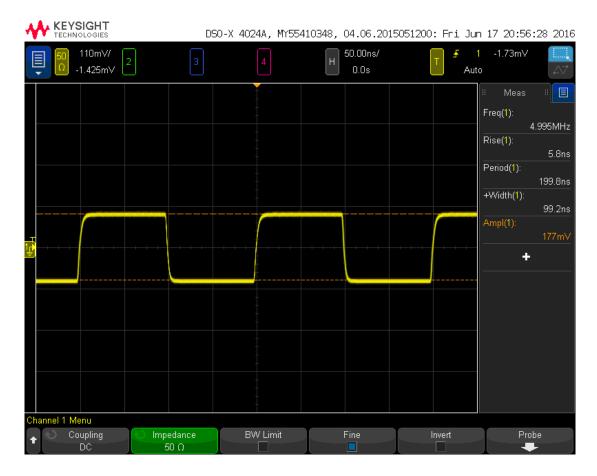

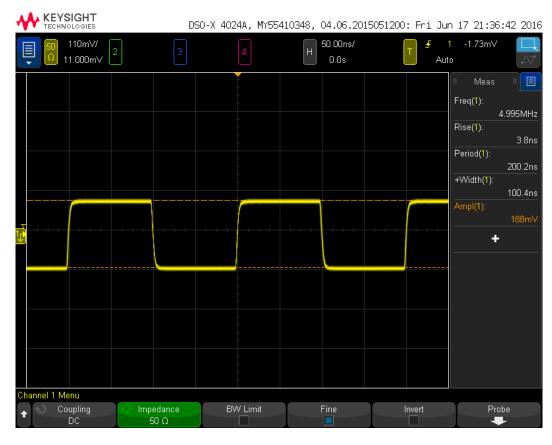

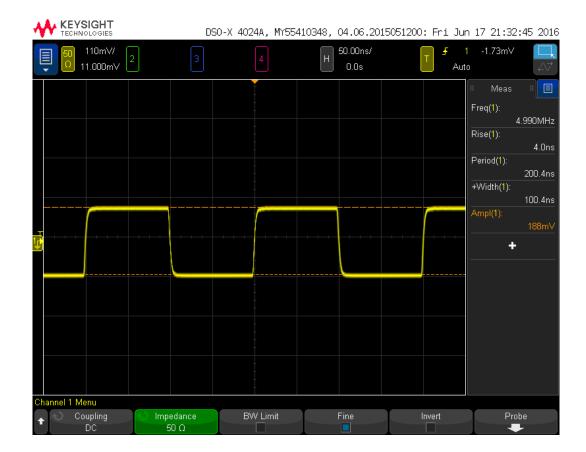

| Figure 62: LVCMOS33-24mA-Fast Time Domain Behaviour                                     | 69   |

| Figure 63: LVCMOS33-24mA-Slow Time Domain Behaviour                                     | 70   |

| Figure 64: LVCMOS33-2mA-Fast Time Domain Behaviour                                      | 70   |

| Figure 65: LVCMOS33-2mA-Slow Time Domain Behaviour                                      | 71   |

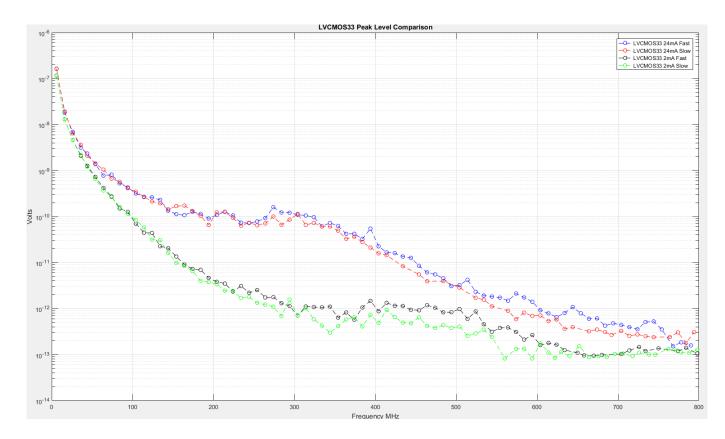

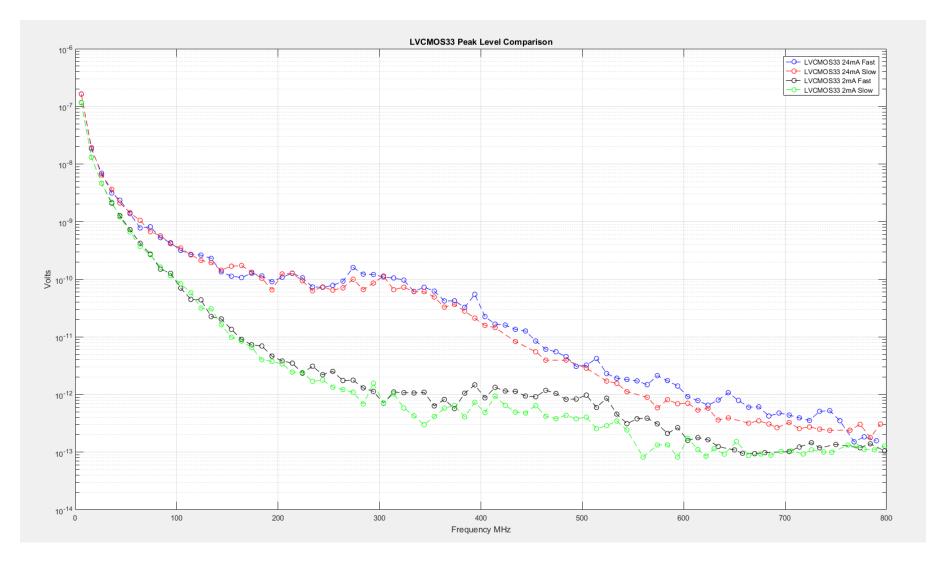

| Figure 66: Peak Level Harmonic Comparison FPGA LVCMOS33 Signals                         | 72   |

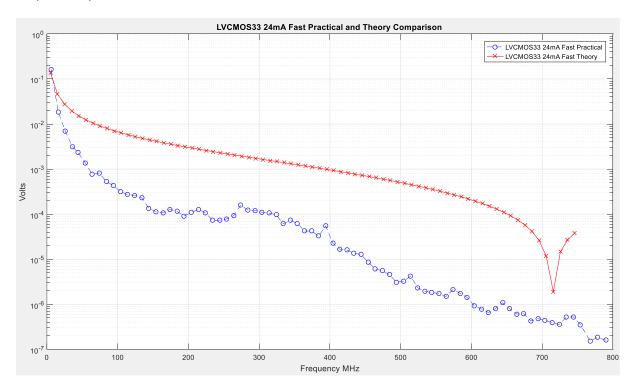

| Figure 67: LVCMOS33-24mA-Fast Practical v Theory Comparison                             | 73   |

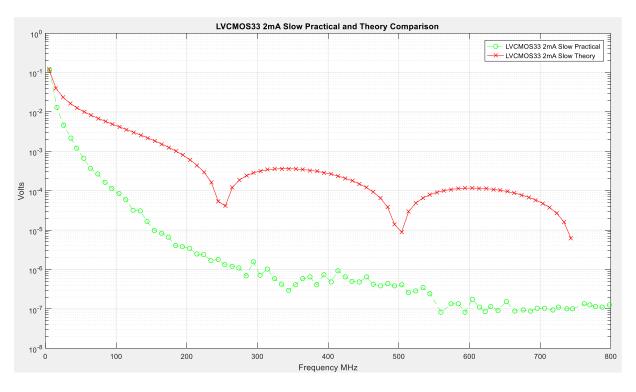

| Figure 68: LVCMOS33-2mA-Slow Practical v Theory Comparison                              | 73   |

| Figure 69: Peak Level Harmonics Comparison FPGA LVCMOS33 Signals                        | 75   |

| Figure 70: Radiated Emissions Test Setup                                                | 76   |

| Figure 71: Radiated Emissions Testing Photograph                                        | 76   |

| Figure 72: Radiated Emissions Cicuitry                                                  | 78   |

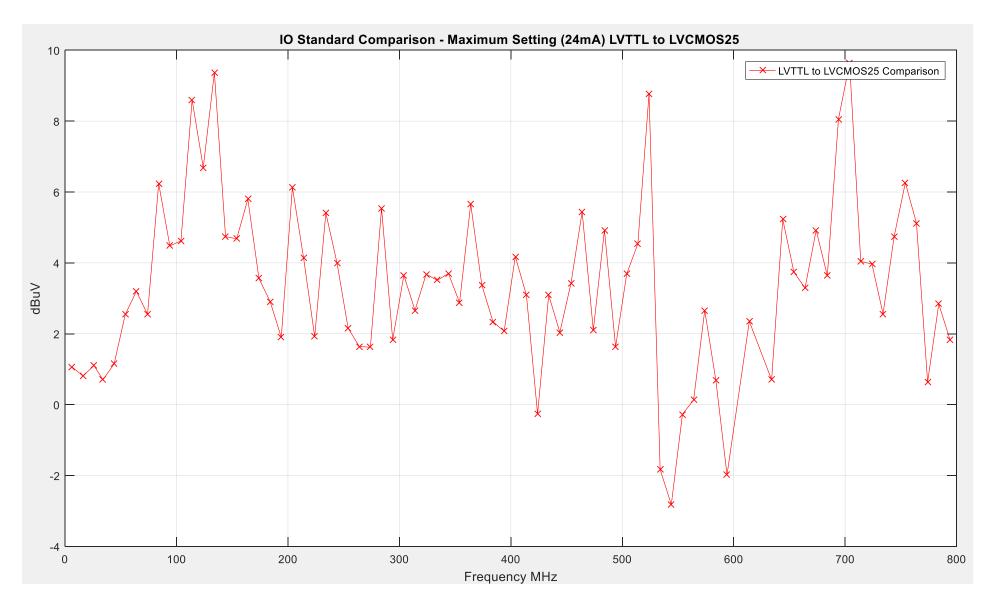

| Figure 73: Logic Standard Testing - Maximum Setting Radiated Emissions Comparison       | 81   |

| Figure 74: Logic Standard Comparison (Max Setting) - Peak Harmonic Difference I/O (LVTT | L to |

| LVCMOS33)                                                                               | 84   |

| Figure 75: Logic Standard Comparison (Max Setting) - Peak Harmonic Difference I/O (LVTT | L to |

| LVCMO25)                                                                                | 85   |

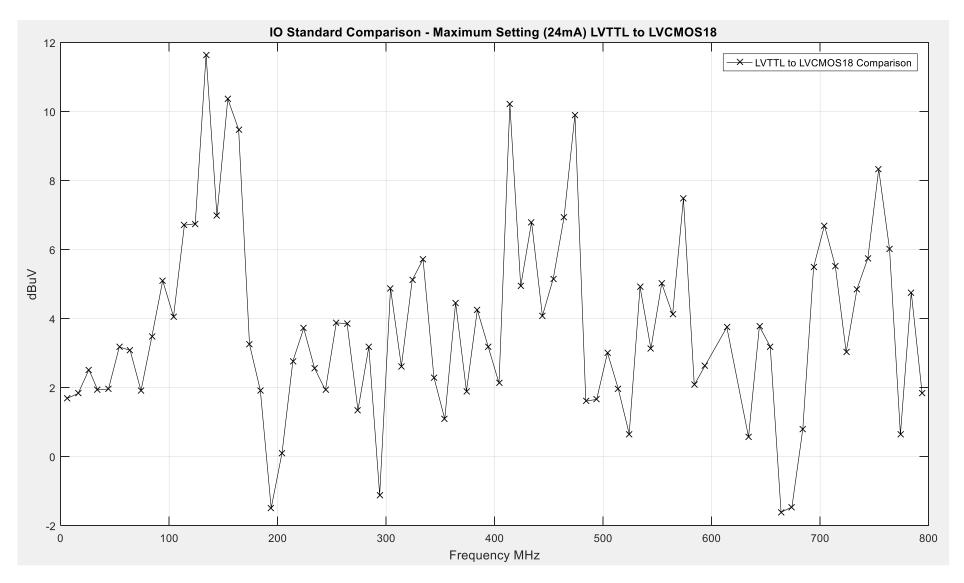

| Figure 76: Logic Standard Comparison (Max Setting) - Peak Harmonic Difference I/O (LVTT | L to |

| LVCMOS18)                                                                               | 86   |

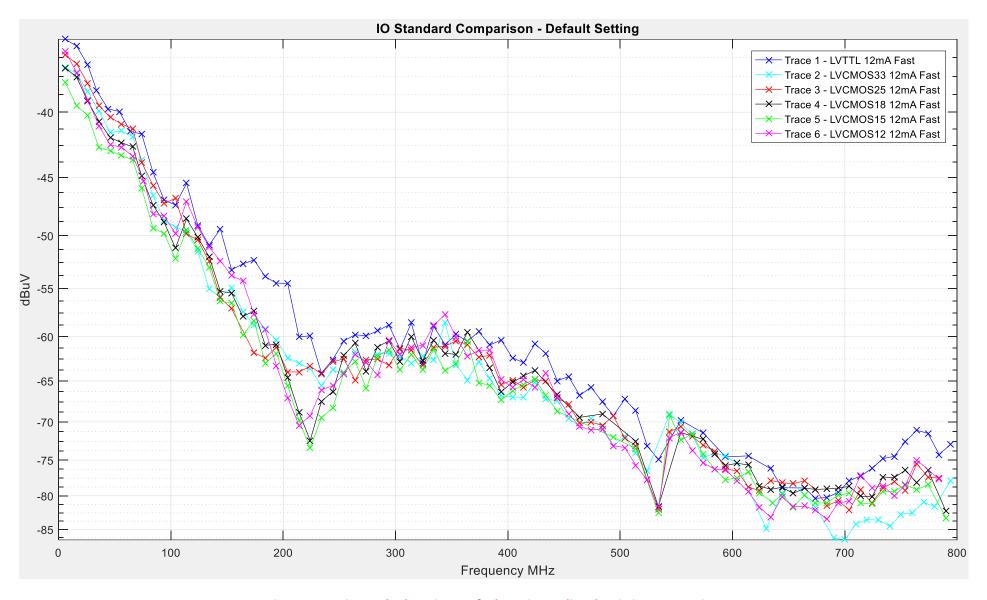

| Figure 77: Logic Standard Testing - Default Setting Radiated Emissions Comparison       | 88   |

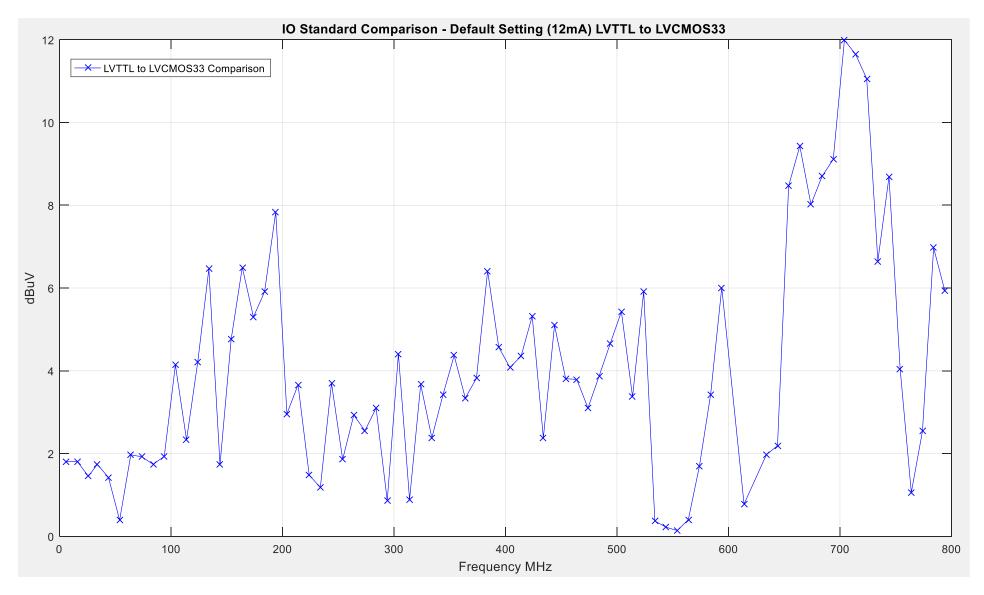

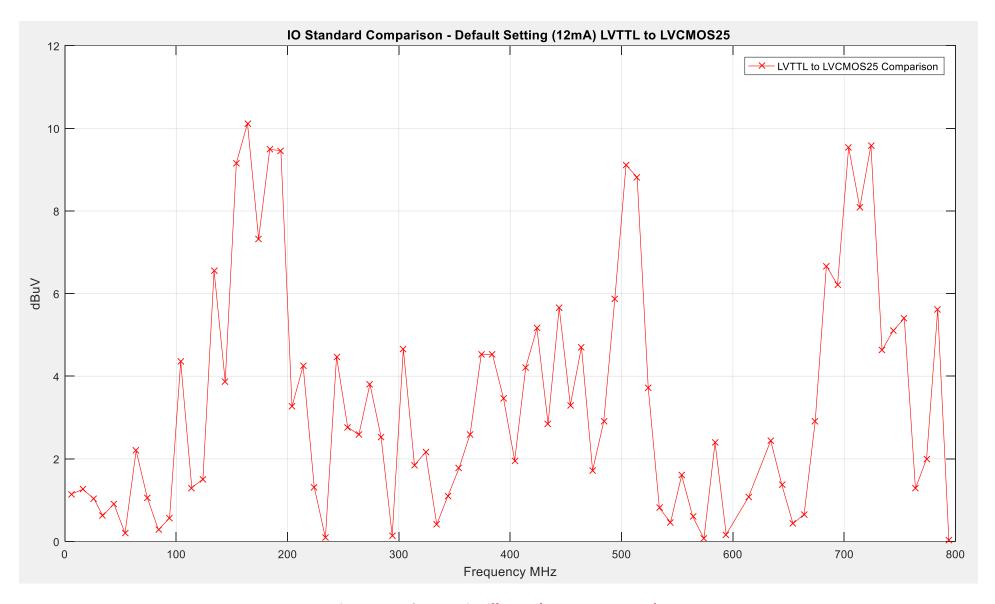

| Figure 78: Peak Harmonic Difference (LVTTL to LVCMOS33)                                 | 91   |

| Figure 79: Peak Harmonic Difference (LVTTL to LVCMOS25)                                 | 92   |

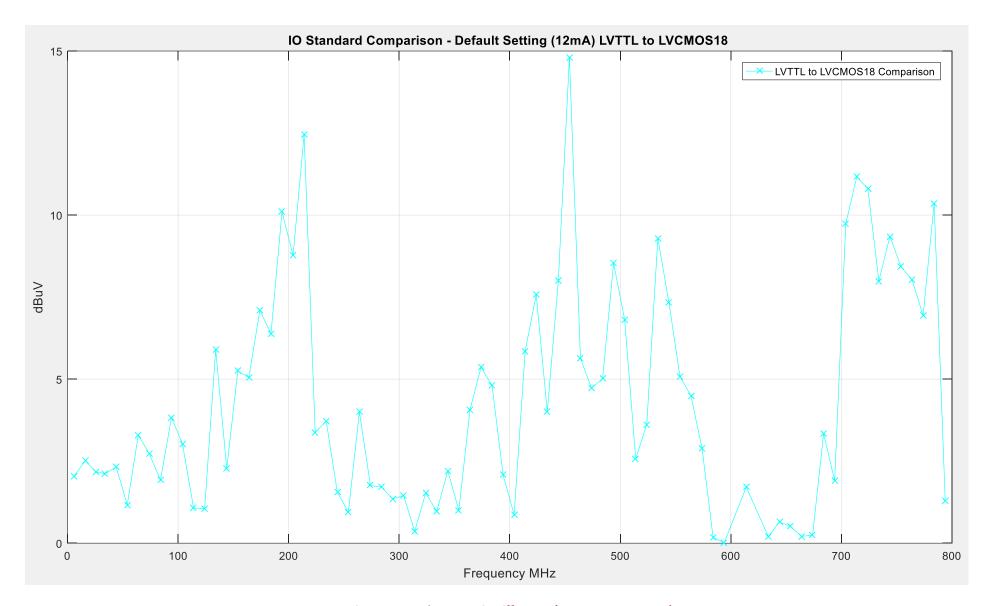

| Figure 80: Peak Harmonic Difference (LVTTL to LVCMOS18)                           | 93   |

|-----------------------------------------------------------------------------------|------|

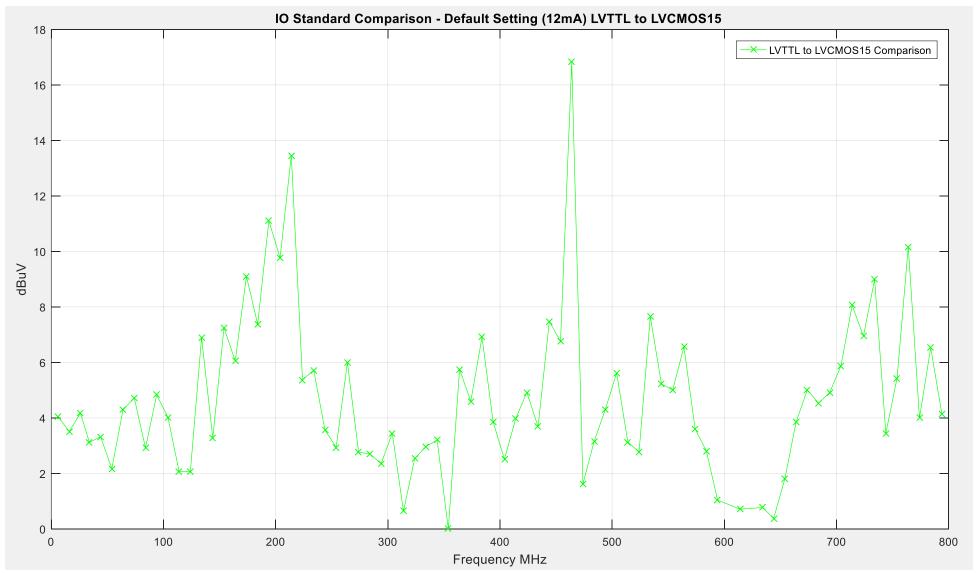

| Figure 81: Peak Harmonic Difference (LVTTL to LVCMOS15)                           | 94   |

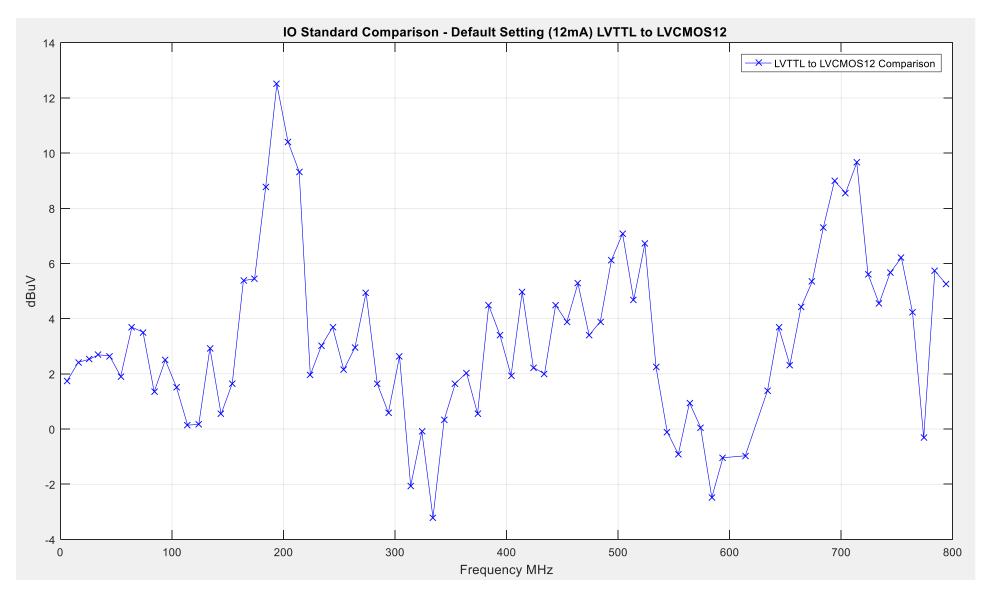

| Figure 82: Peak Harmonic Difference (LVTTL to LVCMOS12)                           | 95   |

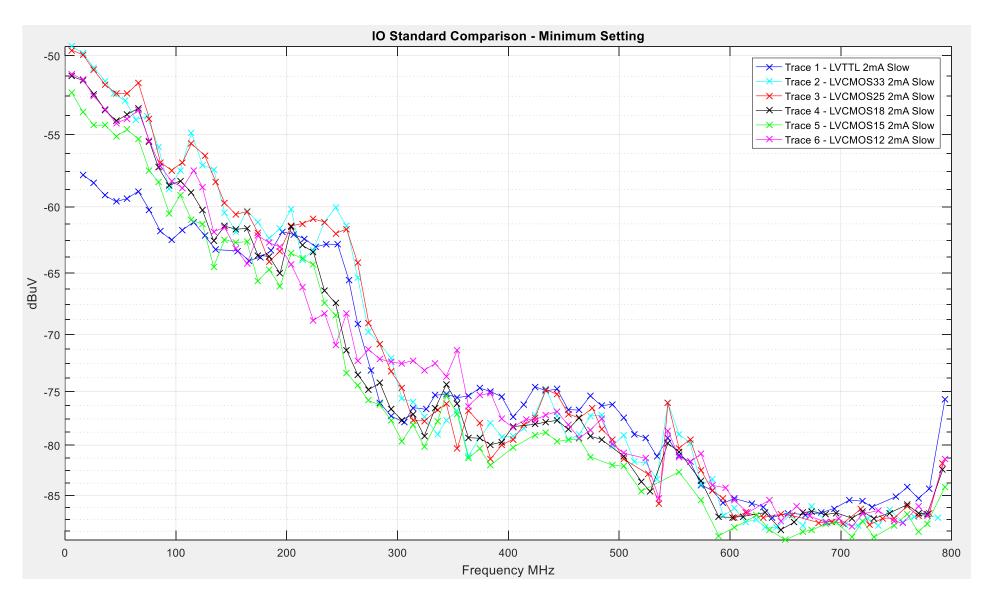

| Figure 83: Logic Standard Testing - Minimum Setting Radiated Emissions Comparison | 97   |

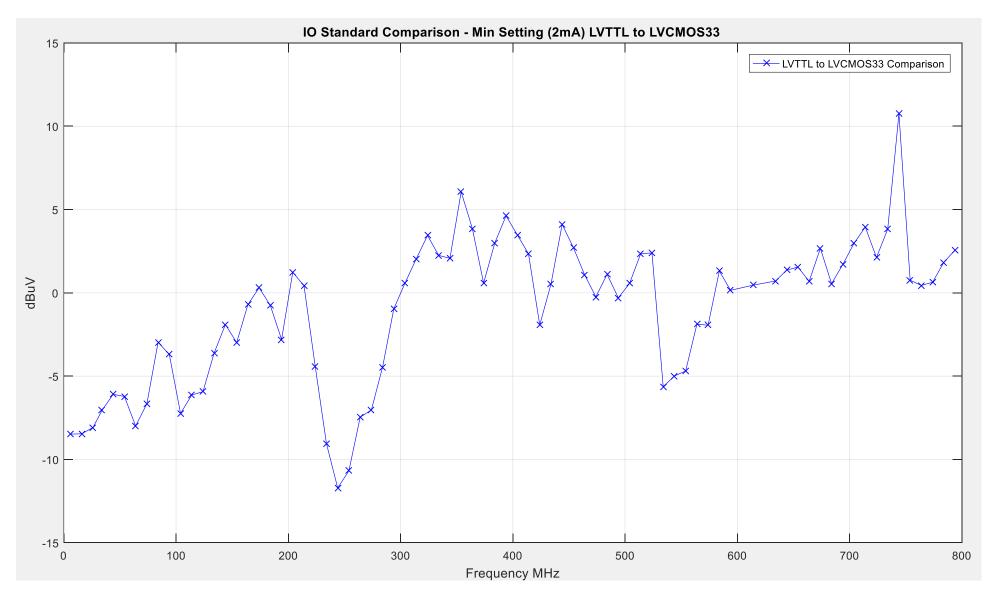

| Figure 84: Peak Harmonic Difference (LVTTL to LVCMOS33)                           | 100  |

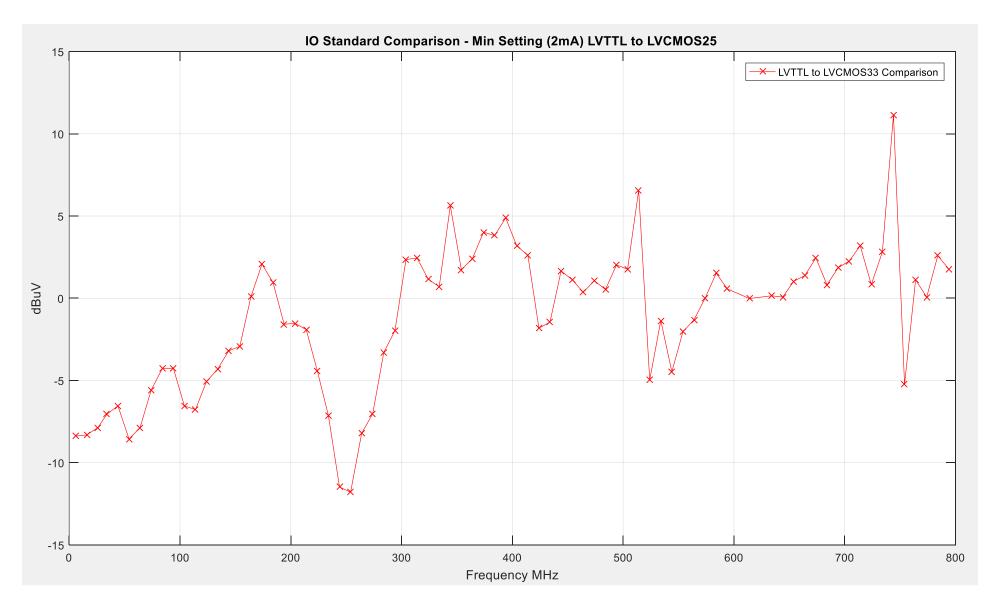

| Figure 85: Peak Harmonic Difference (LVTTL to LVCMOS25)                           | 101  |

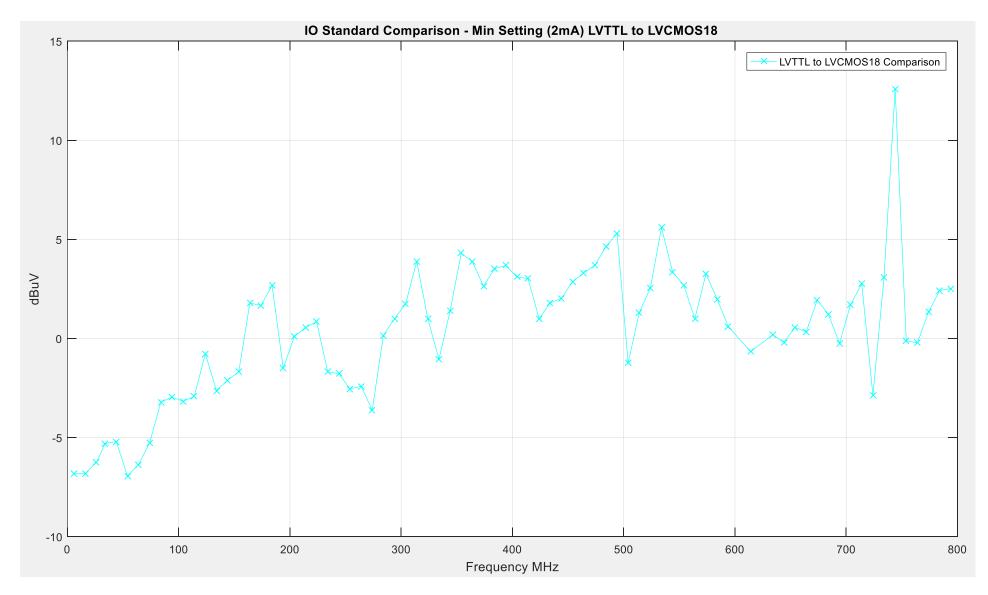

| Figure 86: Peak Harmonic Difference (LVTTL to LVCMOS18)                           | 102  |

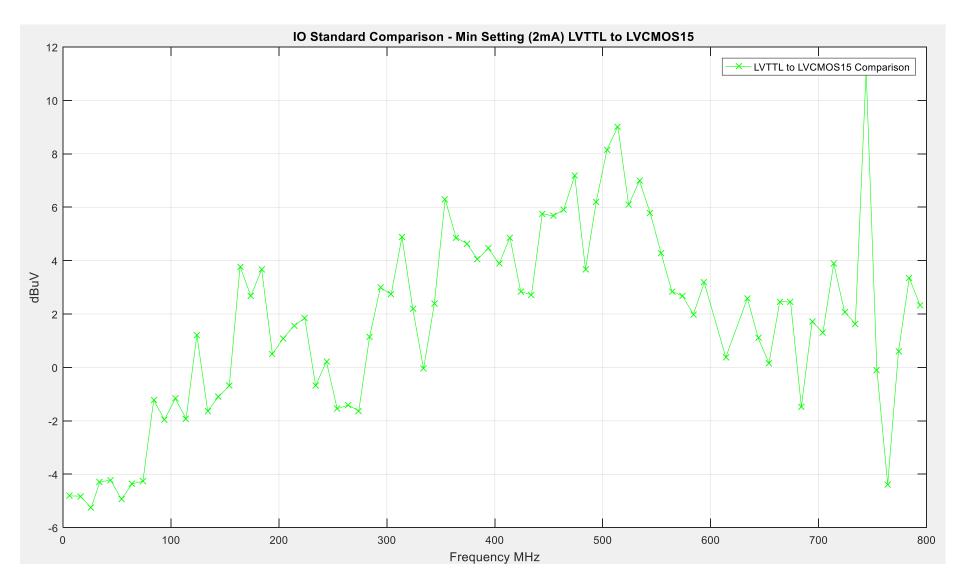

| Figure 87: Peak Harmonic Difference (LVTTL to LVCMOS15)                           | 103  |

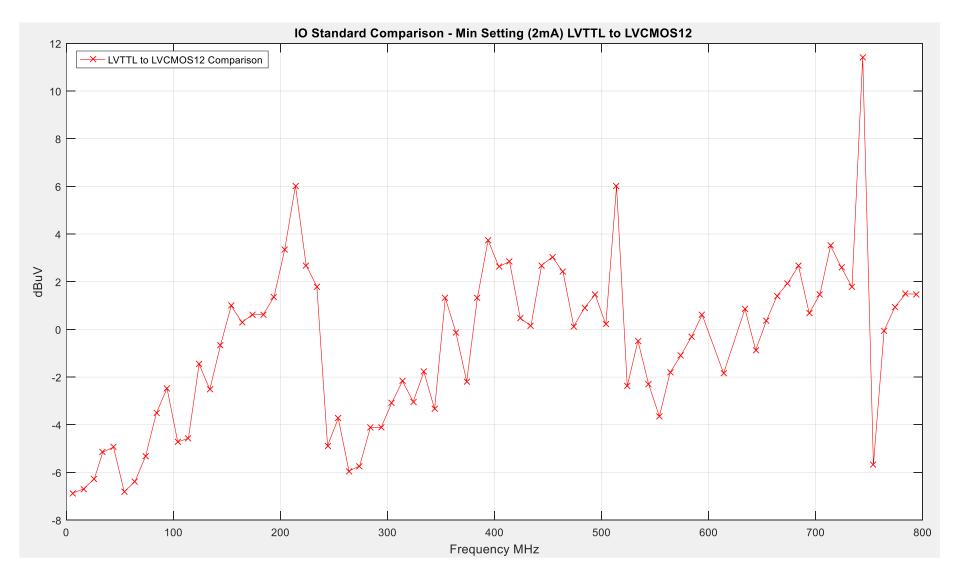

| Figure 88: Peak Harmonic Difference (LVTTL to LVCMOS12)                           | 104  |

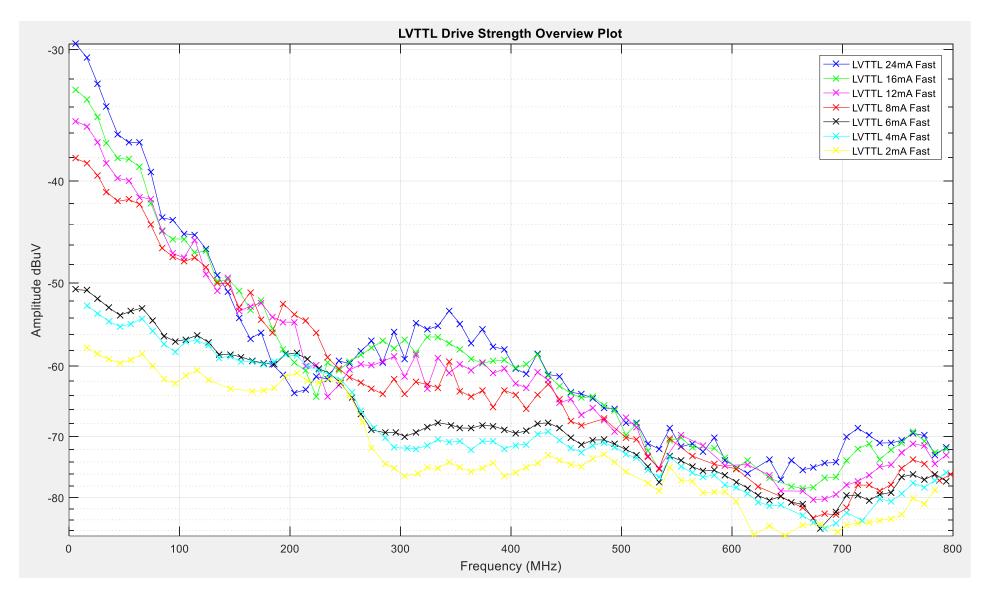

| Figure 89: LVTTL Drive Strength Overview Plot                                     |      |

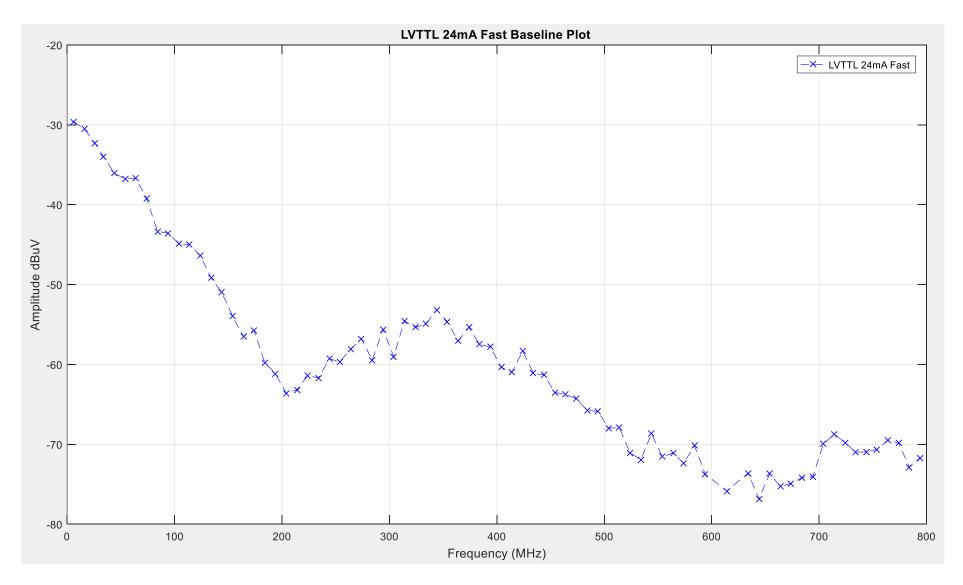

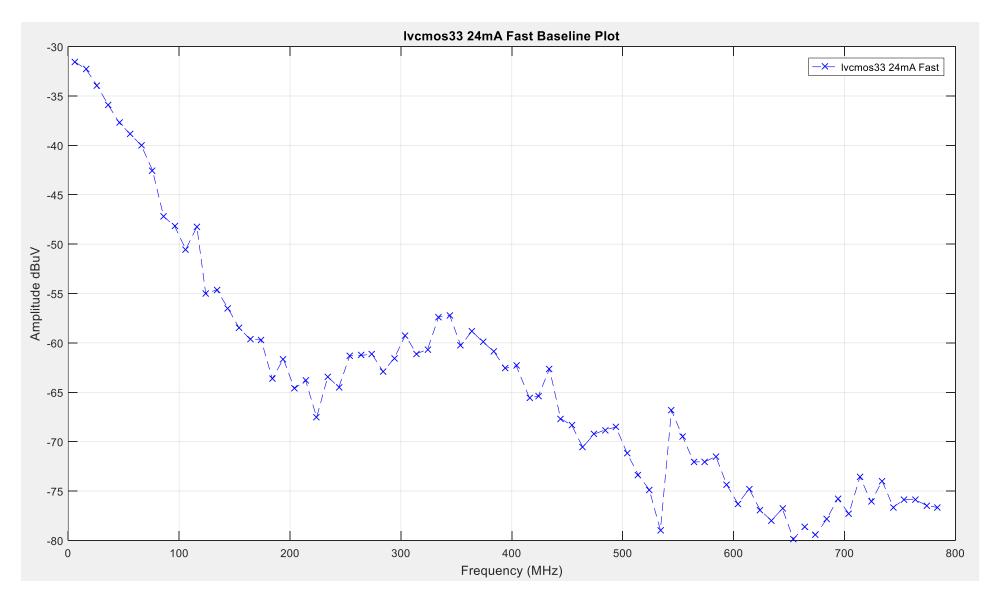

| Figure 90: LVTTL-24mA-Fast Drive Strength Baseline Plot                           | 112  |

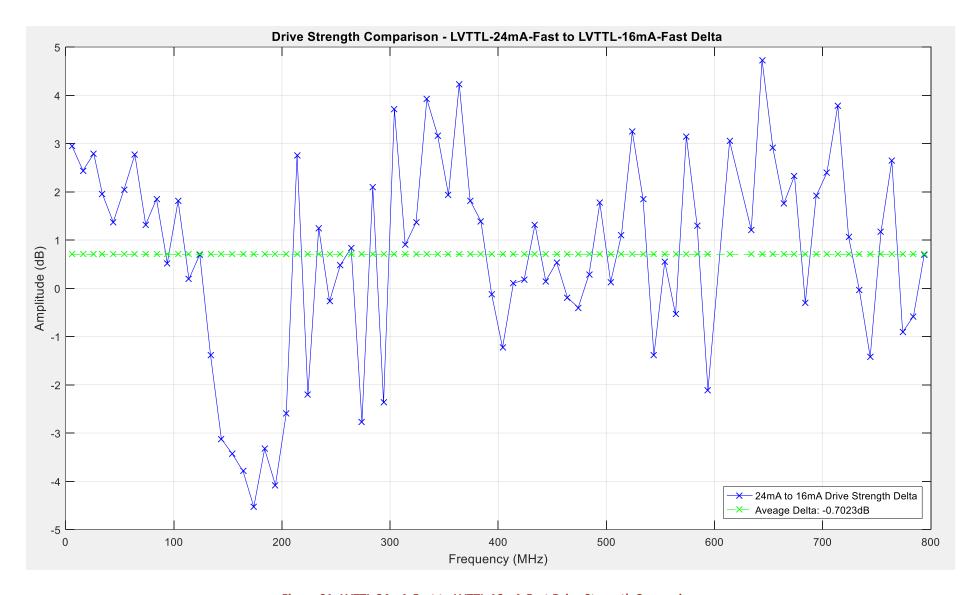

| Figure 91: LVTTL-24mA-Fast to LVTTL-16mA-Fast Drive Strength Comparison           |      |

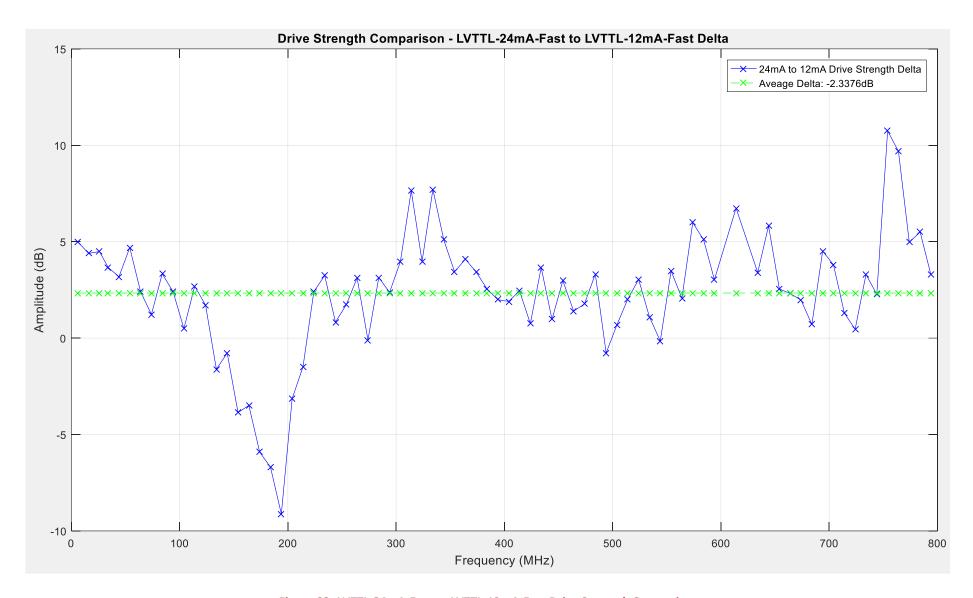

| Figure 92: LVTTL-24mA-Fast to LVTTL-12mA-Fast Drive Strength Comparison           | 114  |

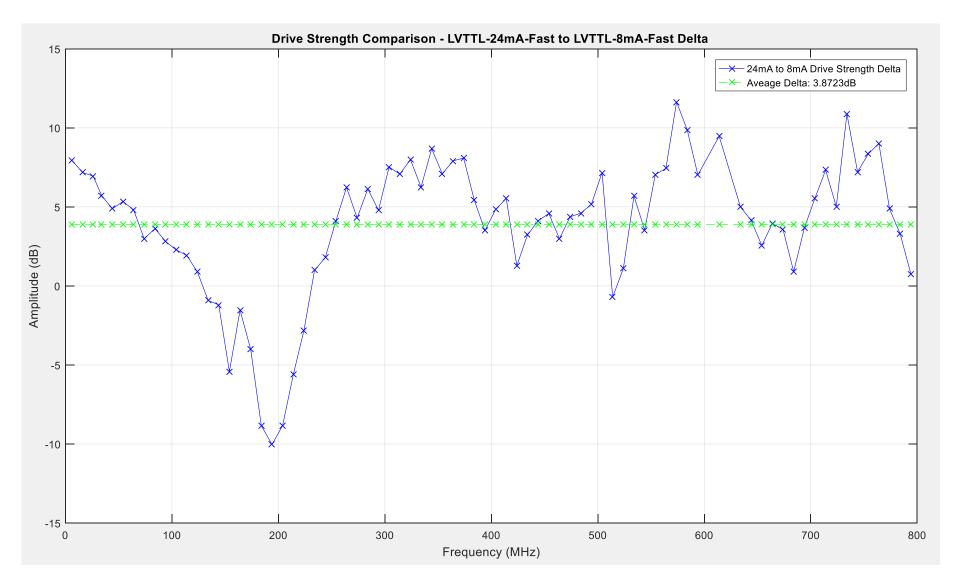

| Figure 93: LVTTL-24mA-Fast to LVTTL-8mA-Fast Drive Strength Comparison            | 115  |

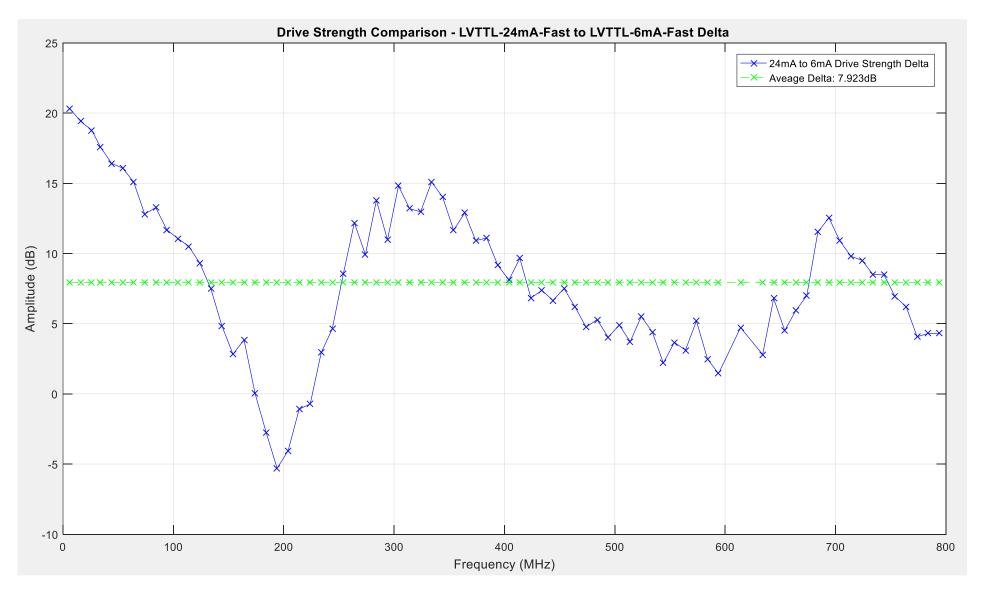

| Figure 94: LVTTL-24mA-Fast to LVTTL-6mA-Fast Drive Strength Comparison            | 116  |

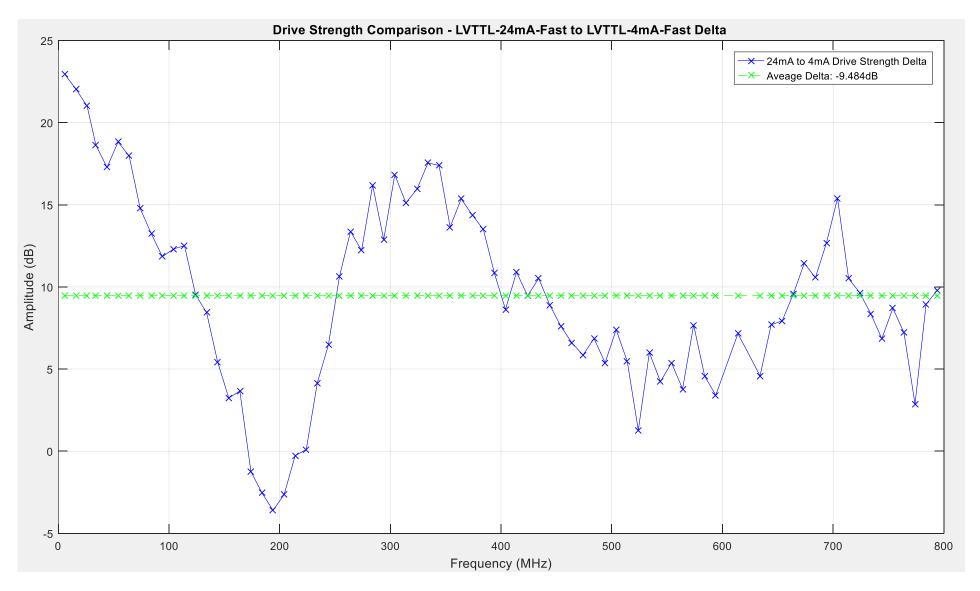

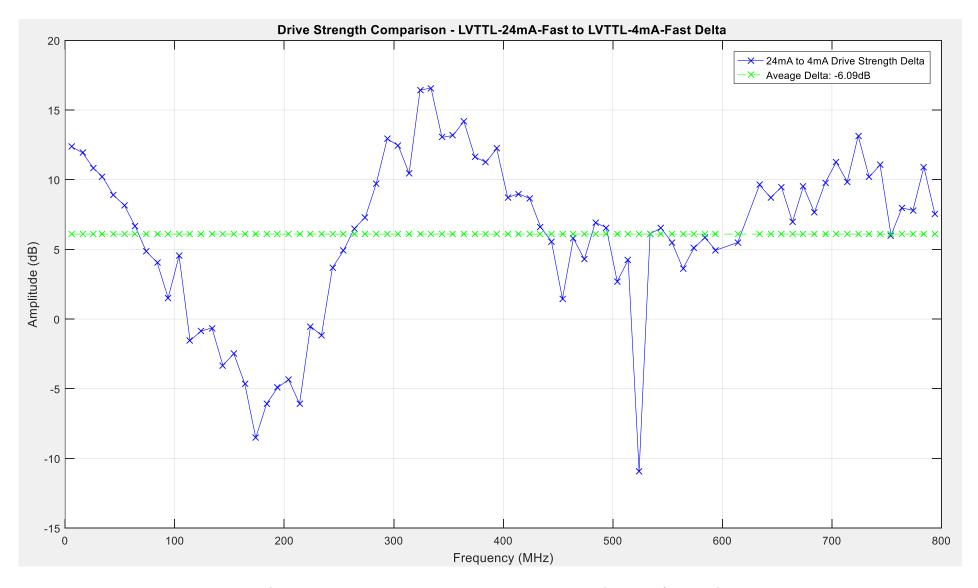

| Figure 95: LVTTL-24mA-Fast to LVTTL-4mA-Fast Drive Strength Comparison            | 117  |

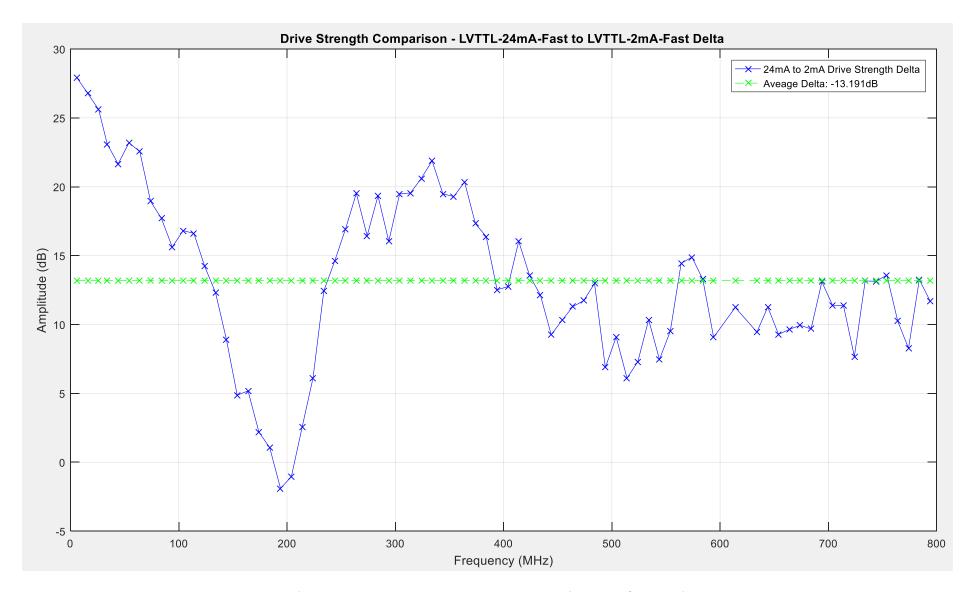

| Figure 96: LVTTL-24mA-Fast to LVTTL-2mA-Fast Drive Strength Comparison            | 118  |

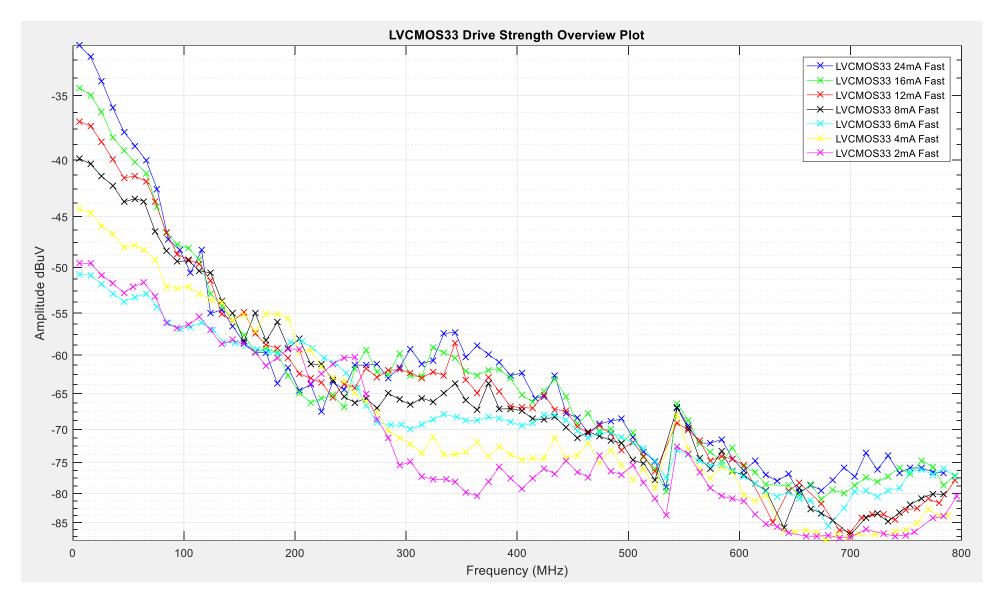

| Figure 97: LVCMOS33 Drive Strength Overview Plot                                  | 123  |

| Figure 98: LVCMOS33 Drive Strength Overview Plot                                  | 124  |

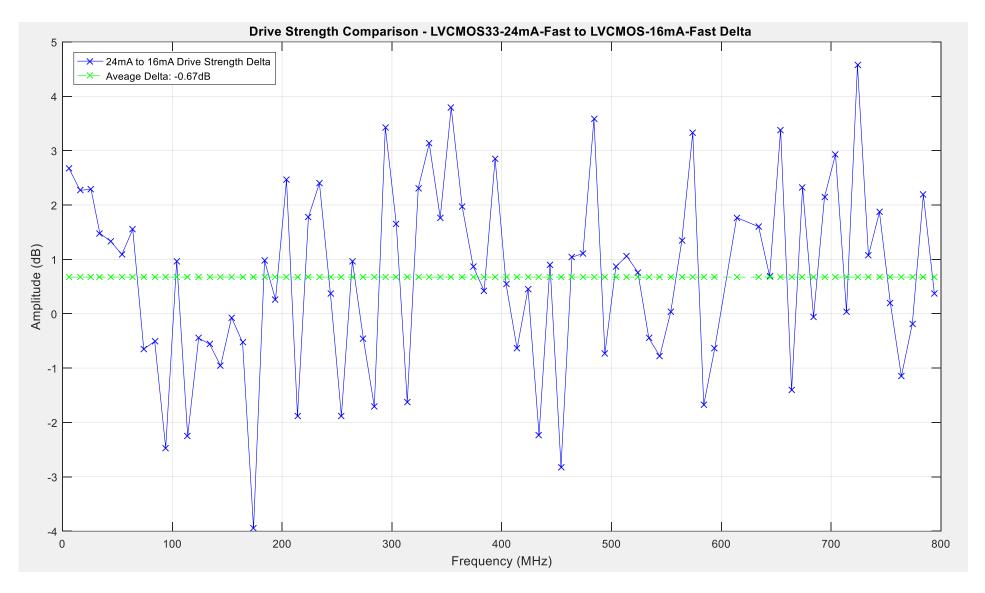

| Figure 99: LVCMOS33-24mA-Fast to LVCMOS33-16mA-Fast Drive Strength Comparison     | 125  |

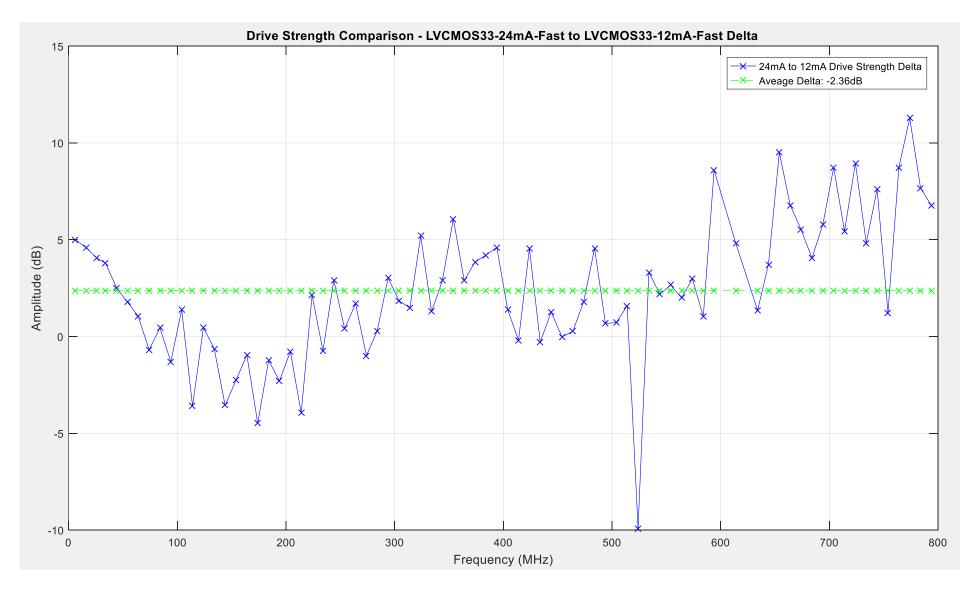

| Figure 100: LVCMOS33-24mA-Fast to LVCMOS33-12mA-Fast Drive Strength Comparison    | .126 |

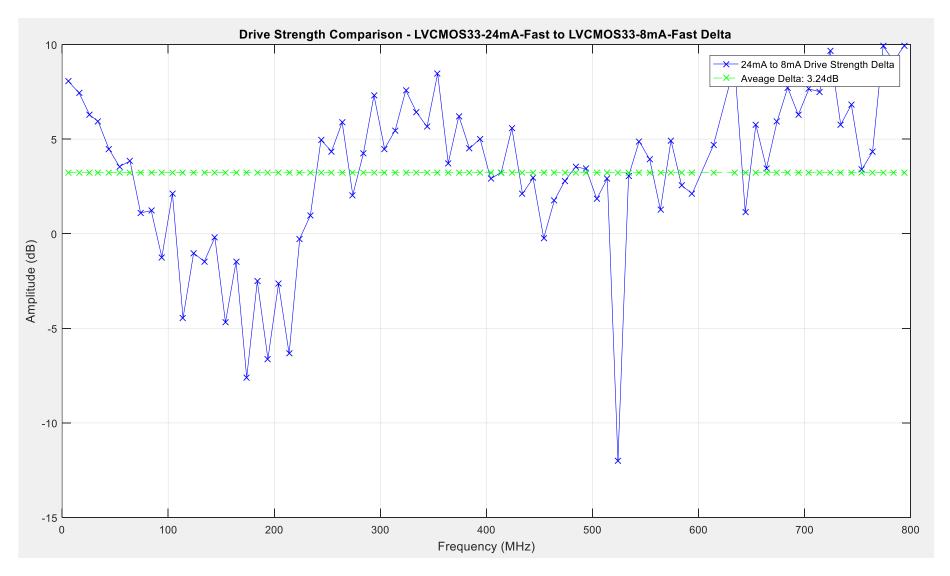

| Figure 101: LVCMOS33-24mA-Fast to LVCMOS33-8mA-Fast Drive Strength Comparison     | 127  |

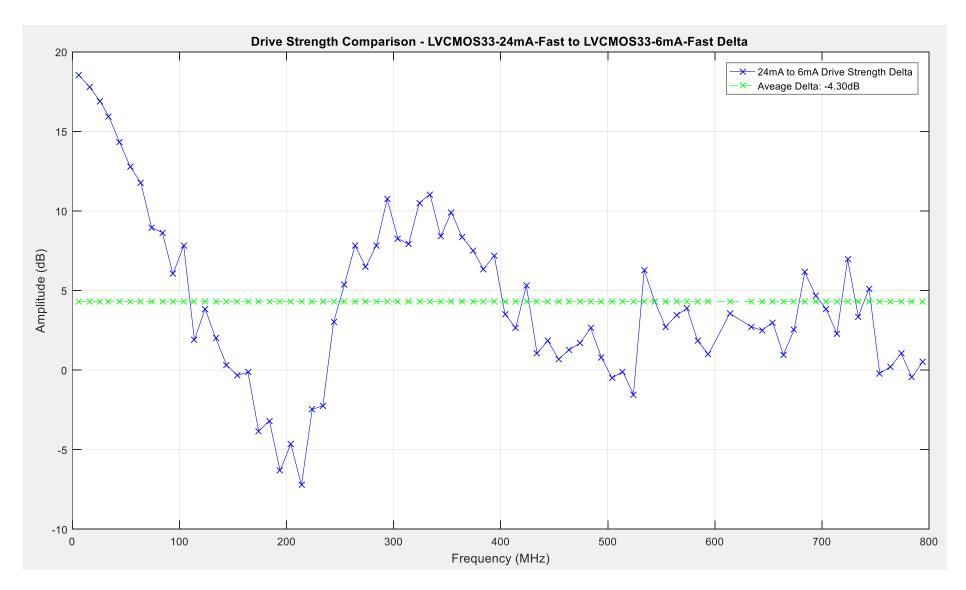

| Figure 102: LVCMOS33-24mA-Fast to LVCMOS33-6mA-Fast Drive Strength Comparison     | 128  |

| Figure 103: LVCMOS33-24mA-Fast to LVCMOS33-4mA-Fast Drive Strength Comparison     | 129  |

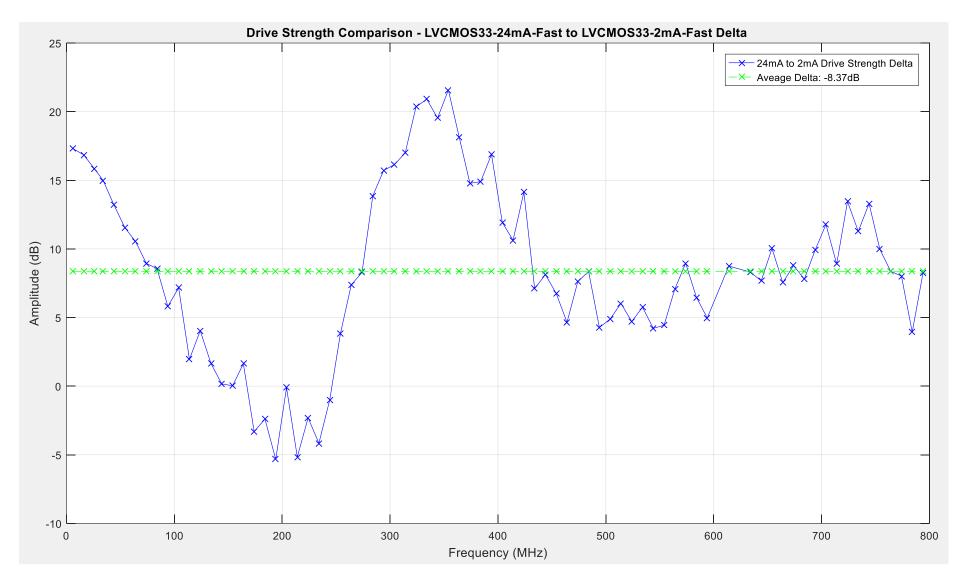

| Figure 104: LVCMOS33-24mA-Fast to LVCMOS33-2mA-Fast Drive Strength Comparison     | 130  |

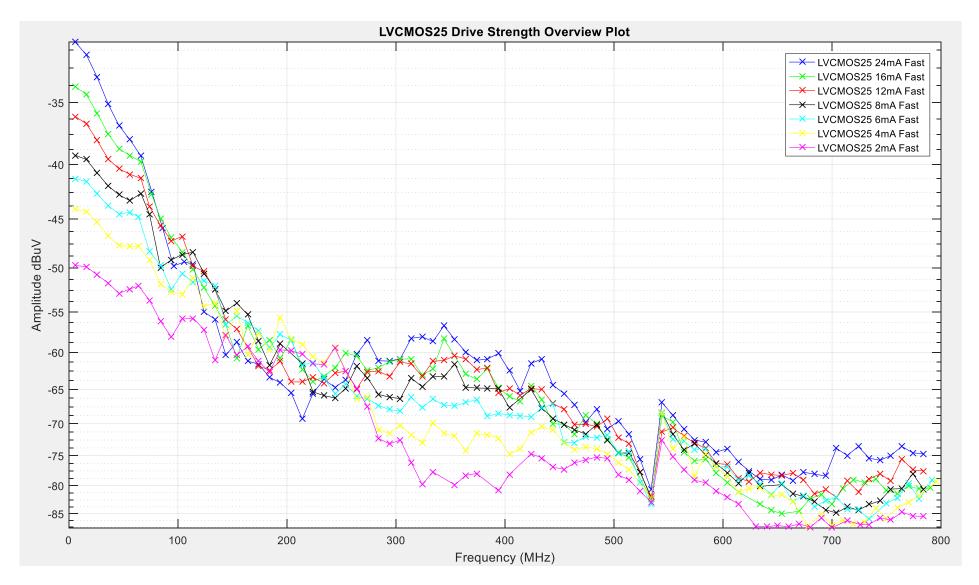

| Figure 105: LVCMOS25 Drive Strength Overview Plot                                 | 135  |

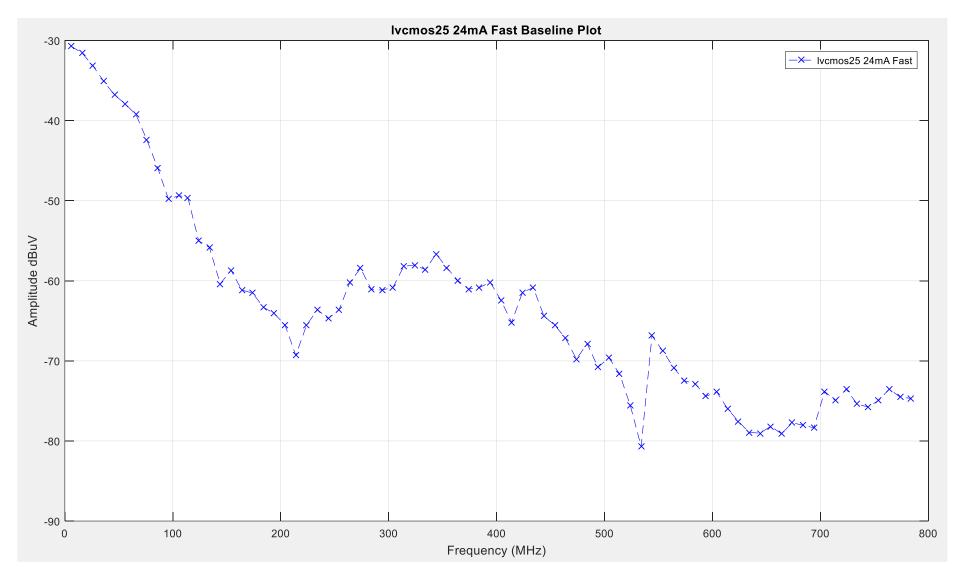

| Figure 106: LVCMOS25 Drive Strength Baseline Plot                                 | 136  |

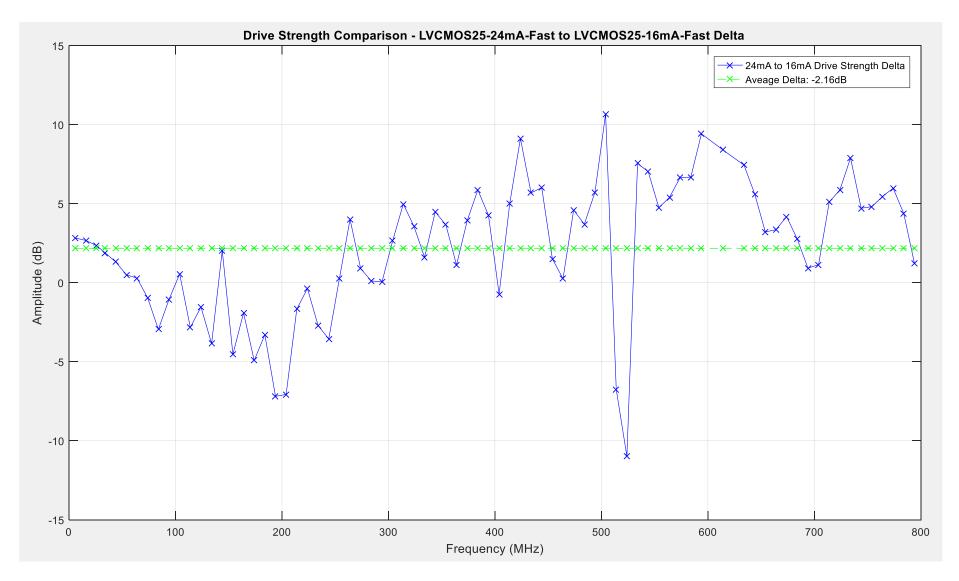

| Figure 107: LVCMOS25-24mA-Fast to LVCMOS25-16mA-Fast Drive Strength Comparison    | .137 |

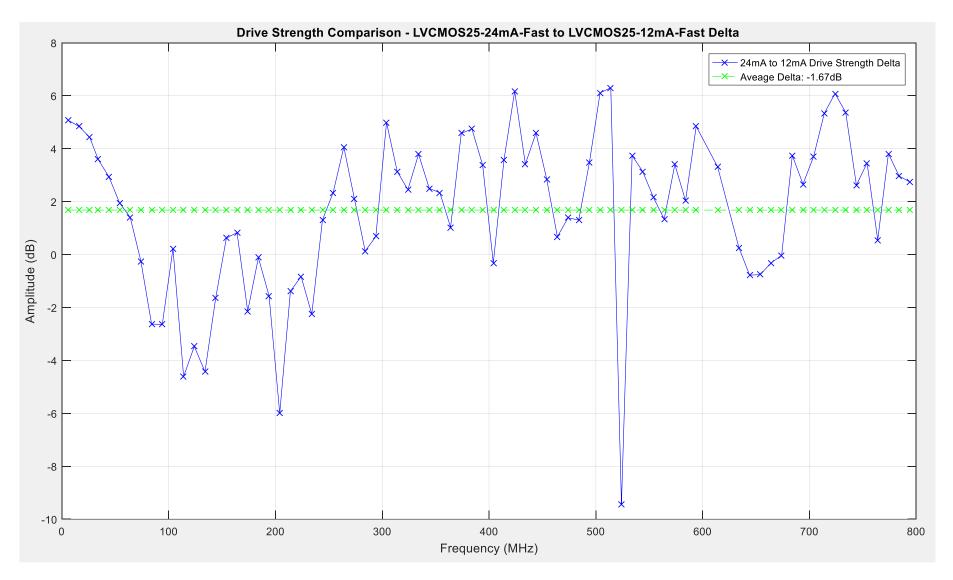

| Figure 108: LVCMOS25-24mA-Fast to LVCMOS25-12mA-Fast Drive Strength Comparison    | .138 |

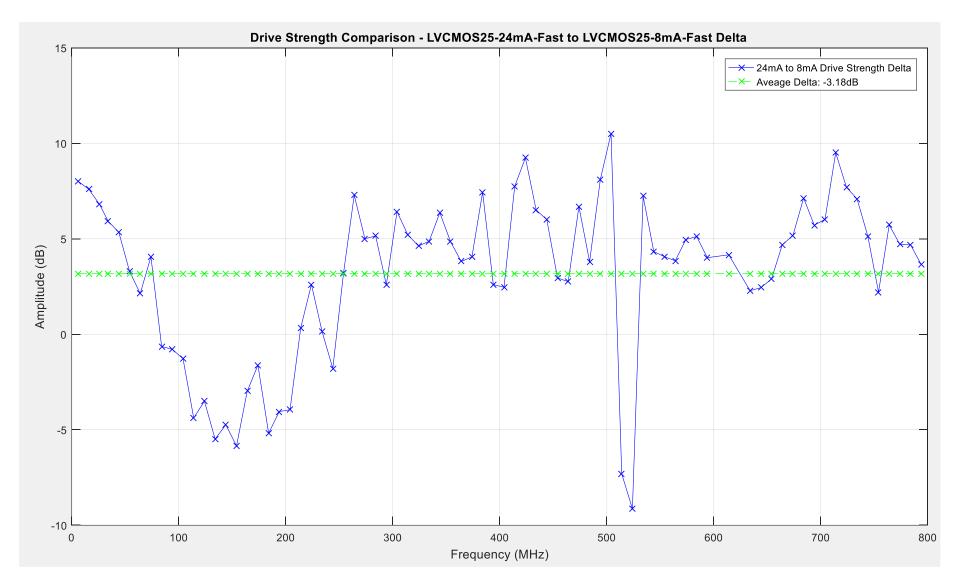

| Figure 109: LVCMOS25-24mA-Fast to LVCMOS25-8mA-Fast Drive Strength Comparison     | 139  |

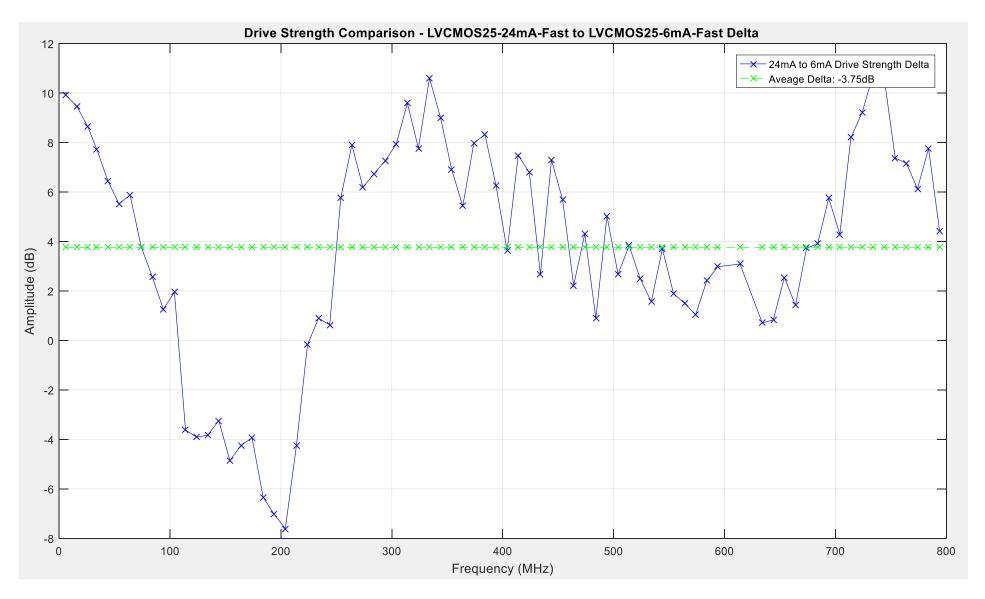

| Figure 110: LVCMOS25-24mA-Fast to LVCMOS25-6mA-Fast Drive Strength Comparison     | 140  |

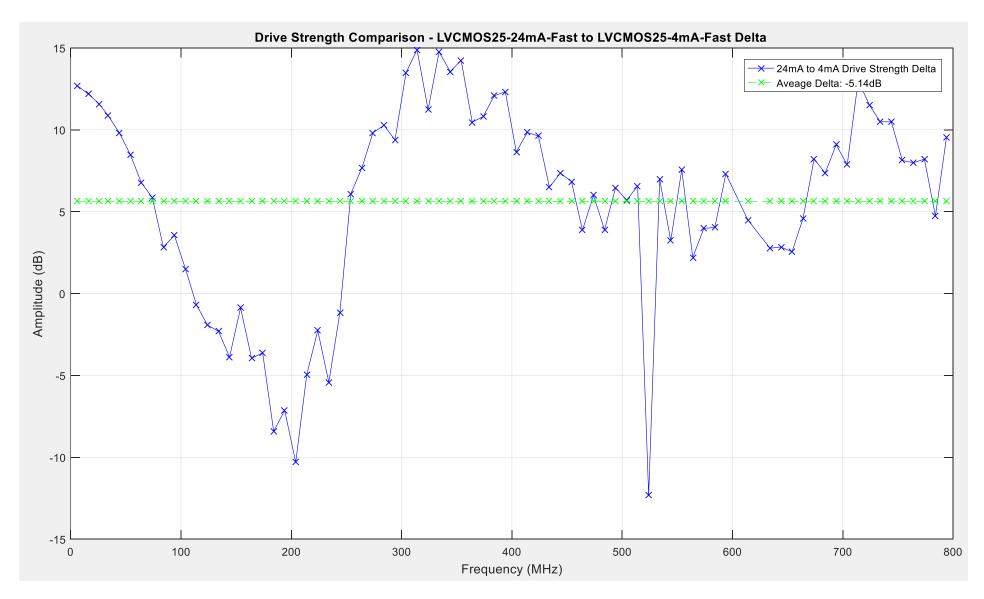

| Figure 111: LVCMOS25-24mA-Fast to LVCMOS25-4mA-Fast Drive Strength Comparison     | .141 |

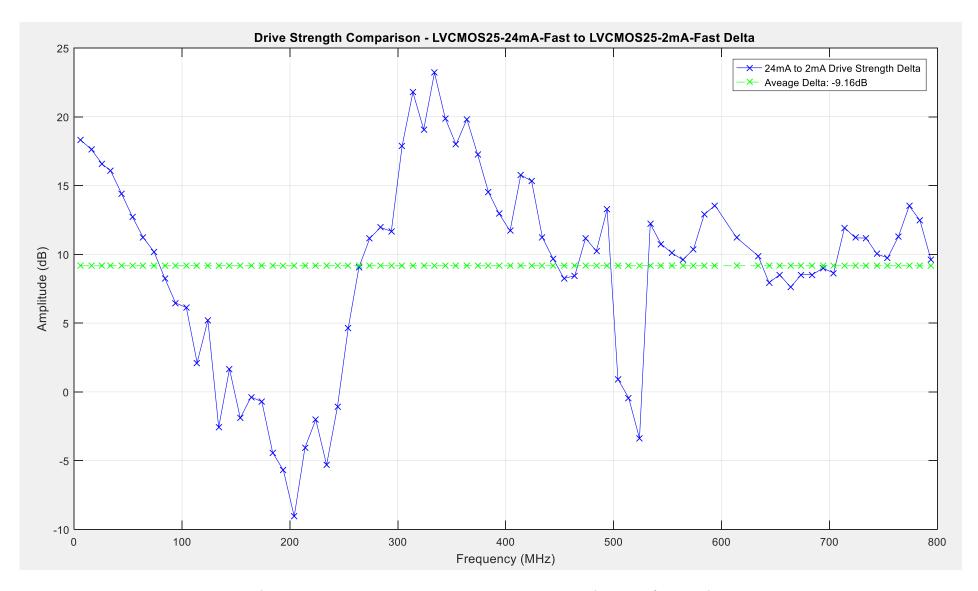

| Figure 112: LVCMOS25-24mA-Fast to LVCMOS25-2mA-Fast Drive Strength Comparison     | 142  |

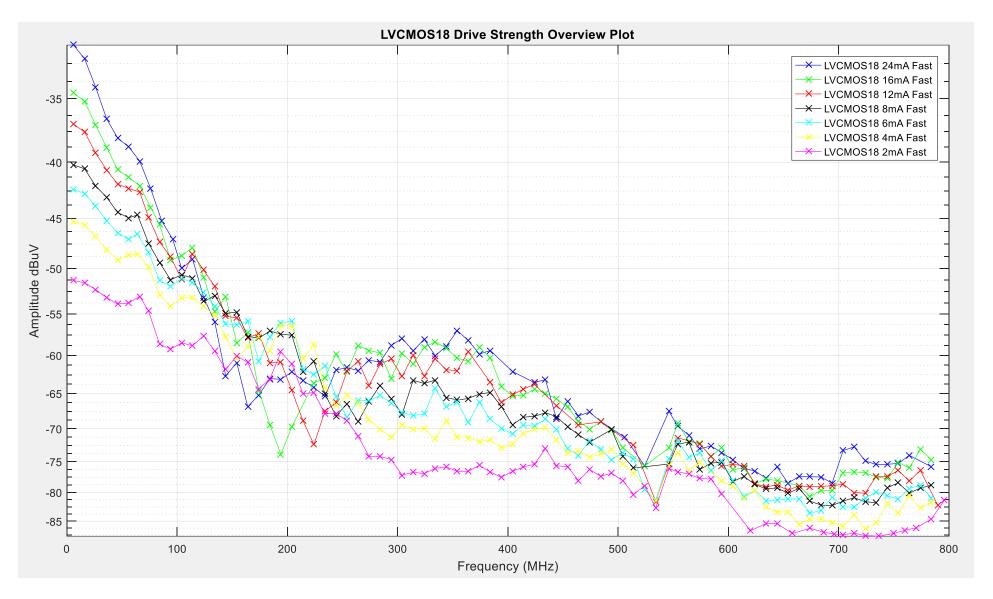

| Figure 113: LVCMOS18 Drive Strength Overview Plot                                 | .147 |

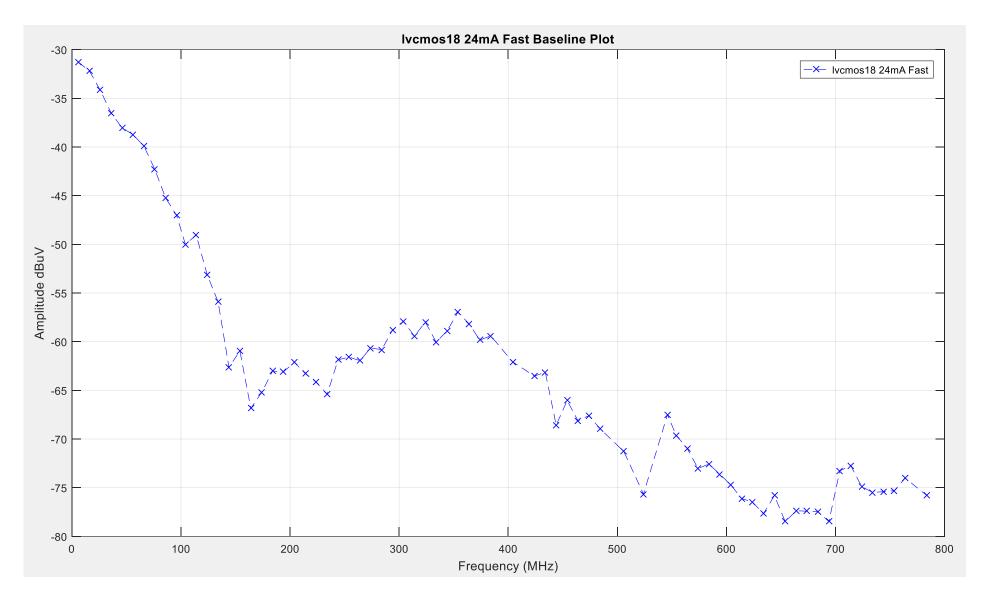

| Figure 114: LVCMOS18 Drive Strength Baseline Plot                                 | .148 |

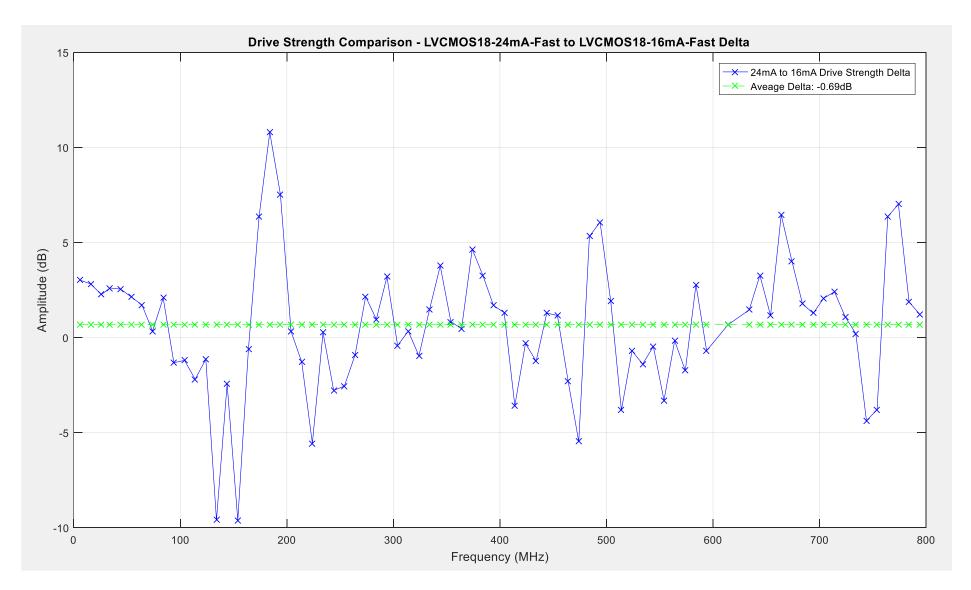

| Figure 115: LVCMOS18-24mA-Fast to LVCMOS18-16mA-Fast Drive Strength Comparison    | .149 |

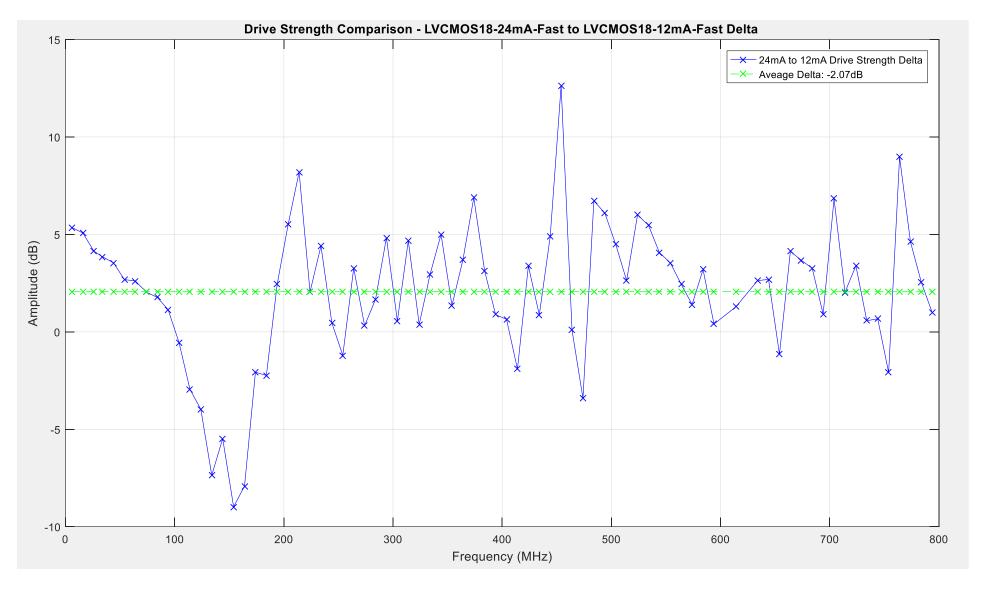

| Figure 116: LVCMOS18-24mA-Fast to LVCMOS18-12mA-Fast Drive Strength Comparison    | .150 |

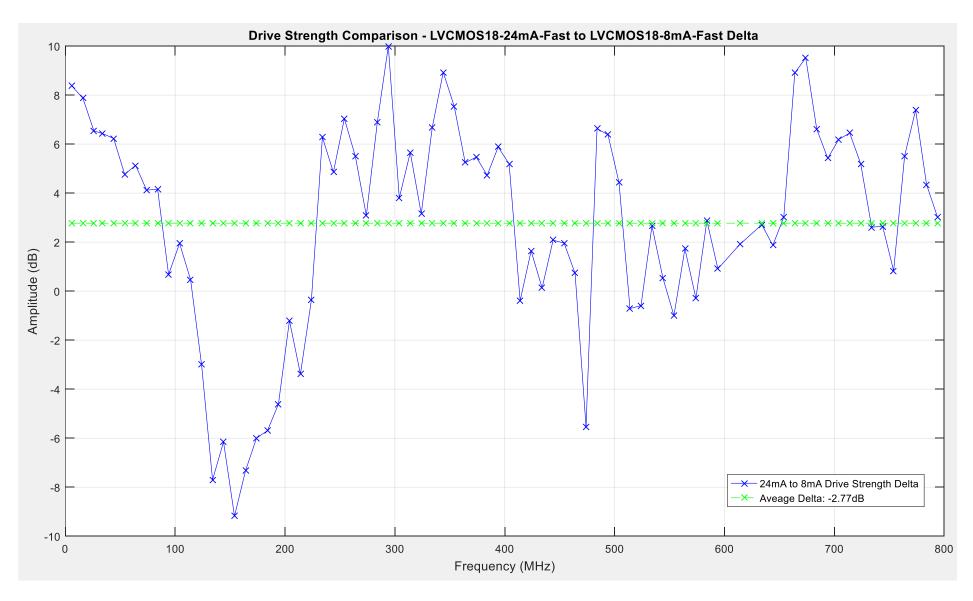

| Figure 117: LVCMOS18-24mA-Fast to LVCMOS18-8mA-Fast Drive Strength Comparison     | 151  |

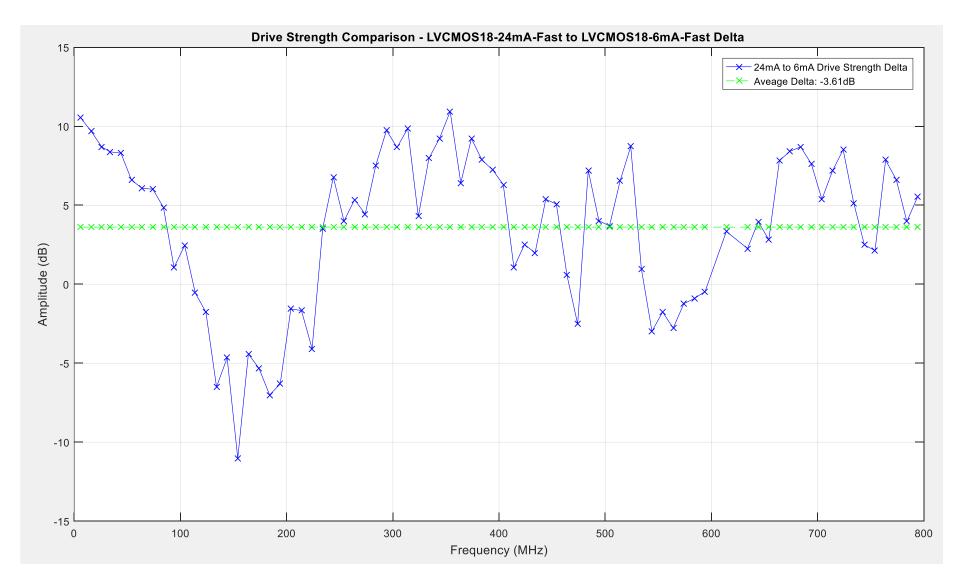

| Figure 118: LVCMOS18-24mA-Fast to LVCMOS18-6mA-Fast Drive Strength Comparison     | 152  |

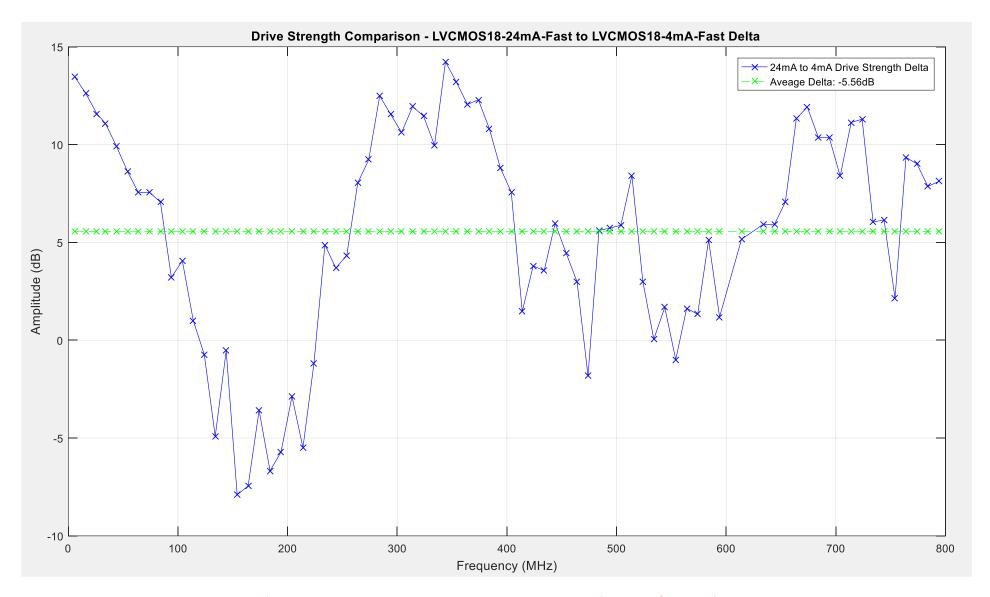

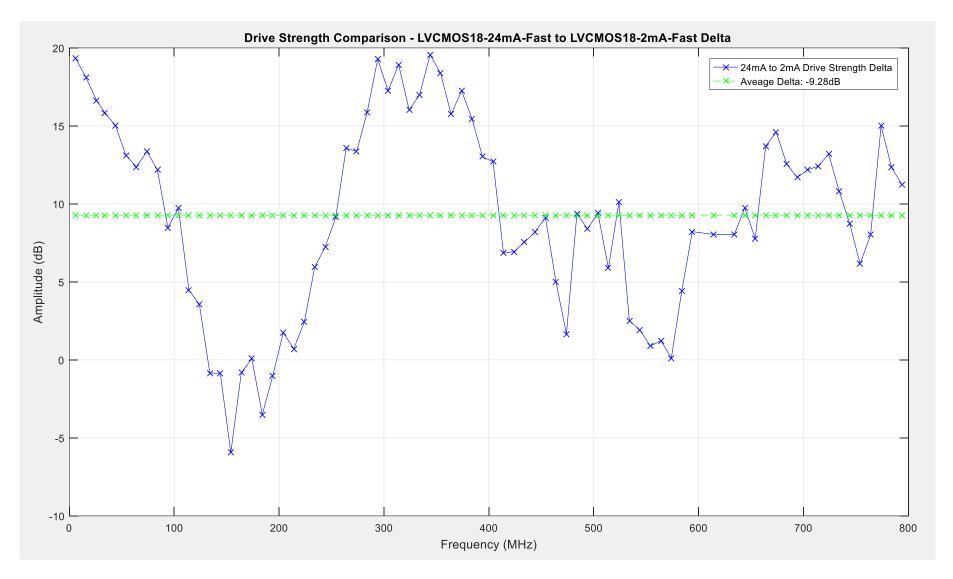

| Figure 119: LVCMOS18-24mA-Fast to LVCMOS18-4mA-Fast Drive Strength Comparison     | 153  |

| Figure 120: LVCMOS18-24mA-Fast to LVCMOS18-2mA-Fast Drive Strength Comparison     | 154  |

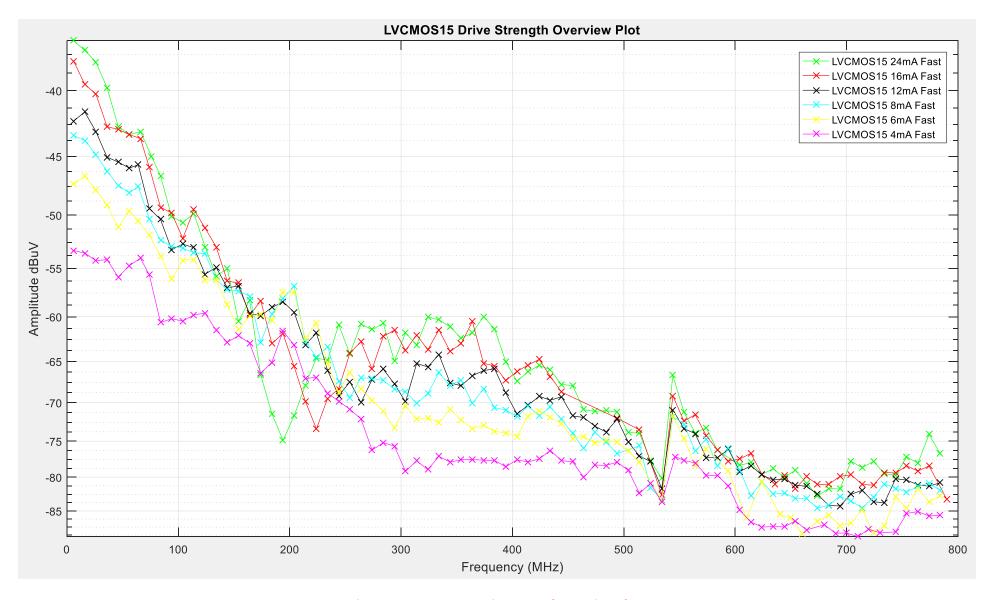

| Figure 121: LVCMOS15 Drive Strength Overview Plot                                 | .158 |

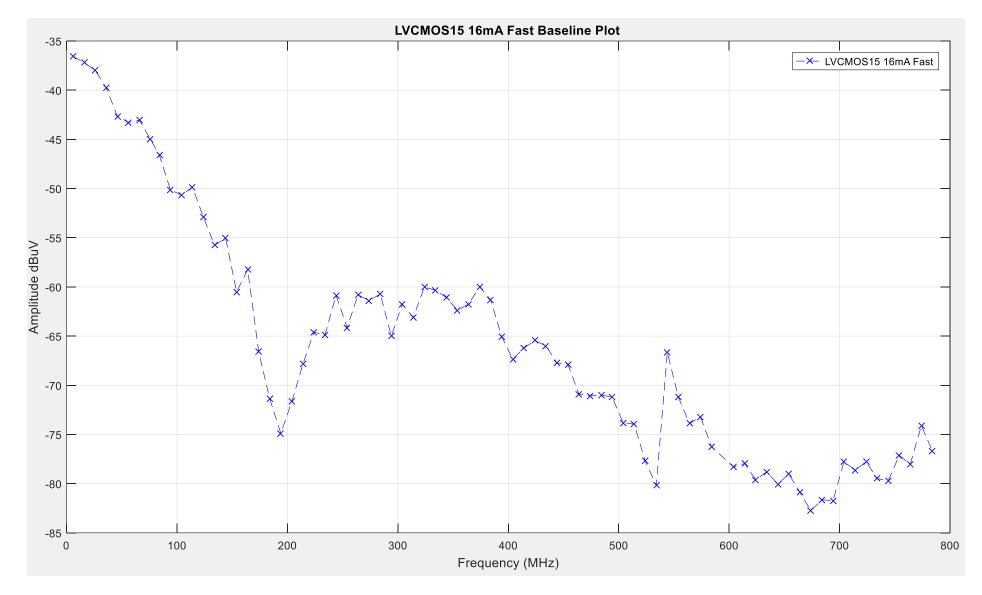

| Figure 122: LVCMOS15 Drive Strength Baseline Plot                                                                  | .159 |

|--------------------------------------------------------------------------------------------------------------------|------|

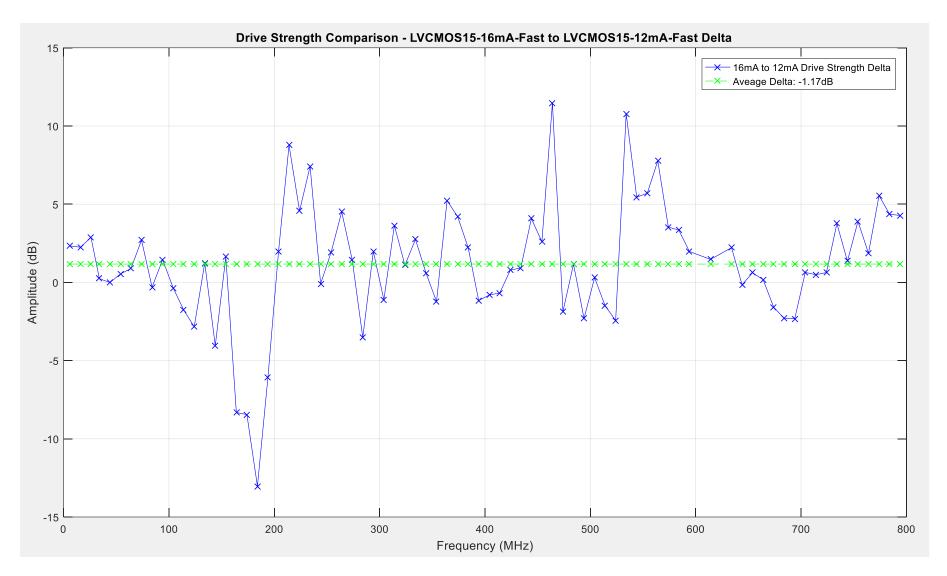

| Figure 123: LVCMOS15-16mA-Fast to LVCMOS15-12mA-Fast Drive Strength Comparison                                     | .160 |

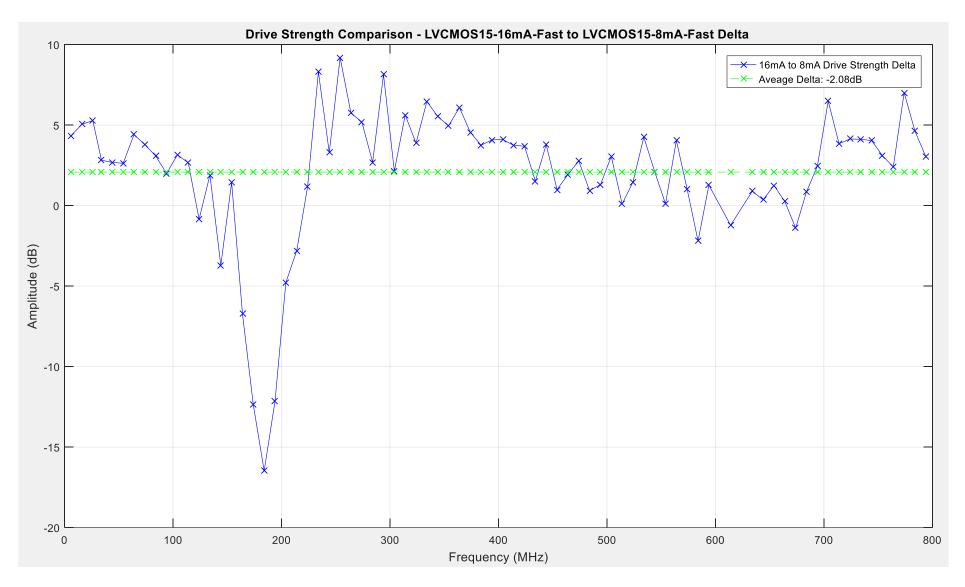

| Figure 124: LVCMOS15-16mA-Fast to LVCMOS15-8mA-Fast Drive Strength Comparison                                      | .161 |

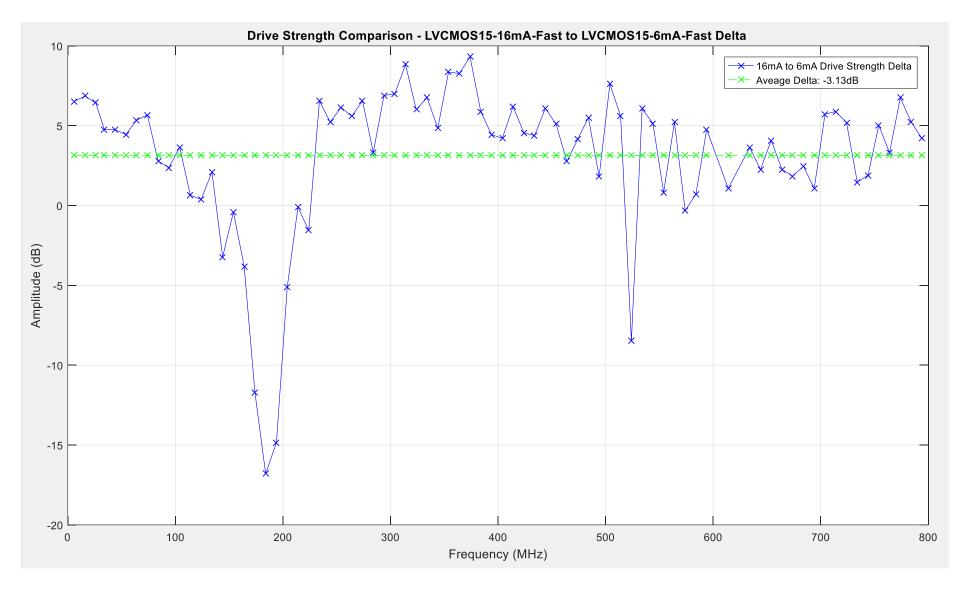

| Figure 125: LVCMOS15-16mA-Fast to LVCMOS15-6mA-Fast Drive Strength Comparison                                      | .162 |

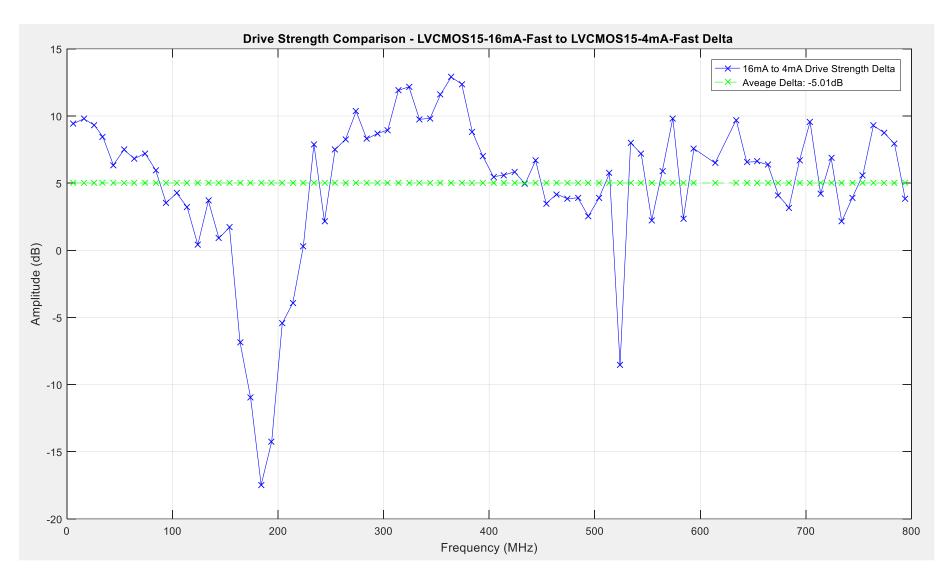

| $\label{thm:prop:strength} \textbf{Figure 126: LVCMOS15-16mA-Fast to LVCMOS15-4mA-Fast Drive Strength Comparison}$ | .163 |

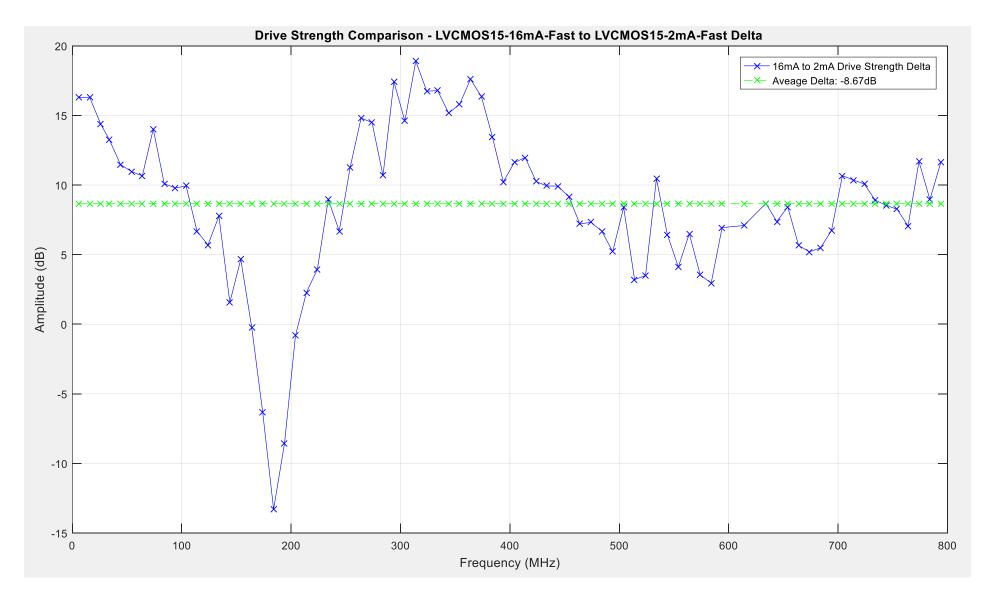

| Figure~127: LVCMOS15-16 mA-Fast~to~LVCMOS15-2 mA-Fast~Drive~Strength~Comparison                                    | .164 |

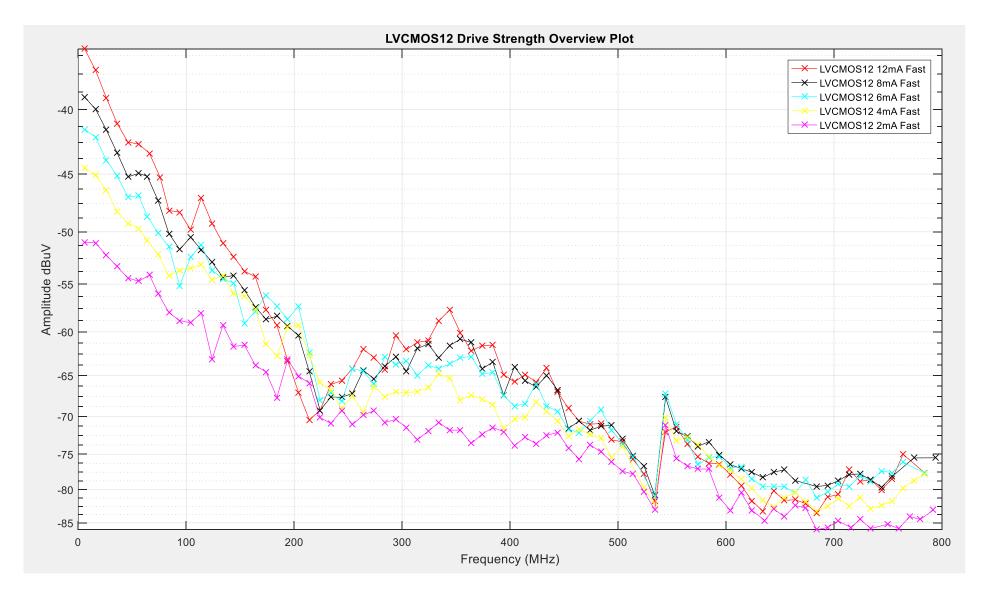

| Figure 128: LVCMOS12 Drive Strength Overview Plot                                                                  |      |

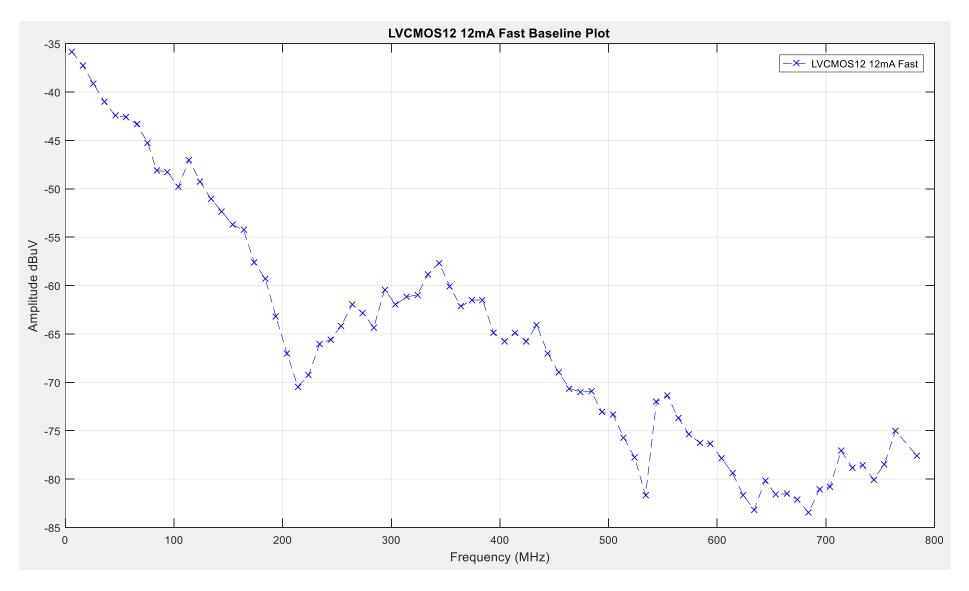

| Figure 129: LVCMOS12 Drive Strength Baseline Plot                                                                  | .169 |

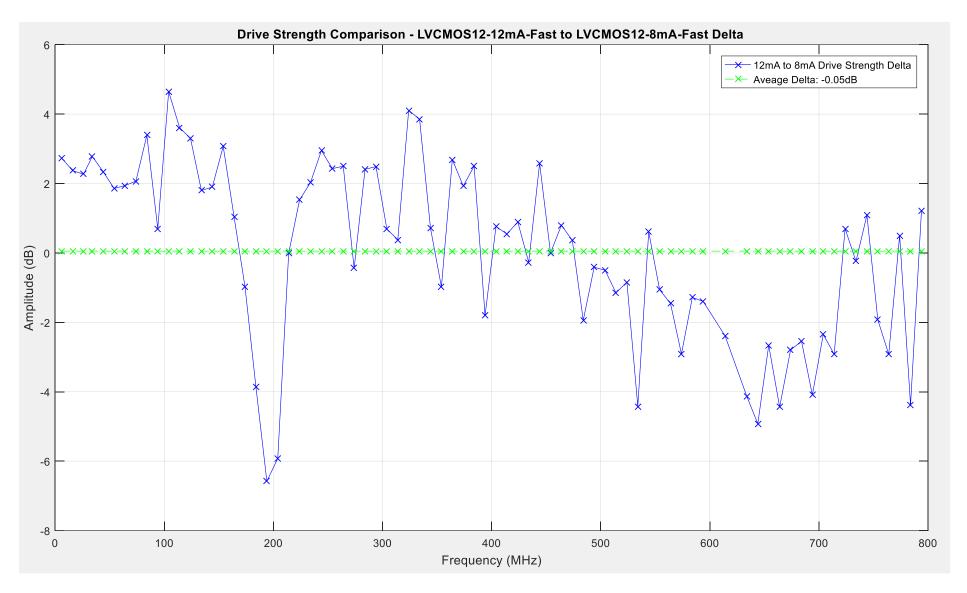

| $\label{thm:prop:sigma} \textit{Figure 130: LVCMOS12-12mA-Fast to LVCMOS12-8mA-Fast Drive Strength Comparison}$    | .170 |

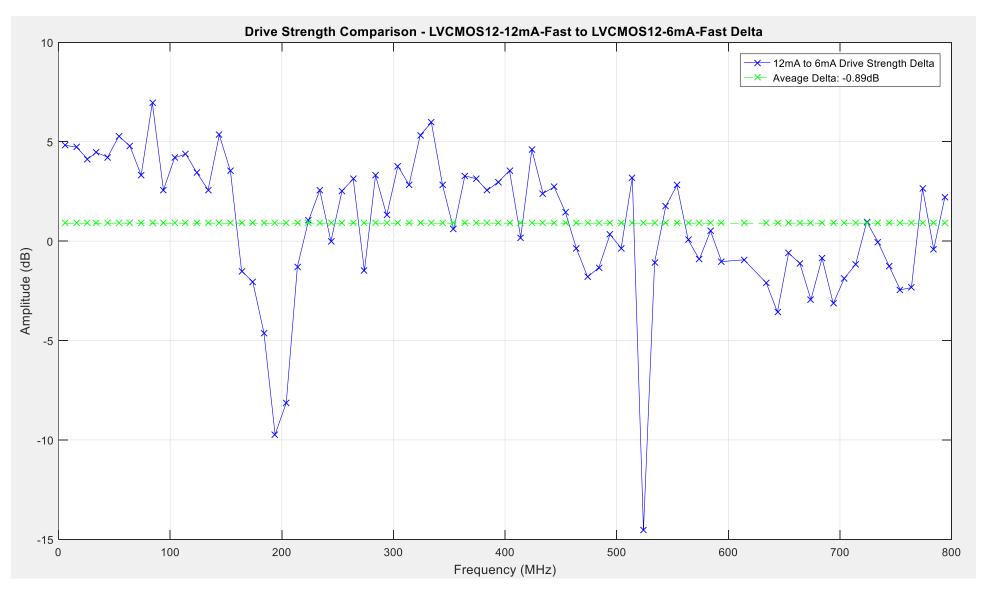

| $\label{thm:prop:strength} \textit{Figure 131: LVCMOS12-12mA-Fast to LVCMOS12-6mA-Fast Drive Strength Comparison}$ | .171 |

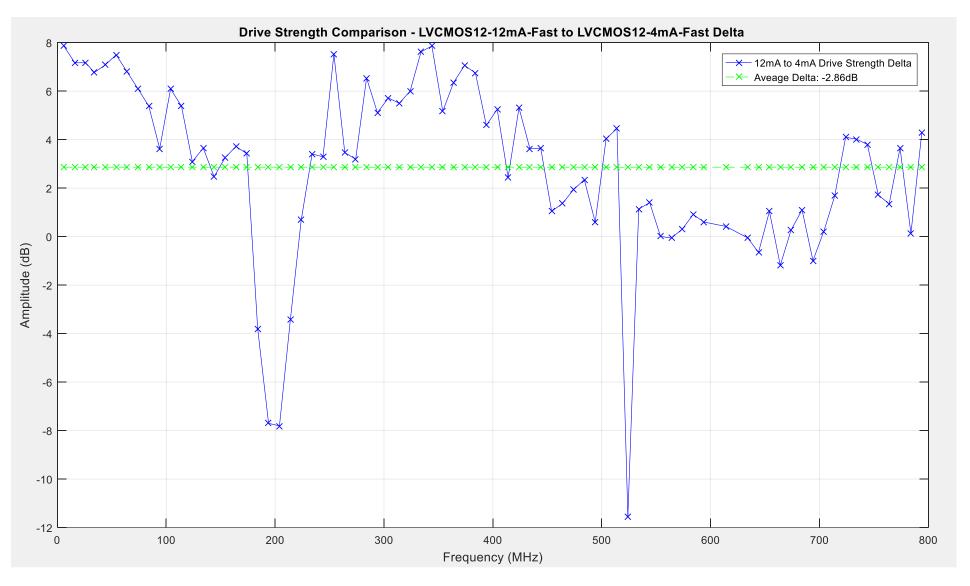

| $\label{thm:prop:strength} \textit{Figure 132: LVCMOS12-12mA-Fast to LVCMOS12-4mA-Fast Drive Strength Comparison}$ | .172 |

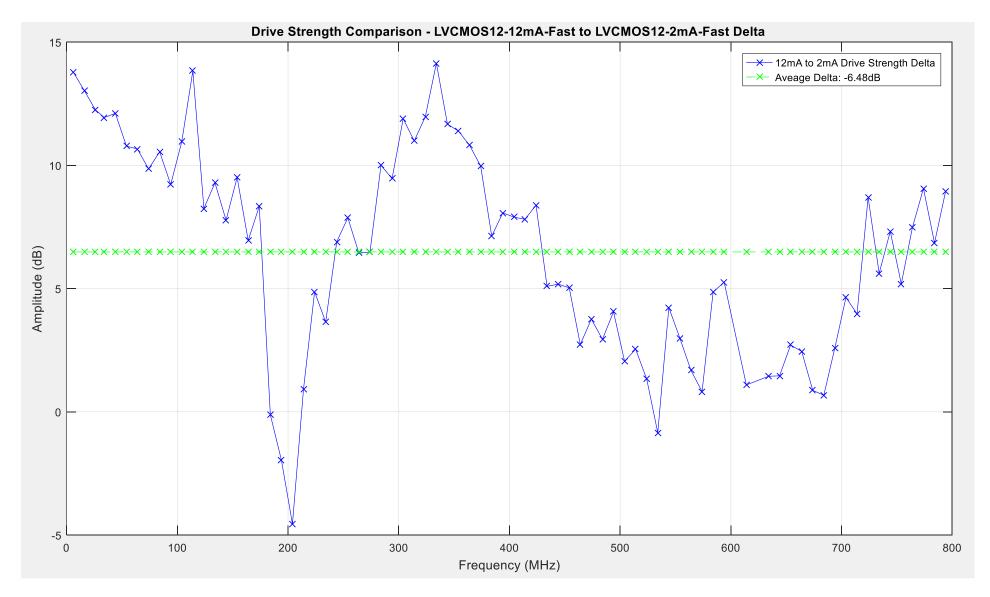

| $\label{thm:prop:strength} \textbf{Figure 133: LVCMOS12-12mA-Fast to LVCMOS12-2mA-Fast Drive Strength Comparison}$ | .173 |

| Figure 134: LVTTL Edge Rate Comparison Overview                                                                    | .178 |

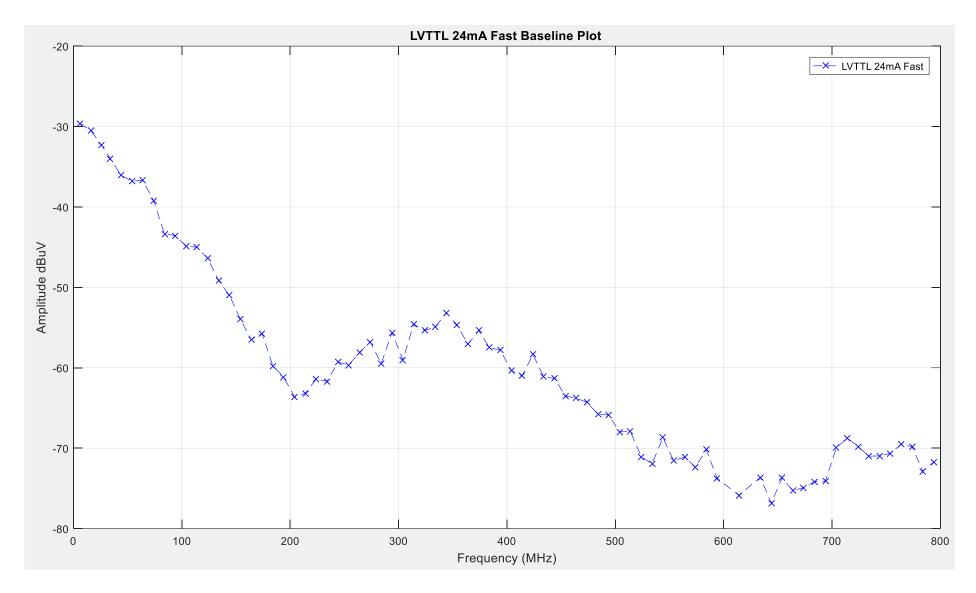

| Figure 135: LVTTL-24mA-Fast Baseline Plot                                                                          | .179 |

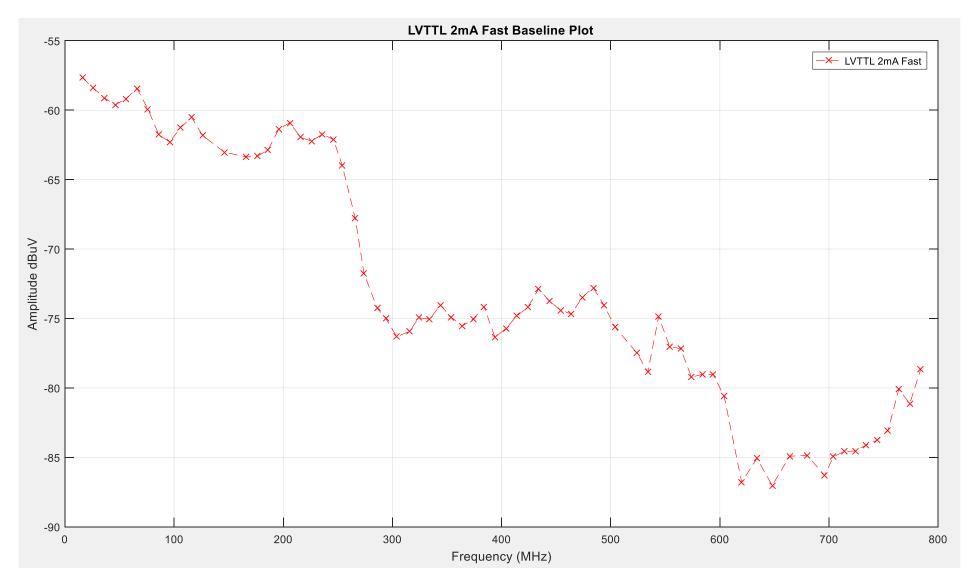

| Figure 136: LVTTL-2mA-Fast Baseline Plot                                                                           | .180 |

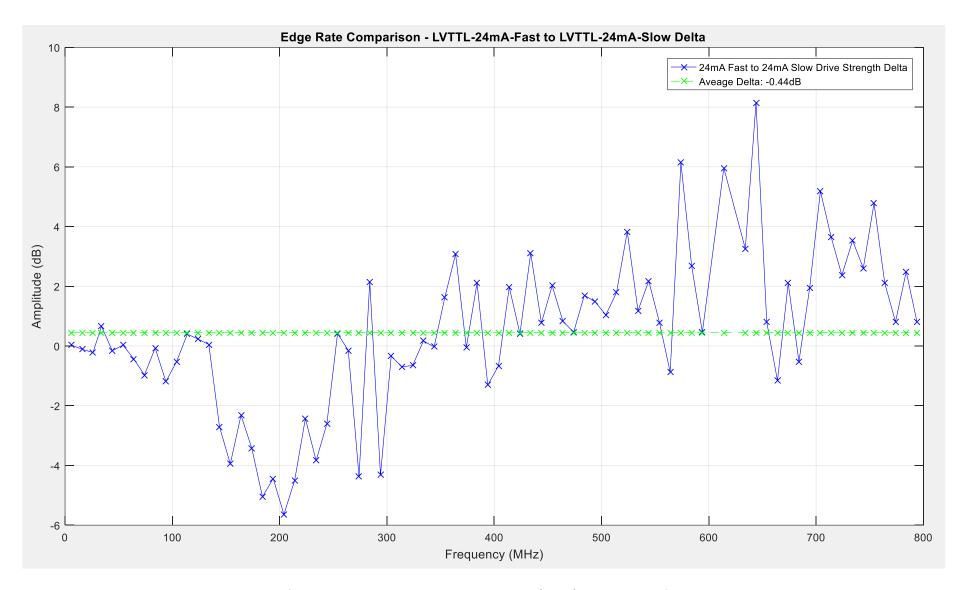

| Figure 137: LVTTL-24mA-Fast to LVTTL-24mA-Slow Edge Rate Comparison                                                | .181 |

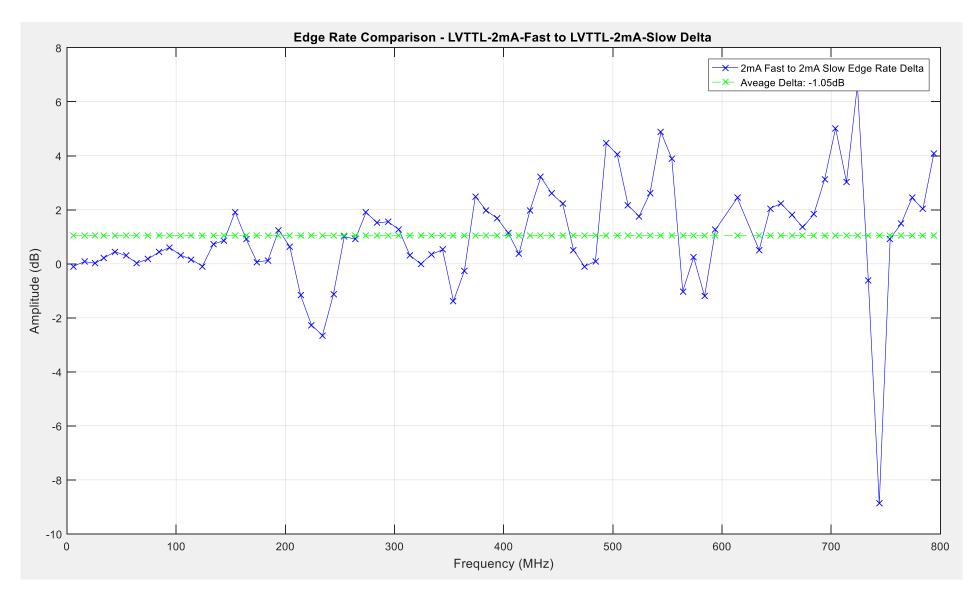

| Figure 138: LVTTL-2mA-Fast to LVTTL-2mA-Slow Edge Rate Comparison                                                  | .182 |

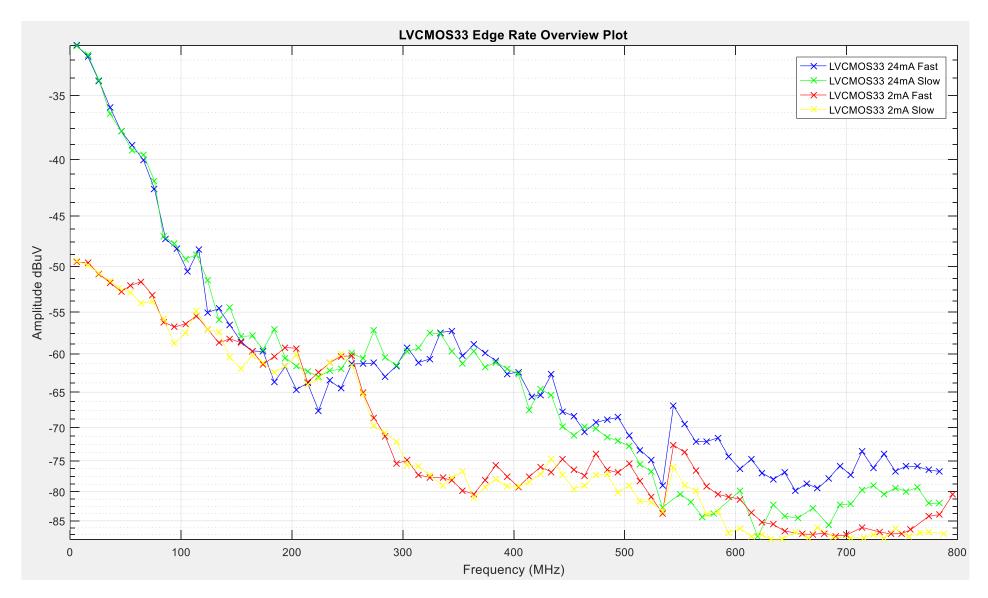

| Figure 139: LVCMOS33 Edge Rate Comparison Overview                                                                 | .185 |

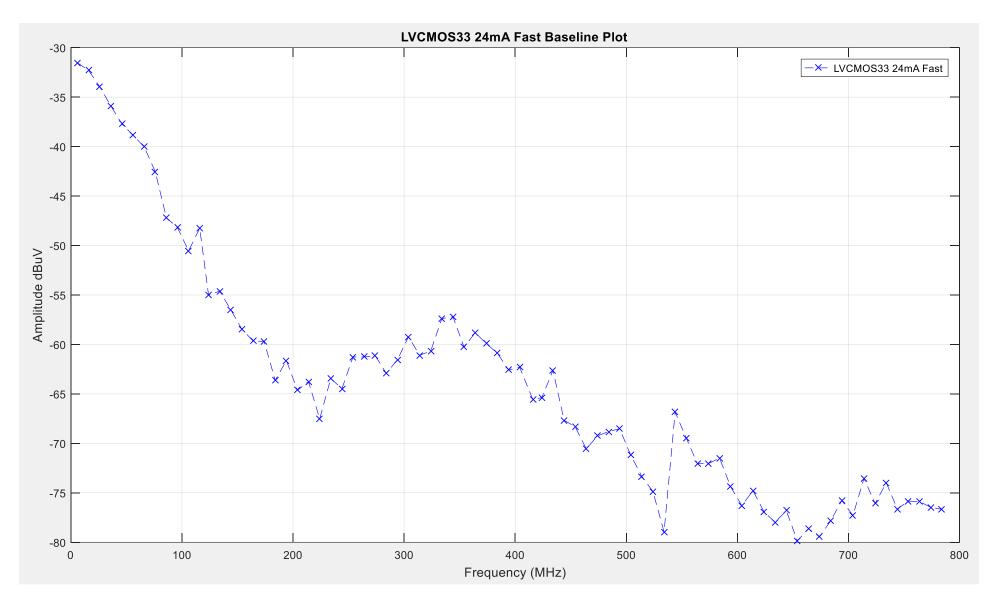

| Figure 140: LVCMOS33 Edge Rate 24mA Baseline Plot                                                                  | .186 |

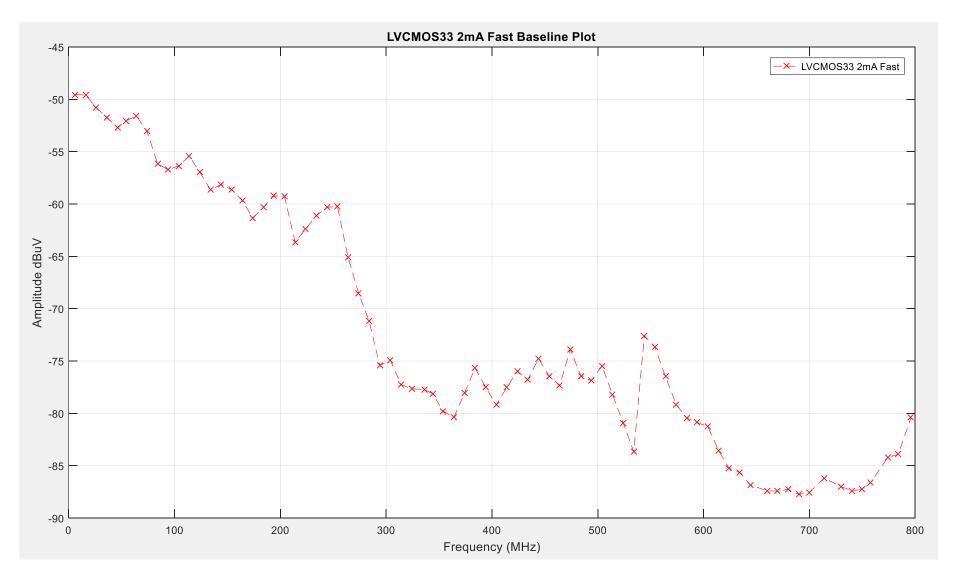

| Figure 141: LVCMOS33 Edge Rate 24mA Baseline Plot                                                                  | .187 |

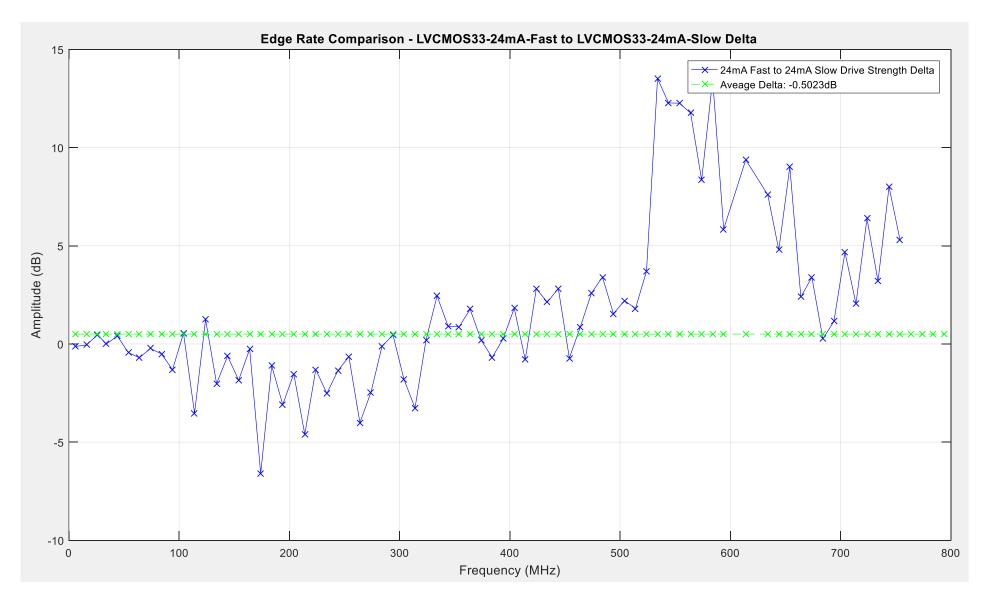

| Figure 142: LVCMOS33-24mA-Fast to LVCCMOS33-24mA-Slow Edge Rate Comparison $\dots$                                 | .188 |

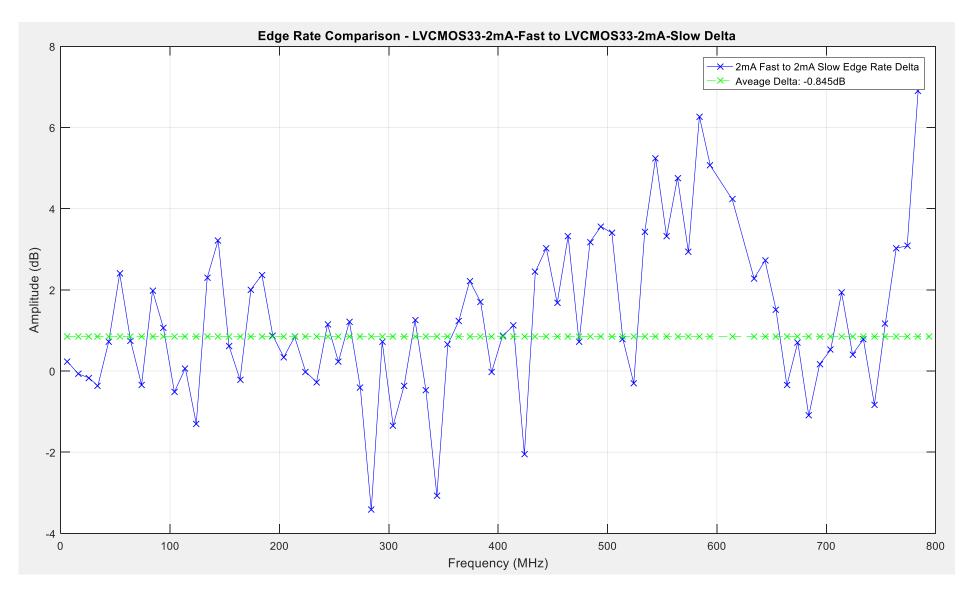

| Figure 143: LVCMOS33-2mA-Fast to LVCCMOS33-2mA-Slow Edge Rate Comparison                                           | .189 |

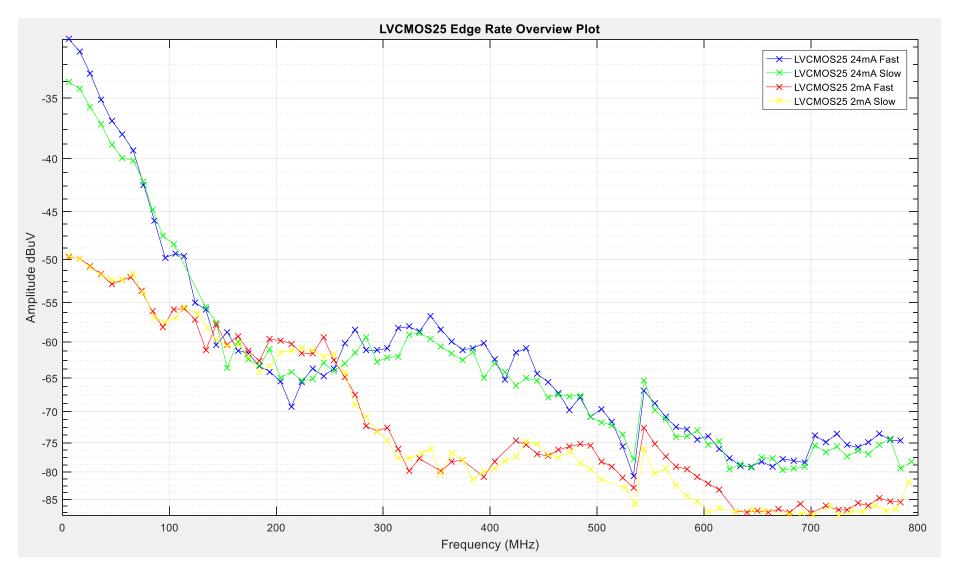

| Figure 144: LVCMOS25 Edge Rate Comparison Overview                                                                 |      |

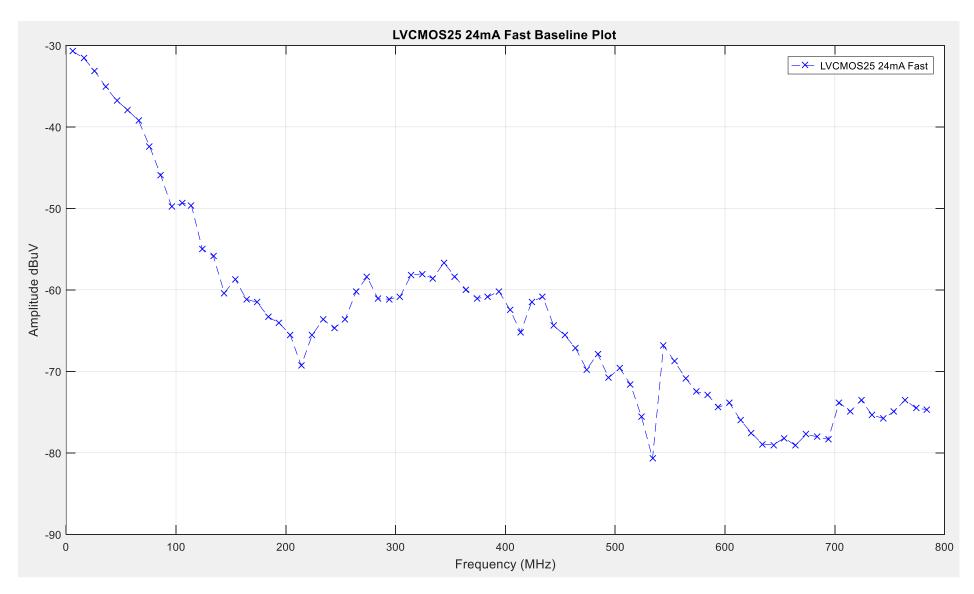

| Figure 145: LVCMOS25-24mA-Fast Baseline Plot                                                                       | .193 |

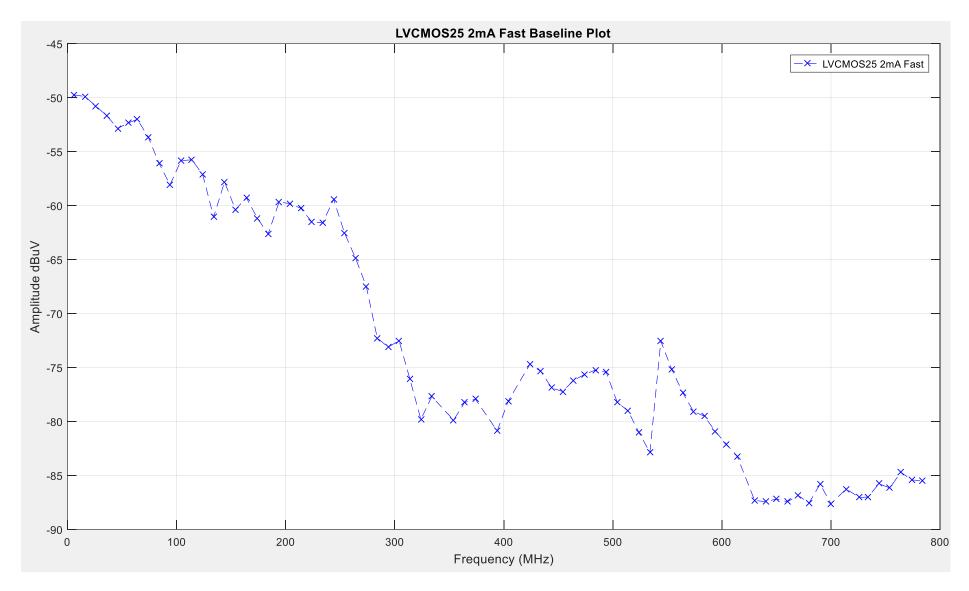

| Figure 146: LVCMOS25-2mA-Fast Baseline Plot                                                                        | .194 |

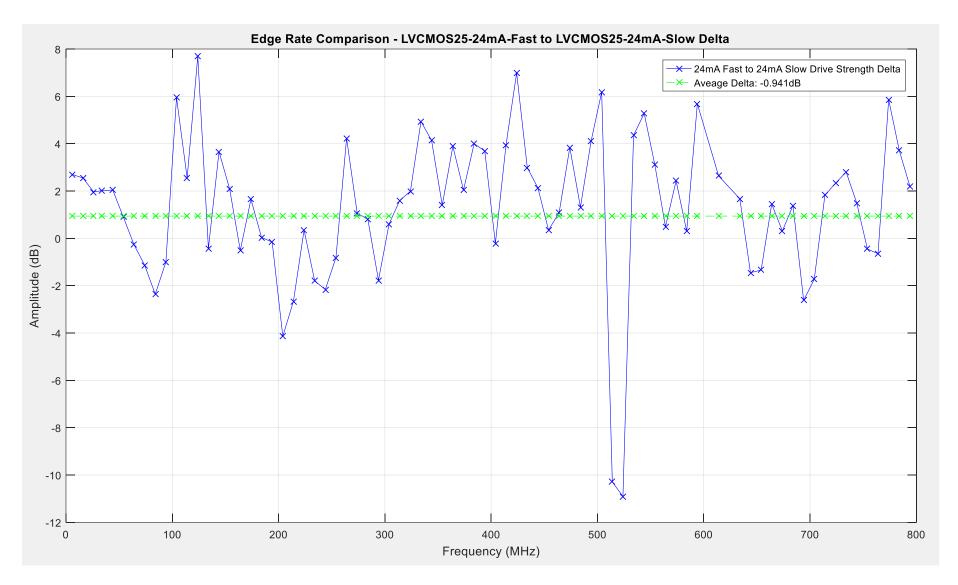

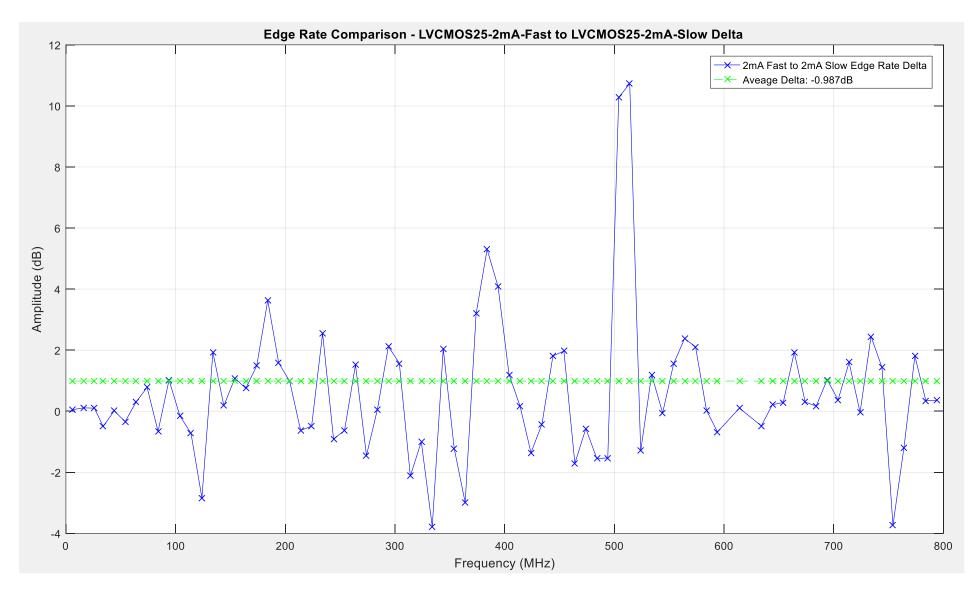

| Figure 147: LVCMOS25-24mA-Fast to LVCMOS25-24mA-Slow Edge Rate Comparison                                          | .195 |

| Figure 148: LVCMOS25-2mA-Fast to LVCCMOS33-2mA-Slow Edge Rate Comparison                                           | .196 |

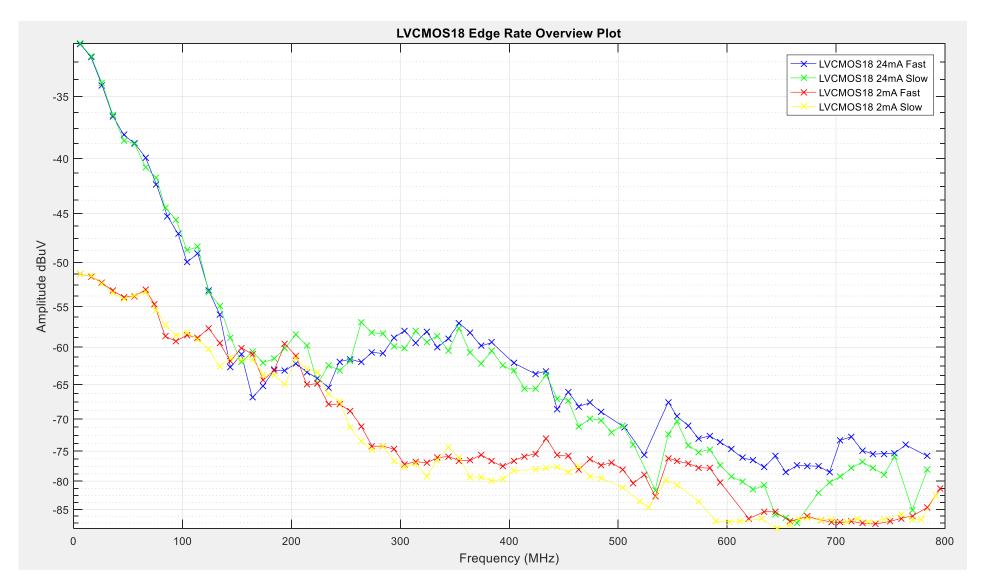

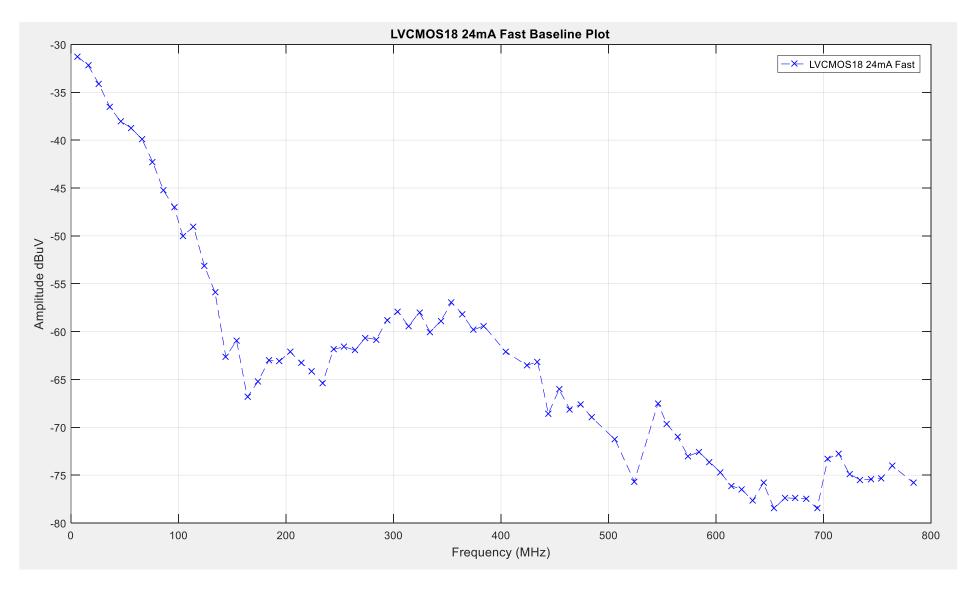

| Figure 149: LVCMOS18 Edge Rate Comparison Overview                                                                 | .199 |

| Figure 150: LVCMOS18-24mA-Fast Baseline Plot                                                                       | .200 |

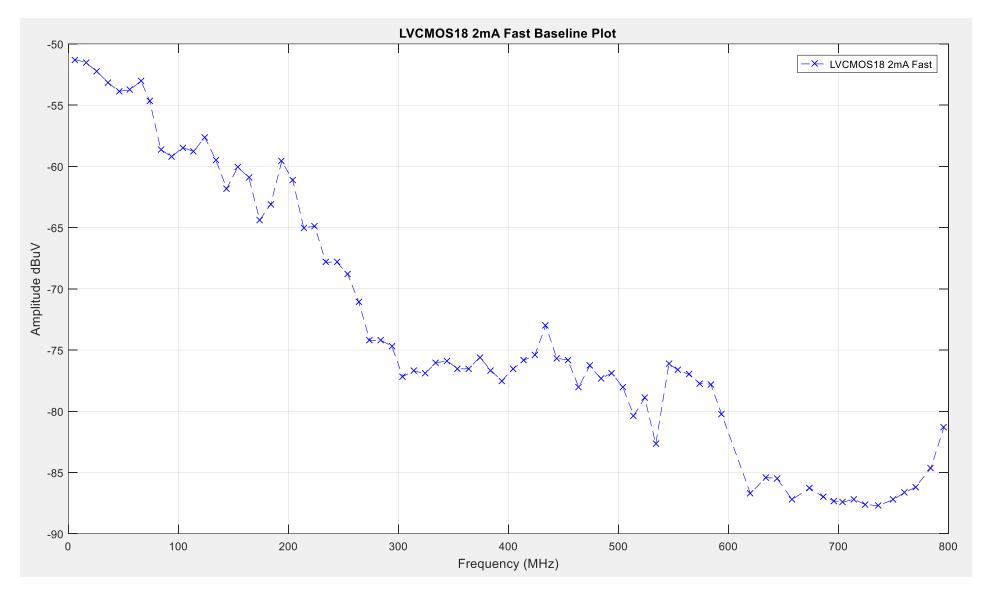

| Figure 151: LVCMOS18-2mA-Fast Baseline Plot                                                                        | .201 |

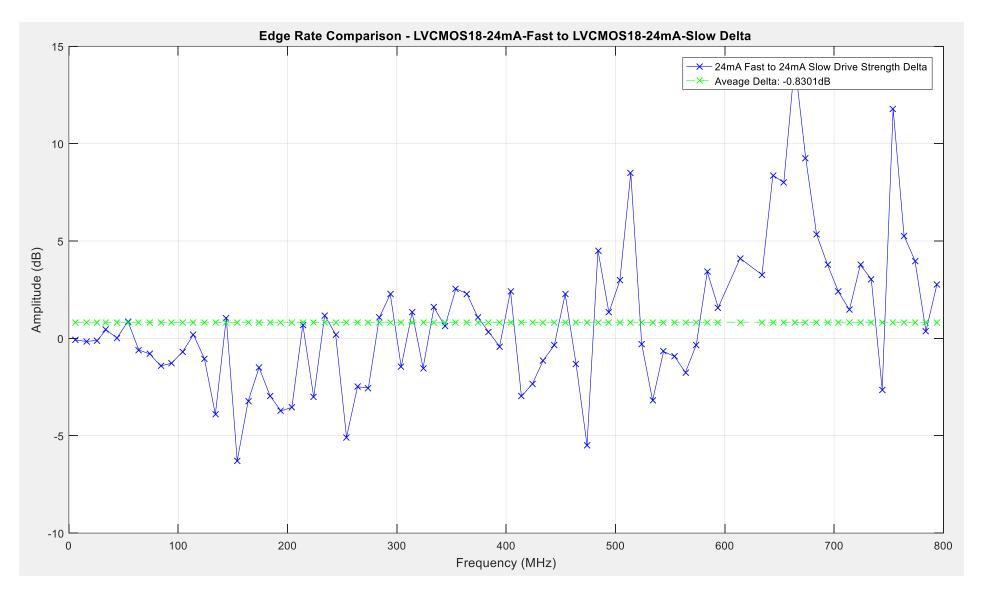

| Figure 152: LVCMOS18-24mA-Fast to LVCMOS18-24mA-Slow Edge Rate Comparison                                          | .202 |

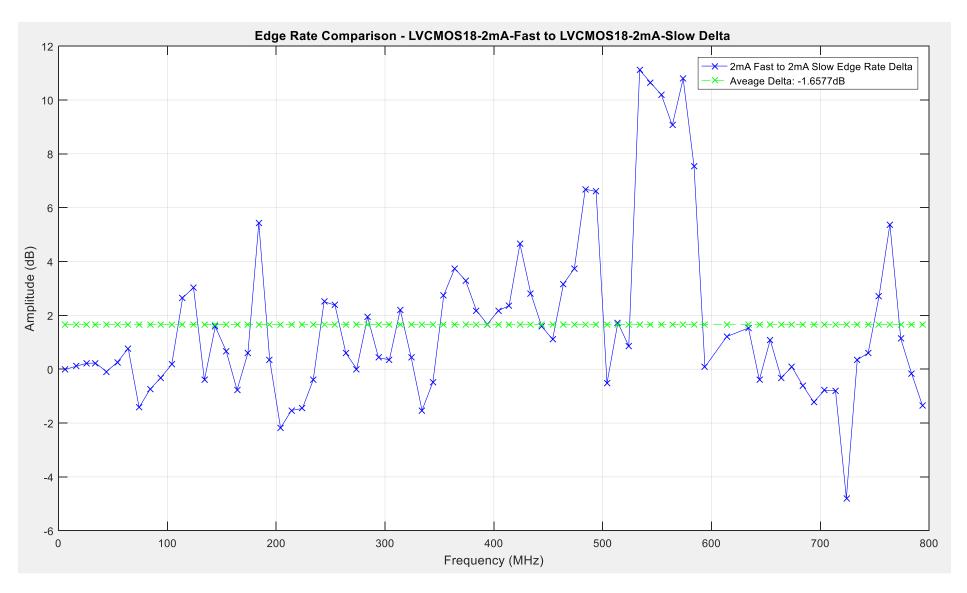

| Figure 153: LVCMOS18-24mA-Fast to LVCMOS18-24mA-Slow Edge Rate Comparison                                          | .203 |

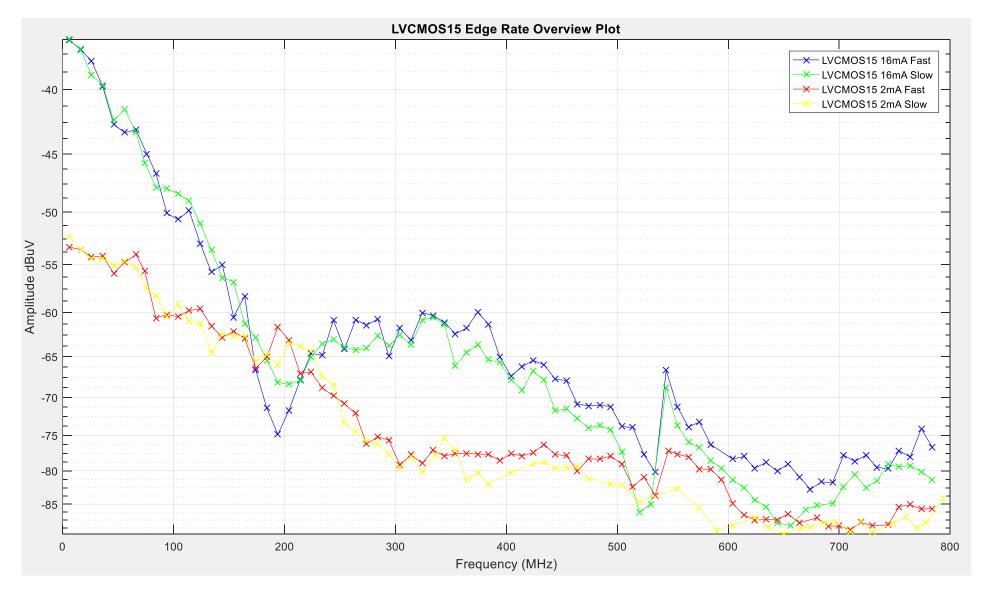

| Figure 154: LVCMOS15 Edge Rate Comparison Overview                                                                 | .206 |

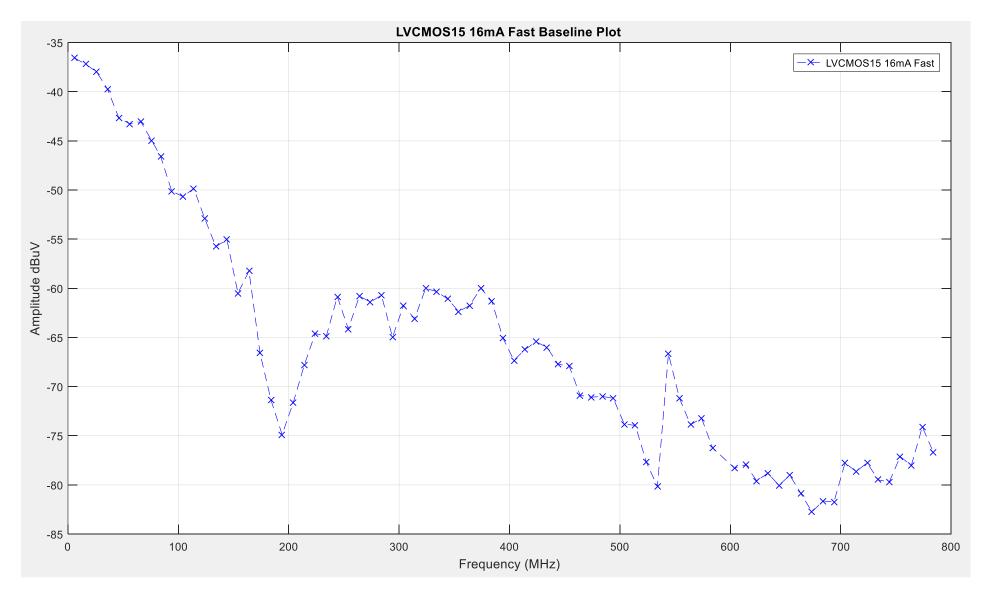

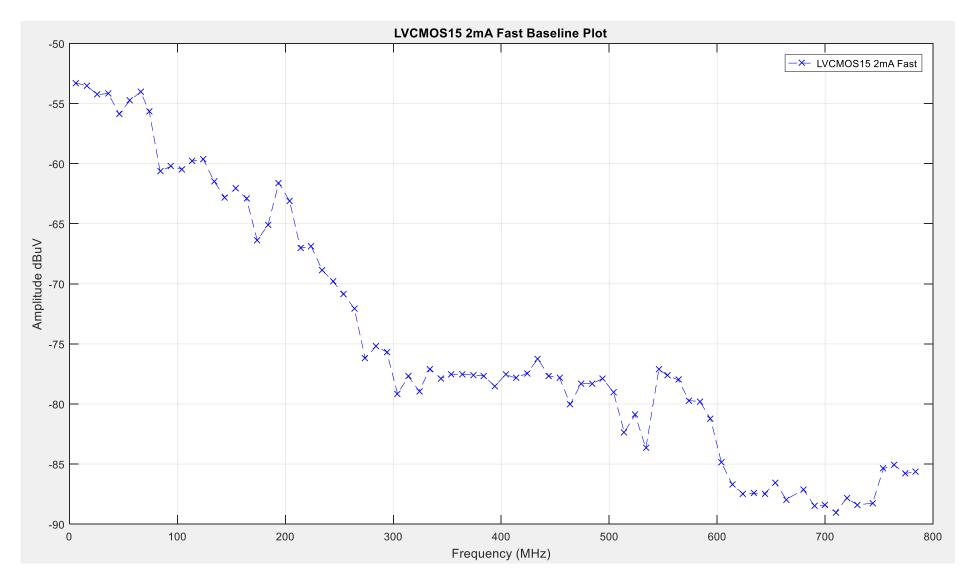

| Figure 155: LVCMOS15-16mA-Fast Baseline Plot                                                                       | .207 |

| Figure 156: LVCMOS15-2mA-Fast Baseline Plot                                                                        | .208 |

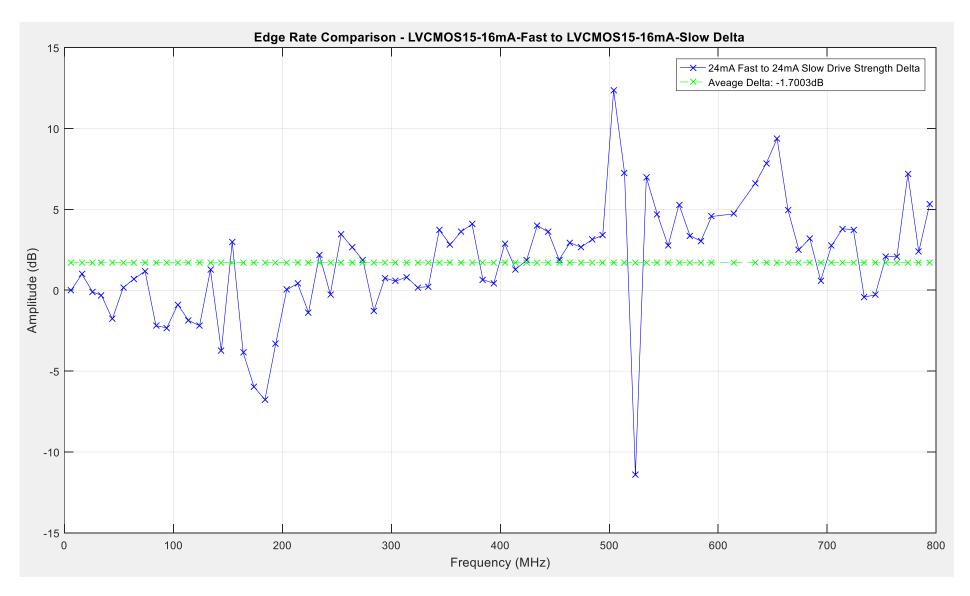

| $\label{thm:prop:sigma} \textbf{Figure 157: LVCMOS15-16mA-Fast to LVCMOS15-16mA-Slow Edge Rate Comparison}$        | .209 |

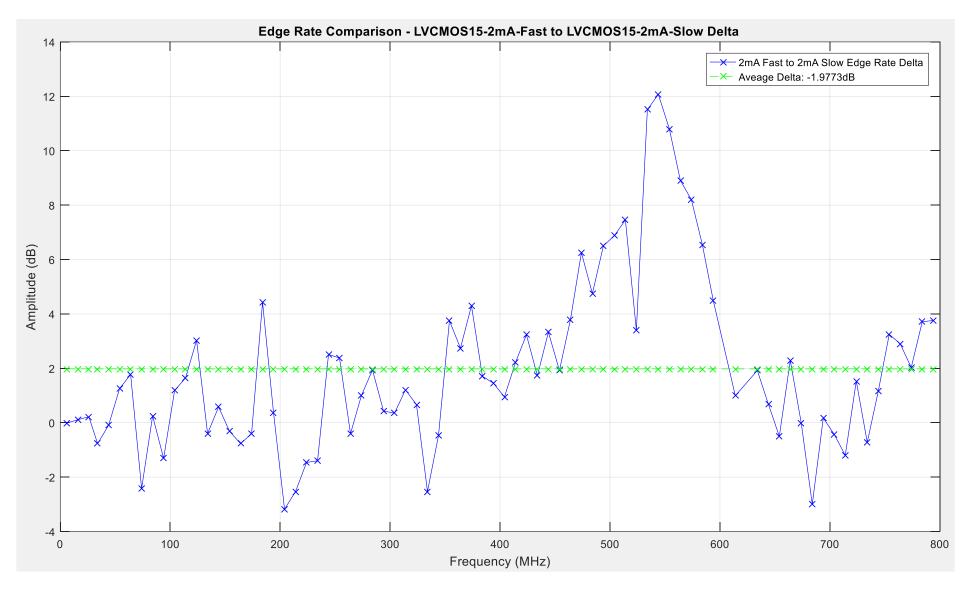

| Figure 158: LVCMOS15-2mA-Fast to LVCMOS15-2mA-Slow Edge Rate Comparison                                            | .210 |

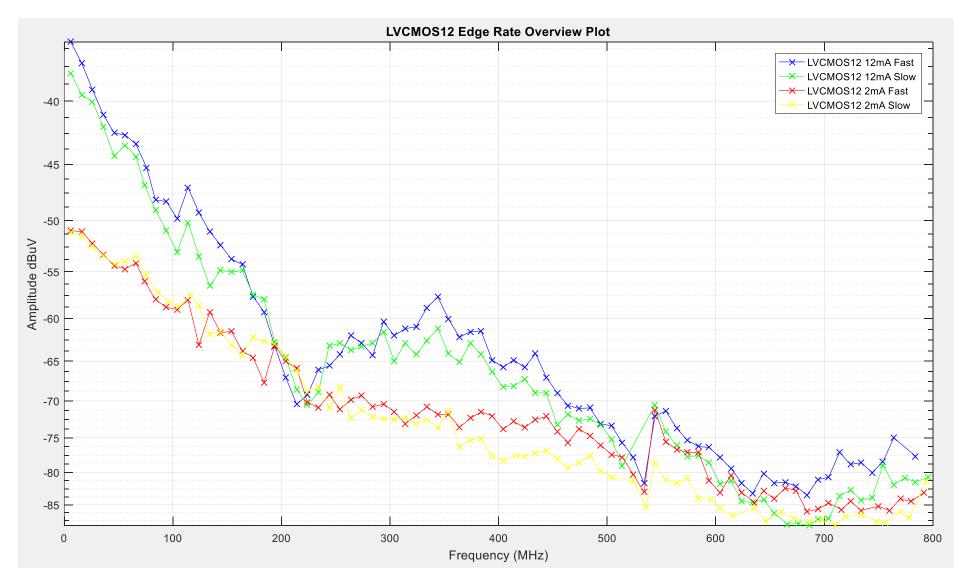

| Figure 159: LVCMOS12 Edge Rate Comparison Overview                                                                 | .213 |

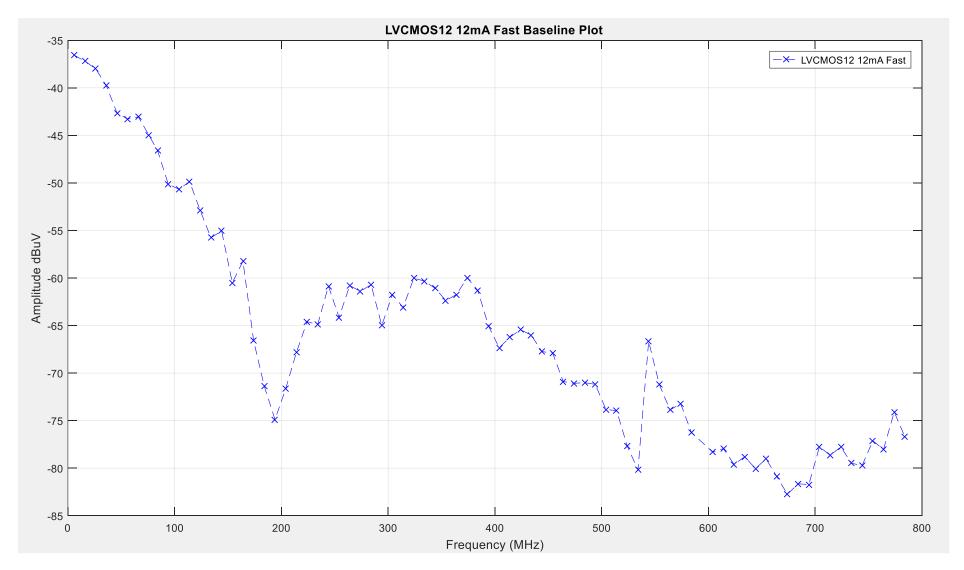

| Figure 160: LVCMOS12 12mA Baseline Comparison                                                                      |      |

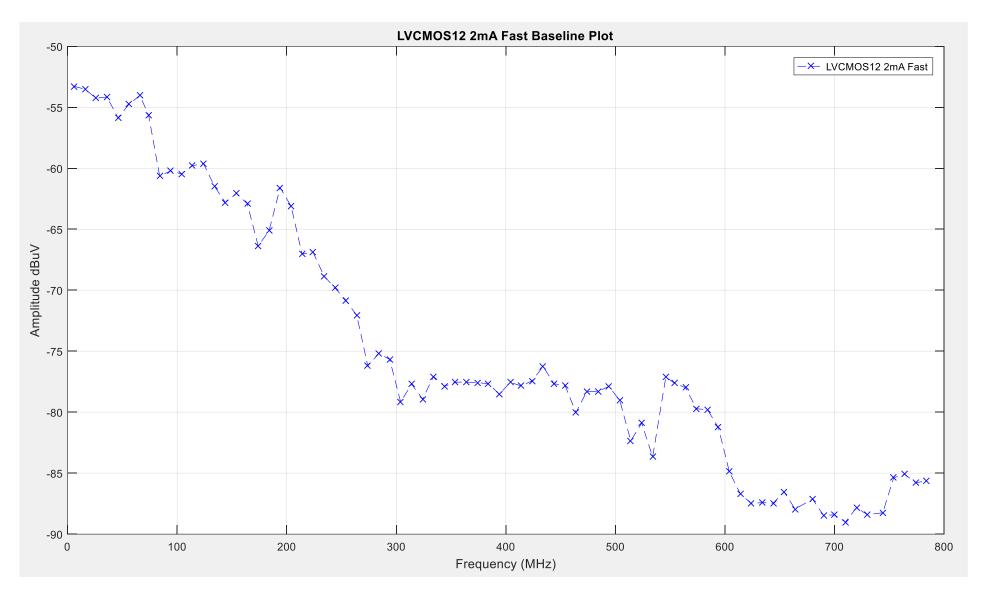

| Figure 161: LVCMOS12 2mA Baseline Comparison                                                                       | .215 |

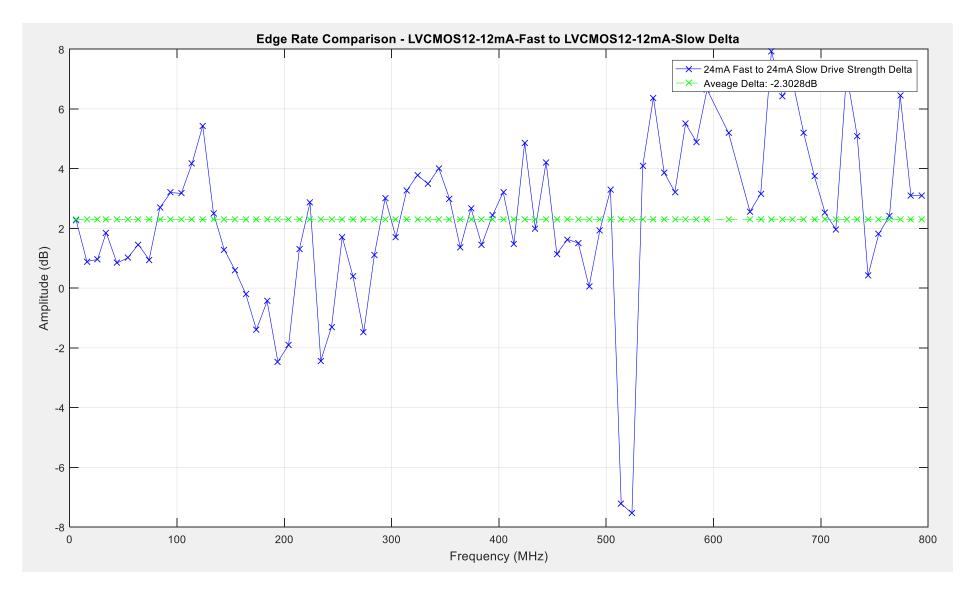

| Figure 162: LVCMOS12-12mA-Fast to LVCMOS12-12mA-Slow Edge Rate Comparison                                          | .216 |

| Figure 163: LVCMOS12-2mA-Fast to LVCMOS12-2mA-Slow Edge Rate Comparison                                            | .217 |

# **Tables**

| Table 1: A Comparison of Logic Families [26]                      | 27  |

|-------------------------------------------------------------------|-----|

| Table 2: Signal Generator Source Signals                          | 43  |

| Table 3: Signal Generator Time Domain Analysis Test Equipment     | 44  |

| Table 4: Signal Generator Frequency Domain Test Equipment         | 46  |

| Table 5: Sig Gen Signals 1 & 2 Results                            | 47  |

| Table 6: Sig Gen Signals 3 - 6 Signal Properties                  | 52  |

| Table 7: Average Level of Peak Harmonics Signal 3 – 6             | 55  |

| Table 8: I/O Properties for Spartan 6                             | 59  |

| Table 9: MSCR-001 Output Driver Attributes                        | 59  |

| Table 10: Time Domain Testing Equipment                           | 61  |

| Table 11: Frequency Domain Testing equipment                      | 61  |

| Table 12: LVTTL Signal Characteristics                            | 64  |

| Table 13: LVTTL Signal Characteristics                            | 71  |

| Table 14: Radiated Emissions Test Equipment                       | 77  |

| Table 15: I/O Properties for Spartan 6                            | 78  |

| Table 16: Logic Standard Testing – Maximum I/O Setting Results    | 80  |

| Table 17: Logic Standard Testing – Default I/O Setting Results    | 87  |

| Table 18: Logic Standard Testing – Minimum I/O Setting            | 96  |

| Table 19: I/O Standard Testing Overview - Average Emission Levels | 105 |

| Table 20: LVTTL Drive Strength Emissions Levels Overview          | 107 |

| Table 21: LVCMOS33 Drive Strength Emissions Levels Overview       | 119 |

| Table 22: LVCMOS25 Drive Strength Emissions Levels Overview       | 131 |

| Table 23: LVCMOS18 Drive Strength Emissions Levels Overview       | 143 |

| Table 24: LVCMOS15 Drive Strength Emissions Levels Overview       | 155 |

| Table 25: LVCMOS12 Drive Strength Emissions Levels Overview       | 165 |

| Table 26: LVTTL Edge Rate Emissions Results                       | 176 |

| Table 27: LVCMOS33 Edge Rate Emissions Results                    | 183 |

| Table 28: LVCMOS25 Edge Rate Emissions Results                    | 190 |

| Table 29: LVCMOS18 Edge Rate Emissions Results                    | 197 |

| Table 30: LVCMOS15 Edge Rate Emissions Results                    | 204 |

| Table 31: LVCMOS12 Edge Rate Emissions Results                    | 211 |

| Table 32: LVTTL Emissions Overview                                | 220 |

| Table 33: LVCMOS33 Emissions Overview                             | 221 |

| Table 34: LVCMOS25 Emissions Overview                             | 221 |

| Table 35: LVCMOS18 Emissions Overview                             | 222 |

| Table 36: LVCMOS15 Emissions Overview                             | 222 |

| Table 37: LVCMOS15 Emissions Overview                             | 223 |

# **Equations**

| Equation 1: Fourier Transform Equation [6]                                             | 17   |

|----------------------------------------------------------------------------------------|------|

| Equation 2: Inductive Reactance                                                        | 20   |

| Equation 3: Capacitive Reactance                                                       |      |

| Equation 4: Capacitor Reactance Formula [24]                                           | 34   |

| Equation 5: Transposed Capcitor Reactance Equation                                     | 34   |

| Equation 6: Voltage Divider Equation [24]                                              | 36   |

| Equation 7: Capacitor Series Impedance                                                 | 36   |

| Equation 8: Capacitive Reactance Formula                                               | 36   |

| Equation 9: Inductive Reactance Formula                                                | 36   |

| Equation 10: Transmissions Line Reflection Coefficient Formula [32]                    | 38   |

| Equation 11: Delta between LVTTL and LVCMOS33 (Comparison 1)                           | 82   |

| Equation 12: Delta between LVTTL and LVCMOS25 (Comparison 1)                           | 82   |

| Equation 13: Delta between LVTTL and LVCMOS18 (Comparison 1)                           | 82   |

| Equation 14: Delta between LVTTL and LVCMOS33 (Comparison 2)                           | 89   |

| Equation 15: Delta between LVTTL and LVCMOS25 (Comparison 2)                           | 89   |

| Equation 16: Delta between LVTTL and LVCMOS18 (Comparison 2)                           | 89   |

| Equation 17: Delta between LVTTL and LVCMOS15 (Comparison 2)                           | 90   |

| Equation 18: Delta between LVTTL and LVCMOS12 (Comparison 2)                           | 90   |

| Equation 19: Delta between LVTTL and LVCMOS33 (Comparison 3)                           | 98   |

| Equation 20: Delta between LVTTL and LVCMOS25 (Comparison 3)                           | 98   |

| Equation 21: Delta between LVTTL and LVCMOS18 (Comparison 3)                           | 98   |

| Equation 22: Delta between LVTTL and LVCMOS15 (Comparison 3)                           | 99   |

| Equation 23: Delta between LVTTL and LVCMOS12 (Comparison 3)                           | 99   |

| Equation 24: Drive Strength Testing: Delta 1 – LVTTL 24mA to 16mA Comparison           | .107 |

| Equation 25: Drive Strength Testing: Delta 2 – LVTTL 24mA to 12mA Comparison           | .108 |

| Equation 26: Drive Strength Testing: Delta 3 – LVTTL 24mA to 8mA Comparison            | .108 |

| Equation 27: Drive Strength Testing: Delta 4 – LVTTL 24mA to 6mA Comparison            | .109 |

| Equation 28: Drive Strength Testing: Delta 5 – LVTTL 24mA to 4mA Comparison            | .109 |

| Equation 29: Drive Strength Testing: Delta 6 – LVTTL 24mA to 2mA Comparison            | .110 |

| Equation 30: Drive Strength Testing: Delta 7 – LVCMOS33 24mA to 16mA Comparison        | .119 |

| Equation 31: Drive Strength Testing: Delta 8 – LVCMOS33 24mA to 12mA Comparison        | .120 |

| Equation 32: Drive Strength Testing: Delta 9 – LVCMOS33 24mA to 8mA Comparison         | .120 |

| Equation 33: Drive Strength Testing: Delta 10 – LVCMOS33 24mA to 6mA Comparison        | .121 |

| Equation 34: Drive Strength Testing: Delta 11 – LVCMOS33 24mA to 4mA Comparison        | .121 |

| Equation 35: Drive Strength Testing: Delta 12 – LVCMOS33 24mA to 2mA Comparison        | .122 |

| Equation 36: Drive Strength Testing: Delta 13 $-$ LVCMOS25 24mA to 16mA Comparison     | .131 |

| Equation 37: Drive Strength Testing: Delta $14 - LVCMOS25\ 24mA$ to $12mA\ Comparison$ | .132 |

| Equation 38: Drive Strength Testing: Delta 15 – LVCMOS25 24mA to 8mA Comparison        | .132 |

| Equation 39: Drive Strength Testing: Delta 16 – LVCMOS25 24mA to 6mA Comparison        | .133 |

| Equation 40: Drive Strength Testing: Delta 17 – LVCMOS25 24mA to 4mA Comparison        | .133 |

| Equation 41: Drive Strength Testing: Delta 18 – LVCMOS25 24mA to 2mA Comparison 134     |

|-----------------------------------------------------------------------------------------|

| Equation 42: Drive Strength Testing: Delta 19 – LVCMOS18 24mA to 16mA Comparison143     |

| Equation 43: Drive Strength Testing: Delta 20 – LVCMOS18 24mA to 12mA Comparison144     |

| Equation 44: Drive Strength Testing: Delta 21 – LVCMOS18 24mA to 8mA Comparison 144     |

| Equation 45: Drive Strength Testing: Delta 22 – LVCMOS18 24mA to 6mA Comparison145      |

| Equation 46: Drive Strength Testing: Delta 23 – LVCMOS18 24mA to 4mA Comparison145      |

| Equation 47: Drive Strength Testing: Delta 24 – LVCMOS18 24mA to 2mA Comparison146      |

| Equation 48: Drive Strength Testing: Delta 25 – LVCMOS15 16mA to 12mA Comparison155     |

| Equation 49: Drive Strength Testing: Delta 26 – LVCMOS15 16mA to 8mA Comparison 156     |

| Equation 50: Drive Strength Testing: Delta 27 – LVCMOS15 16mA to 6mA Comparison 156     |

| Equation 51: Drive Strength Testing: Delta 28 – LVCMOS15 16mA to 4mA Comparison 157     |

| Equation 52: Drive Strength Testing: Delta 29– LVCMOS15 16mA to 2mA Comparison157       |

| Equation 53: Drive Strength Testing: Delta 30– LVCMOS12 12mA to 8mA Comparison165       |

| Equation 54: Drive Strength Testing: Delta 31– LVCMOS12 12mA to 6mA Comparison166       |

| Equation 55: Drive Strength Testing: Delta 32– LVCMOS12 12mA to 4mA Comparison166       |

| Equation 56: Drive Strength Testing: Delta 33– LVCMOS12 12mA to 2mA Comparison167       |

| Equation 57: Edge Rate Testing: Delta 1 – LVTTL-24mA-Fast to LVTTL-24mA-Slow Comparison |

|                                                                                         |

| Equation 58: Edge Rate Testing: Delta 2 – LVTTL-2mA-Fast to LVTTL-2mA-Slow Comparison   |

|                                                                                         |

| Equation 59: Edge Rate Testing: Delta 3 – LVCMOS33-24mA-Fast to LVCMOS33-24mA-Slow      |

| Comparison                                                                              |

| Equation 60: Edge Rate Testing: Delta 4 – LVCMOS33-2mA-Fast to LVCMOS33-2mA-Slow        |

| Comparison                                                                              |

| Equation 61: Edge Rate Testing: Delta 5 – LVCMOS25-24mA-Fast to LVCMOS25-24mA-Slow      |

| Comparison                                                                              |

| Equation 62: Edge Rate Testing: Delta 6 – LVCMOS25-2mA-Fast to LVCMOS25-2mA-Slow        |

| Comparison191                                                                           |

| Equation 63: Edge Rate Testing: Delta 7 – LVCMOS18-24mA-Fast to LVCMOS18-24mA-Slow      |

| Comparison                                                                              |

| Equation 64: Edge Rate Testing: Delta 8 – LVCMOS18-2mA-Fast to LVCMOS18-2mA-Slow        |

| Comparison                                                                              |

| Equation 65: Edge Rate Testing: Delta 9 – LVCMOS15-16mA-Fast to LVCMOS18-16mA-Slow      |

| Comparison204                                                                           |

| Equation 66: Edge Rate Testing: Delta 10 – LVCMOS15-2mA-Fast to LVCMOS15-2mA-Slow       |

| Comparison                                                                              |

| Equation 67: Edge Rate Testing: Delta 11 – LVCMOS12-12mA-Fast to LVCMOS12-12mA-Slow     |

| Comparison211                                                                           |

| Equation 68: Edge Rate Testing: Delta 12 – LVCMOS12-2mA-Fast to LVCMOS12-2mA-Slow       |

| Comparison                                                                              |

# Acknowledgments

I would like to take this opportunity to express my sincerest gratitude to project supervisors Dr John Dawson and Dr Gianluca Tempesti for their continued support and guidance during this research project.

I would also like to say a massive thank you to my wife Ann Fomukong-Boden for your words of wisdom, support and encouragement in completing this thesis.

Finally, I would like to dedicate this research to the memory of my mother Susan Boden. If not for you moments like this would not have been possible. I am forever grateful.

# **Declaration**

I declare that this thesis is a presentation of original work and I am the sole author. This work has not previously been presented for an award at this, or any other, University. All sources are acknowledged as References.

#### 1 Introduction

This report investigates the effect of Field Programmable Gate Arrays (FPGAs) on the electromagnetic (EM) spectrum, more specifically the peak levels of emissions they produce in the near field under the range of I/O (input/output) driver settings available within the chosen device.

The introduction of FPGAs has brought about a new generation of circuits and systems. Faster I/O and bidirectional data buses, coupled with RAM blocks allows a design engineer to implement complex digital computations within a single integrated circuit (IC). The freedom of functionality within this device has led to its use in countless applications of digital circuitry throughout industry and academia. Digital circuits are a well-documented source of Electromagnetic Interference (EMI) due to the harmonic content of pulsed waveforms with fast transitions [1], [2]. The level of EMI produced by a digital circuit is influenced by a number of additional factors other than the edge rate of signals, for example choice of components, clock frequency, circuit layout, shielding and even circuit design [1]. One of the difficulties a designer faces is that these factors are not adequately quantified in terms of their contribution to a circuit's Electromagnetic Compatibility (EMC) performance. A significant effort is being made throughout industry and academia to understand how the evolution of integrated circuits has influenced their EMC performance and how best to manage and mitigate any EMI produced through various EMC design techniques [3], [4]. EMC design techniques for designers are either an unknown or not given sufficient consideration until after the fundamental design decisions that will affect the level of emissions have been made. In reality, the later into the design process that EMC is considered the greater the costs are of implementing the necessary design techniques to achieve EMC compliance. Within this project, logic standard, drive strength and edge rate are examined for their impact on the radiated emissions spectrum when varied across their respective ranges within a Spartan-6 FPGA device. The aim is to equip a designer with the ability to quantify any increase to the EMI produced from changes made to the I/O driver settings of an FPGA. Having this quantitative knowledge will not only help to identify the sources of EMI within a digital circuit; it will also allow the designer to make informed decisions within the conceptual design phase on how to reduce the overall EMI a system may produce. The further into a design that EMC is considered the greater the costs are of implementing the methods of reducing EMI or improving EM immunity, furthermore to this the available fixes that the designer can implement without massive cost is reduced as the development lifecycle progresses.

## 1.1 EMI from Digital Circuits & Systems

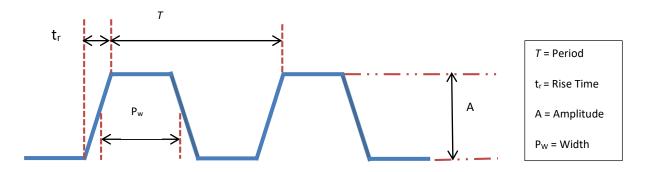

There are many contributing factors to EMI generated by digital circuits; clock signals have been identified as one of the more significant [1], [2]. An 'ideal' clock signal possesses instantaneous and symmetrical rise and fall times making it the perfect square wave. A perfect square wave in practice is not achievable, as it not possible to transition from '0' to '1' in an infinitely small time. Practical clock signals exhibit characteristics that take it away

from the approximation of 'ideal' [5]. The rise and fall times of a practical clock signal are finite in time, making the signal shape more representative of a trapezoidal waveform. In addition to possessing finite rise and fall times, practical clock signals exhibit effects such as ringing and rounding of the transitional edges. Ringing results in overshoot and undershoot on the peaks and troughs of the signal as the potential settles at its intended state. The rounding of the transitional edge, curves the signal as it approaches the intended state increasing the overall rise time of the signal. An approximation of a square wave clock signal is illustrated in Figure 1, identifying the intrinsic properties that will form the basis of the theoretical frequency domain behaviour calculations to allow comparison against the practically obtained results.

Figure 1: Properties of a Clock Waveform [5], [6]

If the rise and fall times are symmetrical, the harmonic current  $I_{(n)}$  at the  $n^{th}$  harmonic is:

$$I(n) = 2A\left(\frac{(P_w)}{T}\right)\left(\frac{\sin n\pi\left(\frac{(P_w)}{T}\right)}{n\pi\left(\frac{(P_w)}{T}\right)}\right)\left(\frac{\sin n\pi\left(\frac{t_T}{T}\right)}{n\pi\left(\frac{t_T}{T}\right)}\right)$$

**Equation 1: Fourier Transform Equation [6]**

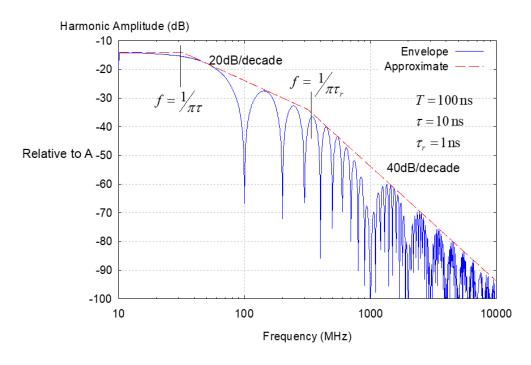

The Fourier series of an 'ideal' square wave gives an accurate representation of the sum of sinusoids at the fundamental and harmonic frequencies [7]. The spectrum behaviour of a periodic signal is calculated using the amplitude 'A' of the time domain signal and the equation contains two  $\frac{\sin(x)}{(x)}$  functions using the pulse width and the rise time of the signal to calculate the additional behaviour that introduce the minima seen within the comb spectrum in Figure 2. A square wave signal possessing symmetrical rise and fall times contains an infinite number of odd harmonics. The amplitude of these harmonics is determined by the frequency, edge rates and amplitude of the periodic signal being examined. The introduction of even harmonics into the frequency spectrum occurs when the rise and fall times of a clock signal are asymmetrical. In the frequency domain, a periodic signal as shown in Figure 1 has a line or comb spectrum envelope. An approximation of this straight-line envelope and spectral behaviour is illustrated in Figure 2, identifying the decay rates of the harmonic amplitude. The amplitude of the harmonics  $I_{(n)}$  remains constant until a first break point of  $I_{(n)}$  decays at a rate of

approximately 20dB/decade until a second frequency break point of  $F_2=\frac{1}{\pi t_r}$ , at which point I<sub>(n)</sub> begins to decay at a rate of 40dB/decade [1]. One of the major differences between the theoretical and practical frequency domain behaviour is that square wave signals with instantaneous rise and fall times only exhibit the one break point F<sub>1</sub>, and would decay at a rate of 20dB/decade until the harmonics were at a level that they fall below the noise floor.

Figure 2: Frequency Domain Behaviour of a Periodic Signal [5], [6]

From the relationship between edge rate and spectral properties, it becomes apparent that the properties of a signal will significantly influence the peak level of emissions produced by a circuit or system. The faster the edge rates of a signal the greater amplitude of harmonics further along the EM spectrum. The only way to ensure any EMI would not cause a non-compliant system is to develop an understanding of how design choices, such as the logic standard and edge rate and drive strength of signals impacts upon the frequency spectrum and ultimately how to design for EMC compliance and signal integrity.

#### 1.1.1 EMI from Practical Signals

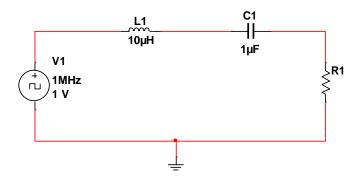

Applying periodic signals to practical circuitry further takes the signal away from the 'ideal' approximation illustrated in Figure 1. In addition to practical signals possessing finite switching times, the signal will present with ringing (oscillations) or rounding of the edges of a signal transition. These effects are present within digital signals due to the component values of physical hardware, for example a capacitor, inductor, wire or a PCB trace. A PCB trace will have an inductance L, capacitance C and a resistance R value giving it an L-C-R circuit response. Having accurate L-C-R models, as illustrated in Figure 3, to predict how practical circuitry will respond to high frequency clock signals has been identified as one of the critical components in high-speed circuit design [8].

Figure 3: L-C-R Circuit Example

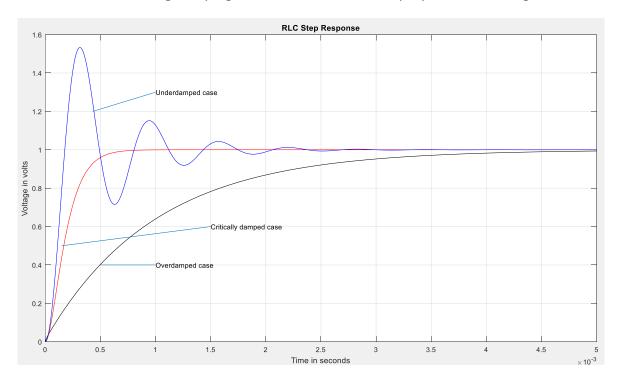

Theoretically simulating the behaviour of an L-C-R circuit gives an indication of the phenomena that occurs when applying signals of this nature to practical circuitry. Using the circuit illustrated in Figure 3, the source voltage is set to be  $V_1$  = 1V, the capacitance C = 1 $\mu$ F, the inductor L = 10 $\mu$ H and the resistor values for the underdamped (UD), critically damped (CD) and over damped (OD) responses are  $R_{UD}$  = 40 $\Omega$ ,  $R_{CD}$  = 200 $\Omega$  and  $R_{OD}$  = 1 $k\Omega$ . Using MATLAB, the behaviour of an L-C-R circuit is modelled to examine the step response with 3 different values of damping resistance. Figure 4 illustrates the different step responses of an L-C-R circuit with an increasing damping resistance to control the properties of the signal.

Figure 4: L-C-R Step Response

The blue trace shows the underdamped step response illustrating ringing on the peak of the signal. In relation to the signals produced by the FPGA, this case is likely to occur when using an excessive drive strength and 'Fast' edge rate setting, resulting in excessive drive current. The red trace shows the critically damped case, which is likely to occur when using a low-end drive strength setting and 'slow' edge rate. Finally, the critically damped case shows when the damping resistance is too high and the rise time of the signal is drastically increased. This case

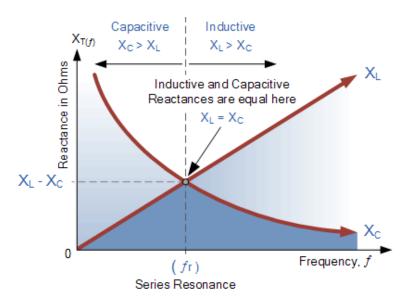

is unlikely to occur when outputting signals from the FPGA as the damping resistance is unlikely to be this excessive on the PCB designed for this project, yet it is included for illustrative purposes of all cases of an L-C-R circuit response. The impact of these effects on the frequency spectrum will vary between each case. The underdamped case, with the ringing on the peak and troughs of the signal, will introduce additional harmonics into the spectrum at the frequency in which it is oscillating. The critically and overdamped case increases the overall rise time of the signal. As a result of damping the signal the harmonics that are present within the frequency domain will be attenuated ultimately altering the EMC performance of the system and integrity of the signals produced. The frequency response of an L-C-R circuit must be taken into account when designing high speed digital circuits. The reactance of the inductor and capacitor shown in Equation 2 and Equation 3 respectively will impact upon the signal applied and ultimately its frequency domain behaviour. As the frequency of the harmonics increases the inductive reactance (X<sub>C</sub>) increases the capacitive reactance (X<sub>C</sub>) decreases.

$$X_L = 2\pi f L$$

Equation 2: Inductive Reactance  $X_C = rac{1}{2\pi f C}$

**Equation 3: Capacitive Reactance**

This relationship between frequency and component reactance leads to a capacitive and inductive region along the frequency spectrum as illustrated in Figure 5. When designing high speed digital circuitry the effect of this behaviour must be taken into account. The fundamental frequency of the signal in question is chosen to be at the resonance point of the series L-C-R circuit, ensuring minimal attenuation as a result of the parasitic component properties.

Figure 5: L-C-R Frequency Response [9]

The rounding of the signals transitional edges stem from the attenuation of the harmonics of the signal being used. The increasing frequency of the harmonics present means that the inductive reactance that they encounter is increasing linearly with frequency. Some potential impacts from this attenuation is that the hardware receiving the data may not be able to sufficiently sample the signals being received leading to timing issues and data loss.

## 1.2 Historical Review of EMC Studies of Integrated Circuits

Earlier studies into the EMC performance of integrated circuits were aimed towards the immunity of components in harsh Electromagnetic environments. The evolution of integrated circuits meant that the power consumption and frequency of transmitters were increasing adding to the severity of the EM environment. Research into the immunity of ICs within circuit operation became a vital part of academic research. Whalen [10] studied the effect of EMI on devices such as the 7400 series NAND gates and showed that the output varied with incident power. From the effects noticed during immunity testing, Larson et al proposed modifications to the transistor model to account for the unusual conditions of RFI [11]. The new Ebers-Moll model allows for the RF behaviour of a transistor to be predicted when the interference conditions are theoretically deduced rather than observed. The introduction of CMOS technology began to replace the existing bipolar technologies (TTL) due to the vast improvement to the power dissipation, and comparisons of their susceptibility to EMI began. Kenneally et al [12] reported that the new CMOS technologies were less susceptible to EMI at frequencies above 5 – 10 MHz, and virtually insensitive to EMI at frequencies above 100 MHz. Laurin et al [13] investigated the effect of EMI on the 6809 microprocessor from Motorola and recorded function loss in oscillator circuits when placed near a current loop. The advancement of CMOS technologies allowed for larger and denser devices; and calls for low-emissive, high-immunity ICs within the frequency band 1MHz – 1GHz began to rise [3]. Research into investigating and controlling the emissions from ICs began in an attempt to investigate their contribution to the EM environment [3]. It was not until the 1990s that the impact of emissions from embedded components was considered [3]. The origins of IC emission measurements stem from a phenomenon identified as simultaneous switching noise (SSN), where studies showed that the noise amplitude was influenced by the number of switching output drivers and grounding techniques [14]. Research into the effect of logic families and circuit design techniques was published by Robinson et al [1] in 1998 who discovered that emissions in the near and far field were dependent upon a combination of the component choice and circuit design. Component choice in this case is relating to the variation of logic inverters from the CMOS & TTL families, and the circuit design was the inclusion of a ground plane to reduce the loop size of the traces on the PCB. Peak emission measurements were taken in an open area test site and the greatest improvement to emissions was observed when technologies with slower switching frequencies and EMC design techniques were combined, delivering a reduction to emissions by over 30dB. Considering the component technology - independent of any circuit design techniques - the 74ACT technology delivered the highest peak emissions in comparison to the 74LS devices with a mean difference of 8dB. This established that the rise and fall times can have a

substantial impact on the amplitude of harmonic content observed - irrelevant of any circuit design techniques applied.

The parasitic emissions from an IC are attributable to the I/O and the digital synchronous cores. Work by Takashima et al [15] proposed that the number of I/O used directly influenced the parasitic emissions from ICs. Van Wershoven [16], using the Taguchi method in an attempt to build a picture of the EMC performance of ICs, discovered that controlling attributes such as the slew rate of the I/O drivers reduced the impact on supply and ground bounce present within a system. With an increase to the number of I/O affecting emissions, combining this with a faster slew rate could produce an exponential rise to EMI in the near and far field. Should a device with variable slew rate be used within a system - where it is supply voltage critical - then variations on the supply and ground rails could potentially cause a malfunction to the system operation. In addition to the number of I/O used and the technology chosen, the software or firmware implemented within a programmable device will affect the overall emissions [17]. Fioro et al [17] conclude that emissions produced are influenced by the embedded software within an 8-bit microcontroller. Often within digital circuits, there are multiple ways of implementing a design to achieve the same function, so care should be applied when utilising a device such as a microprocessor. Methods of reducing these parasitic emissions from ICs came to the forefront of research as calls for low emissive devices were growing rapidly. The most popular and effective methods of controlling the levels of radiated EMI was the inclusion of on-board and on-chip decoupling capacitors [3], and a technique known as spread spectrum clock generation (SSCG). Hardin et al [18] proposed this method of SSCG which intentionally spreads the energy of a narrowband signal to wideband reducing the amplitude of the harmonics. An attenuation as high as 13dB was recorded from this testing and can be applied to emissions produced by the digital synchronous core and I/O to similar effect.

Power supply noise is another consideration when analysing the EMC performance of integrated circuits (ICs). Research has delved into not only practically testing the ICs but developing methods into the prediction of how the power supply noise may present itself based on IC operation and implementation. Modern devices containing millions of gates all switching state simultaneously causes substantial current to be drawn from the power distribution network (PDN) [19]. Laurent [20] found that power supply noise was likely to cause timing issues before any other failures within the IC occurred. Laurent [20] also found that the measured peak noise is largely irrelevant and the average noise during switching is a greater factor when determining the EMC performance of an IC. Ren [19] et al, found that once the PDN has been established the power supply noise can be estimated from the impedance network. The simulated and measured values were relatable in both the time and frequency domain [19]. The designer must be aware of all potential sources of EMI and the implications of using a device or technology within a design. Having this quantitative knowledge in the earlier stages of a design process will allow for EMC measures, such as effective shielding and grounding, to be implemented. From this, an optimised design can be achieved that satisfies both EMC compliance and signal integrity.

#### 1.3 FPGA Overview

Section 1.3 gives an overview of the architecture of an FPGA and examines the circuitry relating to the I/O buffer standards. More specifically an overview into the two standards that form the basis of this research, Low Voltage CMOS (LVCMOS) and Low Voltage TTL (LVTTL).

#### 1.3.1 FPGA Basic Architecture

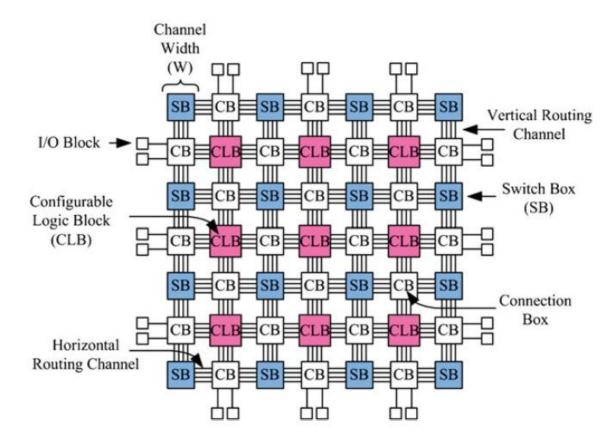

The architecture of an FPGA illustrated in Figure 6, consists of configurable logic blocks (CLBs), I/O Blocks and Routing Channels; all interconnected by Connection Boxes (CB) and Switch Boxes (SB). The vertical and horizontal routing channels are linked through switch boxes and the CLBs are connected to the routing channels through connection boxes [21]. The routing channels allow connections among the internal logic blocks to implement any user defined digital circuit.

Figure 6: FPGA Architecture Overview [21]

#### 1.3.1.1 Configurable Logic Block

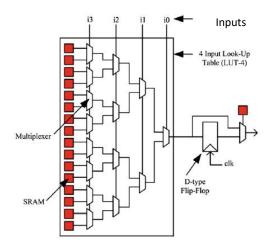

The configurable logic block is the component of an FPGA that provides basic logic and storage functionality for digital circuit designs. Each of the configurable logic blocks consist of an array of Basic Logic Elements (BLEs) varying from 4 to 10 - depending upon the manufacturer [21]. The basic logic elements are made up of an n-bit look-up table (LUT), a D-Type Flip-Flop, and a 2x1 multiplexer (MUX), as shown in Figure 7.

Figure 7: Basic Logic Element [21]

The Static RAM (SRAM) cells of an LUT are used for routing the interconnections and programing the Configurable Logic Blocks that implement the logical functions of a design [21]. The D-type flip-flop allows the user to synchronise the output with the internal clock or act as a storage element. The multiplexer gives the designer the choice between the output of the D Type Flip-Flop or the LUT.

#### 1.3.1.2 FPGA I/O Block

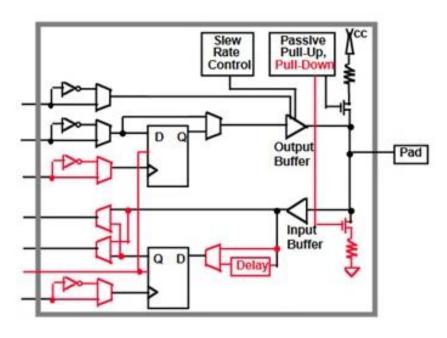

The FPGA I/O block (IOB), shown below in Figure 8, connects the internal logic to the outside world allowing the designer to communicate with peripherals within the circuit or system. The buffering stage of the IOB consists of the input and output buffers. The input and output buffers have the ability to apply a passive pull up or pull down to provide a known state to the connecting PCB traces. The array of D-Type Flip Flops and Multiplexers form the input logic and output logic circuitry. A Spartan 6 FPGA I/O block contains two IOBs, two ILOGICs, two OLOGICs and two IODELAYs shown in Figure 9 [22].

Figure 8: FPGA I/O Block Overview [23]

Figure 9: SPARTAN-6 FPGA I/O Block [22]

The I/O Blocks fall into two categories either single-ended standards or differential standards. The focus of this research is limited to following standards - LVCMOS (1.2V, 1.5V, 1.8V, 2.5V and 3.3V) and LVTTL (3.3V) single-ended I/O standards.

#### 1.3.2 FPGA LVCMOS & LVTTL Logic Standards

The properties of the two I/O logic standards are well documented throughout established literature [24], [25], [26]. The more notable differences being switching speed, power dissipation, output drive capabilities, and logic levels [24]. Each of the I/O buffers within the Spartan-6 FPGA have the ability to configure the logic standard, drive strength and slew rate of the respective drivers. The slew rate setting within the FPGA controls the rate at which the output of the buffer can change. Varying the drive strength introduces additional transistors in parallel to change the current delivered to the load. A combination of an excessive drive strength and a fast slew rate can introduce phenomena such as ringing (overshoot and undershoot) and rounding of the transitional edges. It is likely that because of these phenomena, issues such as timing, component oscillations and an increase to the overall emissions produced will occur.

#### 1.3.3 FPGA Output Buffer Circuit Overview

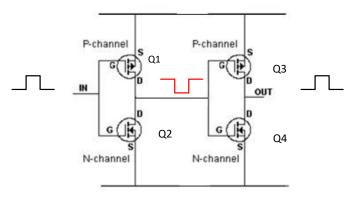

The FPGA I/O buffers hold the configuration illustrated in Figure 10, consisting of two P-channel and two N-channel MOSFET devices. This buffer configuration is used to meet the LVCMOS (Low Voltage Complimentary-Metal-Oxide-Semiconductor) and the LVTTL (Low Voltage Transistor-Transistor-Logic) Standards.

Figure 10: Output Buffer Circuit [27]

When source of Q1 is more positive than the gate, the channel is turned on and providing that the threshold voltage ( $V_{TH}$ ) is positive enough current flows between the source and the drain. As the input signal transitions to logic '1' Q1 turns off and as it returns again to logic '0' Q1 turns on again. The N-Channel Q2 transistor having zero voltage between the gate and the source remains in the OFF state. The second parallel combination of Q3 and Q4 performs the same function as described with Q1 and Q2 and inverts the signal back again to its original state.

#### 1.3.4 Logic Family Comparison

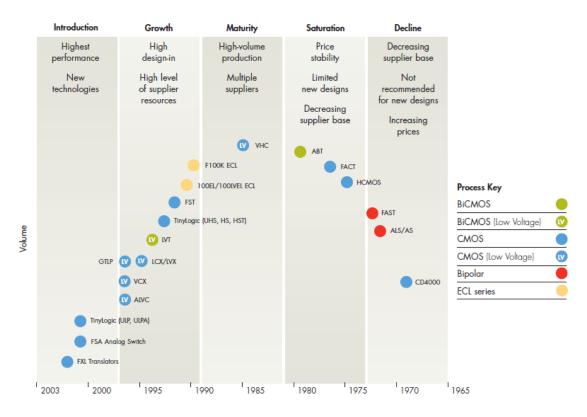

The evolution of logic families has seen CMOS technologies dominate and the bipolar TTL family become an almost extinct logic family except for demonstrations and academia. Figure 11 illustrates a timeline for the progression of logic families since the 1960s.

Figure 11: Logic Family Timeline [26]

The bipolar TTL logic family was the most commonly used logic family in industry and academia in the 1960s to 1970s. The introduction of CMOS technologies in the late 1970s began to displace TTL due to its superior performance and improved susceptibility to EMI. The two logic families that dominated the 1980s and 1990s were the CMOS and BiCMOS. The BiCMOS logic family addressed the need of interfacing with CMOS components requiring TTL logic levels yet keeping the improved performance of CMOS. The low voltage derivatives of the CMOS and BiCMOS were becoming more and more available throughout the 1990s to 2000s as the demand for low power consumption and denser devices were growing. The TTL logic family is not used within new designs today, instead CMOS technology can provide an output that is compatible with the TTL standard and it is this reason the Spartan 6 contains the functionality to provide a TTL output without the drawbacks of using TTL architecture.

Comparing the characteristics from a selection of bipolar and CMOS logic families, it is possible to anticipate which family will produce the greater magnitude of EMI during radiated emissions testing. Paying particular attention to propagation delay and supply current, it becomes clear to predict which family will produce the higher level of emissions.

| Logic Family | Туре  | Propagation Delay<br>(ns) | Supply Current (mA)<br>@ Max Spec and Max Vcc |

|--------------|-------|---------------------------|-----------------------------------------------|

|              | LCX   | 6.5                       | 0.01                                          |

| CMOS         | LVX   | 12.0                      | 0.04                                          |

| CIVIOS       | HC    | 25.0                      | 0.08                                          |

|              | AC    | 7.5                       | 0.08                                          |

|              | FASTr | 3.9                       | 75                                            |

| Bipolar      | FAST  | 6.5                       | 90                                            |

| (TTL)        | AS    | 6.2                       | 90                                            |

|              | ALS   | 10.0                      | 27                                            |

Table 1: A Comparison of Logic Families [26]

The figures detailed in Table 1 indicate that the bipolar families are capable of much faster switching speeds and higher current consumption than the equivalent CMOS families. The FASTr technology records a propagation delay of 3.9ns whereas the CMOS technologies record a delay of 6.5ns - almost half of that of the bipolar family. Comparing the supply current of the LVX and ALS logic type, both exhibiting similar propagation delays, the LVX supply current drawn is at approximately 40µA, whereas the ALS records a supply current of 27mA. From these figures in Table 1, it becomes clear that the TTL family has a higher switching speed than the CMOS equivalent yet it comes with greater power consumption as a result. From this behaviour it is reasonable to expect the higher level of emissions to be produced from the LVTTL logic family than the CMOS equivalents. The ability to control any unnecessary emissions from the overall system will not only reduce the EMI produced it will also deliver a more cost effective system. Reducing characteristics such as the switching speed and power consumption will not only reduce the emissions it will require a smaller power supply.

#### 1.4 Overview of Thesis

The following sections of this thesis detail the research carried out into the radiated emissions produced by the chosen Xilinx Spartan-6 FPGA and the design of the hardware used for testing. Section 2 gives an overview of the PCB hardware specifically designed for this research project and the VHDL code implemented to produce the required signals for testing. An overview of the key hardware blocks, justification for their inclusion and how they potentially impact upon any results gained is included. An overview of the VHDL code used for testing is included to allow for repeatability and to account for the behaviour of the FPGA. The description of the VHDL code covers the key aims of the code and the cores and primitives used for this testing.

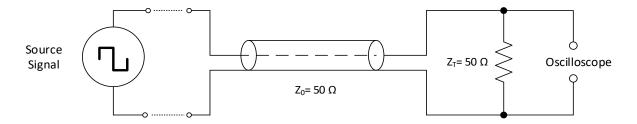

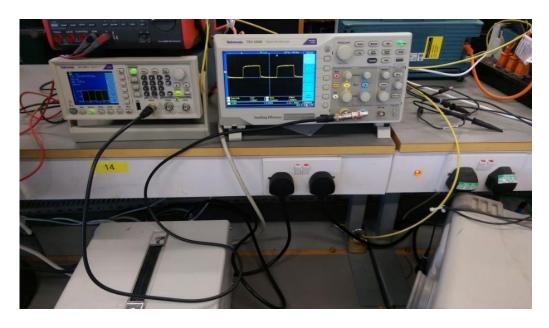

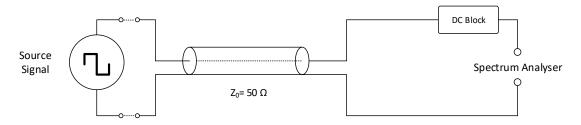

Section 3 establishes and validates a test plan, which will ultimately be used to examine the time and frequency domain behaviour the signals produced by the FPGA. Firstly, to validate the test plan a calibrated or 'known' source in the form of a signal generator has been used to illustrate how the edge rate of signals impact the harmonic content recorded. This establishes a practical understanding of how the harmonic content varies from the theoretical expectations. The time and frequency domain measurements are taken through a  $50\Omega$  coaxial cable from the measurement instrumentation to the  $50\Omega$  output of the signal generator. Section 4 is a theoretical and practical analysis of the harmonic content produced by the signals from the FPGA. This is intended to illustrate and examine the behaviour of the signals and account for any discrepancies or phenomena that occur within the signals produced. The time and frequency domain measurements are taken through a  $50\Omega$  coaxial cable from the measurement instrumentation to a SMa connector that is part of the PCB architecture.

Section 5 examines the emissions produced from each of the FPGA I/O driver settings individually. Logic Standard, Drive Strength and Edge Rate are varied one by one to quantify how these settings impact the peak level of harmonics recorded. The measurements are taken through an H-field probe in the near field and record the voltage on the coil of the probe.

Section 6 gives a full overview of all of the radiated emissions measurements taken for each I/O driver settings. The results within section 6 are organised by logic I/O standard, and within each of the standards, a baseline has been stated to quantify the increase or decrease to the peak level emissions produced by the FPGA.

Section 7 delivers the concluding comments on the research project and gives suggestions on further research beyond this project.

Section 0, contains the additional information relating to this project. This is inclusive of the schematics for the PCB designed for this project, the GERBER files used to manufacture the PCB, the VHDL code to program the FPGA and finally the plots of emissions produced from each I/O driver setting.

## 2 Circuit for Testing - Architecture & Design

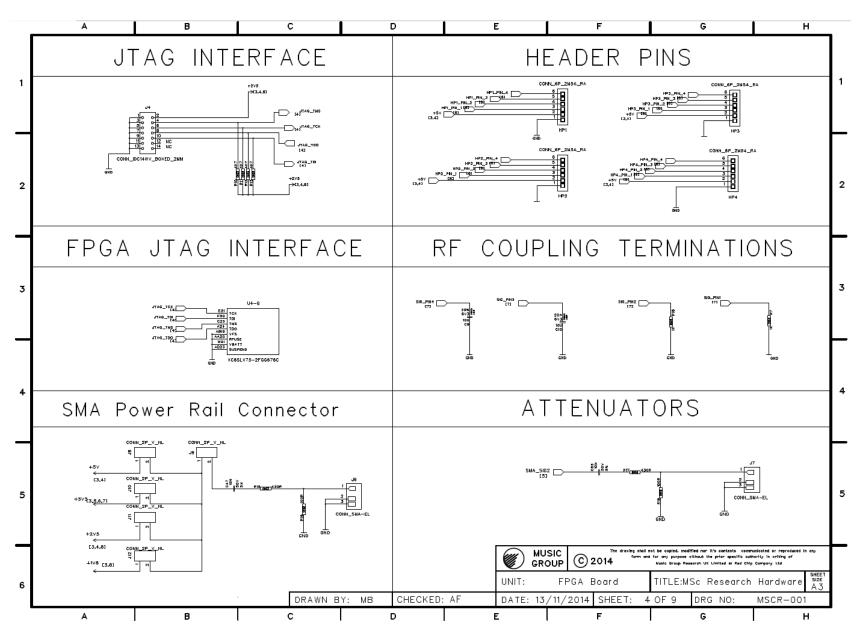

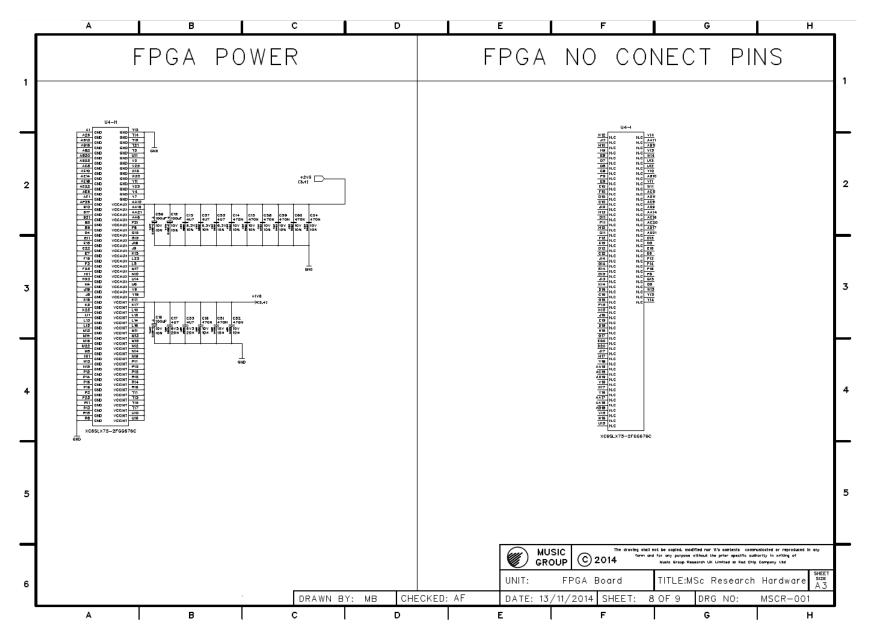

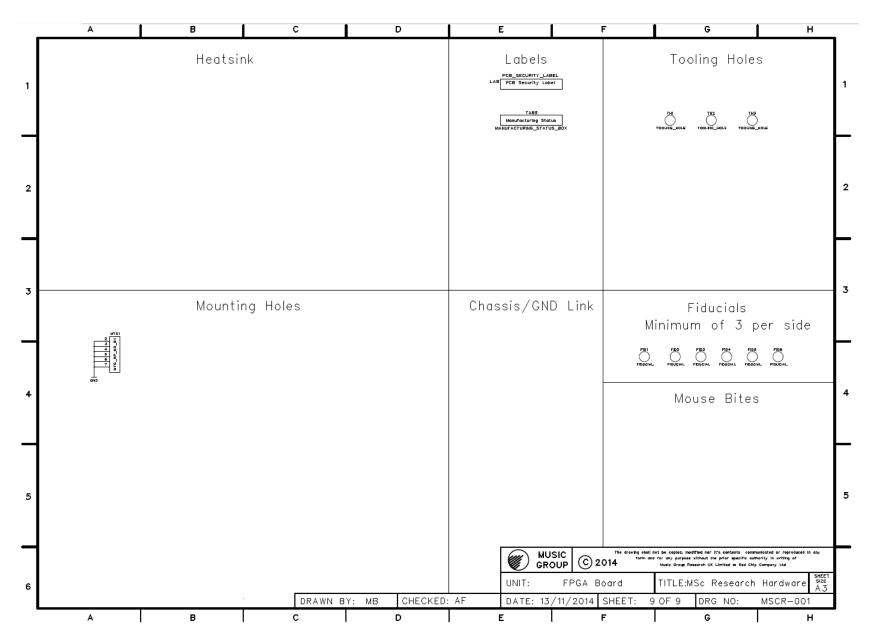

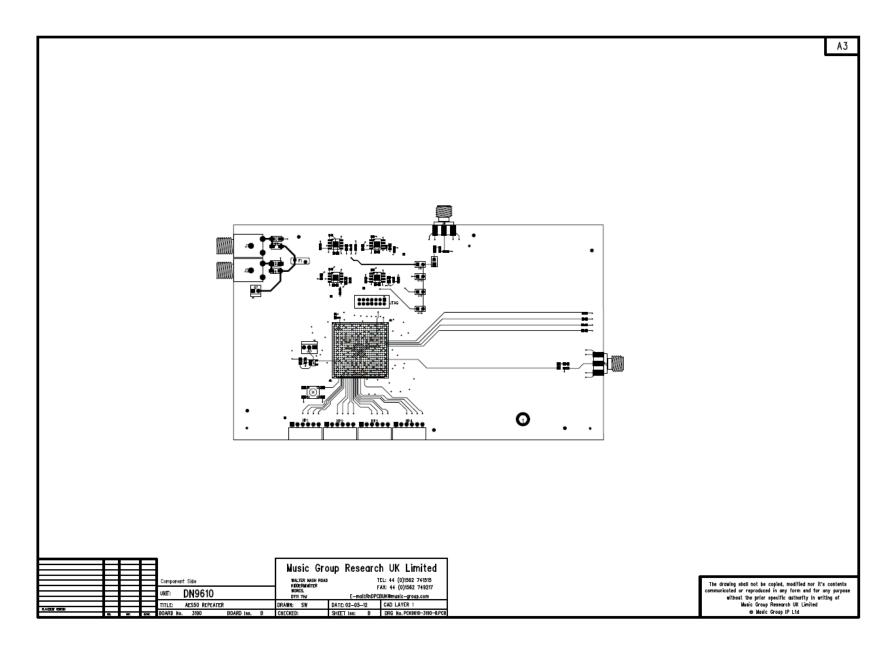

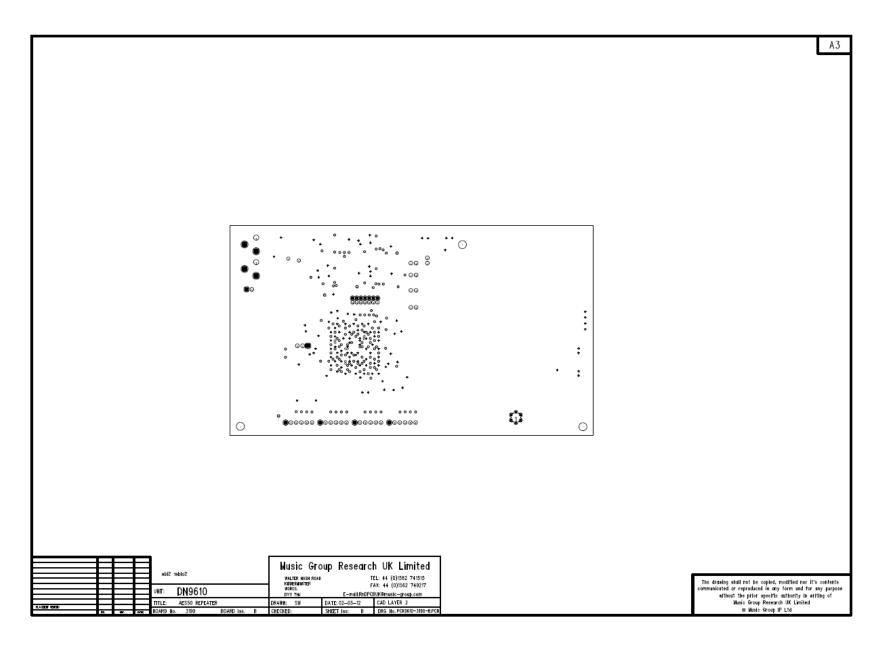

Section 2 describes the hardware designed and manufactured for this research project and the VHDL code used for testing. Included within this section is a description of the circuitry designed to obtain the required measurements and the circuitry implemented to make the FPGA functional. The schematic, GERBER files and VHDL are located in the Appendix 1, Appendix 2 and Appendix 3 respectively.

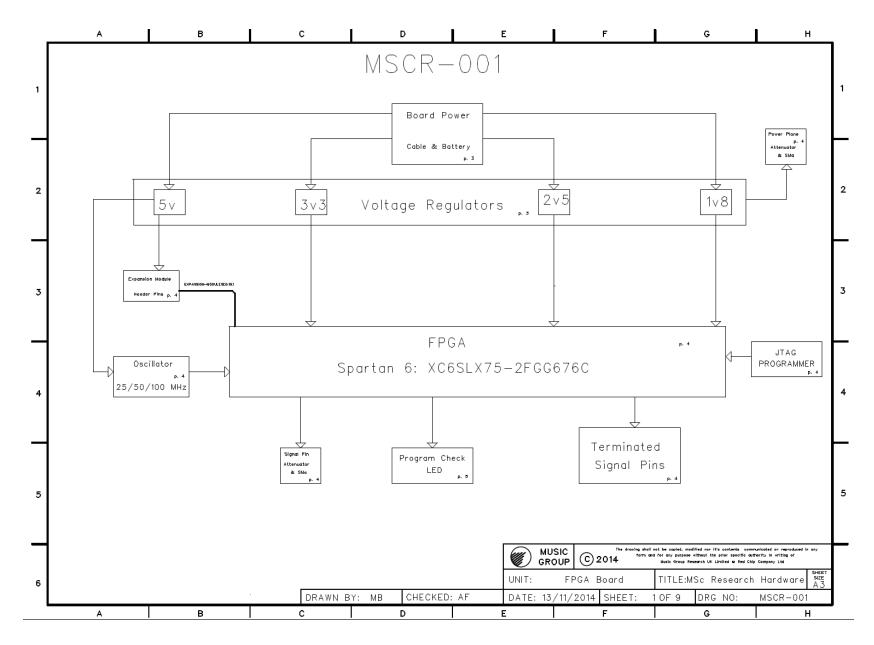

## 2.1 Hardware Design Overview

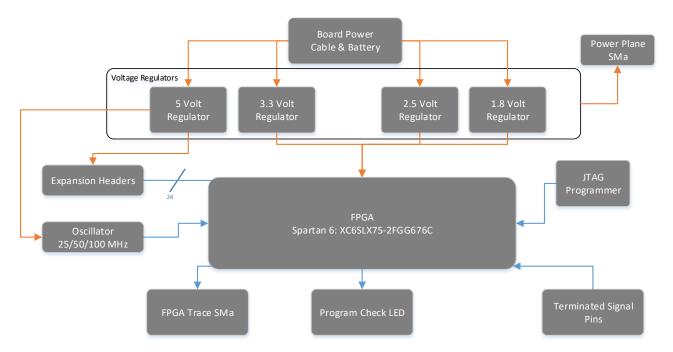

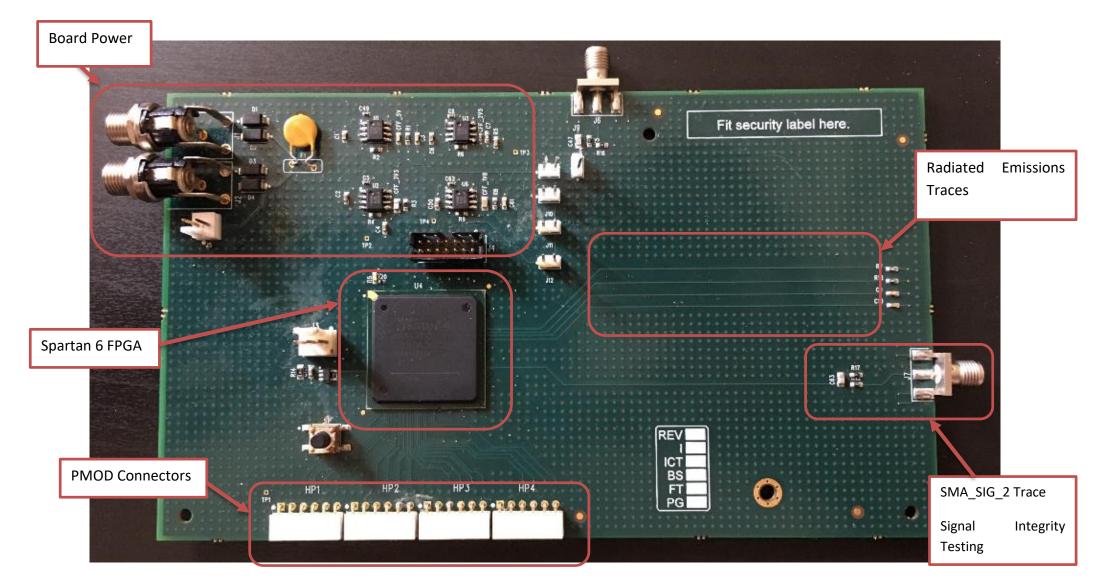

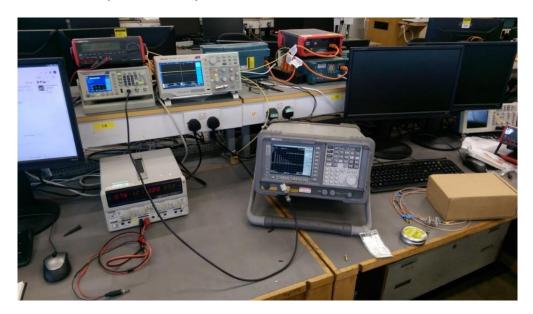

The PCB shown in Figure 13, has been designed with the overall aim of obtaining radiated emissions measurements when varying the I/O driver settings and standards. The hardware present on the board has been kept to a minimum to restrict any emissions from surrounding circuitry.

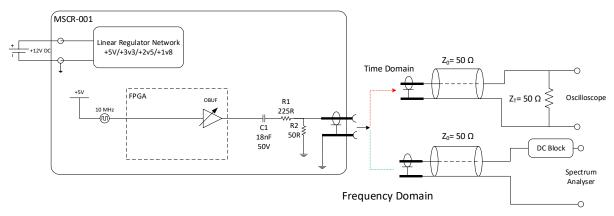

Figure 12, illustrates a conceptual overview for the PCB hereinafter referred to as the MSCR-001 PCB stating the architecture of the board.

Figure 12: MSCR-001 Hardware Architecture

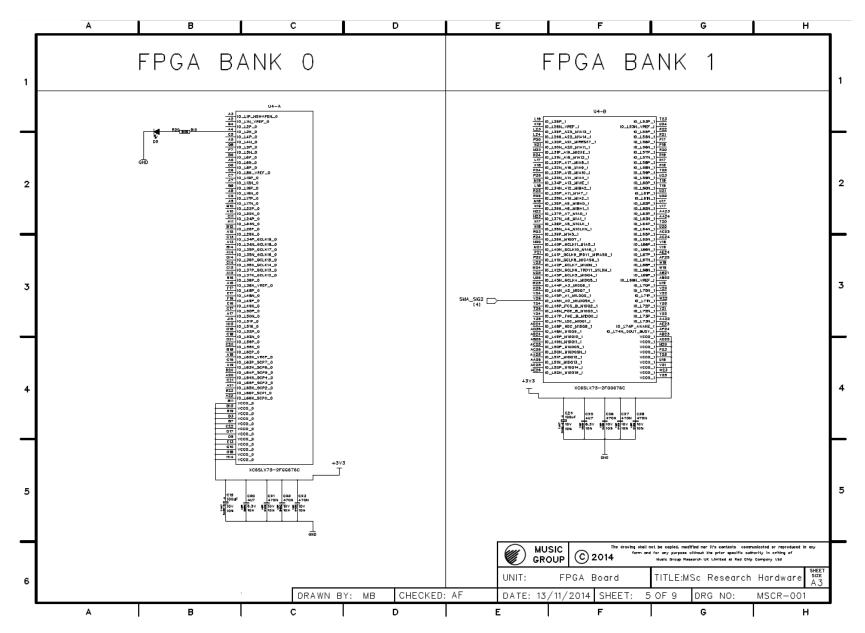

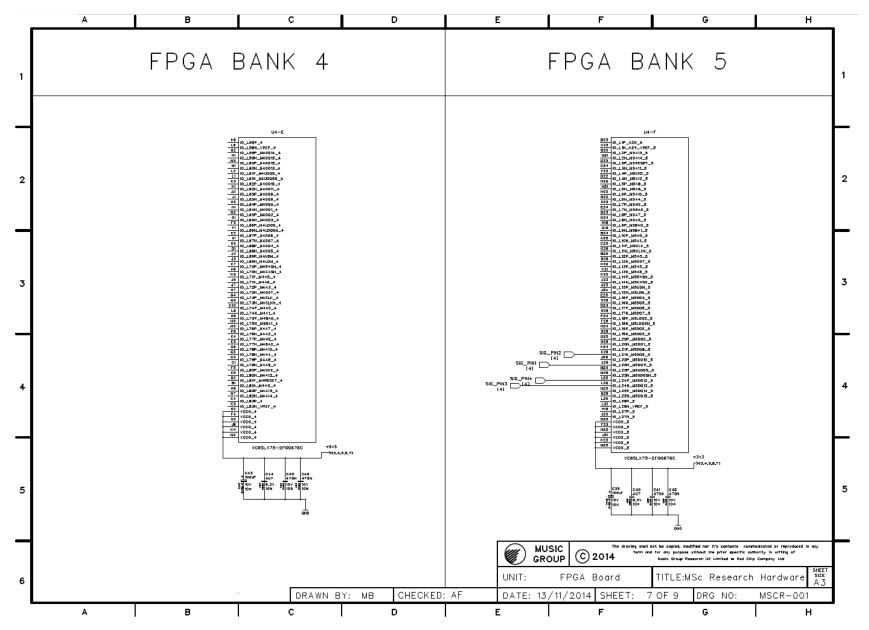

The chosen FPGA for this research is the Spartan 6: XC6SLX75-2FGG676C from Xilinx. The device is a 676 pin Ball Grid Array (BGA) package device and is widely used within the engineering industry for such applications as Audio and Digital Signal Processing, meaning any results gained would be pertinent to current digital system designs. Xilinx have a substantial array of devices available that can be used with readily available design tools such as the Xilinx ISE Design Suite and excellent implementation support through their online datasheets.

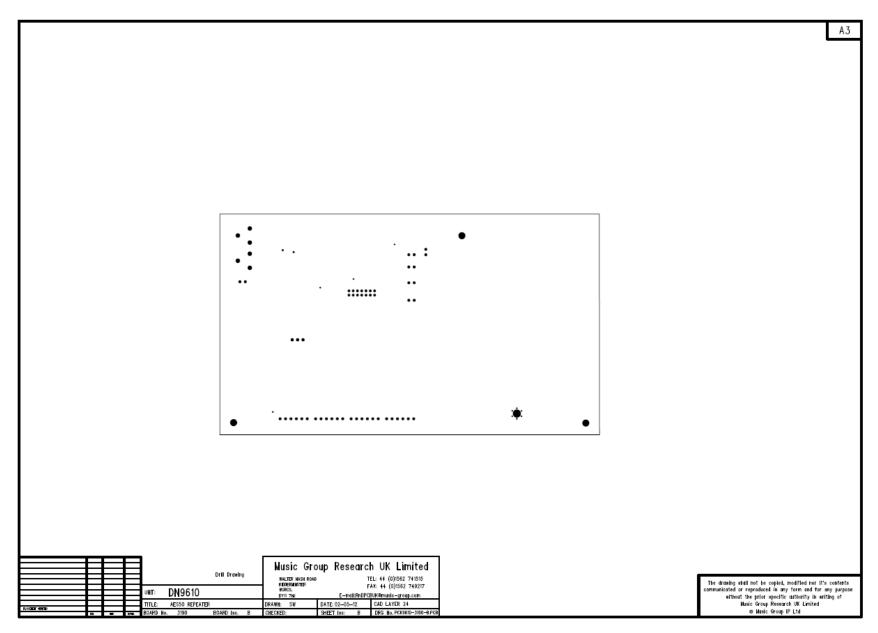

Figure 13: MSCR-001 PCB Overview

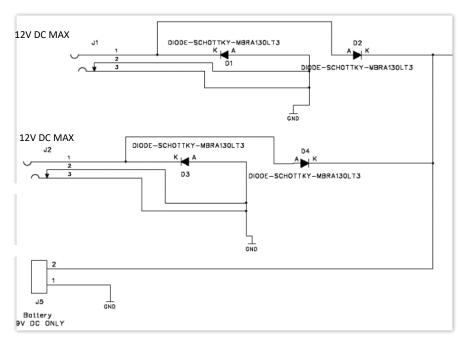

#### 2.1.1 Board Power

The input voltage to the PCB is designed to be +12 Volts DC allowing the board to be battery powered (J5) or powered from an AC/DC mains supply (J1 & J2) shown in Figure 14. The option to power the PCB by AC/DC mains supply allows for constant supply during development testing and the option to power the PCB via battery will allow the mains cables to be removed during radiated emissions testing. Mains and I/O cables have been identified as one of the potential antenna for radiating Electromagnetic Interference [28], [29], this functionality ensures that if the mains cables conduct EMI or act as an antenna to radiate emissions they can be removed entirely and the PCB powered via a battery.

Figure 14: MSCR-001 Board Power

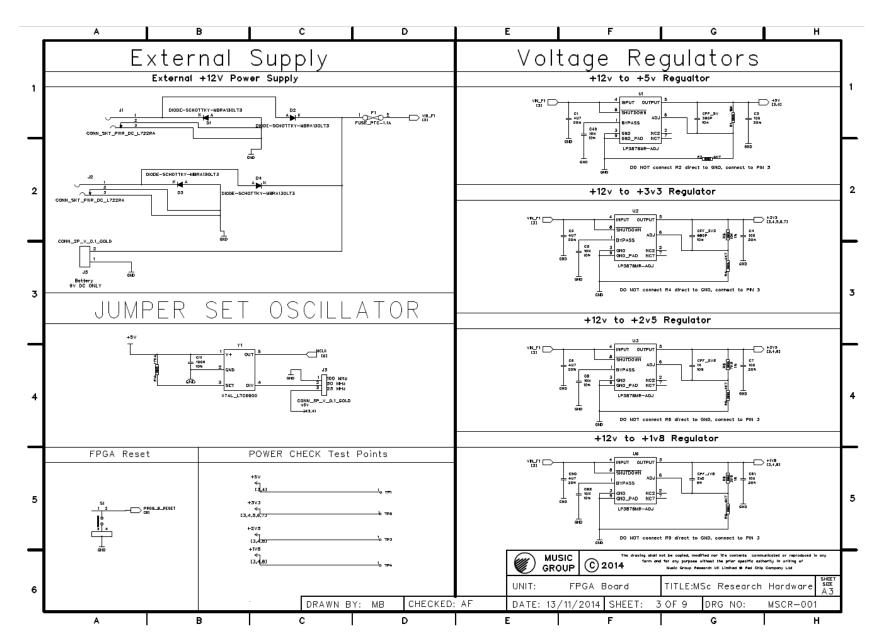

#### 2.1.2 Voltage Regulators

As with many systems containing integrated circuits of this nature, an array of voltages are required for the functionality of the FPGA. The use of other ICs within the circuit that could produce additional EMI needs to be avoided wherever possible. Ouyang *et al* [30] identify switching regulators as a potential source of EMI with the high and low side power MOSFTETs being one of the major sources of EMI. So with the goal of minimising EMI from the surrounding hardware, a linear voltage regulator has been chosen to achieve the voltage derivations required. Linear regulators could be considered an inefficient way to achieve voltage derivations in larger systems. However, for the purpose of this research achieving the required voltages without compromising the emissions results taken is paramount. The onboard linear regulators provide 5 volts, 3.3 volts, 2.5 volts and 1.8 volts. The 5 volts regulator is used to supply the Peripheral Module (PMOD) connectors to allow expansion beyond the MSCR-001 PCB and the oscillator IC. The remaining three voltage regulators are used to supply the FPGA - with the 3.3 volts powering the I/O banks, the 2.5 volts powering the programming interface and the remaining 1.8 volts is used to power the core of the FPGA.

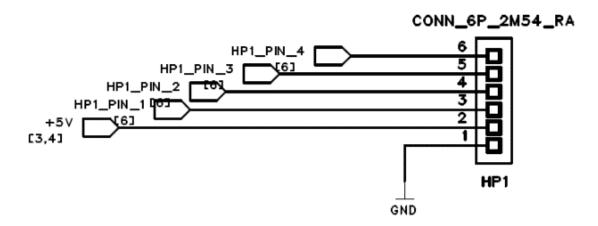

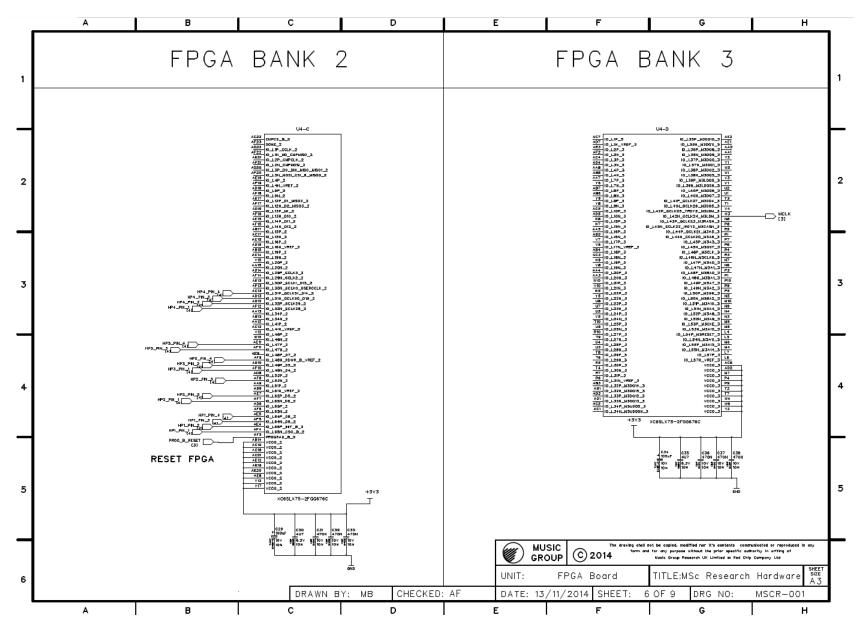

#### 2.1.3 Expansion Headers

A potential for expansion beyond the hardware committed to the PCB is present in the form of four PMOD connectors. This expansion approach is used extensively throughout demonstration boards and may prove to be useful for any additional circuitry that may be required. Each PMOD connector has two pins allocated to supply +5 volts and 0 volts return generated on the MSCR-001 PCB. This will allow further expansion past this board without the need for additional external power supplies.

Figure 15: MSCR-001 Expansion Header

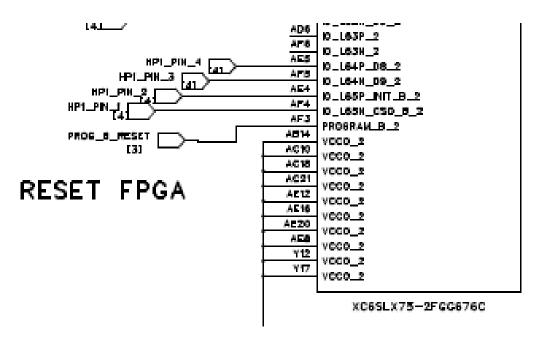

Referring to Figure 15, the remaining four pins on the PMOD connector have been allocated to I/O pins on the FPGA. The PMOD connectors have been labelled HP1, HP2, HP3 and HP4 the individual pins HP1\_PIN\_1 to HP4\_PIN\_4. They provide access to 16 I/O pins located in bank 2 on the FPGA as illustrated in Figure 16.

Figure 16: FPGA Expansion Port Nets

#### 2.2 Measurement Architecture

The measurement architecture on the PCB has been designed to allow measurements to be taken without the need for additional circuitry and to allow the FPGA to drive circuitry, which will not interfere with any emissions measurements gained. All measurement traces have been routed to have an impedance of  $50\Omega$  by controlling the track widths on the PCB.

The key elements of circuitry used for measurements on the MSCR-001 PCB are:

- Signal Integrity Measurement Traces

- Radiated Emissions Traces

#### 2.2.1 Signal Integrity Measurement Traces

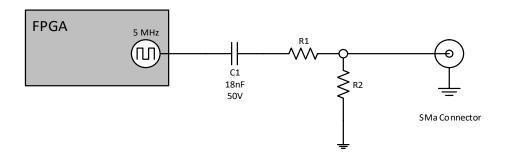

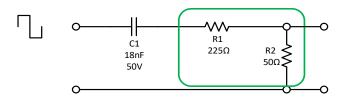

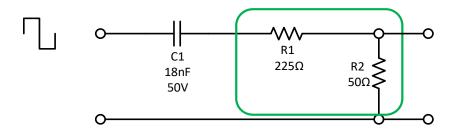

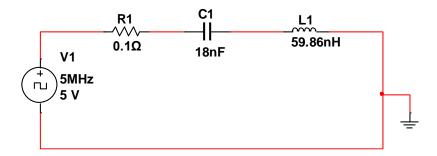

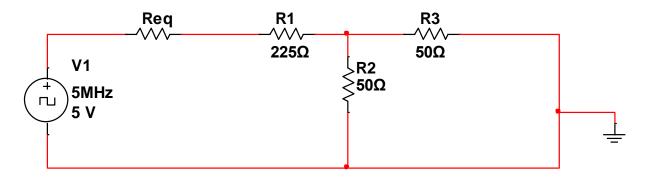

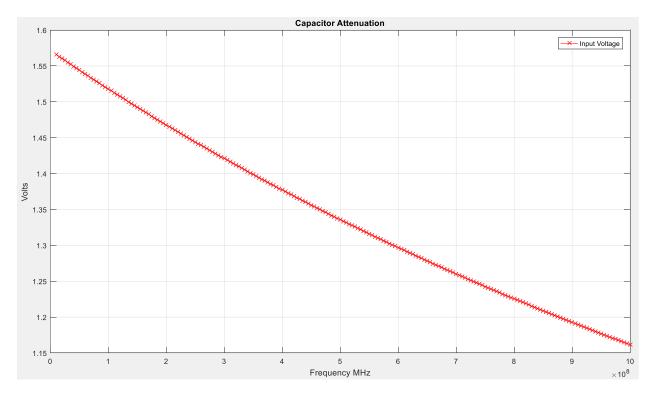

The first of the measurement traces shown in Figure 17, and connects to I/O pin V26 of the FPGA for examination of the signals under the various I/O driver settings. The trace includes a DC blocking capacitor (C1), L-attenuator (R1 & R2) and finally terminates with an SMA connector to allow connection to the measurement instrumentation.

Figure 17: SMA FPGA I/O Connection

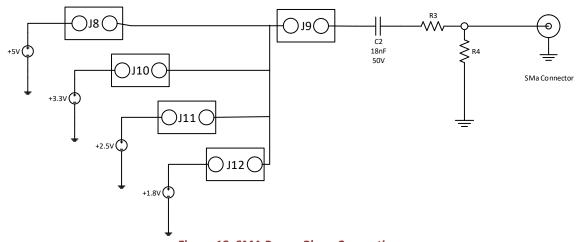

The second of the measurement traces shown in Figure 18 provides access to the power planes on the PCB to monitor noise as a result of the I/O settings within the FPGA. Power supply switching noise can be attributable to such phenomena as clock jitter [19]. Jumpers J8 – J12 allow selection of connection to each of the power planes, and the SMa connector is designed to interface with either the oscilloscope or spectrum analyser.

Figure 18: SMA Power Plane Connection

#### 2.2.2 Measurement Instrument Protection

The instrumentation protection is firstly in the form of a DC blocking capacitor, which will prevent any DC voltages damaging the front end of the measurement instruments. The second is a 10:1 attenuator which has been added to lower the potential of any voltages or transients to the front end of the instruments should they be able to bypass the DC blocking capacitor.

#### 2.2.3 DC Blocking Capacitor

Using Equation 4, the DC blocking capacitor has been chosen to have a low reactance value at the 5MHz source signal frequency. A capacitor behaves like a short at higher frequencies and open circuit at lower frequencies.

$$X_c = \frac{1}{2\pi fC}$$

**Equation 4: Capacitor Reactance Formula [24]**

Figure 19: DC Blocking Capacitor

#### 2.2.3.1 Capacitor Reactance

The reactance value  $X_c$  has been chosen to be less than 2 Ohms at the source signal frequency. Rearranging the Equation 5 to make C the subject:

$$C = \frac{1}{2\pi \times 2 \times (5 \times 10^6)} = 15.9_{nF}$$

**Equation 5: Transposed Capcitor Reactance Equation**

A value of 18nF has been used, as this is the nearest possible value of commonly available capacitors.

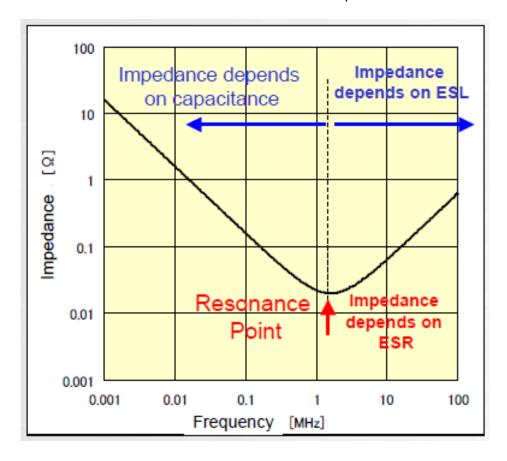

#### 2.2.3.2 Capacitor ESR & ESL

Including a DC blocking capacitor introduces along with it Equivalent Series Resistance (ESR) and Equivalent Series Inductance (ESL). These properties of the capacitor will have an impact on the signals recorded by the spectrum analyser. The ESR is dependent upon the technology of the capacitor used. Capacitors such as wet tantalum can have ESR values in the order of  $5\Omega$ . This additional series resistance will cause attenuation to the peak levels of the harmonics recorded as the resistance will cause a voltage drop across it. To minimise this effect, the technology of the DC blocking capacitor is ceramic, as this technology possesses one of the lowest ESR values for capacitors.