## MODULAR MULTILEVEL CASCADED FLYING CAPACITOR STATCOM FOR BALANCED AND UNBALANCED LOAD COMPENSATION

Oghenewvogaga Oghorada

Submitted in accordance with the requirements for the degree of Doctor of Philosophy

The University of Leeds School of Electronic and Electrical Engineering

August, 2017

The candidate confirms that the work submitted is his/her own, except where work which has formed part of jointly-authored publications has been included. The contribution of the candidate and the other authors to this work has been explicitly indicated below. The candidate confirms that appropriate credit has been given within the thesis where reference has been made to the work of others. Most materials contained in the chapters of this thesis have been previously published in research articles written by the author of this research (Oghenewvogaga Oghorada).

The research has been supervised and guided by Dr. Li Zhang, who appears as co-author on these articles. All the materials included in this document is the author's entire intellectual ownership.

A.) Details of the publications which have been used are given below;

In chapter 3:

Oghorada, OJK, Zhang, L and CJ Nwobu "Performance Evaluation of Pulse Width Modulation Techniques for Losses Reduction in Modular Multilevel Flying Capacitor Converter". Published in 2016 Proceedings of the IET 2016 – 8<sup>th</sup> International Conference on Power Electronics, Machines and Drives (PEMD 2016), IET, **DOI:** 10.1049/cp.2016.0376.

In chapter 5:

Nwobu, CJ, OJK Oghorada, Zhang, L and I. B. Efika "A modular multilevel flying capacitor converter-based STATCOM for reactive power control in distribution systems". Published in 2015 Proceedings of the EPE 2015 – 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), **DOI:** 10.1109/EPE.2015.7309085.

In Chapter 6:

Oghorada, OJK and Zhang, L "*Control of a Modular Multi-level Converter STATCOM for Low Voltage Ride-Through Condition*". Published in 2016 Proceedings of the IECON 2016 - 42nd Annual Conference of the IEEE Industrial Electronics Society, IEEE, **DOI:** 10.1109/IECON.2016.7794143.

Oghorada, OJK, and Zhang, L "Control of a Single-Star Flying Capacitor Converter Modular Multi-level Cascaded Converter (SSFCC-MMCC) STATCOM for Unbalanced Load Compensation". Published in 2016 Proceedings of the IET 2016 – 8<sup>th</sup> International Conference on *Power Electronics, Machines and Drives (PEMD 2016), IET,* **DOI:** 10.1049/cp.2016.0375. Oghorada, OJK and Zhang, L "Unbalanced and Reactive Load Compensation using an MMCC – based SATCOM with Third Harmonic Injection", Submitted in Industrial Electronics System Transaction Journal, IEEE. Under Review.

Oghorada, OJK and Zhang, L "*Analysis of Star and Delta Connected Modular Multilevel Cascaded Converter-Based STATCOM for Load Unbalanced Compensation*", Published in International Journal of Electrical Power and Energy Systems, Elsevier, DOI: https://doi.org/10.1016/j.ijepes.2017.08.034.

Oghorada, OJK and Zhang, L "*Comparison of Star and Delta Configured MMCC based STATCOM for Unbalanced and Reactive Load Compensation*". Submitted in 2017 for IECON 2017 – 43rd Annual Conference of the IEEE Industrial Electronics Society, IEEE. Accepted.

B.) Details of the research contained within these publication which are directly attributed to Oghenewvogaga Oghorada with the exception detailed in C,

The published research is entirely attributed to Oghenewvogaga Oghorada: the introduction section, the novel ideals in the papers, the pulse width modulation FC-MMCC analysis, overlapping hexagon space vector modulation using three and two-level hexagon, derivations and implementation of various zero sequence components under unbalance load and low voltage ride through and all the editing process of the manuscripts.

C.) Details of the contributions of other authors to the research.

Dr. Li Zhang is the co-author for all the publications listed above. These have all been written under her supervision, benefiting from excellent technical advice, guidance and valuable feedback.

C.J Nwobu performed proofreading and carried out voltage regulation for FC-MMCC based STATCOM. This copy has been supplied on the understanding that it is copyright material and that no quotation from the thesis may be published without proper acknowledgement.

## Assertion of moral rights (optional):

The right of Oghenewvogaga Oghorada to be identified as Author of this work has been asserted by him in accordance with the Copyright, Designs and Patents Act 1988.

© 2017 The University of Leeds and Oghenewvogaga Oghorada

#### Acknowledgements

I would sincerely like to appreciate my supervisor Dr. Li Zhang, who in every way showed so much enthusiasm in carrying out this research work. I acknowledge her advice, understanding and assistance during the project. I would like to show my gratitude to Dr. Ikenna Bruce Efika and Dr. John Nwobu, who were previous PhD students that started this work. Many thanks to Edward Bray for assisting with some aspects of the experimental rig.

To my friends, well-wishers and colleagues especially to the international student network (a) St. George church, Leeds, Andrew, Charles, Obinna, Tomisin, Mrs Awonaya, Joy, Nabila, Han, Sultan, Ase; I couldn't have achieved this without your words of encouragement and support. My special thanks goes to My Adora for her love, care and understanding during this research work. Also, my heartfelt appreciation goes to the Delta state scholarship board for their financial assistance during this research.

To my parents, Evang. & Evang. (Mrs) M.S Oghorada, words wouldn't be enough to appreciate all the sacrifices you made. To my sister, Mrs. Uruemu and her husband Mr. Samuel Edheki, who guided and supported me both academically and in everything. My brother Mr. Emmanuel and his wife Blessing Komoda who provided me motivation. Special thanks to my nephew Tega, nieces Iruo, Oreva, Maro and Ufuoma for their love. Also, to my spiritual parents Evang. & Mrs. F.K.A Usenu for their spiritual guidance over this research work.

Most importantly to Him Who, by (in consequence of) the [action of His] power that is at work within me, is able to [carry out His purpose and] do superabundantly, far over and above all that I [dare] ask or think [infinitely beyond my highest prayers, desires, thoughts, hopes, or dreams], To Him be glory in the church and in Christ Jesus throughout all generations forever and ever. Amen

## Abstract

Voltage and current unbalance are major problems in distribution networks, particularly with the integration of distributed generation systems. One way of mitigating these issues is by injecting negative sequence current into the distribution network using a Static Synchronous Compensator (STATCOM) which normally also regulates the voltage and power factor. The benefits of modularity and scalability offered by Modular Multilevel Cascaded Converters (MMCC) make them suitable for STATCOM application.

A number of different types of MMCC may be used, classified according to the sub-module circuit topology used. Their performance features and operational ranges for unbalanced load compensation are evaluated and quantified in this research.

This thesis investigates the use of both single star and single delta configured five-level Flying Capacitor (FC) converter MMCC based STATCOMs for unbalanced load compensation. A detailed study is carried out to compare this type of sub-module with several other types namely: half bridge, 3-L H-bridge and 3-L FC half bridge, and reveals the one best suited to STATCOM operation. With the choice of 5-L FC H-bridge as the sub-module for STATCOM operation, a detailed investigation is also performed to decide which pulse width modulation technique is the best. This was based on the assessment of total harmonic distortion, power loss, sub-module switch utilization and natural balancing of inner flying capacitors. Two new modulation techniques of swapped-carrier PWM (SC-PWM) along with phase disposed and phase shifted PWM (PS-PWM) are analyzed under these four performance metrics.

A novel contribution of this research is the development of a new space vector modulation technique using an overlapping hexagon technique. This space vector strategy offers benefits of eliminating control complexity and improving waveform quality, unlike the case of multilevel space vector technique. The simulation and experimental results show that this method provides superior performance and is applicable for other MMCC sub-modules.

Another contribution is the analysis and quantification of operating ranges of both single star and delta MMCCs in rating the cluster dc-link voltage (star) and current (delta) for unbalanced load compensation. A novel method of extending the operating capabilities of both configurations uses a third harmonic injection method. An experimental investigation validates the operating range extension compared to the pure sinusoidal zero sequence voltage and current injection. Also, the superiority of the single delta configured MMCC for unbalanced loading compensation is validated.

## **Table of Contents**

| Acknowledgementsv                                                                      |

|----------------------------------------------------------------------------------------|

| Abstractvi                                                                             |

| Table of Contentsviii                                                                  |

| List of Tablesxv                                                                       |

| List of Figuresxvii                                                                    |

| List of Abbreviationsxxvi                                                              |

| Symbolsxxvii                                                                           |

| Chapter 1 Introduction1                                                                |

| 1.1 Background Literature1                                                             |

| 1.2 Flexible AC Transmission Systems2                                                  |

| 1.2.1 Thyristor Controlled Series Capacitor (TCSC)2                                    |

| 1.2.2 Static VAR Compensator (SVC)                                                     |

| 1.2.3 Static Synchronous Series Compensator (SSSC)4                                    |

| 1.2.4 Static Synchronous Compensator (STATCOM)4                                        |

| 1.2.5 Unified Power Flow Controller (UPFC)5                                            |

| 1.3 Multilevel Converters5                                                             |

| 1.3.1 Neutral Point Converter (NPC)6                                                   |

| 1.3.2 Flying Capacitor Converter7                                                      |

| 1.3.3 Modular Multilevel Cascaded Converters7                                          |

| 1.4 MMCC-Based Static Synchronous Compensator<br>(STATCOM)8                            |

| 1.4.1 Principles of Voltage and Power Factor Control by<br>STATCOM9                    |

| 1.4.1.1 Voltage Regulation10                                                           |

| 1.4.1.2 Power Factor Correction11                                                      |

| 1.4.2 Grid Voltage Synchronization Techniques12                                        |

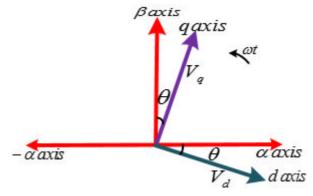

| 1.4.2.1 Synchronous Reference Frame- Phase Lock<br>Loop (SRF-PLL)13                    |

| 1.4.2.2 Decoupled Double Synchronous Reference<br>Frame- Phase Lock Loop (DDSRF-PLL)15 |

| 1.4.3 STATCOM Current Control Method16                                                 |

| 1.4.3.1 Synchronous Reference Frame Current<br>Controller16                            |

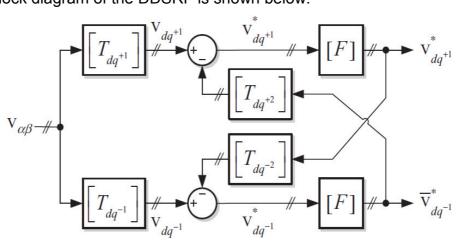

| 1.4.3.2 Decoupled Double Synchronous Reference<br>Frame Current Controller17           |

| 1.4.4 MMCC STATCOM Applications and Challenges18                                       |

| 1.5 Aims, Objectives and Thesis Structure                                                                        | 19       |

|------------------------------------------------------------------------------------------------------------------|----------|

| Chapter 2 ASSESSMENT of MODULAR MULTI-LEVEL CASCAD<br>CONVERTERS IN STATCOM APPLICATIONS                         | ED<br>21 |

| 2.1 Sub-module Circuits of Modular Multilevel Cascaded                                                           |          |

| Converters                                                                                                       |          |

| 2.1.1 Half-bridge cells                                                                                          |          |

| 2.1.1.1 Two-level Half bridge cell                                                                               |          |

| 2.1.1.2 Flying Capacitor half-bridge cell                                                                        |          |

| 2.1.2 H-bridge cells                                                                                             |          |

| 2.1.2.1 Three-level H-bridge cell                                                                                |          |

| 2.1.2.2 Five-level Flying Capacitor bridge cell                                                                  |          |

| 2.2 Classification of Modular Multilevel Converters                                                              |          |

| 2.2.1 Single Cell types                                                                                          | 29       |

| 2.2.1.1 Single Star Bridge Cells (MMCC-SSBC)                                                                     | 29       |

| 2.2.1.2 Single Delta Bridge Cells                                                                                | 32       |

| 2.2.2 Double Cell types                                                                                          | 33       |

| 2.2.2.1 Double Star Cells                                                                                        | 34       |

| 2.2.3 Emerging MMCC Topologies                                                                                   | 37       |

| 2.3 Analysis of MMCC Configurations for STATCOM                                                                  | 37       |

| 2.3.1 Sub-module Components                                                                                      | 37       |

| 2.3.2 Sub-module Number Requirement Based on MMCC<br>Configuration                                               |          |

| 2.3.3 Metrics Analysis                                                                                           | 38       |

| 2.3.3.1 Footprint                                                                                                | 38       |

| 2.3.3.2 Cost                                                                                                     | 42       |

| 2.3.3.3 Redundancy                                                                                               | 44       |

| 2.3.3.4 Control complexity                                                                                       | 46       |

| 2.3.4 Comparison of Sub-module Concepts for an 11kV<br>MMCC-STATCOM                                              | 47       |

| 2.4 Summary                                                                                                      |          |

| Chapter 3 Carrier-Based Sinusoidal PWM Techniques for Flying<br>Capacitor Modular Multi-level Cascaded Converter | )        |

| 3.1 Performance Metrics for FC-MMCC Modulation Techniques                                                        |          |

| 3.1.1 Natural Voltage Self-Balancing Ability                                                                     |          |

| 3.1.2 Power Loss                                                                                                 |          |

| 3.1.2.1 Conduction loss                                                                                          |          |

| 3.1.2.2 Switching loss                                                                                           |          |

| -                                                                                                                |          |

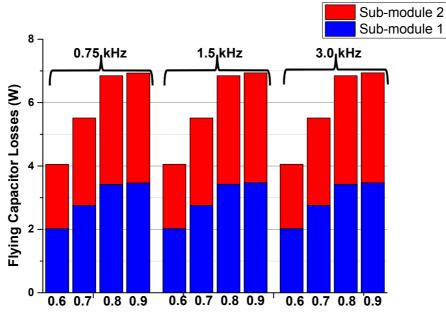

|     |        | 3.1.2.3 Flying capacitor loss                                    | 55  |

|-----|--------|------------------------------------------------------------------|-----|

|     |        | 3.1.2.4 A Power Loss Estimation Algorithm                        | 56  |

|     |        | 3.1.3 Total Harmonic Distortion (THD)                            | 58  |

|     |        | 3.1.4 Sub-module Switch Utilization                              | 58  |

|     | 3.2 (  | Carrier Placement PWM Techniques                                 | 59  |

|     |        | 3.2.1 Phase Disposed PWM (PD-PWM)                                | 59  |

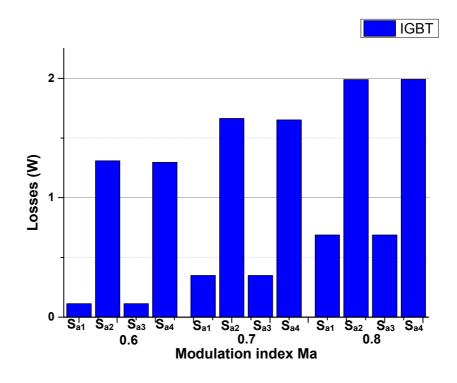

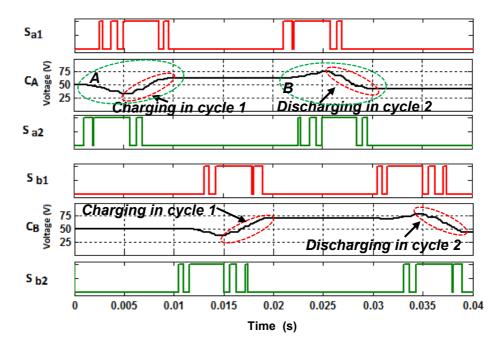

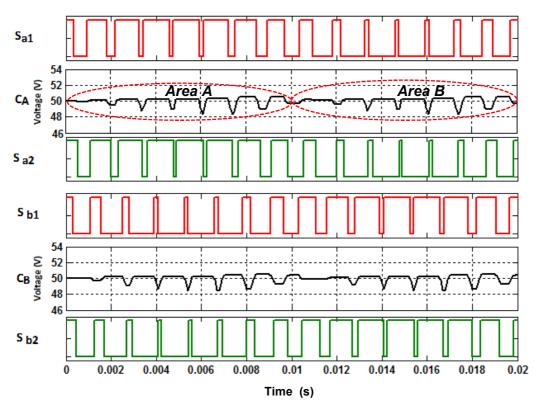

|     |        | 3.2.1.1 Natural Voltage balancing ability                        | 60  |

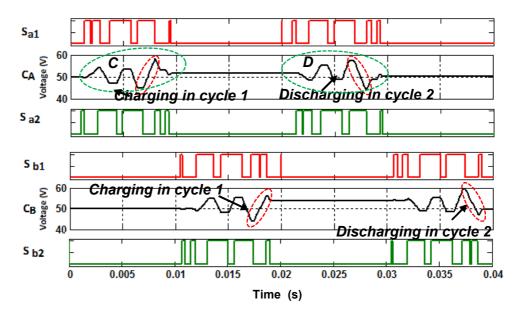

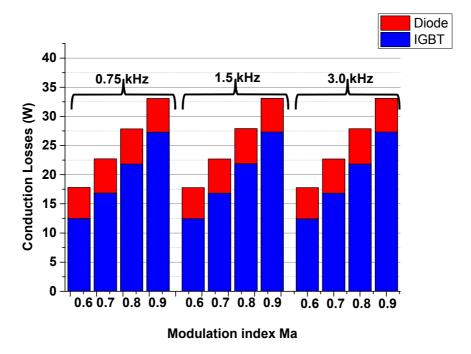

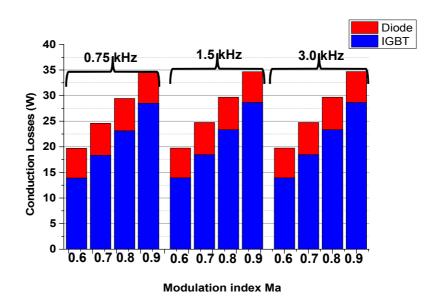

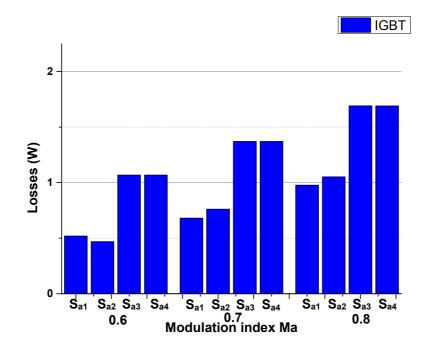

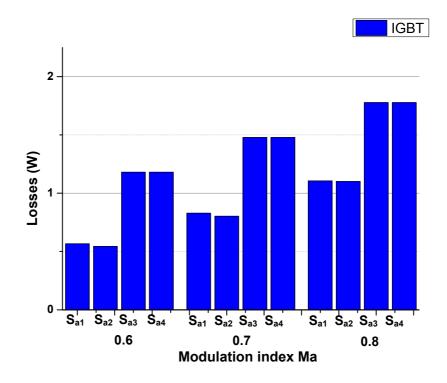

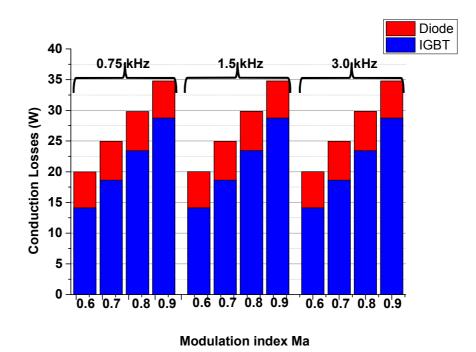

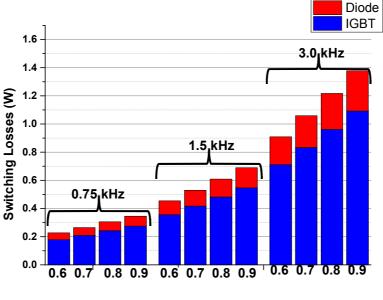

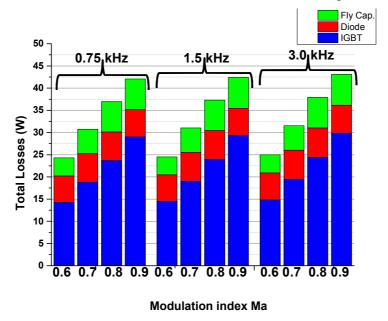

|     |        | 3.2.1.2 Power losses                                             | 62  |

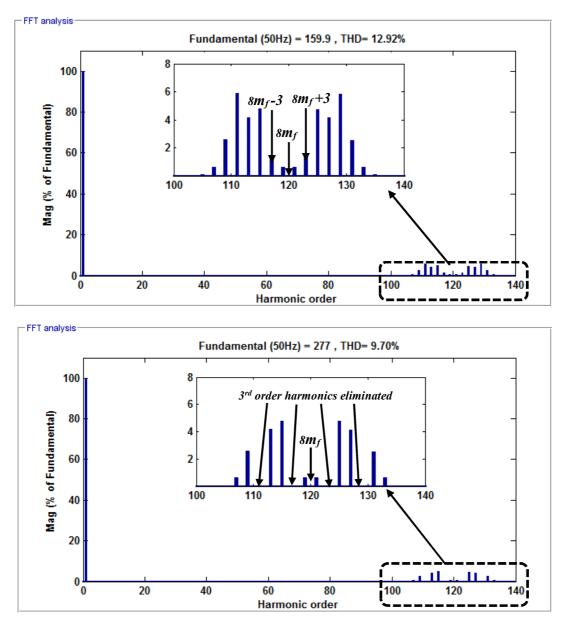

|     |        | 3.2.1.3 Total harmonic distortion (THD) analysis                 | 65  |

|     |        | 3.2.1.4 Sub-module switch utilization                            | 69  |

|     |        | 3.2.2 Swapped Carrier PWM (SC-PWM)                               | 71  |

|     |        | 3.2.2.1 Method 1 - Quarter fundamental cycle rotation            | 71  |

|     |        | 3.2.2.2 Method 2- Carrier cycle rotation method                  | 72  |

|     |        | 3.2.2.3 Natural balancing ability                                | 74  |

|     |        | 3.2.2.4 Power loss                                               | 76  |

|     |        | 3.2.2.5 Total harmonic distortion (THD) analysis                 | 80  |

|     |        | 3.2.2.6 Sub-module switch utilization                            | 82  |

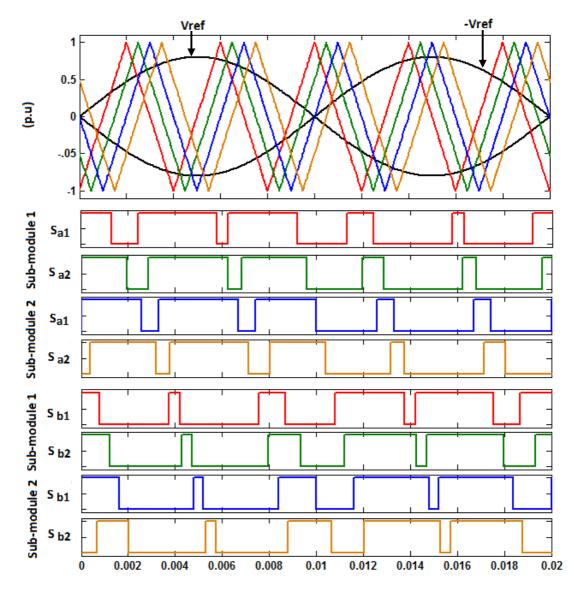

|     |        | 3.2.3 Phase Shifted PWM (PS-PWM)                                 | 85  |

|     |        | 3.2.3.1 Natural balancing ability                                | 87  |

|     |        | 3.2.3.2 Power loss                                               | 88  |

|     |        | 3.2.3.3 Total harmonic distortion (THD) analysis                 | 91  |

|     |        | 3.2.3.4 Sub-module switch utilization                            | 93  |

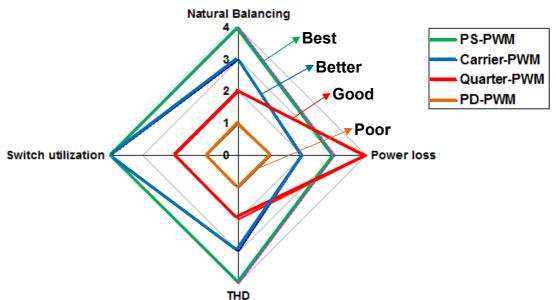

|     | 3.3 I  | Discussion and Comparison of different Carrier PWM<br>Techniques | 93  |

|     |        | 3.3.1Natural Balancing Ability                                   | 93  |

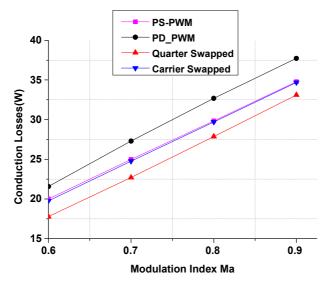

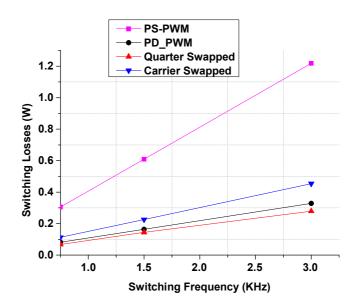

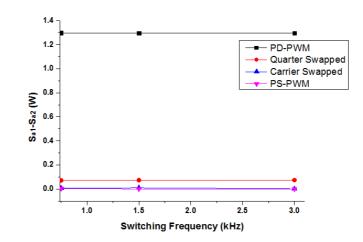

|     |        | 3.3.2 Power loss                                                 | 94  |

|     |        | 3.3.3 Total harmonic distortion                                  | 96  |

|     |        | 3.3.4 Sub-module switch utilization                              | 96  |

|     | 3.4 \$ | Summary                                                          | 97  |

| Cha | -      | 4 Overlapping Hexagon Space Vector Modulation<br>tegy            | 98  |

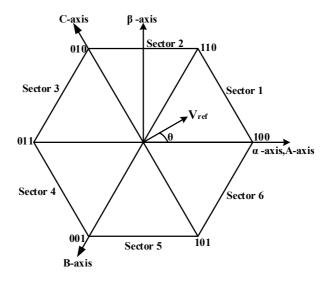

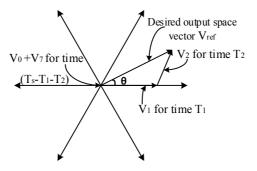

|     | 4.1    | Review of the Basic SVM Method                                   | 99  |

|     | 4.2    | Space Vector Modulation for Multilevel Converters                | 102 |

|     | 4.3    | Overlapping Hexagon Space Vector Modulation                      | 105 |

|     |        | 4.3.1 Using Two-level Hexagon                                    | 105 |

|     |     | 4.3.1.1 Sector identification                                                     | 106 |

|-----|-----|-----------------------------------------------------------------------------------|-----|

|     |     | 4.3.2Using Three-level Hexagons                                                   | 108 |

|     |     | 4.3.2.1 Sector identification                                                     | 109 |

|     |     | 4.3.2.2 Region selection                                                          | 110 |

|     |     | 4.3.2.3 Optimal switching state/voltage vector selection                          | 112 |

|     | 4.4 | Simulation Studies: Comparison of the Different Space                             |     |

|     | 4.5 | Experimental Validation of 2-level Overlapping Hexagon<br>Space Vector Modulation |     |

|     |     | 4.5.1 PWM Generation                                                              | 121 |

|     |     | 4.5.2 Experimental Results                                                        | 122 |

|     | 4.6 | Summary                                                                           | 123 |

| Cha |     | 5 FC-MMC Based STATCOM for Power Factor<br>rection                                | 124 |

|     | 5.1 | Converter Voltage and DC Capacitor Voltage<br>Requirements                        | 124 |

|     |     | 5.1.1 Variation of Converter Cell DC-bus voltage                                  | 128 |

|     | 5.2 | Determination of Sub-module capacitor voltage ripple of MMCC STATCOM              |     |

|     |     | 5.2.1 Variation of Sub-module capacitor voltage ripple.                           | 132 |

|     | 5.3 | FC-MMCC STATCOM Simulation Studies                                                | 134 |

|     |     | 5.3.1 Power System Configuration                                                  | 134 |

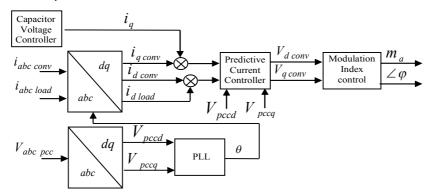

|     |     | 5.3.2FC-MMCC STATCOM Control Scheme                                               | 137 |

|     |     | 5.3.3Overall dc-bus voltage balancing control                                     | 138 |

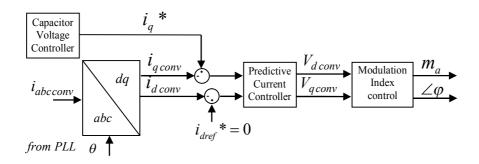

|     |     | 5.3.4Current Controller                                                           | 139 |

|     | 5.4 | Simulation Results and Discussions                                                | 140 |

|     |     | 5.4.1Unity Power Factor Correction                                                | 140 |

|     |     | 5.4.1.1 Active and Reactive Current Responses                                     | 140 |

|     |     | 5.4.1.2 Active and Reactive power                                                 | 141 |

|     |     | 5.4.1.3 PCC Voltage and current Responses                                         | 142 |

|     |     | 5.4.1.4 STATCOM Waveforms                                                         | 144 |

|     |     | 5.4.1.5 DC Converter Capacitor Voltage                                            | 146 |

|     | 5.5 | Experimental System and Validation                                                | 147 |

|     |     | 5.5.1Cell card power circuit                                                      | 150 |

|     |     | 5.5.2Data Acquisition Unit                                                        | 151 |

|     |     | 5.5.3Digital Control unit                                                         | 152 |

|   |       | 5.5.3.1 FPGA Cards152                                                                         |

|---|-------|-----------------------------------------------------------------------------------------------|

|   |       | 5.5.3.2 Digital Signal Processor                                                              |

|   |       | 5.5.4Program Overview                                                                         |

| ļ | 5.6   | Experimental Validation                                                                       |

| · | 0.0   | 5.6.1Control System Implementation                                                            |

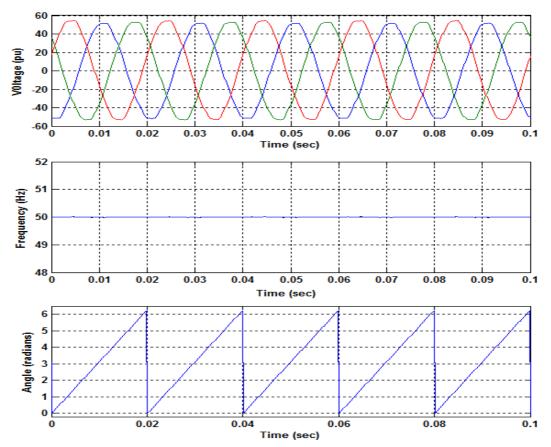

|   |       | 5.6.1.1 Grid Synchronization                                                                  |

|   |       | 5.6.1.2 Discrete time PI Controller for sub-module DC                                         |

|   |       | voltage158                                                                                    |

|   |       | 5.6.1.3 Capacitor Pre-charge Control159                                                       |

|   |       | 5.6.2Result and Discussion160                                                                 |

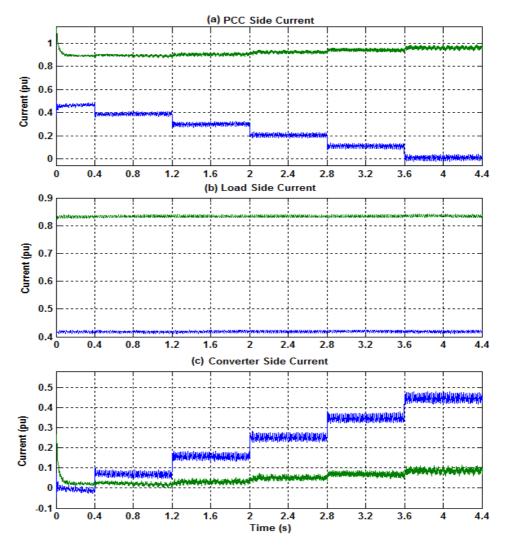

|   |       | 5.6.2.1 Active and Reactive Current responses160                                              |

|   |       | 5.6.2.2 Active and Reactive power162                                                          |

|   |       | 5.6.2.3 PCC Voltage and current Responses163                                                  |

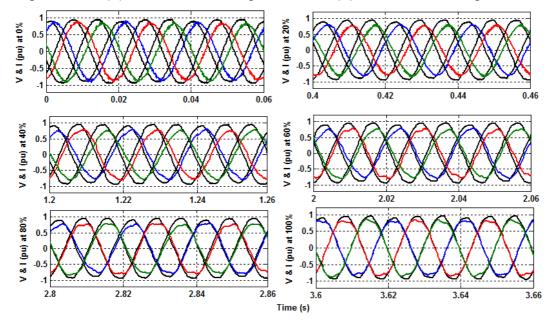

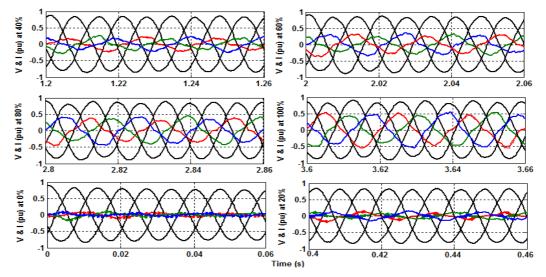

|   |       | 5.6.2.4 Converter side waveforms                                                              |

| į | 5.7   | Conclusion                                                                                    |

|   |       | FC-MMC Based STATCOM for Unbalanced Load                                                      |

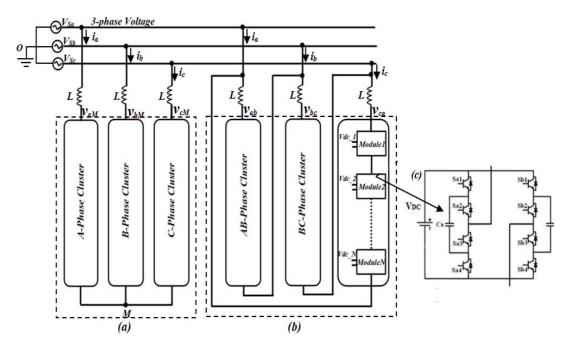

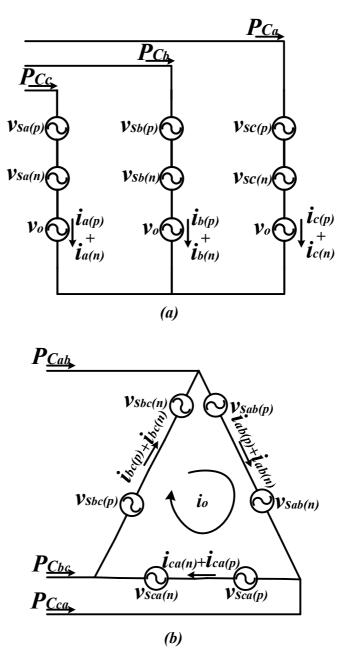

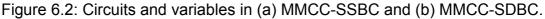

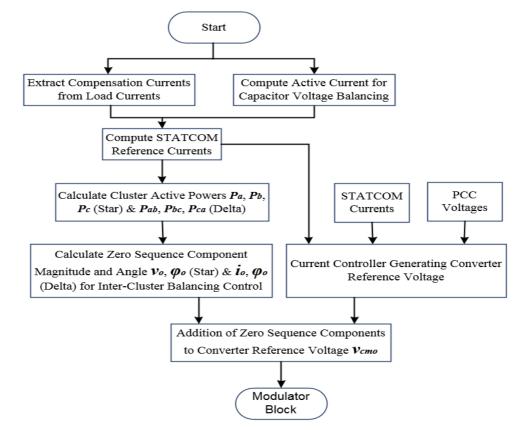

|   | 6.1   | pensation170<br>Circuit Configurations of an MMCC STATCOM170                                  |

|   | 6.2   |                                                                                               |

| , | 0.2   | Inter-Cluster DC Voltage Balancing Control Based on Zero<br>Sequence Components172            |

|   |       | 6.2.1 Current Re-balance Control and Problem Caused172                                        |

|   |       | 6.2.2Analysis of Unbalance Phase Power and Zero<br>Sequence Elements                          |

|   |       | 6.2.3Estimation of Zero Sequence Components177                                                |

| ( | 6.3   | Control of MMCC STATCOMs for Unbalance Load<br>Compensation                                   |

|   |       | 6.3.1DC-link voltage control179                                                               |

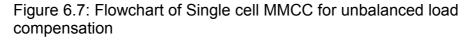

|   |       | 6.3.2Current Control using Dual vector predictive control.181                                 |

|   |       | 6.3.3 Evaluation of the zero sequence voltage and current to the degree of load unbalance     |

| ( | 6.4 C | Derivation of Required Third Harmonic Component                                               |

| ( | 6.5 ( | Operating Range Extensions and Ratings of MMCC under<br>Various Unbalanced Load conditions187 |

|   |       | 6.5.1 SSBC MMCC                                                                               |

|   |       | 6.5.2 SDBC MMCC                                                                               |

| ( | 6.6 5 | Simulation Results and Discussion191                                                          |

| ( | 6.7 E | Experimental Validations198                                                                   |

|   |       | 6.7.1 Experimental set-up198                                                                  |

| 6.7.2Results and Discussion                                                     | 200 |

|---------------------------------------------------------------------------------|-----|

| 6.8 Comparison between Simulation and Experimental<br>Results                   | 207 |

| 6.9 Summary                                                                     |     |

| Chapter 7 Conclusion and Recommendations for Future                             |     |

| Research                                                                        | 209 |

| 7.1 Conclusion                                                                  | 209 |

| 7.2 Future Recommendation                                                       | 211 |

| List of References                                                              | 213 |

| Appendix A                                                                      | 226 |

| Appendix B                                                                      | 228 |

| B.1: IGBT and diode thermal characteristics                                     | 228 |

| B.2: PD-PWM IGBT and diode Conduction loss                                      | 228 |

| B3: PD-PWM IGBT and diode switching loss                                        | 228 |

| B4: PD-PWM Inner flying capacitor power losses                                  |     |

| B5: PD-PWM Total Losses                                                         | 229 |

| B6: PD-PWM Sub-module Switch utilization                                        | 230 |

| B7: Quarter cycle rotation PWM IGBT and diode Conduction<br>loss                | 230 |

| B8: Carrier cycle rotation PWM Conduction loss                                  | 231 |

| B9: Quarter cycle rotation PWM Switching loss                                   | 231 |

| B10: Carrier cycle rotation PWM Switching loss                                  | 231 |

| B11: Quarter cycle rotation PWM Flying Capacitor losses                         | 232 |

| B12: Carrier cycle rotation PWM Flying Capacitor losses                         | 232 |

| B13: Quarter cycle rotation PWM Total loss                                      | 233 |

| B14: Carrier cycle rotation PWM Total loss                                      | 233 |

| B15: Quarter fundamental cycle rotation method Sub-module<br>Switch utilization |     |

| B16: Carrier cycle rotation method Sub-module Switch<br>utilization             | 234 |

| B17: Phase shifted PWM Conduction loss                                          | 234 |

| B18: Phase shifted PWM Switching loss                                           | 235 |

| B19: Phase shifted PWM Flying Capacitor losses                                  | 235 |

| B20: Phase shifted PWM Total loss                                               | 236 |

| B21: Phase shifted PWM Sub-module Switch utilization                            | 236 |

| B22: Comparison of PWM Schemes                                                  | 237 |

| Appendix C                                                                            | 238 |

|---------------------------------------------------------------------------------------|-----|

| C.1 Matlab Code for Case Study                                                        | 238 |

| C.2 Matlab Code for Case Study Capacitor Voltage Ripple                               | 238 |

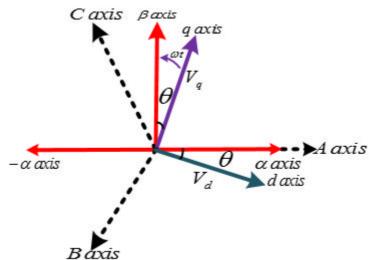

| C.3 Clarke's and Park's Transformation                                                | 240 |

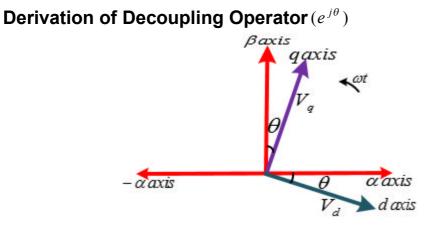

| Derivation of Decoupling Operator $(e^{j\theta})$                                     | 242 |

| C.4 Converter Voltage transformation from abc to d-q                                  | 243 |

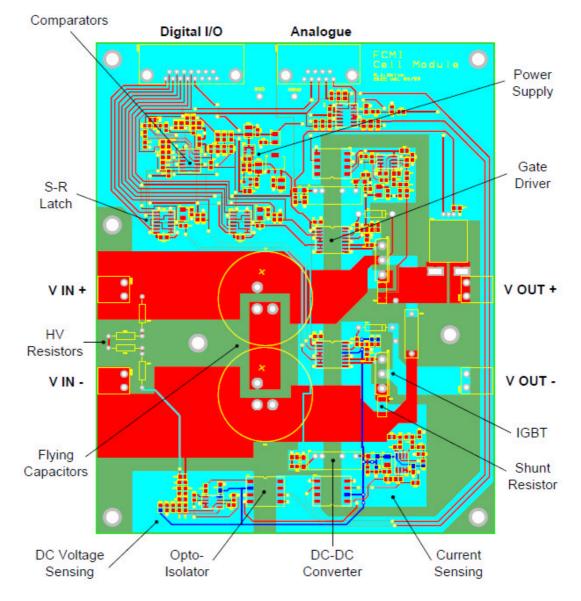

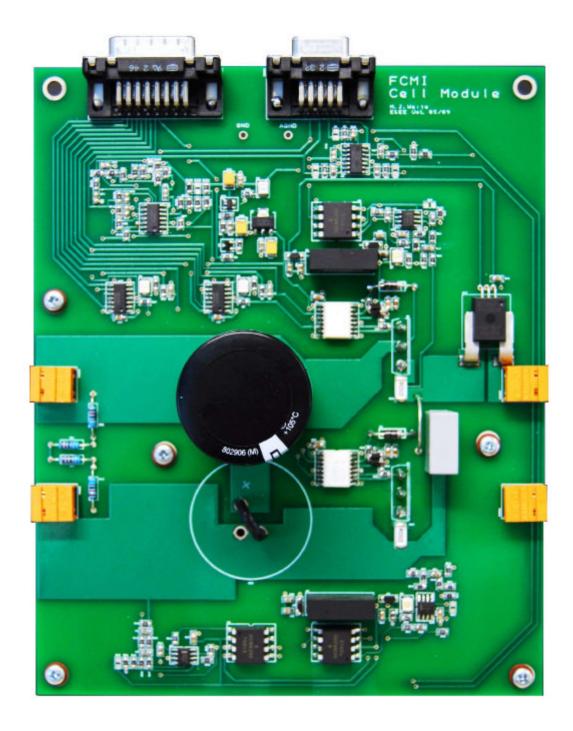

| C.5: Unit power cell card PCB design and Manufactured PCB [35]                        |     |

| C.6: IGBT characteristics and Capacitor characteristics                               | 246 |

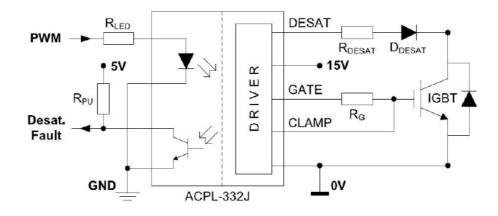

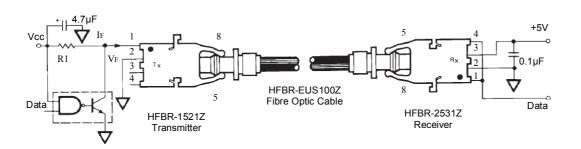

| C.7: Gate Drive Circuit and Fibre Optic Transmitter, Receiver<br>Circuit Diagram [35] | 247 |

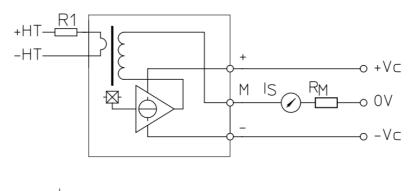

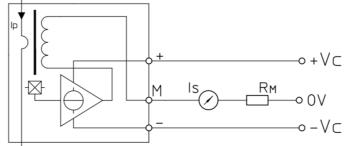

| C.8: Voltage and Current Transducer Circuit [35]                                      | 248 |

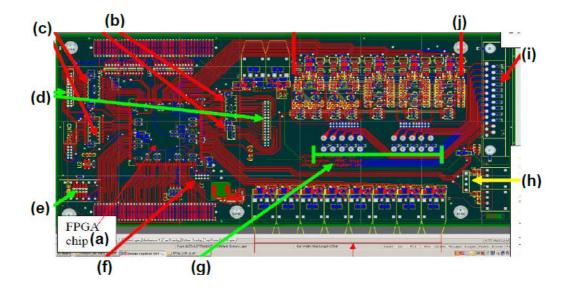

| C.9: Actel ProASIC FPGA board layout [35]                                             | 248 |

| Appendix D                                                                            | 250 |

| D1:Zero sequence Component derivation                                                 | 250 |

| D2: Positive and Negative Sequence Decoupling Operator<br>Derivation                  | 253 |

| D3: Converter Voltage transformation from abc to d-q                                  | 254 |

| D4:Zero sequence Component Simplification for Unbalanced<br>Load Analysis             | 256 |

## List of Tables

| Table 2.1: Two-level half bridge sub-module operating states23                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2: Three-level FC half bridge sub-module operating states                                                                                                                                       |

| Table 2.3: Three-level H-bridge sub-module operating states25                                                                                                                                           |

| Table 2.4: Five-level FC H-bridge sub-module operating states27                                                                                                                                         |

| Table 2.5: Top and bottom arm voltages of double star cells35                                                                                                                                           |

| Table 2.6: Components used for sub-module analysis                                                                                                                                                      |

| Table 2.7: Number of sub-modules required per phase limb38                                                                                                                                              |

| Table 2.8: Per-unitised sizes for sub-module width40                                                                                                                                                    |

| Table 2.9: $n_t$ and $n_{smt}$ for sub-module types based on differentMMCC configurations41                                                                                                             |

| Table 2.10: Sub-module per unit width and MMCC configurationFootprint calculation                                                                                                                       |

| Table 2.11: Prices of components for one sub-module unit43                                                                                                                                              |

| Table 2.12: sub-module and MMCC configuration cost         calculation                                                                                                                                  |

| Table 2.13: Possible charging and discharging sub-module andinner capacitor combinations for different sub-modules44                                                                                    |

| Table 2.14: Possible redundant combinations of sub-moduletypes across different MMCC configurations45                                                                                                   |

| Table 2.15: Control complexity assessment for each MMCC-<br>configuration       46                                                                                                                      |

| Table 2.16: Control complexity assessment for each sub-module type                                                                                                                                      |

| Table 2.17: Comparison of MMCC types based on 11kV         STATCOM      47                                                                                                                              |

| Table 2.18: Comparison of MMCC types based on 11kV         STATCOM                                                                                                                                      |

| Table 4.1: Region selection based on $m_a = V_{ref}/V_{dc}$                                                                                                                                             |

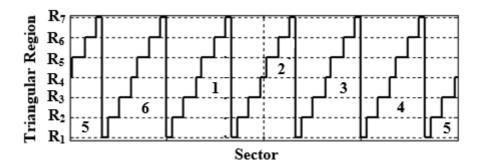

| Table 4.2: Selection criteria for regions $R_1 \rightarrow R_7$ 105                                                                                                                                     |

| Table 4.3: Region selection Criteria $(M_a = V_{ref} / V_{DC})$ 111                                                                                                                                     |

| Table 4.4: Duty Cycle calculation formulae112                                                                                                                                                           |

| Table 4.5: Vector combination chart showing optimized selection<br>of voltage vectors for region 1 sector 1 (U=Vref) and sector 4<br>(V=Vref') where Green=charging state and Red= discharging<br>state |

| Table 4.6: 5L-FC and 3L-HB MMCC parameters115                                                                                                                                                           |

| Table 4.7: Computational Comparison of SVM schemes                                                                                                                                                      |

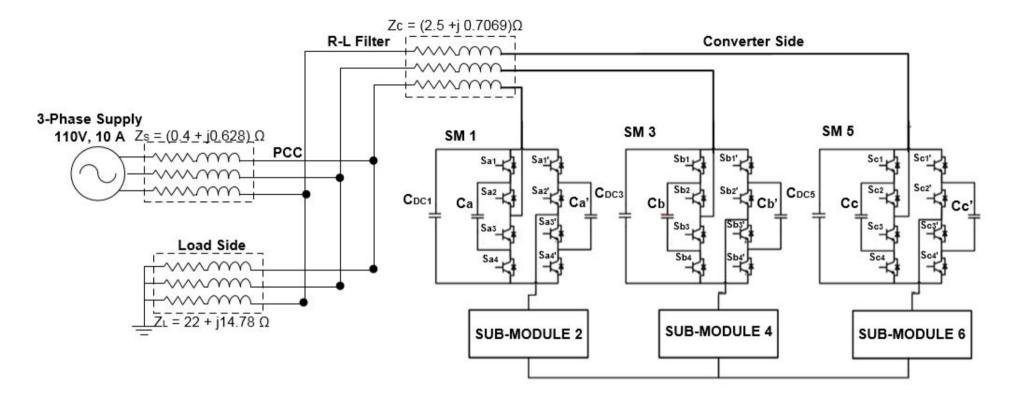

| Table 5.1: FC-MMCC power system parameters | 135 |

|--------------------------------------------|-----|

| Table 5.2: Power system Characteristics    | 154 |

| Table 6.1: MMCC power system parameters    | 192 |

| Table 6.2: Control gain parameters         | 192 |

| Table 6.3: Power system Characteristics    | 198 |

| Table 6.4: Control gain parameters         | 200 |

# List of Figures

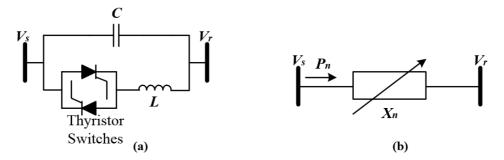

| Figure 1.1: Thyristor controlled series capacitor: (a) Thyristor<br>controlled reactor with fixed capacitors, (b) Variable<br>reactance representation                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

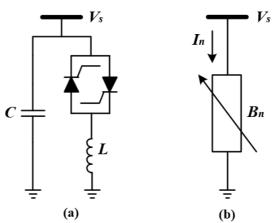

| Figure 1.2: Static VAR Compensator: (a) TCR with fixed capacitors, (b) Variable susceptance representation [35]3                                                                 |

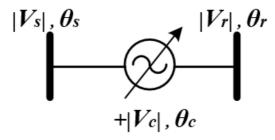

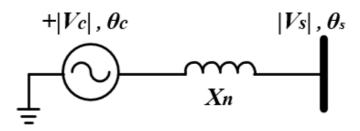

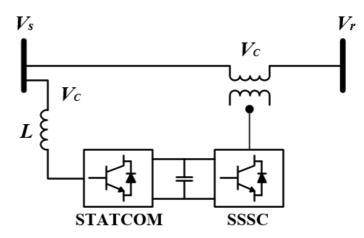

| Figure 1.3: Static Synchronous Series Compensator equivalent circuit model4                                                                                                      |

| Figure 1.4: STATCOM equivalent power circuit model5                                                                                                                              |

| Figure 1.5: Unified Power Flow Controller [35]5                                                                                                                                  |

| Figure 1.6: 5-level H-bridge Neutral Point Clamped Converter [35]6                                                                                                               |

| Figure 1.7: 5-level full bridge Flying Capacitor Converter[35]7                                                                                                                  |

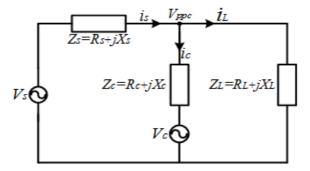

| Figure 1.8: Single phase circuit representation9                                                                                                                                 |

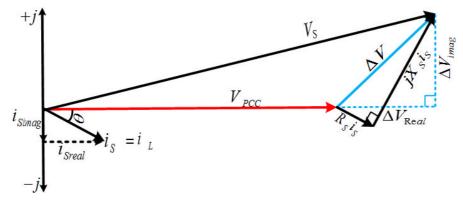

| Figure 1.9: Phasor diagram between supply and PCC voltages10                                                                                                                     |

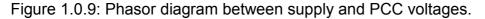

| Figure 1.10: Phasor diagram illustrating  V <sub>s</sub>  = V <sub>PCC</sub>  11                                                                                                 |

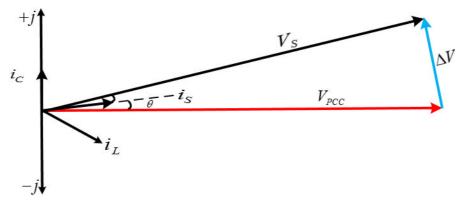

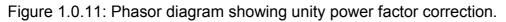

| Figure 1.11: Phasor diagram showing unity power factor correction12                                                                                                              |

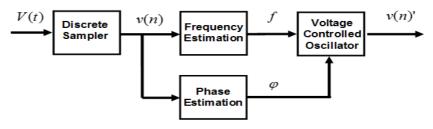

| Figure 1.12: Open loop synchronization technique block diagram [35]13                                                                                                            |

| Figure 1.13: Closed loop synchronization technique block diagram                                                                                                                 |

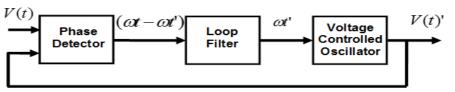

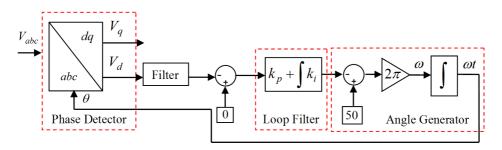

| Figure 1.14: Synchronous Reference Frame (SRF-PLL)14                                                                                                                             |

| Figure 1.15: SRF-PLL + Filter14                                                                                                                                                  |

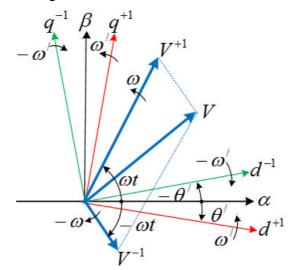

| Figure 1.16: Double Synchronous Reference Frame structure15                                                                                                                      |

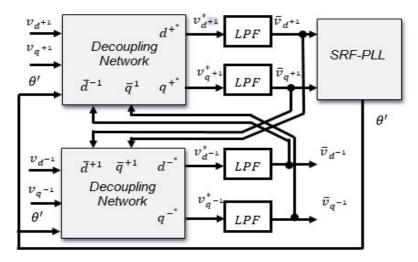

| Figure 1.18: Block diagram of the DDSRF-PLL16                                                                                                                                    |

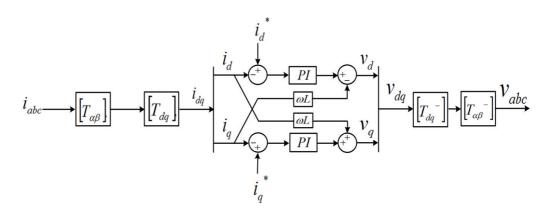

| Figure 1.19: Synchronous reference frame current controller17                                                                                                                    |

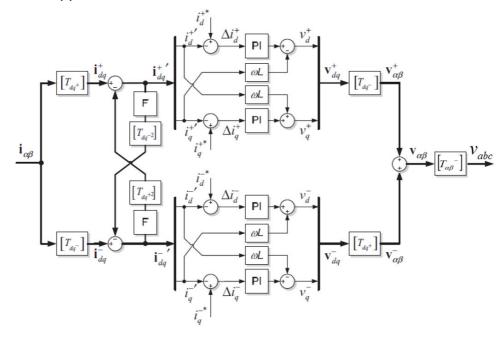

| Figure 1.20: Decouple double synchronous reference frame current controller [104]17                                                                                              |

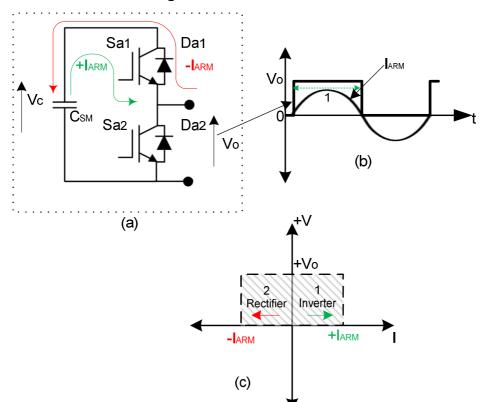

| Figure 2.1: Two-level half bridge sub-module: (a) Power Circuit;<br>(b) sub-module output voltage and current; (c) Two quadrant<br>operation modes current22                     |

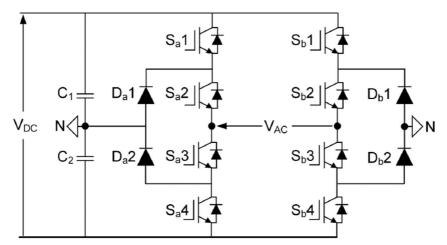

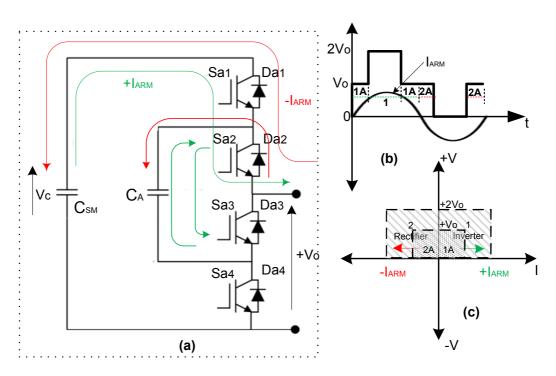

| Figure 2.2: Three-level FC half bridge sub-module: (a) Power<br>Circuit; (b) sub-module output voltage and current; (c) and <i>i-</i><br><i>v</i> two quadrant operation modes23 |

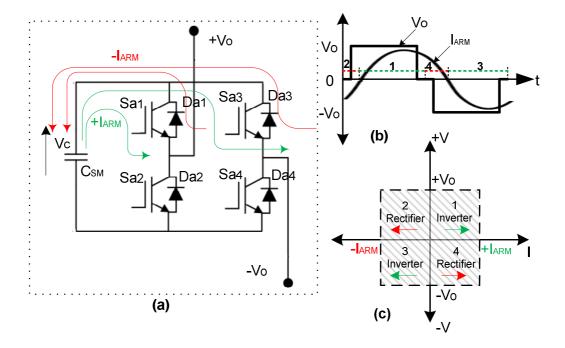

| Figure 2.3: Three-level H-bridge sub-module: (a) Power Circuit; (b) sub-module output voltage and current; (c) and <i>i-v</i> four quadrant operation modes                      |

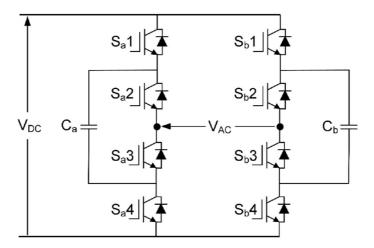

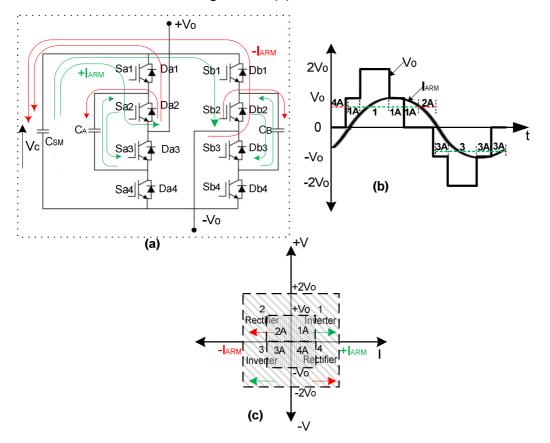

| Figure 2.4: Five-level FC H-bridge sub-module: (a) Power Circuit;<br>(b) sub-module output voltage and current; (c) and <i>i-v</i> four<br>quadrant operation modes              |

| Figure 2.5: MMCC single star structure                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.6: MMCC single star equivalent circuit                                                                                                                                                               |

| Figure 2.7: MMCC single delta structure32                                                                                                                                                                     |

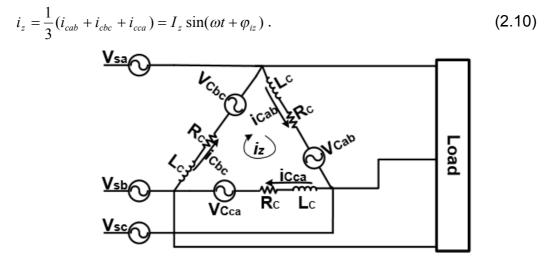

| Figure 2.8: Circulating Current flow in MMCC single delta structure                                                                                                                                           |

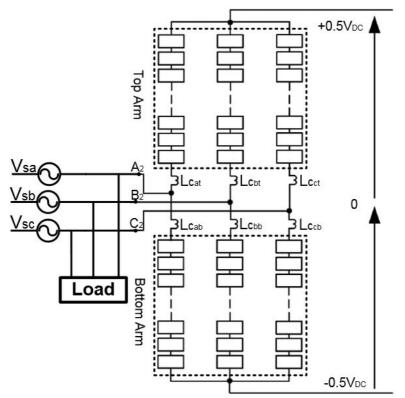

| Figure 2.9: MMCC double star cell structure                                                                                                                                                                   |

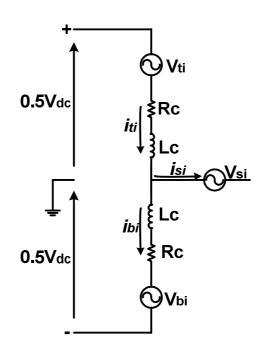

| Figure 2.10: double star MMCC single phase equivalent circuit36                                                                                                                                               |

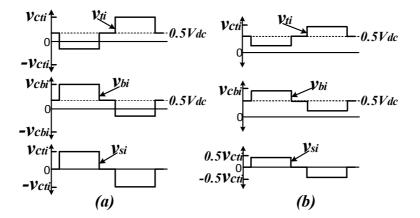

| Figure 2.11: Waveforms of top, bottom arms and phase voltage (a)<br>DSBC and (b) DSCC                                                                                                                         |

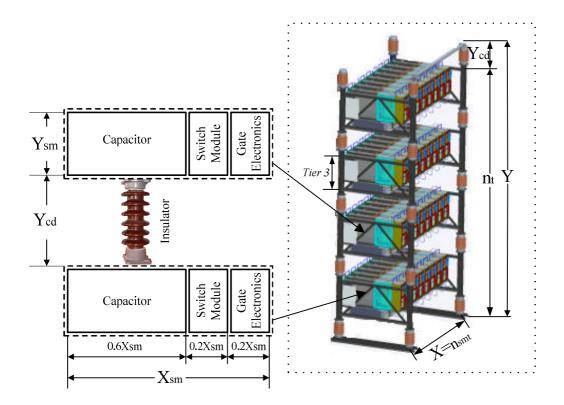

| Figure 2.12: Guideline for footprint assessment (a) sub-module<br>layout showing clearance distance (i.e. insulation between<br>two sub-modules); (b) single platform layout with sub-<br>modules [35, 147]40 |

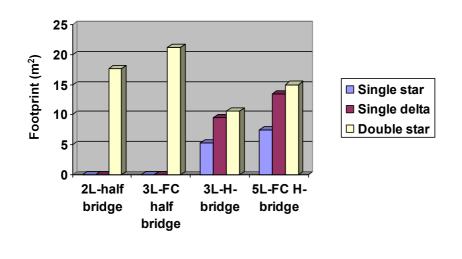

| Figure 2.13: MMCC-STATCOM footprint assessment42                                                                                                                                                              |

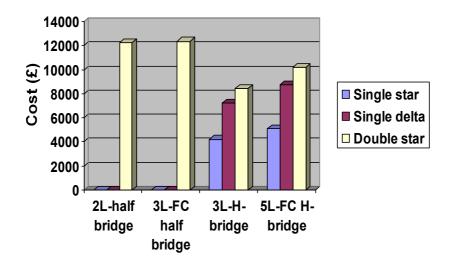

| Figure 2.14: MMCC-STATCOM cost assessment44                                                                                                                                                                   |

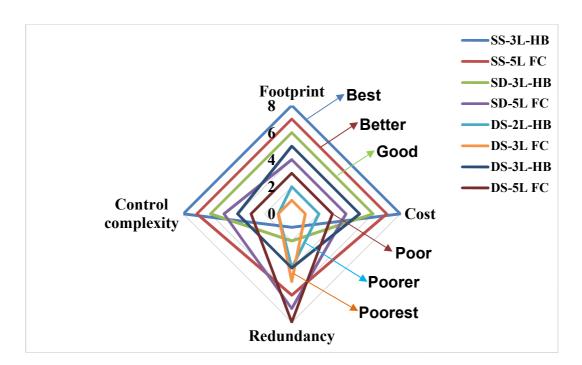

| Figure 2.15: MMCC configuration ranking50                                                                                                                                                                     |

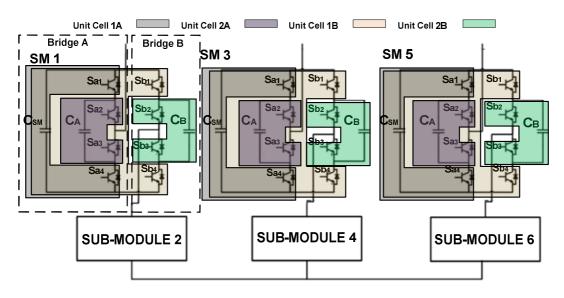

| Figure 3.1: FC-MMCC circuit structure [35]52                                                                                                                                                                  |

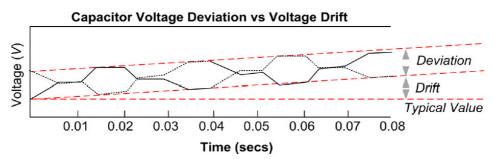

| Figure 3.2: Graphical illustration of capacitor voltage drift and variation [35]53                                                                                                                            |

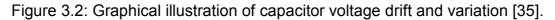

| Figure 3.3: Characteristic curves for (a) $i_c$ and $T_{j_T}$ vs $V_{CE}$ and (b) $i_c$ and $T_{j_T}$ vs $E_s$                                                                                                |

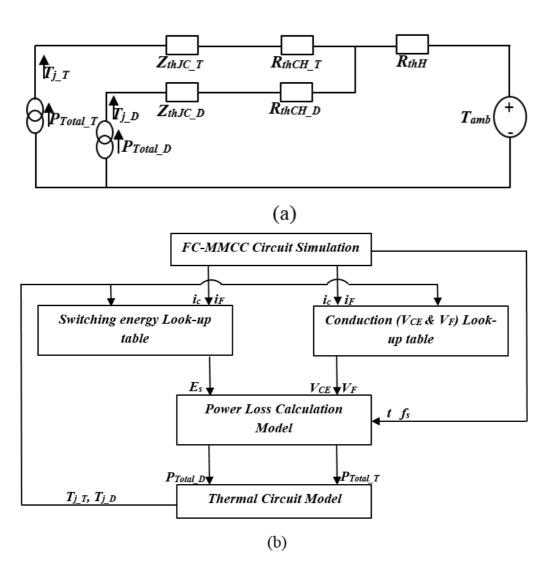

| Figure 3.4: (a) Thermal and (b) loss evaluation model for an FC-<br>MMCC                                                                                                                                      |

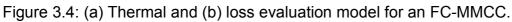

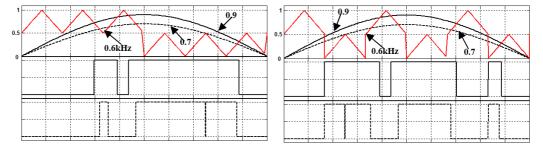

| Figure 3.5: Phase disposed PWM for FC-MMCC at <i>m</i> <sup>f</sup> =1560                                                                                                                                     |

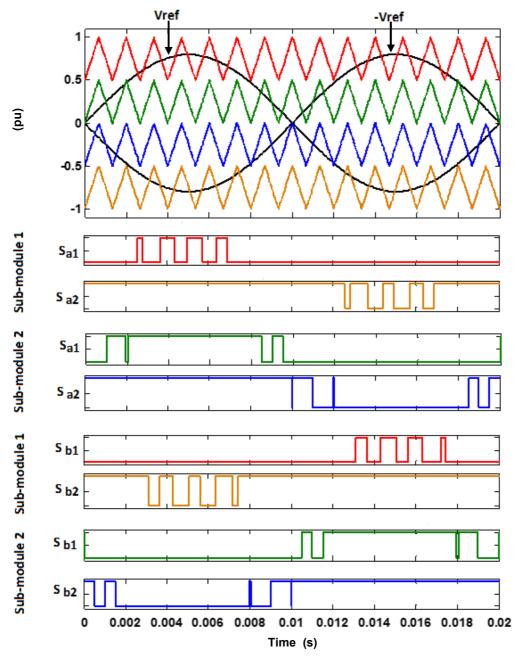

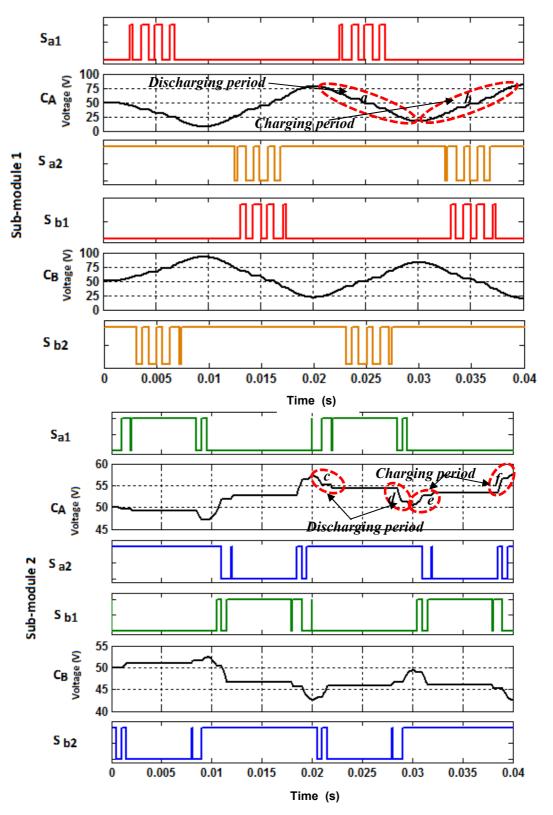

| Figure 3.6: PD-PWM switching actions for investigating sub-<br>module flying capacitor variation61                                                                                                            |

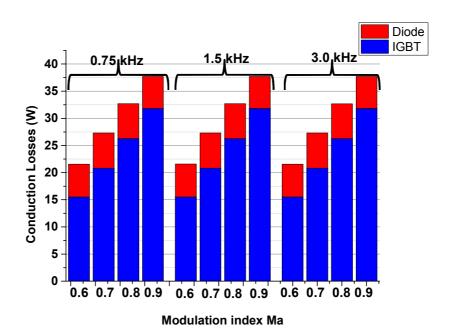

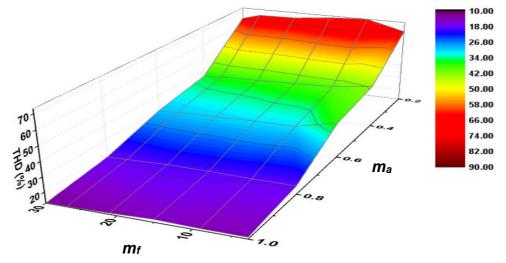

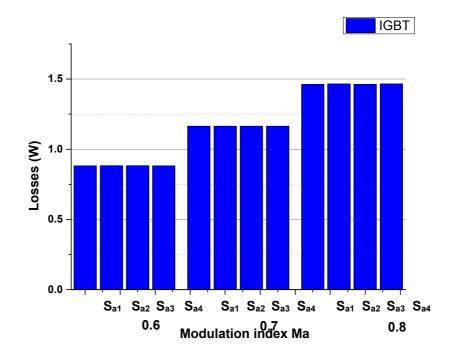

| Figure 3.7: IGBT and Diode conduction losses63                                                                                                                                                                |

| Figure 3.8: (a) variation in reference signal <i>m</i> <sub>a</sub> ; (b) variation in carrier signal frequency63                                                                                             |

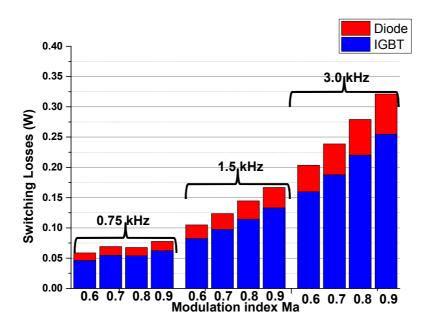

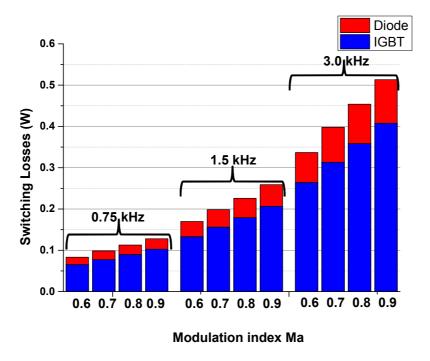

| Figure 3.9: IGBT and Diode switching loss64                                                                                                                                                                   |

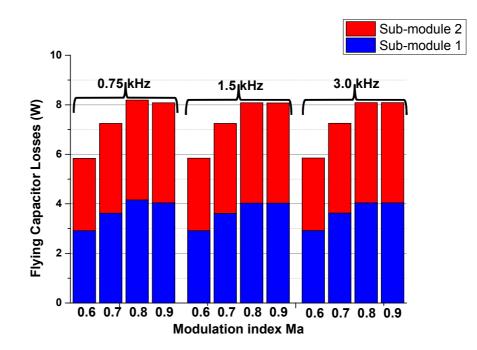

| Figure 3.10: Flying capacitor loss64                                                                                                                                                                          |

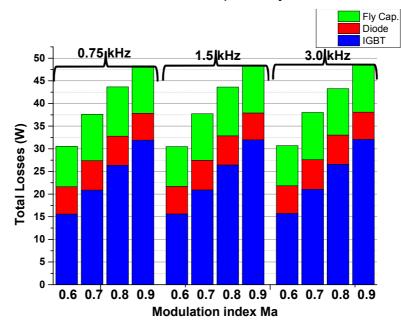

| Figure 3.11: Total Losses65                                                                                                                                                                                   |

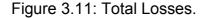

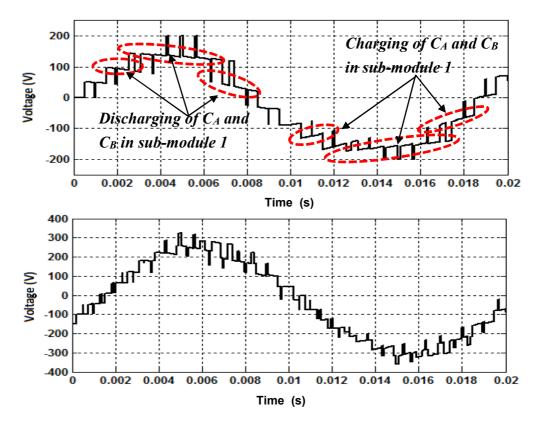

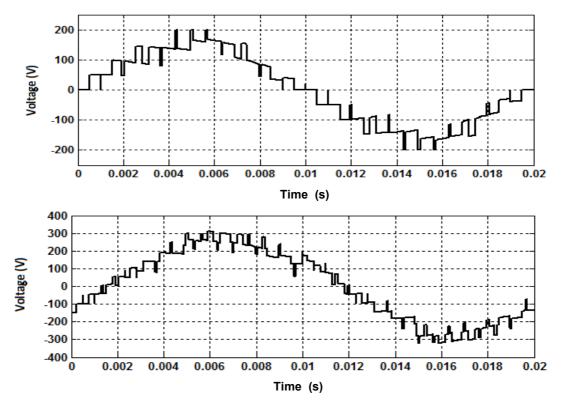

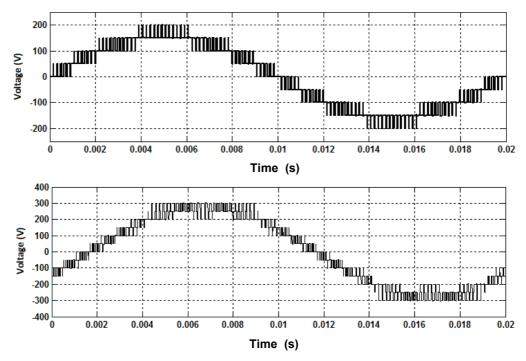

| Figure 3.12: (a) Phase voltage waveform, (b) Line-line voltage waveform67                                                                                                                                     |

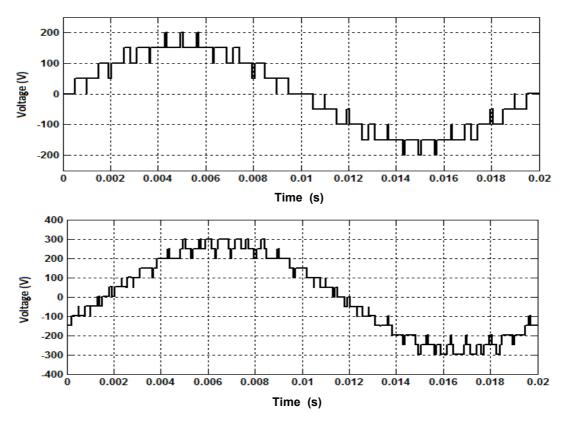

| Figure 3.13: (a)Phase voltage spectrum, (b) Line voltage spectrum68                                                                                                                                           |

| Figure 3.14: (a) Phase voltage of the FC-MMCC (highlighting the intermediate voltage levels that are contributing to the distortion of voltage waveform) and (b) Line voltage                                 |

| Figure 3.15: (a) Phase and (b) line voltage spectra70                                                                                                                                                         |

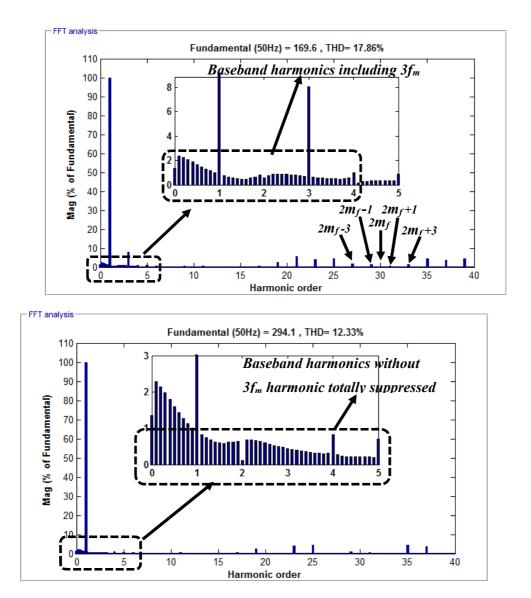

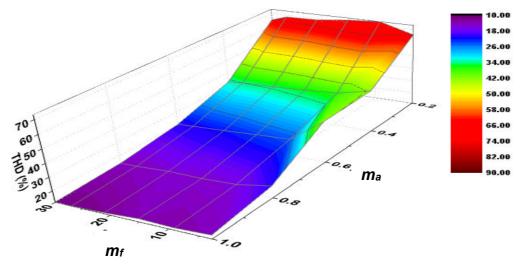

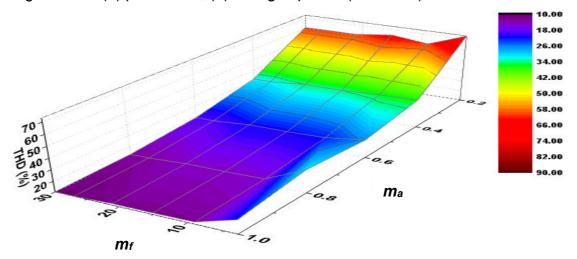

| Figure 3.16:3-D plot of Total harmonic distortion as a function of $m_a$ and $m_f$                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------|

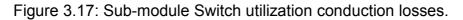

| Figure 3.17: Sub-module Switch utilization conduction losses71                                                                              |

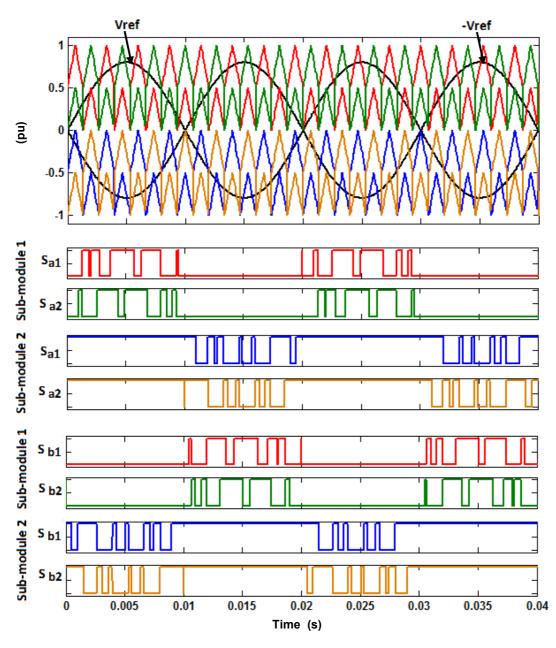

| Figure 3.18: Quarter fundamental cycle rotation method for FC-<br>MMCC73                                                                    |

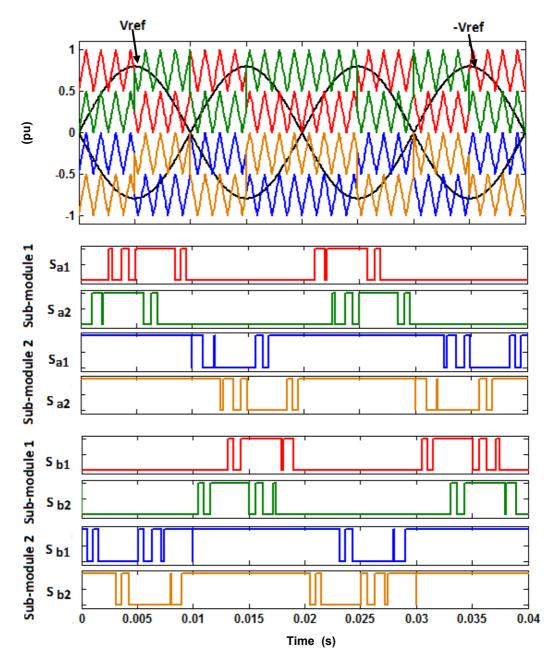

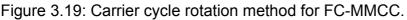

| Figure 3.19: Carrier cycle rotation method for FC-MMCC74                                                                                    |

| Figure 3.20: Quarter cycle rotation PWM switching actions for investigating sub-module flying capacitor variation75                         |

| Figure 3.21: Carrier cycle rotation PWM switching actions for investigating sub-module flying capacitor variation75                         |

| Figure 3.22: Quarter cycle rotation PWM IGBT and Diode conduction loss76                                                                    |

| Figure 3.23: Carrier cycle rotation PWM IGBT and Diode conduction loss77                                                                    |

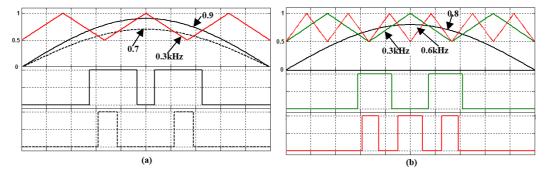

| Figure 3.24: Variation in reference signal <i>m</i> <sub>a</sub> (a) Quarter cycle rotation PWM; (b) Carrier cycle rotation PWM77           |

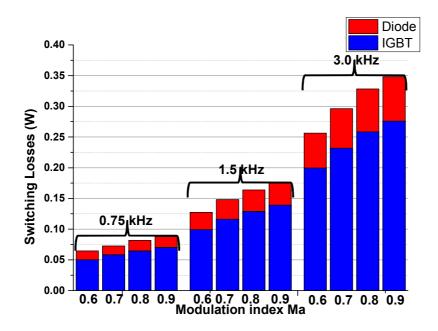

| Figure 3.25: Quarter cycle rotation PWM IGBT and Diode switching loss78                                                                     |

| Figure 3.26: Carrier cycle rotation PWM IGBT and Diode switching loss                                                                       |

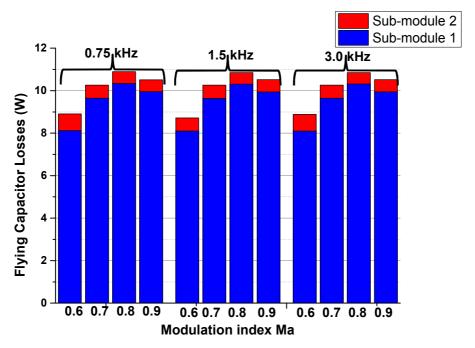

| Figure 3.27: Quarter cycle rotation PWM Flying capacitor loss79                                                                             |

| Figure 3.28: Carrier cycle rotation PWM Flying capacitor loss79                                                                             |

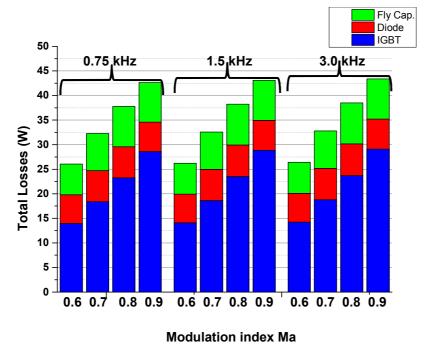

| Figure 3.29: Quarter cycle rotation PWM total loss80                                                                                        |

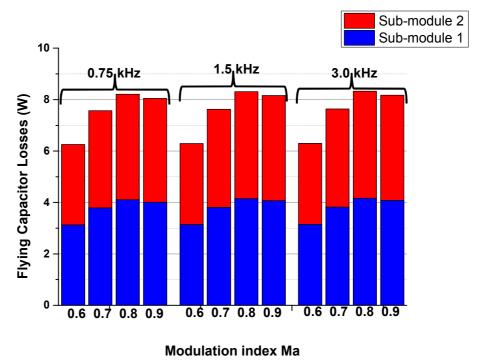

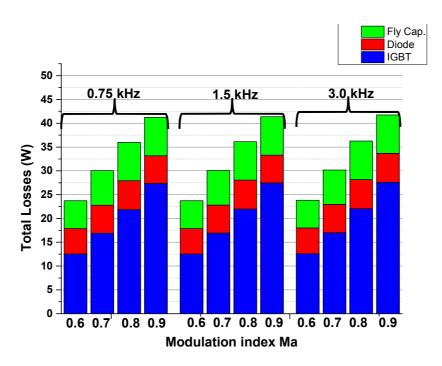

| Figure 3.30: Carrier cycle rotation PWM total loss80                                                                                        |

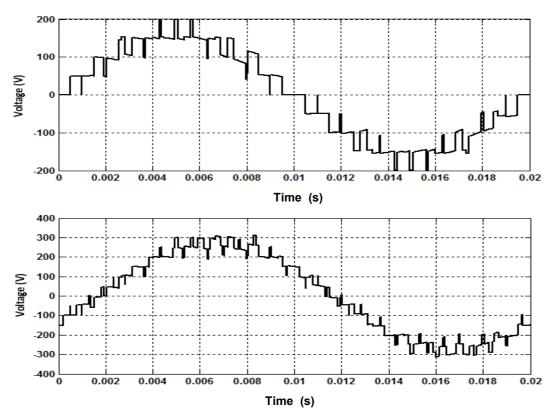

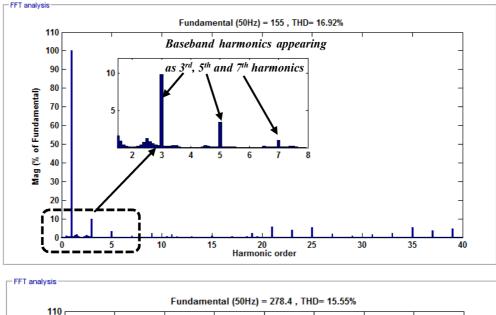

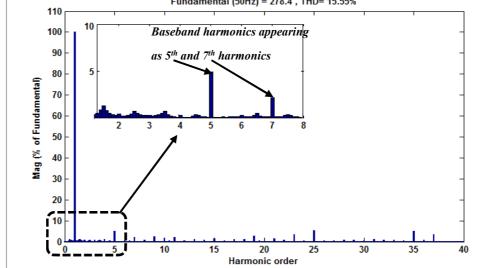

| Figure 3.31: Quarter cycle method (a) Phase, (b) line voltage waveforms81                                                                   |

| Figure 3.32: Carrier cycle method (a) Phase, (b) line voltage<br>waveforms82                                                                |

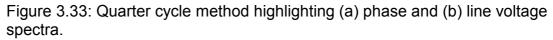

| Figure 3.33: Quarter cycle method highlighting (a) phase and (b) line voltage spectra83                                                     |

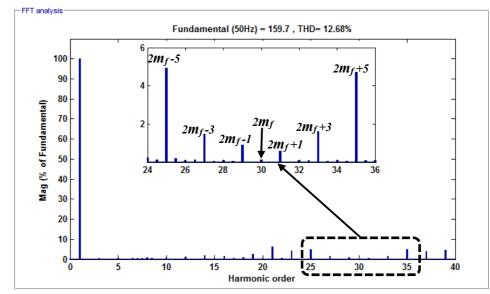

| Figure 3.34: Carrier cycle method highlighting (a) phase and (b) line voltage spectra                                                       |

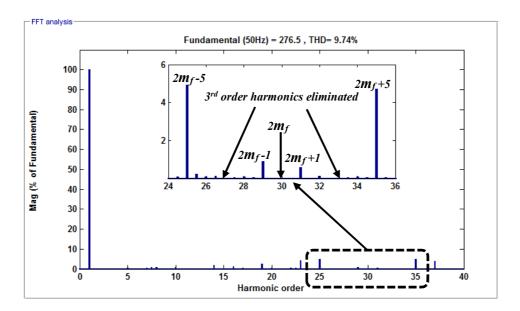

| Figure 3.35: Quarter cycle PWM 3-D plot of Total Harmonic Distortion as a function of $m_a$ and $m_f$                                       |

| Figure 3.36: Carrier cycle PWM 3-D plot of Total Harmonic<br>Distortion as a function of <i>m</i> <sub>a</sub> and <i>m</i> <sub>f</sub> 84 |

| Figure 3.37: Quarter cycle PWM sub-module switch utilization conduction losses85                                                            |

| Figure 3.38: Quarter cycle PWM sub-module switch utilization conduction losses85                                                            |

| Figure 3.39: Phase shifted PWM for FC-MMCC at m <sub>f</sub> =587                                                                           |

| Figure 3.40: Phase shifted PWM switching actions for investigating sub-module flying capacitor variation           |

|--------------------------------------------------------------------------------------------------------------------|

| Figure 3.41: IGBT and Diode conduction loss                                                                        |

| Figure 3.42: IGBT and Diode switching loss                                                                         |

| Figure 3.43: Flying capacitor loss90                                                                               |

| Figure 3.44: Total Losses90                                                                                        |

| Figure 3.45: (a) phase and (b) line voltage waveforms of the FC-<br>MMCC                                           |

| Figure 3.46: (a) phase and; (b) voltage spectra (PS-PWM)92                                                         |

| Figure 3.47: PS-PWM 3-D plot of Total harmonic distortion as a function of $m_a$ and $m_f$ 92                      |

| Figure 3.48: PS-PWM sub-module switch utilization conduction losses                                                |

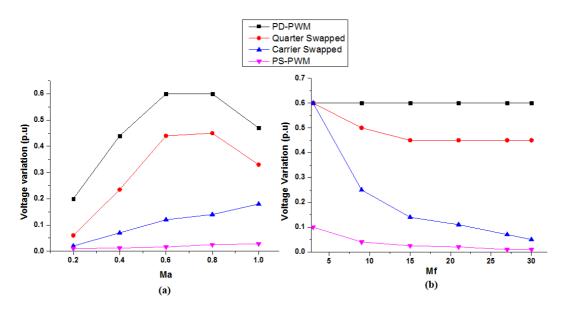

| Figure 3.49: Inner flying capacitor voltage with respect to (a)<br>modulation index and (b) modulation frequency94 |

| Figure 3.50: Power losses (a) conduction and (b) switching losses                                                  |

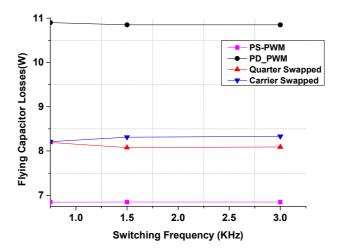

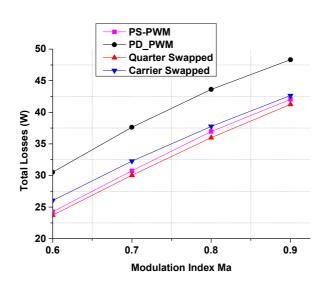

| Figure 3.51: Power losses (a) Flying capacitor and (b) total losses                                                |

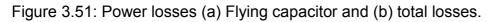

| Figure 3.52: Total harmonic distortion with respect to (a)<br>modulation index and (b) modulation frequency96      |

| Figure 3.53: Sub-module switch utilization97                                                                       |

| Figure 3.54: Carrier placement PWM ranking97                                                                       |

| Figure 4.1: Two-level SVM scheme showing voltage vectors101                                                        |

| Figure 4.2: Creation of the desired output space vector with<br>nearest three switching vectors101                 |

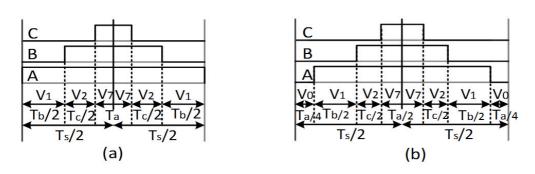

| Figure 4.3: Vector sequence for the (a) Two-phase and (b) symmetrical method in the first sextant102               |

| Figure 4.4: 5-level hexagon SVM implementation on two cascaded 5-Level FCC103                                      |

| Figure 4.5: Conventional Multilevel-SVM (a) Hexagon for a 5-level SVM and (b) Sector 1 of the 5-level hexagon104   |

| Figure 4.6: Sector identification for 5-level hexagon reference vectors104                                         |

| Figure 4.7: Region selection for <i>m</i> <sub>a</sub> >0.75105                                                    |

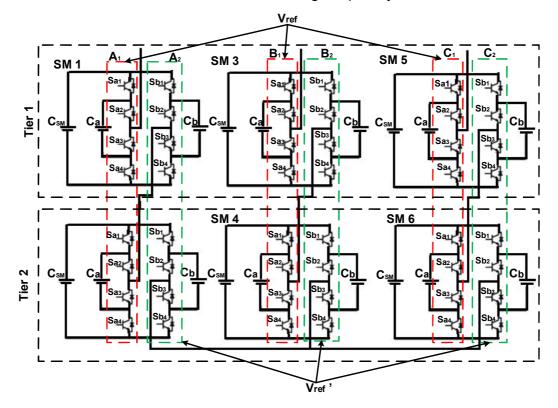

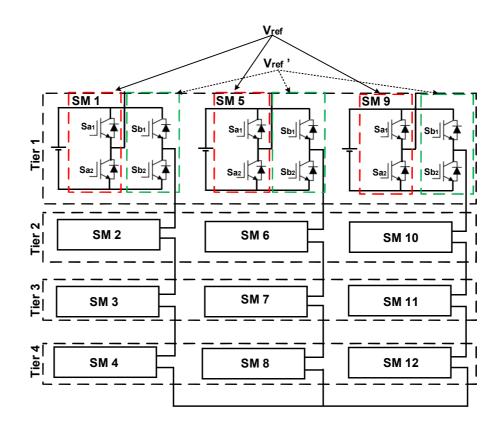

| Figure 4.8: Schematic diagram of a MMCC with four cascaded 3-L<br>H-bridges107                                     |

| Figure 4.9: Two-level hexagon for OH-SVM highlighting phase shift between each hexagons107                         |

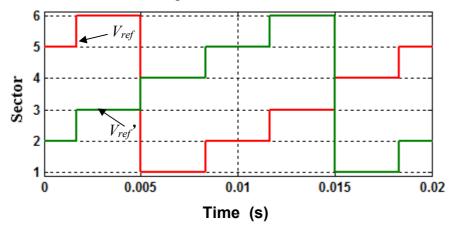

| Figure 4.10: Sector identification for 2-level hexagon reference vector                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

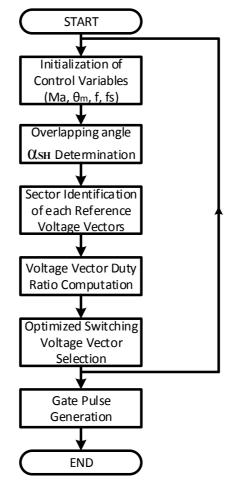

| Figure 4.11: Flowchart for 2-level hexagon implementation109                                                                                                                                        |

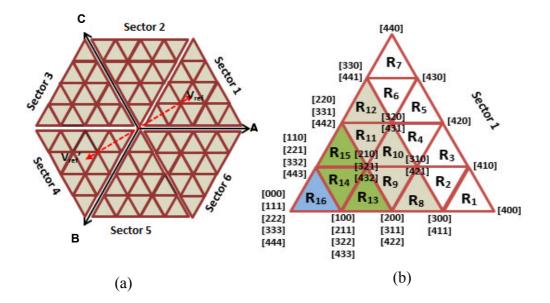

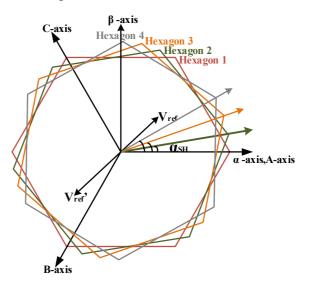

| Figure 4.12: 3-level hexagon for OH-SVM (a) all sectors and reference voltages (b) region detection in sector 1 (c) phase shift between two hexagons110                                             |

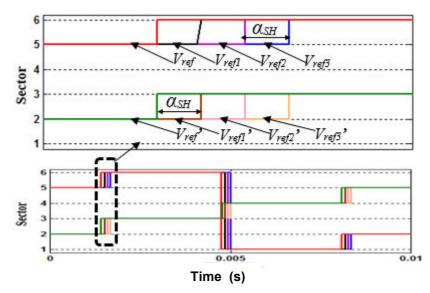

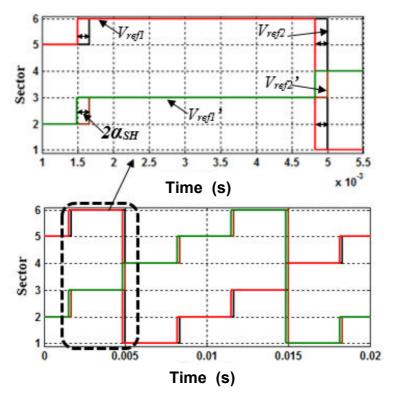

| Figure 4.13: Sector identification of reference voltage vectors in a 3-level hexagon                                                                                                                |

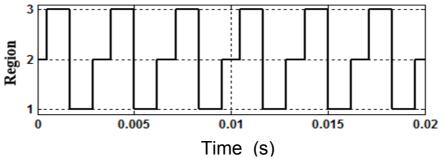

| Figure 4.14: Region selection for <i>m</i> <sub>a</sub> >0.5112                                                                                                                                     |

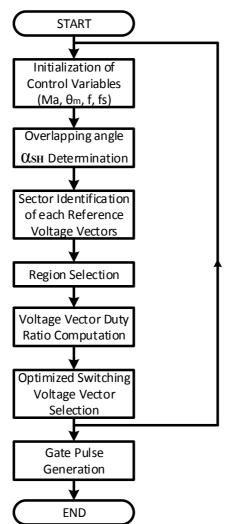

| Figure 4.15: Flowchart for 3-level hexagon implementation114                                                                                                                                        |

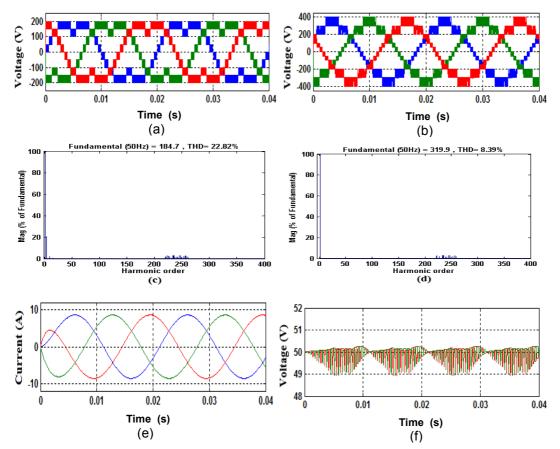

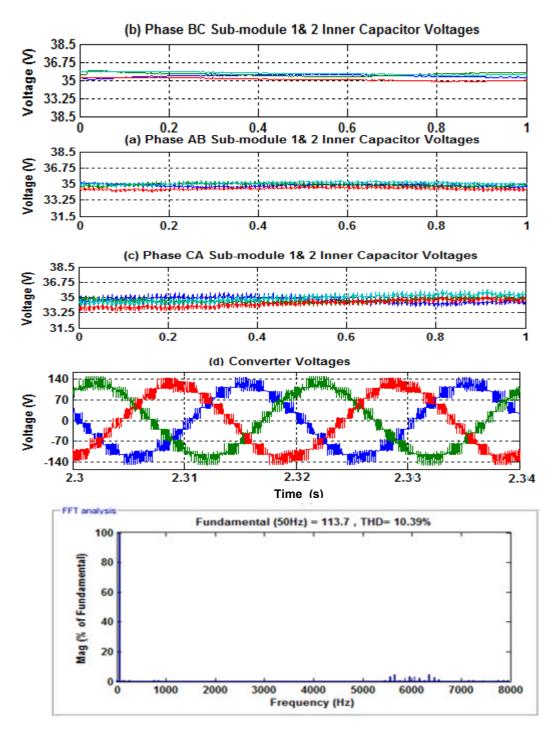

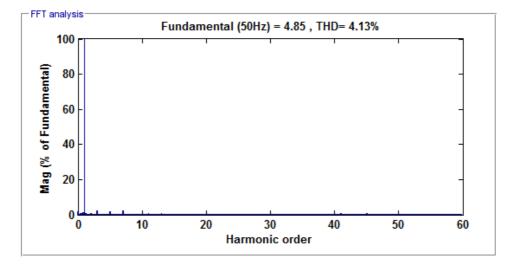

| Figure 4.16: 2-level OH-SVM for MMCC with 5L-FCC; (a) Phase<br>voltage, (b) Line voltage, (c) Phase voltage THD, (d) Line<br>voltage THD(e) Load current(f) Inner flying capacitor<br>voltage       |

| Figure 4.17: 3-level OH-SVM for MMCC with 5L-FCC; (a) Phase<br>voltage, (b) Line voltage, (c) Phase voltage THD, (d) Line<br>voltage THD (e) Load current (f) Inner flying capacitor<br>voltage     |

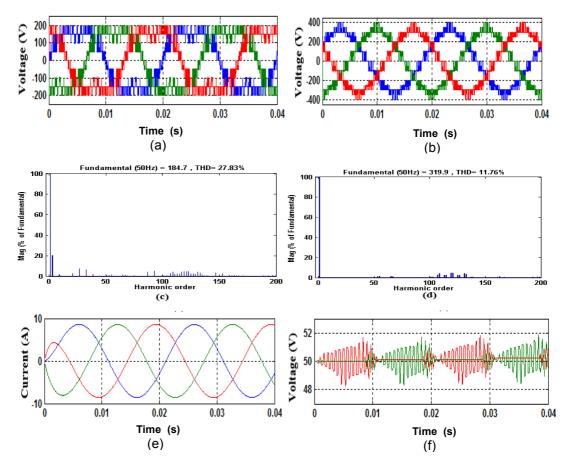

| Figure 4.18: 5-level OH-SVM for MMCC with 5L-FCC; (a) Phase<br>voltage, (b) Line voltage, (c) Phase voltage THD, (d) Line<br>voltage THD (e) Load current and (f) Inner flying capacitor<br>voltage |

| Figure 4.19: 2-level OH-SVM for MMCC with 3L-HB; (a) Phase<br>voltage, (b) Line voltage, (c) Phase voltage THD (d) Line<br>voltage THD and (e) current119                                           |

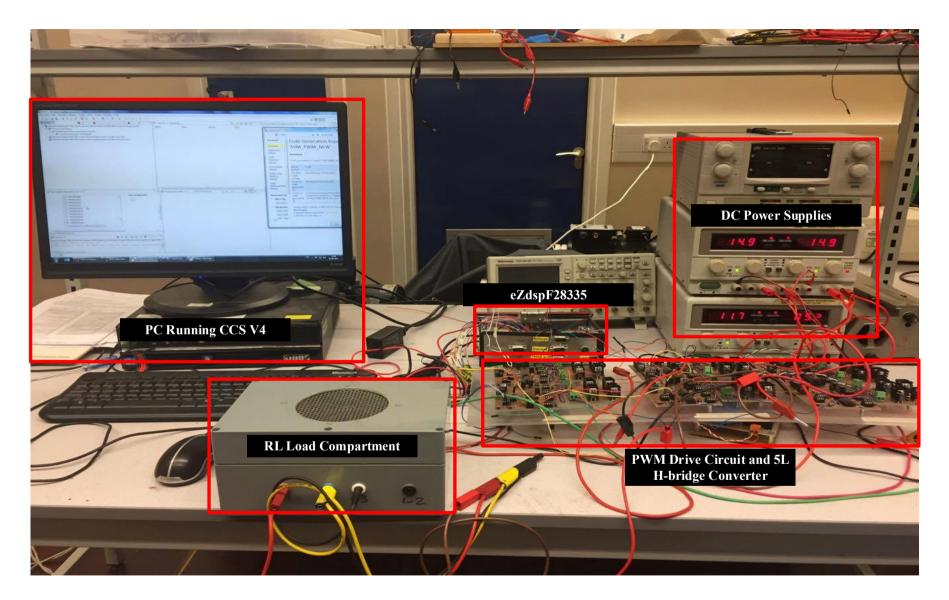

| Figure 4.20: MMCC experimental setup120                                                                                                                                                             |

| Figure 4.21: Spectrum Digital eZdspF28335 board [183]121                                                                                                                                            |

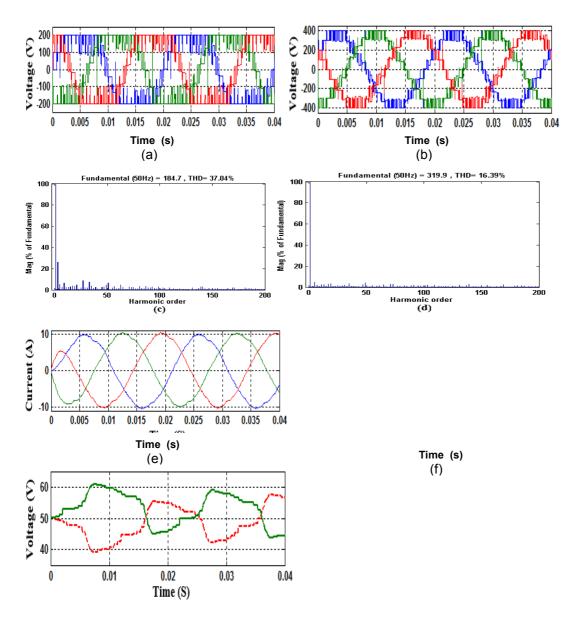

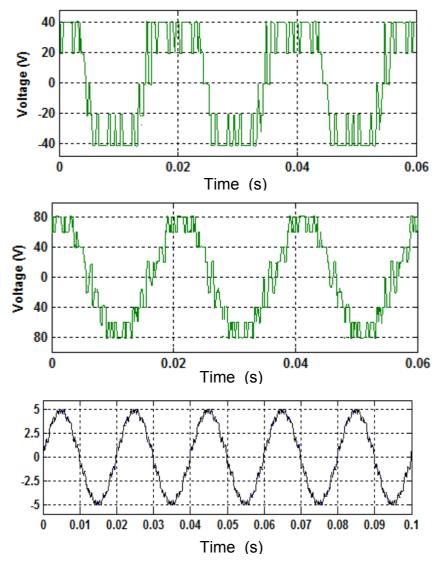

| Figure 4.22: Experimental results (a) Two cascaded H-bridge<br>output Phase voltage, (b) Line voltage and (c) phase current<br>waveform122                                                          |

| Figure 4.23: Simulation results (a) Two cascaded H-bridge output<br>Phase voltage, (b) Line voltage and (c) phase current<br>waveform                                                               |

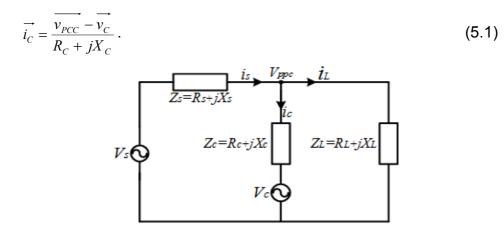

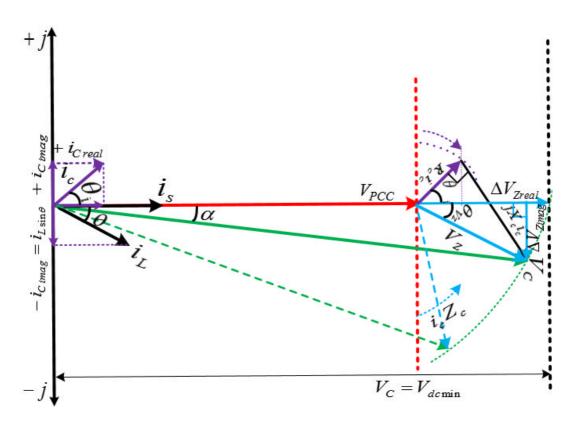

| Figure 5.1: Diagram showing phasor relationship between converter, PCC voltages and currents                                                                                                        |

| Figure 5.2: Diagram showing phasor relationship between converter and PCC voltages127                                                                                                               |

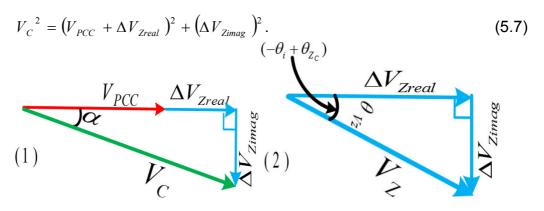

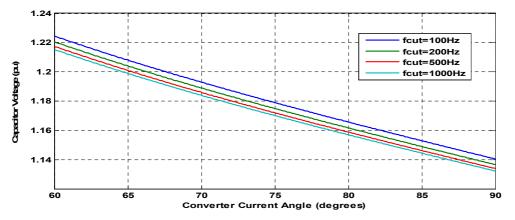

| Figure 5.3: Changes in converter current phase angle against minimum required converter dc-bus voltage when <i>kr</i> =0.3 for <i>f<sub>cut</sub></i> between 100Hz to 1kHz129                      |

| Figure 5.4: Changes in converter current phase angle against<br>minimum required converter dc-bus voltage when <i>k<sub>f</sub></i> =0.1 for<br><i>f<sub>cut</sub></i> between 100Hz to 1kHz129     |

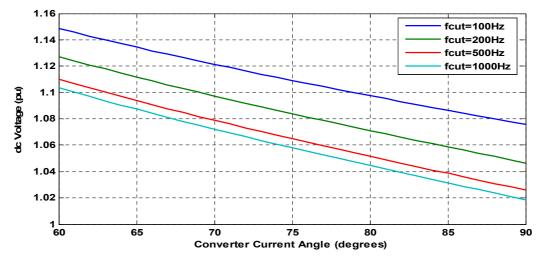

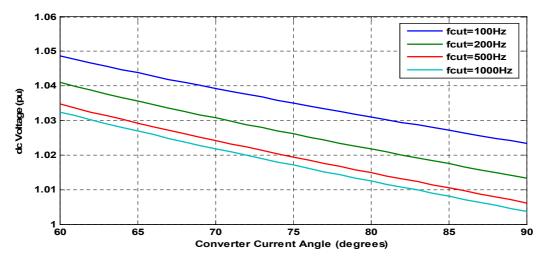

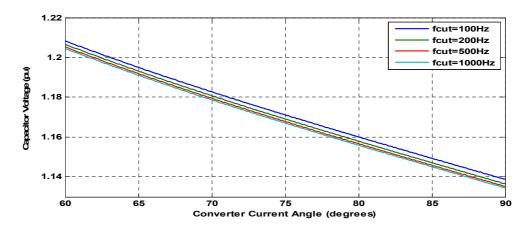

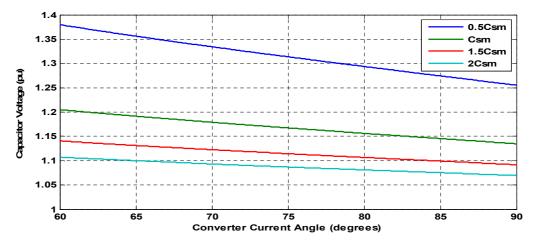

| Figure 5.5: Changes in converter current phase angle against<br>capacitor voltage when $k_{f}=0.3$ for $f_{cut}$ between 100Hz to 1kHz<br>and a fixed capacitance value $C_{sm}=0.56$ mF132       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.6: Changes in converter current phase angle against<br>capacitor voltage ripples when $k_f=0.1$ for $f_{cut}$ between 100Hz<br>to 1kHz and a fixed capacitance value $C_{sm}=0.56$ mF133 |

| Figure 5.7: Changes in converter current phase angle against capacitor voltage when <i>k<sub>f</sub></i> =0.1 for <i>f<sub>cut</sub></i> =1kHz and varying capacitance value                      |

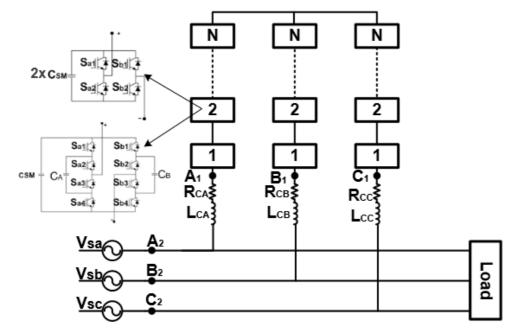

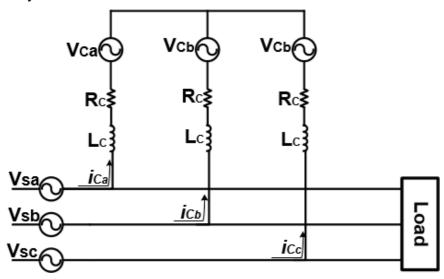

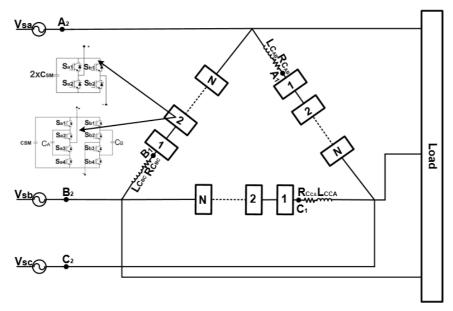

| Figure 5.8: Simulated Power System Configuration136                                                                                                                                               |

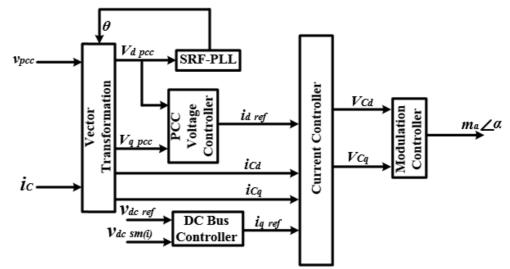

| Figure 5.9: Block diagram of STATCOM controller137                                                                                                                                                |

| Figure 5.10: Overall dc-voltage controller139                                                                                                                                                     |

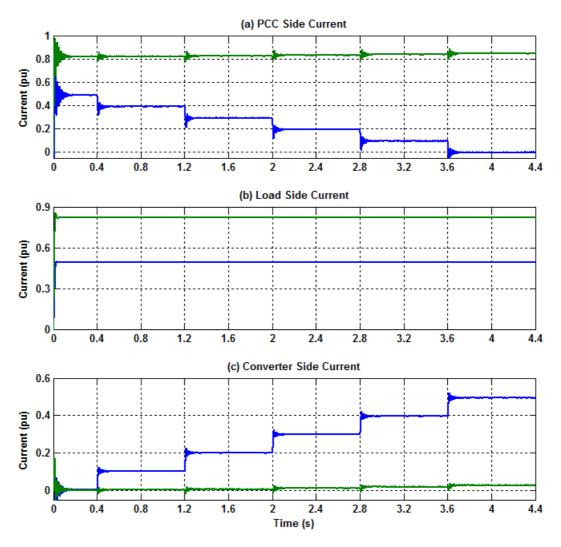

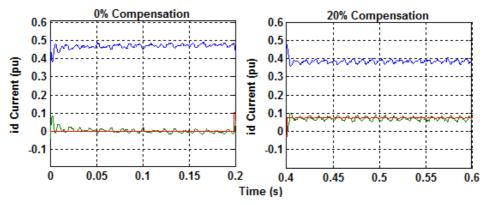

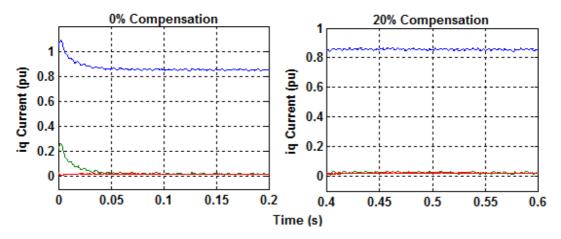

| Figure 5.11: <i>d-q</i> current control, (a) PCC, (b) Load and (c)<br>STATCOM141                                                                                                                  |

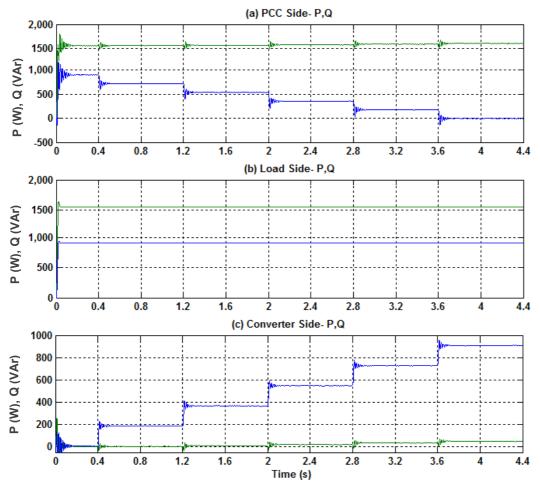

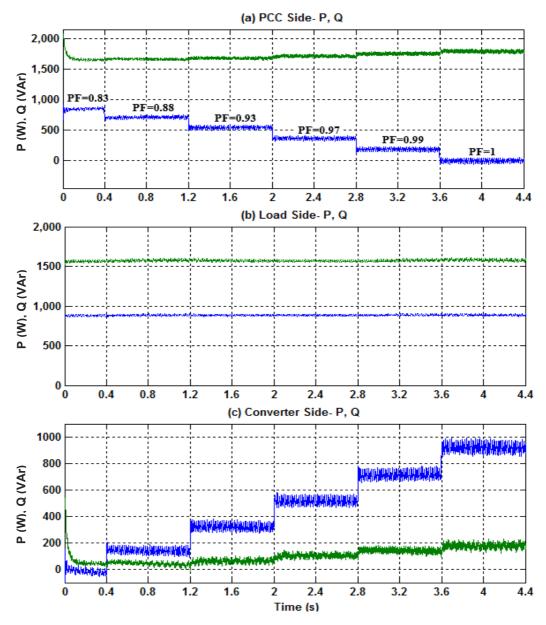

| Figure 5.12: Active and reactive power across (a) PCC, (b) Load<br>and (c) converter sides142                                                                                                     |

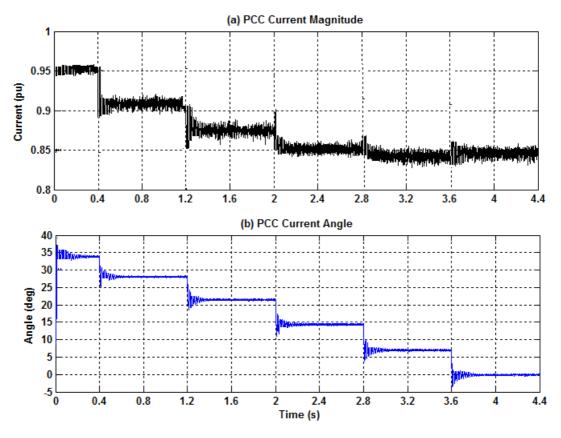

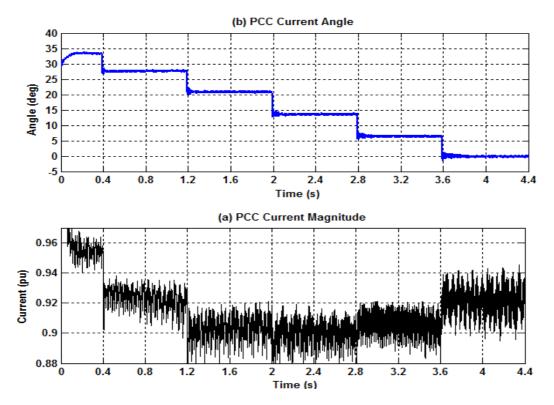

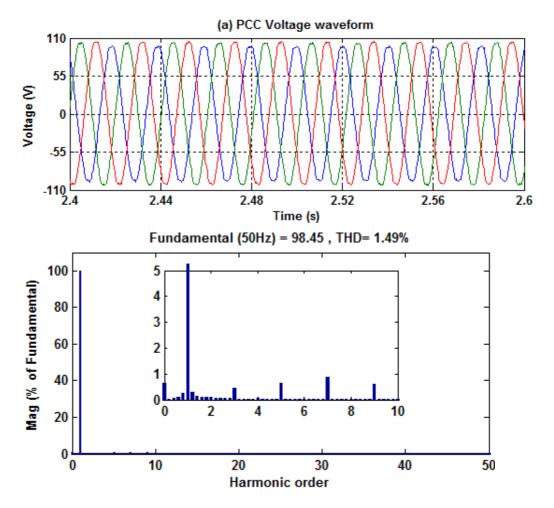

| Figure 5.13: (a) PCC Current magnitude and (b) PCC Current angle                                                                                                                                  |

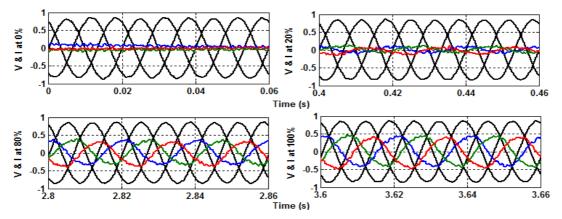

| Figure 5.14: PCC voltage and current waveforms143                                                                                                                                                 |

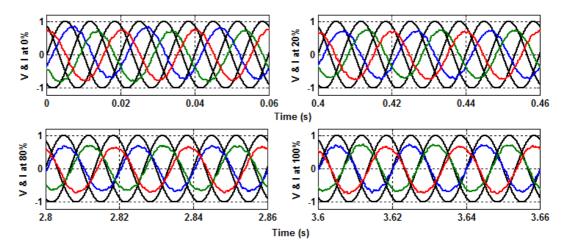

| Figure 5.15: STATCOM voltage and current waveforms144                                                                                                                                             |

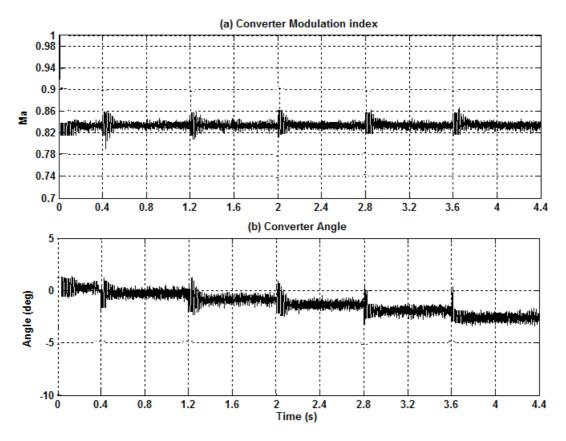

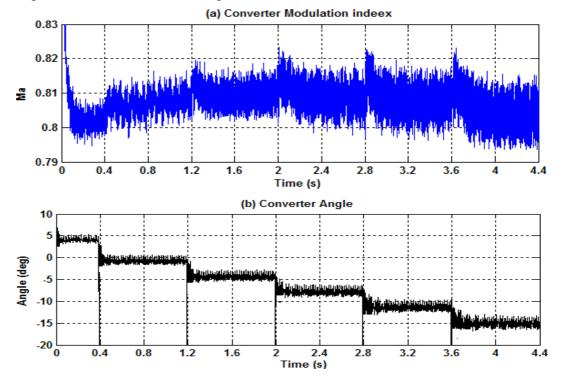

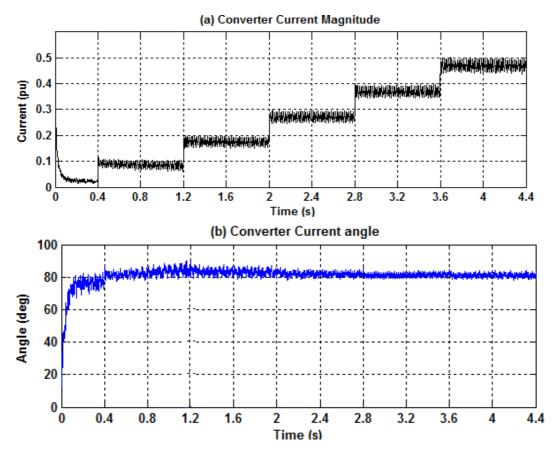

| Figure 5.16: (a) Converter voltage magnitude and (b) angle at zero compensation, 20%, 40%, 60%, 80% and 100%145                                                                                   |

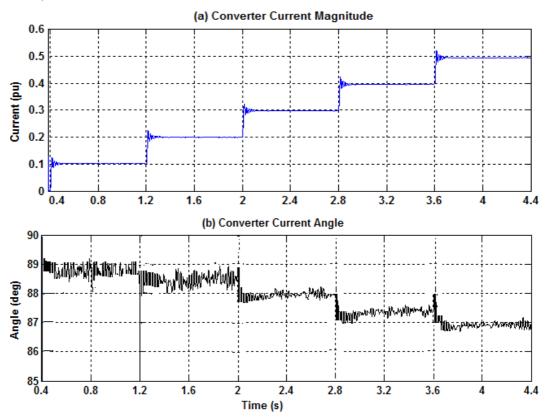

| Figure 5.17: (a) Converter Current magnitude and (b) angle at zero compensation, 20%, 40%, 60%, 80% and 100%145                                                                                   |

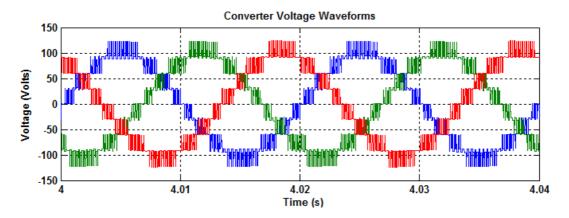

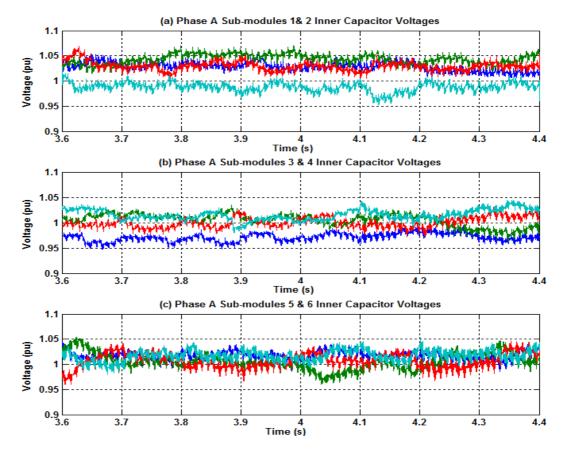

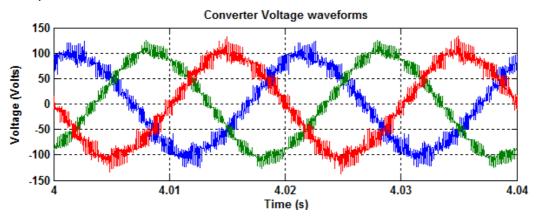

| Figure 5.18: (a) converter Voltage waveforms146                                                                                                                                                   |

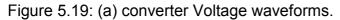

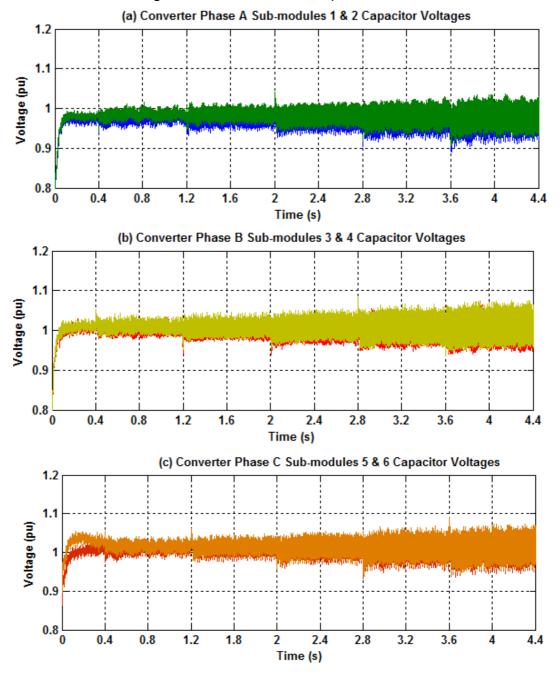

| Figure 5.19: Converter Sub-module capacitor voltages across (a)<br>phase A, (b) phase B and (c) Phase C146                                                                                        |

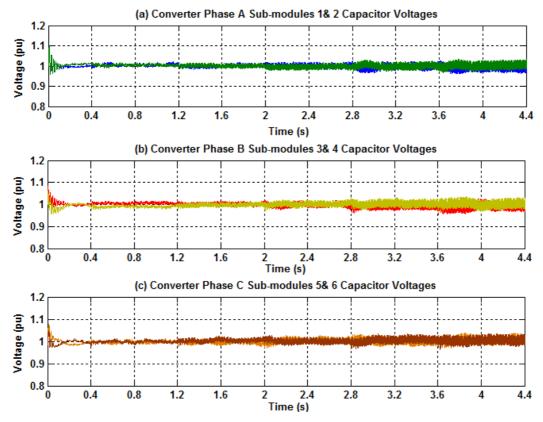

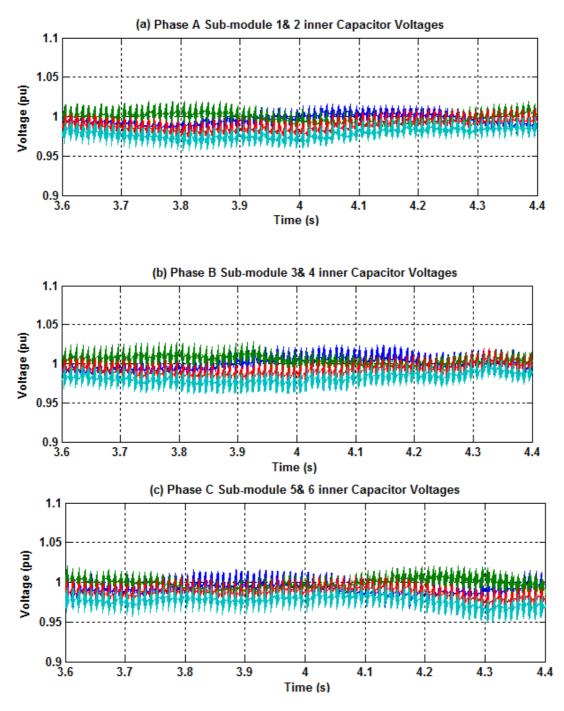

| Figure 5.20: Converter Sub-module inner flying capacitor voltages<br>across (a) phase A, (b) phase B and (c) Phase C147                                                                           |

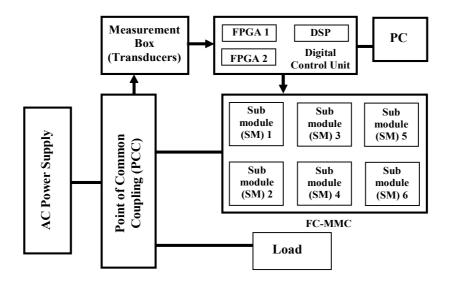

| Figure 5.21: FC-MMCC STATCOM block diagram148                                                                                                                                                     |

| Figure 5.22: (b) 5-level full bridge flying capacitor149                                                                                                                                          |

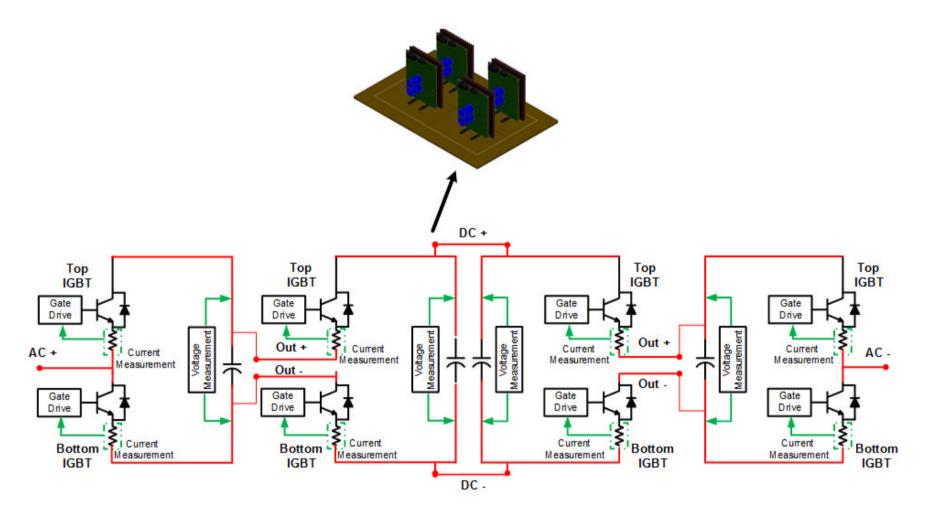

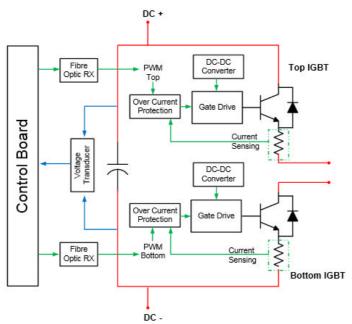

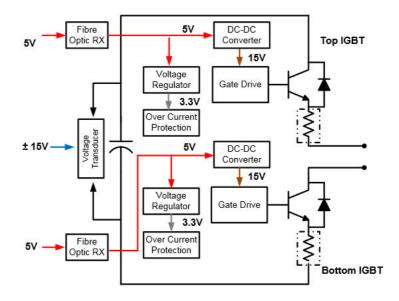

| Figure 5.23: Power cell card circuit diagram150                                                                                                                                                   |

| Figure 5.24: Power cell card power supply layout151                                                                                                                                               |

| Figure 5.25: Measurement Box152                                                                                                                                                                   |

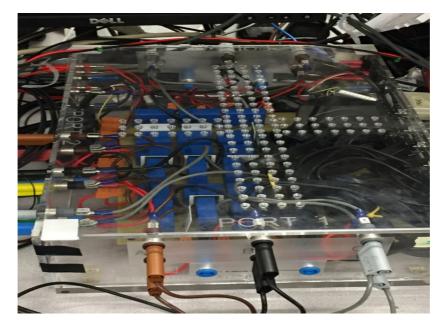

| Figure 5.26: FPGA connected with Fibre Optic Break out Board153                                                                                                                                   |

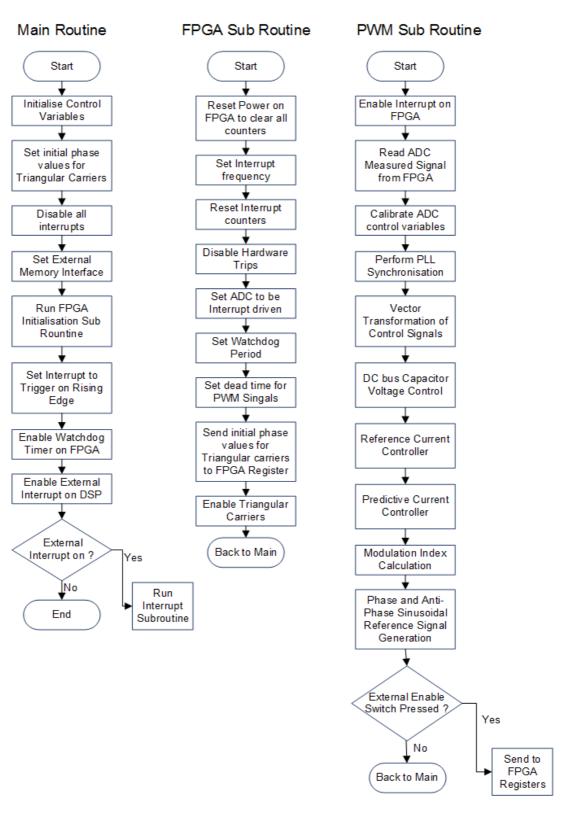

| Figure 5.27: Program Flow Chart for Program Main, FPGA and<br>PWM Routines155                                                                                                                     |

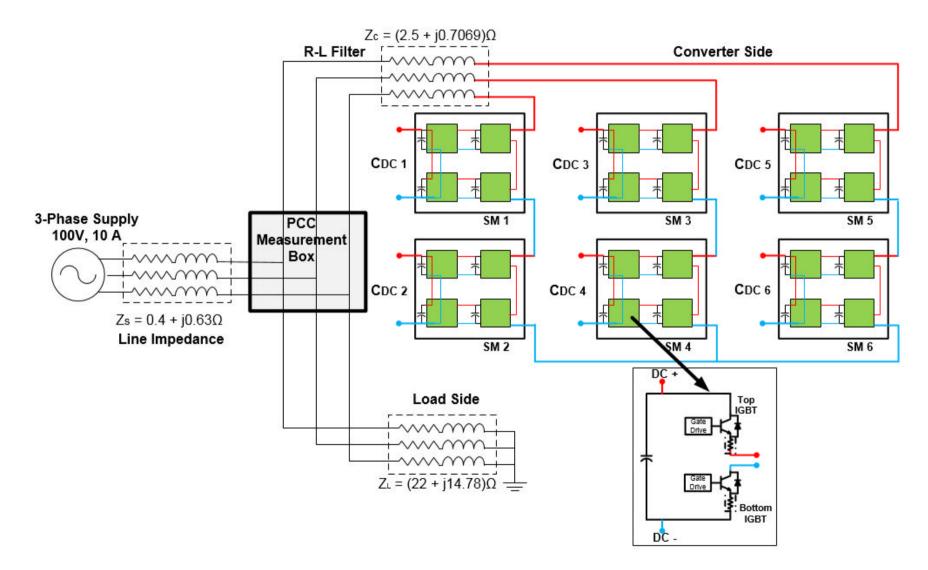

| Figure 5.28: Experimental power system configuration156                                                                                                                                           |

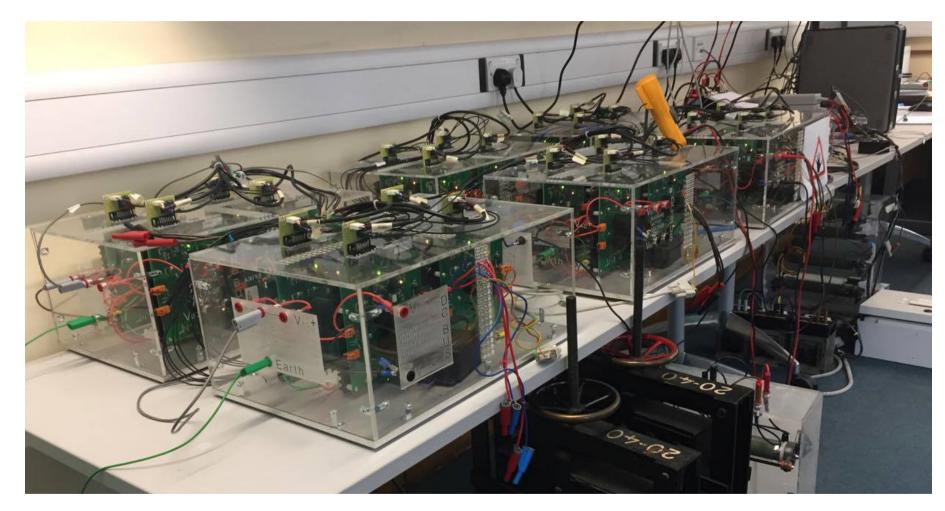

| Figure 5.29: Experimental setup157                                                                                                                                                                |

| Figure 5.30: Block diagram of control system158                                                                                                                                                   |

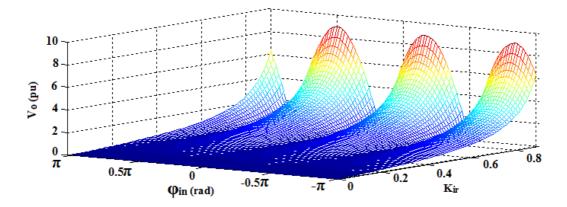

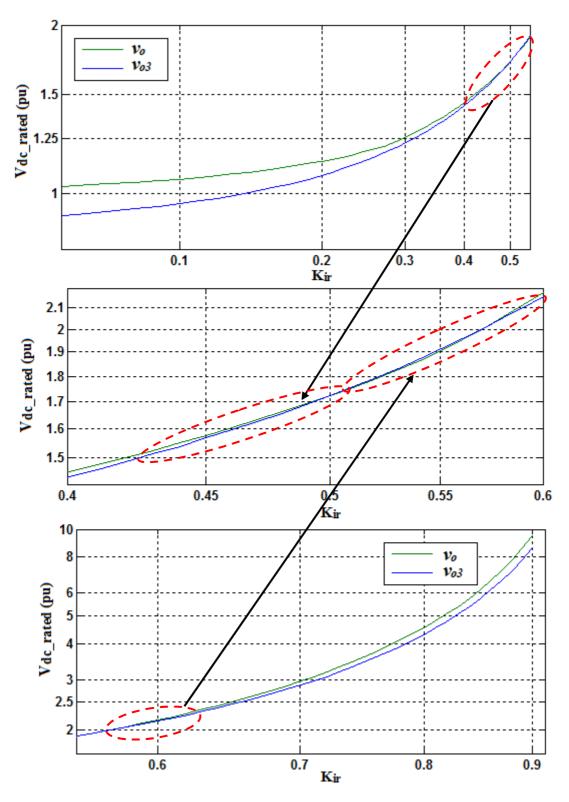

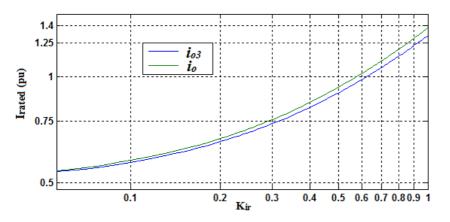

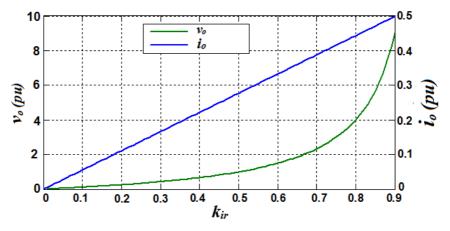

| Figure 6.9: Relationship between the zero sequence voltage<br>magnitude $V_o$ , degree of unbalance $K_{ir} = I_n/I_p$ , and the phase<br>angle of the negative sequence current $\varphi_{in}$ at the maximum<br>PCC voltage 230V                                                                                                         |

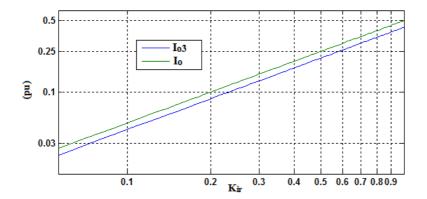

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

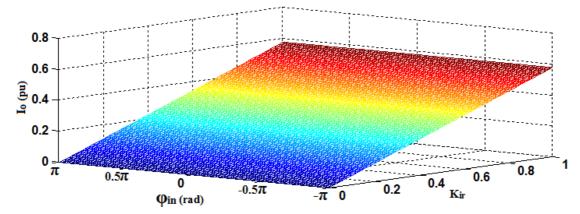

| Figure 6.10: Relationship between the zero sequence current $I_o$ ,<br>degree of unbalance $K_{ir} = I_n/I_p$ , and the phase angle of the<br>negative sequence current $q_n$ at maximum cluster current<br>(2/ $\sqrt{3}$ ) A                                                                                                             |

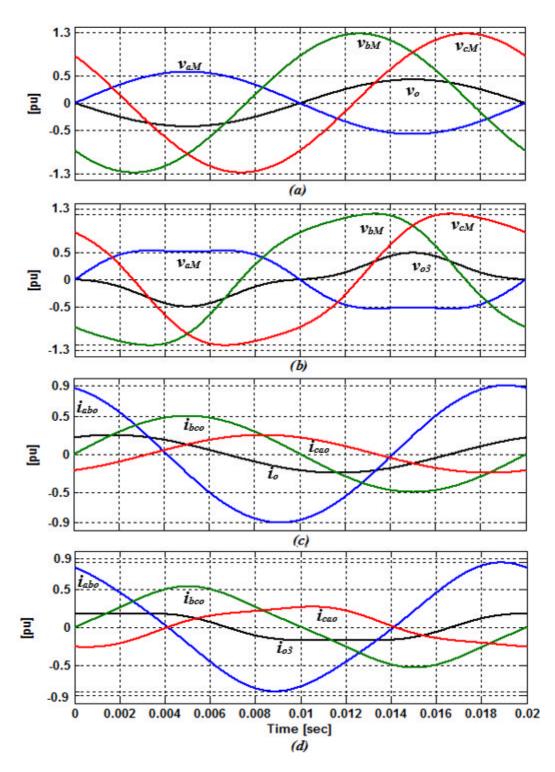

| Figure 6.11: SSBC and SDBC converter cluster voltage and<br>current reference waveforms (a) injecting zero sequence<br>voltage, (b) zero sequence voltage + its third harmonic for<br>$I_n/I_p = 0.3p.u$ , (c) injecting zero sequence current and (d) zero<br>sequence current + its third harmonic injection with<br>$I_n/I_p = 0.55p.u$ |

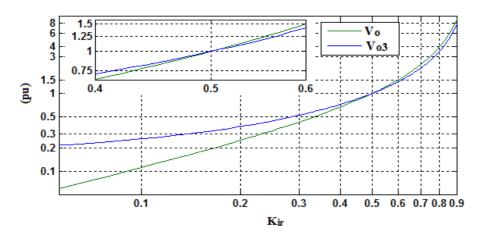

| Figure 6.12: Comparison between sinusoidal and third harmonic zero sequence injection with respect to <i>K</i> <sub>ir</sub> 188                                                                                                                                                                                                           |

| Figure 6.13: Comparison between sinusoidal and third harmonic zero sequence injection with respect to estimated DC-link cluster voltage                                                                                                                                                                                                    |

| Figure 6.14: Comparison between sinusoidal and third harmonic zero sequence injection with respect to <i>K</i> <sub>ir</sub> 190                                                                                                                                                                                                           |

| Figure 6.15: Comparison between sinusoidal and third harmonic zero sequence injection with respect to estimated cluster current                                                                                                                                                                                                            |

| Figure 6.16: Comparison between Zero sequence current and voltage for the same K <sub>ir</sub> =I <sub>n</sub> /I <sub>p</sub> condition at their maximum limits                                                                                                                                                                           |

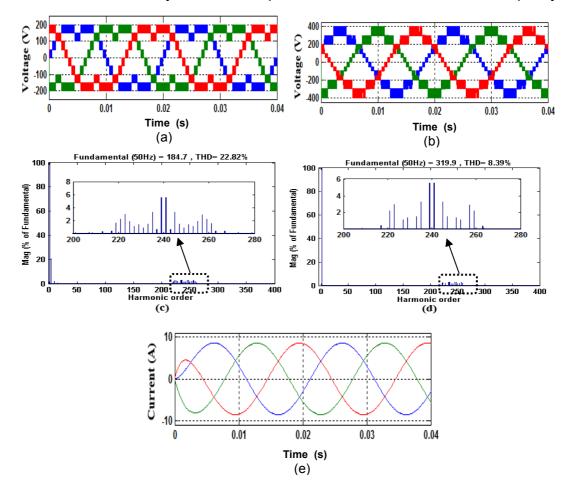

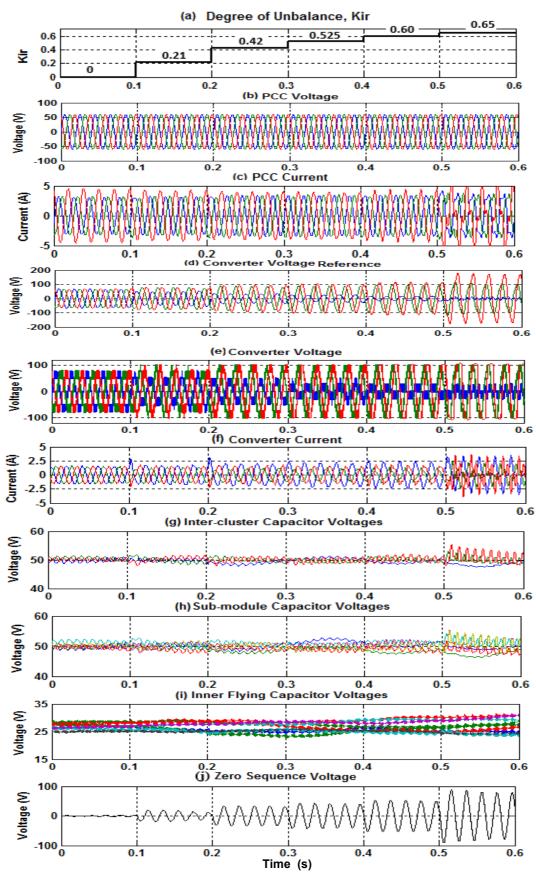

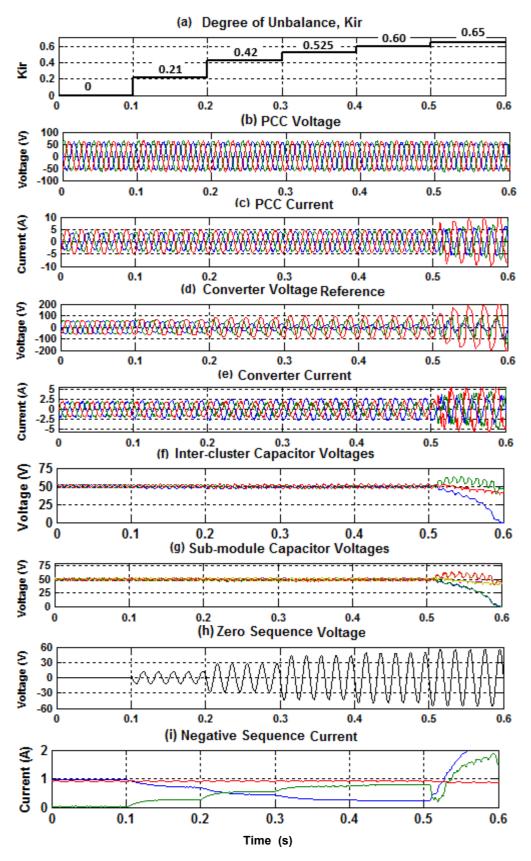

| Figure 6.17: Operating behaviour of SSBC under unbalance load using sinusoidal zero sequence injection194                                                                                                                                                                                                                                  |

| Figure 6.18: Operating behaviour of SSBC under unbalance load compensation using third harmonic zero sequence injection                                                                                                                                                                                                                    |

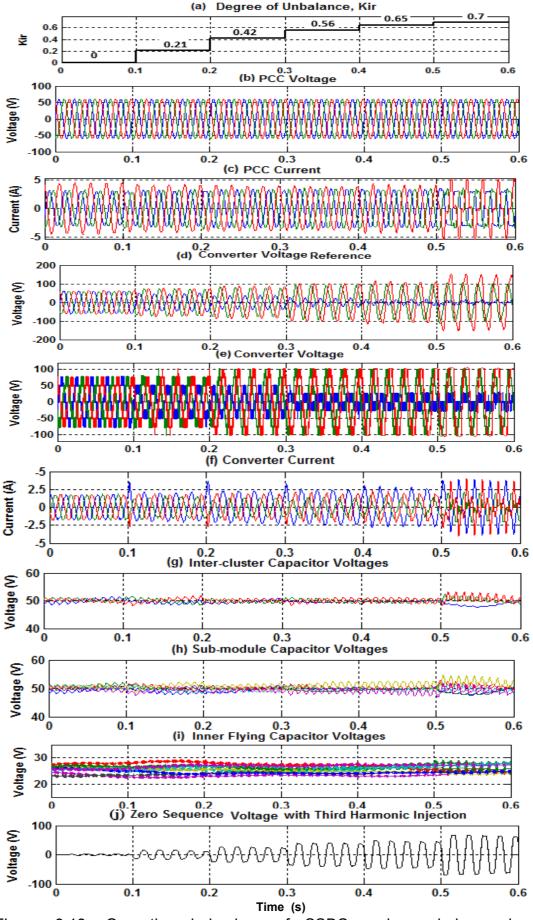

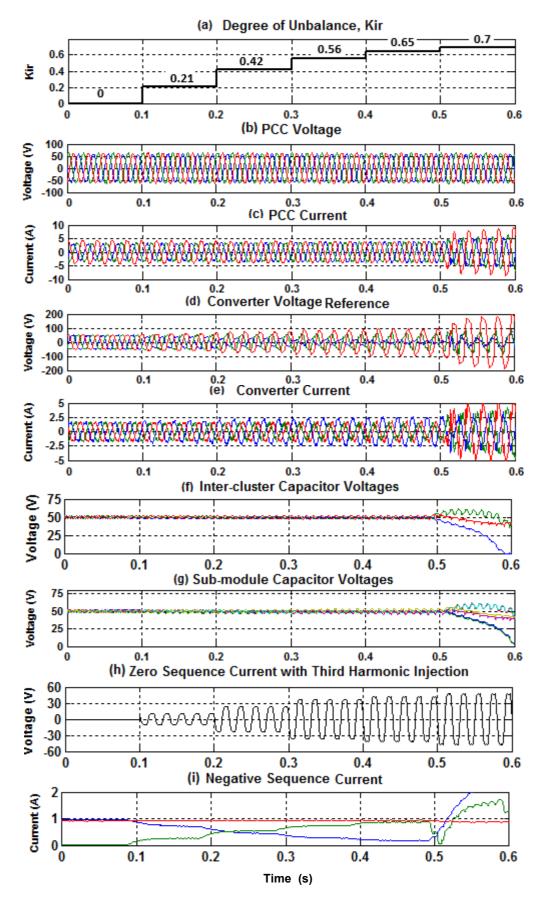

| Figure 6.19: Operating behaviour of SDBC under unbalance load<br>using sinusoidal zero sequence injection                                                                                                                                                                                                                                  |

| Figure 6.20: Operating behaviour of SDBC under unbalance load<br>compensation using third harmonic zero sequence<br>injection                                                                                                                                                                                                              |

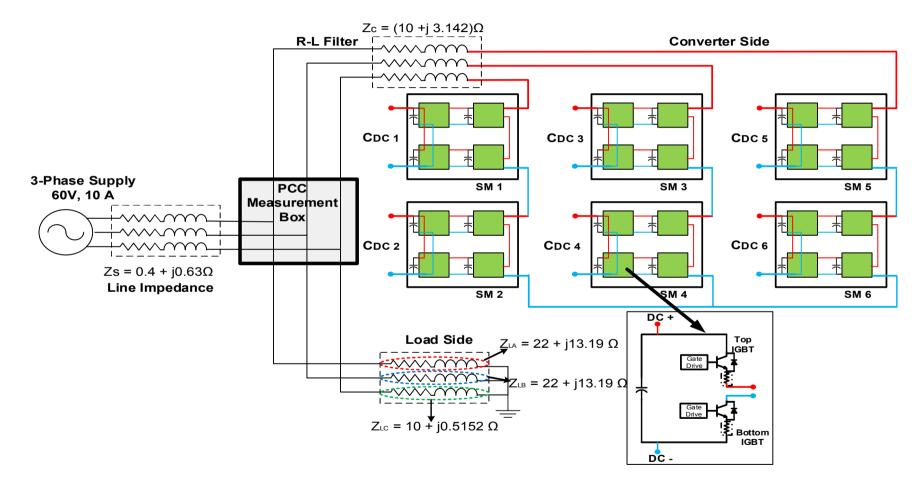

| Figure 6.21: Experimental power system configuration for MMCC in star configuration199                                                                                                                                                                                                                                                     |

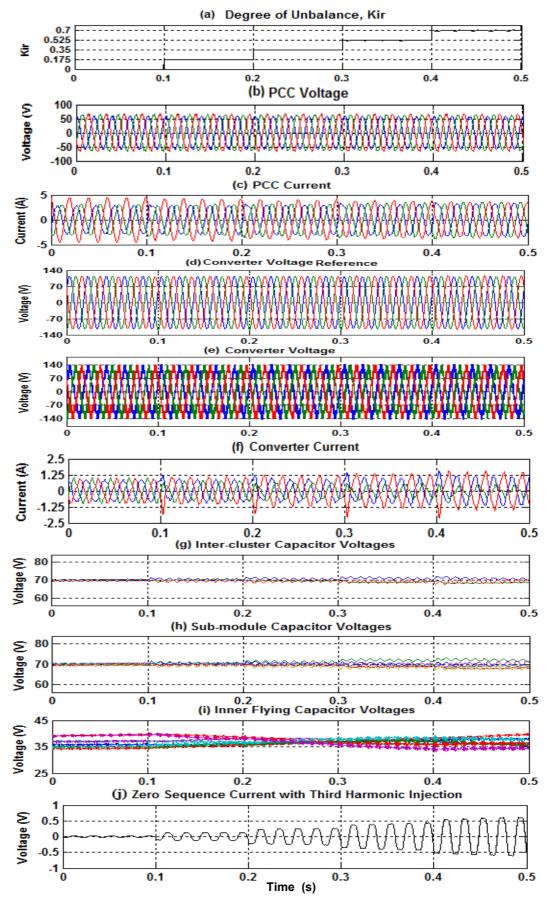

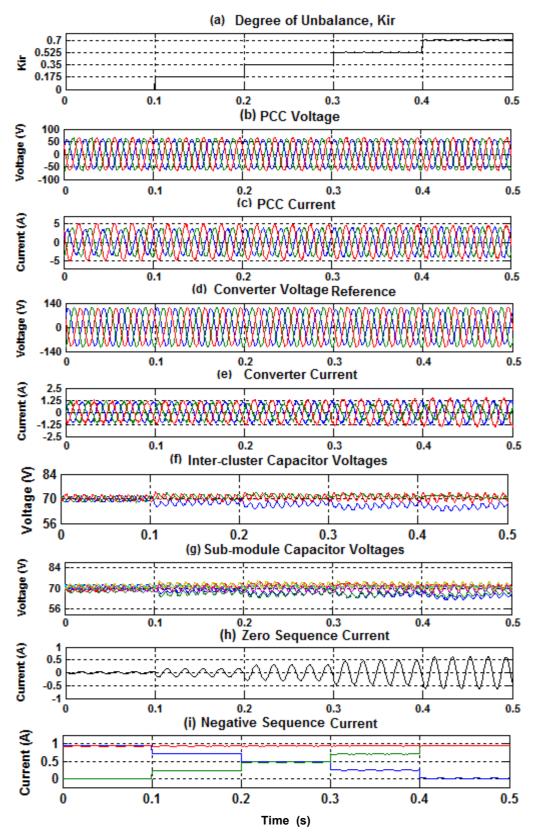

| Figure 6.22: Operating behaviour of SSBC under unbalance load using sinusoidal zero sequence injection                                                                                                                                                                                                                                     |

| - | re 6.23: Operating behaviour of SSBC under unbalance load<br>compensation using third harmonic zero sequence<br>injection |

|---|---------------------------------------------------------------------------------------------------------------------------|

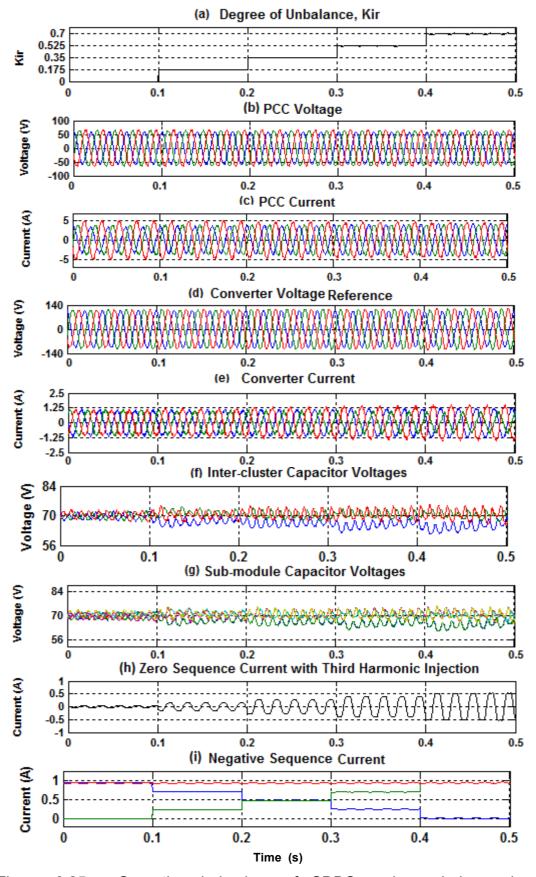

|   | re 6.24: Operating behaviour of SDBC under unbalance load<br>using sinusoidal zero sequence injection                     |

| - | re 6.25: Operating behaviour of SDBC under unbalance load<br>compensation using third harmonic zero sequence<br>injection |

| • | re 6.26: Operating behaviour of SDBC under unbalance load<br>compensation using third harmonic zero sequence<br>injection |

|   | re 6.27: Supply end phase current THD during full compensation of SDBC207                                                 |

## List of Abbreviations

| AC       | Alternating Current                                    |

|----------|--------------------------------------------------------|

| DC       | Direct Current                                         |

| PCC      | Point of Common Coupling                               |

| TCSC     | Thyristor Controlled Series Capacitor                  |

| SVC      | Static VAR Compensator                                 |

| SSSC     | Static Synchronous Series Compensator                  |

| STATCOM  | Static Synchronous Compensator                         |

| UPFC     | Unified Power Flow Controller                          |

| PLL      | Phase Locked Loop                                      |

| DDSRF    | Decoupled Double Synchronisation Reference Frame PLL   |

| CDSC-PLL | Cascaded Delay Signal Cancellation PLL                 |

| EO-PLL   | Energy Operator PLL                                    |

| SRF-PLL  | Synchronisation Reference Frame PLL                    |

| NPC      | Neutral Point Clamped Converter                        |

| FC, FCC  | Flying Capacitor Converter                             |

| MMCC     | Modular Multilevel Cascaded Converter                  |

| FC-MMCC  | Flying Capacitor Modular Multilevel Cascaded Converter |

| PS-PWM   | Phase-Shifting Pulse-Width Modulation                  |

| PD-PWM   | Phase Deposition Pulse Width Modulation                |

| SC-PWM   | Swapped Carrier Pulse Width Modulation                 |

| FACTS    | Flexible AC Transmission Systems                       |

| HVDC     | High Voltage DC Transmission                           |

| SSBC     | Single Star Bridge Cells                               |

| SDBC     | Single Delta Bridge Cells                              |

| DGS      | Distributed Generated System                           |

| 3L       | Three-level                                            |

| 5L       | Five-level                                             |

# Symbols

| Vo, İo                                       | Zero sequence voltage and current                                               |

|----------------------------------------------|---------------------------------------------------------------------------------|

| φο                                           | Zero sequence phase angle                                                       |

| Ip, In                                       | positive and negative sequence currents                                         |

| $oldsymbol{arPhi}$ ip, $oldsymbol{arPhi}$ in | positive and negative sequence current phase angles                             |

| Vp, Vn                                       | positive and negative sequence voltages                                         |

| <b>φ</b> νp, <b>φ</b> νn                     | positive and negative sequence voltage phase angles                             |

| <b>K</b> ir                                  | degree of Load unbalance, $I_n/I_p$                                             |

| lq_ref                                       | reference converter positive sequence active current                            |

| Vdc_avg                                      | average value of three phase sub-module capacitor voltages                      |

| V <sub>dc_i</sub>                            | average value of phase sub-module capacitor voltages,                           |

| <b>n</b> <sub>mp</sub>                       | number of sub-modules per phase                                                 |

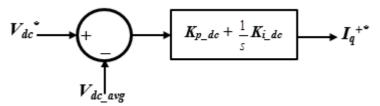

| Kp_dc, Ki_dc                                 | Active Current proportional and integral controller gains                       |

| Kp_c, Ki_c                                   | Cluster voltage balancing proportional and integral controller gains per phases |

| Kio                                          | Circulating current proportional controller gain                                |

| Vs                                           | Maximum Supply side voltage                                                     |

| Vdc_sm(i)                                    | Sub-module capacitor voltage where <i>i=a, b, c or ab, bc, ca</i>               |

| İs                                           | Supply side current                                                             |

| Vci                                          | Converter cluster reference voltages where <i>i=a, b, c or ab, bc, ca</i>       |

| <b>İ</b> ci                                  | Converter cluster currents where <i>i=a, b, c or ab, bc, ca</i>                 |

| ma, Ma                                       | Amplitude modulation index                                                      |

| <b>m</b> f                                   | Frequency modulation index                                                      |

| f                                            | Frequency                                                                       |

| fs                                           | Switching frequency                                                             |

| Ts                                           | Sampling period                                                                 |

| S                                            |                                                                                 |

## Chapter 1 Introduction

## 1.1 Background Literature

Recent decades have seen a tremendous growth in usage of electrical power mainly resulting from industrialization and high population growth rate, especially in developing countries. This has led to more installation of conventional generating units utilizing fossil fuels and in turn increases emission of greenhouse gases especially carbon dioxide, methane, and nitrous oxide. These gases cause an increase in atmospheric temperature which results in global warming and climate change. With the urgent need of reducing these gases, clean and sustainable means of generating electricity using renewable natural sources like wind and solar are now integrated into distributed grid network as distributed generation systems (DGS). Also, the integration of these DGS into the distribution network is encouraged by the market de-regulation. These DGS provide benefits of reduced carbon emission and increase total power capacity.

However, integrating these DGS results in the power network becoming more complex and subject to disturbances. The latter is due to the fact that these DGS are subject to weather conditions, unlike conventional generating sources. With the utilization of electric vehicles and interconnection of several electric grids, there is also the need for integrating AC grids with DC grids, making the distribution network requiring bi-directional flow of power.

An important issue in a distribution network is the current imbalance and voltage unbalance. The unbalanced load connected across the phases results in current imbalance whilst unbalanced voltage is caused by fault conditions across а distribution line and connection of large single phase loads such as single phase traction drives and arc furnaces. These conditions cause undesired effects of equipment malfunction, low power factor and increased line losses. All these challenges pose a serious concern about how the aging existing electrical grid will cope with these issues.

A cost-effective solution is to establish a more efficient distribution network with communication facilities which improve the control of power flow within the distribution network (i.e. efficient management of electrical power distribution and consumption). Therefore, power electronic devices are the electrical infrastructure required in achieving the efficient control of power flow. Presently active research has been carried out on the use of Flexible AC Transmission System (FACTs) [1-13] and High Voltage DC Systems [14-25] in power flow control.

## 1.2 Flexible AC Transmission Systems