## Design and Evaluation of a Single Phase 5 Level Full Bridge Neutral Point Clamped Multi Level Converter

By:

Jonathan David Gomez Palomino

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

The University of Sheffield

Faculty of Engineering

Electronic and Electronical Engineering Department

## **Summary**

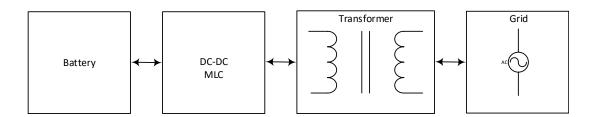

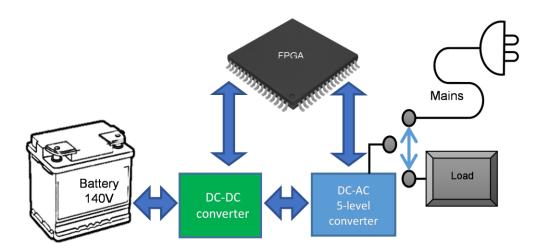

This thesis describes multilevel converters (MLC) designed for use with a repurposed electronic vehicle battery (battery 2<sup>nd</sup> life). MLC is of particular interest due to the low harmonic distortion content and reduced voltage stress in the switching devices. A detailed study of the MLC topologies and modulation techniques is presented. Space vector modulation is analysed and implemented to evaluate the converter. A comprehensive assessment of the MLC is presented using wide bandgap (WBG) devices highlighting the devices' thermal and high switching frequency features.

The converter is designed to be used in construction sites where a reduced output voltage is required. For battery management a DC-DC converter is also added to the system. The modulation of the converters has been evaluated in simulation and a space vector modulation adaptation for single phase converters has been selected to generate the switching sequence and capacitor voltage balancing.

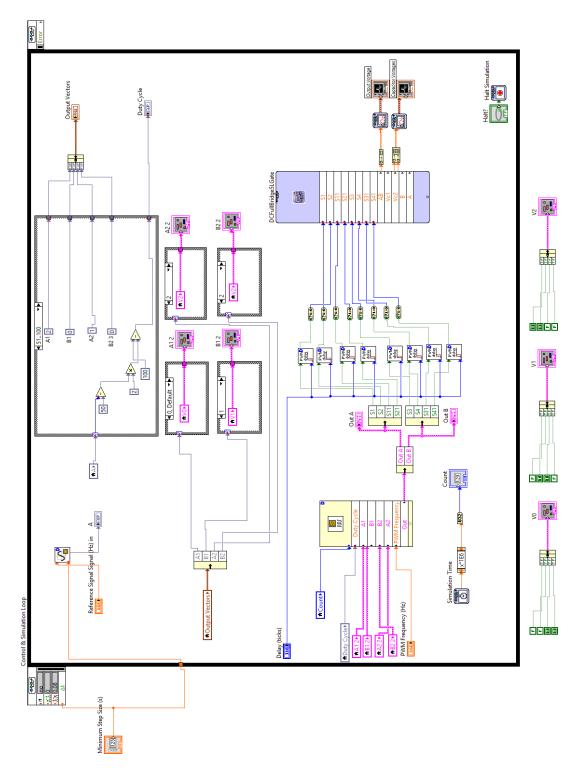

The topology studied in this research is a full bridge 5-Level Neutral Point Clamped (NPC). This thesis presents the evaluation of the MLC including the design and system validation through simulation and physical implementation, showing the feasibility of the use of the converter for the intended application. The control of the converters was developed using NI LabVIEW FPGA and validated using Co-simulation. In this thesis, the use of the Co-simulation with NI Multisim to evaluate the system provided a design environment for a smooth transition into the hardware implementation and it enabled a robust and reliable control system.

This thesis also presents an evaluation of performance using WBG semiconductor devices in the MLC based on the temperature rise over a range of frequencies. Therefore, a comparison between WBG and silicon devices is assessed and an investigation on the power quality of the converter has been examined in terms of the harmonic content and overall efficiency. The experimental results using WBG devices show a considerable advantage in terms of a reduced temperature rise and an increase in the overall efficiency when the MLC was operated using WBG devices.

## **Publications**

- [P1] **J.D. Gomez-Palomino**, M.P. Foster and D.A. Stone, 'Performance evaluation of SiC MOSFET in 5-level single phase converter' IET Power Electronics Machines and Drives (PEMD) 2016.

- [P2] **J.D. Gomez-Palomino**, M.P. Foster and D.A. Stone, 'Bidirectional cascaded DC-DC converter and multilevel converter (MLC) integrated for vehicle-to-grid (V2G) interface using hybrid/electric vehicle's (HEV/EV) battery' UK Energy Storage (UKES) 2014.

## Acknowledgements

I would like to thank firstly to my supervisors Prof. Martin Forster and Prof. David Stone for their guidance and support during my studies.

A special acknowledgement to my parents for their support and encouragement to complete my degree.

I would also like to thank all the staff in the University of Sheffield EEE department for their support and dedication to maintain the department and EMD group running smoothly. Special thanks to my colleagues Jonathan Davidson, David Hewitt, Shahab Nejad, Sami Abuzed and my friends Chi Wa Tsang and Rui Zhao for their help and support.

This study was done with financial support of the Mexican Council of Science and Technology (CONACyT) under the scholarship number 215289

## Table of contents

| Summary                               | i    |

|---------------------------------------|------|

| Publications                          | ii   |

| Acknowledgements                      | iii  |

| Table of contents                     | iv   |

| Symbol list                           | viii |

| Acronyms list                         |      |

| List of Figures                       |      |

| List of Tables                        |      |

| Chapter 1 Introduction                |      |

| 1.1 Application and Motivation        | 2    |

| 1.2 Thesis outline                    | 4    |

| 1.3 References                        | 5    |

| Chapter 2 – Background                | 6    |

| 2.1 – Introduction                    | 6    |

| 2.2 – Multi-Level Converters          | 7    |

| 2.2.1 Neutral-Point Clamped Converter | 8    |

| 2.2.2 Flying capacitor converter      | 15   |

| 2.2.3 Cascaded H-Bridge.              | 22   |

| 2.2.4 Comparison                      | 25   |

| 2.3 – Modulation in MLC               | 26   |

| 2.3.1 Selective harmonic elimination  | 26   |

| 2.3.2 Space Vector Modulation         | 26   |

| 2.3.3 Sinusoidal PWM                  | 27   |

| 2.4 – Applications                    | 27   |

| 2.4.1 – Battery connected MLCs        | 29   |

| 2.5– Conclusion                       | 31   |

| 2.6 – References                      | 32   |

| Chapter 3 – | Modulation Techniques                         | 36 |

|-------------|-----------------------------------------------|----|

| 3.1 – Intr  | oduction                                      | 36 |

| 3.2 – Sin   | usoidal PWM                                   | 38 |

| 3.2.1 S     | inusoidal PWM simulation                      | 43 |

| 3.3 – 1-D   | Space vector modulation                       | 58 |

| 3.3.1 N     | Nearest 2 vectors modulation for 5-L-FB-NPC   | 59 |

| 3.3.2 C     | Capacitor Voltage Balancing N2V               | 61 |

| 3.3.3 –     | Simulation space vector modulation            | 63 |

| 3.4 Chapt   | ter conclusion                                | 66 |

| 3.5 Refer   | ences                                         | 66 |

| Chapter 4 – | Converter design                              | 68 |

| 4.1 Introd  | luction                                       | 68 |

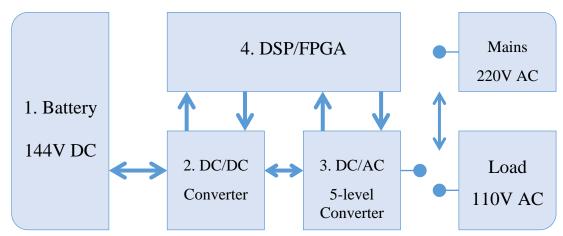

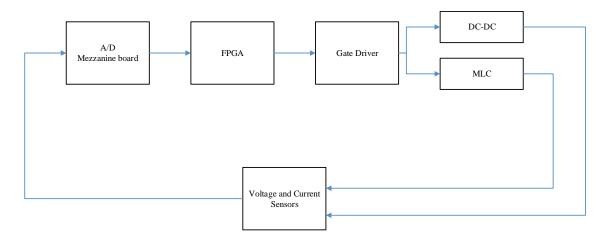

| 4.2 Platfo  | orm system description and specification      | 69 |

| 4.3 Conv    | erter Design                                  | 71 |

| 4.3.1 D     | OC-DC converter design                        | 71 |

| 4.3.2 N     | Multilevel converter design                   | 76 |

| 4.4 Syste   | m Simulation Results                          | 82 |

| 4.4.1 D     | Discharging mode with nominal battery voltage | 83 |

| 4.4.2       | Discharging mode with minimum battery voltage | 84 |

| 4.4.3       | Charging mode with maximum grid voltage       | 87 |

| 4.4.4       | Charging mode with minimum grid voltage       | 87 |

| 4.4.5       | Closed loop evaluation                        | 88 |

| 4.5 Chapt   | ter conclusion                                | 91 |

| 4.6 Refer   | ences                                         | 91 |

| Chapter 5 – | System experimental evaluation                | 93 |

| 5.1 – Intr  | oduction                                      | 93 |

| 5.2 – FPC   | GA control platform                           | 94 |

| 5.2.1       | FPGA implementation.                          | 95 |

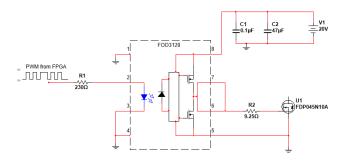

| 5.3 Gate   | driver circuit design                                                    | 99     |

|------------|--------------------------------------------------------------------------|--------|

| 5.4 Isolat | ed voltage and current input and output                                  | 100    |

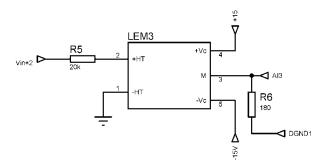

| 5.4.1      | Isolated voltage transducer                                              | 101    |

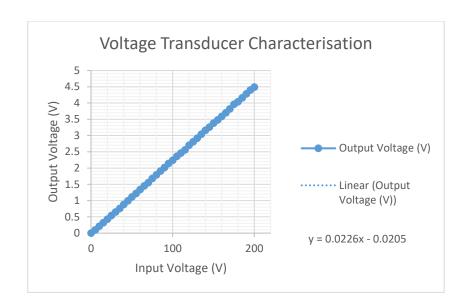

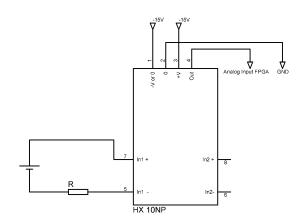

| 5.4.2      | Isolated current transducer.                                             | 102    |

| 5.5 DO     | C-DC converter evaluation                                                | 103    |

| 5.5.1      | Inductor                                                                 | 104    |

| 5.5.2 D    | OC-DC converter testing                                                  | 105    |

| 5.6 Multi  | level converter testing                                                  | 109    |

| 5.6.1 N    | Multilevel converter full bridge operation and capacitor voltage balanci | ng 110 |

| 5.6.2 F    | Full-bridge 5-level converter operation                                  | 111    |

| 5.6.3 T    | ransformer                                                               | 113    |

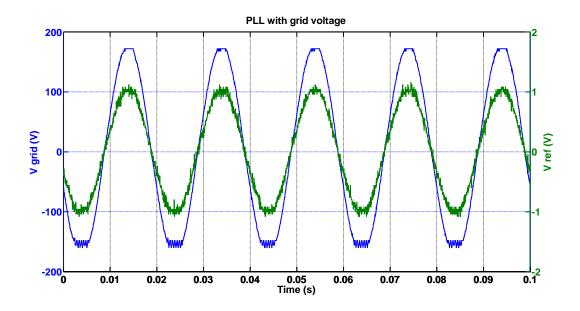

| 5.7 Phase  | locked loop with grid                                                    | 113    |

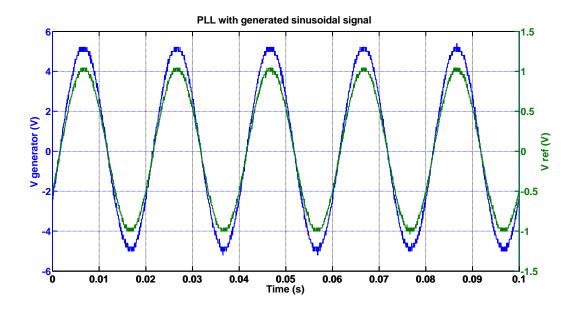

| 5.7.1      | PLL to generate reference signal for MLC                                 | 114    |

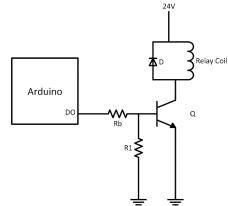

| 5.8 Sa     | fety and protection circuit                                              | 115    |

| 5.8.1      | Fuse selection                                                           | 115    |

| 5.8.2 B    | Sattery protection circuit                                               | 115    |

| 5.8.3      | Safety enclosure                                                         | 116    |

| 5.9 Chap   | ter conclusion                                                           | 117    |

| 5.10 Refe  | erences                                                                  | 117    |

| -          | - Evaluation of 5L-FB-NPC MLC featuring wide bandgap semicon             |        |

|            | oduction                                                                 |        |

| 6.2 – 5-le | vel NPC Converter                                                        | 121    |

| 6.3 – Wio  | de bandgap semiconductors devices                                        | 121    |

| 6.3.1      | – Si and SiC evaluation devices                                          | 122    |

| 6.4 – I    | Experimental evaluation                                                  | 123    |

| 6.4.1      | - Hardware setup                                                         |        |

| 6.4.2      | Temperature rise and efficiency results                                  | 126    |

|            |                                                                          |        |

| 6.4.3 – Voltage and current waveforms comparison      | 130 |

|-------------------------------------------------------|-----|

| 6.5 – Conclusion                                      | 135 |

| 6.6 – References                                      | 136 |

| Chapter 7 – Power quality evaluation in 5L-FB-NPC MLC | 137 |

| 7.1 – Introduction                                    | 137 |

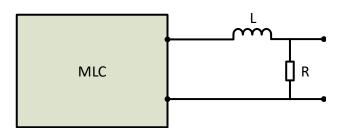

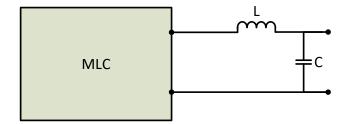

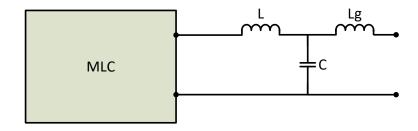

| 7.2 – Multilevel converter (MLC) filter               | 138 |

| 7.2.1 – L filter                                      | 138 |

| 7.2.2 – LC filter                                     | 139 |

| 7.2.3 – LCL filter                                    | 139 |

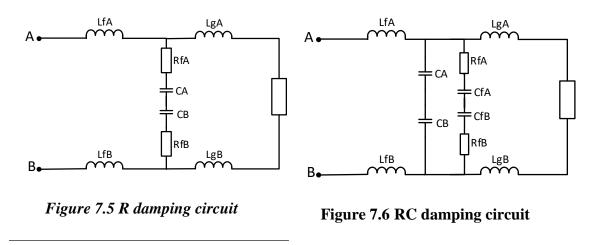

| 7.2.4 – Damping circuit                               | 140 |

| 7.3 – Power Quality                                   | 143 |

| 7.3.1 Norms and standards                             | 144 |

| 7.3.2 MLC harmonic evaluation                         | 145 |

| 7.3.1 THD comparison Si and SiC                       | 147 |

| 7.4 – Conclusion                                      | 153 |

| 7.5 – References                                      | 154 |

| Chapter 8 – Conclusion and further work               |     |

| 8.1 Conclusion                                        | 156 |

| 8.2 Further work                                      | 158 |

# Symbol list

| Symbol              | Definition                     |

|---------------------|--------------------------------|

| $\Delta I_L$        | Current ripple                 |

| $\Delta V_C$        | Capacitor voltage ripple       |

| a                   | Reference signal               |

| A,B                 | Output terminals               |

| $A_{CU}$            | Conductor area                 |

| $A_e$               | Effective area                 |

| $A_W$               | Winding area                   |

| $B_s$               | Saturation flux density        |

| C, C0, C1,,C15      | Capacitors                     |

| $C_{DC}$            | DC link capacitor              |

| $C_f$               | Damping capacitor              |

| $C_{ISS}$           | Input capacitance              |

| D                   | Duty cycle                     |

| D, D0, D01, D1,, D6 | Diodes                         |

| $D_{boost}$         | Duty cycle in discharging mode |

| $D_{buck}$          | Duty cycle in charging mode    |

| f                   | Frequency                      |

| $f_{sw}$            | Switching frequency            |

| $I_{DS}$            | Drain to source current        |

| $I_G$               | Gate current                   |

| $I_L$               | Inductor current               |

| $I_{out}$           | Output current                 |

| $I_{sw}$            | Switch drain source current    |

| $k_{CU}$            | Packing factor                 |

| L                   | Inductor                       |

| $L_f$               | Inductor filter                |

| $l_g$               | Airgap length                  |

| $L_g$               | Grid side inductor             |

| m                   | Number of levels               |

| $N_{min}$           | Minimum number of turns        |

| $P_{out}$           | Output power                   |

*Q1, ..., Q4* MOSFETs

Q1', ..., Q4' MOSFETs operating in complementary form

$Q_G$  Gate charge  $R_b$  Base resistor

$R_{DS}$  Drain to source resistance

$R_f$  Damping resistor

$R_G$  Gate resistor  $R_{load}$  Load resistor

$R_{th}$  Thermal resistance

*S, S1, ..., S8* MOSFETs

S', S1', ..., S8' MOSFETs operating in complementary form S11, S21, S31, S41 MOSFETs operating in complementary form

*t*<sub>transition</sub> Transition time

*V*, *V*/2, *V*/4 Voltages

$V_1$  Fundamental component

$V_{batt}$  Battery voltage

$V_C$ ,  $V_{C1}$ ,  $V_{C2}$  Capacitor voltage

$V_{DC}$  DC-link voltage

$V_{DS}$  Drain to source voltage

$V_{grid}$  Grid voltage

$V_n$  Harmonics of fundamental

$V_{out}$  Output voltage

### Acronyms list

**Definition** Acronym AC**Alternating Current APOD** Alternately in Opposition Disposition ASIC **Application Specific Integrated Circuits** BSI **British Standards Institution CENELEC** Comite Europeen de Normalisation Electrotechnique **CHB** Cascaded H-Bridge DC Direct Current DSP Digital Signal Processor **EMC Electromagnetic Compatibility** EV Electric Vehicle **FACTS** Flexible AC Transmission System FB Full Bridge FCC Flying Capacitor Converter FFT Fast Fourier Transform **FPGA** Field Programmable Array GaN Gallium Nitride **GTO** Gate Turn-Off HB Half Bridge **HBC** H-Bridge Converter **HEV** Hybrid Electric Vehicle IC **Integrated Circuit**

**IEEE** Institute of Electrical and Electronic Engineers

**IGBT** Insulated Gate Bipolar Transistor

LB Logic Blocks

LUT Look-Up Tables

**MEA** More Electric Aircraft **MLC** Multi-level Converter

Modular Multilevel Converter **MMC**

Metal-Oxide Semiconductor Field Effect Transistor **MOSFET**

N<sub>2</sub>V Nearest 2 vectors

NI **National Instruments**  NPC Neutral-Point Clamped

PD Phase Disposition

PHEV Plug-in Hybrid Electric Vehicle

PI Proportional and Integral controller

PLL Phase-Locked Loop

POD Phase Opposition Disposition

PWM Pulse Width Modulation

SiC Silicon Carbide

STATCOM Static-Synchronous Compensation

SVM Space Vector Modulation

THD Total Harmonic Distortion

V2G Vehicle to Grid

VHDL VHSIC Hardware Description Language

WBG Wide bandgap

# List of Figures

| Figure 1.1: Circuit diagram for the 5-level single-phase converter                | ∠        |

|-----------------------------------------------------------------------------------|----------|

| Figure 2.1 Functional diagram of a DC to AC converter                             | <i>6</i> |

| Figure 2.2 Neutral-Point Clamped 3-levels single phase                            | 8        |

| Figure 2.3 NPC 3-levels output waveform                                           | 9        |

| Figure 2.4 Neutral-Point Clamped 5-levels full bridge single phase                | 10       |

| Figure 2.5 NPC 5-levels full bridge output voltage waveform                       | 11       |

| Figure 2.6 Neutral-Point Clamped 5-level Half Bridge Single phase                 | 12       |

| Figure 2.7 NPC 5-levels output voltage waveform                                   | 13       |

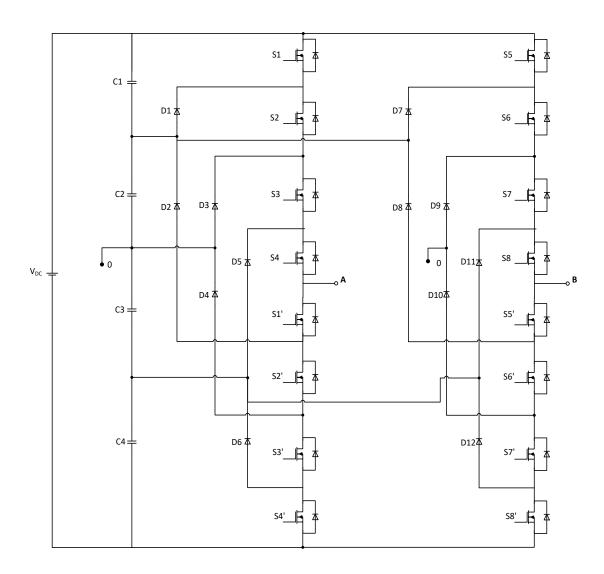

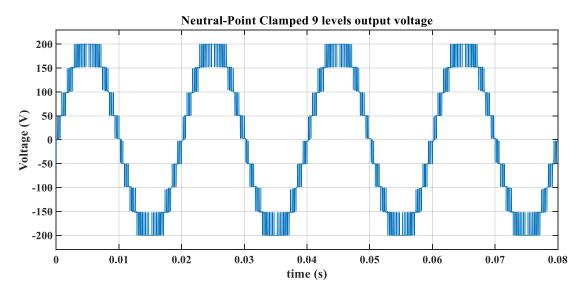

| Figure 2.8 Neutral-Point Clamped 9-level Full Bridge Single phase                 | 14       |

| Figure 2.9 NPC 9-levels full bridge output voltage waveform                       | 14       |

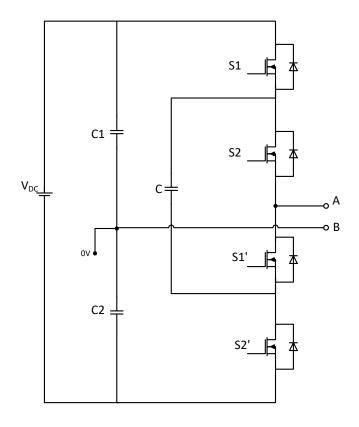

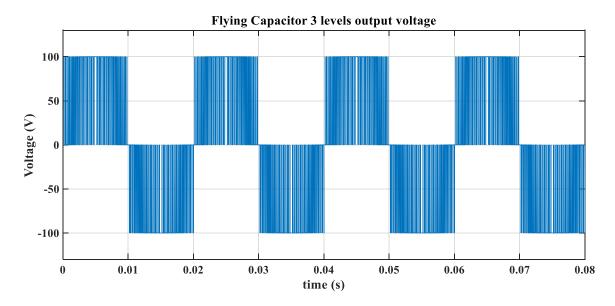

| Figure 2.10 Flying capacitor 3-level single phase                                 | 16       |

| Figure 2.11 Flying capacitor 3-levels output voltage waveform                     | 17       |

| Figure 2.12 Flying Capacitor 5-level Full Bridge Single phase                     | 18       |

| Figure 2.13 Flying capacitor 5-levels output voltage waveform                     | 19       |

| Figure 2.14 Flying capacitor 5-level half bridge single phase                     | 19       |

| Figure 2.15 Flying capacitor 5-levels half bridge output voltage waveform         | 20       |

| Figure 2.16 Flying capacitor 9-level full bridge single phase                     | 21       |

| Figure 2.17 Flying capacitor 9-levels output voltage waveform                     | 22       |

| Figure 2.18 Cascaded H-bridge 3-levels topology                                   | 22       |

| Figure 2.19 H-bridge 3-levels output voltage waveform                             | 23       |

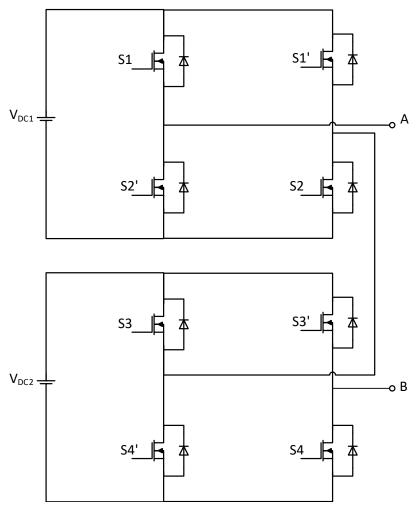

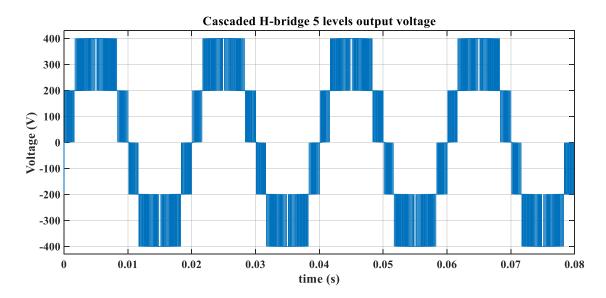

| Figure 2.20 Cascaded H-bridge 5-levels topology                                   | 24       |

| Figure 2.21 5-levels cascaded H-bridge output voltage waveform                    | 24       |

| Figure 2.22 Bidirectional buck boost cascade converter                            | 30       |

| Figure 2.23 Simplified bidirectional buck boost cascade conveter                  | 31       |

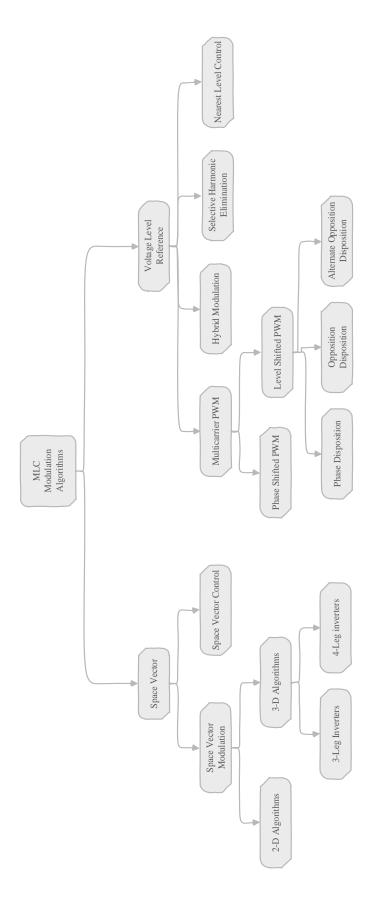

| Figure 3.1 MLC modulation classification                                          | 37       |

| Figure 3.2 5-level Neutral Point Clamped Converter                                | 39       |

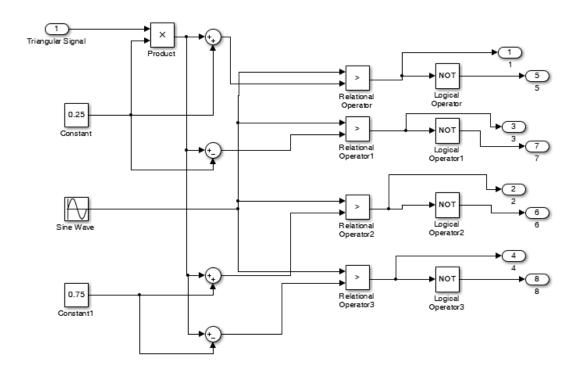

| Figure 3.3. PWM generator for 5-level converter.                                  | 40       |

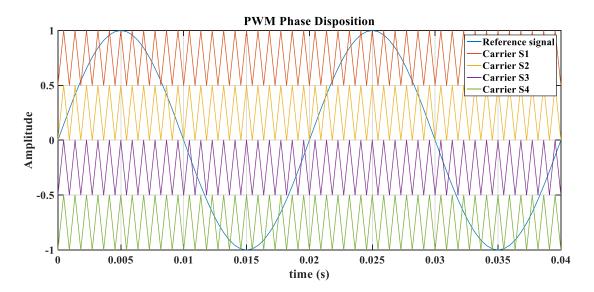

| Figure 3.4 Sinusoidal reference and carrier signals for Phase Disposition PWM     | 41       |

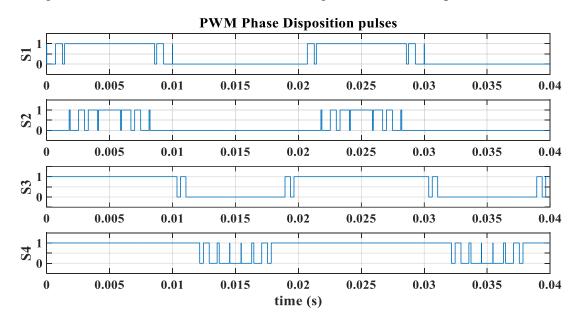

| Figure 3.5 Switching pulses Phase Disposition                                     | 41       |

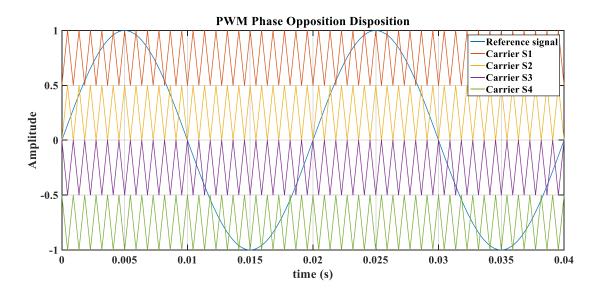

| Figure 3.6 Sinusoidal reference and carrier signals for Phase Opposition PWM      | 42       |

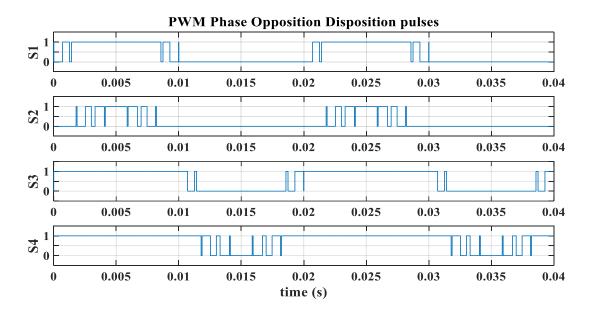

| Figure 3.7 Switching pulses Phase Opposition Disposition                          | 42       |

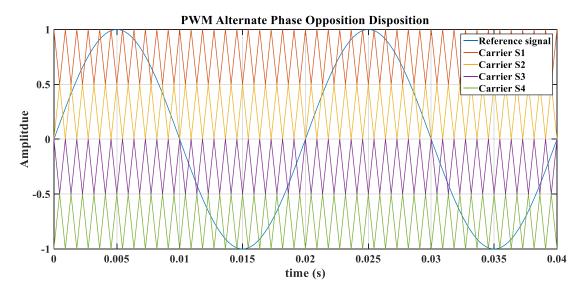

| Figure 3.8 . PWM sinusoidal reference and carrier signals for Alternately in Oppo | osition  |

| PWM                                                                               | 43       |

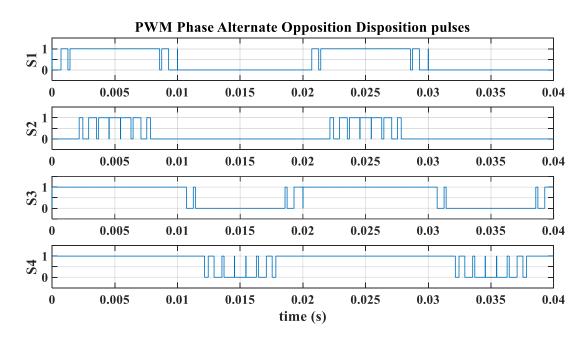

| Figure 3.9 Switching pulses Alternately in Opposition Disposition                    | 43    |

|--------------------------------------------------------------------------------------|-------|

| Figure 3.10. 5-level Diode Clamped Single Phase Half Bridge MLC                      | 45    |

| Figure 3.11. Diode Clamped 1 leg 5-level converter - Phase Disposition               | 46    |

| Figure 3.12. Diode Clamped 1 leg 5-level converter - Phase Opposition Disposition    | 47    |

| Figure 3.13. Diode Clamped 1 leg 5-level converter - Alternatively Opposit           | ition |

| Disposition.                                                                         | 48    |

| Figure 3.14. Flying Capacitor 5-level Single Phase Half Bridge                       | 49    |

| Figure 3.15. Flying Capacitor 1 leg 5-level converter - Phase Disposition            | 50    |

| Figure 3.16. Flying Capacitor 1 leg 5-level converter - Phase Opposition Disposition | n.51  |

| Figure 3.17. Flying Capacitor 1 leg 5-level converter - Phase Alternatively Opposit  | tion  |

|                                                                                      | 52    |

| Figure 3.18. Diode Clamped 9-level Single Phase, Full Bridge.                        | 53    |

| Figure 3.19. Diode Clamped Full Bridge 9-level converter                             | 54    |

| Figure 3.20. Flying Capacitor Full Bridge 5-level converter.                         | 55    |

| Figure 3.21. Flying Capacitor Full Bridge 9-level converter                          | 56    |

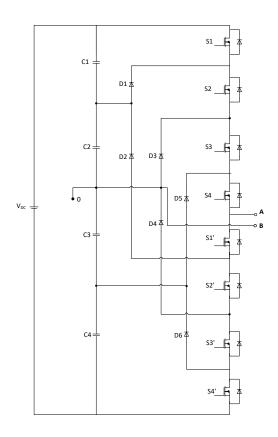

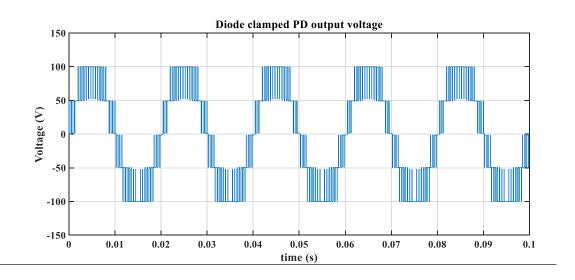

| Figure 3.22 Diode Clamped Full Bridge 5-level converter                              | 57    |

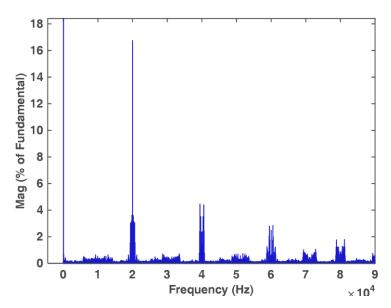

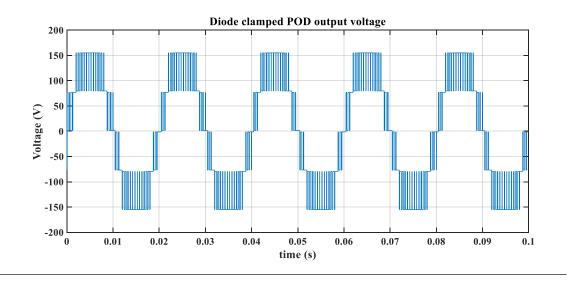

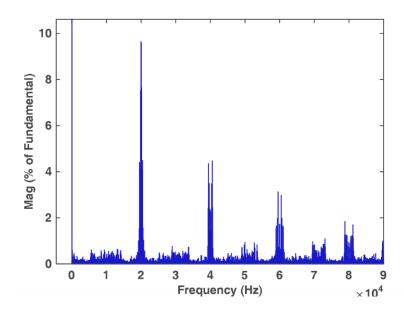

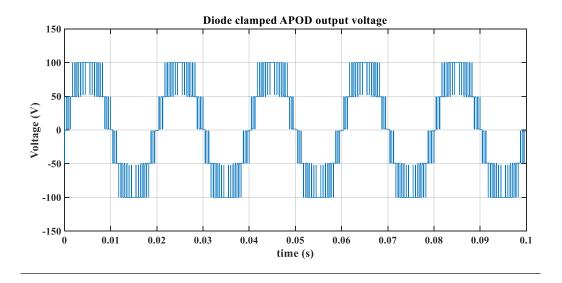

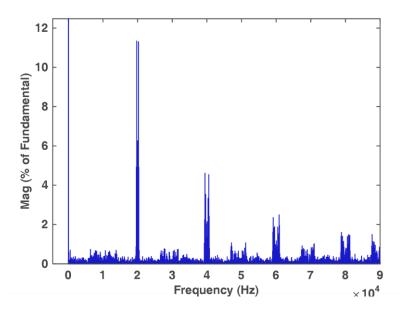

| Figure 3.23 NPC Full Bridge 5-level converter waveform and FFT                       | 58    |

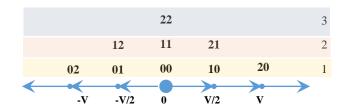

| Figure 3.24. Control region for 5-level inverter.                                    | 60    |

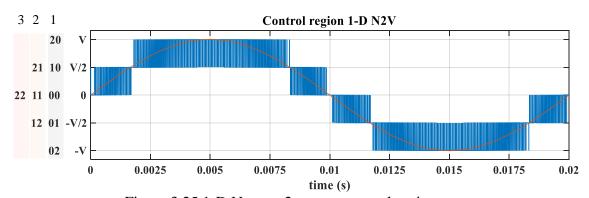

| Figure 3.25 1-D Nearest 2 vectors control regions                                    | 61    |

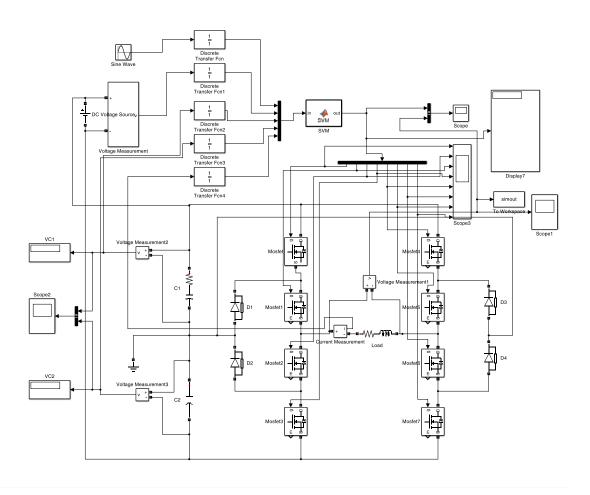

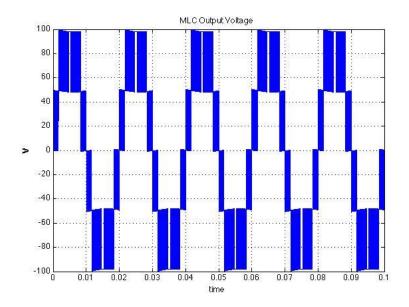

| Figure 3.26. Simulink model of the 5-level converter.                                | 63    |

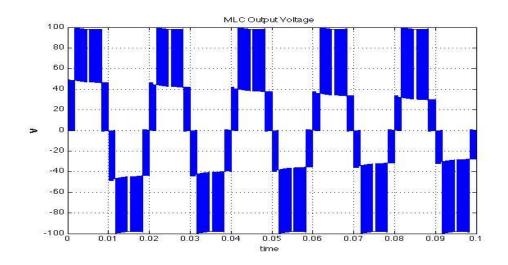

| Figure 3.27 Output voltage with no balance algorithm implemented                     | 64    |

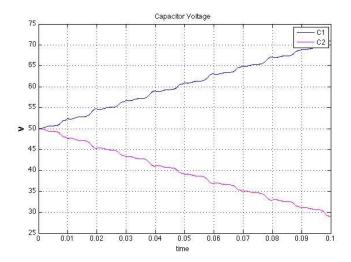

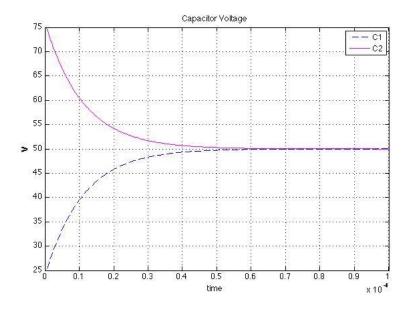

| Figure 3.28 Voltage in the DC-link capacitors with no balance algorithm implement    | ıted. |

|                                                                                      | 64    |

| Figure 3.29 Output voltage with balance algorithm implemented                        | 65    |

| Figure 3.30 Voltage in the DC-link capacitors with balance algorithm implemented     | 65    |

| Figure 4.1 Block Diagram of the system.                                              | 69    |

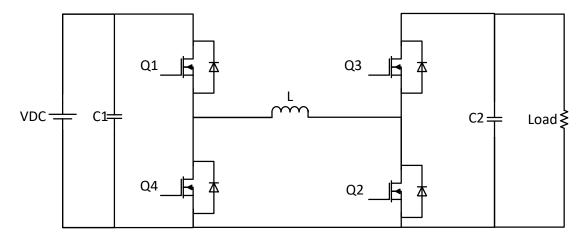

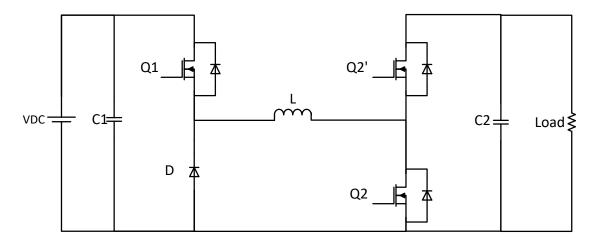

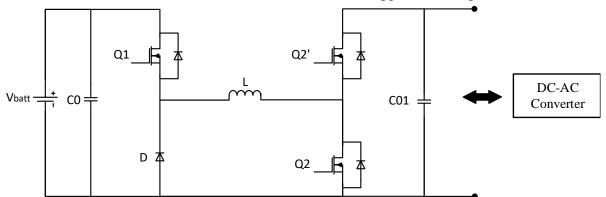

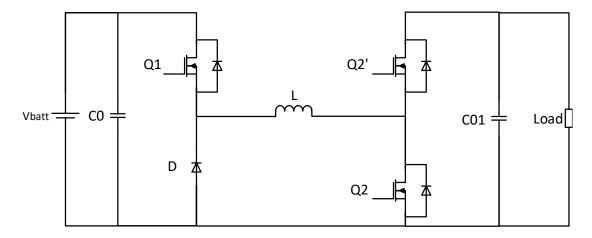

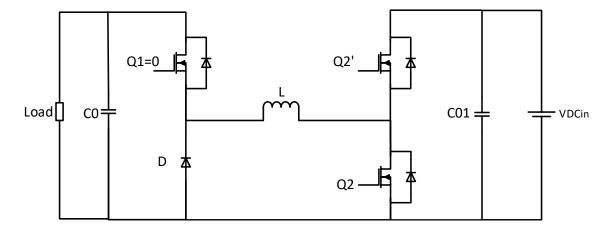

| Figure 4.2 DC-DC bidirectional converter                                             | 71    |

| Figure 4.3 DC-DC bidirectional converter                                             | 74    |

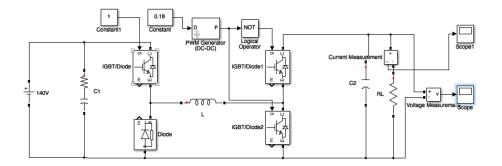

| Figure 4.4 Simulink Model Boost Buck Converter                                       | 74    |

| Figure 4.5 Boost Mode test circuit                                                   | 75    |

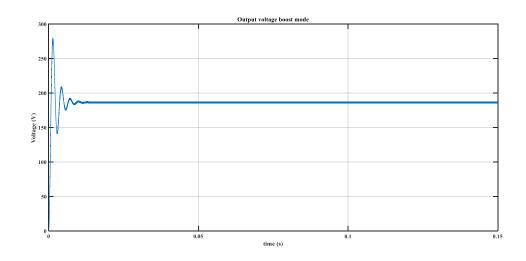

| Figure 4.6 Boost (Discharge)Mode Output voltage                                      | 75    |

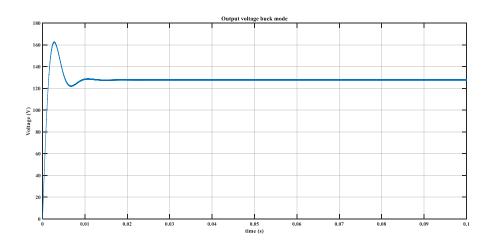

| Figure 4.7 Buck Mode test circuit                                                    | 75    |

| Figure 4.8 Buck (Charge) Mode Output                                                 | 76    |

| Figure 4.9 5-level NPC converter in full bridge topology.                            | 77    |

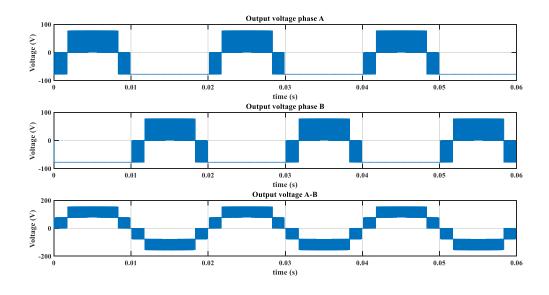

| Figure 4.10 Output voltage per phase and total                                                           | 77      |

|----------------------------------------------------------------------------------------------------------|---------|

| Figure 4.11 DC-DC and MLC converter integrated.                                                          | 79      |

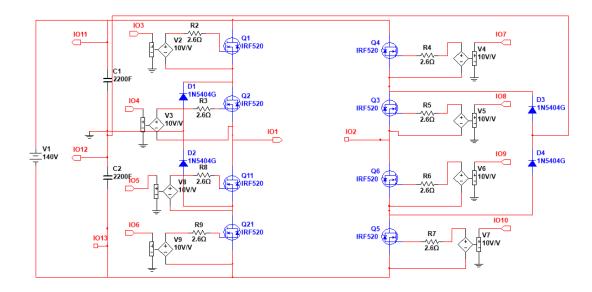

| Figure 4.12 5-level NPC single phase full bridge converter Multisim model                                | 80      |

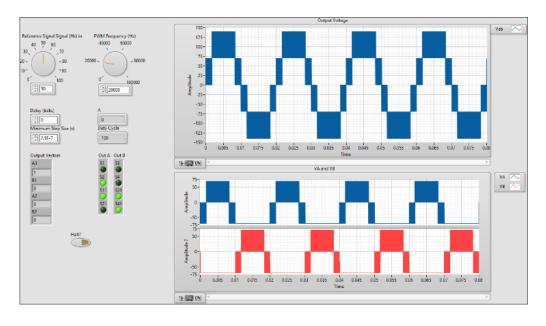

| Figure 4.13 Co-Simulation Front Panel Output Voltage and phase voltages                                  | 80      |

| Figure 4.14 CoSimulation block diagram.                                                                  | 81      |

| Figure 4.15 DC-DC and MLC integrated                                                                     | 82      |

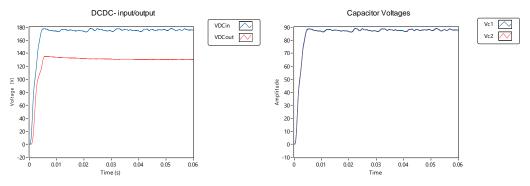

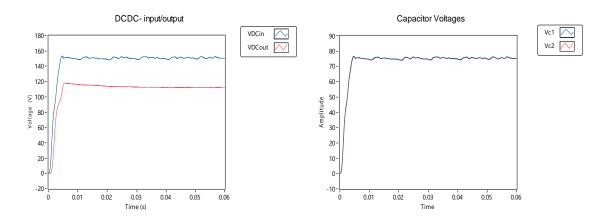

| Figure 4.16 DC-DC converter input and output waveforms. On the right graph t                             | he DC   |

| link capacitor voltages                                                                                  | 83      |

| Figure 4.17 Output Voltage and Current waveforms with V <sub>batt</sub> =144V                            | 83      |

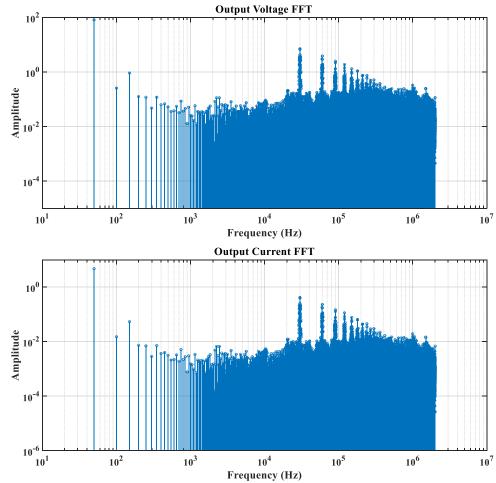

| Figure 4.18 Current and Voltage FFT in discharging mode with $V_{\text{batt}}$ =144V $V_{\text{batt}}$ = | =140V   |

|                                                                                                          | 84      |

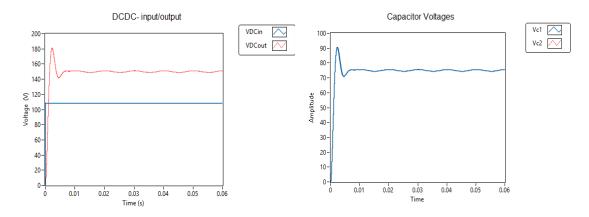

| Figure 4.19 Generator Mode DC-DC converter input and output waveforms. On the                            | e right |

| graph the DC link capacitor.                                                                             | 85      |

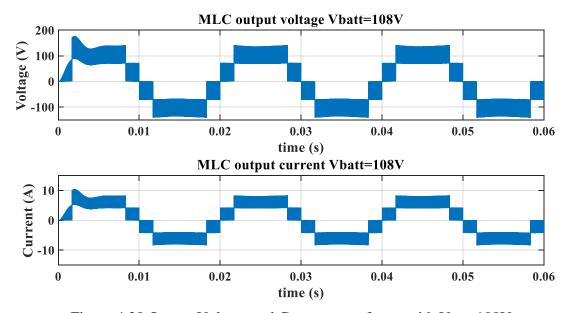

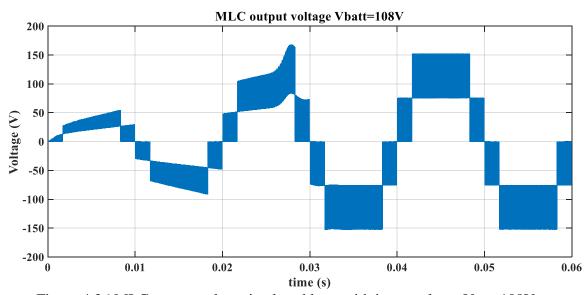

| Figure 4.20 Output Voltage and Current waveforms with V <sub>batt</sub> =108V                            | 85      |

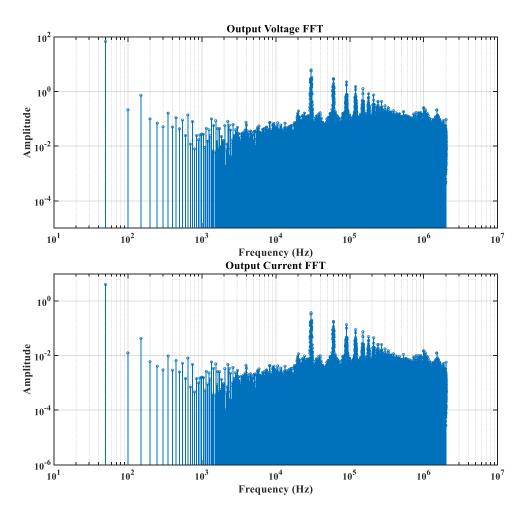

| Figure 4.21 Current and voltage FFT                                                                      | 86      |

| Figure 4.22 Charging Mode DC-DC converter input and output waveforms. On the                             | e right |

| graph the DC link capacitor voltage.                                                                     | 87      |

| Figure 4.23 Charging Mode DC-DC converter input and output waveforms. On the                             | e right |

| graph the DC link capacitor voltage.                                                                     | 87      |

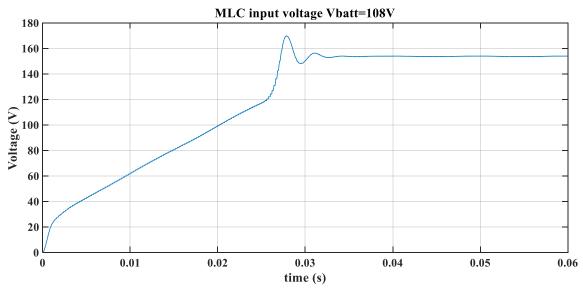

| Figure 4.24 Control loop block diagram                                                                   | 88      |

| Figure 4.25 DC-link voltage in closed loop with V <sub>batt</sub> =108V                                  | 89      |

| Figure 4.26 MLC output voltage in closed loop with input voltage $V_{\text{batt}} = 108V$                | 89      |

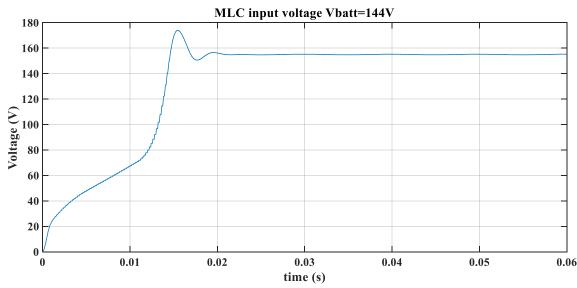

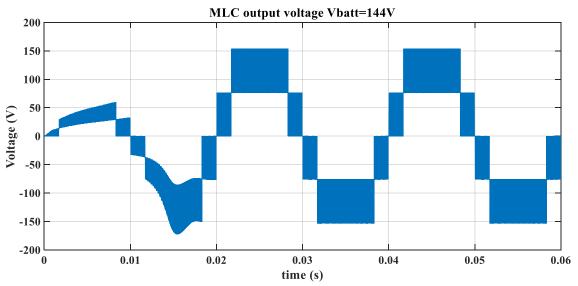

| Figure 4.27 DC-link voltage in closed loop with V <sub>batt</sub> =144V                                  | 90      |

| Figure 4.28 MLC output voltage in closed loop with input voltage $V_{\text{batt}} = 108V$                | 90      |

| Figure 5.1 5-level NPC converter in full bridge topology.                                                | 96      |

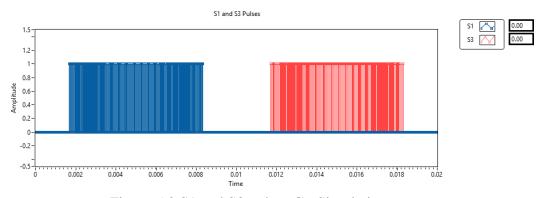

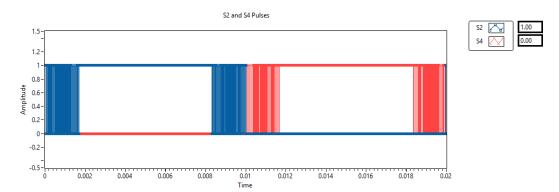

| Figure 5.2 S1 and S3 pulses Co-Simulation output.                                                        | 96      |

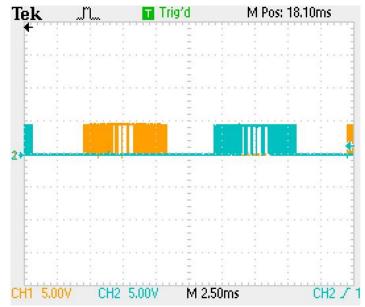

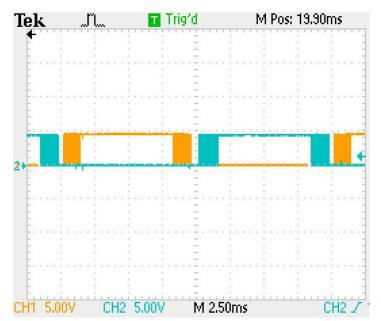

| Figure 5.3. S1 and S3 Digital Output FPGA.                                                               | 97      |

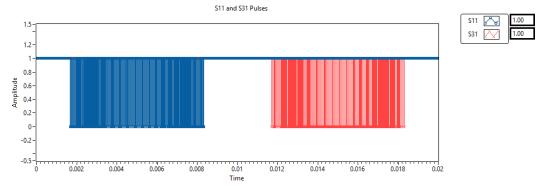

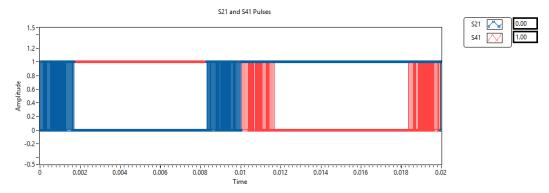

| Figure 5.4 S11 and S31 pulses Co-Simulation output.                                                      | 97      |

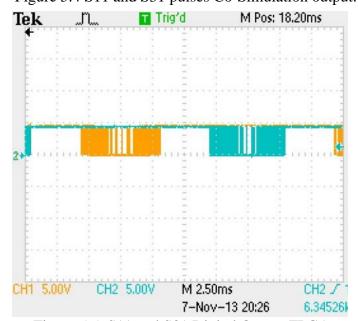

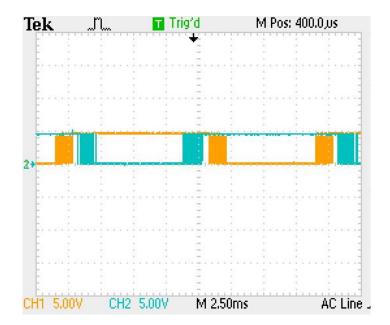

| Figure 5.5. S11 and S31 Digital Output FPGA.                                                             | 97      |

| Figure 5.6 S2 and S4 pulses Co-Simulation output.                                                        | 98      |

| Figure 5.7 S2(CH1) and S4(CH2) Digital Output FPGA.                                                      | 98      |

| Figure 5.8 S21 and S41 pulses Co-Simulation output.                                                      | 98      |

| Figure 5.9 S21(CH1) and S41(CH2) Digital Output FPGA.                                                    | 99      |

| Figure 5.10 Gate Driver Circuit interface with MOSFET.                                                   | 100     |

| Figure 5.11 Voltage transducer circuit.                                            | 101   |

|------------------------------------------------------------------------------------|-------|

| Figure 5.12 Voltage transducer characterisatic curve.                              | 102   |

| Figure 5.13 Current transducer circuit.                                            | 102   |

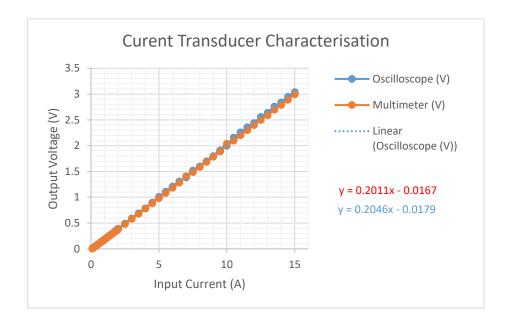

| Figure 5.14 Current transducer characteristic curve                                | 103   |

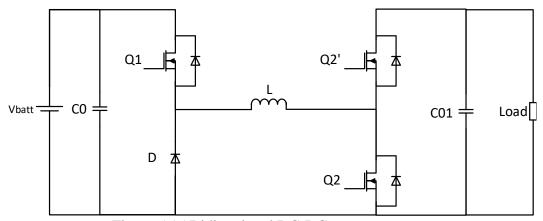

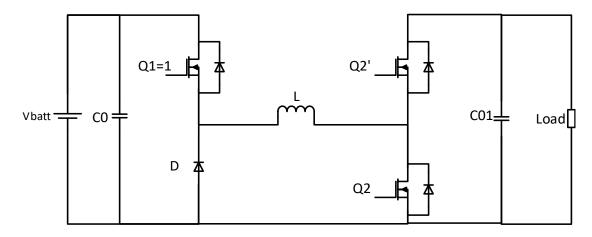

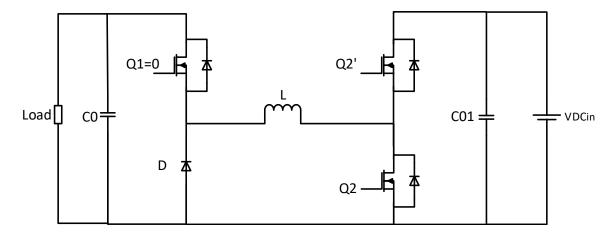

| Figure 5.15 Bidirectional DC-DC converter                                          | 104   |

| Figure 5.16. DC-DC converter PCB and FPGA.                                         | 104   |

| Figure 5.17 Boost mode test circuit                                                | 106   |

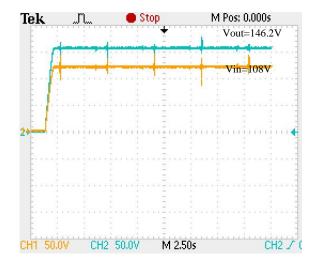

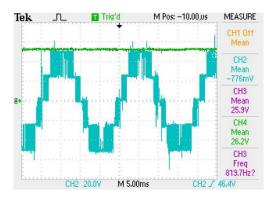

| Figure 5.18 Input and output voltages in boost mode with minimum battery voltage   | . 107 |

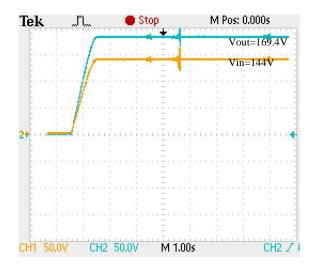

| Figure 5.19 Input and output voltages in boost mode with maximum battery voltage   | . 107 |

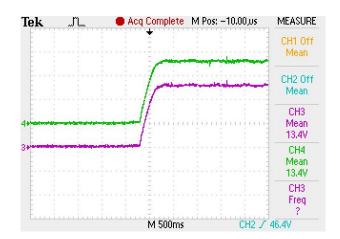

| Figure 5.20 Buck mode test circuit                                                 | 108   |

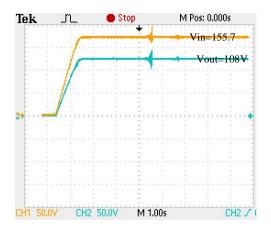

| Figure 5.21 Input and output voltages in buck mode                                 | 109   |

| Figure 5.22. 5-level diode clamped full bridge converter.                          | 109   |

| Figure 5.23 Phase A (3-level) converter circuit.                                   | 110   |

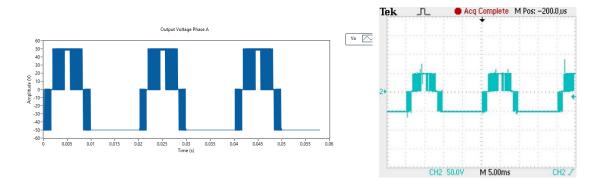

| Figure 5.24 Output voltage of phase A, Co-simulation.                              | 110   |

| Figure 5.25 Phase A output voltage tested.                                         | 110   |

| Figure 5.26 Co-simulation front panel output voltage and output voltages per phase | . 111 |

| Figure 5.27. 5-level converter output test at 50V input.                           | 111   |

| Figure 5.28 DC-link capacitor voltage balanced                                     | 111   |

| Figure 5.29 DC-DC and MLC integrated                                               | 112   |

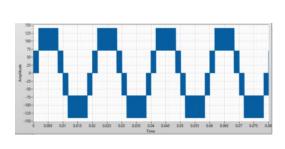

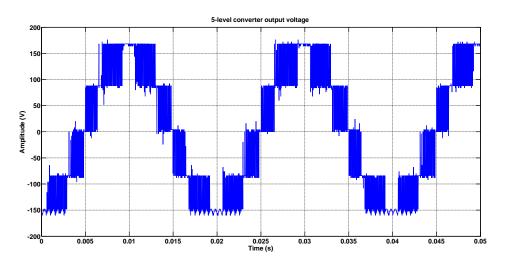

| Figure 5.30 5-level output voltage before filtering                                | 112   |

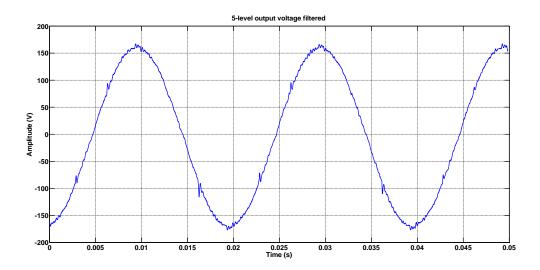

| Figure 5.31 5-level output voltage filtered                                        | 113   |

| Figure 5.32 Block diagram of the grid interface.                                   | 113   |

| Figure 5.33 PLL with sinusoidal generated in FPGA Vgen(blue) and Vref(green)       | 114   |

| Figure 5.34 PLL with grid voltage Vgrid(blue) and Vref(green)                      | 115   |

| Figure 5.35 Battery protection circuit.                                            | 116   |

| Figure 5.36 Enclosure safety box                                                   | 116   |

| Figure 6.1: Circuit diagram for the 5-level single-phase converter                 | 119   |

| Figure 6.2: Block diagram of MLC system                                            | 121   |

| Figure 6.3: MOSFET with external SiC antiparallel diode and blocking diode         | 124   |

| Figure 6.4 Converter enclosure component distribution                              | 125   |

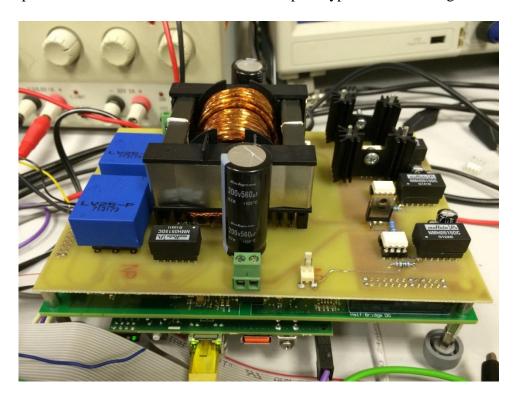

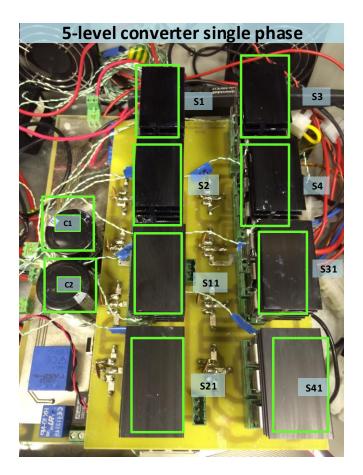

| Figure 6.5 Hardware of converter evaluated                                         | 126   |

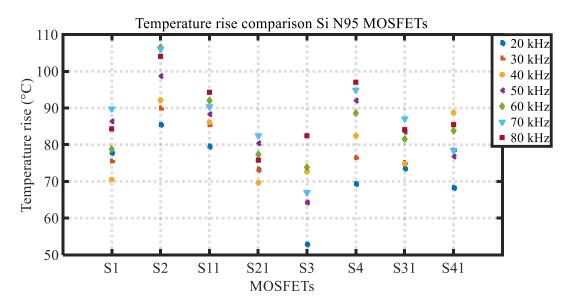

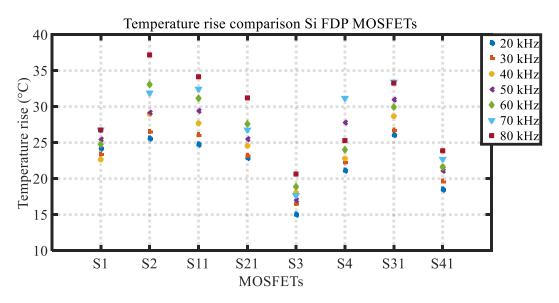

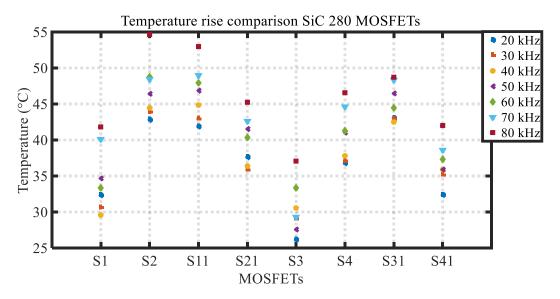

| Figure 6.6: Temperature rise of Si N95 MOSFETs in MLC                              | 127   |

| Figure 6.7: Temperature rise of Si FDP MOSFETs in MLC                              | 127   |

| Figure 6.8: Temperature rise of SiC 280 MOSFETs in MLC                             | 128   |

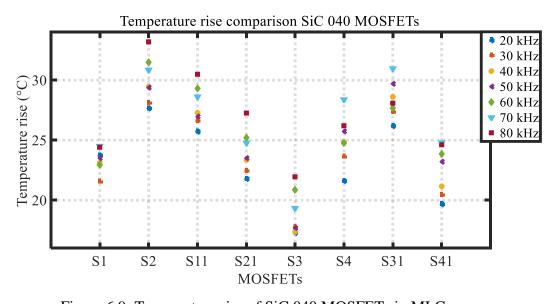

| Figure 6.9: Temperature rise of SiC 040 MOSFETs in MLC                                             | 128         |

|----------------------------------------------------------------------------------------------------|-------------|

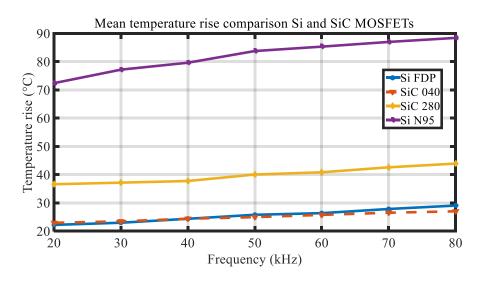

| Figure 6.10: Average temperature as a function of frequency for the Si and SiC                     | devices     |

|                                                                                                    |             |

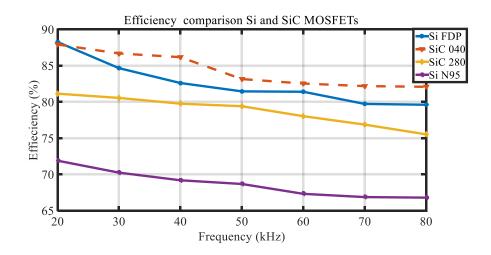

| Figure 6.11: Efficiency comparison as a function of frequency                                      |             |

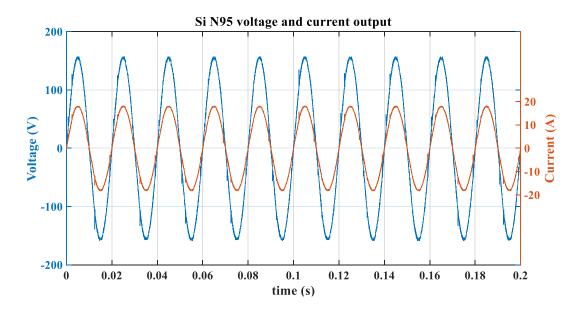

| Figure 6.12 Si N95 voltage and current waveforms                                                   |             |

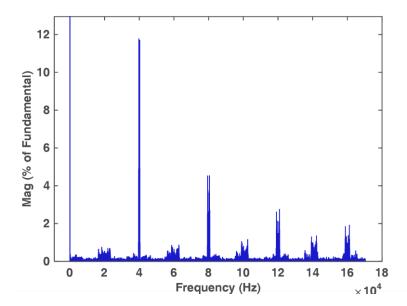

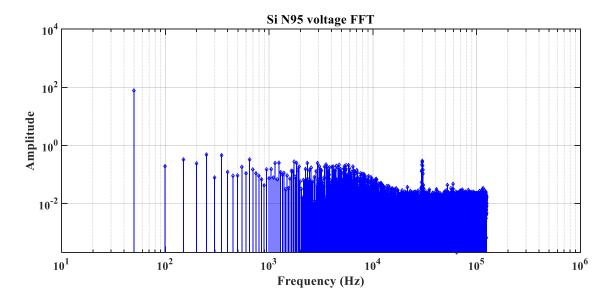

| Figure 6.13 Si N95 voltage FFT                                                                     |             |

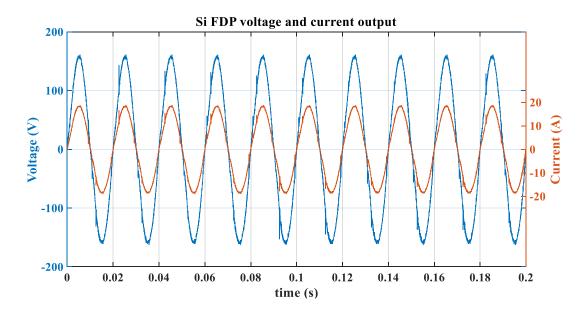

| Figure 6.14 Si FDP voltage and current waveforms                                                   |             |

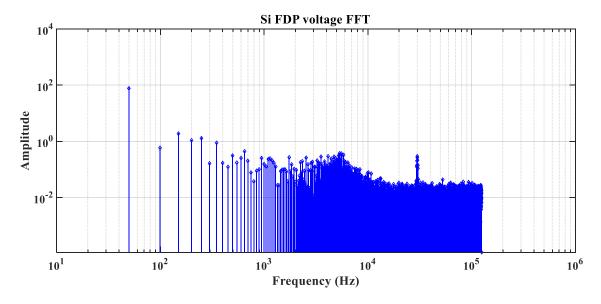

| Figure 6.15 Si FDP voltage FFT                                                                     | 132         |

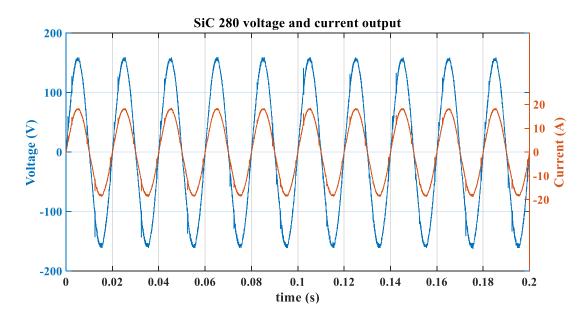

| Figure 6.16 SiC 280 voltage and current waveforms                                                  | 133         |

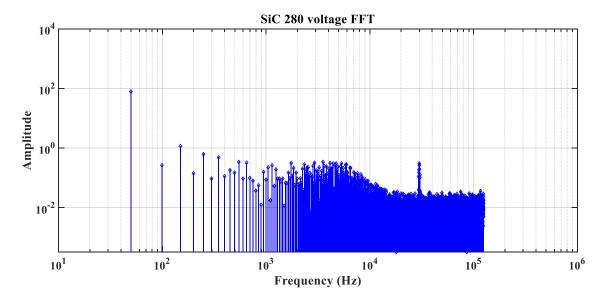

| Figure 6.17 SiC 280 voltage FFT                                                                    | 133         |

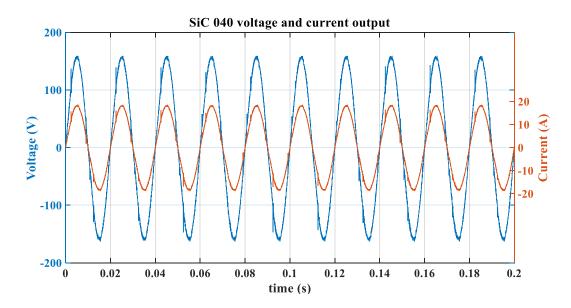

| Figure 6.18 SiC 040 voltage and current waveforms                                                  | 134         |

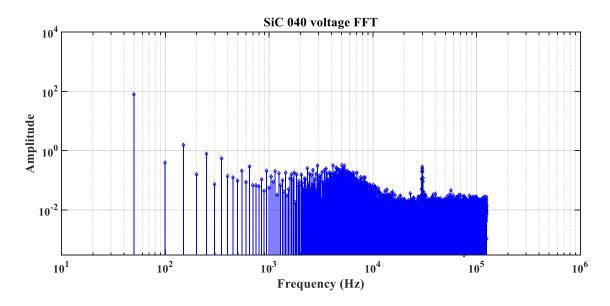

| Figure 6.19 SiC 040 voltage FFT                                                                    | 134         |

| Figure 7.1 L-filter                                                                                | 138         |

| Figure 7.2 LC-filter                                                                               | 139         |

| Figure 7.3 LCL filter                                                                              | 139         |

| Figure 7.4 MLC with LC filter                                                                      | 140         |

| Figure 7.5 R damping circuit                                                                       | 141         |

| Figure 7.6 RC damping circuit                                                                      | 141         |

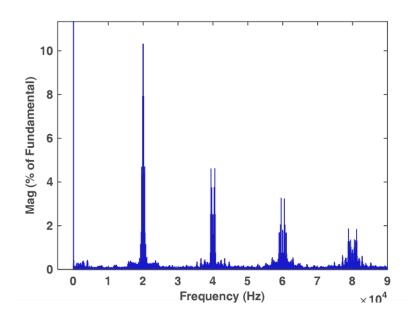

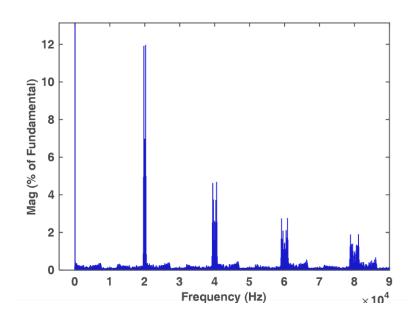

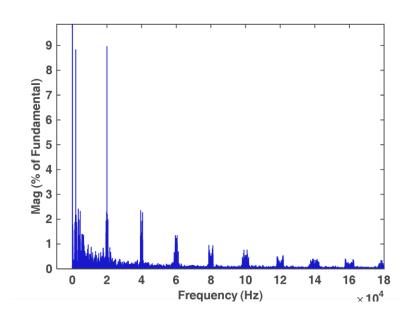

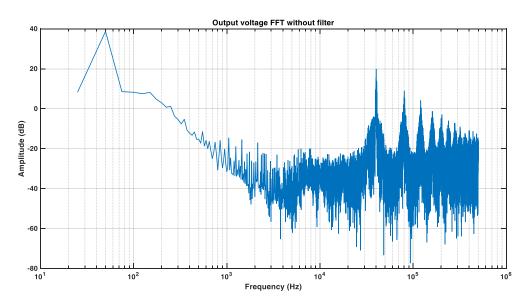

| Figure 7.7 Output voltage FFT without filter                                                       | 141         |

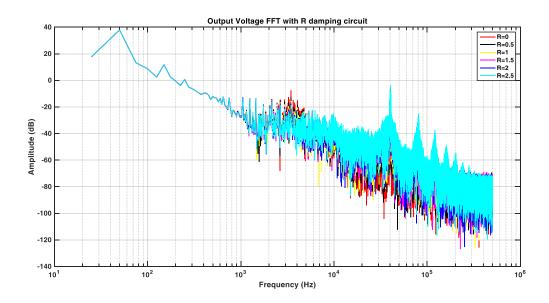

| Figure 7.8 Output voltage FFT for the R damped LCL filter with Rfa=Rfb=0Ω                          | $0.5\Omega$ |

| $1\Omega, 1.5\Omega, 2\Omega$ and $2.5\Omega$ .                                                    | 142         |

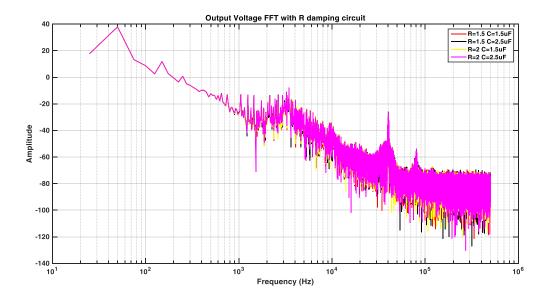

| Figure 7.9 Output voltage FFT for the RC damped LCL filter with R=1.5 $\Omega$ C=                  | =1.5µF      |

| $R{=}1.5\Omega \; C{=}2.5\mu F,  R{=}2\Omega \; C{=}1.5\mu F,  R{=}2\Omega \; C{=}2.5\mu F, \dots$ | 142         |

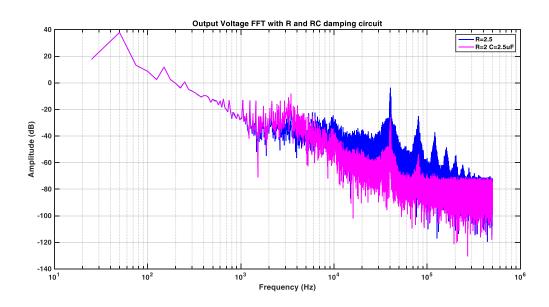

| Figure 7.10 Output voltage FFT with $R=2\Omega$ $C=2.5\mu F$ and $R=2.5\Omega$                     | 143         |

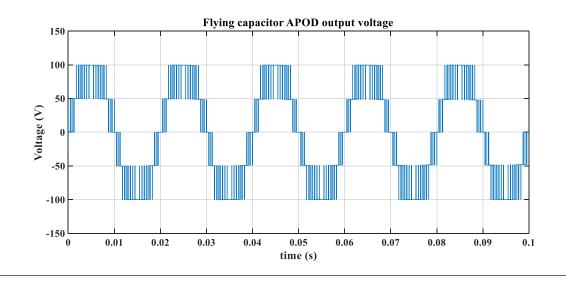

| Figure 7.11 MLC with LC filter                                                                     | 146         |

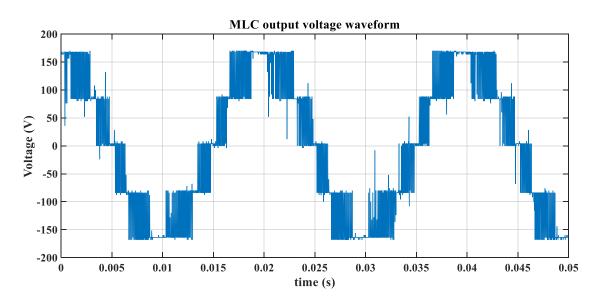

| Figure 7.12 Output voltage waveform                                                                | 146         |

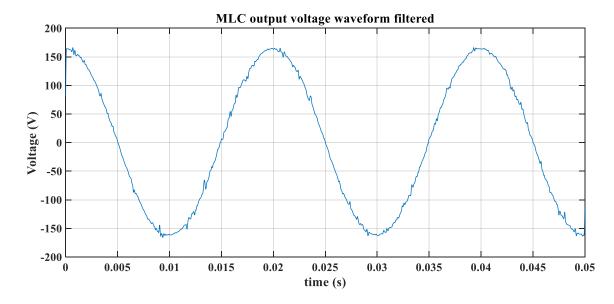

| Figure 7.13 Filtered output voltage waveform                                                       | 147         |

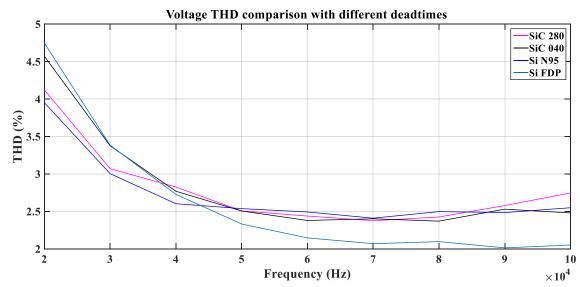

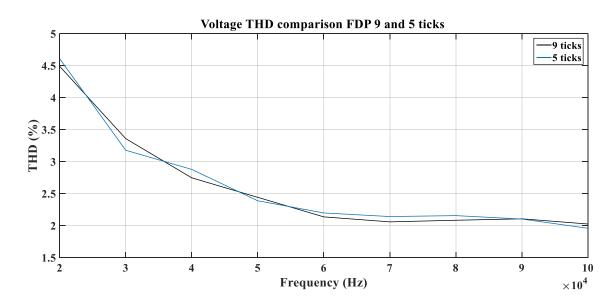

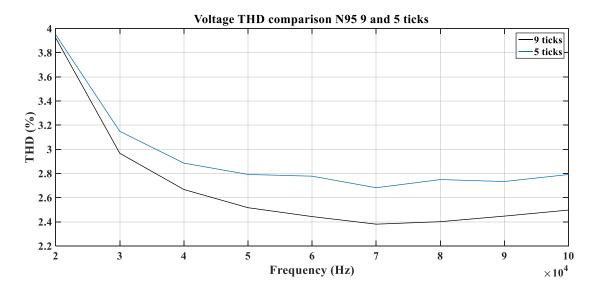

| Figure 7.14 THD comparison with different dead time.                                               | 149         |

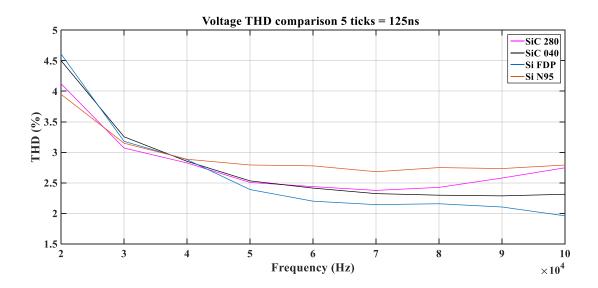

| Figure 7.15 THD comparison with 5 ticks                                                            | 150         |

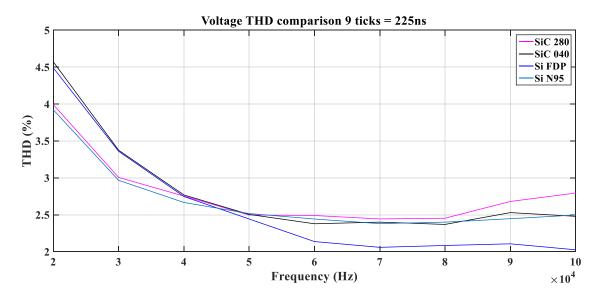

| Figure 7.16 THD comparison with 9 ticks                                                            | 150         |

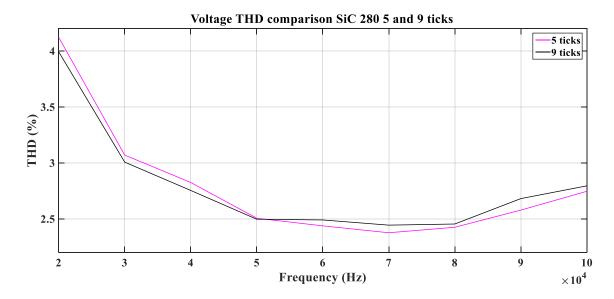

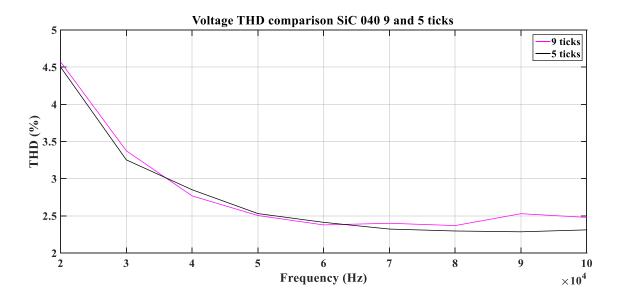

| Figure 7.17 SiC 280 THD comparison                                                                 | 151         |

| Figure 7.18 SiC 040 THD comparison                                                                 | 152         |

| Figure 7.19 Si FDP THD comparison                                                                  | 152         |

| List of Tables Table 2.1 Switch states 3-level Neutral-Point Clamped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 7.20 Si N95 THD comparison                                                  | 153      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------|

| Table 2.1 Switch states 3-level Neutral-Point Clamped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |          |

| Table 2.2 Switch states 5-level Neutral-Point Clamped Full Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | List of Tables                                                                     |          |

| Table 2.3 Switch states 5-level Neutral-Point Clamped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 2.1 Switch states 3-level Neutral-Point Clamped                              | 9        |

| Table 2.4. Switching states and output voltage 3L-HB-FC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 2.2 Switch states 5-level Neutral-Point Clamped Full Bridge                  | 10       |

| Table 2.5 Switch states 5-level Flying Capacitor Full Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 2.3 Switch states 5-level Neutral-Point Clamped                              | 13       |

| Table 2.6. Switch states 5-level Flying Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 2.4. Switching states and output voltage 3L-HB-FC                            | 16       |

| Table 2.7 CHB switching states and output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 2.5 Switch states 5-level Flying Capacitor Full Bridge                       | 18       |

| Table 2.8. Comparison of components and levels of the NPC and FC topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 2.6. Switch states 5-level Flying Capacitor                                  | 20       |

| Table 3.1. THD comparison for Different PWM techniques and topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 2.7 CHB switching states and output voltage                                  | 23       |

| Table 3.2. Switching states for the 5-level full bridge NPC (5L-FB-NPC) converter in Figure 3.22. 60  Table 3.3. States Sequence based on reference signal "a" 61  Table 3.4. Voltage effect in the DC link capacitors for the 5-level converter 62  Table 4.1 System specification 69  Table 5.1 Test conditions 106  Table 5.2 Specifications buck mode 108  Table 6.1 Switching devices for performance evaluation in 5-level single phase converter 123  Table 6.2 Experimental evaluation test conditions 123  Table 6.3. Characteristics of blocking diode and antiparallel diode 124  Table 7.1 Switching times of the devices evaluated 147 | Table 2.8. Comparison of components and levels of the NPC and FC topologies        | 25       |

| Figure 3.22. 60 Table 3.3. States Sequence based on reference signal "a" 61 Table 3.4. Voltage effect in the DC link capacitors for the 5-level converter 62 Table 4.1 System specification 69 Table 5.1 Test conditions 106 Table 5.2 Specifications buck mode 108 Table 6.1 Switching devices for performance evaluation in 5-level single phase converter 123 Table 6.2 Experimental evaluation test conditions 123 Table 6.3: Characteristics of blocking diode and antiparallel diode 124 Table 6.4 Harmonics voltage FFT magnitude 135 Table 7.1 Switching times of the devices evaluated 147                                                 | Table 3.1. THD comparison for Different PWM techniques and topologies              | 52       |

| Table 3.3. States Sequence based on reference signal "a"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 3.2. Switching states for the 5-level full bridge NPC (5L-FB-NPC) converge   | erter in |

| Table 3.4. Voltage effect in the DC link capacitors for the 5-level converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 3.22.                                                                       | 60       |

| Table 4.1 System specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 3.3. States Sequence based on reference signal "a"                           | 61       |

| Table 5.1 Test conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Table 3.4. Voltage effect in the DC link capacitors for the 5-level converter      | 62       |

| Table 5.2 Specifications buck mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 4.1 System specification                                                     | 69       |

| Table 6.1 Switching devices for performance evaluation in 5-level single phase converted 123  Table 6.2 Experimental evaluation test conditions 123  Table 6.3: Characteristics of blocking diode and antiparallel diode 124  Table 6.4 Harmonics voltage FFT magnitude 135  Table 7.1 Switching times of the devices evaluated 147                                                                                                                                                                                                                                                                                                                 | Table 5.1 Test conditions                                                          | 106      |

| Table 6.2 Experimental evaluation test conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 5.2 Specifications buck mode                                                 | 108      |

| Table 6.2 Experimental evaluation test conditions123Table 6.3: Characteristics of blocking diode and antiparallel diode124Table 6.4 Harmonics voltage FFT magnitude135Table 7.1 Switching times of the devices evaluated147                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 6.1 Switching devices for performance evaluation in 5-level single phase con | nvertei  |

| Table 6.3: Characteristics of blocking diode and antiparallel diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    | 123      |

| Table 6.4 Harmonics voltage FFT magnitude                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Table 6.2 Experimental evaluation test conditions                                  | 123      |

| Table 7.1 Switching times of the devices evaluated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 6.3: Characteristics of blocking diode and antiparallel diode                | 124      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 6.4 Harmonics voltage FFT magnitude                                          | 135      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 7.1 Switching times of the devices evaluated                                 | 147      |

| Table 7.2 Dead time in ns and ticks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 7.2 Dead time in ns and ticks                                                | 148      |

### Chapter 1 Introduction

The impact created by the advancement of electronic systems has had, and is still having, an unprecedented impact on society. Electronics has not only created an industry in its own right, but has had a major impact on our quality of life. This impact can be felt everywhere and in a variety of market sectors including: i) electric transportation (trains, trams and now electric vehicles (EV)); ii) medical and health (MRI scanners to automated dosing); iii) information and communications technologies (computing and the internet); iv) automation of industry (improved industrial process and manufacturing) and v) consumer electronics and entertainment (television, game consoles). All of these are supported by networks of manufacturers and taken together this has led to enormous wealth creation.

Energy management is still a major concern with many actors including governments, energy suppliers, equipment manufacturers and users wanting to reduce wastage. Most electronic systems require some form electricity conditioning circuit to generate the correct voltage levels for operation. Power electronic conversion is now widely accepted as the best way of achieving this translation at high-efficiency and now is one of the most active research areas encompassing circuit topologies, devices and control.

The increasing concern surrounding the use of fossil fuels has motivated the use of electrical alternatives demanding efficiency and reliability. An example of this is the growing demand of EVs, in 2015 the UK government reiterated the promise to make sure that nearly all cars and vans are zero emission vehicles by 2050 [1-1]. One recent publication [1-2] shows that the number of electric vehicles registered during the second quarter (Q2) 2016 increased in 49% compared to 2015 and 253% compared to 2014 and it also details a plan introduced by the UK government to help to buy an EV with grant plans for up to £8,000.

EVs require a rechargeable battery and it is predicted that these batteries will reach their end of life within 5 to 10 years of standard driving as capacity reduction through ageing and wear out will make them no longer viable for vehicle applications. However, the EV battery will retain some useful capability and so it is predicted that 2<sup>nd</sup> life applications will emerge for them before their ultimate end-of-life and recycling. With the predicted

increased in the numbers of EVs on the road, the battery second life can help to reduce the cost of applications such as residential storage for a solar panel system.

There is presently a transition occurring in the energy generation industry where countries such as the UK are phasing out older fossil fuel power stations and replacing them with greener renewable energy supplies including both wind and solar. This transition presents many challenges and opportunities for power electronic energy conversion and energy storage systems, which are required to interface the renewable energy generators to the grid and provide grid support to maintain correct voltage levels and frequency. These power converters not only have to be efficient but they also have to produce a good power quality low distortion waveforms.

The previously described new and emerging applications are supported by significant advances in electronic technologies including semiconductor devices, power electronic converter topologies and digital control. High power converters require the use of electronic devices capable of withstanding high voltage and current stresses and this has led to the development of multilevel converters (MLC) that conveniently divide a high voltage into lower voltage levels suitable for power devices. By their virtue, these multiple levels introduce further quantisation steps in the output waveform, which significantly lower harmonic distortion and improve power quality when compared to conventional 2-level converters. Numerous MLC topologies have been studied with different characteristics that make them more appropriate for certain applications. Some MLC use separate DC voltage sources while others split a single DC voltage into several levels using capacitor dividers and diodes and require elaborated control algorithms to ensure waveform cleanliness by maintaining the capacitor voltage balanced.

#### 1.1 Application and Motivation

This thesis describes the development of a 2<sup>nd</sup> life battery powered single-phase multilevel converter based power supply for operating hand tools and lighting on construction sites. A Neutral Point Clamped (NPC) multilevel converter was chosen as it represented the best option for this application since, not only it is the most studied topology in recent years, but it provides good performance in terms of harmonic reduction. A two stage conversion process was used where the multilevel converter provided a high power factor AC-DC interface and a buck-boost stage was used for

battery voltage conversion. Considering the application, the main focus of the research was:

- Control In the MLC the voltage balancing of the DC-link capacitors and the output voltage. The DC-DC control to balance the DC-link and operation in both modes, charging and discharging.

- Efficiency The efficiency improvement as a result of control methods, thermal management or new trends in devices.

- Emerging power device technology The use of emerging wide band gap semiconductor devices in power electronics in MLC and DC-DC.

- Filtering With an incremented number of levels on the MLC the reduction of harmonics and better voltage waveforms can be achieved which results in a reduction of filter size.

- Co-simulation The use of modern design tools for system simulation and controller design within a single development environment.

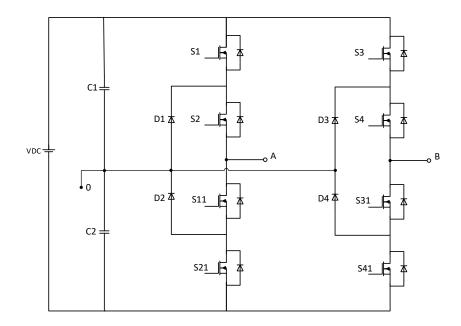

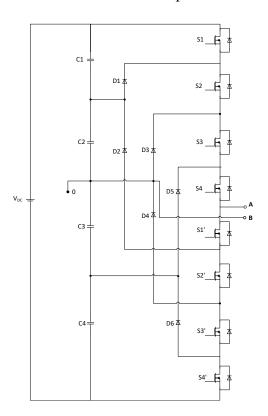

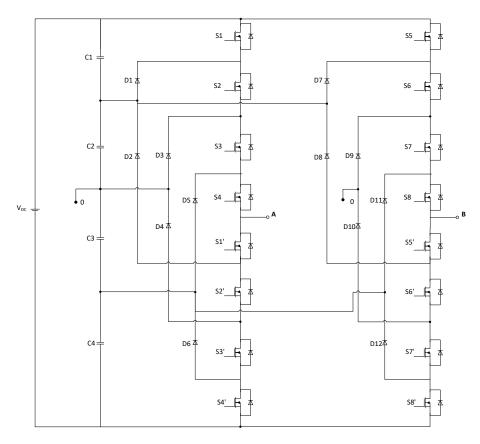

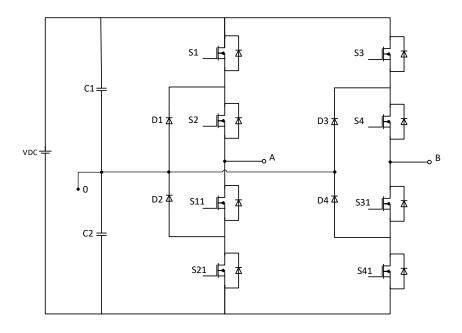

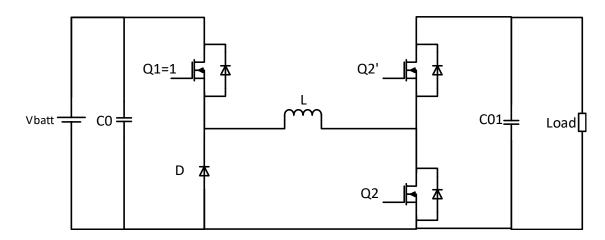

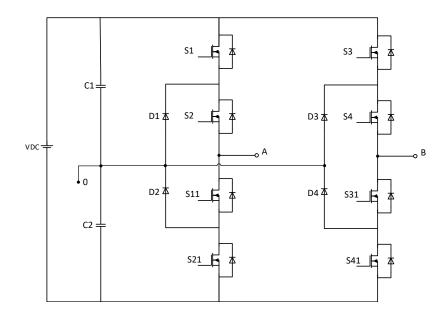

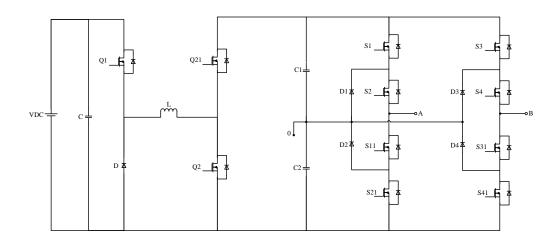

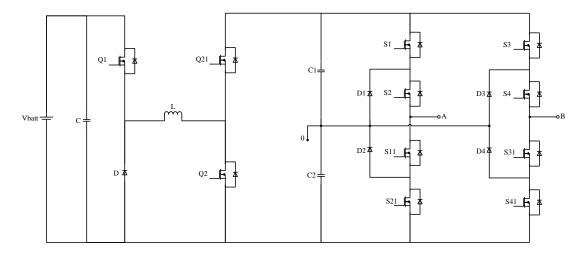

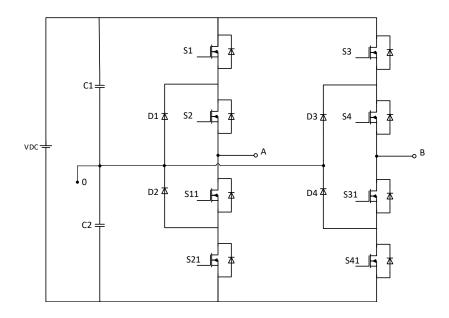

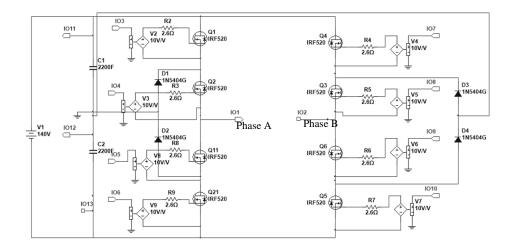

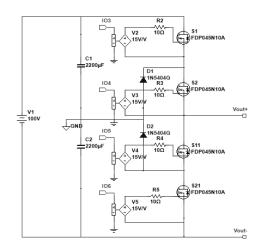

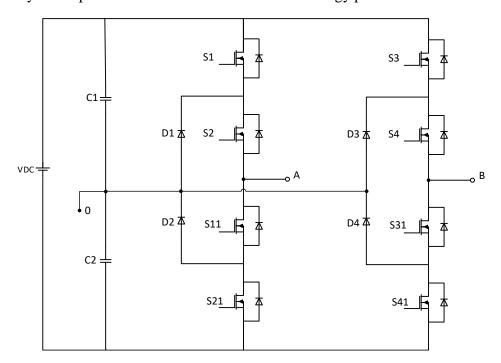

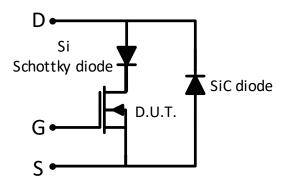

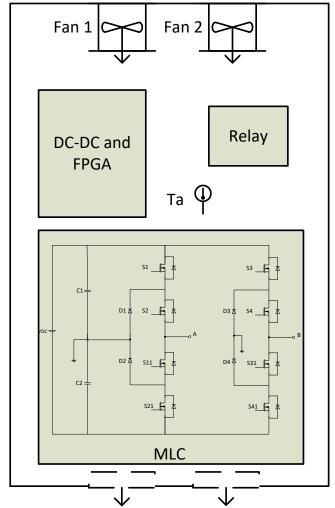

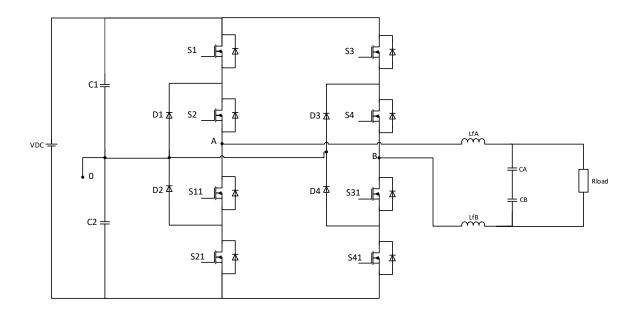

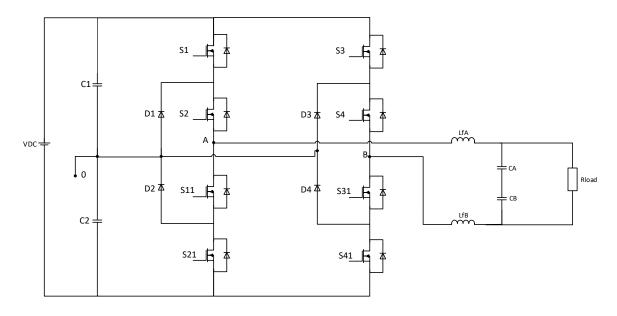

A Five Level, Neutral Point Clamped Multilevel converter (5L-NPC-MLC) shown in Figure 1.1 was designed, constructed and experimentally validated. The National Instruments Multisim and LabVIEW environment was selected as the co-simulation platform and the control was implemented using an FPGA to provide fast and reliable control. The use of wide bandgap devices in the MLC proving the effects on thermal and efficiency improvements compared to those of the Si counterparts. Moreover the effect of WBG on harmonic distortion is also addressed.

Figure 1.1: Circuit diagram for the 5-level single-phase converter

#### 1.2 Thesis outline

This section briefly outlines the contents of the thesis chapter by chapter.

A review of prior research is presented in Chapter 2, which incorporates a literature review. This chapter describes formative work by introducing the main multilevel converter topologies, circuit operation, typical waveforms and control requirements including modulation techniques.

Modulation techniques are covered in further detail in Chapter 3. A typical multilevel converter consists of multiple switching devices (i.e. MOSFETs or IGBTs) connected to multiple voltage sources. The conduction states of the switching devices are controlled by a modulator whose role is to ensure: i) the required output is generated, ii) prevent damage occurring via cross-conduction (i.e. shoot-through) and for some specific topologies iii) to manage voltage levels on batteries or capacitors. This chapter reviews sinusoidal and space-vector modulation techniques and presents the Nearest 2 Vectors (N2V) method implemented in the hardware platform.

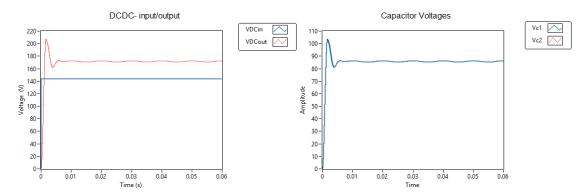

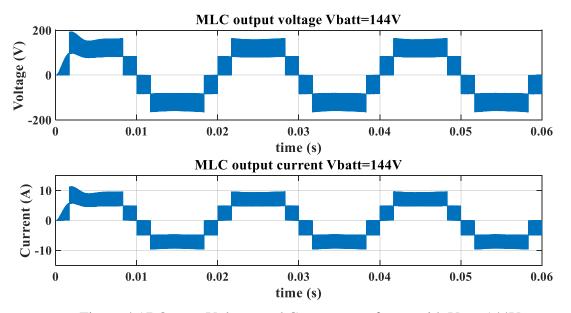

Chapter 4 describes the detailed design of the 5-level NPC multilevel converter (MLC) hardware platform used for experimental validation in this study. Detailed simulation

results of the subsystem in Simulink and then the integration of both sub-systems (DC-DC and MLC) in LabVIEW Co-simulation with Multisim.

Chapter 5 describes the design, implementation and experimental validation of the prototype hardware. The basic operating concepts of bidirectional converter are discussed alongside experimental results. The FPGA controller is described and the design power electronic converter stages are given. Throughout this chapter, LabVIEW was used as a co-simulation development system to expedite the design by allowing the FPGA based control system to be developed within a simulation environment and then downloaded onto the hardware platform. Experimental results demonstrating the performance of the system are also given.

Chapter 6 presents an experimental study on the performance of SiC MOSFETs and SiC anti-parallel diodes operating within a 5-level NPC MLC. The thermal performance of the MLC operating with SiC devices is compared with that of Si devices by measuring the temperature rise of the devices and the total efficiency of the converter. A description of the complete system and converter is presented and the semiconductor devices used in the evaluation are described.

Expanding on the previous section, Chapter 7 investigates the impact of SiC devices on the output waveform total harmonic distortion. This chapter initially review filter design and damping circuit through simulation and discusses norms and standards for power quality. A comparison with the THD performance against frequency and dead-time is given for the same SiC devices used in the previous chapter.

Conclusions and Future work are discussed in Chapter 8.

#### 1.3 References

- [1-1] A. Jones "UK government pledges bold ambition for electric cars" DfT press notice, Dec. 2015 [Online]. Available: https://www.gov.uk/government/news/uk-government-pledges-bold-ambition-for-electric-cars

- [1-2] L. Butcher. "Electric Vehicles and infrastructure" Briefing Paper number CBP07480. House of Commons library. Dec. 2016 [Online]. Available: http://researchbriefings.files.parliament.uk/documents/CBP-7480/CBP-7480.pdf

## Chapter 2 – Background

#### 2.1 – Introduction

The principal function of a converter is to transform energy in a form of direct current (DC) or alternating current (AC) to either the same form or to the other i.e. DC to DC, AC to AC or DC to AC. Converters can also be operated in bidirectional mode, permitting the reduction of system components when used in certain applications such as starter-generator drive systems.

The use of power electronic semiconductors in such converters, alongside filtering components (inductors and capacitors), allows efficient conversion of electrical energy. For DC-DC conversion, the input voltage may be stepped up or down both with or without the use of a transformer. For the case of the DC to AC, a suitable sequence and ON time of the switching components is required to form the required output voltage.

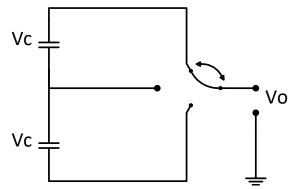

Figure 2.1 Functional diagram of a DC to AC converter

As shown in Figure 2.1 the conversion from DC to AC requires the voltage taken from the DC-link capacitors (Vc) being switched to the output (Vo) and periodically reversed at the output to provide AC and a very rough approximation to a sinusoidal voltage output. By using more switching elements, an appropriate switching sequencing, and clamping or balancing elements, the approximation to the sinusoidal output signal can be much improved and further enhanced by adding more steps (or levels) to the output to form a staircase waveform. The multilevel converter (MLC) was first introduced in [2-1] and the different topologies are investigated and explained in the following sections.

Although the increased number of levels significantly improves the quality of the waveform, it has a negative outcome in terms of the control of the voltage on the DC-link and the sequencing of the switches. Nowadays the use of Field Programmable Gate Array

(FPGA) to control the converters allows a profusion of levels due to: the availability of pulse width modulation (PWM) configurable cells; the reduction in cost; and ease of programming. An implementation of an algorithm proposed in [2-2], [2-3] is programmed and tested for the selected topology of MLC, as will be discussed later.

#### 2.2 – Multi-Level Converters

Having an increased number of switching elements compared to the 2-level converter and clamping or balancing elements to generate the n-level staircase different topologies of multi-level converter are reviewed in [2-4] [2-5] and [2-6].

In recent years, there has been an increasing amount of literature on MLC. The most known and studied are concerned with:

- Neutral-Point-Clamped Converter (NPC)

- Flying Capacitor Converter (FCC)

- H bridge Converter (HBC)

The first topology of a 3-level converter was introduced in 1980 [2-1], the Neutral-Point-Clamped (NPC) converter, this converter uses diodes to clamp the voltage to form the 3-level output. The second topology FCC was introduced in 1992 by Maynard Foch, this uses capacitors to divide the voltage to form the n-level output. These two converters use a single DC source so the introduction of new topologies using separate DC sources are described in [2-7] mostly derived from the H-bridge topology and a combination with the previous basic topologies.

The conversion from DC to AC using MLCs allows generating a low distortion output and the advantages of reduced device ratings (voltage and current) for the components. The single-phase converter can be implemented in half-bridge (HB) or full-bridge (FB) for both topologies, [2-8] provides an example giving the analysis and design of the single phase system as it is implemented. Interfacing with the grid for applications on renewable energy sources feeding the network and vehicle to grid (V2G) is studied in [2-9] [2-10].

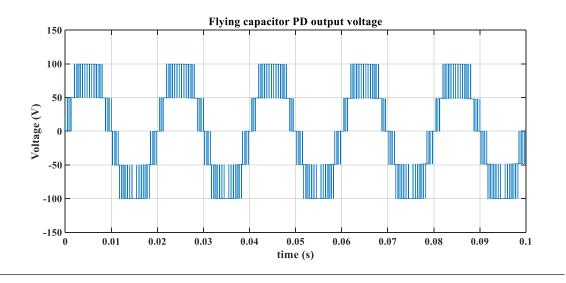

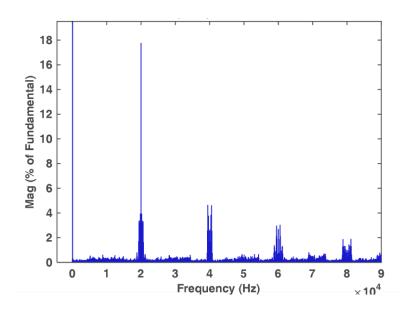

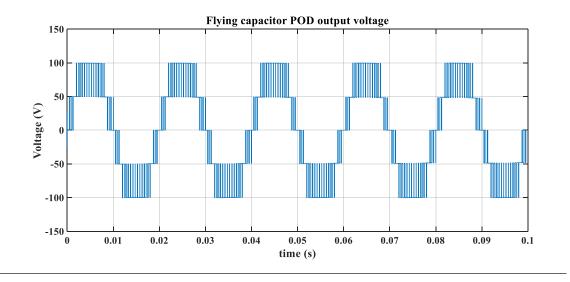

In the following subsections the 3 main topologies are introduced, with a description of each topology and the typical output waveforms. The waveforms were obtained from an open-loop simulation under no-load conditions for illustration. The switching frequency used is 5 kHz so the switching events are visible and the input DC voltage is 200V. At

the end of this section, a comparison of the topologies introduced will be available in terms of number of levels, output voltage and number of clamping elements.

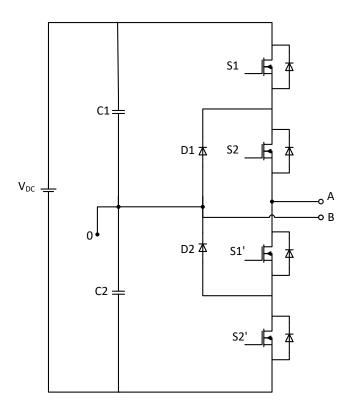

#### 2.2.1 Neutral-Point Clamped Converter

The neutral point clamped converter takes its name from the operation principle of clamping the voltage of each level using a diode. Taking only one phase from the topology proposed in [2-8] the 3-Level Half-Bridge Neutral-Point Clamped (3L-HB-NPC) topology is formed, the topology and waveform are shown in Figure 2.2 and Figure 2.3. The DC-link is composed of the capacitors  $C_1$  and  $C_2$  where the voltage is divided in 2 to create the level V/2 and -V/2 and the diodes D1 and D2 to clamp the voltage. The antiparallel diodes shown in each switch (S1-S2) and (S1'-S2'). The MOSFETs in this case allow the converter to work in regeneration mode, enabling the converter to work as an AC to DC converter.

Figure 2.2 Neutral-Point Clamped 3-levels single phase

The output of the converter is taken from nodes A and B, where node B is the neutral point between the 2 capacitors, and the switches are controlled in such a way to ensure each capacitor is charged at V/2 so the Voltage in AB can be -V/2, 0, and V/2, these makes the 3 levels. The states of the switches  $(S_1,S_2)$  and the complementary switches

(S<sub>1</sub>', S<sub>2</sub>') are shown in Table 2.1 where '1' means the switch is ON and '0' indicating the switch state is OFF.

| Vout   | S <sub>1</sub> | S <sub>2</sub> | S <sub>1</sub> ' | S2' |

|--------|----------------|----------------|------------------|-----|

| Vdc/2  | 1              | 1              | 0                | 0   |

| 0      | 0              | 1              | 1                | 0   |

| -Vdc/2 | 0              | 0              | 1                | 1   |

Table 2.1 Switch states 3-level Neutral-Point Clamped

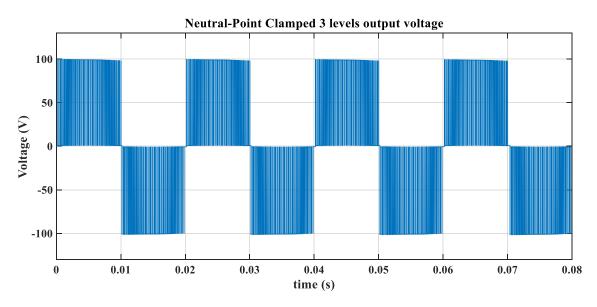

Figure 2.3 NPC 3-levels output waveform

The main advantages of this topology are the lower harmonic content of the output as the number of levels increase, reducing the size of the filter components, and also the control is easy to implement. The main disadvantage of this topology is the number of clamping diodes when the number of levels is high.

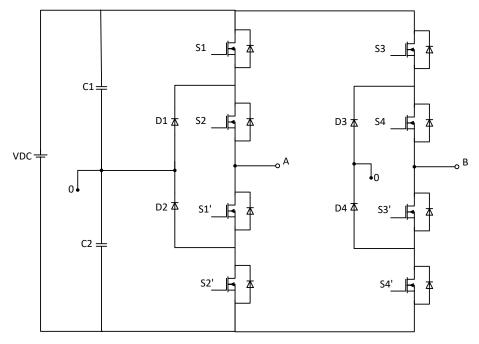

There are different implementations of the NPC topology reviewed in [2-11], for a single phase system, an additional leg or phase can be added to the topology as shown in Figure 2.4 making a 5-Levels Full-Bridge NPC (5L-FB-NPC) topology.

Figure 2.4 Neutral-Point Clamped 5-levels full bridge single phase

The advantage of this topology is the increased number of output levels, and these being V, V/2, 0, -V/2 and -V with a single DC source. The switching states are shown in Table 2.2

| Vout   | S <sub>1</sub> | S <sub>2</sub> | S <sub>1</sub> ' | S <sub>2</sub> ' | S <sub>3</sub> | S <sub>4</sub> | S <sub>3</sub> ' | S <sub>4</sub> ' |

|--------|----------------|----------------|------------------|------------------|----------------|----------------|------------------|------------------|

| Vdc    | 1              | 1              | 0                | 0                | 0              | 0              | 1                | 1                |

| Vdc/2  | 0              | 1              | 1                | 0                | 0              | 0              | 1                | 1                |

| 0      | 0              | 0              | 1                | 1                | 0              | 0              | 1                | 1                |

| -Vdc/2 | 0              | 0              | 1                | 1                | 0              | 1              | 1                | 0                |

| -Vdc   | 0              | 0              | 1                | 1                | 1              | 1              | 0                | 0                |

Table 2.2 Switch states 5-level Neutral-Point Clamped Full Bridge

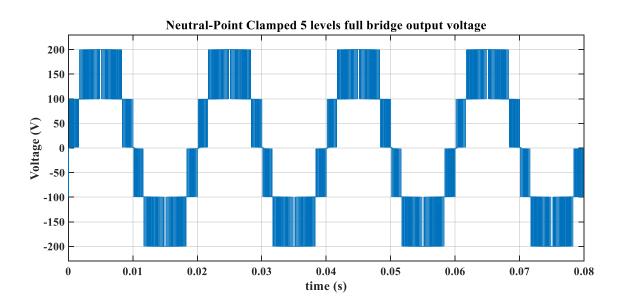

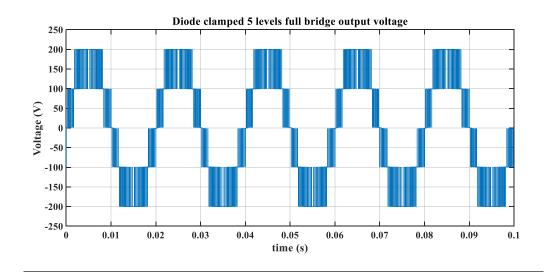

The waveform can be seen in Figure 2.5. The redundant states to generate the output voltage levels are detailed in the next section. The drawback of this topology is the common mode voltage.

Figure 2.5 NPC 5-levels full bridge output voltage waveform

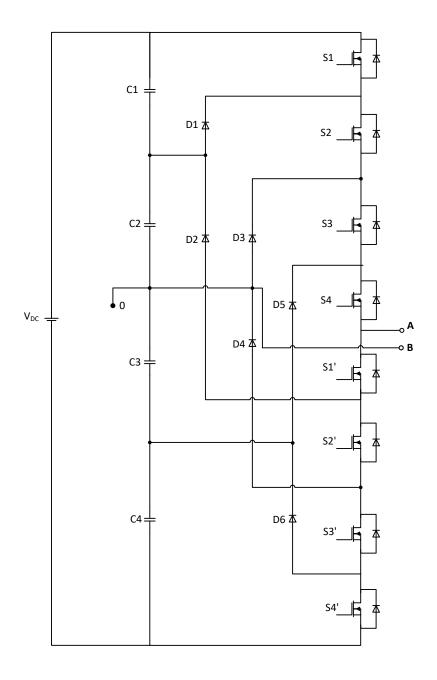

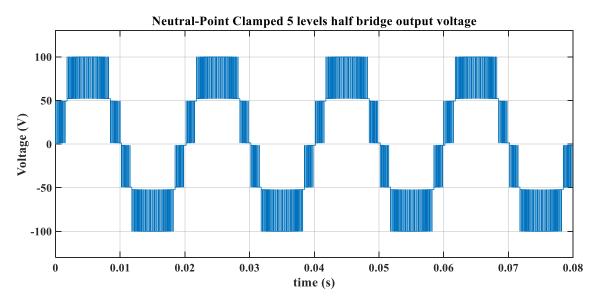

The 5-Level Half Bridge (5L-HB-NPC) topology and the output voltage waveform is shown in Figure 2.6 and Figure 2.7 respectively, this topology has the same number of levels as the 5L-FB-NPC topology explained previously, but the levels are V/2, V/4, 0, - V/4, -V/2. The number of switching elements in each topology is the same but the number of DC-link capacitors is now 4, with 6 clamping diodes.

Figure 2.6 Neutral-Point Clamped 5-level Half Bridge Single phase

The switching states for  $S_1$  to  $S_4$  and their correspondent complementary states to generate each of the levels are shown in Table 2.3.

The control of the switching sequences can be achieved using PWM or Space Vector Modulation (SVM) techniques explained in following sections.

| Vout   | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>1</sub> ' | S2' | S <sub>3</sub> ' | S4' |

|--------|----------------|----------------|----------------|----------------|------------------|-----|------------------|-----|

| Vdc/2  | 1              | 1              | 1              | 1              | 0                | 0   | 0                | 0   |

| Vdc/4  | 0              | 1              | 1              | 1              | 1                | 0   | 0                | 0   |

| 0      | 0              | 0              | 1              | 1              | 1                | 1   | 0                | 0   |

| -Vdc/4 | 0              | 0              | 0              | 1              | 1                | 1   | 1                | 0   |

| Vdc/2  | 0              | 0              | 0              | 0              | 1                | 1   | 1                | 1   |

Table 2.3 Switch states 5-level Neutral-Point Clamped

Figure 2.7 NPC 5-levels output voltage waveform

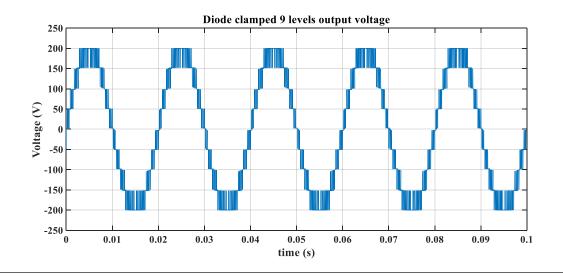

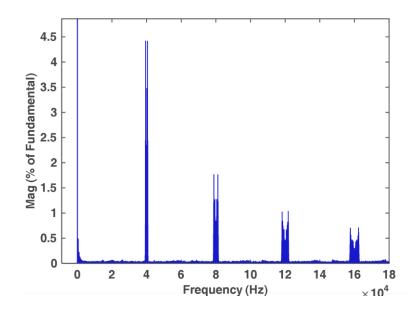

Similar to the adaptation made to form the 5L-FB-NPC, another leg or phase is added to the 5L-HB-NPC to form a 9-Levels Full-Bridge Neutral-Point Clamped (9L-FB-NPC) as shown in Figure 2.8 the 9-levels can be appreciated in Figure 2.9.

Figure 2.8 Neutral-Point Clamped 9-level Full Bridge Single phase

Figure 2.9 NPC 9-levels full bridge output voltage waveform

The complexity of the control of this topology is greater as there are 16 switches to control, along with 4 capacitors to balance in the DC-link.

The levels can be increased to n-number following the concept presented in this section. The literature presented in [2-12] investigates a 5 and 7 levels converter and a comparison is made between NPC, FCC and HB converters. A 7-level converter in [2-13] studies back-to-back converters focusing on the control and harmonic content of the system. A work presented in [2-14] introduces a simulation system for a 13-level converter analyzing the Total Harmonic Distortion (THD) and simulation performance.

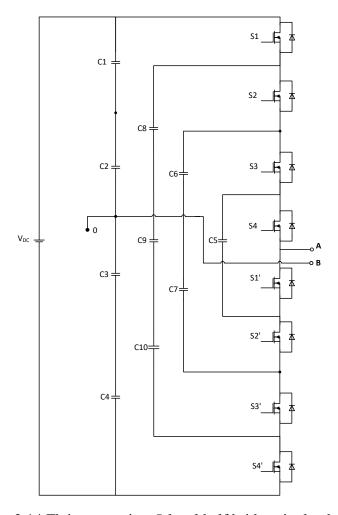

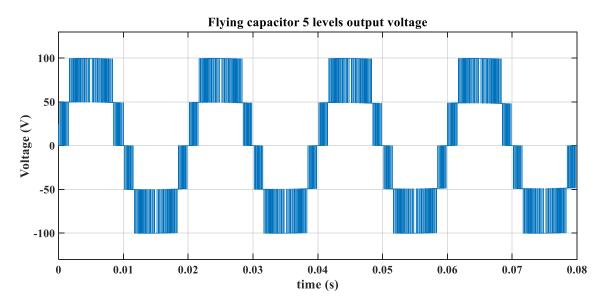

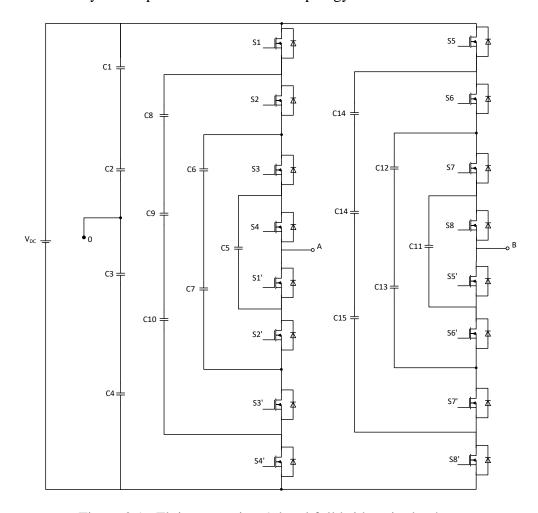

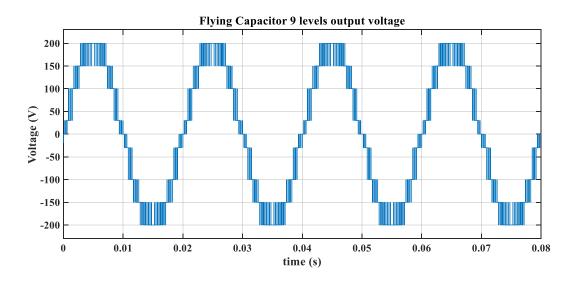

#### 2.2.2 Flying capacitor converter

In Figure 2.10 the 3 levels FCC is presented, this topology uses four switches (S1, S2, S1' and S2'). Two of those switches control the current flow while the other two generate the switching to form the output waveform. The converter also has two input capacitors (C1 and C2) to split the input voltage in two parts in a similar way to the NPC discussed previously. Additionally, a third capacitor (C) is included, denominated as a flying capacitor for its position in this topology, this capacitor generates the level zero in the output waveform Figure 2.11. The output is taken as well from nodes A and B and the operating principle is similar to that in the NPC but instead of using diodes to block the levels, capacitors are used to do it. The switches are controlled in such a way to ensure each capacitor is charged at V/2 and –V/2 so the Voltage in AB can be –V/2, 0, and V/2, these makes the 3 levels.

Figure 2.10 Flying capacitor 3-level single phase

The switching states of the 3L-HB-FC are shown in Table 2.4. It can be seen that for the level 0 there are 2 different states that can be used, known as redundant states. As the number of levels increase, the redundant states increase, giving degrees of freedom to control different characteristics in the converter, such as the balance in the DC-link capacitors.

| Vout   | $S_1$ | $S_2$ | S <sub>1</sub> ' | S <sub>2</sub> ' |

|--------|-------|-------|------------------|------------------|

| Vdc/2  | 1     | 1     | 0                | 0                |

| 0      | 1     | 0     | 0                | 1                |

| 0      | 0     | 1     | 1                | 0                |

| -Vdc/2 | 0     | 0     | 1                | 1                |

Table 2.4. Switching states and output voltage 3L-HB-FC

Figure 2.11 Flying capacitor 3-levels output voltage waveform

The main advantages of this topology are the redundant combinations required to generate a level that allows the capacitor voltage balancing, the reduction in filtering size when the number of levels is high. The main disadvantage is that it requires an excessive amount of capacitors as the number of levels increases. The capacitors tend to suffer from large volumes, high costs, and lower reliability when compared to semiconductors.

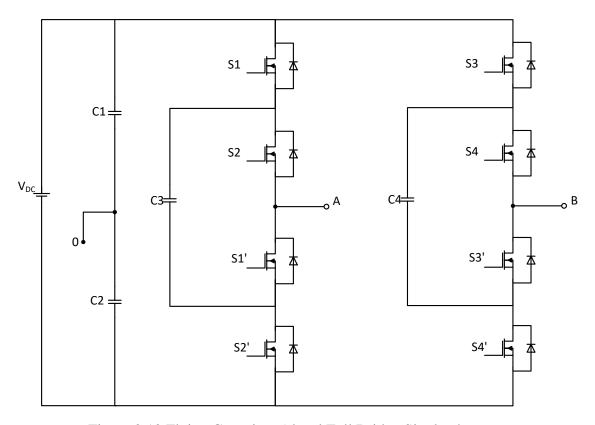

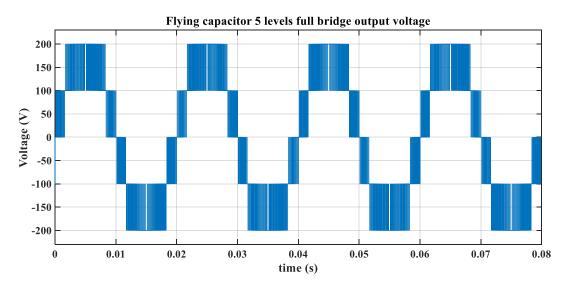

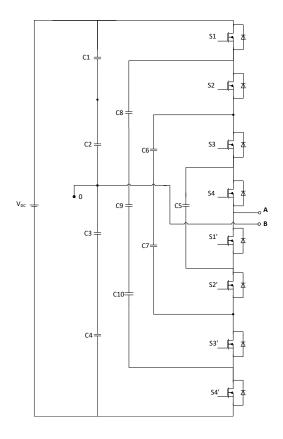

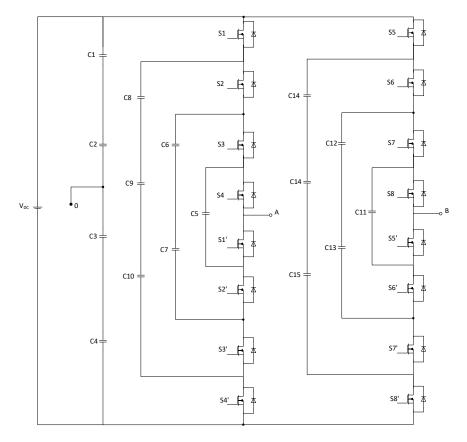

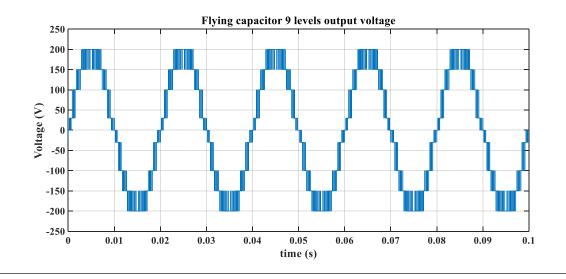

The 5-Levels Full-Bridge Flying-Capacitor is shown in Figure 2.12 formed by adding an additional leg to the 3L-HB-FC. The switching states are shown in Table 2.5. The topology employs 2 capacitors (C3 and C4) to balance the voltage in order to form the staircase waveform of 5-levels see Figure 2.13

Figure 2.12 Flying Capacitor 5-level Full Bridge Single phase

| Vout   | S <sub>1</sub> | S <sub>2</sub> | S <sub>1</sub> ' | S2' | S <sub>3</sub> | S <sub>4</sub> | S <sub>3</sub> ' | S <sub>4</sub> ' |

|--------|----------------|----------------|------------------|-----|----------------|----------------|------------------|------------------|

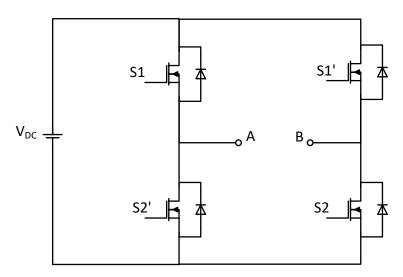

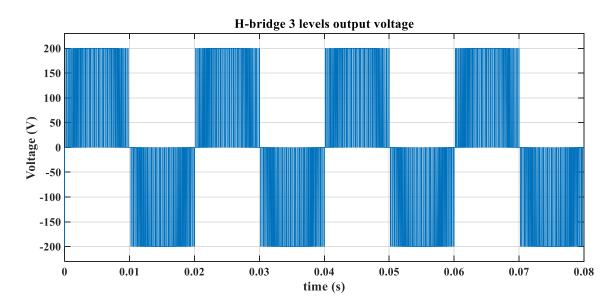

| Vdc    | 1              | 1              | 0                | 0   | 0              | 0              | 1                | 1                |