#### THE UNIVERSITY OF SHEFFIELD

# EVALUATION OF THERMAL MANAGEMENT SOLUTIONS FOR POWER SEMICONDUCTORS

#### By

### Manoj Balakrishnan

A Thesis submitted for the degree of Doctor of Philosophy in the Department of Electronic and Electrical Engineering, The University of Sheffield.

**MAY 2016**

#### **ABSTRACT**

This thesis addresses the thermal management and reliability concerns of power semiconductor devices from die to system level packaging design. Power electronics is a continuously evolving and challenging field. Systems continue to evolve, demanding increasing functionality within decreasing packaging volume, whilst maintaining stringent reliability requirements. This typically means higher volumetric and gravimetric power densities, which require effective thermal management solutions, to maintain junction temperatures of devices below their maximum and to limit thermally induced stress for the packaging medium.

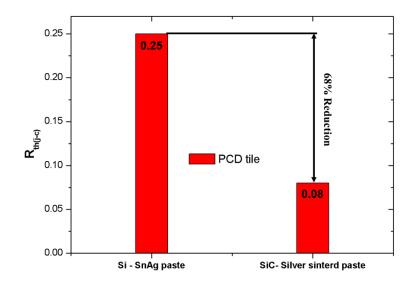

A comparison of thermal performance of Silicon and Silicon Carbide power semiconductor devices mounted on Polycrystalline Diamond (PCD) and Aluminum Nitride (AlN) substrates has been carried out. Detailed simulation and experimental analysis techniques show a 74% reduction in junction to case thermal resistance (R<sub>th (j-c)</sub>) can be achieved by replacing the AlN insulating layer with PCD substrate. In order to improve the thermal performance and power density of polycrystalline diamond substrates further at the system level, direct liquid cooling technique of Direct Bonded Copper (DBC) substrates were performed.

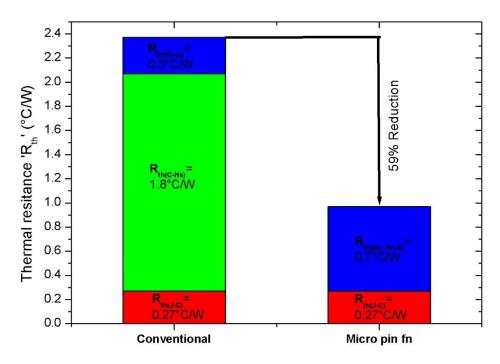

An empirical model was used to analyse the geometric and thermo-hydraulic dependency upon thermal performance of circular micro pins fins. Results show that micro pin fin direct cooling of DBC can reduce the number of thermal layers in the system, and reduce the thermal resistance by 59% when compared to conventional DBC cooling without a base plate.

Thermal management and packaging solutions for the wide band gap semiconductors, such as GaN, is also described in detail. Comparisons of face up and flip chip thermal performance of GaN on Sapphire, Silicon and 6H-SiC substrates in a T0-220 package system is presented. Detailed thermal simulation results analysed using ANSYS® show that a flip chip mounted GaN on sapphire substrate can reduce junction to case thermal resistance by 28% when compared against the face up mounted technique.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks to Professor Shankar Ekkanath Madathil, Dr Mark Sweet and Dr Vineet Unni for their invaluable guidance, encouragement and support during the course of the research and the writing of this thesis

I would also like to thank the Rolls-Royce SRC for the award of a research studentship and financial support. I would like to thank the staff at Rolls-Royce, especially Dr Kalyani Menon and Dr Graham Bruce for their support and enthusiasm.

I would also like to thank the technical staff in the Electrical Machines and Drives group, who were particularly helpful in the construction and installation of the test-rig. Thanks are also due to my colleagues in the University technology centre in electrical machines, for both their technical advice and for providing a lively and friendly atmosphere.

To end with, I would like to thank my family for their constant support and encouragement throughout my life, and Jinny Robson for the great times which helped me keep my stability during the course of this PhD.

# TABLE OF CONTENTS

| ABSTRACT                              | I    |

|---------------------------------------|------|

| ACKNOWLEDGEMENTS                      | III  |

| TABLE OF CONTENTS                     | V    |

| LIST OF FIGURES                       | IX   |

| LIST OF TABLES                        | XV   |

| LIST OF ACRONYMS                      | XVI  |

| NOMENCLATURE                          | XVII |

| CHAPTER 1: INTRODUCTION               | 1    |

| 1.1 Introduction                      | 3    |

| 1.2 What is Thermal management?       | 3    |

| 1.3 WHY THERMAL MANAGEMENT?           | 4    |

| 1.4 ELECTRICAL AND THERMAL PARAMETERS | 4    |

| 1.5 HEAT TRANSFER MODES               | 5    |

| 1.5.1 Radiation                       | 6    |

| 1.5.2 Conduction                      | 6    |

| 1.5.3 Convection                      | 8    |

| 1.6 THERMAL MODELLING TECHNIQUES      | 9    |

| 1.6.1 Electro-thermal modelling       | 10   |

| 1.6.2 Finite element analysis         | 13   |

| 1.7 Reliability                       | 14   |

| 1.7.1 Failure mode                    | 14   |

| 1.8 Semiconductor Power loss          | 15   |

| 1.9 THERMAL ENERGY AND POWER DENSITY  | 17   |

| 1.10 Thesis structure                 | 19   |

| REFERENCES                            | 20   |

| CHAPTER 2: SEMICONDUCTOR PACKAGING    | 21   |

| 2.1 Introduction                      | 23   |

| 2.2    | SINGLE CHIP/DISCRETE PACKAGES:                                       | 23 |

|--------|----------------------------------------------------------------------|----|

| 2.2.1  | Through hole and surface mount packages                              | 24 |

| 2.2.2  | Interconnection medium                                               | 27 |

| 2.3    | Power Electronics Module packaging                                   | 32 |

| 2.3.1  | 3D packaging of power modules                                        | 34 |

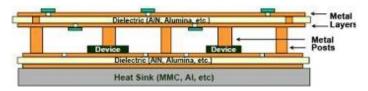

| 2.3.2  | Metal Post Interconnect Parallel Plate Structure packaging technique | 34 |

| 2.3.3  | Flip chip power module package:                                      | 35 |

| 2.3.4  | Power overlay technology:                                            | 35 |

| 2.3.5  | Pressure contact interconnect technology:                            | 36 |

| 2.3.6  | Pressure assisted/pressure less silver sintering                     | 37 |

| 2.4    | SUMMARY OF VARIOUS INTERCONNECT TECHNOLOGIES                         | 38 |

| Refere | NCES                                                                 | 42 |

| СНАРТЕ | R 3: THERMAL PERFORMANCE OF ALN AND PCD SUBSTRATES.                  | 45 |

| 3.1    | Introduction                                                         | 47 |

| 3.2    | SELECTION OF MATERIALS                                               | 52 |

| 3.2.1  | Power semiconductor Device                                           | 52 |

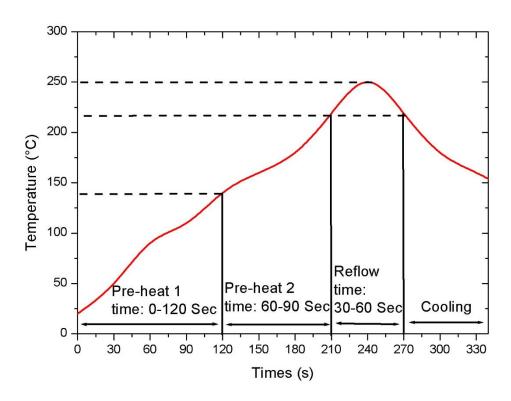

| 3.2.2  | Die attach medium                                                    | 52 |

| 3.2.3  | DBC Substrates                                                       | 53 |

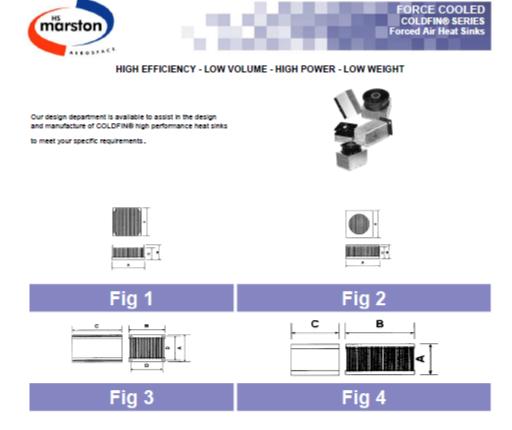

| 3.2.4  | Heat sink                                                            | 55 |

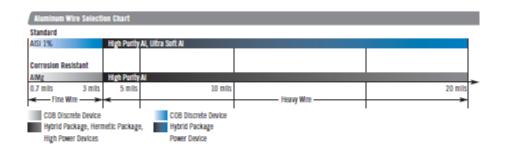

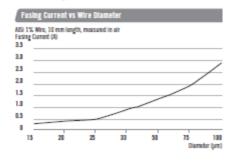

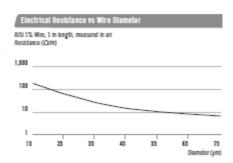

| 3.2.5  | Wire bonding                                                         | 55 |

| 3.3    | Experimental setup                                                   | 56 |

| 3.3.1  | Junction temperature measurement                                     | 56 |

| 3.4    | OVERVIEW OF EXPERIMENTAL SETUP                                       | 59 |

|        | EXPERIMENTAL MEASUREMENT OF THERMAL RESISTANCE OF PCD AND ALN ATES   | 60 |

| 3.5.1  | Thermal resistance (junction-case) R <sub>th(j-c)</sub>              | 60 |

| 3.5.2  | Thermal Impedance (junction to case) Z <sub>th(j-c)</sub>            | 62 |

| 3.5.3  | Void influence and contact thermal resistance                        | 65 |

| 3.5.4  | Simulation structure and specifications                              | 68 |

| 3.5.5  | Thermal Cycle Reliability for PCD & AlN substrates                   | 70 |

| 3.5.6  | Rated current and switching frequency improvement                    | 77 |

| 3.6    | NEXT GENERATION TECHNOLOGIES                                         | 79 |

| 3.6.1  | Simulation structure and specification                               | 80 |

| 3.6.2  | Simulation results                                        | 81  |

|--------|-----------------------------------------------------------|-----|

| 3.6.3  | Thermal cycling reliability                               | 83  |

| 3.7    | Conclusion                                                | 85  |

| Refere | NCES                                                      | 87  |

|        | CR 4: DIRECT COOLING OF RYSTALLINE DIAMOND SUBSTRATES     | 91  |

| 4.1    | Introduction                                              | 93  |

| 4.1.1  | Direct cooling of base plate                              | 94  |

| 4.1.2  | Double sided cooling                                      | 95  |

| 4.1.3  | Direct cooling of power modules (without base plate)      | 96  |

| 4.2    | EMPIRICAL MODEL                                           | 101 |

| 4.2.1  | Input block                                               | 102 |

| 4.2.2  | Pressure drop                                             | 103 |

| 4.2.3  | Reynolds number                                           | 104 |

| 4.2.4  | Thermal resistance                                        | 104 |

| 4.3    | Empirical results                                         | 105 |

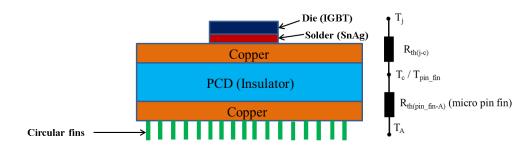

| 4.4    | COMPARISON BETWEEN CONVENTIONAL AND MICRO PIN FIN COOLING | 109 |

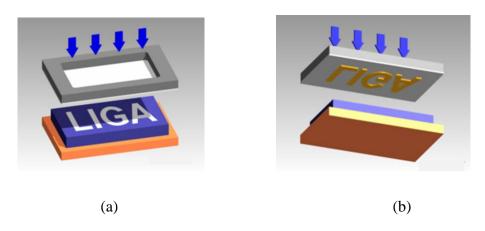

| 4.5    | LIGA FABRICATION TECHNOLOGY                               | 111 |

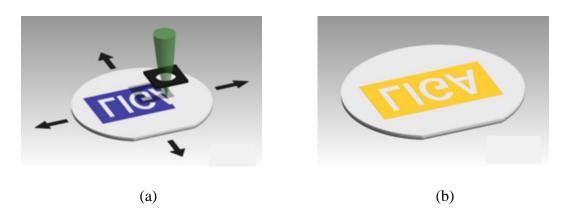

| 4.5.1  | Fabrication (Intermediate mask)                           | 111 |

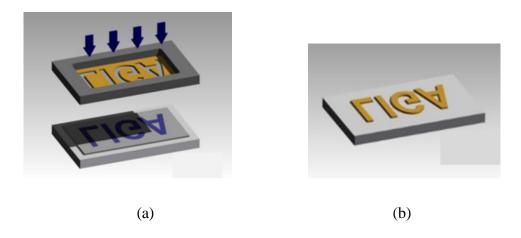

| 4.5.2  | Fabrication (Working mask)                                | 112 |

| 4.5.3  | Microstructure fabrication                                | 113 |

| 4.5.4  | Electroforming                                            | 113 |

| 4.6    | MICRO STRUCTURE GEOMETRIC DESIGNS FOR LIGA PROCESS        | 114 |

| 4.7    | FABRICATED MICRO STRUCTURES USING LIGA TECHNOLOGY         | 115 |

| 4.8    | Conclusion                                                | 116 |

| Refere | NCES                                                      | 117 |

|        | CR 5 : THERMAL PERFORMANCE OF GAN FACE UP AND FLI         |     |

| 5.1    | Introduction                                              | 121 |

| 5.1.1  | Material Properties                                       | 121 |

| 5.1.2  | GaN substrate options                                     | 123 |

| 5.1.3  | Device Topology                                           | 124 |

| 5.1.4  | GaN Packaging options and mounting techniques             | 125 |

| 5.2 F   | ELECTRICAL PACKAGE PARASITIC                            | 125 |

|---------|---------------------------------------------------------|-----|

| 5.2.1   | Equivalent circuit model of package lead                | 127 |

| 5.3 I   | FACE UP MOUNTING                                        | 128 |

| 5.3.1   | Structure definition                                    | 128 |

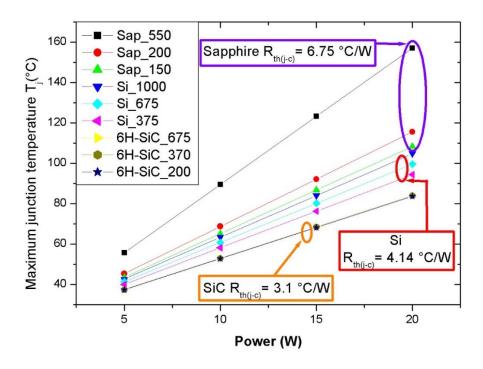

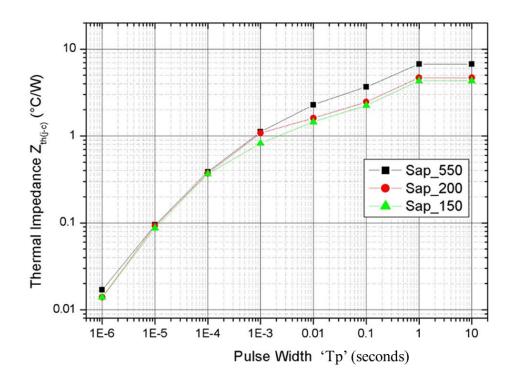

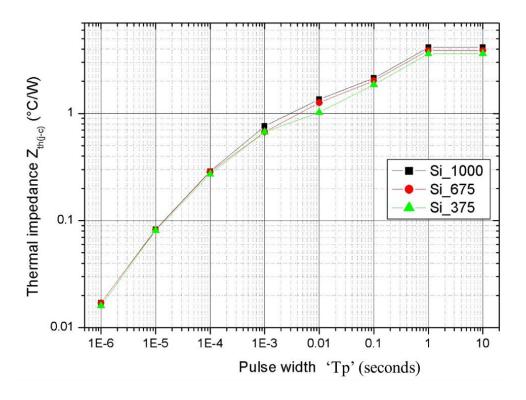

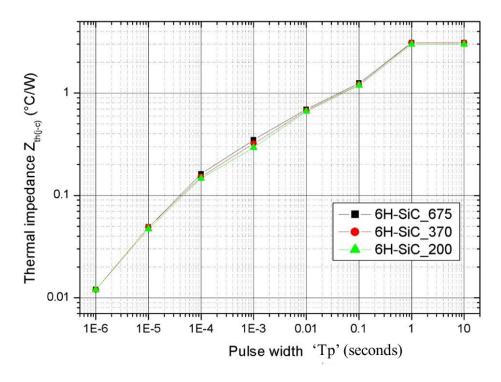

| 5.3.2   | Face up mounting results                                | 132 |

| 5.4 H   | FLIP CHIP MOUNTING                                      | 141 |

| 5.4.1   | Structure definition                                    | 141 |

| 5.4.2   | Flip chip mounting results                              | 145 |

| 5.5     | COMPARISON BETWEEN FACE UP AND FLIP CHIP MOUNTED SYSTEM | 154 |

| 5.5.1   | Steady state thermal resistance                         | 154 |

| 5.5.2   | Transient thermal impedance                             | 156 |

| 5.5.3   | Parasitic elements                                      | 158 |

| 5.6     | Conclusion                                              | 160 |

| Referen | NCES                                                    | 161 |

| CHAPTE  | R 6 : CONCLUSIONS                                       | 163 |

| 6.1 F   | Future work                                             | 168 |

| 6.2 I   | PUBLICATIONS                                            | 169 |

| APPENDI | ICES                                                    | 171 |

# LIST OF FIGURES

| Figure 1.1: Thermal flux trend[1]3                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: (a) Electrical and (b) Thermal domain5                                                                                                                    |

| Figure 1.3: Heat flow in a wire bonded power module6                                                                                                                  |

| Figure 1.4: Conductional heat flow in a body7                                                                                                                         |

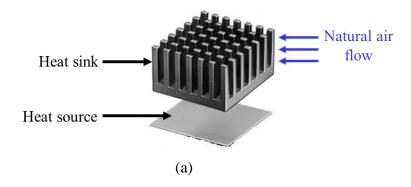

| Figure 1.5:Convectional heat flow (a) Natural convection; (b) Forced convection[5]9                                                                                   |

| Figure 1.6: Foster thermal network of a single chip module                                                                                                            |

| Figure 1.7: Cauer thermal network                                                                                                                                     |

| Figure 1.8: Bath tub curve[1]14                                                                                                                                       |

| Figure 1.9: IGBT I-V characteristics                                                                                                                                  |

| Figure 1.10: DC-DC converter16                                                                                                                                        |

| Figure 1.11: Voltage and current waveforms of IGBT16                                                                                                                  |

| Figure 1.12: Instantaneous power loss per cycle                                                                                                                       |

| Figure 1.13: Switching power loss                                                                                                                                     |

| Figure 1.14: Heat sink thermal resistance and heat sink length                                                                                                        |

| Figure 2.1: Through hole power packages[2] (a) Dual inline package (b) Transistor outline T0-220 (c) Pin grid array24                                                 |

| Figure 2.2: Surface mount packages[2] (a) Small Outline Package; (b) Quad flat pack (QFP); (c) small outline transistor (SOT); (d) Plastic leaded chip carrier (PLCC) |

| Figure 2.3: TO Packages [3] (a)T0-247; (b)T0-220; (c)SuperT0-220/superT0-247; (d)T0-263/D <sup>2</sup> PAK                                                            |

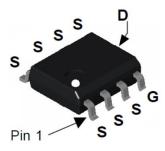

| Figure 2.4: Surface mount SO package [3];(a)S0-8; (b)TSSOP-8; (c)SOT-223; (d)SOT-23; (e)TSOP-6                                                                        |

| Figure 2.5: Silicon to foot print ratio for surface mount package[4]27                                                                                                |

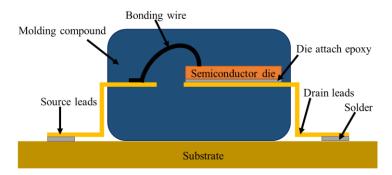

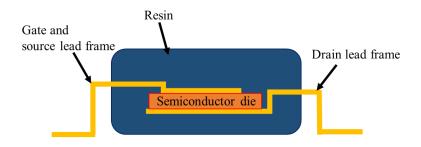

| Figure 2.6: Conventional wire bond package28                                                                                                                          |

| Figure 2.7: Power connect technology[7]29                                                                                                                             |

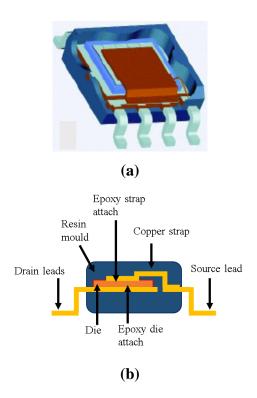

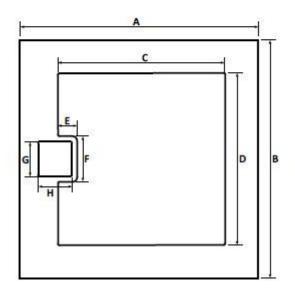

| Figure 2.8: Copper strap technology (a) Outline view[8] (b) cross sectional schematic view 29                                                                         |

| Figure 2.9: SO-8 Wireless package30                                                                                                                                   |

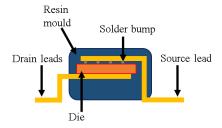

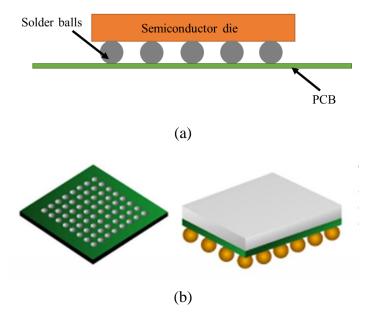

| Figure 2.10: BGA MOSFET package (a) cross sectional view; (b) outline view[9]31                                                                                       |

| Figure 2.11: Bottomless package[11]31                                                                                                                                 |

| Figure 2.12: FlipFET power MOSFET[12]32                                                                                                                               |

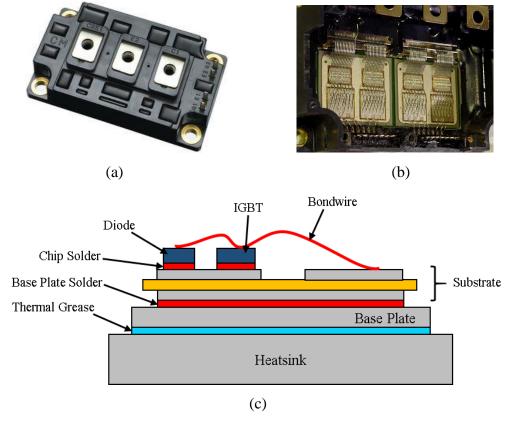

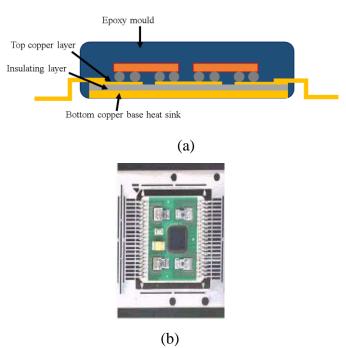

| Figure 2.13: Conventional IGBT module (a) & (b) outline and detailed view [13]; (c) Schematic cross sectional view                                                    |

|                                                                                                                                                                       |

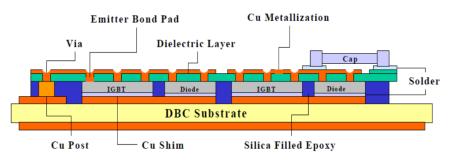

| Figure 2.15: Flip chip power module(a) cross sectional schematic view (b) Detailed view                                    | _  |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.16: Schematic cross section of power overlay interconnect technology [26]                                         |    |

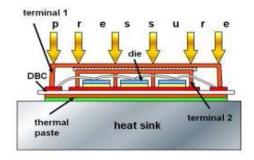

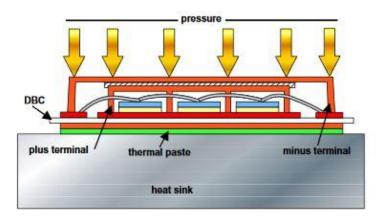

| Figure 2.17: Semikron's SkiiPPack pressure contact interconnect technology[27]                                             | 37 |

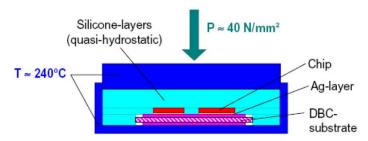

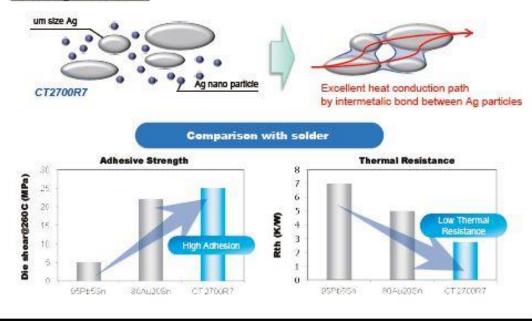

| Figure 2.18: Schematic setup for silver sintering[31]                                                                      | 37 |

| Figure 2.19: Semikron Skin technology with flexible interconnect[32]                                                       | 38 |

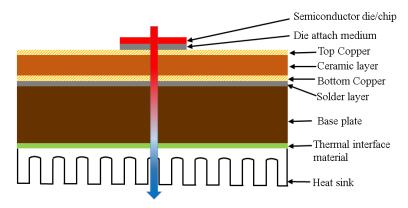

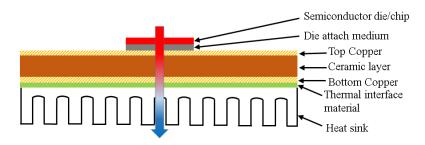

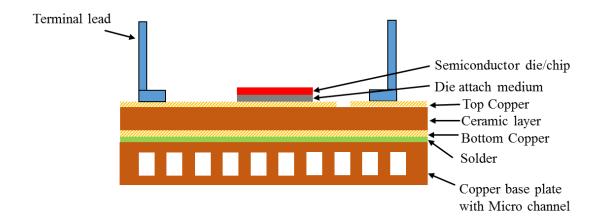

| Figure 3.1: Typical cross-section of a conventional wire bond package                                                      | 47 |

| Figure 3.2: The thermal resistance distribution in a conventional power module                                             | 48 |

| Figure 3.3: Schematic cross section of high power density module without the base plate                                    | 49 |

| Figure 3.4: Cauer thermal model of a power module cross section                                                            | 51 |

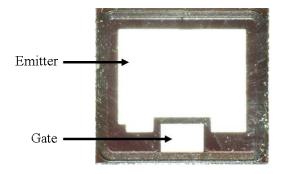

| Figure 3.5: IGBT die                                                                                                       | 52 |

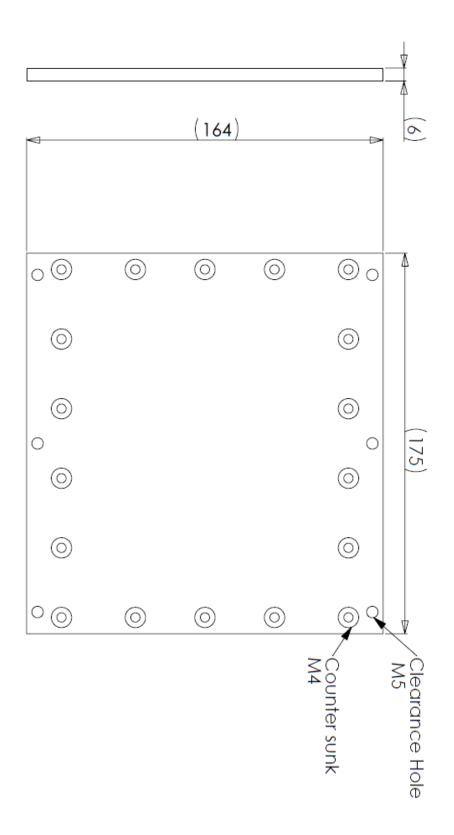

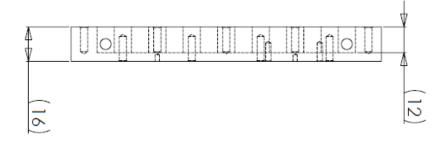

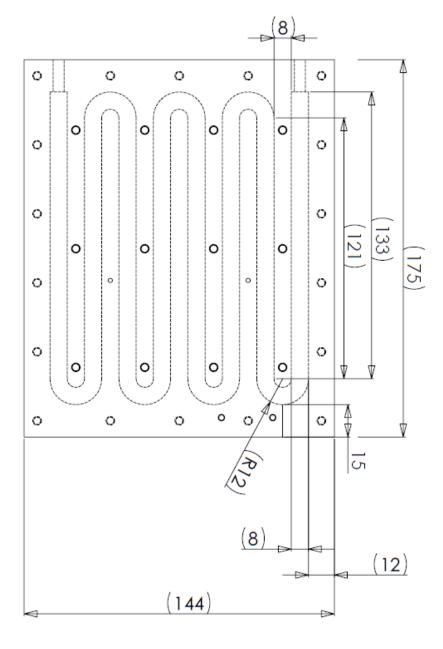

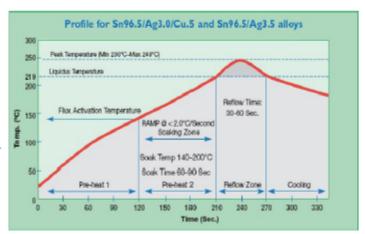

| Figure 3.6: Temperature profile for lead free solder[12]                                                                   | 53 |

| Figure 3.7: Schematic cross section of DBC                                                                                 | 53 |

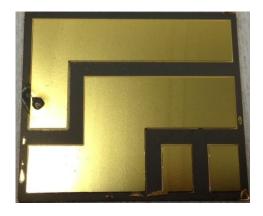

| Figure 3.8: PCD substrates                                                                                                 | 54 |

| Figure 3.9: AlN substrates                                                                                                 | 54 |

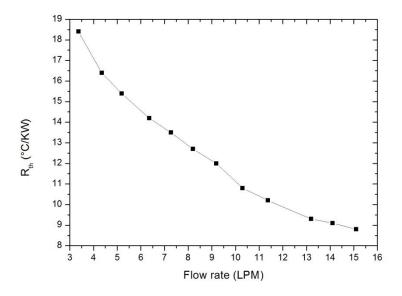

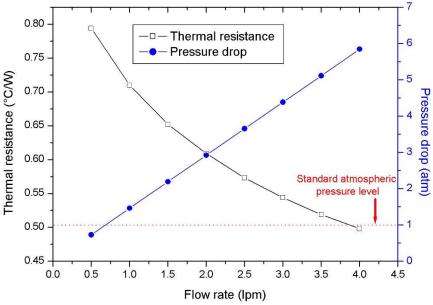

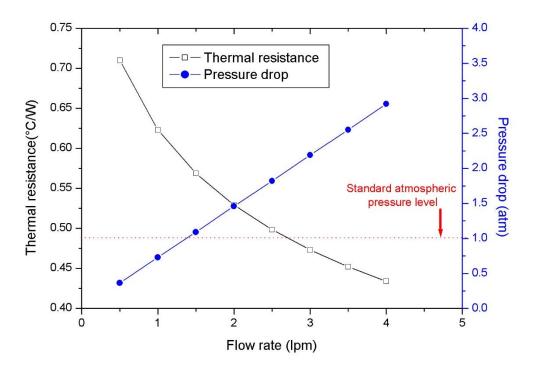

| Figure 3.10: Thermal resistance Vs Flow rate                                                                               | 55 |

| Figure 3.11: PCD substrate die attached and wire bonded                                                                    | 56 |

| Figure 3.12: I-V characteristics of IGBT measured at junction temperatures of 25°C and 150°C                               | 57 |

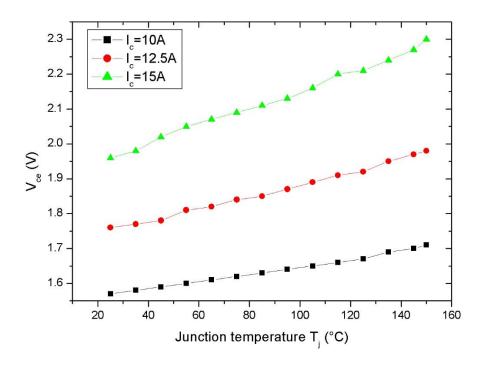

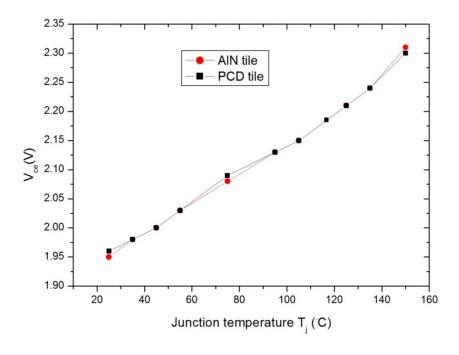

| Figure 3.13: V <sub>ce</sub> Vs T <sub>j</sub> at gate voltage V <sub>gs</sub> =10V                                        | 58 |

| Figure 3.14: $V_{ce}$ Vs $T_j$ at $V_{ge} = 10V$ and $I_c = 15A$ for PCD and AlN substrate                                 | 58 |

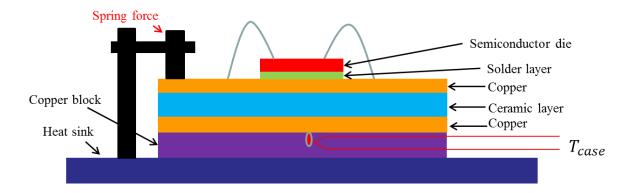

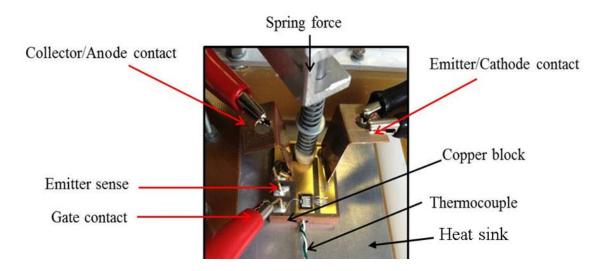

| Figure 3.15: Schematic cross section of the experimental structure                                                         | 59 |

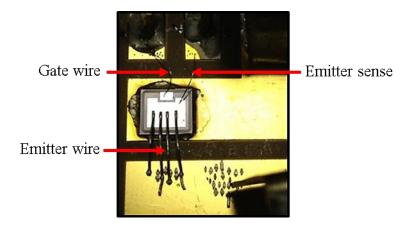

| Figure 3.16: Photographic view of the experimental structure                                                               | 59 |

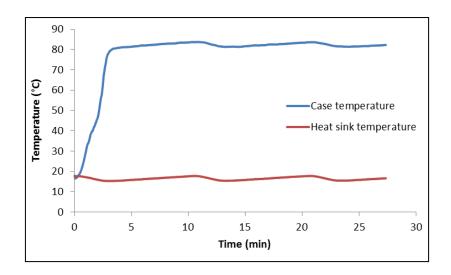

| Figure 3.17: Data log of case and heat sink temperature                                                                    | 60 |

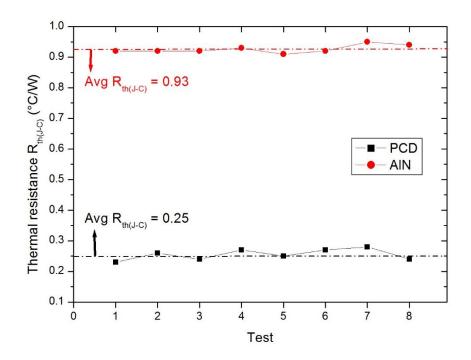

| Figure 3.18: Thermal Resistance (Junction – Case) R <sub>th(j-c)</sub> at ~32w<br>For PCD and ALN Substrates               | 61 |

| Figure 3.19: Thermal Resistance (junction – case) R <sub>th(j-c)</sub> at ~40W for PCD And AlN Substrates                  | 62 |

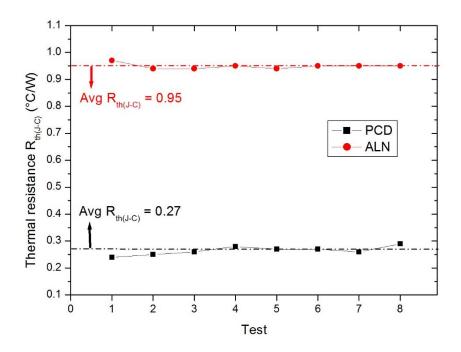

| Figure 3.20: Schematic wave form for thermal impedance (Z <sub>th</sub> ) for PCD tile measured at 100µs (50% duty cycle). | 63 |

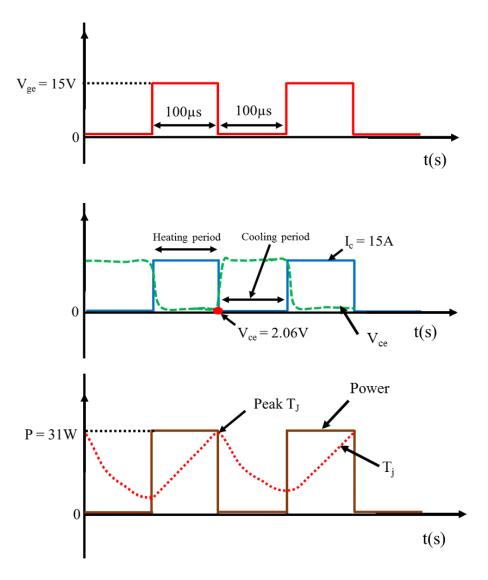

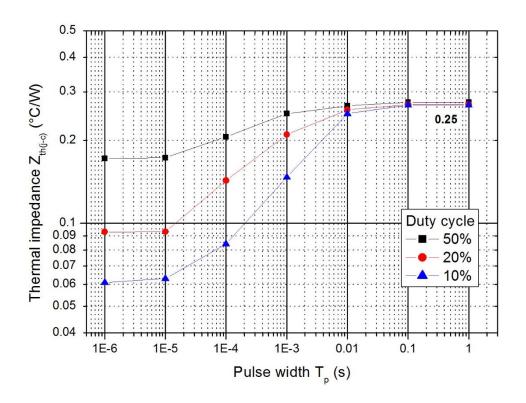

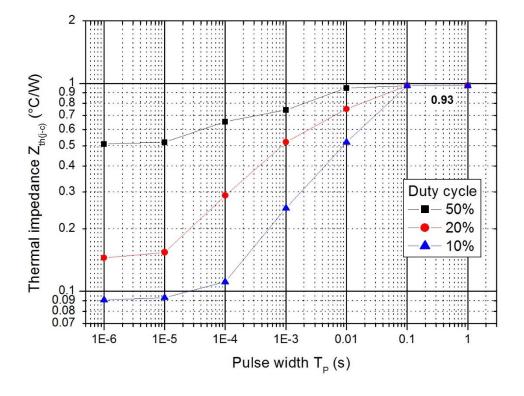

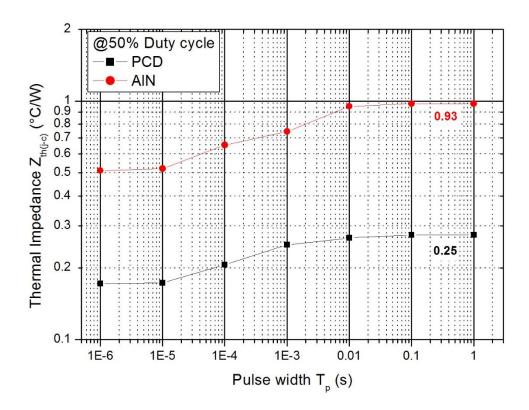

| Figure 3.21: Thermal impedance (junction to case) Z <sub>th(j-c)</sub> for PCD substrate                                   | 64 |

| Figure 3.22: Thermal impedance (junction to case) Z <sub>th(j-c)</sub> for AlN substrate                                   | 64 |

| Figure 3.23: Thermal impedance (junction to case) Zth(j-c) for PCD and substrates at 50% duty cycle                                 | AlN<br>65 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------|

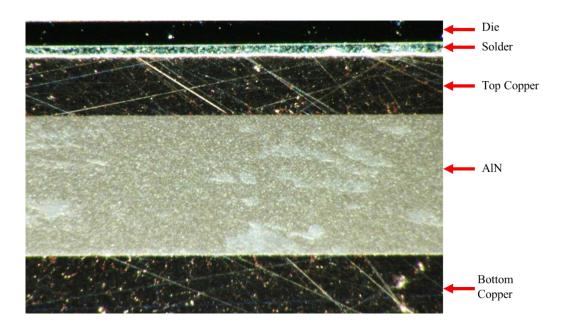

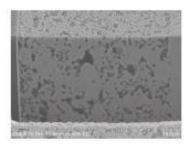

| Figure 3.24: Cross-section of AlN DBC tile                                                                                          | 66        |

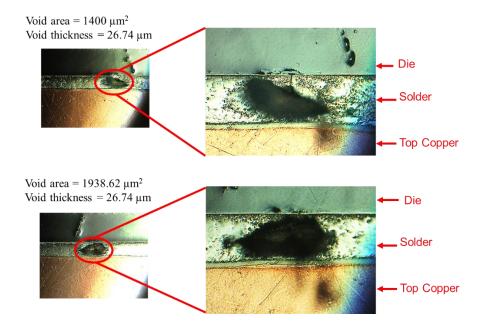

| Figure 3.25: Detailed view of Solder voids                                                                                          | 66        |

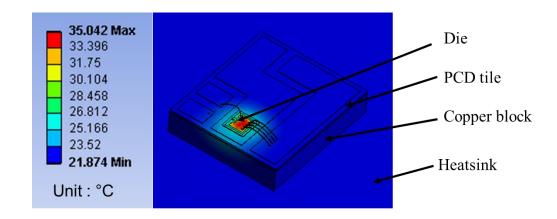

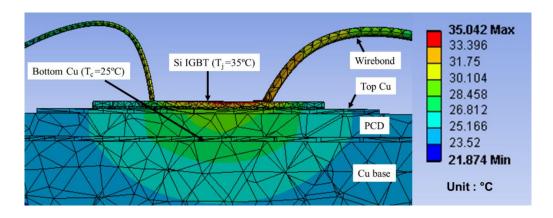

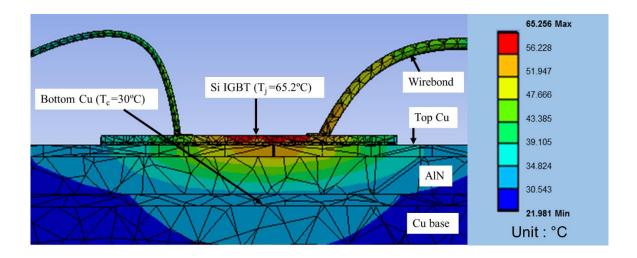

| Figure 3.26: 3D view of PCD tile mounted on a copper block and heatsink                                                             | 68        |

| Figure 3.27: Cross-sectional thermal contours for PCD tile (Thermal loading = $40W$ , Ambient = $22^{\circ}C$ )                     | 68        |

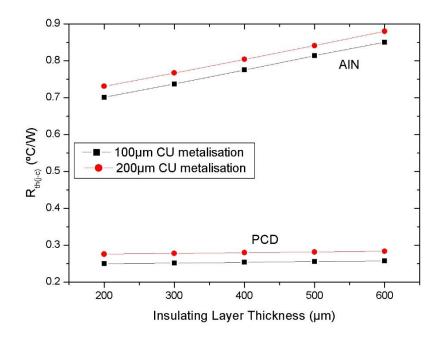

| Figure 3.28: Cross-sectional thermal contours for AlN tile (Thermal loading = $40W$ , Ambient = $22^{\circ}C$ )                     | 69        |

| Figure 3.29: Variation in the thermal resistance with thicknesses for Si dies on AlN and Diamond tiles                              | 70        |

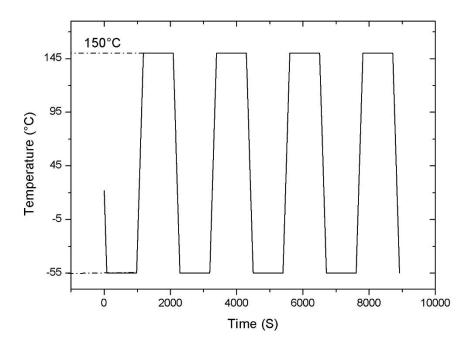

| Figure 3.30: Thermal loading                                                                                                        | 71        |

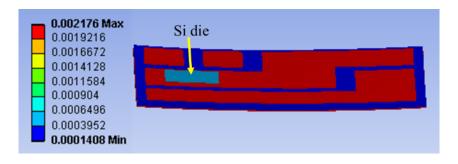

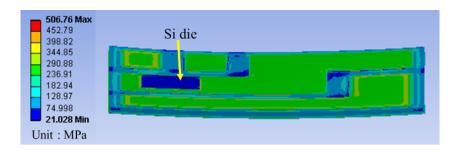

| Figure 3.31: Thermal strain contours for Si die mounted over polycrystalline diamond tile at 150°C                                  | 72        |

| Figure 3.32: Thermal strain contours for Si die mounted over Aluminium nitride tile 150°C                                           | 72        |

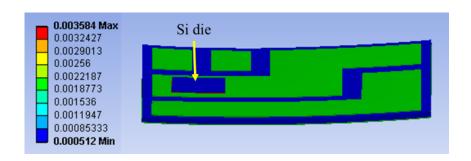

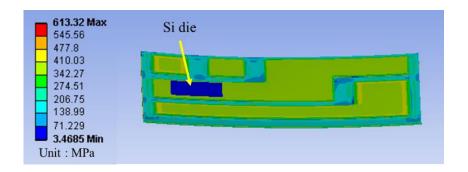

| Figure 3.33: Thermal stress contours for Si die mounted over polycrystalline diamond tile 150°C.                                    | 73        |

| Figure 3.34: Thermal stress contours for Si die mounted over aluminium nitrite tile 150°C                                           | 73        |

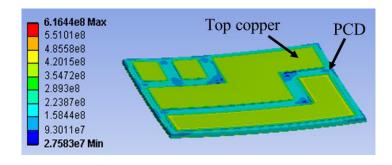

| Figure 3.35: Equivalent stress contours for PCD substrate                                                                           | 75        |

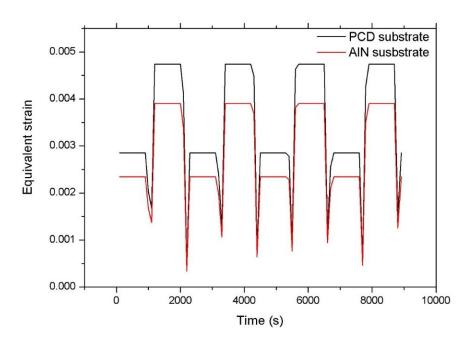

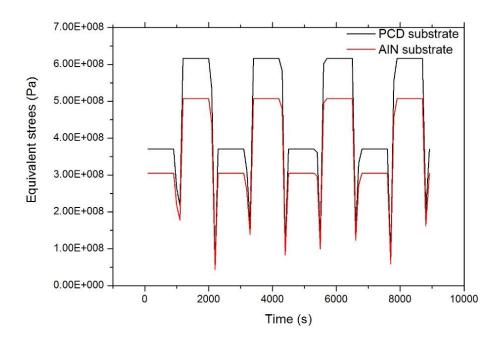

| Figure 3.36: Maximum equivalent strain for PCD and AlN substrates                                                                   | 75        |

| Figure 3.37: Maximum equivalent stress for PCD and AlN substrates                                                                   | 76        |

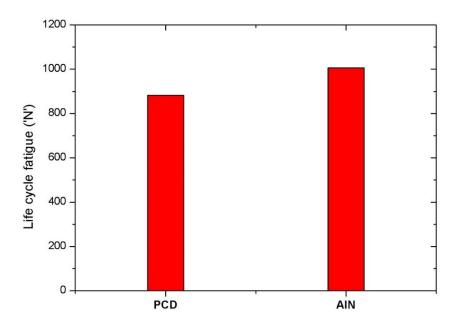

| Figure 3.38: Life cycle fatigue for PCD and AlN substrates                                                                          | 76        |

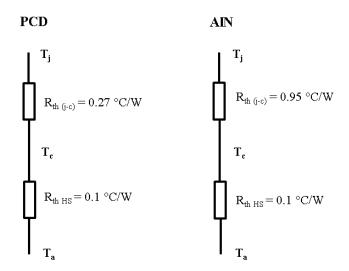

| Figure 3.39: Thermal resistance junction to ambient $(R_{th(j-a)})$ network path                                                    | 77        |

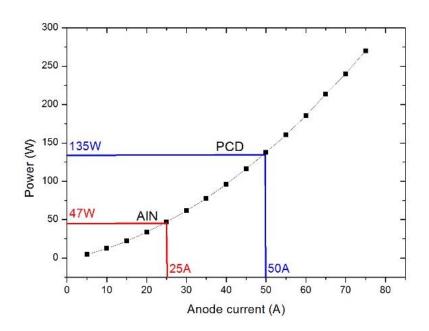

| Figure 3.40: IGBT current rating at 100°C ambient temperature                                                                       | 78        |

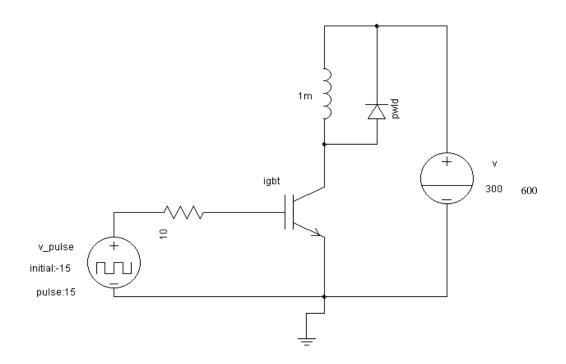

| Figure 3.41: DC-DC converter                                                                                                        | 79        |

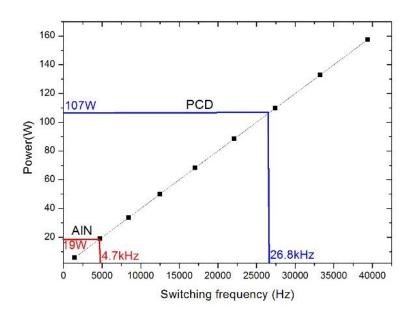

| Figure 3.42: Maximum switching frequency for the AlN and PCD tiles operated at 25A.                                                 | 79        |

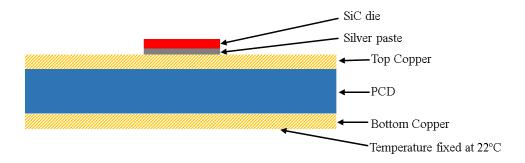

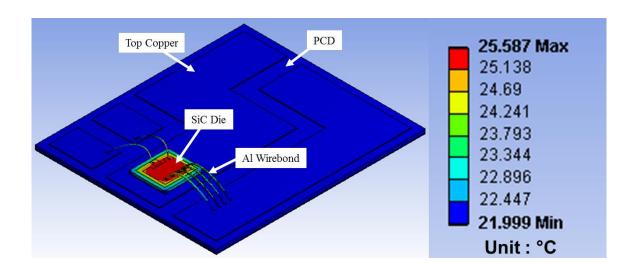

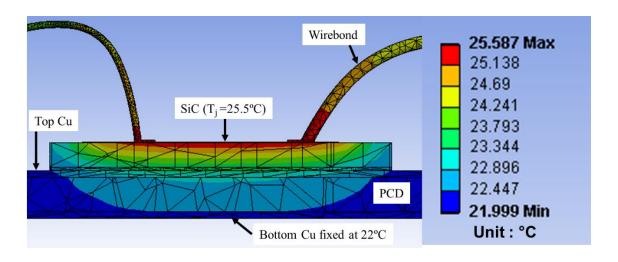

| Figure 3.43: Simplified cross-section of the simulation thermal system                                                              | 81        |

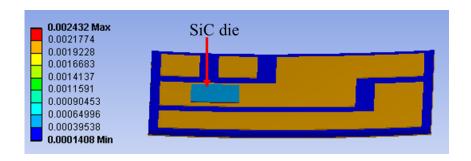

| Figure 3.44: Three-dimensional simulation of the silicon carbide dies attached to a PCD tile                                        | 82        |

| Figure 3.45: Cross-sectional Thermal contours of SiC dies on PCD tile using silver paste die attach                                 | 82        |

| Figure 3.46: Thermal resistance reduction in percentage                                                                             | 83        |

| Figure 3.47: Thermal strain contours for SiC die mounted over polycrystalline diamond tile using silver sinterd die attach at 150°C | 84        |

| Figure 3.48: Thermal stress contours for SiC die mounted over polycrystalline diamond tile using silver sinterd die attach at 150°C | 84             |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------|

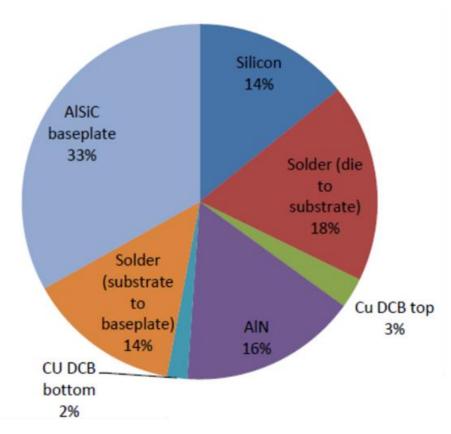

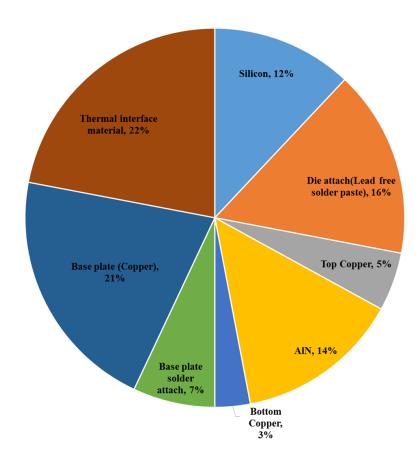

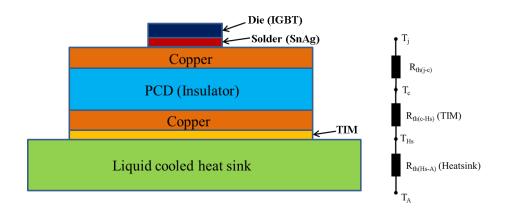

| Figure 4.1: Cross sectional view of a power module                                                                                  | 93             |

| Figure 4.2: Percentage of thermal resistance contribution [1]                                                                       | 94             |

| Figure 4.3: Micro channel structure for direct cooling of base plate[2]                                                             | 95             |

| Figure 4.4: Photographic view of Micro channelled base plate[2]                                                                     | 95             |

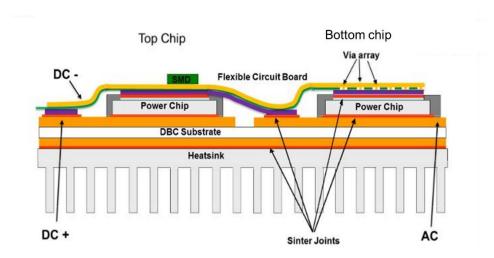

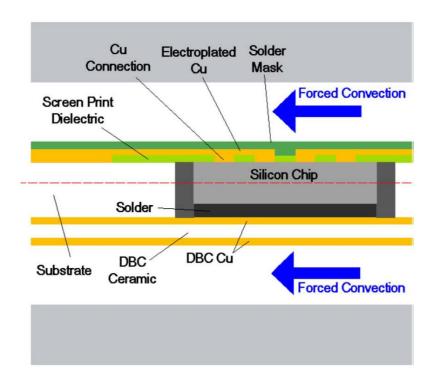

| Figure 4.5: Double sided cooling for embedded power module [3]                                                                      | 96             |

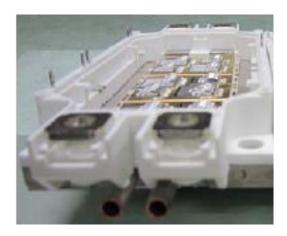

| Figure 4.6: Semikron power module[4]                                                                                                | 97             |

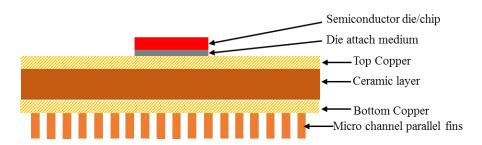

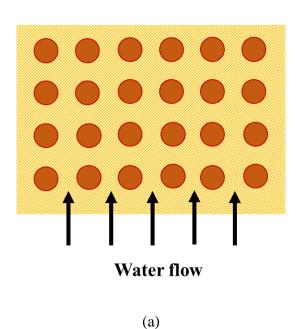

| Figure 4.7: (a) Cross sectional schematic of micro channel parallel fins in a DBC (b) Top view                                      |                |

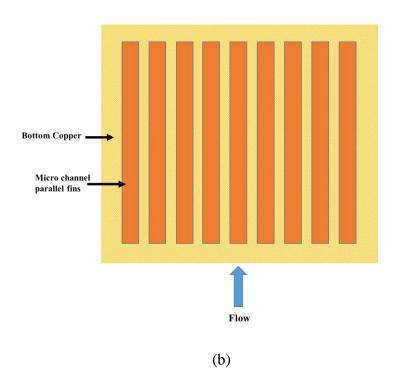

| Figure 4.8: Thermal resistance comparison between micro channel fin micro pin fin structures[10]                                    | and<br>99      |

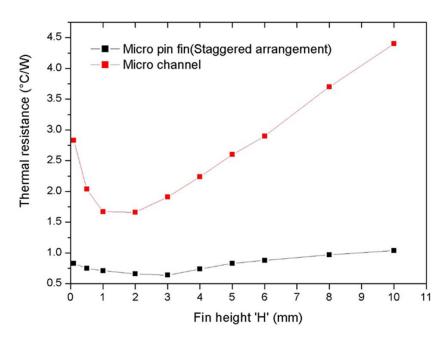

| Figure 4.9: (a) Micro pin fin in-line arrangement (b) Micro pin fin staggered arra                                                  | angement 100   |

| Figure 4.10: Thermal resistance comparison of circular, hydrofoil, cone and rectangular shaped micro pin fin structures[15].        | 100            |

| Figure 4.11: Simulink model for determining Thermal resistance and pressure dr circular micro pin fin.                              | -              |

| Figure 4.12: Pin fin geometry parameters                                                                                            | 102            |

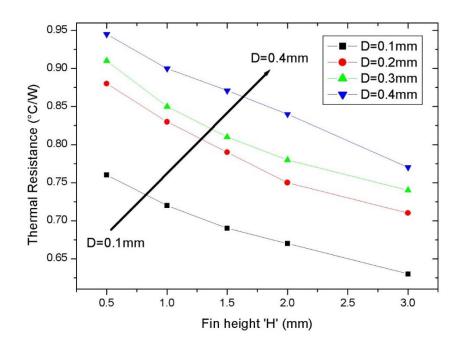

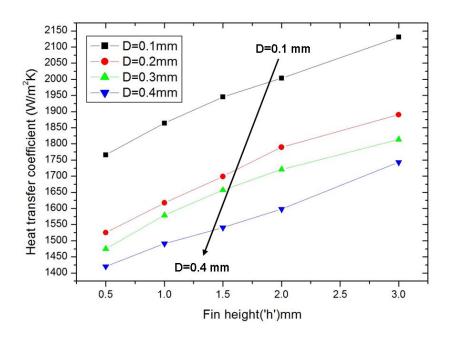

| Figure 4.13: Thermal resistance for varying pin fin diameter and height at a fixed flow rate of 1 lpm                               | 106            |

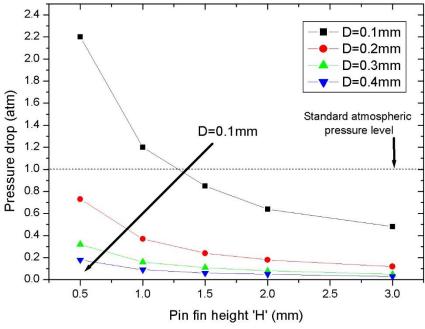

| Figure 4.14: Pressure drop for varying pin fin diameter and height fixed flow rate of 1 lpm                                         | at a<br>106    |

| Figure 4.15: Heat transfer co efficient for varying pin fin diameter and height at a fixed flow rate of 1 lpm                       | 107            |

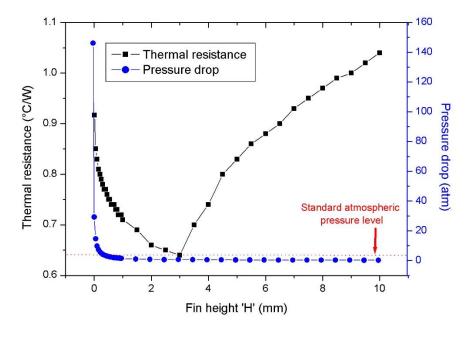

| Figure 4.16: Thermal resistance and pressure drop for pin fin D=0.1mm at fixed flow of 1 lpm                                        | 107            |

| Figure 4.17: Thermal resistance and pressure drop for circular Design 1 (D=0.1mm; H=1mm)                                            | 108            |

| Figure 4.18: Thermal resistance and pressure drop for circular Design 2 (D=0.2mm; H=2mm)                                            | 109            |

| Figure 4.19: Cooling of power module without baseplate                                                                              | 110            |

| Figure 4.20: Micro pin fin direct cooling of DBC substrate                                                                          | 110            |

| Figure 4.21: Comparison between conventional and micro pin fin direct cooling of DBC substrates                                     | 111            |

| Figure 4.22:Fabrication[18] (a) Electron beam lithography; (b) Gold electroplatic                                                   | ng112          |

| Figure 4.23: Working mask[18] (a) X-Ray lithography; (b) Gold deposition on re-                                                     | esist laver112 |

| Figure 4.24: X-ray lithography process [18](a) Top isometric view;  Bottom isometric view                                                                     | (b)<br>113 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 4.25: Fabricated microstructures[18]                                                                                                                   | 113        |

| Figure 4.26: Electroplating [18](a) Electroplated micro structures; (b) Final structure Injection moulded on to base material.                                | 114        |

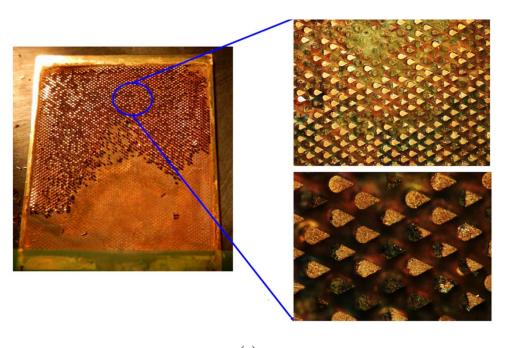

| Figure 4.27: LIGA fabricated Cone shaped micro pin fin structures (a) detailed view of shaped structures; (b) pin fin structure lift off due to poor adhesion |            |

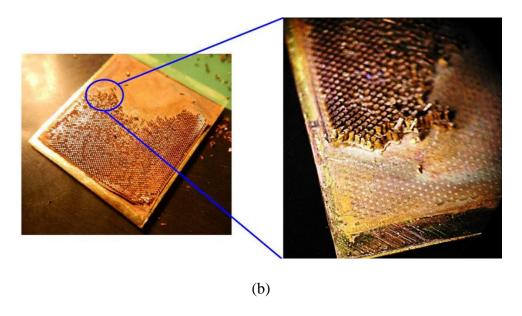

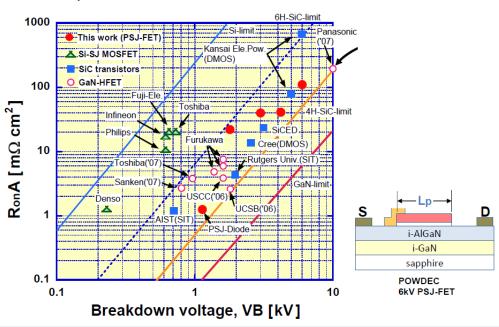

| Figure 5.1: On state resistance and breakdown voltage for various semiconductor device technologies [1, 2]                                                    | 122        |

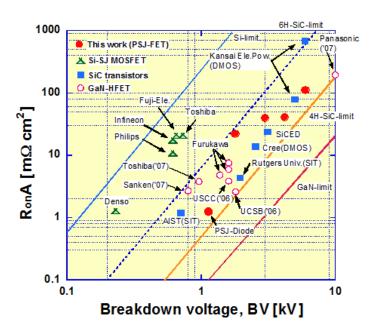

| Figure 5.2: Cross sectional schematic view of GaN heteroepitaxial structure a FET device[6]                                                                   | for<br>123 |

| Figure 5.3: (a) Vertical GaN device (b) Lateral GaN device[8]                                                                                                 | 124        |

| Figure 5.4: Self and mutual inductance of a single loop                                                                                                       | 126        |

| Figure 5.5: T-equivalent circuit                                                                                                                              | 127        |

| Figure 5.6: Schematic 3D view of GaN face up structure                                                                                                        | 128        |

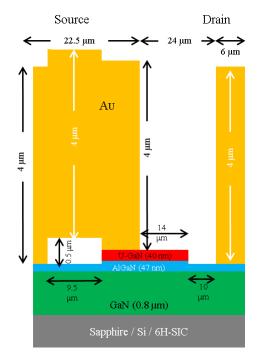

| Figure 5.7: Detailed cross-section schematic view along the channel region of GaN face up structure.                                                          | 128        |

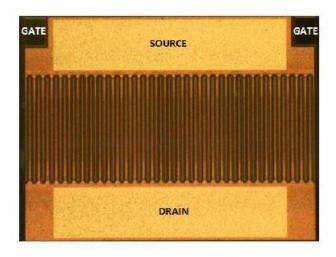

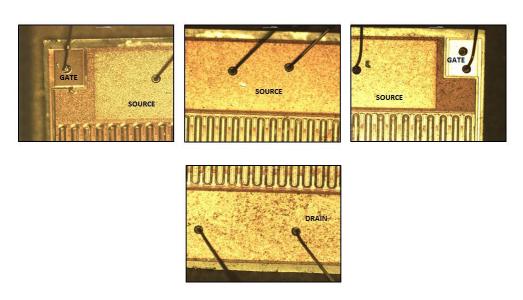

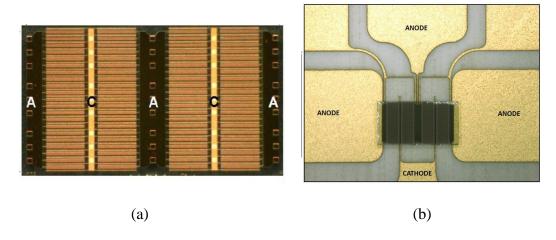

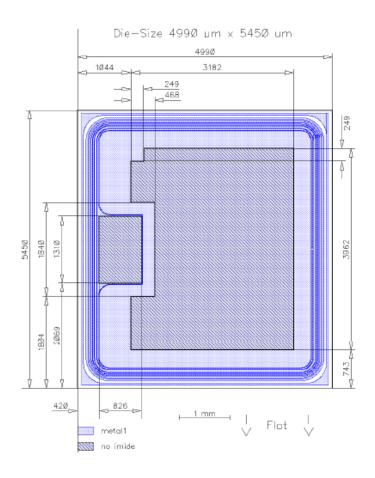

| Figure 5.8: Fabricated GaN on SiC serpentine Gate PSJ HFET[10]                                                                                                |            |

| Figure 5.9: Wire-bonded PSJ HFET[10]                                                                                                                          |            |

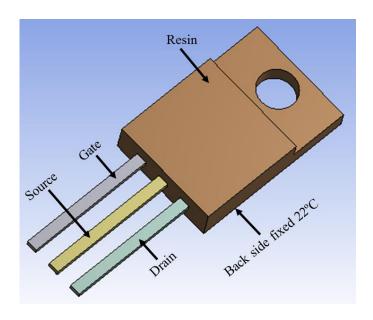

| Figure 5.10: 3D schematic view of GaN face up on TO-220 package without the epoxy resin                                                                       |            |

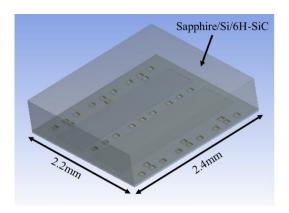

| Figure 5.11: 3D view of GaN on sapphire/silicon/6H-SiC with face up mounting in a T0-220 package system                                                       | 130        |

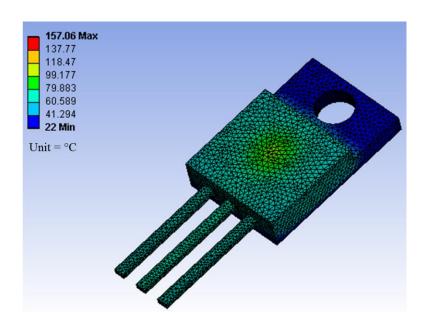

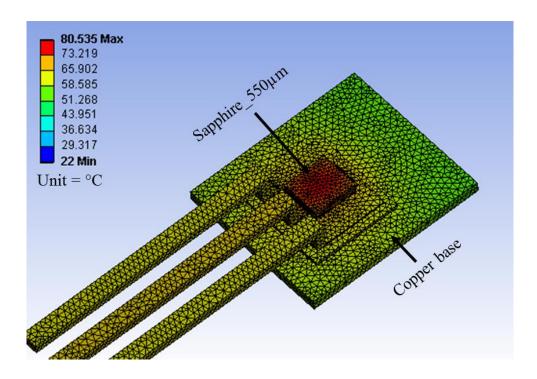

| Figure 5.12: 3D thermal contours for GaN on sapphire (550µm) in a T0-220 package with a thermal loading of 20W                                                | 132        |

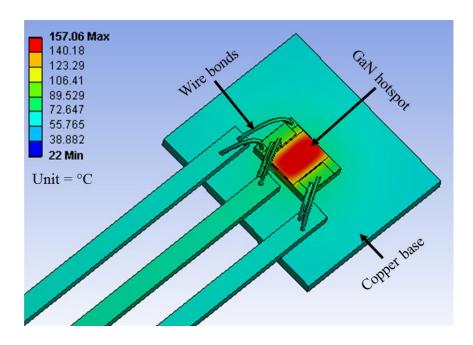

| Figure 5.13: Detailed view representing hotspot region without the resin body                                                                                 | 133        |

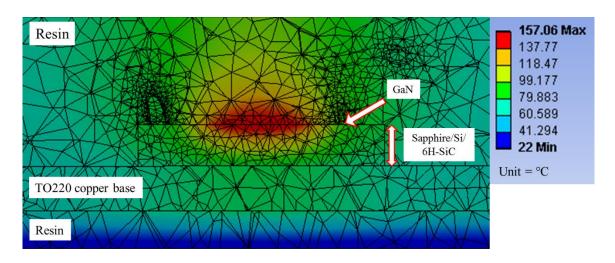

| Figure 5.14: Cross-sectional view of GaN on Sapphire (550µm) with thermal contour distribution.                                                               | 134        |

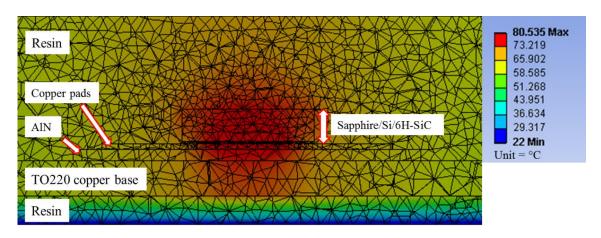

| Figure 5.15: Maximum junction temperature $(T_j)$ with respect to variation in substrate layer thicknesses for face up GaN                                    | 134        |

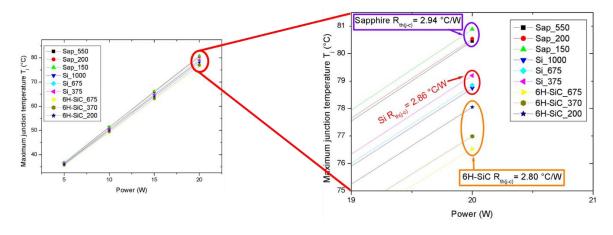

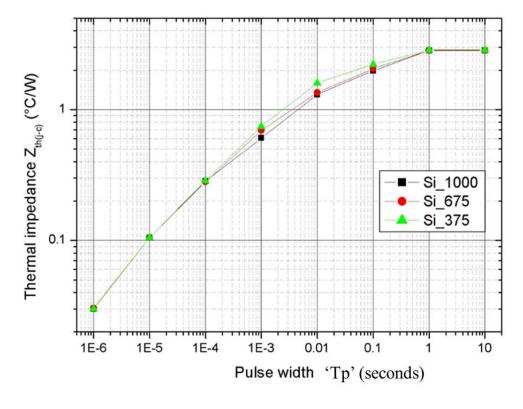

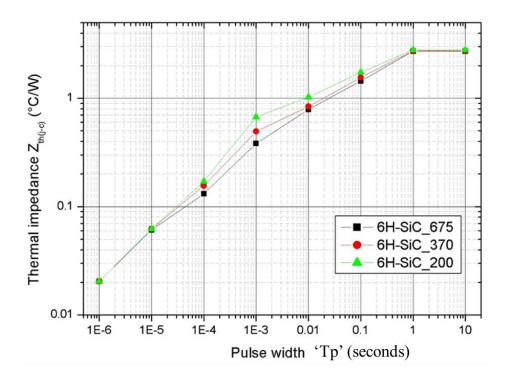

| Figure 5.16: Transient response for GaN on Sapphire substrates                                                                                                | 137        |

| Figure 5.17: Transient response for GaN on Silicon substrates                                                                                                 | 137        |

| Figure 5.18: Transient response for GaN on 6H-SiC substrates                                                                                                  | 138        |

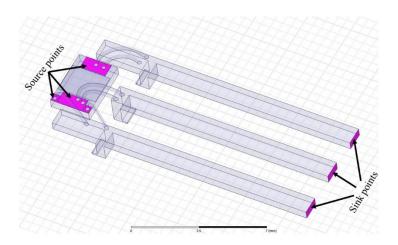

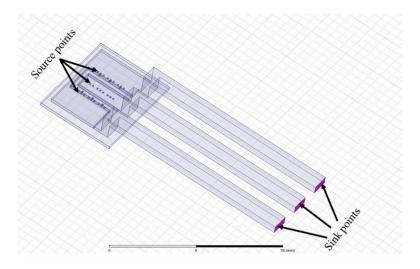

| Figure 5.19: 'Source' and 'sink' points used in Q3D for analysing the parasitic elements                                                                      | 139        |

| Figure 5.20: (a) Fabricated PN diode of GaN on SiC with multi finger design structure; (b) Image after flip chip process[10]                                  | 141        |

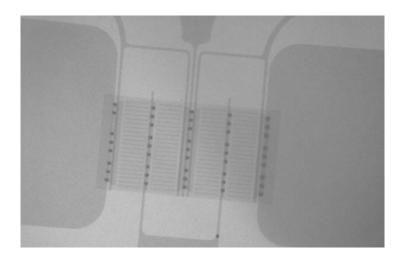

| Figure 5.21: X-ray image of flip chipped device                                                                                       | 141         |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------|

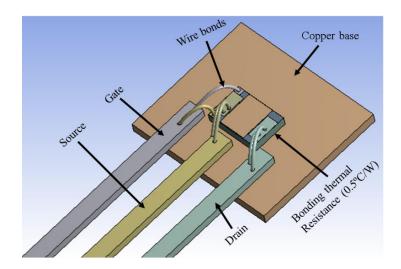

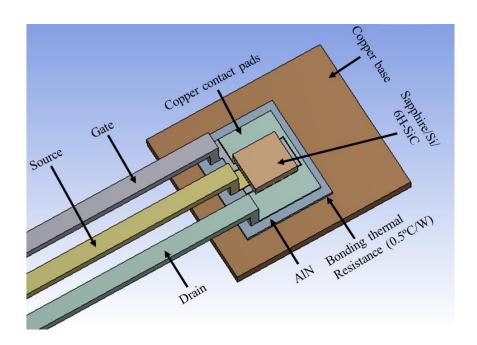

| Figure 5.22: Schematic 3D view of GaN flip chip structure                                                                             | 142         |

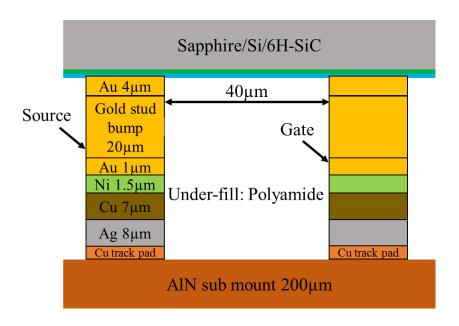

| Figure 5.23: Schematic cross-section of flip chip interconnection                                                                     | 143         |

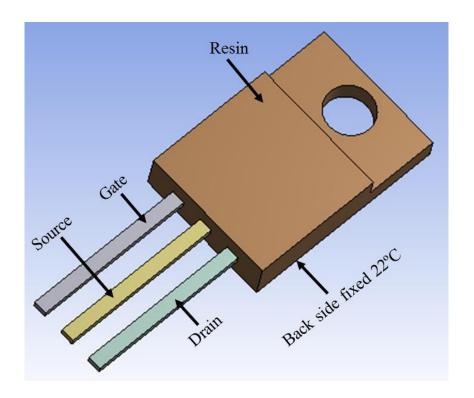

| Figure 5.24: 3D schematic view of GaN flip chip on TO-220 package without the epoxy resin                                             | 143         |

| Figure 5.25: 3D view of GaN on sapphire/silicon/6H-SiC with flip chip mounting in a T0-220 package system                             | 144         |

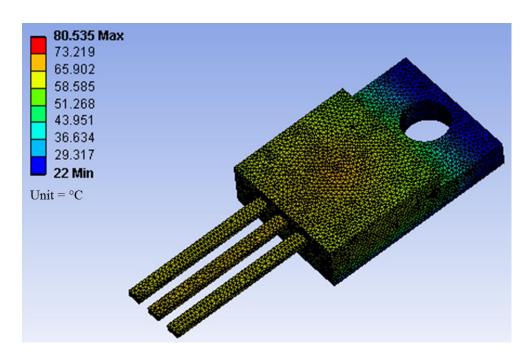

| Figure 5.26: 3D thermal contours for GaN on sapphire (550µm) in a T0-220 packag with a thermal loading of 20W                         |             |

| Figure 5.27: Detailed view representing hotspot region without the resin body                                                         | 146         |

| Figure 5.28: Cross-sectional view of GaN on Sapphire (550µm) with thermal contour distribution                                        | 147         |

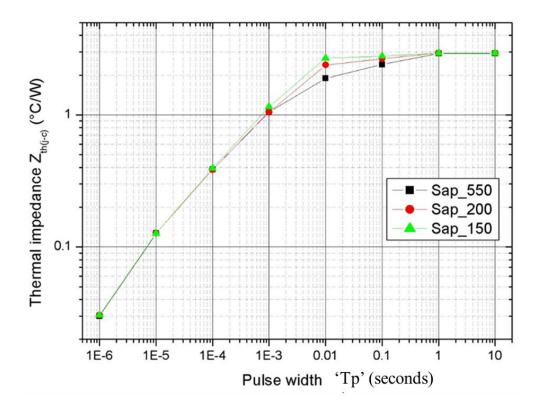

| Figure 5.29: Maximum junction temperature $(T_j)$ with respect to variation in substrate layer thicknesses for flip chip GaN          | 147         |

| Figure 5.30: Transient response for GaN on sapphire substrates                                                                        | 150         |

| Figure 5.31: Transient response for GaN on Si substrates                                                                              | 150         |

| Figure 5.32: Transient response for GaN on 6H-SiC substrates                                                                          | 151         |

| Figure 5.33: 'Source' and 'sink' points used in Q3D for analysing the parasitic elements                                              | 152         |

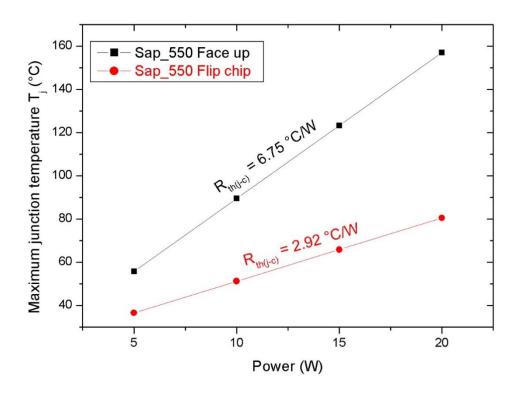

| Figure 5.34: Steady state thermal comparison of GaN on sapphire (550µm) for face up and flip chip mounted systems                     | 154         |

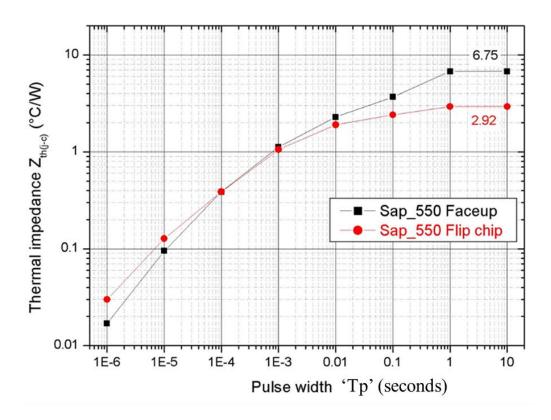

| Figure 5.35: Transient thermal impedance comparison of GaN on sapphire (550µm) up and flip chip mounted systems at 50% duty cycle     |             |

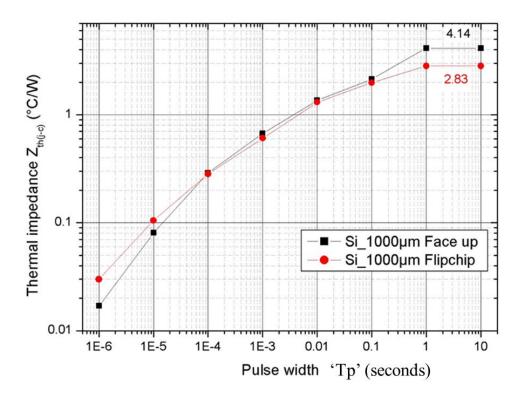

| Figure 5.36: Transient thermal impedance comparison of GaN on Si (1000µm) for f and flip chip mounted systems at 50% duty cycle       | _           |

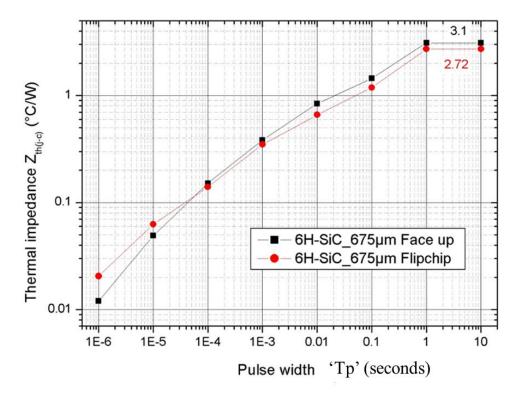

| Figure 5.37: Transient thermal impedance comparison of GaN on 6H-SiC (675 $\mu$ m) up and flip chip mounted systems at 50% duty cycle |             |

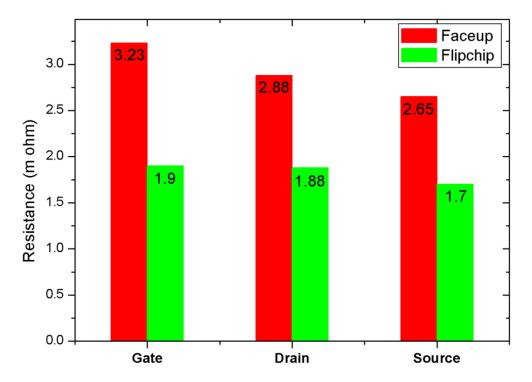

| Figure 5.38: Self-resistance parasitic comparison for face up and chip system observed at 500 kHz frequency                           | flip<br>158 |

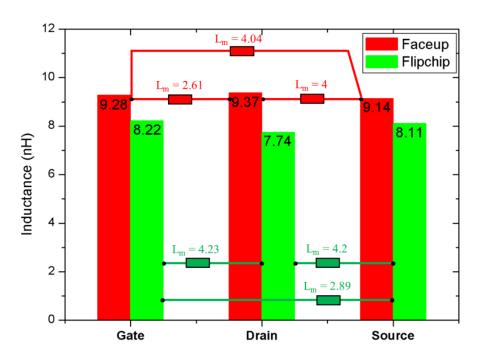

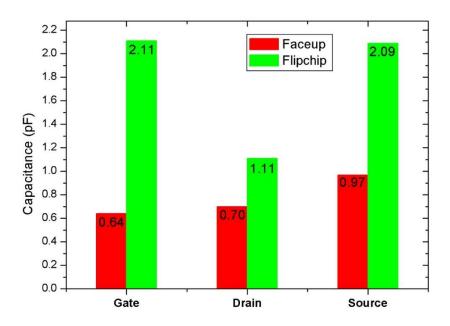

| Figure 5.39: Self/mutual parasitic inductance comparison for face up and chip system observed at 500 kHz frequency                    | flip<br>159 |

| Figure 5.40 : Self-capacitance for face up and flip chip mounted system at 500 kHz frequency                                          | 159         |

# LIST OF TABLES

| Table 1.1: Common materials used in packaging                                                                                     | 8   |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1: Summary of various interconnection medium                                                                              | 40  |

| Table 3.1: Mechanical and thermal properties of the common materials at 25°C used in power electronics packaging[5, 6, 8]         | 50  |

| Table 3.2: Summary of voids in solder and copper layers                                                                           | 67  |

| Table 3.3: Void thermal resistance in solder and copper layers                                                                    | 67  |

| Table 3.4: Measured and Simulated Thermal Resistance (junction – case) $R_{\text{th(j-c)}}$                                       | 69  |

| Table 3.5: Thermal stress and safety factor in silicon device mounted on polycrystalline diamond and aluminium nitride substrates | 74  |

| Table 3.6: Material Thicknesses for the polycrystalline diamond substrate                                                         | 81  |

| Table 3.7: Si-SnAG & SiC-Silver sintered paste comparison                                                                         | 83  |

| Table 3.8: Comparison of thermal stress and safety factors for Si - SnAg and SiC – silver sintered mounted over PCD substrates    | 85  |

| Table 4.1: Geometric parameters considered                                                                                        | 103 |

| Table 4.2: Thermo-hydraulic parameters                                                                                            | 105 |

| Table 4.3: Circular pin fin designs                                                                                               | 108 |

| Table 4.4: Circular and Cone shaped Micro pin fins for LIGA fabrication                                                           | 114 |

| Table 5.1: Material properties of Si, 4H-SiC & GaN[3]                                                                             | 122 |

| Table 5.2: Substrates thermal conductivity                                                                                        | 124 |

| Table 5.3: Substrate thicknesses                                                                                                  | 131 |

| Table 5.4: Thermal conductivity values at 25°C used in simulation                                                                 | 132 |

| Table 5.5: Thermal resistance junction to case at 20W power level for GaN devices mounted on a T0-220 package.                    | 135 |

| Table 5.6: Density and specific heat capacity values used in the simulation                                                       | 136 |

| Table 5.7: Thermal impedance junction to case for different substrates at 10 micro-second pulse width                             | 139 |

| Table 5.8: Self-resistance, inductance and capacitance                                                                            | 140 |

| Table 5.9: Mutual inductance and resistance                                                                                       | 140 |

| Table 5.10: Coupling Co-efficient 'k' between the leads                                                                           | 140 |

| Table 5.11: Thermal conductivity values at 25°C used in simulation                                                                | 145 |

| Table 5.12: Thermal resistance junction to case at 20W power level for GaN devices mounted on a T0-220 package.                   | 148 |

| Table 5.13: Density and specific heat capacity values used in the simulation                 | 149                     |

|----------------------------------------------------------------------------------------------|-------------------------|

| Table 5.14: Thermal impedance junction to case for substrates at 10 micro-second pulse width |                         |

| Table 5.15: Self-resistance, inductance and capacita                                         | nce153                  |

| Table 5.16: Mutual resistance and inductance                                                 |                         |

| Table 5.17: Coupling Co-efficient 'k' between the le                                         | eads153                 |

| Table 5.18: Comparison of flip chip and face up mo SiC substrates                            |                         |

| LIST OF ACR                                                                                  | ONYMS                   |

| Si                                                                                           | Silicon                 |

| SiC                                                                                          | Silicon carbide         |

| GaN                                                                                          | Gallium nitride         |

| Beo                                                                                          | Beryllium oxide         |

| AlN                                                                                          | Aluminium nitride       |

| PCD                                                                                          | Polycrystalline diamond |

| DBC                                                                                          | Direct Bonded Copper    |

| PGA                                                                                          | Pin grid array          |

| QFP                                                                                          | Quad flat pack          |

| SOT                                                                                          | Small outline package   |

| SnAg                                                                                         | Lead free solder        |

| $Al_2O_3$                                                                                    | Aluminium oxide         |

| MCM                                                                                          | Multichip modules       |

Figure of Merit

High Electron Mobility Transistor

Lithographie, Galvanik and Abformung

FOM

**HEMT**

LIGA

xvi

# **NOMENCLATURE**

| Symbol             | Definition                           | Unit           |

|--------------------|--------------------------------------|----------------|

| V                  | Voltage                              | (V)Volt        |

| I                  | Current                              | (A)Ampere      |

| R                  | Resistance                           | $(\Omega)$ Ohm |

| L                  | Inductance                           | (H)Henry       |

| С                  | Capacitance                          | (F)Farad       |

| $\Delta T$         | Temperature difference               | °C             |

| $P_D$              | Power dissipated                     | W              |

| $R_{th}$           | Thermal resistance                   | °C/W           |

| k                  | Thermal conductivity                 | W/mK           |

| A                  | Cross sectional area                 | $m^2$          |

| $C_{th}$           | Thermal capacitance                  | J/°C           |

| $c_p$              | Specific heat capacity               | J/Kg.K         |

| ho                 | Density                              |                |

| V                  | Volume                               | $m^3$          |

| $F_{sw}$           | Switching frequency                  | Hz             |

| $E_{on}$           | Turn on energy loss                  | J              |

| $E_{off}$          | Turn off energy loss                 |                |

| $A_c$              | Contact area m                       |                |

| $A_v$              | Void area m                          |                |

| $\alpha$           | Coefficient of thermal expansion     |                |

| $\sigma_e$         | Equivalent stress Pa                 |                |

| $\Delta arepsilon$ | Strain amplitude                     | -              |

| $arepsilon_f$      | Fracture strain                      | -              |

| C                  | Empirical fatigue ductility exponent | -              |

| $T_{j}$            | Junction temperature                 | °C             |

| $T_{c}$            | Case temperature                     | °C             |

| $R_{th(j-c)}$      | Thermal resistance junction to case  | °C/W           |

| $R_{th(c-HS)}$     | Thermal resistance case to heat sink | °C/W           |

| Symbol         | Definition                              | Unit     |

|----------------|-----------------------------------------|----------|

| $R_{th(Hs-a)}$ | Thermal resistance heat sink to ambient | °C/W     |

| $R_{th(j-a)}$  | Thermal resistance junction to ambient  | °C/W     |

| $Z_{th(j-c)}$  | Thermal impedance junction to case      | °C/W     |

| L              | Tile length                             | m        |

| b              | Tile breadth                            | m        |

| $W_L$          | Wetting area length                     | m        |

| $W_b$          | Wetting area breadth                    | m        |

| H              | Fin height                              | m        |

| D              | D Fin diameter                          |          |

| $\Delta P$     | $\Delta P$ Pressure drop                |          |

| $m_f$          | Mass flow rate                          | Kg/s     |

| $R_e$          | Reynolds number                         | -        |

| $\mu$          | Viscocity                               | Kg/(s.m) |

| $p_r$          | Prandtl number of water                 | -        |

| $p_{rs}$       | Prandtl number of air                   | -        |

| $k_{fluid}$    | Thermal conductivity of fluid           | W/mK     |

| $k_{fluid}$    | Thermal conductivity of fin             | W/mK     |

# **CHAPTER 1: INTRODUCTION**

#### 1.1 Introduction

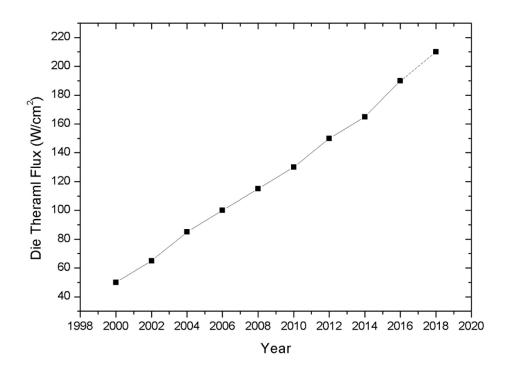

Power electronics is a continuously evolving and challenging field as power systems continue to demand increasing functionality within a decreasing packaging volume whilst maintaining stringent reliability requirements. This typically results in higher volumetric and power densities, which require effective thermal management solutions to maintain junction temperatures below their maximum rating. The thermal design of a semiconductor package depends upon the semiconductor die size, power dissipation, junction and ambient temperatures as well as cost constraints. The focus of semiconductor engineering to increase die current densities makes the thermal design more challenging due to its associated increase of heat flux[1]. Moreover, over the next decade, the advancements in the power density is expected because of the increase in power dissipation and reduction in the size, which is illustrated in Figure 1.1. The advancements in power density highlight the importance of thermal management solutions in determining the future semiconductor device technology.

Figure 1.1: Thermal flux trend[1]

#### 1.2 What is Thermal management?

The flow of electrical current through the leads and Silicon layers of a power semiconductor device, effects in substantial internal heat generation within an operating environment. The heat generated internally has to be removed appropriately using adequate cooling techniques. In the absence of cooling—the junction temperature of the semiconductor device would rise at

a constant rate to its maximum value at which semiconductor device fails catastrophically[2]. In order to maintain the junction temperature of the semiconductor device below its maximum allowable limit, the device should be placed in contact with a medium at a lower temperature, which assists heat flow away from the device as heat flows from a hot to a cold medium. Due to the cooling effect, the junction temperature rise is restrained as it approaches thermal equilibrium. Under steady-state conditions, all the heat generated by the component is transferred to the ambient. Thus by implementing forced cooling technique, such as liquid cooling or forced impingement cooling instead of natural convection, the junction temperature rise above the ambient can be reduced. Conduction, convection and radiation are the three modes of heat transfer which plays a vital role in electronics cooling. Effective power semiconductor thermal packaging relies on careful combination of materials and heat transfer mechanisms to maintain the device junction temperature well below its maximum limit.

#### 1.3 Why Thermal management?

Advancement in the field of power electronics has led to substantial increase in power density integration and reduction in component size. This leads to high heat flux dissipation at the chip level. In order to keep the junction temperature well below the maximum allowable limit with respect to device performance and reliability, enhancements in cooling techniques are required; therefore thermal management solutions are increasingly important in determining the future of the power electronics industry. The significant challenge lies in maintaining the junction temperature below the maximum allowable limit by dissipating the heat flux from the power semiconductor device. The key factors influencing the thermal design of the system are chip size, power dissipation, material layer properties, junction temperature and ambient temperature. Power semiconductor manufacturers aim at reducing the chip size over the years which in turn increases the thermal design challenges, due to the increased levels of heat flux. The growth in power density is estimated to increase significantly over the next few decades due to smaller chip size and high power dissipation. The increasing power density and challenges in thermal design indicates the need for thermal management and its significance in determining the future of power semiconductor devices[3].

#### 1.4 Electrical and thermal parameters

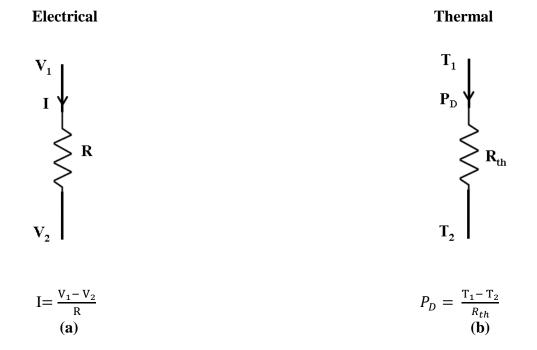

A correlation between the electrical and thermal parameters is shown in Figure 1.2[4]. In the electrical domain, according to Ohm's law, a linear relationship exist between current flowing through a resistor causing a voltage drop across it.

$$V = I.R \tag{1.1}$$

In the thermal domain, the voltage and current relationship is defined as the temperature difference is equal to product of the power dissipated and the thermal resistance of the object.

$$\Delta T = P_D. R_{th} \tag{1.2}$$

Where, electrical resistance in electrical domain corresponds to thermal resistance in thermal domain. Current (I) in electrical domain corresponds to power dissipated ( $P_D$ ) in thermal domain, while voltage difference in electrical domain corresponds to temperature difference ( $\Delta T$ ) in thermal domain as described in Figure 1.2.

Figure 1.2: Electrical and thermal domain (a) Electrical and (b) Thermal domain

#### 1.5 Heat transfer modes

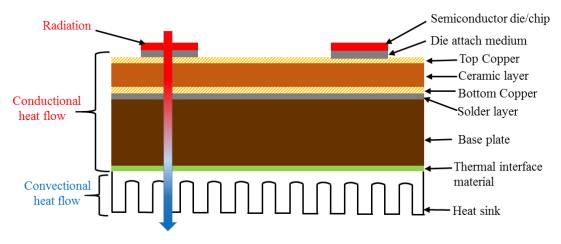

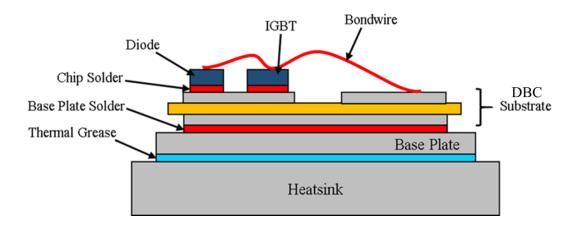

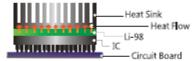

Heat transfer in a power module occurs in three modes conduction, convection and radiation[5]. Figure 1.3 shows the cross sectional heat transfer path for a convectional wire bonded power module. Radiative heat transfer occurs in the active region of the semiconductor die due to power dissipation. Whereas, conductional heat transfer occurs in the board level mainly through the die attach medium, DBC substrate, base plate and thermal interface material. Convectional heat transfer occurs in the heat sink level either through natural or forced convection.

Figure 1.3: Heat flow in a wire bonded power module

#### 1.5.1 Radiation

Radiative heat transfer is due to the electromagnetic waves propagating through empty space. Heat radiation occurs in all bodies when the temperature reaches above absolute zero. Radiation in the power semiconductor devices is due to the movement of electrons in the atom which are observed as electromagnetic radiation. The radiated electromagnetic waves transmit heat energy away from the active area of the semiconductor die. Equation (1.3) describes the radiative heat transfer.

$$P_r = \sigma \cdot \varepsilon \cdot A \cdot (T_1 - T_2) \tag{1.3}$$

Where,  $\sigma$ ,  $\epsilon$ , A and T are the Stefan-Boltzman constant (5.66x10<sup>-8</sup> W/m<sup>2</sup>K<sup>4</sup>), emissivity, surface area of the body and temperature difference respectively.

#### 1.5.2 Conduction

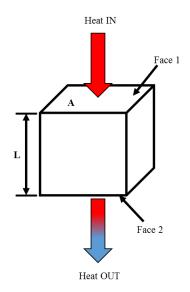

Conduction heat transfer occurs due to temperature gradient in a body. Heat energy is transferred from a hot surface to a cold surface, the conductional heat flow can be represented as one dimensional heat flow as shown in Figure 1.4. Heat flows into Face1 and out from Face 2, assuming no heat loss distributed through sides of the object. According to the one-dimensional thermal conduction equation, when the two faces are held at identical temperature, temperature of the object mainly depends on the distance (L) between the Face 1 and Face 2 and its thermal conductivity.

Figure 1.4: Conductional heat flow in a body

Heat transfer rate by conduction through the object in Figure 1.4 can be expressed as,

$$\frac{Q}{t} = \frac{kA}{L} \Delta T_{12} \tag{1.4}$$

Where,

A - Cross-sectional area of the object

L – Wall thickness

$\Delta T_{12}$  – Temperature difference between two surfaces ( $\Delta T_{12} = T_1 - T_2$ )

k – Thermal conductivity of the material (W/mK)

The thermal resistance for conductional heat flow depends upon the thermal conductivity of the material, material thickness and area. Theoretically the thermal resistance for conductional heat flow can be represented using equation (1.5).

$$R_{Conduction} = \frac{L}{kA} \tag{1.5}$$

Where L , k and A are the thickness of the material, thermal conductivity and cross sectional area respectively. Thermal resistance can be decreased by either increasing the cross sectional area, thermal conductivity or decreasing the thickness of the material. Table 1.1 compares the thermal conductivity of the common materials at 25°C used in electronics packaging.

Table 1.1: Common materials used in packaging

| Material                   | Thermal conductivity 'k' (W/mK) at 25°C |

|----------------------------|-----------------------------------------|

| Si                         | 140                                     |

| SiC                        | 360                                     |

| Solder (SnAg)              | 57                                      |

| Silver thin film sintering | 200                                     |

| Copper                     | 390                                     |

| BeO                        | 300                                     |

| Alumina                    | 35                                      |

| AlN                        | 170                                     |

The thermal resistance for conductional heat flow can be calculated using equation (1.6), the ratio of the temperature difference to the corresponding power dissipation.

$$R_{Conduction} = \frac{T_1 - T_2}{P_d} \tag{1.6}$$

Where  $P_d$  is power dissipation and  $T_1$  -  $T_2$  are temperature difference between the two surfaces.

#### 1.5.3 Convection

Convectional flow is due to the transfer of heat energy in ambient temperature via air or liquid mediums. Convectional heat transfer can be classified into natural convection and forced convection; natural convection occurs due to buoyancy force arising from density differences caused by temperature variations in the fluids. Natural convection does not require any external source like a pump or fan to push the air or fluid through it. Forced convection occurs due to the air/fluid motion generated due to external medium like a fan or pump as shown in Figure 1.5. A significant amount of heat energy can be transported efficiently using forced convection. Convectional heat transfer occurs at the system level in which the heat from the power device through different thermal layers is transported to the ambient effectively through air cooled or liquid cooled heatsinks.

Figure 1.5:Convectional heat flow (a) Natural convection; (b) Forced convection[5]

#### 1.6 Thermal Modelling Techniques

Power electronics design involves careful consideration of the electrical and thermal domains. For instance, overdesigning the system will increase the cost and weight whereas, under designing the system may cause early failure of the power electronic components. An optimised design solution is therefore essential for perfect operation of power electronic components, which involves a good understanding and accurate prediction of semiconductor die junction temperatures and transferring the heat efficiently to the ambient. No sole thermal analysis tool works best in all circumstances[6]. A good thermal evaluation requires a combination of empirical calculations based upon thermal specifications and thermal modelling. The art of thermal analysis involves utilising one or more existing thermal tools to validate each other. Some of the existing thermal models available and widely used are

- Electro-thermal modelling

- Finite element analysis

#### 1.6.1 Electro-thermal modelling

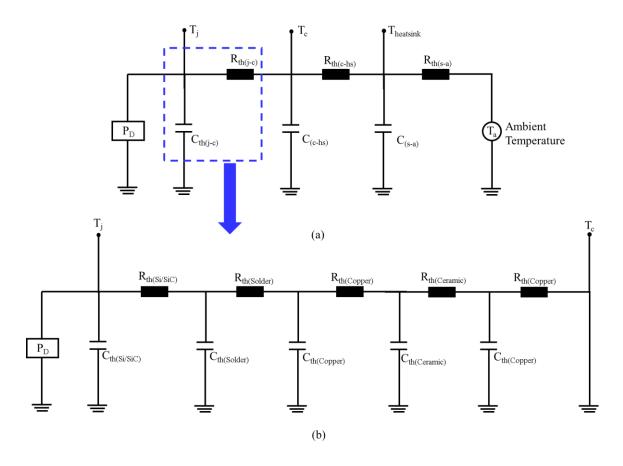

Physics based electro-thermal modelling would provide a more theoretical representation of thermal behaviour. Thermal model uses the material properties of the thermal layers to determine the thermal behaviour of the system. Commonly used electro thermal models are Cauer and Foster networks.

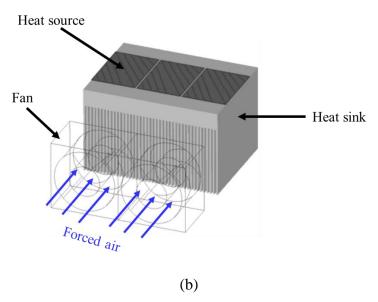

#### 1.6.1.1 Foster thermal network

Figure 1.6 shows the Foster thermal network with parallel R/C pairs connected in a series sequence for a single chip module. The RC parameters are extrapolated from the measured thermal impedance data using curve fitting methods to determine the finite exponential terms (1.7) [7]

$$Z_{th} = \sum_{i=1}^{n} R_i \left( 1 - e^{-\frac{t}{\tau_i}} \right)$$

(1.7)

Where *i* is the index term,  $R_i$  and  $\tau_i$  represent thermal resistance and time constant respectively. Thermal capacitance  $C_i$  can be calculated from equation (1.8)

$$\tau_i = R_i C_i \tag{1.8}$$

Time constant  $\tau_i$  and thermal resistance  $R_i$  values are generally provided by manufacturer data sheets which eases in calculating the remaining index term and thermal capacitance  $C_i$ . The main advantage of Foster model is it provides a quick and easier estimation of thermal resistances and capacitances for each index terms respectively. On the other hand, the disadvantages of the Foster thermal network is that it represents only the behaviour characteristics of the model, and is not associate with the physical parameters of the thermal layer materials and geometries involved. Moreover, the Foster network does not relate to physical thermal response of the overall system where the heat flow from junction to case are governed by the heat capacity and thermal resistance of various layers which accounts thermal delays in the system. With the transient curve representing junction temperature against time, exponential terms comprising of a time constant and amplitudes could be fit to the transient curve to represent the Foster RC model.

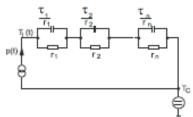

Figure 1.6: Foster thermal network of a single chip module

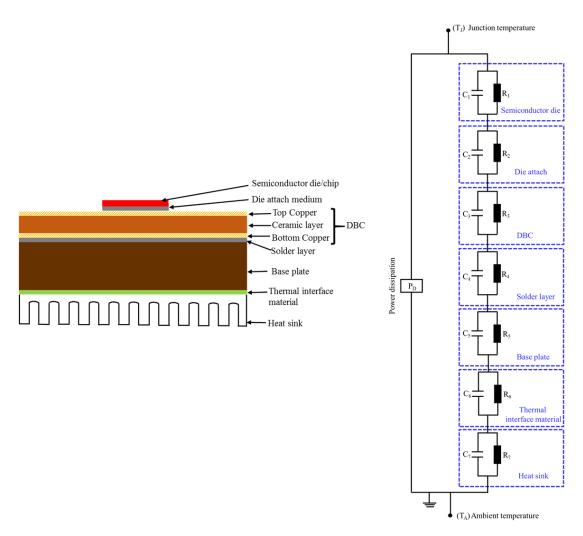

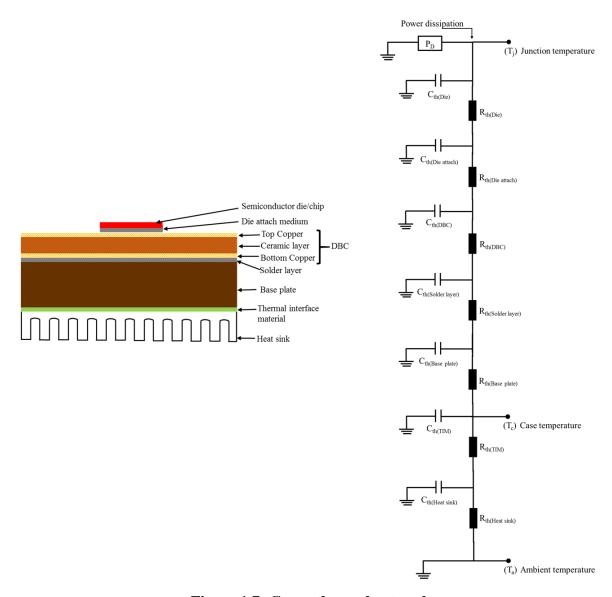

#### 1.6.1.2 Cauer thermal network

Cauer thermal network utilises thermal capacitors connected to a thermal ground, referred at absolute zero, allowing the network to store heat energy. The Cauer thermal network provides more realistic physical representation of the system transient behaviour by accounting for time delays using material properties[7]. Figure 1.7 shows the Cauer thermal network with thermal resistance and capacitance path for a single chip module. Thermal resistance and capacitance values for each node or layers can be obtained from the geometric and its material parameters such as thermal conductivity, density and specific heat capacity values[7].

Figure 1.7: Cauer thermal network

This approach of thermal modelling provides accurate simulations as it utilises material layer properties unlike the Foster thermal model. Thermal resistance is calculated as shown in equation (1.5), whereas thermal capacitance is calculated using equation (1.9) where  $c_p$ ,  $\rho$  & V are specific heat capacity, density and volume of each layer.

$$C = c_p. \rho. V \tag{1.9}$$

#### 1.6.1.3 Comparison between Foster and Cauer thermal network

Cauer thermal network provides a physical representation of the system; However, to utilise the best of the Cauer thermal model circuit certain simulation tools are required. When Cauer thermal network is used along with the circuit simulation tools for thermal calculation, it provides accurate results for any complex thermal model with time varying, multiple heat sources with arbitrary power inputs. Foster network is mathematically easier to perform thermal calculations. Even though only junction temperature has physical representativeness in the Foster network, if transient response curves are measured under certain ambient environmental conditions, then it could be transferred onto Foster model to predict the temperatures under varying power level. Even complex thermal models can be constructed using Foster model. Cauer thermal network does not require measured data to calculate the thermal resistance of the system as it uses material layer properties. Whereas, Foster network require measured data and it does not interpret the layer material properties for calculating the thermal resistance.

#### 1.6.2 Finite element analysis

The finite element method (FEM) is a numerical technique for finding approximate solutions to boundary value problems for partial differential equations. It is also referred to as finite element analysis (FEA). It subdivides a large problem into smaller, simpler parts that are called finite elements. The simple equations that model these finite elements are then assembled into a larger system of equations that models the entire problem. Three dimensional (3D) approach in finite element analysis predicts more accurate results close to the experimental values. Finite element analysis involves dividing a body or a system into smaller elements allowing equations governing the system physics to be solved. The biggest challenge in using the FEM thermal simulation tools lies in constructing appropriate geometry and finding thermal parameters to predict results accurately. Thermal parameters required for the simulations are Density, Specific Heat Capacity and Thermal conductivity. These parameters are temperature dependent and it exhibits significant variation over temperature ranges from 25°C to 250°C and it's important to include these parameters for predicting accurate results[8]. Advantages of FEM thermal simulation tool are summarised below,

- 3D finite element analysis provides a three dimensional thermal approach in solving thermal models unlike, Cauer or Foster thermal model which uses one dimensional thermal approach.

- Complex thermal model with multiple heat sources are easy to be modelled using finite element analysis.

- Temperature dependent parameters such as density, specific heat capacity and thermal conductivity can be used with the thermal modelling simulation in a tabular form for varying temperature ranges.

Thermal contours and temperature distributions results with hotspots can be performed

using finite element modelling and moreover, temperature differences between each

individual thermal layers can be identified using temperature probes for thermal

calculations.

#### 1.7 Reliability

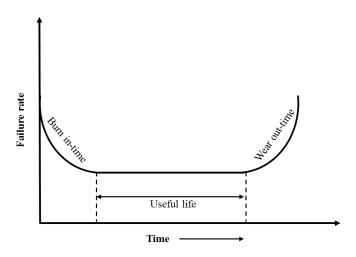

The main aim of thermal management in power electronics packaging is to ensure the reliability of a system. Reliability can be defined as a probability measurement of adequate system performance, in which the system must function without failure when subjected to certain operating conditions. The reliability of power electronics devices is widely characterised using a bath-tub curve[1] with three distinct phases as shown in Figure 1.8. The first phase in a bath-tub curve corresponds to burn in-time phase in which the failures are caused due to the component malfunction, manufacturing defects, etc.

Figure 1.8: Bath tub curve[1]

The subsequent phase is the useful life or normal life period since the failure rate throughout this phase is much lower compared to the infant mortality. Wear-out time period is the final phase in which the failure rate is higher due to aging and fatigue of the components.

#### 1.7.1 Failure mode

The main failure rate in electronics are due to overheating[9], occurring when the electronic component is operated constantly above the maximum junction temperature limit. Device junction temperature has high influence on the reliability and semiconductor device operation[1]. The materials with different co-efficient of thermal expansions are bonded together in electronic packages, they expand with respect to temperature variation and result in

thermal strain and stress between the layers. The induced thermo-mechanical stress leads to failure of the electronic component; wire bond lift off and solder layer degradation, crack generation and propagation are some of the common thermo- mechanical failures[10-12].

#### 1.8 Semiconductor Power loss

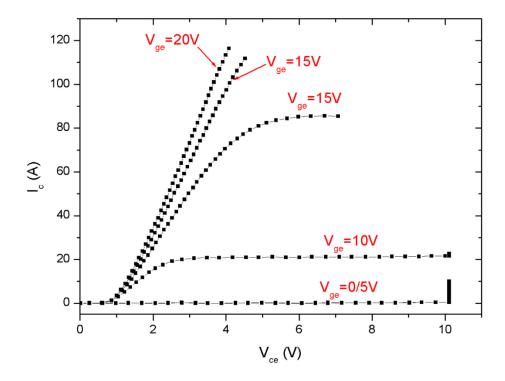

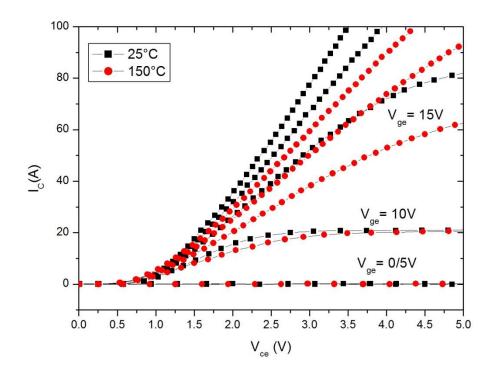

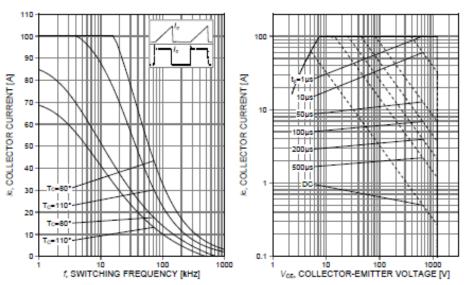

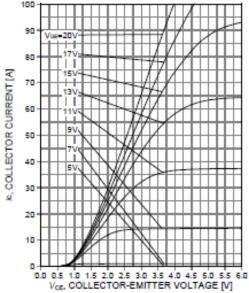

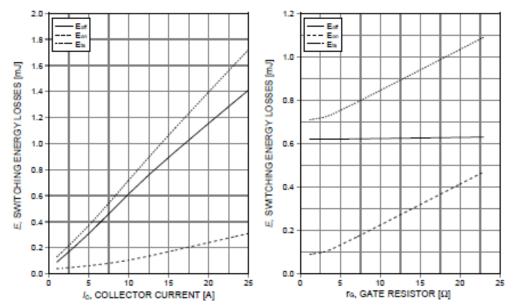

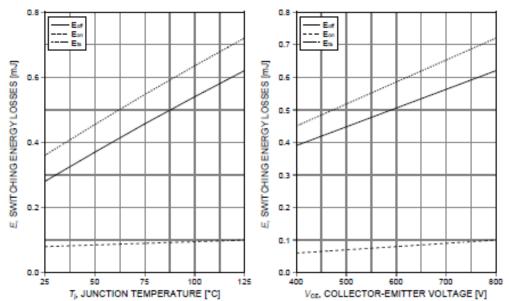

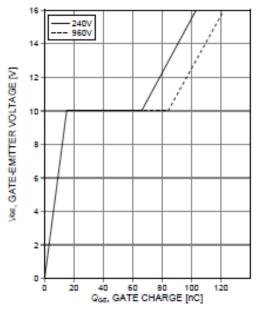

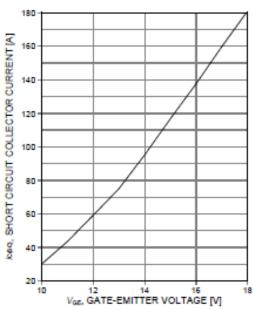

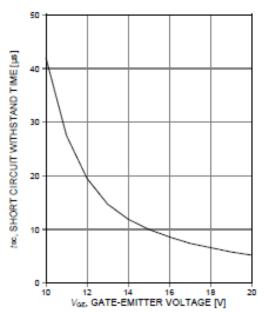

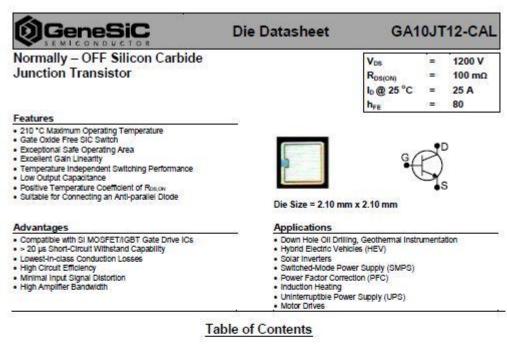

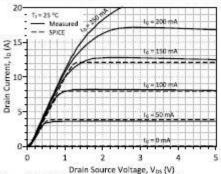

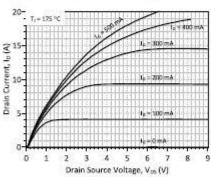

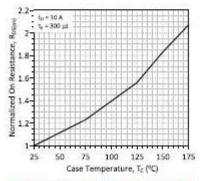

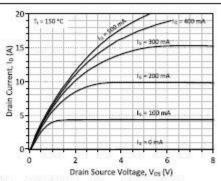

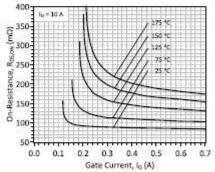

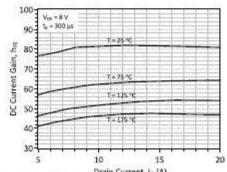

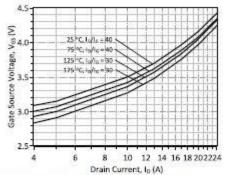

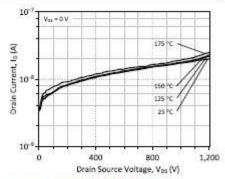

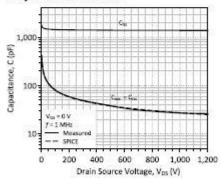

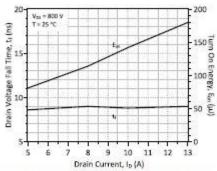

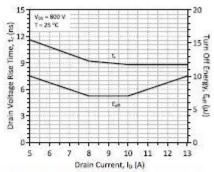

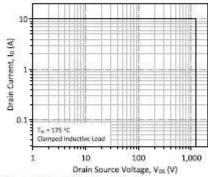

Ideal power semiconductor switch should turn on and off instantly, should have infinite impedance in the off state and exhibit zero resistance whilst operating in the on state. However, these ideal characteristic are not achievable in semiconductor devices. The semiconductor power loss can be divided into three sections conduction loss, switching (Turn ON and Turn OFF) loss and off state loss. When the semiconductor switch is turned off the off state losses are very low due to the negligible small leakage current and is generally neglected under normal operating temperature conditions. Conduction loss occur when the semiconductor device is fully turned on, Figure 1.9 shows the IV characteristic of an 25A 1200V IGBT[13] (see Appendix 1). The conduction loss is calculated using (1.10)

$$P_{conduction} = V_{ce} \times I_c$$

(1.10)

Where, V<sub>ce</sub> is corresponding onstate voltage drop and I<sub>c</sub> is the collector current.

Figure 1.9: IGBT I-V characteristics

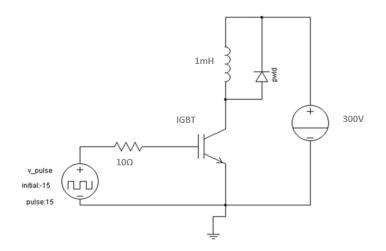

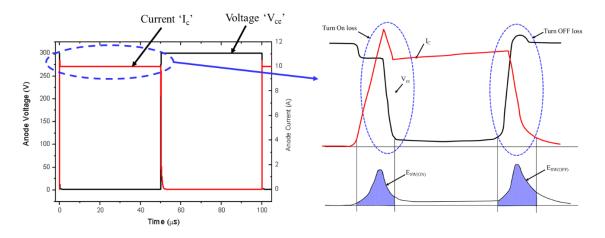

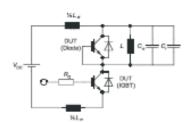

Figure 1.9 represents I-V characteristic of IGBT power semiconductor switch representing the voltage and current relationship during the ON state of the semiconductor switch. Power dissipation during conduction mode is calculated by multiplying the on-state voltage ( $V_{ce}$ ) to its corresponding on-state current. Switching losses occur during the turn on and turn off switching events. In order to examine the switching and conduction losses in a semiconductor die, a DC-DC converter with IGBT as switching device is considered. Figure 1.10 shows a DC-DC converter operating at 50% duty cycle, the corresponding voltage and current wave form during turn on and turn off are illustrated in Figure 1.11. Red line indicates the current wave form and black line indicates the voltage of an IGBT.

Figure 1.10: DC-DC converter

Figure 1.11: Voltage and current waveforms of IGBT

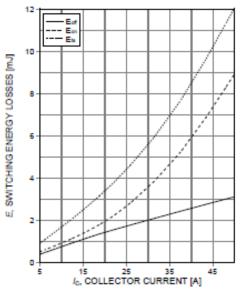

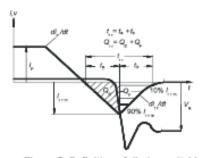

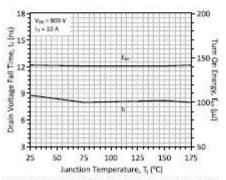

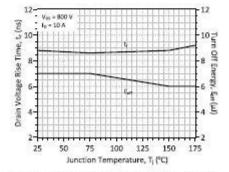

Switching losses are further classified into turn on and turn off losses and they are represented in terms of turn on energy loss  $(E_{on})$  and turn off energy loss  $(E_{off})$  which is represented as power loss integrated over a switching time. Turn on losses occur when the semiconductor

device is switched from its OFF state to ON state. Whereas, the turn off loss occur when the semiconductor devices is switched from its ON state to OFF state. Switching losses are frequency dependent. When the current and voltage are constant the  $E_{sw(ON)}$  and  $E_{sw(OFF)}$  are identical for each turn on and turn off event, the average switching loss can be calculated by summing the  $E_{sw(ON)}$  and  $E_{sw(OFF)}$  and multiplying it over the frequency as shown in equation (1.11)

$$P_{SW} = F_{sw}(E_{sw(ON)} + E_{sw(OFF)})$$

(1.11)

Where, Fsw is the switching frequency; total power loss is the sum of conduction loss and switching loss times the percentage of duty cycle.

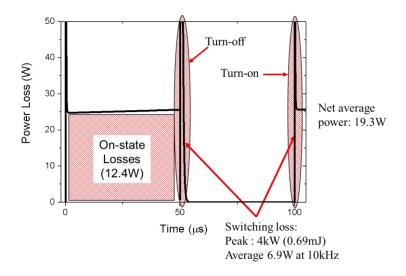

Figure 1.12: Instantaneous power loss per cycle

Figure 1.12 shows the instantaneous power loss per cycle at 10kHz switching frequency for a DC-DC convertor using an IGBT device as depicted in Figure 1.10, these power loss are observed as thermal energy and they must be dissipated whilst maintain the junction temperature below its maximum value.

# 1.9 Thermal energy and power density

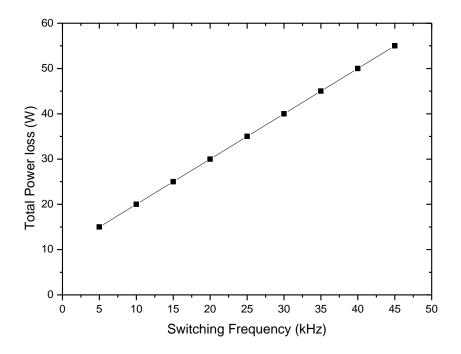

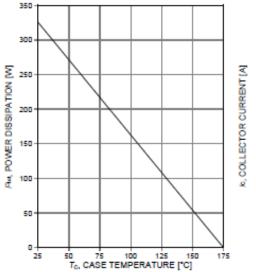

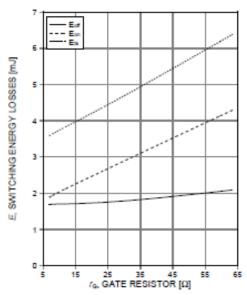

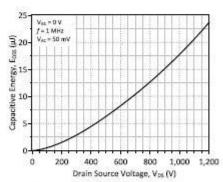

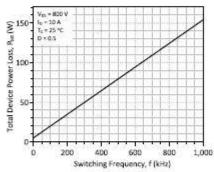

The power loss from the semiconductor die are observed as thermal energy. Power density is directly influenced by the power loss, for example, considering an 25A 1200V IGBT[14](see Appendix 2) the total power loss at different switching frequency is shown in Figure 1.13 for a DC-DC converter at a fixed duty cycle.

Figure 1.13: Switching power loss

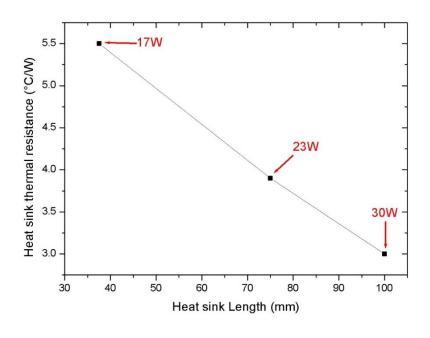

The power loss increases with switching frequency. The required heat sink thermal resistance at power losses of 17, 23 and 30W were calculated using equation (1.6) for worst case condition with maximum junction temperature  $(T_j)$  150°C and a 60° ambient temperature  $(T_a)$ . Figure 1.14 shows the calculated heat sink thermal resistance and the corresponding heatsink length. The heat sink thermal resistance required decreases with increase in power loss whereas, the heat sink size increases with power loss.

Figure 1.14: Heat sink thermal resistance and heat sink length

#### 1.10 Thesis structure

This thesis addresses the thermal management and reliability concerns of power semiconductor device technologies like Silicon and wide band gap semiconductors (SiC and GaN) right from die level to system level packaging designs for discrete and power module packages. The evolution of electronics packaging with different mounting and interconnect techniques available for conventional for discrete and power module packaging are summarised and discussed in Chapter 2. Moreover, summary of different interconnect technologies with its advantages and disadvantages are also detailed. Comparison of thermal performance of Silicon and Silicon Carbide power semiconductor dies mounted on Polycrystalline Diamond (PCD) and Aluminum Nitride (AlN) substrates for a traditional wire bond are shown. Detailed simulation and experimental analysis techniques were performed to measure the junction to case thermal resistance (Rth (i-c)) under steady state and transient conditions. The thermomechanical reliability of PCD and AlN substrates were analysed using thermal cycling test using ANSYS structural tool to examine the stress, strain, safety factor and life cycle fatigue. The thermal performance of PCD substrates were further analysed for next generation semiconductor technologies and silver sintering die attach. Polycrystalline diamond has shown improved thermal performance over the conventional insulators in DBC substrates from Chapter 3. Thermal performance of PCD insulator on DBC substrate was further enhanced by using direct liquid cooling technique, micro fins were embedded on to the bottom copper of the DBC substrate with PCD as ceramic layer. This reduces the number of thermal layers in the system compared to the conventional one and in turn increase the thermal performance of the overall system. Moreover, the high thermal conductivity of PCD can be utilised efficiently by using direct cooling technique. An Empirical model was used to analyse the thermal performance of micro pin fins geometries and thermo-hydraulic parameters were varied accordingly to find the optimal circular micro pin fin diameter and length. Thermal management and packaging solutions for the next generation wide band gap semiconductors such as GaN is described in Chapter 5. Comparison of face up and flip chip thermal performance of GaN on Sapphire, Silicon and 6H-SiC substrates in a T0-220 package system is presented. Detailed thermal simulation results were analysed using ANSYS® thermal tool moreover, the effect of package parasitic for flip chip and face up mounted on T0-220 package were observed. Finally, a summary of all chapters with concluding remarks and suggestion for future work are described in Chapter 6.

#### References

- [1] Fundamentals of Microsystems Packaging: Mcgraw-hill, 2001.

- [2] U. S. Government, Thermal Management of Power Semiconductor Packages-Matching Cooling Technologies with Packaging Technologies: IMAPS 2nd Advanced Technology Workshop: General Books LLC, 2012.

- [3] M. Ohadi and Q. Jianwei, "Thermal management of harsh-environment electronics," in *Semiconductor Thermal Measurement and Management Symposium*, 2004. Twentieth Annual IEEE, 2004, pp. 231-240.

- [4] Y. Liu, Power Electronic Packaging: Design, Assembly Process, Reliability and Modeling: Springer New York, 2012.

- [5] J. P. Holman, *Heat Transfer: J. P. Holman*: McGraw Hill, 1963.

- [6] D. Lemonnier and J. B. Saulnier, Advanced Concepts and Techniques in Thermal Modelling: Proceedings of the Eurotherm Seminar 36, September 21-23, 1994, Poitiers, France: Elsevier, 1996.

- [7] J. Altet and A. Rubio, *Thermal Testing of Integrated Circuits*: Springer US, 2013.

- [8] X. Chen and Y. Liu, *Finite Element Modeling and Simulation with ANSYS Workbench*: Taylor & Francis, 2014.

- [9] M. Ciappa and W. Fichtner, "Lifetime prediction of IGBT modules for traction applications," in *Reliability Physics Symposium*, 2000. Proceedings. 38th Annual 2000 IEEE International, 2000, pp. 210-216.

- [10] H. Jun, V. Mehrotra, and M. C. Shaw, "Thermal design and measurements of IGBT power modules: transient and steady state," in *Industry Applications Conference*, 1999. Thirty-Fourth IAS Annual Meeting. Conference Record of the 1999 IEEE, 1999, pp. 1440-1444 vol.2.

- [11] M. Musallam, C. M. Johnson, C. Yin, H. Lu, and C. Bailey, "Real-time life expectancy estimation in power modules," in 2008 2nd Electronics System-Integration Technology Conference, 2008, pp. 231-236.

- [12] W. S. Loh, M. Corfield, H. Lu, S. Hogg, T. Tilford, and C. M. Johnson, "Wire Bond Reliability for Power Electronic Modules Effect of Bonding Temperature," in 2007 International Conference on Thermal, Mechanical and Multi-Physics Simulation Experiments in Microelectronics and Micro-Systems. EuroSime 2007, 2007, pp. 1-6.

- [13] InfineonTechnologies, "Infineon's IGBT4 Low Power Chip," IGC27T120T6L datasheet, 2007.

- [14] InfenionTechnologies, "Infineon's TRENCHSTOP IGBT technology," IGW25N120H3 datasheet, Dec.2003.

| <b>CHAPTER</b> | 2. | SEMI      | CONDIT | CTOR P | ACKA | GING |

|----------------|----|-----------|--------|--------|------|------|

| CHALLEN        | 4. | TAINIAI I |        |        |      |      |

#### 2.1 Introduction

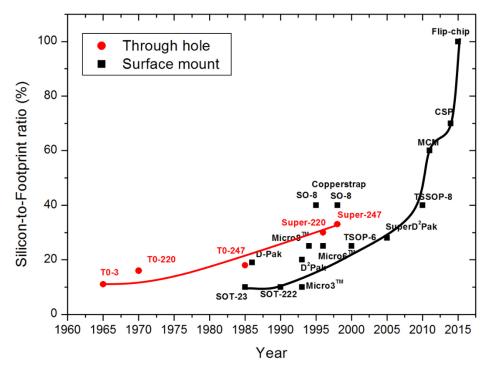

Essentially, power electronics packages deliver device protection, mechanical support, cooling, electrical connection and electrical isolation for electronic components. Packaging technology is an important field next to power devices in determining the overall performance of single chip or multichip power packages. Power-semiconductor manufacturers have been focusing on electronic power conversion research effort by moving towards high-frequency operation, which results in improved converter performance, higher power density and decrease of system weight and cost. This typically results in pushing the limits of present packaging technologies, which in turn indicates packaging as the dominant technology limiting the rapid growth of power electronics applications. The main drives for semiconductor development are on-state resistance reduction, miniaturisation of semiconductor die, increased thermal performance and thermo-mechanical reliability. Power density can be identified in terms of Silicon to foot print ratio[1], which is semiconductor die (Silicon) divided by total foot print ratio.

In this chapter an overview of the evolution of semiconductor packaging with different mounting and interconnect technologies are discussed. Further, the advantages and disadvantages of various mounting and interconnect technologies are analysed and discussed.

# 2.2 Single chip/Discrete packages:

Through hole and surface mount packages are the two main classifications of discrete power semiconductor packaging. Some of the through-hole packages available commercially are:

- Dual-In-Line Package

- Transistor Outline Package (T0)

- Pin Grid Array (PGA)

Whereas, surface mount packages are:

- Small Outline Package

- Quad Flat pack (QFP)

- Small Outline Transistor (SOT)

- Plastic Leaded Chip Carrier (PLCC)

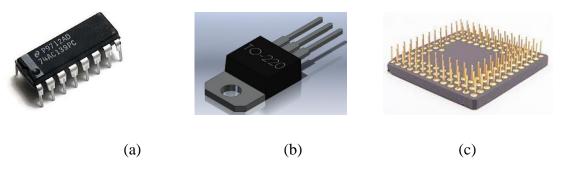

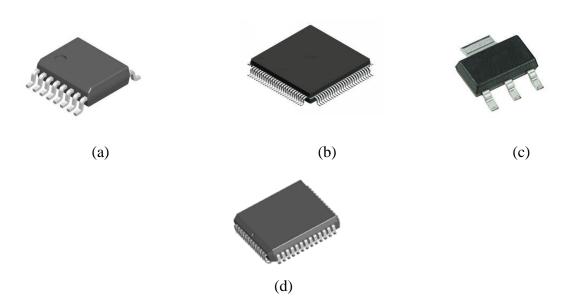

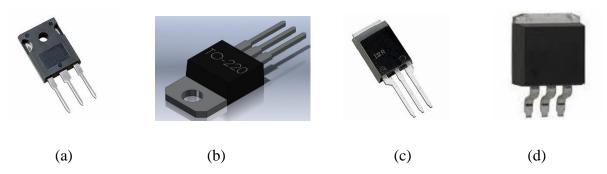

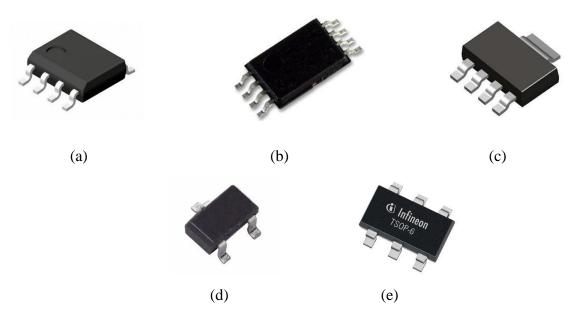

Figure 2.1 shows a selection of through-hole packages whereas, Figure 2.2 shows surface mount packages for power devices.

Figure 2.1: Through hole power packages[2] (a) Dual inline package (b) Transistor outline T0-220 (c) Pin grid array

Figure 2.2: Surface mount packages[2] (a) Small Outline Package; (b) Quad flat pack (QFP); (c) small outline transistor (SOT); (d) Plastic leaded chip carrier (PLCC)

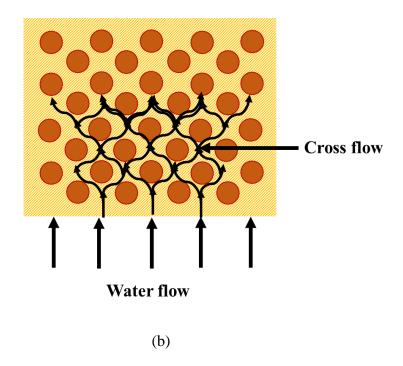

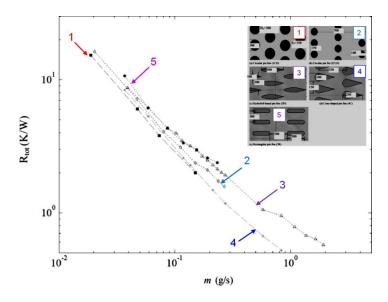

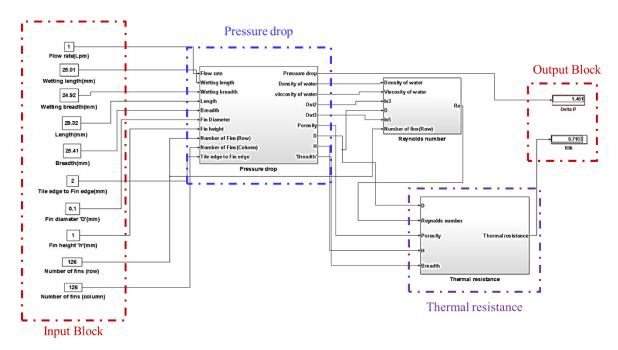

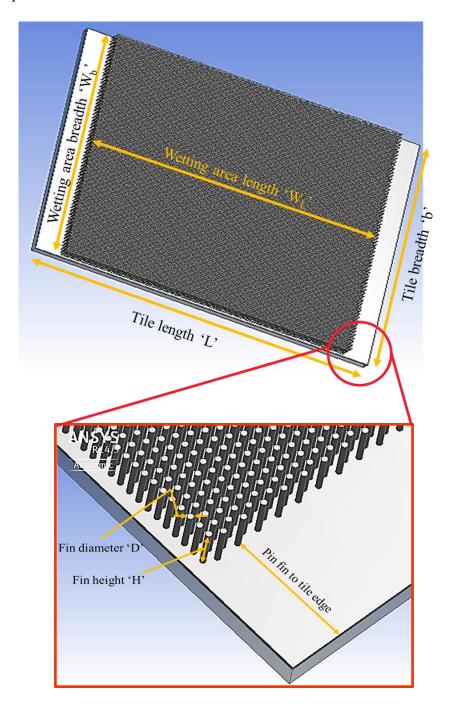

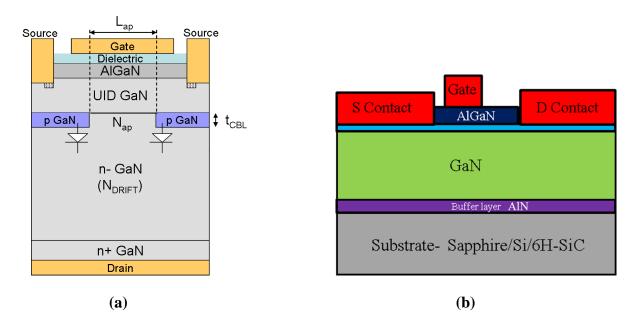

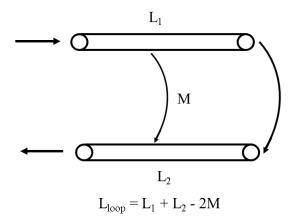

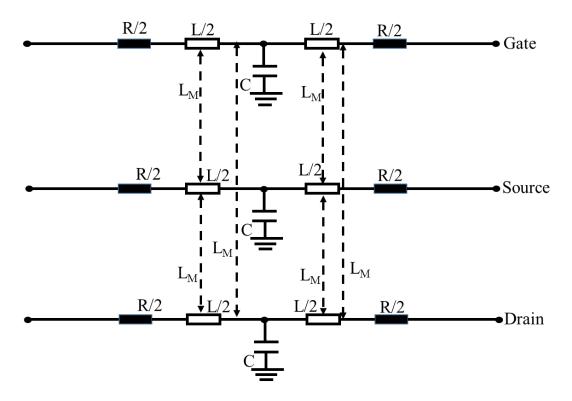

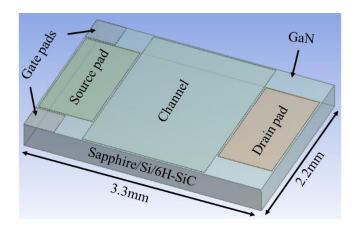

# 2.2.1 Through hole and surface mount packages