# Planar InAs avalanche photodiodes for infrared sensing: Towards a true solid state photomultiplier

By:

Benjamin Stephen White

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

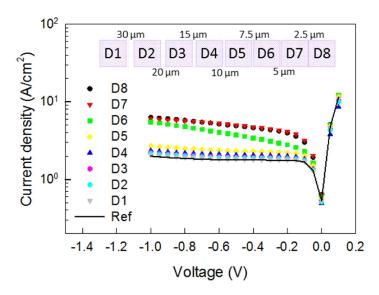

The University of Sheffield

Faculty of Engineering

Department of Electronic and Electrical Engineering

**Submission Date**

5<sup>th</sup> August 2016

# Contents

| A | cknowl    | edgements                                              | 6  |

|---|-----------|--------------------------------------------------------|----|

| A | bstract   |                                                        | 7  |

| P | ublicati  | ons                                                    | 8  |

| L | ist of sy | /mbols                                                 | 11 |

| 1 | Intro     | oduction                                               | 13 |

|   | 1.1       | Semiconductors used in photon detectors                | 14 |

|   | 1.2       | Photoconductors                                        | 18 |

|   | 1.3       | Photodiodes                                            | 19 |

|   | 1.4       | Avalanche photodiodes                                  | 20 |

|   | 1.5       | Photomultiplier tube                                   | 24 |

|   | 1.6       | Thermal detectors                                      | 24 |

|   | 1.7       | InAs APDs                                              | 24 |

|   | 1.8       | Motivation and thesis organisation                     | 30 |

|   | 1.9       | References                                             | 33 |

| 2 | Bac       | kground information                                    | 38 |

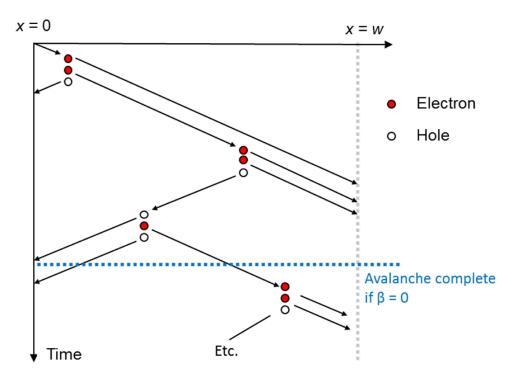

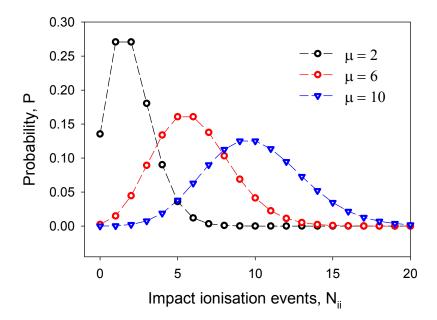

|   | 2.1       | Impact ionisation                                      | 38 |

|   | 2.2       | Avalanche gain                                         | 40 |

|   | 2.3       | Excess noise                                           | 42 |

|   | 2.4       | Ion implantation introduction.                         | 46 |

|   | 2.5       | Implanted ion distributions                            | 47 |

|   | 2.6       | Ion implantation damage                                | 48 |

|   | 2.7       | Annealing                                              | 50 |

|   | 2.8       | Hot implants                                           | 51 |

|   | 2.9       | Ion implantation and annealing in III-V semiconductors | 53 |

|   | 2.10      | Hotspots in planar APDs                                | 56 |

|   | 2.11      | Methods of mitigating hotspots in planar APDs          | 58 |

|   | 2.12      | References                                             | 59 |

| 3  | Exp     | perimental methods                                                            | 62      |

|----|---------|-------------------------------------------------------------------------------|---------|

|    | 3.1     | Current-Voltage                                                               | 62      |

|    | 3.1.    | 1 Measurement details                                                         | 63      |

|    | 3.1.    | 2 Surface leakage                                                             | 64      |

|    | 3.1.    | 3 Bulk leakage                                                                | 65      |

|    | 3.2     | Capacitance-Voltage                                                           | 68      |

|    | 3.2.    | 1 Measurement details                                                         | 68      |

|    | 3.2.    | 2 One sided abrupt junction approximation                                     | 69      |

|    | 3.2.    | 3 One dimensional Poisson solver                                              | 69      |

|    | 3.3     | Gain and Responsivity                                                         | 69      |

|    | 3.3.    | 1 Measurement details                                                         | 70      |

|    | 3.3.    | 2 Anti-reflective coating                                                     | 72      |

|    | 3.3.    | 3 Optical absorption coefficient                                              | 73      |

|    | 3.3.    | 4 Carrier collection                                                          | 74      |

|    | 3.4     | References                                                                    | 75      |

| 4  | Opt     | imisation of Be implantation and annealing to fabricate planar InAs available | alanche |

| p] | hotodio | odes                                                                          | 76      |

|    | 4.1     | Introduction                                                                  | 76      |

|    | 4.2     | Review of implantation and annealing in InAs for P-type doping                | 76      |

|    | 4.3     | Fabrication of P-i-N mesa diodes using Be implantation                        | 77      |

|    | 4.4     | Recovery of Be implanted mesa diodes through annealing                        | 79      |

|    | 4.5     | Hot implants into InAs and post implant annealing                             | 82      |

|    | 4.6     | MOVPE growth of InAs wafers with low background doping                        | 83      |

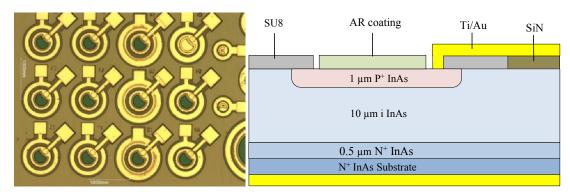

|    | 4.7     | Fabrication of planar InAs APDs with low surface leakage                      | 85      |

|    | 4.8     | Lateral diffusion of Be implanted APDs.                                       | 91      |

|    | 4.9     | Redistribution of Be in InAs upon annealing                                   | 92      |

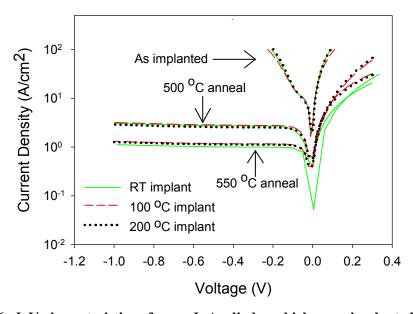

|    | 4.10    | Optimisation of Be implantation conditions                                    | 93      |

|    | 4.10    | 0.1 Fabrication                                                               | 94      |

|    | 4.10    | 0.2 Characterisation                                                          | 96      |

|    | 4.11    | Comparison of the detectivity of Be implanted diodes                          | 98      |

|    | 4.12    | Conclusion                                                                    | 99      |

|    | 4.13    | References                                                                    | 100     |

| 5 | Cha  | racterisation of High gain planar InAs APDs                                 | 102    |

|---|------|-----------------------------------------------------------------------------|--------|

|   | 5.1  | Introduction                                                                | 102    |

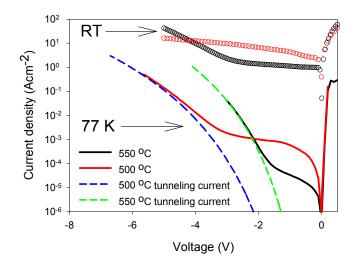

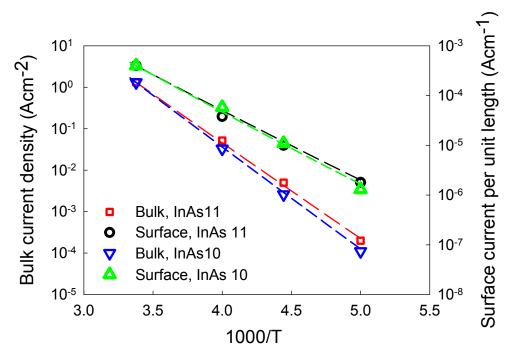

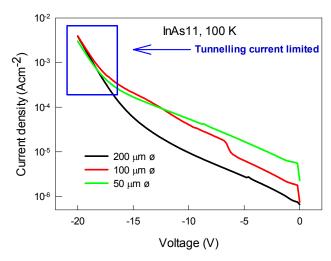

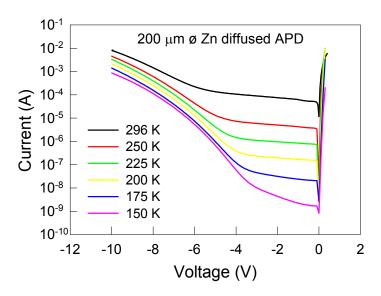

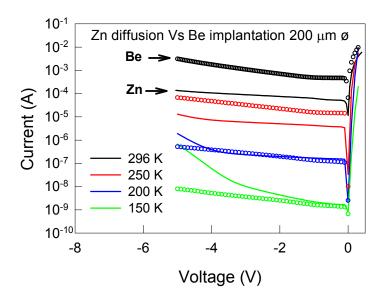

|   | 5.2  | Temperature dependence of the dark current                                  | 102    |

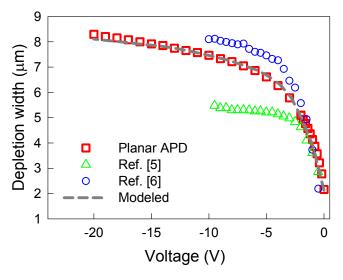

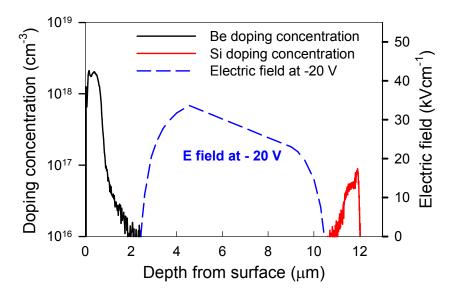

|   | 5.3  | Depletion width and background doping of high gain planar InAs APDs         | 105    |

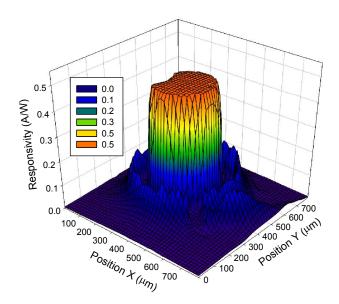

|   | 5.4  | Responsivity and gain                                                       | 108    |

|   | 5.5  | Breakdown characteristics                                                   | 112    |

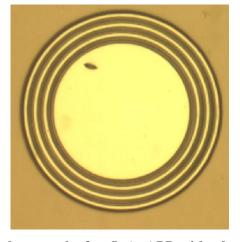

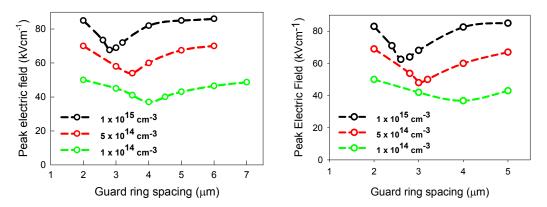

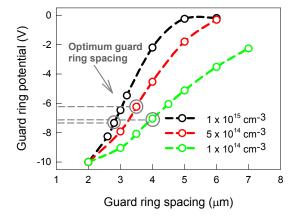

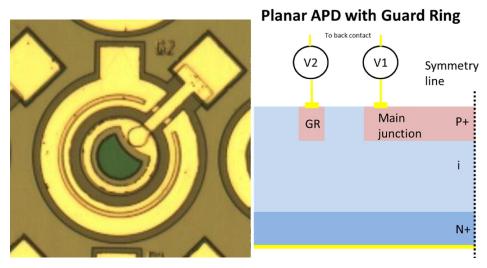

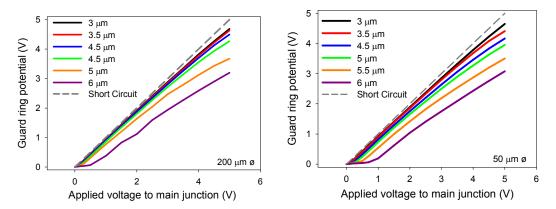

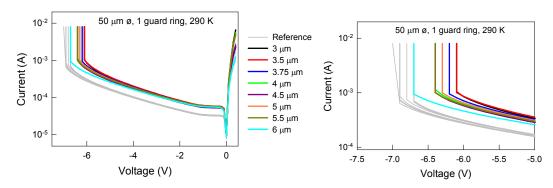

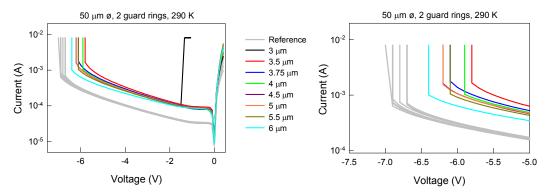

|   | 5.6  | Design of planar InAs APDs with guard rings.                                | 118    |

|   | 5.7  | Fabrication and characterisation of a guard ring test structure             | 120    |

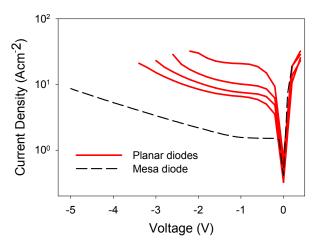

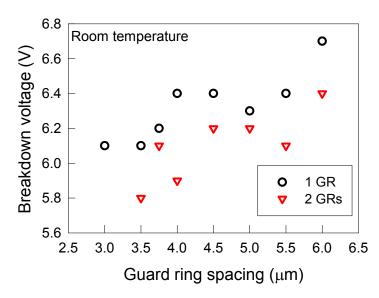

|   | 5.8  | Breakdown of planar InAs APDs with guard rings                              | 122    |

|   | 5.9  | Discussion                                                                  | 126    |

|   | 5.10 | Conclusion                                                                  | 127    |

|   | 5.11 | References                                                                  | 128    |

| 6 | Si i | mplantation for N-type doping and the fabrication and characterisation of l | ateral |

| A | PDs  |                                                                             | 130    |

|   | 6.1  | Introduction                                                                | 130    |

|   | 6.2  | Review of implantation and annealing in InAs for N-type doping              | 131    |

|   | 6.3  | Si implantation for selective area N-type doping                            | 132    |

|   | 6.4  | Si implantation profiles as measured by SIMS                                | 136    |

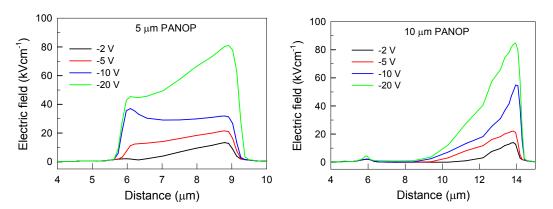

|   | 6.5  | Lateral APD design                                                          | 137    |

|   | 6.6  | Fabrication of lateral InAs APDs                                            | 142    |

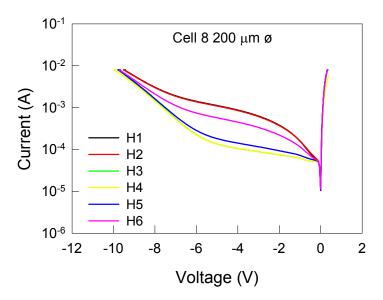

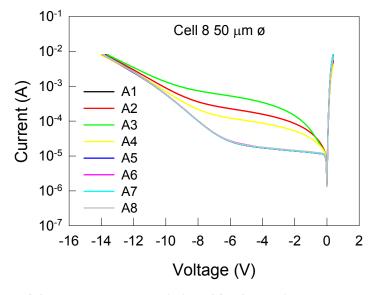

|   | 6.7  | I-V characteristics of lateral APDs                                         | 144    |

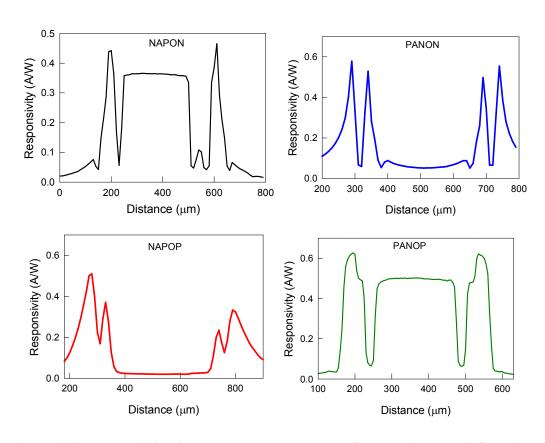

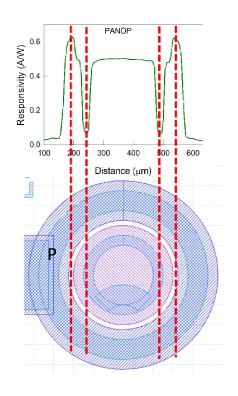

|   | 6.8  | Responsivity of lateral APDs                                                | 148    |

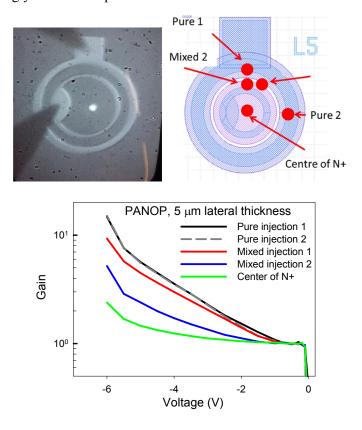

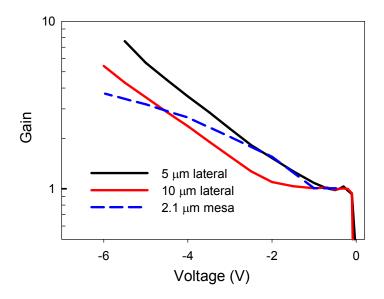

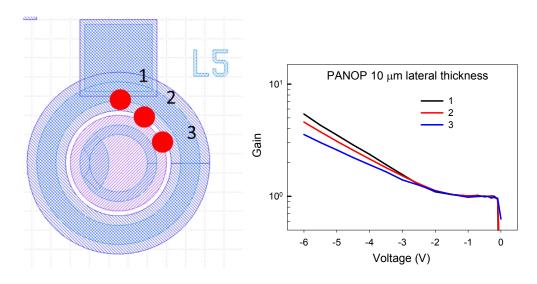

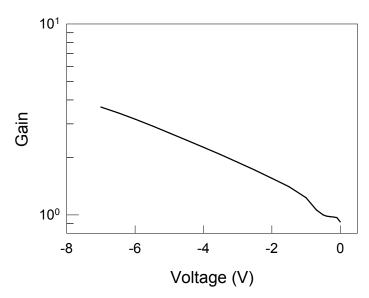

|   | 6.9  | Gain of lateral APDs                                                        | 150    |

|   | 6.10 | Conclusion                                                                  | 154    |

|   | 6.11 | References                                                                  | 154    |

| 7 | Con  | clusion and future work                                                     | 156    |

|   | 7.1  | Future Work                                                                 | 159    |

| 8 | App  | pendices                                                                    | 163    |

|   | 8.1  | Mesa fabrication procedure                                                  | 163    |

| 8.2 W  | afer details                                  | 164 |

|--------|-----------------------------------------------|-----|

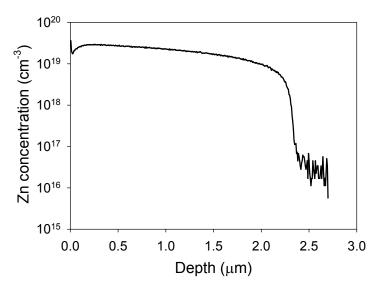

| 8.3 Zr | n diffusion                                   | 165 |

| 8.4 Pl | anar fabrication procedure                    | 170 |

| 8.4.1  | Cleaving                                      | 170 |

| 8.4.2  | Cleaning                                      | 170 |

| 8.4.3  | Deposit the encapsulating layer               | 171 |

| 8.4.4  | Pattern alignment marks                       | 172 |

| 8.4.5  | Define alignment marks                        | 173 |

| 8.4.6  | Mask for implantation                         | 173 |

| 8.4.7  | Send the sample for implantation              | 174 |

| 8.4.8  | Removing the photoresist after implantation   | 174 |

| 8.4.9  | Annealing                                     | 174 |

| 8.4.10 | Deposit the back contact                      | 175 |

| 8.4.11 | Deposit top contacts                          | 175 |

| 8.4.12 | Deposit Bond pads                             | 176 |

| 8.4.13 | Passivate with SU8                            | 177 |

| 8.4.14 | Bond pad metallisation (broken field plating) | 178 |

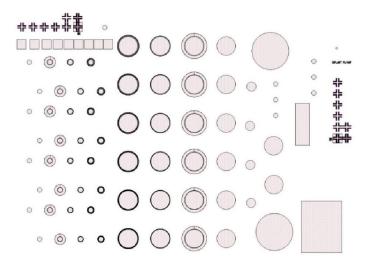

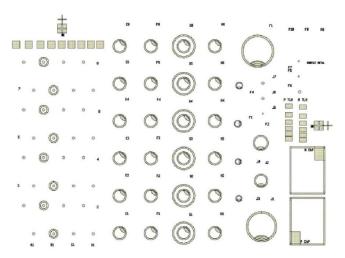

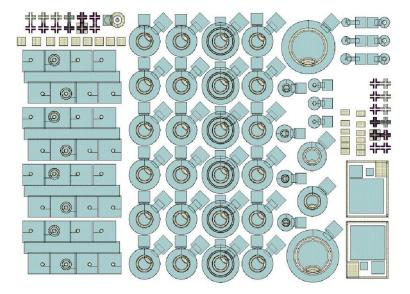

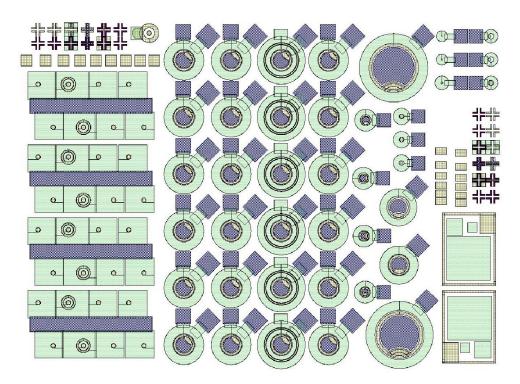

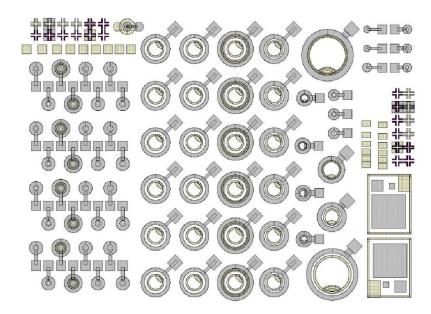

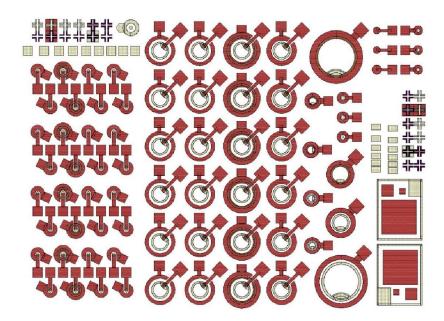

| 8.4.15 | V7 mask set description                       | 178 |

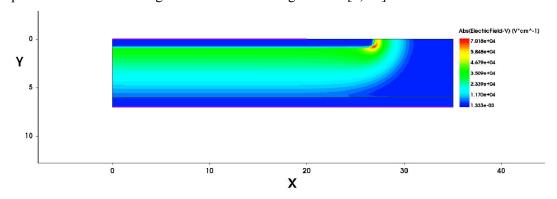

| 8.5 Sy | nopsys device simulations                     | 183 |

# Acknowledgements

I would like to express my sincere gratitude to Prof. Chee Hing Tan for his continuous support throughout my PhD. For your patience, inspiration, guidance, and financial support I am truly grateful. I am fortune to have met Dr. Jon Willmott whose guidance overt the last 4 years has greatly enriched my experience. I would like to thank Prof. John David for many enjoyable discussions, and finding time to share his knowledge. I am in debt to Dr. Ian Sandall for teaching me the art of fabrication and characterisation. I would like to thank Dr. Jo Shien Ng, and past and present members of the Impact Ionisation Group for the useful discussions, support and friendship most notably from Drs, Zhou, Meng, Dimler, Kerr, Hobbs, Richards, Gomez, Green, J. Xie, S. Xie, Cheong and Auckloo.

I would like to express gratitude to Dr. Ken McEwan from DSTL and LAND Instruments for funding this project and providing industrial relevance.

This work would not have been possible without the National III-V Centre, with a special thanks to Dr. Andrey Krysa for growing InAs wafers, and also Dr. Ken Kennedy, Dr. Rob Airy and Saurabh Kumar for fabrication advice. I would like to thank Prof. Russell Gwilliam for many useful discussions and for enabling access to the Ion Beam Centre at the University of Surrey. I would like to thank all the EEE staff, particularly Ian Wraith and Stephen Dorward, for enabling this work to be carried out, and keeping the department running smoothly.

The last four years have been particularly enjoyable as it has been my good fortune to share them with Gemma, who has balanced my academic work with many fond memories of Sheffield. Finally, I would like to thank my family and friends for their unwavering support throughout this time.

# Abstract

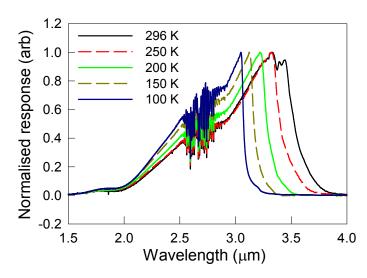

Planar InAs avalanche photodiodes (APDs) are reported as low noise, high gain photon detectors operating across the electromagnetic spectrum from 1.5 to 3.5  $\mu m$ . This work includes a study of post-growth selective area doping techniques in InAs required for forming planar junctions, through to developing the first planar and lateral InAs APDs to realise high gain.

Be ion implantation and annealing are developed for selective area P-type doping InAs. An implantation and annealing procedure was optimised to maximise Be activation and recovery, whilst minimising Be diffusion. A planar fabrication procedure was developed and InAs planar photodiodes were characterised with high uniformity and low surface leakage achieving a detectivity of  $6.08 \times 10^8$  cmHz<sup>-1/2</sup>W<sup>-1</sup> at room temperature.

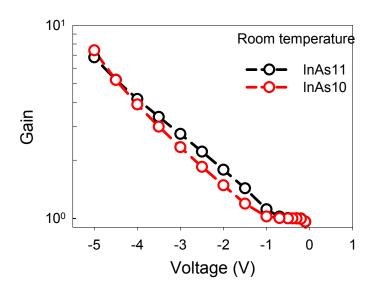

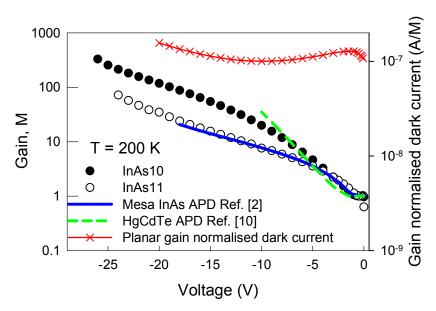

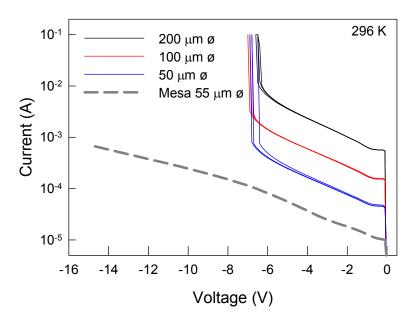

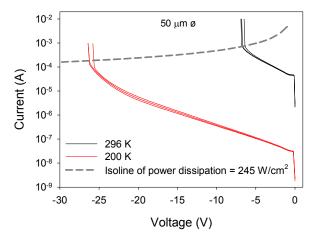

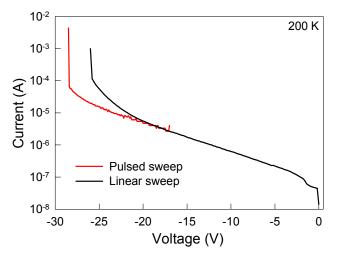

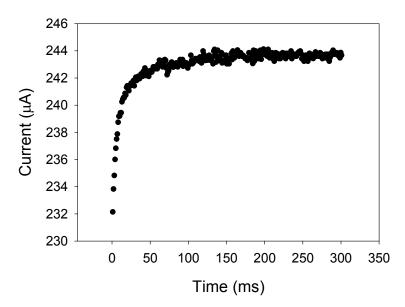

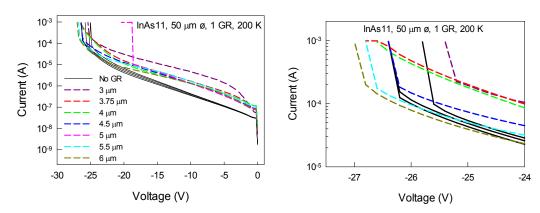

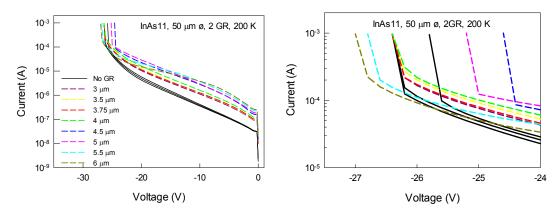

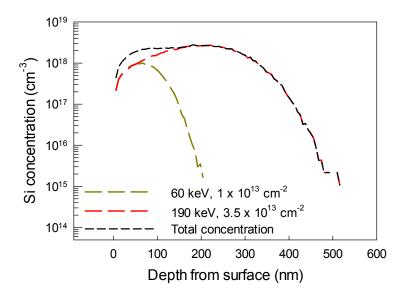

InAs APDs were fabricated using a planar fabrication process. The activation energy of the bulk and surface leakage components of the dark current were analysed to determine the dominant leakage mechanisms. Utilising an optimised structure to minimise tunnelling current, a record high gain in excess of 300 was achieved at -26 V at 200 K. The maximum gain was limited by breakdown, and the breakdown mechanism was found to be due to an unusual thermal runaway effect within an electric field hotspot at the planar junction edge. To mitigate the formation of electric field hotspots, planar APDs with guard rings were designed and characterised. Planar APDs with optimised guard ring placements were characterised with lower dark current near breakdown, and an increased breakdown voltage at 200 K compared to unguarded APDs.

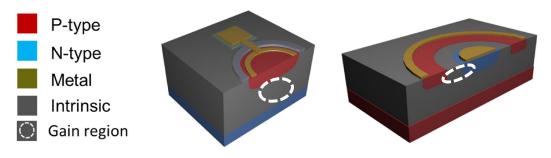

The gain limitations of InAs APDs utilising a conventional structure are discussed. To overcome such limitations a novel lateral APD structure was proposed. A range of lateral APD structures were simulated to evaluate the evolution of a lateral electric field that may lead to enhanced lateral gain. N-type selective area doping using Si implantation and annealing were developed, and a range of lateral APD structures were fabricated utilising Be and Si implantation and annealing. Lateral APDs were characterised and an optimised structure was identified. Finally a discussion of the recommended work to be carried out on InAs APDs is presented.

# **Publications**

### Journal papers:

- X. Zhou, M. J. Hobbs, **B. S. White**, J. P. R. David, J. R. Willmott, and C. H. Tan, "An InGaAlAs-InGaAs Two-Color Photodetector for Ratio Thermometry," *IEEE Transactions on Electron Devices*, vol. 61, pp. 838-843, 2014.

- I. C. Sandall, F. Bastiman, **B. White**, R. Richards, D. Mendes, J. P. R. David *and C. H. Tan* "Demonstration of InAsBi photoresponse beyond 3.5 μm," *Applied Physics Letters*, vol. 104, p. 171109, 2014.

- **B. S. White**, I. C. Sandall, J. P. R. David, and C. H. Tan, "InAs Diodes Fabricated Using Be Ion Implantation," *IEEE Transactions on Electron Devices*, vol. 62, pp. 2928-2932, 2015.

- **B. S. White**, I. C. Sandall, X. Zhou, A. Krysa, K. McEwan, J. P. R. David and C. H. Tan "High-Gain InAs Planar Avalanche Photodiodes," *IEEE Journal of Lightwave Technology*, vol. 34, pp. 2639-2644, 2016

- J. Willmott, D. Lowe, M. Broughton, **B. White**, G. Machin "Potential for improved radiation thermometry measurement uncertainty through implementing a primary scale in an industrial laboratory," *Measurement Science and Technology*, vol. 27, p. 094002, 2016.

- T. Wilkes, A. McGonigle, T. Pering, A. Taggart, **B. White**, R. Bryant and J. Willmott. "Ultraviolet Imaging with Low Cost Smartphone Sensors: Development and Application of a Raspberry Pi-Based UV Camera," Sensors, vol. 16, p. 1649, 2016.

### **Conference papers:**

- **B. S. White**, I. Sandall, and C. H. Tan, "Planar InAs pin photodiodes fabricated using ion implantation," in *2014 IEEE Photonics Conference (IPC)*, 2014, pp. 352-353.

- C. H. Tan, **B. S. White,** I. Sandall "InAs APD with solid state photomultiplier characteristics" in 2014 IEEE Photonics Conference (IPC), pp. 354-355, 2014.

- **B. S. White**, I. Sandall, C. H. Tan "Planar InAs avalanche photodiodes" in *2015 IEEE Photonics Conference (IPC)*, pp. 454-455, 2015.

J. R. Willmott, D. Lowe, M. Broughton, **B. S. White**, and G. Machin, "Improved radiation thermometry measurement uncertainty through implementing a primary scale in an industrial laboratory," in *17th International Congress of Metrology*, 2015, p. 15004.

#### **Conference proceedings:**

- **B. S. White**, I. Sandall and C. H. Tan, "Development of ion implantation procedures for InAs avalanche photodiodes" *Dstl National PhD Scheme Conference*, Oxford, UK, February, 2013.

- **B. S. White**, I. Sandall, X. Zhou, C. H. Tan, J. R. Willmott and A. B. Krysa, "Single pixel thermal imaging using an InAs photodiode," *UK compound semiconductors*, Sheffield, UK, July, 2013.

- C. H. Tan, I. Sandall, X. Zhou, **B. S. White**, M. Hobbs, S. Zhang, A. B. Krysa and J. P. David, "Mid-IR detectors at Sheffield," *UK compound semiconductors conference*, Sheffield, UK, July 2013.

- X. Zhou, I. Sandall, M. J. Hobbs, **B. S. White**, C. H. Tan and J. R. Willmott, "Evaluation of InAs photodiodes for radiation thermometry," *27th Meeting of the Semiconductor and Integrated Optoelectronics (SIOE)*, Cardiff, UK, 2013.

- X. Zhou, I. Sandall, **B. S. White**, A. B. Krysa, J. R. Willmott and C. H. Tan, "InAs photodiode for 3.43 µm radiation thermometer," *41th International Symposium on Compound Semiconductors (ISCS)*, Montpellier, France, May 2014.

- I. Sandall, **B. S. White**, X. Zhou and C. H. Tan, "An InAs/QDIP multispectral detector," *UK compound semiconductors conference*, Sheffield, UK, July 2014.

- I. C. Sandall, F. Bastiman, **B. S. White**, R. Richards, J. David, C. H. Tan "Demonstration of an InAsBi photodiode operating in the MWIR" SPIE Emerging Technologies in Security and Defence, 2014.

- **B. S. White**, X. Zhou, I. Sandall, C. H. Tan and J. R. Willmott "Remote temperature sensing using InAs photodiodes" in *2014 IEEE Photonics Conference (IPC)*, San Diego, California, USA, October, 2014.

**B. S. White** and C. H. Tan "Novel lateral cascaded InAs avalanche photodiodes for infrared sensing: Towards a true solid state photomultiplier" Defence and Security symposium, Defence Academy of the United Kingdom, Shrivenham, UK, November, 2016.

# List of symbols

| A Area                   |                                                | MWIR Mid-wavelength infrared |                                        |  |

|--------------------------|------------------------------------------------|------------------------------|----------------------------------------|--|

| a                        | Tunnelling current fitting parameter           | n                            | Ideality factor                        |  |

| APD Avalanche photodiode |                                                | $N_A$                        | Acceptor concentration                 |  |

| AR                       | Anti-reflective                                | $N_D$                        | Donor concentration                    |  |

| b                        | Recombination constant                         | NEP                          | Noise equivalent power                 |  |

| BIB                      | Blocked impurity band                          | $n_i$                        | Intrinsic carrier concentration        |  |

| C-V                      | Capacitance-voltage                            | $N_i$                        | Unintentional doping concentration     |  |

| $D^*$                    | Detectivity                                    | $N_{ii}$                     | Impact ionisation frequency            |  |

| $d_{arc}$                | Thickness of the anti-<br>reflective coating   | NIR                          | Near-infrared                          |  |

| $d_{\mathrm{e}}$         | Dead space                                     | PDF                          | Probability density function           |  |

| $d_{\text{eff}} \\$      | Effective device thickness                     | PMF                          | Probability mass function              |  |

| $D_n$                    | Diffusion coefficient of                       | PMT                          | Photomultiplier tube                   |  |

| _                        | electrons                                      | -                            | •                                      |  |

| $D_p$                    | Diffusion coefficient of holes                 | P <sub>opp</sub>             | Optical power                          |  |

| DUT                      | Device under test                              | QWIP                         | Quantum well infrared photodetector    |  |

| E <sub>g</sub>           | Band gap energy                                | R                            | Resistance                             |  |

| Е-Н                      | Electron-hole                                  | R <sub>opp</sub>             | Reflectance                            |  |

| E <sub>th</sub>          | Threshold energy                               | R <sub>p</sub>               | Projected range                        |  |

| F                        | Excess noise factor                            | RPL                          | Random Path Length                     |  |

| f                        | frequency                                      | R <sub>res</sub>             | Responsivity                           |  |

| $G_{opp}$                | Optical generation rate                        | R <sub>s</sub>               | Shunt resistance                       |  |

| h<br>+                   | Planck constant                                | RTA                          | Rapid thermal anneal                   |  |

| ħ                        | Reduced Planck constant                        | S                            | Device average collection efficiency   |  |

| НН                       | Heavy hole                                     | SAM                          | Separate absorption and multiplication |  |

| I                        | Current                                        | SRH                          | Shockley Reed Hall                     |  |

| $I_A$                    | Imaginary current                              | SIMOX                        | Separation by implantation of oxygen   |  |

| $I_n$                    | Noise spectral density                         | SIMS                         | Secondary ion mass spectroscopy        |  |

| $I_{nAPD}$               | Noise spectral density of an amplified current | SWIR                         | Short-wavelength infrared              |  |

| $I_{ph}$                 | Photocurrent                                   | Т                            | Absolute temperature                   |  |

| I-V                                         | Current-voltage                           | TRIM              | Transport of Ions in Matter             |  |

|---------------------------------------------|-------------------------------------------|-------------------|-----------------------------------------|--|

| $J_0$                                       | J <sub>0</sub> Saturation current density |                   | Speed of light in a vacuum              |  |

| $J_b$                                       | J <sub>b</sub> Bulk current density       |                   | Test signal voltage                     |  |

| J <sub>diff</sub> Diffusion current density |                                           | $V_{bi,}$         | Built in potential                      |  |

|                                             | Generation recombination c                |                   |                                         |  |

| $J_{GRBB}$                                  | Current density due to band               | $V_{Ph}$          | Photovoltage                            |  |

|                                             | to band transitions                       |                   |                                         |  |

| т                                           | Surface leakage per unit                  | V                 | Phase sensitive voltage                 |  |

| $J_{\rm s}$                                 | length                                    | $ m V_{PSD}$      |                                         |  |

| ī                                           | Trap assisted generation                  |                   | Multiplication region width             |  |

| $ m J_{SRH}$                                | recombination current                     | W                 |                                         |  |

| ī                                           | Total primary dark current                |                   | Local electron impact ionisation        |  |

| $J_{tot}$                                   | density                                   | α                 | coefficient                             |  |

| J-V                                         | Current density-voltage                   | α*                | Enabled impact ionisation coefficient   |  |

| 1,                                          | Ratio of the electron to hole             | $lpha_{ m opp}$   | Optical absorption coefficient          |  |

| k                                           | impact ionisation coefficient             |                   |                                         |  |

| k                                           | Dalt-mann agustant                        | β                 | Local hole impact ionisation            |  |

| K                                           | Boltzmann constant                        | β                 | coefficient                             |  |

| LH                                          | Light hole                                | $\epsilon_{ m r}$ | Relative permittivity                   |  |

| LIA                                         | Lock-in amplifier                         | η                 | External quantum efficiency             |  |

| $L_n$                                       | Diffusion length of electrons             | m                 | Refractive index of the anti-reflective |  |

| Ln                                          |                                           | $\eta_{ m ARC}$   | coating                                 |  |

| $L_p$                                       | Diffusion length of holes                 | θ                 | Phase                                   |  |

| LWIR                                        | Long-wavelength infrared                  | $\lambda_{ m c}$  | Cut-off wavelength                      |  |

| M                                           | Avalanche gain                            | ξ                 | Electric field                          |  |

| m*                                          | Effective mass                            | $	au_{ m eff}$    | Effective carrier lifetime              |  |

| $m_{e}$                                     | Electron effective mass                   | ω                 | Angular frequency                       |  |

| $m_{h}$                                     | Hole effective mass                       | μ                 | Average                                 |  |

| MIS                                         | Metal insulator                           |                   |                                         |  |

| 14113                                       | semiconductors                            |                   |                                         |  |

# 1 Introduction

Light detection and measurement are powerful tools for non-destructive analysis, high speed communication, imagery and video. Semiconductors provide an excellent medium for facilitating light detection for three key reasons. 1) Semiconductors are highly sensitive to light as photo-generated carriers are not readily thermalized, or reemitted as photons, but induce a significant change in a variety of the semiconductor's electronic properties that can be accurately measured. 2) The band gap and band diagram of a device can be engineered to optimise performance 3) High manufacturability has enabled micro-scaling and mass production with very low costs and easy integration with read-out electronics for digitisation and further processing.

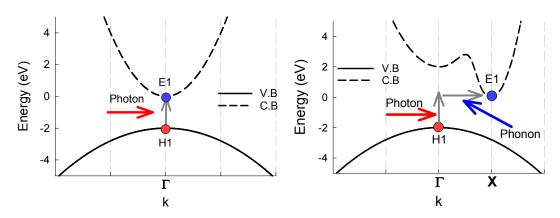

Figure 1.1 E-k diagrams of optical generation in a direct (left) and indirect (right) semiconductor

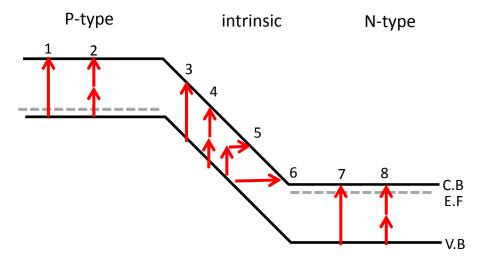

The detection of light using a semiconductor is facilitated through the absorption of a photon's energy to excite an electron to a higher energy state. Within a direct bandgap semiconductor, the absorption of a photon excites an electron directly from the valence band (V.B) to the conduction band (C.B) creating an electron-hole (E-H) pair as shown in Figure 1.1. Making use of the relatively long carrier lifetime in semiconductors, various devices have been designed to extract the photo-generated E-H pair facilitating the detection of light.

No energy states exist within the bandgap of a semiconductor, and therefore photons carrying less energy than the fundamental bandgap energy cannot be absorbed. The absorption edge of a semiconductor is referred to as the cut-off wavelength. As bandgap energy of a semiconductor also has a strong inverse relationship with the magnitude of the thermally generated noise of the detector, detector performance is optimised using a semiconductor with a cut-off wavelength equal the longest wavelength required for

detection. However, the design of a photon detector also requires the consideration of additional parameters including the optical absorption coefficient, manufacturability, uniformity, cost and electronic properties of the semiconductor. A brief review of common semiconductor materials and photon detectors is presented.

# 1.1 Semiconductors used in photon detectors

Unrivalled manufacturing, maturity and cheap processing costs enable Si detectors to dominate applications from visible to the near infrared (NIR) sharing the largest proportion of the detector market in terms of volume. However, Si has an indirect bandgap due to the minima of the conduction band and the maxima of the valence band occurring at different vectors of crystal momentum, k, within the first Brillouin zone as shown in Figure 1.1. To conserve energy and momentum during the absorption of a photon near the band edge of in an indirect semiconductor, a third partial, such as a phonon, is required to accommodate the difference in crystal momentum. The three particle process has a significantly lower probability of occurring compared to a direct band to band transition, and causes indirect bandgap semiconductors to display a low optical absorption coefficient near the band edge. To maintain high quantum efficiency, indirect bandgap semiconductors require a greater length of material to achieve high optical absorption. However, the thicker optical absorption regions increase the carrier transit time resulting in a lower device bandwidth. Indirect bandgap semiconductors are therefore not well suited as high performance photon detectors. Ge also suffers from an indirect bandgap, however, the bandgap is narrower compared to Si, and Ge detectors provides useful response out to 1.6 µm while also benefiting from mature manufacturing.

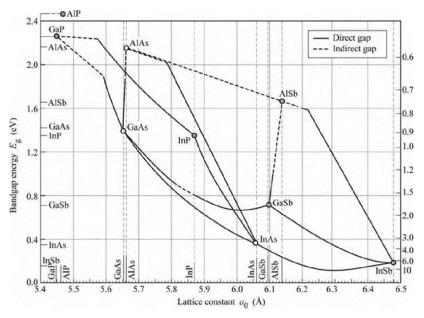

Although III-V semiconductors are more expensive and less mature than elemental semiconductors, many III-V semiconductors have a direct bandgap. The electron transport of III-V semiconductors are also significantly greater than elemental semiconductors allowing for further improvements to the detector bandwidth. For example, the electron saturation velocity of Si is 1 x 10<sup>7</sup> cms<sup>-1</sup> [1] while for InGaAs the peak saturation velocity is 2.9 x 10<sup>7</sup> cms<sup>-1</sup> [2]. Epitaxial growth techniques for III-V semiconductors can provide layered III-V semiconductors with different bandgap energies to form heterojunctions for advanced detector optimisation to improve responsivity, speed and noise. The relationship between lattice constant and the bandgap energy of III-V semiconductors is shown in Figure 1.2 [3].

Figure 1.2: The bandgap energy and lattice constant of III-V semiconductors at room temperature [1]

Lattice match growth of III-V semiconductors to a binary substrate is required to maintain high crystal quality, and commercial III-V detectors are generally fabricated with In <sub>0.53</sub>Ga<sub>0.47</sub>As, InAs or InSb absorption regions to provide cut off wavelengths of 1.7, 3.5 and 5.5 µm respectively [4]. In<sub>0.53</sub>Ga<sub>0.47</sub>As grown lattice matched to InP is one of the most mature III-V semiconductors covering telecommunications wavelengths. The intrinsic carrier concentration and minority carrier lifetime of semiconductors are highly important parameters for discussing the detector performance as they govern the magnitude of the thermally generated noise, as discussed in section 3.1. The minority carrier lifetime of intrinsic In<sub>0.53</sub>Ga<sub>0.47</sub>As at 300 K is  $\approx 10 \mu s$  and  $\approx 10 ns$  when doped P or N-type at  $1 \times 10^{18}$ cm<sup>-3</sup> [5]. The relatively long minority carrier lifetime and low intrinsic carrier concentration of  $\approx 5 \times 10^{11}$  cm<sup>-3</sup> [6] enables In<sub>0.53</sub>Ga<sub>0.47</sub>As detectors to be operated at room temperature with acceptable levels of thermally generated noise. In As is utilised less extensively with comparably few commercial vendors. InAs has a bandgap of 0.35 eV at 300 K generating a large intrinsic carrier concentration of  $\approx 1 \times 10^{15}$  cm<sup>-3</sup>. Although InAs detectors can be operated at room temperature, many applications require InAs detectors to operate at low temperatures to supress the thermally generated noise to an acceptable level. Operating InAs detectors at a temperature of 200 K using Peltier coolers is usually sufficient to supress thermal noise to an acceptable level. The intrinsic carrier concentration of InAs reduces to  $\approx$  $7 \times 10^{12} \ cm^{-3}$  at 200 K and a minority carrier diffusion length of 1  $\mu s$  in slightly N-type InAs at 200 K has also been reported [7]. InSb detectors are considered to be a mature technology, however, they require significant cooling due to the narrow bandgap of 0.18 eV at room temperature. InSb detectors are often operated at  $\approx 80 \text{ K}$  [6] with a minority carrier

concentration of  $3 \times 10^9$  cm<sup>-3</sup> at 77k. Lattice mismatched growth using sophisticated buffer layers has yielded detectors with acceptable crystal quality and cut-off wavelength between those covered by the lattice matched growth. Commonly grown lattice mismatched materials are extended InGaAs for 2.2 to 2.8  $\mu$ m [8] and InAsSb for wavelengths > 5.5  $\mu$ m [9].

The II-VI semiconductor family has high potential for photon detectors as the band gap of the ternary alloy of CdTe and HgTe can be tuned to span across the short-wavelength infrared (SWIR) to long-wavelength infrared (LWIR) spectrum with only a 0.3 % increase in the lattice constant [10]. The distribution and production of HgCdTe is largely controlled by defence associates limiting the free study and publication. It is understood that there are major growth and fabrication challenges preventing HgCdTe from dominating the infrared detector market. Lattice matched CdZnTe substrates are many times the cost of III-V substrates while also only being a fraction of the size [10]. Non-lattice matched growth on Si substrates has been developed [11], however, the epitaxially grown crystal has significantly higher defect densities and suffers from thermal expansion mismatch issues. The strong dependence of band gap energy, thus the cut-off wavelength, on mercury composition causes uniformity issues with very high composition tolerances required to meet the demands of modern applications [12]. Growth and fabrication of HgCdTe is further complicated by the weak Hg bond which dissociate at low temperatures leading to high concentration of Hg vacancies at typical processing temperatures [13]. Consequently, production of HgCdTe is not suited to large scale manufacturing, and its use is limited to applications where the best performance possible is paramount, regardless of cost.

In addition to interband optical absorption, alternative electron transitions can be detected across Schottky barriers [14], metal insulator semiconductors (MIS) [15], blocked impurity band (BIB) [16], and quantum wells [6]. Although most detection methods cannot yet compete against the performance of optimised interband detectors, they provide compelling options for spectral tuning and can be implemented in mature, cheap, wide bandgap semiconductors. Two of the most promising detectors are quantum well infrared photodetectors (QWIPs) [17] and detectors made from type-II superlattice materials [18]. Both are typically implemented from III-V semiconductors with layer thickness comparable to the de Broglie wavelength of the carriers. Confinement of the carriers in one or more direction modifies the wave function, density of states and dispersion. Most structures are designed to operate across the mid-wavelength infrared (MWIR) or LWIR spectrum as competitors against interband HgCdTe photodetectors. In addition providing growth on a cheap large area substrate, quantum well detectors have a low intrinsic carrier concentration and reduced tunnelling current due to the higher effective electron mass. Furthermore, type

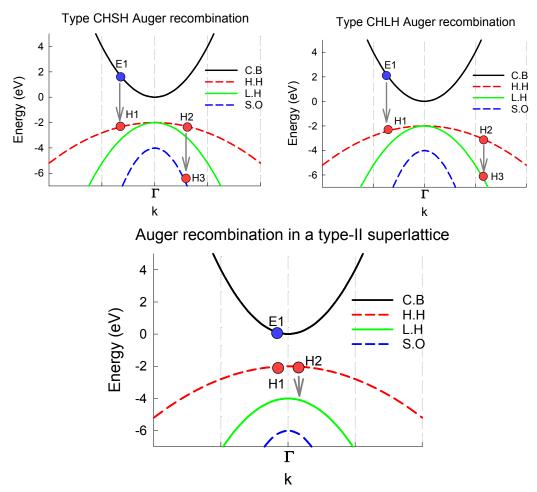

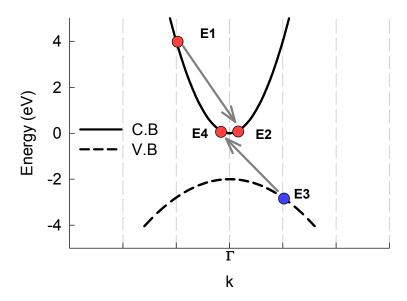

CHSH and CHLH Auger recombination is reduced in type-II superlattice materials as the heavy hole (HH) and light hole (LH) bands are split reducing the number of available transitions [19]. A schematic diagram of CHSH and CHLH Auger recombination are shown in Figure 1.3 with the schematic diagram of a type-II superlattice also shown. CHSH and CHLH Auger recombination transitions are reported to be the dominant recombination mechanism limiting the minority carrier lifetime, thus increasing thermally generated noise, in narrow bandgap semiconductors such as InAs, InSb and HgCdTe.

Figure 1.3: Top left - type CHSH Auger recombination where E1 and H1 recombine and H2 gains energy by moving to H3. Top right - type CHLH Auger recombination where E1 and H1 recombine and H2 gains energy by moving to H3. Bottom – Auger recombination in a Type-II superlattice is less likely to occur as H2 does not have many free states to transition into.

# 1.2 Photoconductors

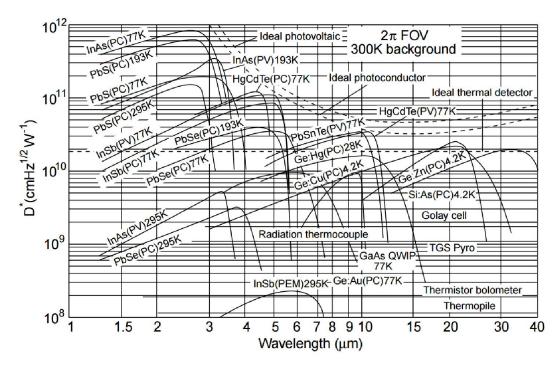

Figure 1.4: The detectivity of various commercial photoconductors (PC) and photodiodes (PV) at indicated temperatures. Measurement details can be found in [20].

Photoconductors are fabricated from homogenous semiconductor with non-rectifying contacts placed at either end of the active region, much like a semiconductor resistor. A voltage is applied to separate and extract the photo generated E-H pairs before they recombine, inducing a photocurrent. As discussed in section 3, detectivity is often used as a figure of merit when comparing the performance of detectors, and the detectivity of InSb, InAs and lead salt photoconductors are shown in Figure 1.4 [20]. Thermal generation of E-H pairs can be large in narrow bandgap semiconductors and cooling can be required to improve the signal to noise ratio. Alternatively the leakage current can be reduced by inducing a high density of deep-level impurities to reduce the intrinsic carrier concentration. However, traps can also capture photo-generated carriers and significantly reduce detector speed and responsivity. Photoconductors can also provide intrinsic gain which is useful for photon starved applications. Photoconductive gain is induced when the drift velocity of the carriers transiting the active region is significantly different. The slow moving carriers, that can also be trapped, creates a charge imbalance while it is in transit and consequently many of the fast moving carriers are injected into the active region in one transit of the slow carrier to maintain charge neutrality [21]. Photoconductor design has a significant trade-off between bandwidth, gain and dark current. Photoconductors are easy to manufacture due to their simple structure, however, advances in other detector technologies has limited use with

photodiodes generally providing higher performance and are more easily multiplexed onto a focal plane. Modern bolometers can provide similar performance with significantly lower manufacturing and operation costs replacing the applications where photoconductors were traditionally used. InSb and HgCdTe photoconductors provide a compelling option for some applications operating across the MWIR as moderate sensitivity can be achieved at Peltier cooled temperatures.

# 1.3 Photodiodes

A photodiode has a built-in potential generated by an electric field developed across a depleted space charge region that acts to separate photo-generated E-H pairs created within its vicinity. The separation and grouping of carrier types creates a net potential across the device as the E-H pairs seek to recombine providing electromotive force, as described by the photovoltaic effect. The internal electric field enables photodiodes to be operated at 0V, termed photoconductive mode, and consequently very low dark currents can be achieved compared to the ohmic leakage of a biased photoconductor. The response speed and responsivity of a photodiode can be increased by applying a small reverse bias voltage to extract the carriers at saturation velocity. The built in potential of a photodiode can be formed across any interface where significant charge transfer has occurred. Narrow bandgap photodiodes are often fabricated using a P-N junction to create a built-in potential, however, charge transfer can also occur across a heterojunction or Schottky barrier, although such methods typically result photodiodes with poorer performance [6]. Si photodiodes are used in most applications up to 1.1 µm, however, telecommunications applications require a direct bandgap semiconductor operating at longer wavelengths to which III-V semiconductors are mainly used. In<sub>0.53</sub>Ga<sub>0.47</sub>As based heterojunction photodiodes are widely employed across telecommunications wavelengths due to a high optical absorption coefficient and large saturation velocity. Traditional front illuminated P-i-N InGaAs photodiodes are limited to a bandwidth of  $\approx$  15 GHz while maintaining good responsivity, while optimised uni-travelling-carrier photodiodes have been reported with a bandwidth in excess of 300 GHz [22, 23]. InAs has a cut off wavelength of 3.5 μm and a higher optical absorption coefficient and saturation velocity compared to In 0.53Ga0.47As. However, the narrow bandgap of InAs causes a significantly larger thermally generated noise compared to InGaAs photodiodes. Furthermore, the growth of InAs and InAs heterostructures based upon the 6.06 Å lattice constant is less well explored compared to InGaAs, as discussed in greater detail in section 1.7. Consequently there are comparably few commercial vendors, or reports of InAs photodiodes. Commercial InAs photodiodes are mainly utilised in radiation thermometry and infrared spectroscopy applications [24]. InSb photodiodes are widely used

in radiation thermometry instruments as they provide response across the atmospheric transmission window of  $3-5~\mu m$  [6]. HgCdTe photodiodes from the SWIR to LWIR are usually reported in a focal plane array format for imaging applications. HgCdTe photodiodes adopt a heterojunction to optimise performance, and SWIR photodiodes are often operated at room or 200 K, while MWIR compositions are operated at temperatures of  $\approx 80~K$  [6].

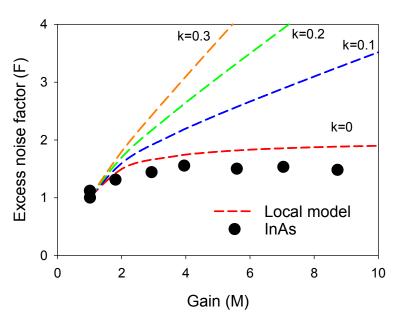

# 1.4 Avalanche photodiodes

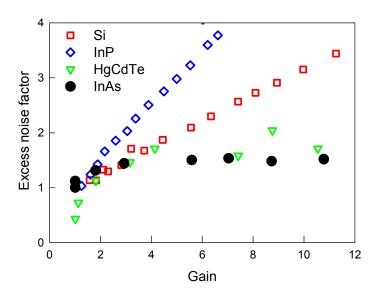

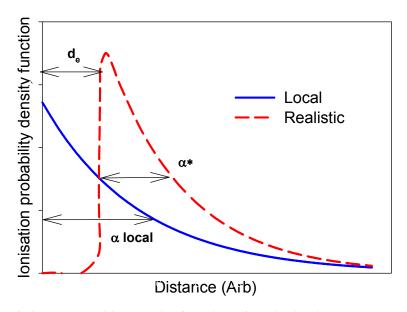

The input referred noise of front end amplifiers matched to the bandwidth of common photodiodes are of the order of  $\approx 5 pAHz^{-0.5}$  amassing a total input referred noise current of 300 nA over 4 GHz. Consequently although the detectivity of most photodiodes is very high, the sensitivity of the module employing a unity gain detector can be very poor due to the dominance of amplifier noise. When the amplifier noise is dominant, pre-amplification of the photocurrent can significantly improve the sensitivity of the detector module. An avalanche photodiode (APD) can be biased to generate a large electric field, under which charge carriers impact ionise and multiply. The sensitivity of a detector module employing an APD will continue to improve with increasing APD gain until the noise from the APD becomes dominant. Noise from an APD is generated through device leakage current, but also due to the stochastic nature of impact ionisation leading to 'excess' photocurrent noise after amplification. Optimisation of crystal quality, device design, and reduction of operating temperature can supress the leakage current of an APD. The excess noise is reduced by decreasing the variance in gain experienced by each photo-generated carrier contributing to the average device gain. Impact ionisation and excess noise theory are discussed in detail in section 2.1, and it is shown that the excess noise of an APD is minimised when the hole and electron impact ionisation coefficients of a semiconductor are disparate, such that the ratio, k, deviates far from unity [25]. Impact ionisation rates are largely a material property and efforts to optimise APD performance have focused on characterizing new materials. Typical excess noise characteristics of InP [26], Si [27],  $Hg_{0.5}Cd_{0.5}Te$  ( $\lambda_c = 2.2 \mu m$ ) [28] and InAs [29] APDs are shown in Figure 1.5.

Figure 1.5: Excess noise characteristics of InP [26], Si [27],  $Hg_{0.5}Cd_{0.5}Te$  ( $\lambda_c$  = 2.2  $\mu$ m) [28] and InAs [29].

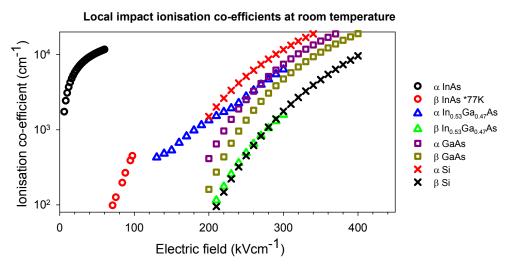

Si has a very low k value at low electric fields and thick Si APDs can achieve low excess noise [30]. However, such devices require high voltages to develop gain, and also operate with a low bandwidth due to long carrier transit times. III-V semiconductors can provide longer wavelength response with research largely driven by long haul telecommunications operating at 1.55 µm [31]. However, the impact ionisation coefficients of common III-V semiconductors tend to converge at large electric fields causing high excess noise as shown in Figure 1.6 for Si [30], GaAs [32], In<sub>0.53</sub>Ga<sub>0.47</sub>As [33], InAs [29]. InGaAs provides good absorption, but high tunnelling currents develop before significant avalanche gain can be achieved [34]. Telecommunications APDs therefore employ a heterojunction structure using separate materials for the absorption and multiplication regions termed a separate absorption and multiplication (SAM) APD [35]. For manufacturability, InP is widely used as the multiplication region, however, the excess noise is high due to unfavourable ionisation coefficients [36] limiting the useful gain to  $\approx 20$  (before the multiplication noise exceeds the amplifier noise). The excess noise performance of an APD can be improved by utilising a thin (< 1 µm) multiplication region [37] due to the dead space effect, which is discussed in section 2.3. As the lattice matched alloy In<sub>0.52</sub>Al<sub>0.48</sub>As has larger band gap than InP, in recent years thin multiplication regions have been developed to reduce the excess noise of  $In_{0.52}Al_{0.48}As APDs [38].$

Figure 1.6: The local impact ionisation coefficients of for Si [30], GaAs [32],  $In_{0.53}Ga_{0.47}As$  [33], InAs [29].

The lack of suitable III-V semiconductors with naturally low k vales has led research to engineer APD structures which enhance the multiplication of one carrier type, while supressing that of the other. In 1980 it was hypothesised that electron impact ionisation could be locally enhanced at conduction band discontinuity as hot carriers transferred from a wide bandgap into a narrow bandgap semiconductor [39]. Improvements to avoid charge trapping at the heterojunctions where subsequently suggested utilising graded bandgap layers to create large discontinuities in the conduction-band, but a smooth valence band [40]. The resulting band structure resembled a staircase and research into staircase APDs was popular for many years. However, by the 1990s with no incontrovertible evidence presented, interest diminished. It was later established that it was not the premise of the staircase APD that was at fault, but the material system choice. Within the GaAs/AlGaAs heterojunctions used, charge carriers transfer out of the gamma valley before gaining sufficient energy to impact ionize, and the advantage of the conduction-band discontinuity is lost [41]. With advances in growth technology and impact ionisation theory, a recent publication has shown strong evidence for single carrier multiplication in a single-step staircase APD using AlInAsSb/InAsSb interfaces [42]. The deep gamma valley of InAsSb has a very low intervalley scattering rate and consequently hot electrons transferring into this material have a high probability of impact ionising. However, to whether higher orders of repeating step regions can be successfully grown remains to be seen and presents a significant challenge to extract useful gain from staircase APDs [43].

There are comparably very few reports of APDs operating at wavelengths beyond 1.65  $\mu$ m. This is likely to be due to a combination of factors including, generation of large dark current and difficulties supressing surface leakage and tunnelling currents in reverse biased

diodes. To achieve long wavelength response without using narrow bandgap semiconductors, a strain balanced type-II superlattice has been reported as the absorption region in a SAM APD lattice-matched to InP [44]. Such use for a type-II superlattice is a promising option for providing tuneable long wavelength response, however, there are significant growth and fabrication difficulties to overcome. Early work in 1967 tentatively reported the electron impact ionisation coefficient in InSb APDs is approximately 10 times larger than that of the hole impact ionisation rate as a promising material for low noise APDs [45]. However, the aforementioned difficulties have severely encumbered progress with the next significant report of InSb APDs only published in 2015 [46], although measurement of the low excess noise is yet to be confirmed. Early work on InAs APDs was not so promising with a poor k ratio being reported [47]. The validity of this early work was questioned by many researchers, however, the impact ionisation coefficient could not be verified. In 2008 electron dominated impact ionisation in InAs was reported [48], and quickly followed by measurements of the excess noise of InAs APDs [29] and the impact ionisation coefficients of InAs [49], as plotted in Figure 1.5 and Figure 1.6 respectively. These results provide incontrovertible evidence for true single carrier multiplication in InAs, and a highly promising semiconductor for low noise APDs discovered, to which this thesis is based upon. A review of InAs APDs is presented in section 1.7.

APDs with compositions of  $Hg_{1-x}Cd_xTe$  varying from x = 0.7 - 02 to achieve cut-off wavelengths of 1.3 to 11 µm have been measured to show a large variation in excess noise [50, 51]. The earliest work on  $Hg_{0.38}Cd_{0.62}Te$  ( $\lambda = 1.3 \mu m$ ) APDs reported low field resonant hole impact ionisation with a maximum k ratio of 30 achieved for an optimised composition [51, 52]. Electron dominated impact ionisation was later measured in  $Hg_{0.78}Cd_{0.22}Te$  ( $\lambda = 11$ μm), and unlike the resonant hole impact ionisation, was not limited to only low fields showing great potential for low noise, high gain APDs [50]. Improvement to growth, fabrication, and device design has recently yielded Hg<sub>0.7</sub>Cd<sub>0.3</sub>Te APDs with a noiseless avalanche gain in excess of 1270 at 13.1 V at 80 K [28, 53]. The noiseless avalanche was due to electron only impact ionisation, but also ballistic electron transport [54]. Recently, through integration with low noise amplifiers Hg<sub>0.7</sub>Cd<sub>0.3</sub>Te APD detector units have demonstrated remarkable sensitivity by achieving linear mode photon counting [55, 56]. However, exceptionally high material quality is required to support the high electric fields within HgCdTe APDs and compounds the already difficult manufacturing issues. Consequently production of HgCdTe APDs is limited and still after huge financial investment, commercially viable manufacturing is yet to be established.

# 1.5 Photomultiplier tube

The performance of the photomultiplier tube (PMT) is unrivalled with gain in excess of 1 million, negligible excess noise and low timing jitter. However, PMTs are based upon otherwise obsolete vacuum tube technology which are inherently fragile, bulky, require a supply voltage  $\geq 1000~V$  and are highly susceptible to magnetic fields. Furthermore, photocathode materials are limited to operating in the SWIR and have poor quantum efficiency of  $\approx 2\%$  at wavelengths longer than 1  $\mu$ m. PMTs operate with absorption of a photon stimulating the emission of an electron by the photoelectric effect. The electron is accelerated in a vacuum and impinges on a cascade of dynodes causing further electrons to be emitted through secondary emission. The gain at each dynode is highly deterministic and consequently, many dynodes can be cascaded to achieve high gain incurring significant excess noise. PMTs are one of the few commercially available detector technologies providing single photon detection while operating in a linear mode.

# 1.6 Thermal detectors

Long wavelength photon detectors require significant cooling to supress thermally generated dark current. Such cooling systems are costly, bulky and have high power consumption. Thermal detectors provide an attractive cheap alternative, however, the detector performance is significantly reduced. Thermal detectors thermalize the absorbed photon energy to heat a thin detector material changing its electronic properties. The properties of the detecting element measured are; resistance in bolometers, a voltage created by a thermoelectric effect in thermopiles, a voltage due to pyro-electricity in a pyrometer and the I-V characteristics in a diode type thermal detector. Bolometers are the most widely used thermal detector, providing excellent performance at room temperature. Furthermore, the uses of amorphous Si detecting elements has enabled micro-bolometer arrays to be fabricated using Si processes directly onto CMOS read out circuits. Such technology has enabled cheap fabrication of detector arrays operating at room temperature across the 7.5 to 14 µm spectrum, where room temperature objects have peak blackbody emissions.

#### 1.7 InAs APDs

Narrow band gap semiconductors are acknowledged to be highly susceptible to surface leakage. In InSb photodiodes, surface leakage has largely been overcome through developments of the fabrication procedures, device design and use of passivation layers [57]. Surface leakage across the InAs surface however, was reported to be particularly severe due

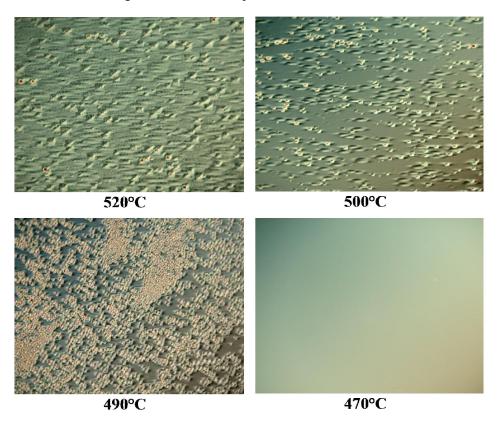

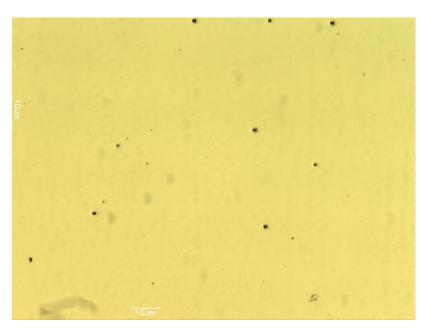

to Fermi level pinning at the InAs surface producing a high sheet carrier concentration [58]. InAs APDs were pioneered by A. Marshall et. al, first focusing on growth and fabrication procedures [59]. Although significant previous work on the epitaxial growth of InAs had been carried out, A. Marshall reported the growth of InAs APDs using molecular beam epitaxy (MBE). From reflection high-energy electron diffraction (RHEED) observations, a thermal clean temperature of 500 °C was reported as being optimum. A trial and error approach was adopted to optimise the growth temperature with four growth temperatures of 470, 490, 500 and 520 °C utilised in the study. The defect density of the 470 °C growth temperature was far less than any of the other temperatures and produced a wafer with a shiny surface indicating a low defect density as shown in Figure 1.7 [59]. However, Maddox et. al reported high quality InAs utilising a growth temperature of 500 °C and a growth rate of 1 µm per hour [60]. Furthermore, dopant cells were cooled to idle temperatures (350 °C) during the growth of the intrinsic region to eliminate parasitic incorporation of dopant species achieving a very low unintentional background doping of 2 x 10<sup>14</sup> cm<sup>-3</sup>. The significant difference in optimum growth temperature reported for InAs are likely to due to difficulties in determining the true wafer temperature in the MBE reactor.

Figure 1.7: Photographs of the surface of InAs wafers grown at temperatures of 520, 500 490 and 470 °C [59]

Previous work has also been carried out on the epitaxial growth of InAs using Metalorganic vapour phase epitaxy (MOVPE), however, the material was reported with a very high background doping concentration of 2 x  $10^{17}$  cm<sup>-3</sup> due to unintentional carbon doping [61]. InAs APDs require increasingly thick structures,  $\approx 10$  µm, to achieve higher gain and so MOVPE growth techniques would be preferable over MBE.

Auger spectroscopy was used to investigate the surface conditions of InAs diodes prepared using a variety of wet chemical etching techniques. The study suggested that the high surface leakage in InAs could be due to the formation of an indium oxide after etching. A wet chemical etching recipe was developed to prevent the formation of indium oxide layer and was successful in significantly reducing the surface leakage current in reverse biased InAs diodes [59]. The low surface leakage measured in bulk InAs devices suggests the fermi level pinning effects may not cause significant surface leakage issues.

Development of etching and growth techniques enabled the gain and excess noise of InAs APDs to be measured accurately. The gain measured on InAs APDs is exponential and unlike any other established III-V APDs which generally show a sharp rise to breakdown [48]. This unusual behaviour is an artefact of electron only impact ionisation as holes are unable to sustain the avalanche breakdown by providing feedback and negate breakdown conditions from being reached. Excess noise and measurements confirmed true single carrier multiplication in InAs APD [29]. Due to the single carrier multiplication, InAs APDs have reported the largest gain-bandwidth product of any III-V APD [62]. Furthermore InAs APDs can achieve significant gain at a low bias voltages due to the high electron impact ionisation coefficient at low electric fields [63].

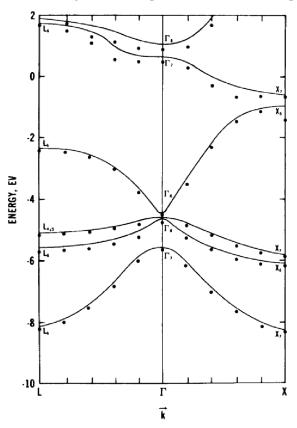

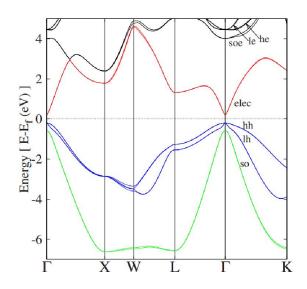

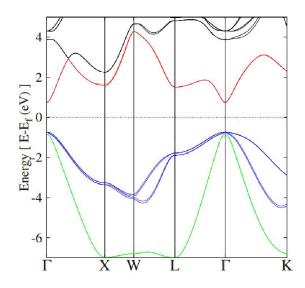

Characterisation of the impact ionisation coefficients of InAs was unusual when compared to other III-V semiconductors showing single carrier multiplication but also high impact ionisation coefficient at low electric fields, sharing similarities with long wavelength HgCdTe [29]. Impact ionisation theory of HgCdTe is well established, and observation of the HgCdTe band structure provides an accurate insight into the origins of the electron dominated impact ionisation [64]. The band structure of Hg<sub>0.7</sub>Cd<sub>0.3</sub>Te is shown in Figure 1.8 [65]. The HH mass of HgCdTe remains fixed at  $\approx 0.55 \text{ m}_0$  across all IR compositions resulting in low hole-mobility with very high optical-phonon scattering. Holes therefore reside close to the HH band maxima over a wide electric field range due to inefficient energy gain. The effective mass of the gamma valley is approximately 30 times lighter, and the low optical phonon scattering yields a very high electron motility, approximately 100 times greater than hole mobility[66]. Hg<sub>0.7</sub>Cd<sub>0.3</sub>Te has a very small band gap energy, E<sub>g</sub>, of 0.29

eV, but unlike most III-V semiconductors, the ratio of the band gap energy to valley separation energy is very large with L and X valleys 1.5 and 2.5 eV higher respectively [67]. The intervalley phonon scattering rate from the gamma valley is low and the band structure of Hg<sub>0.7</sub>Cd<sub>0.3</sub>Te can be simplified to electrons confined to the gamma valley and holes immobilised in the HH band. Under this simplified band structure, the minimum energy required for the carriers to impact ionise, defined as the threshold energy can be described as a function of the effective mass ratio [68]. Due to the strong asymmetry of effective masses in HgCdTe, the electron threshold energy is Eg while for holes it is 2Eg. Hole impact ionisation is therefore very unlikely until very high electric fields are reached as carriers must attain a minimum energy of 2 Eg with inefficient energy gain from the electric field. Electron impact ionisation is very likely, even at low electric fields, as the threshold energy is low and carriers can gain energy quickly while remaining in the low scattering environment of the gamma valley [69]. It should also be noted that due to the very low scattering rates and low threshold energy, electrons are able to travel ballistically before impact ionising in HgCdTe yielding noiseless gain [53, 64]. HgCdTe band structure is therefore optimised for stimulating electron impact ionisation while supressing that of holes.

Figure 1.8: The band structure of Hg<sub>0.7</sub>Cd<sub>0.3</sub>Te [65]

Figure 1.9: The band structure of InAs [70]

Figure 1.10: The band structure of InP [70]

| Energy given with  | Hg <sub>0.7</sub> Cd <sub>0.3</sub> Te [67]  | InAs [71]                  | InP [71]                   |

|--------------------|----------------------------------------------|----------------------------|----------------------------|

| respect to the V.B | 11g <sub>0.7</sub> Cu <sub>0.3</sub> 1C [07] |                            |                            |

| $E_g(eV)$          | 0.29                                         | 0.35                       | 1.35                       |

| $E_L(eV)$          | 1.79 (6.1E <sub>g</sub> )                    | 1.07 (3.05E <sub>g</sub> ) | 1.94 (1.44E <sub>g</sub> ) |

| $E_X(eV)$          | 2.79 (9.62E <sub>g</sub> )                   | 1.37 (3.91E <sub>g</sub> ) | 2.27 (1.68E <sub>g</sub> ) |

Table 1.1: A comparison of some band structure properties of Hg<sub>0.7</sub>Cd<sub>0.3</sub>Te, InAs and InP

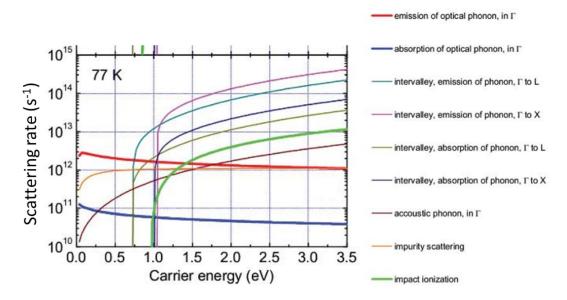

The band structure of InAs, shown in Figure 1.9, shares many similarities with HgCdTe, and not like other wide bandgap III-V semiconductors which are exemplified by the band structure of InP shown in Figure 1.10. Table 1.1 shows the X and L satellite valley energies compared to the bandgap energy for InAs, InP and HgCdTe. Electrons in both InAs and HgCdTe are able to gain the bandgap energy,  $\approx E_{th}$ , while remaining within the gamma valley. However, both satellite valleys within InP are less than 2Eg and consequently electrons in InP scatter around the lower mobility X and L valleys before able to gain Eth. While the impact ionisation process in InAs similar in principal to HgCdTe, the valley separation energies of InAs are relatively smaller and electrons begin to transfer out of the gamma valley in InAs at  $\approx 2.5 \text{ kVcm}^{-1}$  as observed in drift velocity simulations [72]. The impact ionisation coefficient below such electric fields is negligible and therefore although the gamma valley is deep, carriers are not as well confined to the gamma valley as they are in HgCdTe. Monte Carlo simulations have shown that the while significant energy is gained from the gamma valley, a significant fraction of electrons transfer over to the L valley before impact ionising [73, 74]. The implications of this are that the electron impact ionisation rate of InAs is slightly lower compared to HgCdTe. Furthermore the energy gain of carriers with increasing electric field within the L valley is poor. The electron impact ionisation coefficient of InAs is only weakly dependant on the electric field.

As the electron impact ionisation coefficient is relatively independent of electric field, higher gain in InAs APDs is achieved with thicker avalanche regions. The thick avalanche region also is used to suppress the tunnelling current while achieving high gain. However, the background doping of the avalanche region must be kept low so to maintain an even electric field across the APD.

Another peculiarity of InAs APDs is that for any given bias, the gain is observed to decrease with decreasing temperature [29, 75]. Carrier scattering rates decrease significantly with reducing temperature and consequently, carriers achieve higher energies for the same electric field strength before being scattered. However, in all semiconductors but some compositions of HgCdTe, the bandgap and thus the threshold energy increase with decreasing temperature. Usually the increase in bandgap is outweighed by the reduced scattering rates, however, simulations have shown that in InAs the dependence on threshold energy is dominant [73]. It should also be noted that this effect has also been observed in InSb, [45] and at low electric fields in In<sub>0.53</sub>Ga<sub>0.47</sub>As [33].

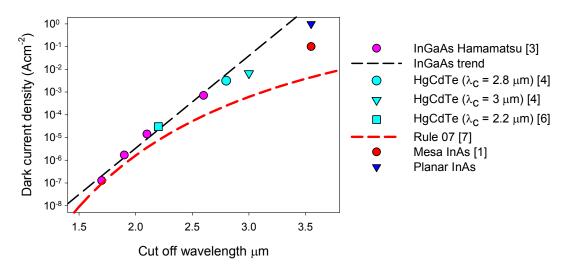

Recent work has focused in optimising the performance of InAs APDs reducing the dark current and achieving higher gain by maintain wide avalanche regions with low background doping. The dark current of mesa APDs has been shown to be dominated by a diffusion current between 300 and 175 K [76]. Low dark current has been achieved using a highly doped surface layer to increase the barrier to thermionic emission [77] and also a wide bandgap AlAs<sub>0.16</sub>Sb<sub>0.84</sub> blocking layer with a large conduction band offset within the P-type region to block the diffusion of electrons generated at the surface [59]. At temperatures below 200 K, Shockley Reed Hall (SRH) generation and recombination currents dominate the dark current generated from within the intrinsic region [74]. Furthermore, the optimised wet etching procedure is generally been reported to produce significant leakage current in small area InAs APDs or at low temperatures [76]. In a comparative study the polymer SU-8 was identified as the most suitable passivation layer for mesa InAs APDs [78]. A recent publication has shown the surface leakage can be eliminated with the immediate use of SU8 passivation after wet chemical etching to lock-in the surface conditions [74].

# 1.8 Motivation and thesis organisation

Remote sensing is rapidly gaining popularity with increasing interest at SWIR and MWIR wavelengths, however, a commercially available detector providing gain at wavelengths greater than 1.7 µm does not currently exist. Despite significant effort, HgCdTe APDs have not yet overcome the serious manufacturing issues, and the questions to whether these issues can be overcome are ever more pressing. Thermal detectors do not provide photon starved sensitivity while PMTs cannot operate at wavelengths longer than 1.7 µm. InAs is a widely accessible semiconductor with similar electronic properties to HgCdTe, but crucially, the potential for superior growth and fabrication which could promise high device yields on a comparatively cheap, and large area substrate. While InAs has a cut-off wavelength of InAs 3.5 µm, alloying with dilute amounts of Bismuth or Nitrogen has been shown to significantly reduce the bandgap energy while incurring minimal lattice strain for bandgap tuning; the first InAsBi photodiode was recently reported [79]. With InAs as a platform technology, a tuneable bandgap III-V semiconductor operating beyond telecommunications wavelengths could bring a tectonic shift in detector and sensing applications. However, current InAs APDs lack highly uniform and repeatable growth and fabrication procedure that is required to exploit InAs APDs for practical applications. All current InAs APDs utilise a mesa design, and although great progress has been made developing wet chemical etching procedures to reduce the surface leakage [59], complete removal of surface leakage current in small area mesa APDs remains a challenge and the surface chemistry of InAs remains poorly understood. Furthermore, while the excess noise of InAs APDs can compete with HgCdTe, the gain from the current mesa APDs is lower.

This thesis is primarily concerned with fabrication and characterisation of planar InAs APDs to achieve high gain. The motivation and summary of individual chapters are given below.

#### Chapter 2:

Background information on the core topics discussed in this thesis are presented including literature reviews on impact ionisation, avalanche gain, excess noise, ion implantation, annealing, premature breakdown in planar APDs and methods of mitigating the formation of electric field hotspots.

### Chapter 3:

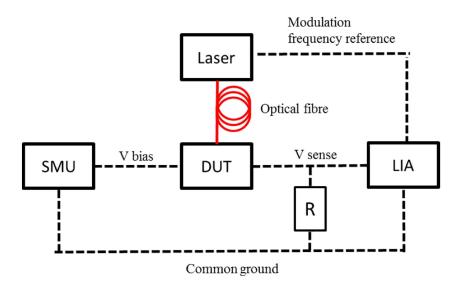

Figures of merit for detectors are discussed in addition to experimental techniques used to characterise InAs APDs in this thesis. The experimental techniques discussed are current-voltage (I-V), capacitance-voltage (C-V), responsivity and gain.

# Chapter 4:

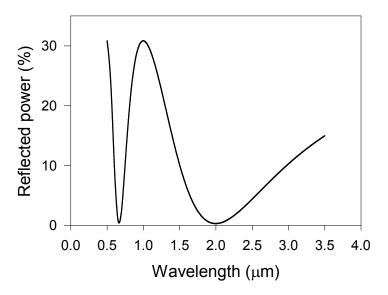

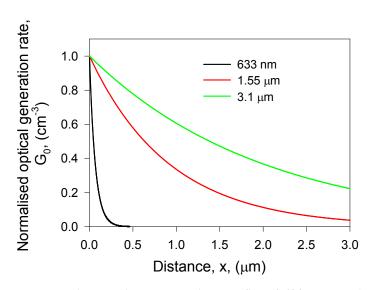

Photodiodes and APDs based on mature semiconductors such as Si, InGaAs/InP [80], InSb [81] and HgCdTe [82] utilise a planar topology to benefit from a simplified and economic fabrication process with high manufacturing yields, device uniformity and reliability, and excellent control over surface conditions. Furthermore adopting a planar topology gives additional degrees of freedom to design advanced heterostructures using wide bandgap lattice matched alloys. In order to fabricate planar InAs APDs, selective area doping techniques must be utilised, however, there are few reports of Zn diffusion or ion implantation into InAs. Zn diffusion has been utilised to fabricate planar InAs photodiodes with good results [83], however, Zn diffusion is unfavourable when fabricating low noise InAs APDs as the poor dopant control results in unavoidable doping near the saturation limit  $(\approx 3 \times 10^{19} \text{ cm}^{-3})$  with a very short minority carrier diffusion length in Zn diffused material. To maintain low excess noise within InAs APDs, photons should be absorbed within the Ptype layer, however, the thickness of the Zn diffused P-type required for high photon absorption is significantly longer than the minority carrier diffusion length. Consequently high responsivity could not be achieved with low excess noise. Ion implantation is a far more versatile selective area doping technique with excellent control over the doping profile and density. However, there are very few reports of ion implantation for P-type doping in InAs. A literature review of ion implantation for P-type doping is presented with Be implantation found to be the most suitable. Through the characterisation of diodes fabricated using Be implantation, the activation of Be in unannealed material was found to be poor. Annealing was investigated, and an optimised implantation and annealing procedure developed for selective area P-type doping InAs. The use of hot implants to reduce the

implant damage was also investigated. A procedure for fabricating planar InAs photodiodes was developed and the bulk and surface leakage currents of planar InAs photodiodes analysed. Diffusion of the Be implantation profile caused by annealing and hot implants were investigated using secondary ion mass spectroscopy (SIMS). The dominant leakage mechanisms in InAs photodiodes are discussed and optimised Be implantation profiles are investigated to maximise the detectivity of planar photodiodes. The detectivity is compared to other reports of planar and mesa InAs photodiodes fabricated using various methods. The majority of this work has been published in IEEE Transactions on Electron Devices [84].

### Chapter 5:

Planar APDs were fabricated from 2 wafers, one of which had a very wide intrinsic region with low background doping to achieve very high gain. The activation energies of the bulk and surface leakage mechanisms were determined through analysing the temperature dependence of the dark current of planar APDs. The depletion width and background doping of high gain APDs were characterised and found to equal the largest reported for a mesa InAs APD. Due to the large depletion region, the gain at 200 K was the largest achieved for any InAs APD. The breakdown conditions of InAs APDs were investigated and it was found that the positive temperature dependence of the electron impact ionisation coefficient causes a thermal runaway in hotspots in planar InAs APDs biased near breakdown. Guard rings are designed to prevent the formation of electric field hotspots. The effectiveness of various guard ring structures was investigated from room temperature to 77 K and the results discussed. Recommended improvements to planar InAs APDs are discussed. The majority of this work has been published in IEEE Journal of Lightwave Technology [85].

# Chapter 6:

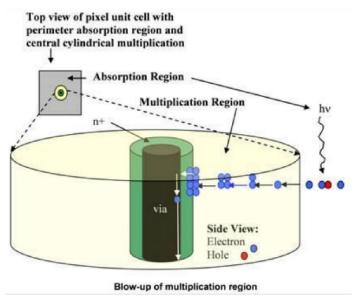

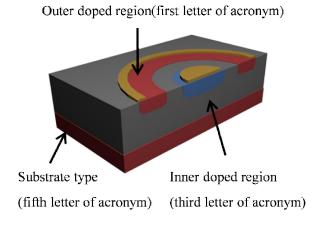

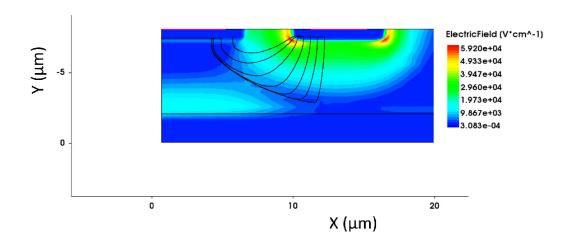

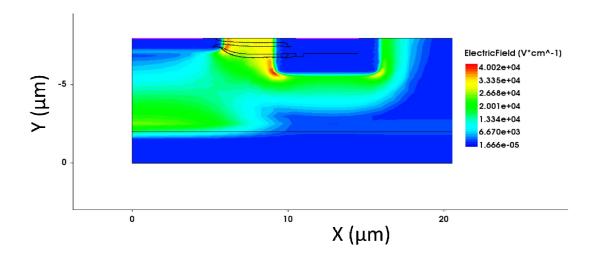

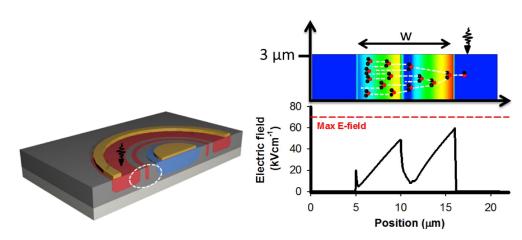

It is becoming increasingly difficult and impractical to grow the thick structures with very low background doping to achieve gain in InAs APDs. To reduce the stringent growth requirements, a structure in which the avalanche gain develops laterally, perpendicular to the direction of growth, is discussed. The advantage of the lateral APDs is that it can be fabricated from only a thin layer of InAs. Various lateral APDs were simulated with an optimised device identified. N-type selective area doping using Si ion implantation and annealing were developed, and along with Be implantation, utilised to fabricate a range of lateral APDs. Responsivity measurements along with electric field simulations were performed to establish the carrier extraction mechanisms of the lateral APD structures. In a comparative gain study, enhanced lateral gain was measured in an optimised lateral APD structure. A conclusion to the work on lateral APDs presented in this thesis is presented before the recommended future direction for developing lateral APDs is discussed.

#### Chapter 7:

A conclusion to the work contained in this thesis is presented.

#### **Chapter 8:**

Based on the conclusions and drawing from my experiences, areas to prioritise future work are suggested.

#### Chapter 9:

The appendices to this works are contained.

# 1.9 References

- [1] C. Canali, G. Majni, R. Minder, and G. Ottaviani, "Electron and hole drift velocity measurements in silicon and their empirical relation to electric field and temperature," *IEEE Transactions on Electron Devices*, vol. 22, pp. 1045-1047, 1975.

- [2] J. L. Thobel, L. Baudry, A. Cappy, P. Bourel, and R. Fauquembergue, "Electron transport properties of strained InxGa1-xAs," *Applied Physics Letters*, vol. 56, pp. 346-348, 1990.

- [3] E. F. Schubert, T. Gessmann, and J. K. Kim, *Light emitting diodes*: Wiley Online Library, 2005.

- [4] M. Fox, *Optical properties of solids* vol. 3: Oxford university press, 2010.

- [5] R. K. Ahrenkiel, R. Ellingson, S. Johnston, and M. Wanlass, "Recombination lifetime of In0.53Ga0.47As as a function of doping density," *Applied Physics Letters*, vol. 72, pp. 3470-3472, 1998.

- [6] A. Rogalski, K. Adamiec, and J. Rutkowski, *Narrow-gap semiconductor photodiodes* vol. 77: SPIE Press, 2000.

- [7] H. H. Wieder and D. A. Collins, "Minority carrier lifetime in InAs epilayers," *Applied Physics Letters*, vol. 25, pp. 742-743, 1974.

- [8] Y. Zhang, Y. Gu, C. Zhu, G. Hao, A. Li, and T. Liu, "Gas source MBE grown wavelength extended 2.2 and 2.5 μm InGaAs PIN photodetectors," *Infrared physics & technology*, vol. 47, pp. 257-262, 2006.

- [9] J. D. Kim, S. Kim, D. Wu, J. Wojkowski, J. Xu, J. Piotrowski, *et al.*, "8–13 μm InAsSb heterojunction photodiode operating at near room temperature," *Applied Physics Letters*, vol. 67, pp. 2645-2647, 1995.

- [10] A. Rogalski, "HgCdTe infrared detector material: history, status and outlook," *Reports on Progress in Physics*, vol. 68, p. 2267, 2005.

- [11] S. Johnson, M. Kalisher, W. Ahlgren, J. James, and C. Cockrum, "HgCdTe 128× 128 infrared focal plane arrays on alternative substrates of CdZnTe/GaAs/Si," *Applied Physics Letters*, vol. 56, pp. 946-948, 1990.

- [12] W. E. Tennant, C. A. Cockrum, J. B. Gilpin, M. A. Kinch, M. B. Reine, and R. P. Ruth, "Key issues in HgCdTe-based focal plane arrays: An industry perspective," *Journal of Vacuum Science & Technology B*, vol. 10, pp. 1359-1369, 1992.

- [13] W. E. Spicer, J. A. Silberman, I. Lindau, A. B. Chen, A. Sher, and J. A. Wilson, "Band gap variation and lattice, surface, and interface "instabilities" in Hg1-xCdxTe and related compounds," *Journal of Vacuum Science & Technology A*, vol. 1, pp. 1735-1743, 1983.

- [14] B. Sharma, *Metal-semiconductor Schottky barrier junctions and their applications*: Springer Science & Business Media, 2013.

- [15] M. Kinch, "Metal-insulator-semiconductor infrared detectors," *Semiconductors and semimetals*, vol. 18, pp. 313-378, 1981.

- [16] M. D. Petroff and M. G. Stapelbroek, "Blocked impurity band detectors," ed: Google Patents, 1986.

- [17] A. Rogalski, "Quantum well photoconductors in infrared detector technology," *Journal of Applied Physics*, vol. 93, pp. 4355-4391, 2003.

- [18] D. L. Smith and C. Mailhiot, "Proposal for strained type II superlattice infrared detectors," *Journal of Applied Physics*, vol. 62, pp. 2545-2548, 1987.

- [19] J. H. Davies, *The physics of low-dimensional semiconductors: an introduction*: Cambridge university press, 1997.

- [20] A. Rogalski, "Infrared detectors: status and trends," *Progress in quantum electronics*, vol. 27, pp. 59-210, 2003.

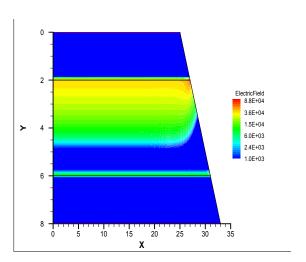

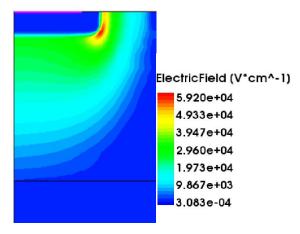

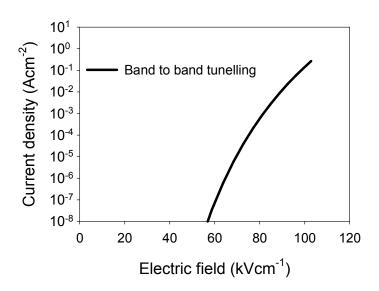

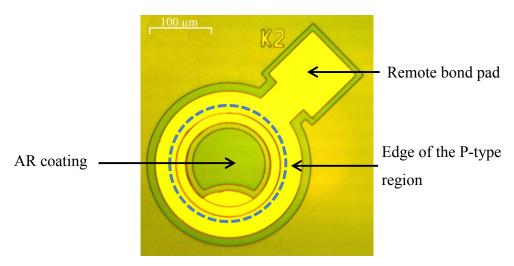

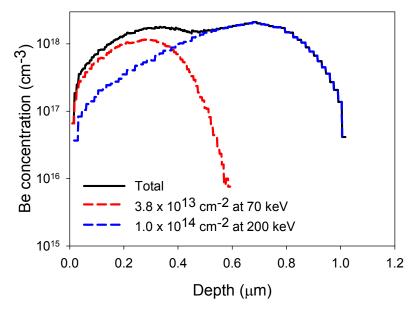

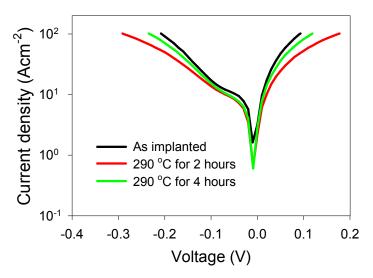

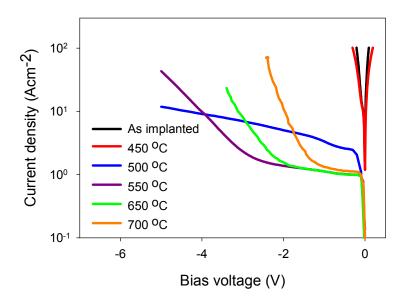

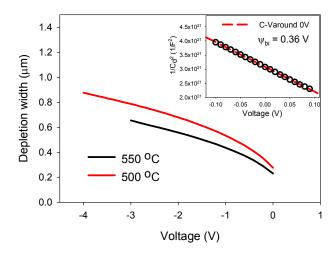

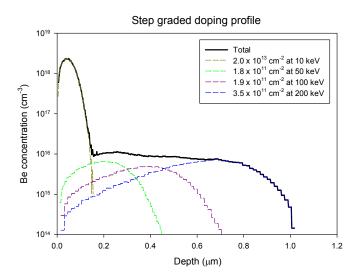

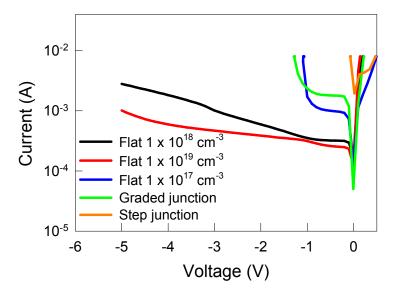

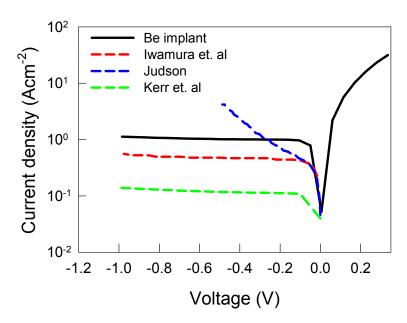

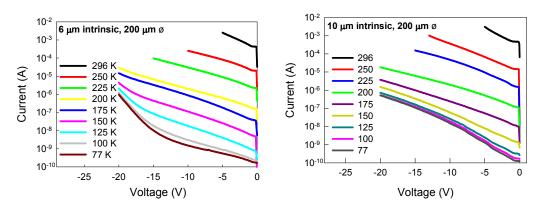

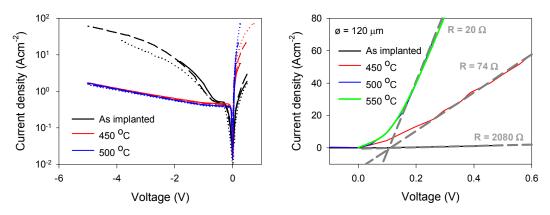

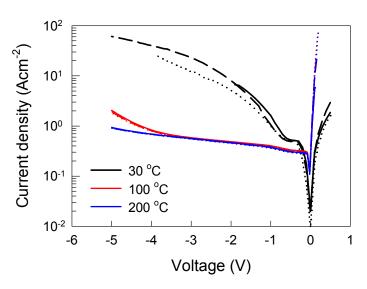

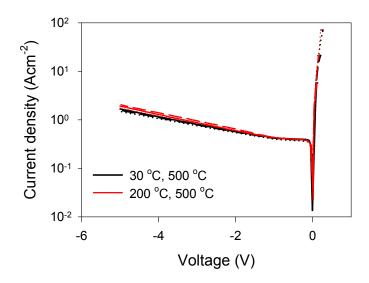

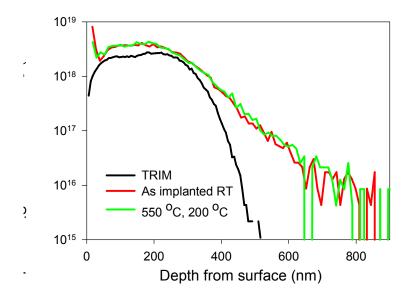

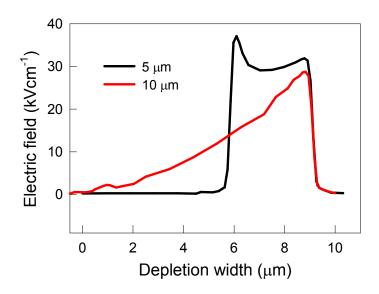

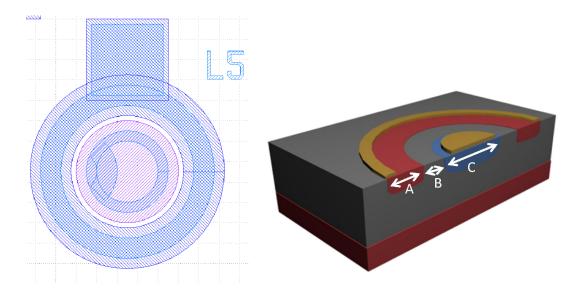

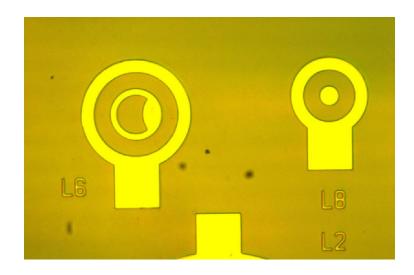

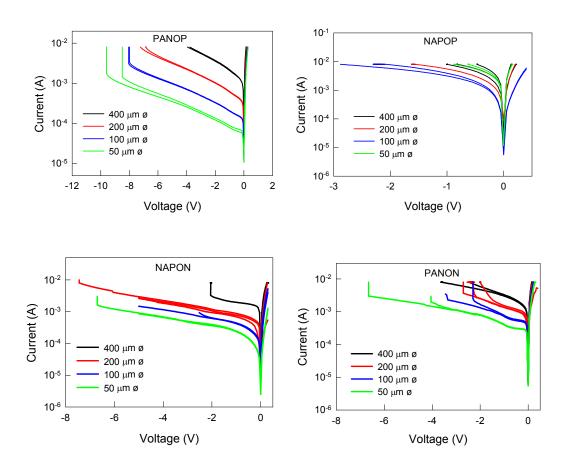

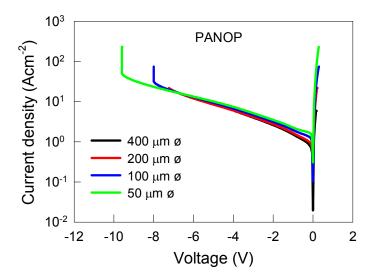

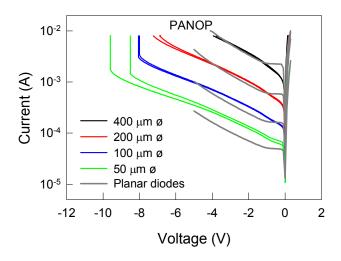

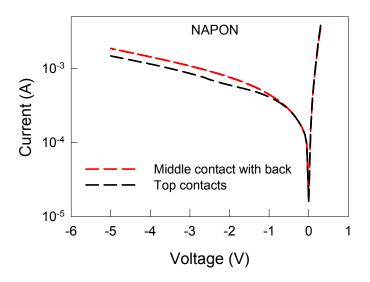

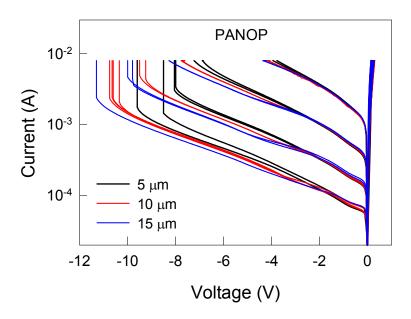

- [21] A. E. Iverson and D. L. Smith, "Mathematical modeling of photoconductor transient response," *IEEE Transactions on Electron Devices*, vol. 34, pp. 2098-2107, 1987.