# Efficient Design and Implementation of Elliptic Curve Cryptography on FPGA

By

Zia Uddin Ahamed Khan

Thesis submitted for the Degree of Doctor of Philosophy

Department of Electronic & Electrical Engineering

The University of Sheffield

October-2015

ı

#### **Abstract**

This thesis is concerned with challenging the design space of Elliptic Curve Cryptography (ECC) over binary Galois Field,  $GF(2^m)$  in hardware on field-programmable gate array (FPGA) in terms of area, speed and latency. Novel contributions have been made at the algorithmic, architectural and implementation levels that produced leading performance figures in terms of key hardware implementation metrics on FPGA. This demonstrated performance will enable ECC to be deployed across a range of application requiring public key security using FPGA technology. The proposed low area ECC implementation outperforms relevant state of the art in both area-time and area<sup>2</sup>-time metrics.

The proposed high throughput ECC implementation adopts a new digit serial multiplier over  $GF(2^m)$  incorporating a novel pipelining technique along with algorithmic and architectural level modification to support parallel operations in the arithmetic level. The resulting throughput/area performance outperforms state of the art designs on FPGA to date.

The proposed high-speed only implementation utilises a new full-precision multiplier and smart point multiplication scheduling to reduce the latency. The resulting high speed ECC design with three multipliers achieves the lowest reported latency figure to date with high speed (450 clock cycles to get 2.83 µs on Virtex7).

Finally, the proposed low resources scalable ECC implementation is based on very low latency multiprecision multiplication and low latency multiprecision squaring. The scalable ECC point multiplication design over all NIST curves consumes very low latency and shows the best area-time performance on FPGA to date.

ı

#### Acknowledgements

I am extremely grateful that my supervisor Dr. Mohammed Benaissa offered me a PhD position in the University of Sheffield. His guidance and expertise in my research field have been played a central role over the four years of my PhD research. Foremost, my sincere thank to my supervisor for everything that he did. I truly appreciate him.

I am very pleased with my examiners, Professor Said Boussakta and Dr Jonathan M. Rigelsford. I honestly thank both of my examiners for their dedication in reading my thesis, for a friendly viva, and their important suggestions to improve my thesis presentation.

I like to thank my colleagues and friends for their support throughout my PhD. I like to acknowledge Dr. M. Nabil Hassan and Dr. J. Chu, who were PhD students of my supervisor, for helping me to start my cryptography research, and Dr. S.Tan, who was a research scholar in my lab, for his support to develop new algorithms for my multiprecision arithmetic operation. I am also grateful to Russ Drieberg, a kind colleague for his work in proofreading my thesis and Sandipan Pal, PhD student, for his support during preparation of my thesis. I would like to thank Dr. Tim Good, Dr. Luke Seed and Neil Powel for their support in the FPGA implementations and presentation of the implementation results. I also like to thank Professor John David, who was head of my department, for supporting me by providing a departmental scholarship in my PhD. I always appreciate Hilary Levesley, PGR administrator, for her outstanding support. I am also thankful to Dr. Wei Liu and Dr. Charith Abhayaratne for their friendly attitude to me.

I would also like to thank my lab mates who became my friends and made my study enjoyable. I am also thankful to my Bangladeshi friends with whom I relished my PhD time.

Last, but not least, thanks to my wife, Farzana Yousuf Anee (MD in internal medicine) and our parents for their ultimate sacrifice and support to complete my PhD. I would also like to thank to my brothers and sisters for their motivation.

To all of you, I am eminently grateful to you. Thank you very much!

Zia Uddin Ahamed Khan

Sheffield

11/06/2016

#### **Contents**

| Abstract                                               | i    |

|--------------------------------------------------------|------|

| Acknowledgements                                       | ii   |

| Contents                                               | iii  |

| Table of Figures                                       | viii |

| List of Tables                                         | X    |

| List of Algorithms                                     | xi   |

| Glossary                                               | xii  |

| Chapter 1 Introduction of Thesis                       | 1-1  |

| 1.1 Overview                                           | 1-2  |

| 1.2 Motivation                                         | 1-3  |

| 1.3 Thesis Main Contributions                          | 1-5  |

| 1.4 Thesis Outlines                                    | 1-9  |

| 1.5 Published Papers                                   | 1-10 |

| Chapter 2 Background                                   | 2-1  |

| 2.1 Introduction                                       | 2-2  |

| 2.2 Cryptography Basics                                | 2-2  |

| 2.3 Cryptography Schemes                               | 2-4  |

| 2.3.1 Symmetric Key Cryptography                       | 2-4  |

| 2.3.2 Public Key Cryptography                          | 2-5  |

| 2.3.3 Hash Functions                                   | 2-7  |

| 2.4 Elliptic Curve Cryptography                        | 2-8  |

| 2.5 Finite Field Theory                                | 2-9  |

| 2.5.1 Binary extension field $GF(2^m)$                 | 2-11 |

| 2.5.2 Representation of Finite Field                   | 2-13 |

| 2.5.3 Finite field arithmetic over $GF(2^m)$           | 2-13 |

| 2.6 Elliptic Curve Arithmetic                          | 2-19 |

| 2.6.1 Elliptic Curve over Binary Fields                | 2-20 |

| 2.6.3 Advantages of Projective Coordinates             | 2-21 |

| 2.6.4 The Main Operation of ECC - Point Multiplication | 2-22 |

| 2.7 Koblitz Curve                                      | 2-27 |

| 2.8 Domain Parameters of ECC                                     | 2-28 |

|------------------------------------------------------------------|------|

| 2.9 Elliptic Curve Cryptography Protocols                        | 2-29 |

| 2.9.1 Elliptic Curve Key Generation                              | 2-29 |

| 2.9.2 Elliptic curve Diffie-Hellman key exchange (ECDH)          | 2-29 |

| 2.9.3 ElGamal Elliptic Curve Cryptosystem                        | 2-30 |

| 2.9.4 Elliptic Curve Digital Signature Algorithm (ECDSA)         | 2-30 |

| 2.10: Design and Implementation Issues of ECC                    | 2-32 |

| 2.10.1 Implementation of Point Multiplication                    | 2-32 |

| 2.10.2 Why Hardware design is suitable for the crypto processor? | 2-34 |

| 2.10.3 Hardware platform-FPGA                                    | 2-34 |

| 2.10.4 Design flow                                               | 2-36 |

| 2.10.5 Design metrics                                            | 2-37 |

| Chapter 3 Low Area elliptic Curve Cryptography                   | 3-1  |

| 3.1 Introduction                                                 | 3-2  |

| 3.2 Background                                                   | 3-3  |

| 3.2.1 Koblitz Curves based ECC                                   | 3-3  |

| 3.2.2 Low Area Multiplier                                        | 3-5  |

| 3.2.3 Low Area Square Circuit                                    | 3-5  |

| 3.2.4 Inversion operation                                        | 3-5  |

| 3.3 Low Area ECC Implementation using Montgomery algorithm       | 3-7  |

| 3.4 Low Area ECC Implementation using Binary Algorithm           | 3-8  |

| 3.5 Frobenius Map based Low Area ECC Implementation              | 3-9  |

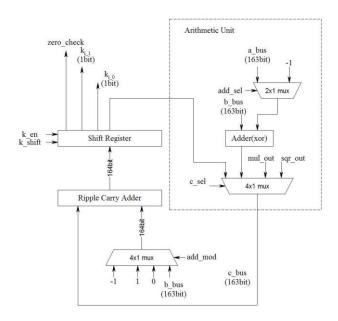

| 3.6 Arithmetic circuit                                           | 3-10 |

| 3.6.1 Frobenius mapping unit:                                    | 3-11 |

| 3.7 Memory unit                                                  | 3-13 |

| 3.8 Interface unit                                               | 3-14 |

| 3.9 Control Unit                                                 | 3-15 |

| 3.10 Latency of the proposed ECC operation                       | 3-16 |

| 3.11 FPGA Implementation Results                                 | 3-17 |

| 3.11.1 Analysis of the results                                   | 3-19 |

| 3.12 Conclusions                                                 | 3-25 |

| Chapter 4 Implementing High Throughput/Area Elliptic Curve Cryptog    | raphy 4-1            |

|-----------------------------------------------------------------------|----------------------|

| 4.1 Introduction                                                      | 4-2                  |

| 4.2 Background                                                        | 4-4                  |

| 4.3 Resource Constrained High Throughput ECC                          | 4-5                  |

| 4.4 Proposed throughput/area Efficient ECC processor                  | 4-5                  |

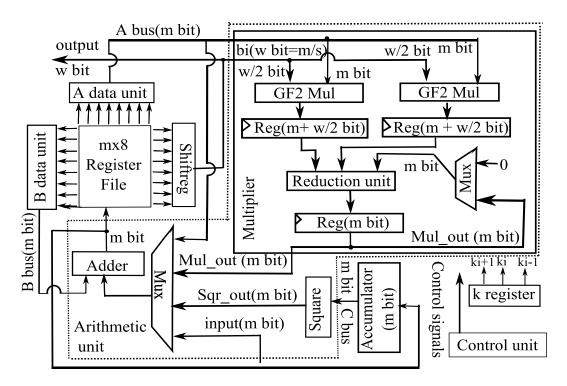

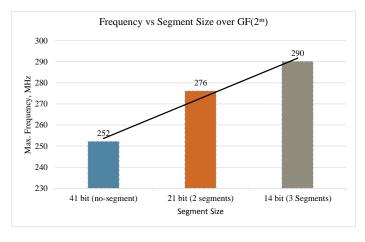

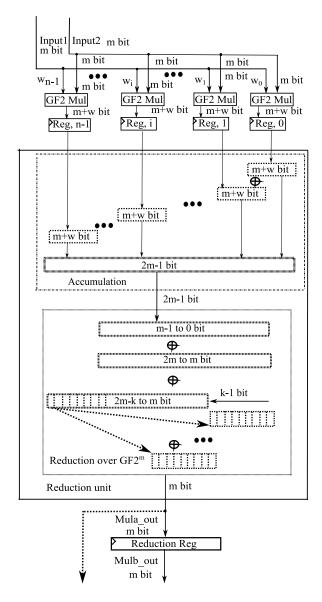

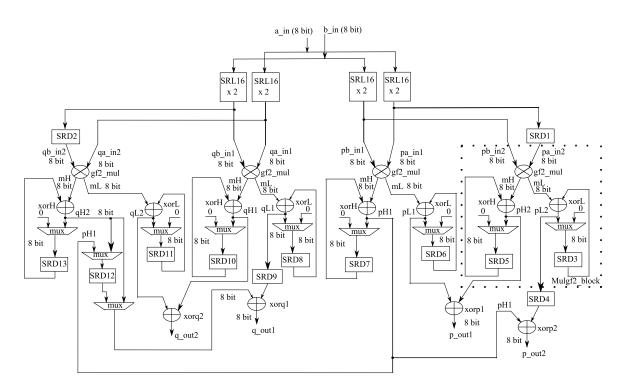

| 4.4.1 Segmented Pipelining Based Digit Serial Multiplier              | 4-6                  |

| 4.4.2 Optimized Memory Unit                                           | 4-8                  |

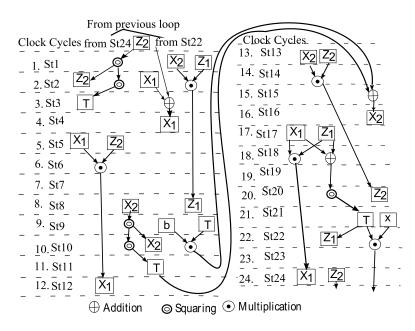

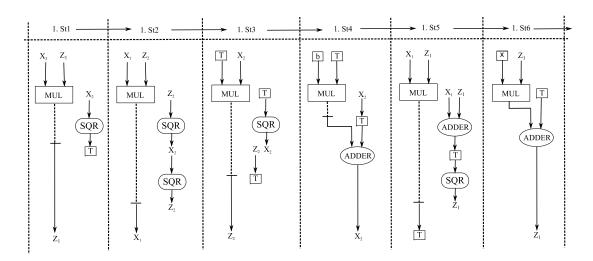

| 4.4.3 Scheduling for point operations                                 | 4-9                  |

| 4.5 Implementation on FPGA and Results                                | 4-10                 |

| 4.5.1 Analysis of the Results                                         | 4-12                 |

| 4.6 Conclusion                                                        | 4-15                 |

| Chapter 5 Implementing High Speed Elliptic Curve Cryptography         | 5-1                  |

| 5.1 Introduction                                                      | 5-2                  |

| 5.2 Background                                                        | 5-4                  |

| 5.2.1 High Speed Scalar Point Multiplication                          | 5-4                  |

| 5.2.2 Field Arithmetic over $GF(2^m)$                                 | 5-6                  |

| 5.3 Proposed Full-precision Multiplier for High Speed ECC Application | ion 5-6              |

| 5.3.1 Multiplier with Segmented Pipelining                            | 5-8                  |

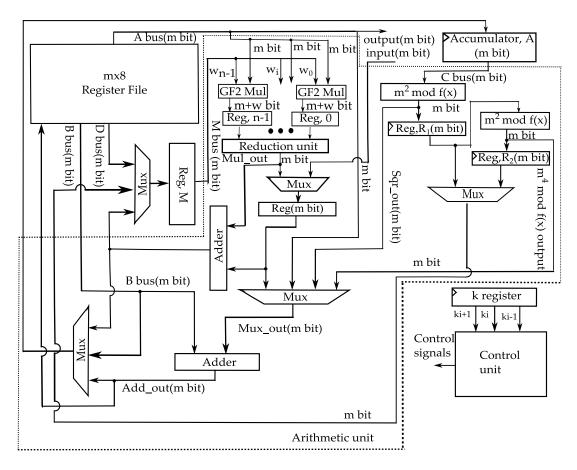

| 5.4 Proposed High Performance ECC (HPECC) for Point Multiplication    | ion 5-9              |

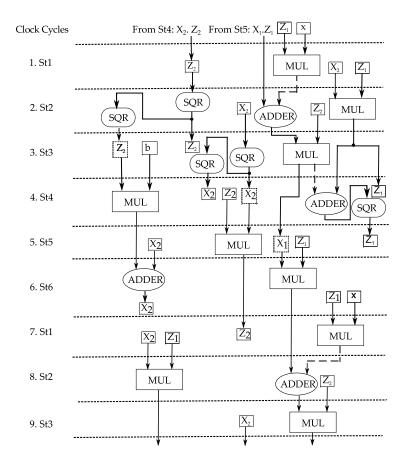

| 5.4.1 Point Multiplication without Pipelining Delay                   | 5-9                  |

| 5.4.2 Multiplier with Segmented Pipelining for HPECC                  | 5-15                 |

| 5.4.3 Square Circuit, Memory Unit and Control Unit of HPECC           | C 5-15               |

| 5.4.4 Critical path delay and clock cycles of the HPEEC               | 5-17                 |

| 5.5 Proposed the highest possible frequency based ECC (HFECC) for     | Point Multiplication |

|                                                                       | 5-18                 |

| 5.5.1 Low latency Point Multiplication Shecdualing for HFECC          | 5-18                 |

| 5.5.2 Square Circuits, field Inversion operation and coordinates con  |                      |

|                                                                       |                      |

| 5.5.3 Memory Unit and Control Unit of HFECC                           |                      |

| 5.5.4 Pipelining in the ECC Architecture of HFECC                     |                      |

| 5.6 Proposed Low Latency ECC (LLECC) Processor for Point Multip       | olication 5-23       |

| 5.6.2        | Multiplier with Segmented Pipelining for LLECC                           | 5-28         |

|--------------|--------------------------------------------------------------------------|--------------|

| 5.6.3        | Square Circuit, Memory Unit and Control Unit of LLECC                    | 5-28         |

| 5.6.4        | Critical path delay and clock cycles of the LLEEC                        | 5-29         |

| 5.7 Imp      | plementation Results                                                     | 5-30         |

| 5.7.1 Aı     | nalysis of Results                                                       | 5-31         |

| 5.7.2 Co     | omparison with state of the art                                          | 5-34         |

| 5.8 Co       | nclusions                                                                | 5-38         |

| Chapter 6 Lo | ow Latency Multiprecision Arithmetic Circuit based Scalable ECC ov       | er $GF(2^m)$ |

|              |                                                                          | 6-1          |

| 6.1 Introd   | uction                                                                   | 6-2          |

| 6.2 Backg    | round                                                                    | 6-6          |

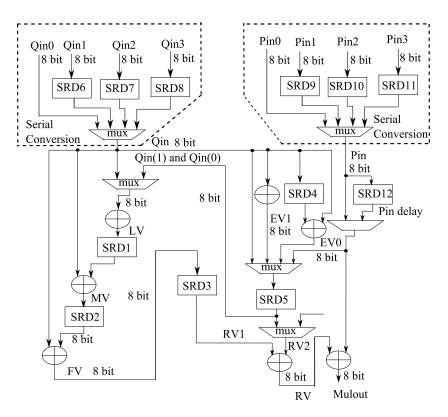

| 6.2.1 Co     | omba Multiprecision Multiplication over $GF(2^m)$                        | 6-8          |

| 6.2.2 M      | ultiprecision squaring over $GF(2^m)$                                    | 6-10         |

| 6.2.3 M      | ultiprecision modular reduction over $GF(2^m)$                           | 6-10         |

| 6.2.4 In     | version and Multiprecision Addition over $GF(2^m)$                       | 6-11         |

| 6.3 Implei   | menting Multiprecision Multiplier over $GF(2^m)$                         | 6-11         |

| 6.3.1 Pr     | eliminary of the Multiprecision Multiplier over $GF(2^m)$                | 6-11         |

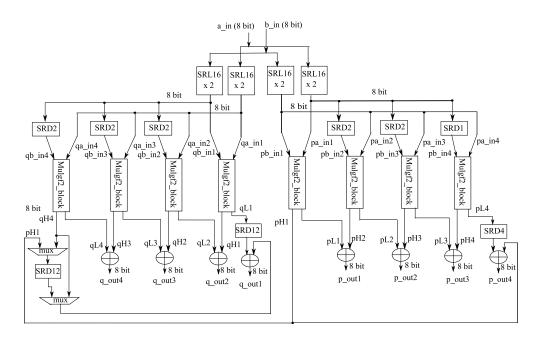

| 6.3.2 Pr     | oposed Comba Multiprecision Multiplier over $GF(2^m)$                    | 6-13         |

| 6.3.3 Im     | nplementation of Proposed Comba Multiprecision Multiplier on FPGA        | 6-17         |

| 6.3.4 Im     | nplementing Two-and-two <i>GF2MUL</i> based Multiprecision Multiplier of |              |

|              | nplementing Four-and-Four <i>GF2MUL</i> based Multiprecision Multiplier  |              |

|              | aplementing On-the-fly Reduction Unit for Multiprecision Multiplier of   |              |

|              | nalytical Comparison of multiprecision multipliers on FPGA               |              |

| 6.4 Implei   | menting Proposed Multiprecision Square Circuit                           | 6-31         |

| 6.4.1 No     | ovel Architecture of Multiprecision Square Circuit with On-the-Fly Re    | eduction     |

|              |                                                                          | 6-31         |

| 6.4.2 Re     | epeated Squaring                                                         | 6-35         |

| 6.4.3 Co     | omparison with relevant square circuit and discussion                    | 6-36         |

| 6.5 Propos   | sed Hardware Architecture of Scalable ECC                                | 6-37         |

| 6.5.1 Proposed Montgomery Point Multiplication            | 6-39 |

|-----------------------------------------------------------|------|

| 6.5.2 Careful Scheduling for Point Multiplication         | 6-40 |

| 6.5.3 Proposed Scalable Multiprecision Multiplier Circuit | 6-43 |

| 6.5.4 Proposed Scalable Multiprecision Square circuit     | 6-43 |

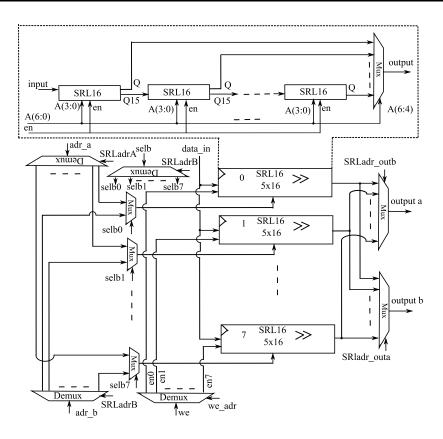

| 6.5.5 SRL16 based Register file                           | 6-45 |

| 6.6 Implementation Results                                | 6-47 |

| 6.7 Conclusion                                            | 6-50 |

| Chapter 7 Conclusions and Future Research Work            | 7-1  |

| 7.1 Conclusions                                           | 7-2  |

| 7.1 Future Research Works                                 | 7-4  |

| References                                                | 1 -  |

#### **Table of Figures**

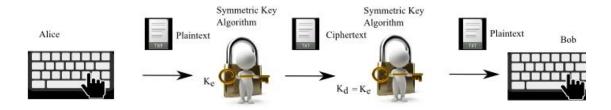

| Figure 2.1 Symmetric key cryptography based communication system                                   | 2-4     |

|----------------------------------------------------------------------------------------------------|---------|

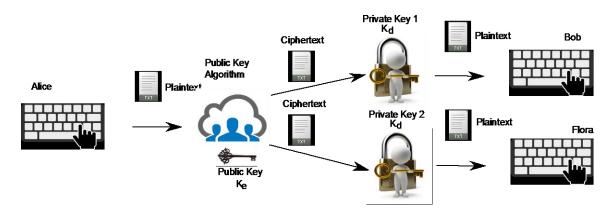

| Figure 2.2 Public key cryptography based communication                                             | 2-5     |

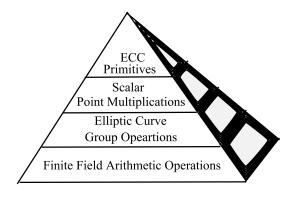

| Figure 2.3 ECC hierarchy diagram                                                                   | 2-9     |

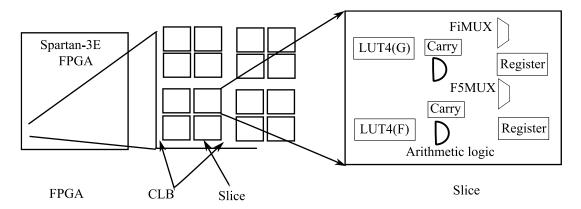

| Figure 2.4 Slice in Spartan 3E FPGA                                                                | 2-36    |

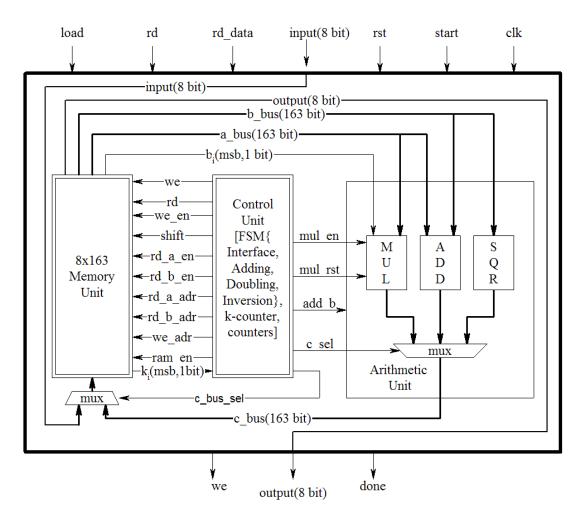

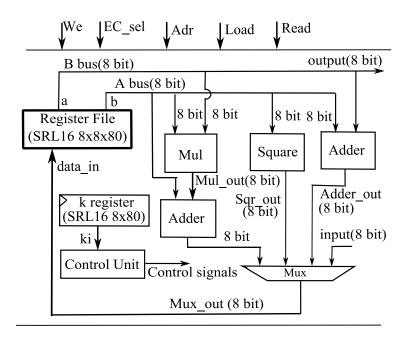

| Figure 3.1 Low area ECC system architecture                                                        | 3-6     |

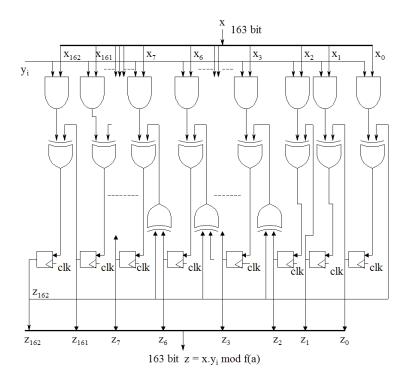

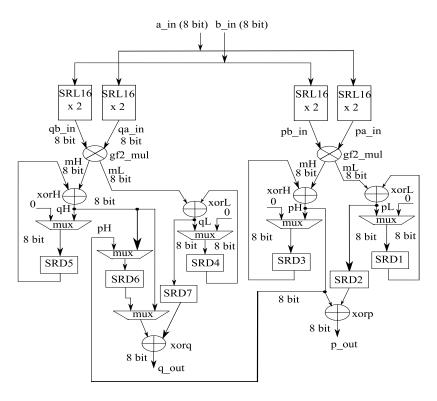

| Figure 3.2 Finite field multiprecision multiplier over $GF(2^{163})$                               | 3-11    |

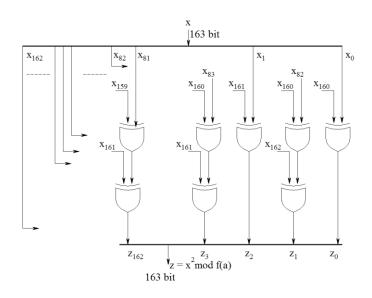

| Figure 3.3 Finite field square circuit over $GF(2^{163}$                                           | 3-11    |

| Figure 3.4 Frobenius mapping unit                                                                  | 3-12    |

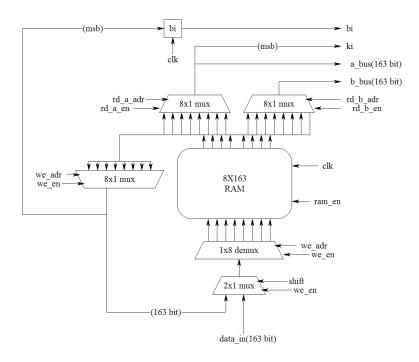

| Figure 3.5 8xm memory unit                                                                         | 3-13    |

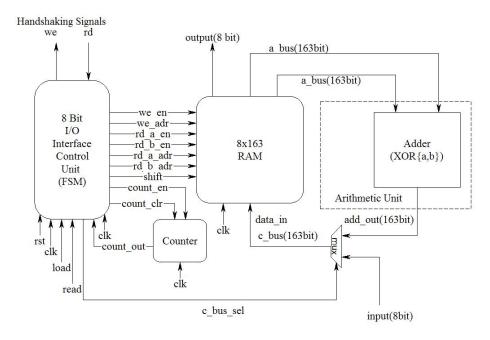

| Figure 3.6 8-bit input/output interface                                                            | 3-14    |

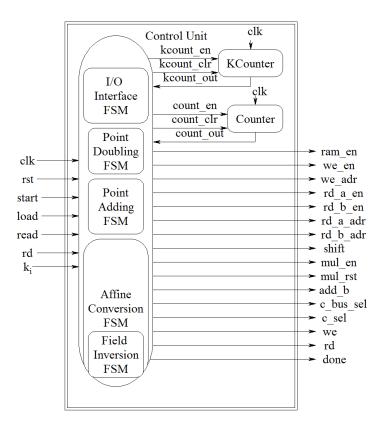

| Figure 3.7 FSM based control unit                                                                  | 3-15    |

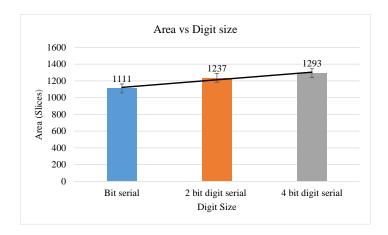

| Figure 3.8 Area vs digit size over $GF(2^{163})$ in S3 for Montgomery method                       | 3-20    |

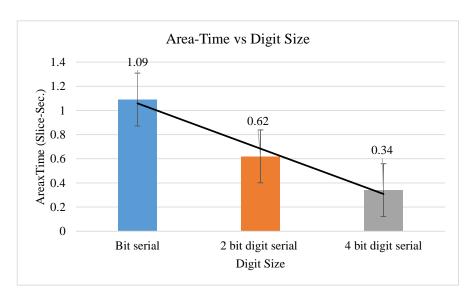

| Figure 3.9 Area-time vs digit size over $GF(2^{163})$ in S3 for Montgomery method                  | 3-20    |

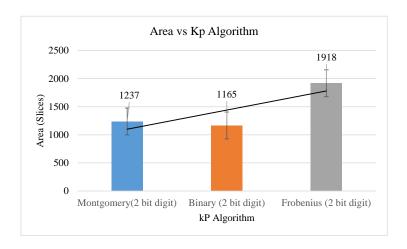

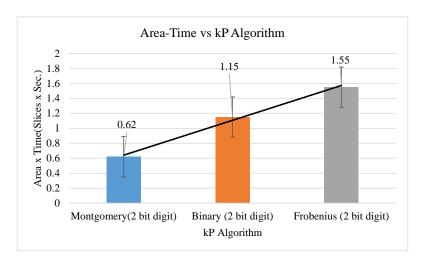

| Figure 3.10 Area vs $kP$ algorithm (2 bit digit serial) over $GF(2^{163})$                         | 3-21    |

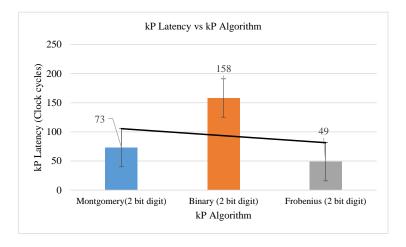

| Figure 3.11 Latency vs $kP$ algorithm (2-bit digit serial) over $GF(2^{163})$                      | 3-21    |

| Figure 3.12 Area-time vs kP algorithm (2-bit digit serial) over $GF(2^{163})$                      | 3-22    |

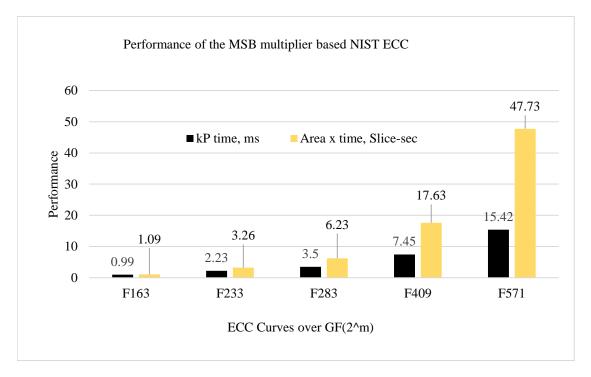

| Figure 3.13 Performance of bit-serial multiplier based ECC over all NIST curves                    | 3-23    |

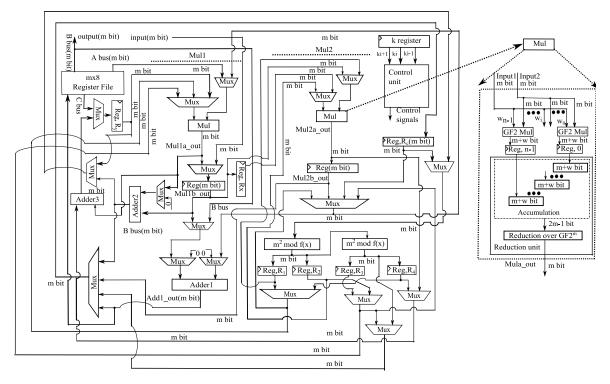

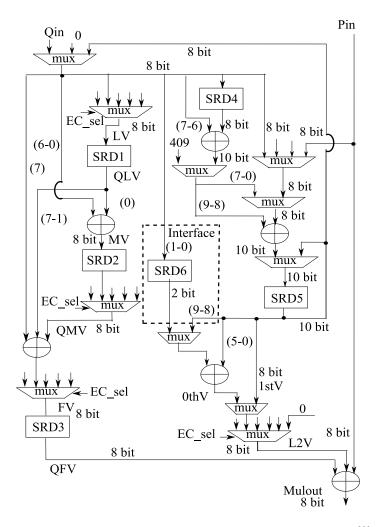

| Figure 4.1 Proposed throughput/area efficient ECC architecture (for n=2)                           | 4-6     |

| Figure 4.2 Proposed careful scheduling (4 clock cycles/multiplication)                             | 4-9     |

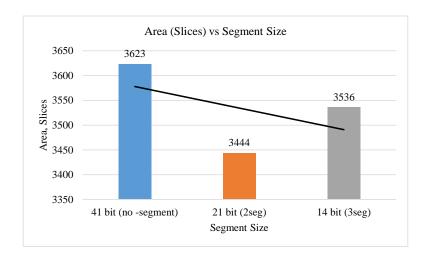

| Figure 4.3 Frequency vs segment size of the ECC over $GF(2^{163})$                                 | 4-12    |

| Figure 4.4 Area vs segment size of the ECC over $GF(2^{163})$                                      |         |

| Figure 4.5 Throughput/slices vs segment size of the ECC over $GF(2^{163})$                         | 4-13    |

| Figure 5.1 Proposed segmented pipelining based full-precision multiplier over $GF(2^m)$            | 5-7     |

| Figure 5.2 Proposed high performance ECC architecture                                              | 5-11    |

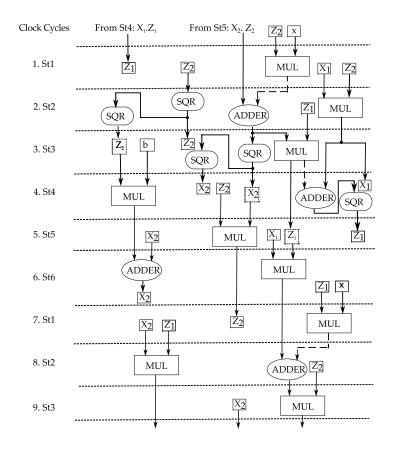

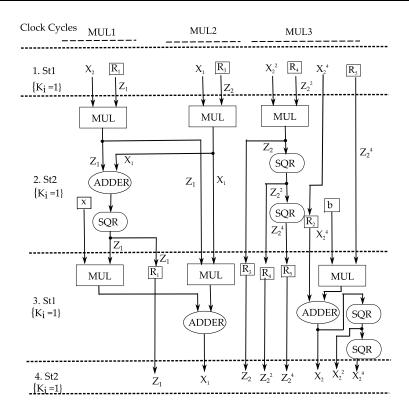

| Figure 5.3 Data flow of HPECC for $k_{i+1} = 1$ , $k_i = 1$ and $k_{i-1} = 1$                      | 5-13    |

| Figure 5.4 Data flow of HPECC for $k_{i+1} = 0$ , $k_i=1$ and $k_{i-1} = 1$                        | 5-14    |

| Figure 5.5 Proposed HFECC architecture for the high speed point multiplication                     | 5-19    |

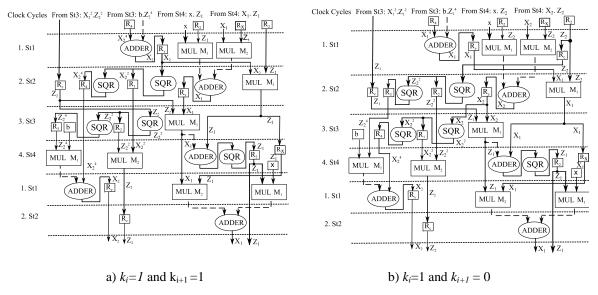

| Figure 5.6 Main loop operations with the $k_i$ values, including: a) $k_i=1$ and $k_{i+1}=1$ and b | $k_i=1$ |

| and $k_{i+1} = 0$                                                                                  | 5-20    |

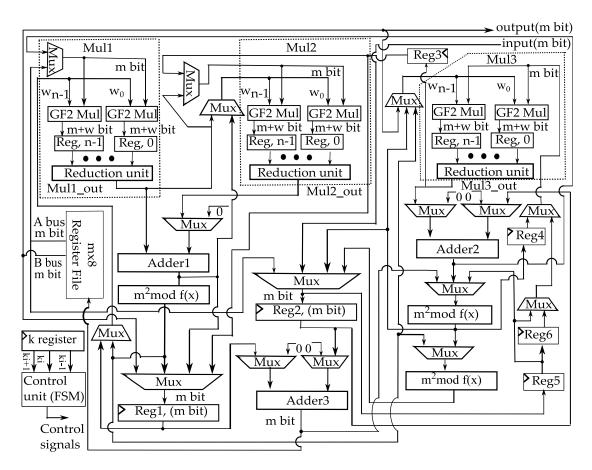

| Figure 5.7 Proposed low latency ECC architecture                                                   | 5-23    |

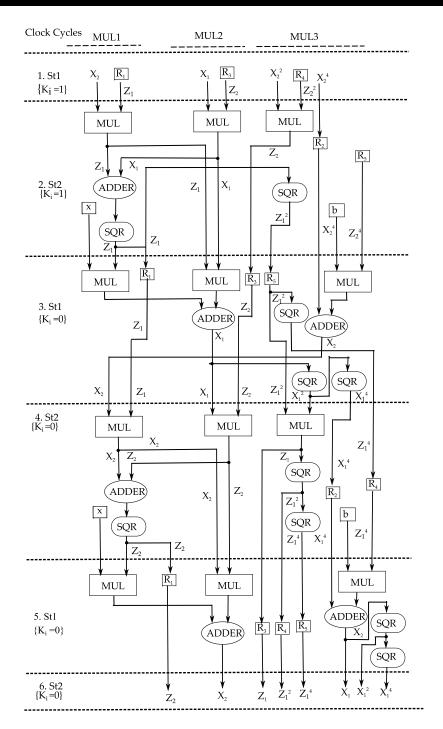

| Figure 5.8 Data flow of LLECC for $k_{i+1}=1$ , $k_i=1$ and $k_{i-1}=1$                            | 5-25    |

| Figure 5.9 Data flow diagram of <i>LLECC</i> for $k_{i+1}=1$ , $k_i=0$ and $k_{i-1}=0$             | 5-26    |

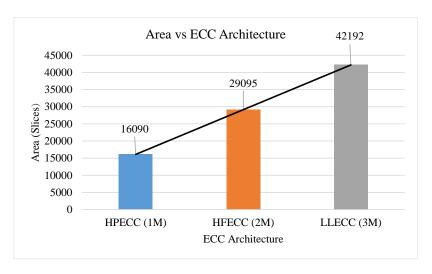

| Figure 5.10 Area vs ECC architecture over $GF(2^{163})$                                            | 5-32    |

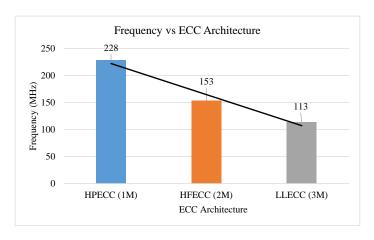

| Figure 5.11 Frequency vs ECC architecture over $GF(2^{163})$                                       | 5-32    |

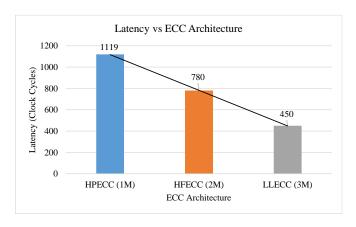

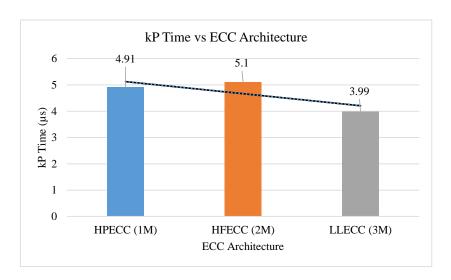

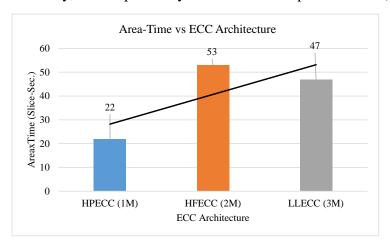

| Figure 5.12 Latency vs ECC architecture over $GF(2^{163})$                                         |         |

| Figure 5.13 $kP$ time vs ECC architecture over $GF(2^{163})$                                       |         |

| Figure 5.14 Area-time vs ECC architecture over $GF(2^{163})$                                       | 5-34    |

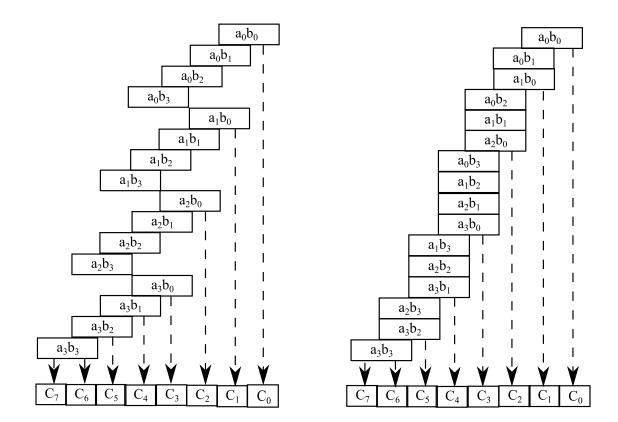

| Figure 6.1 Row-wise and Column-wise multiprecision multiplication                                  | 6-7     |

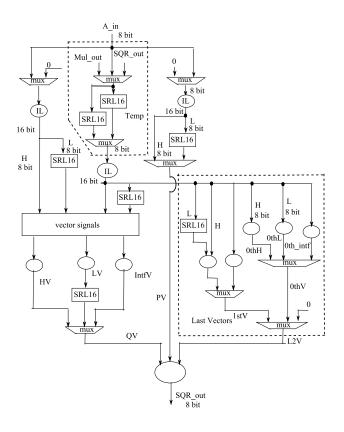

| Figure 6.2 Proposed Comba multiprecision multiplier over $GF(2^m)$                 | 6-16        |

|------------------------------------------------------------------------------------|-------------|

| Figure 6.3 Proposed two-and-two GF2MUL based Comba multiprecision multiplies       | over        |

| $GF(2^m)$                                                                          | 6-19        |

| Figure 6.4 Proposed four-and-four GF2MUL based Comba multiprecision multiplie      | er over     |

| $GF(2^m)$                                                                          | 6-20        |

| Figure 6.5 Reduction unit of multiprecision multiplication                         | 6-22        |

| Figure 6.6 Scalable multiprecision multiplier reduction over $GF(2^{233})$         | 6-25        |

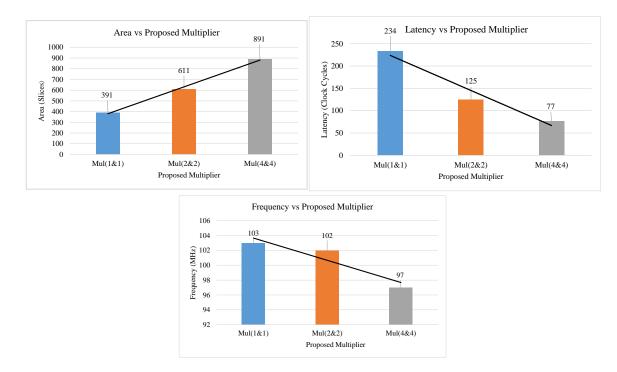

| Figure 6.7 Area, latency, max. frequency vs proposed multiplier over $GF(2^{163})$ | 6-28        |

| Figure 6.8 Multiprecision square circuit over $GF(2^{163})$                        | 6-32        |

| Figure 6.9 Multiprecision square circuit over $GF(2^{233})$                        | 6-34        |

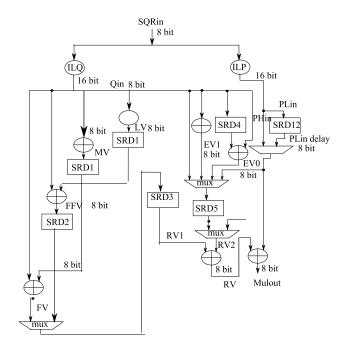

| Figure 6.10 Proposed scalable ECC architecture                                     | 6-38        |

| Figure 6.11 Data flow graph of the proposed combined Montgomery point multipli-    | cation 6-41 |

| Figure 6.12 SRL16 based 8xm memory unit                                            | 6-46        |

#### **List of Tables**

| Table 2.1 Equivalent key size of AES, ECC and RSA/DH and a comparison of computation                |

|-----------------------------------------------------------------------------------------------------|

| cost [96]                                                                                           |

| Table 2.2 Number of field operations for a point addition and a point doubling 2-22                 |

| Table 2.3 Total field operations for the point multiplication algorithm                             |

| Table 3.1 Latency of MSB multiplier based ECC for Montgomery point multiplication 3-17              |

| Table 3.2 Implementation results of this proposed low area ECC for point multiplication over        |

| $GF(2^{163})$ after place and route                                                                 |

| Table 3.3 Performance of the proposed ECC for different digit-size multipliers over $GF(2^{163})$   |

|                                                                                                     |

| Table 3.4 Implementation results of the proposed bit-serial multiplier based ECC over all           |

| NIST curves after place and route                                                                   |

| Table 3.5 Comparison of the propsed ECC with the state of the art over $GF(2^{163})$ after place    |

| and route                                                                                           |

| Table 4.1 Latency, critical path delay and resources of digit serial multipliers over $GF(2^m)$ 4-7 |

| Table 4.2 Latency of ECC for $\lceil m/w \rceil = 4$ , mul= $M_4/M_7$ . add=1. sqr=2                |

| Table 4.3 Results of our ECC over $GF(2^{163})$ after place and route                               |

| Table 4.4 FPGA implementation results after place and route in Virtex7 4-12                         |

| Table 4.5 Comparison of state of the art after place and route on FPGA 4-14                         |

| Table 5.1 Latency, critical path delay ( $T_{mul}$ ) and resources of the proposed full-precision   |

| multiplier and a comparison with the relevant multiplier over $GF(2^m)$                             |

| Table 5.2 Critical path delay ( $T_{ECC}$ ) of the proposed ECC                                     |

| Table 5.3 Latency of the proposed ECC ( $MUL=M_1=1$ , or $M_2=2$ , or $M_3=3$ , $ADD=1$ , $SQR=1$ , |

| and 4SQR =1) 5-29                                                                                   |

| Table 5.4 Comparison of the results of proposed ECC with the state of the art over $GF(2^m)$ on     |

| FPGA after place and route                                                                          |

| Table 6.1 Lv, Mv, Fv vectors generation over $GF(2^{163})$                                          |

| Table 6.2 Latency of the proposed multiprecision multiplier                                         |

| Table 6.3 Area and maximum frequency of the proposed multiprecision multiplier over                 |

| <i>GF</i> (2 <sup>163</sup> ) on FPGA 6-26                                                          |

| Table 6.4 Comparison of the proposed multiplier with the relevant multipliars 6-28                  |

| Table 6.5 Multiprecision reduction operation over $GF(2^{233})$ on the 465 bits of square output    |

| (w = 8 bit) 6-34                                                                                    |

| Table 6.6 Comparison of the proposed square circuit with the relevant square circuit 6-35           |

| Table 6.7 Comparison of the proposed scalable ECC with the state of the art on FPGA after           |

| place and route                                                                                     |

#### **List of Algorithms**

| Algorithm 2.1 Addition or subtraction over $GF(2^m)$                                                                                                                           | 2-14     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Algorithm 2.2 MSB field multiplication over $GF(2^m)$                                                                                                                          | 2-15     |

| Algorithm 2.3 LSB field multiplication over $GF(2^m)$                                                                                                                          | 2-16     |

| Algorithm 2.4 Digit serial multiplier over $GF(2^m)$                                                                                                                           | 2-17     |

| Algorithm 2.5 Fermat's little theorem based inversion over $GF(2^m)$ ( $m$ odd)                                                                                                | 2-18     |

| Algorithm 2.6 Left to right binary point multiplication algorithm                                                                                                              | 2-24     |

| Algorithm 2.7 Binary non-adjacent form method for point multiplication                                                                                                         | 2-25     |

| Algorithm 2.8 Montgomery point multiplication                                                                                                                                  | 2-26     |

| Algorithm 2.9 Projective coordinates to affine coordinates conversion                                                                                                          | 2-27     |

| Algorithm 2.10 Elliptic curve key generation                                                                                                                                   | 2-29     |

| Algorithm 2.11 Elliptic curve Diffie-Hellman key exchange (ECDH)                                                                                                               | 2-30     |

| Algorithm 2.12 ElGamal elliptic curve key exchange                                                                                                                             | 2-30     |

| Algorithm 2.13 ElGamal elliptic curve decryption                                                                                                                               | 2-31     |

| Algorithm 2.14 ECDSA signature generation                                                                                                                                      | 2-31     |

| Algorithm 2.15 ECDSA signature verification                                                                                                                                    | 2-32     |

| Algorithm 3.1 Montgomery point multiplication (loop operation)                                                                                                                 | 3-7      |

| Algorithm 3.2 Combined doubling and adding operations of Montgomery algorithm                                                                                                  | 3-8      |

| Algorithm 3.3 Modified LD mix-coordinates algorithm                                                                                                                            | 3-9      |

| Algorithm 3.4 Binary NAF based Frobenius map in the projective coordinates                                                                                                     | 3-10     |

| Algorithm 3.5 Itoh and Tsujii multiplicative inversion algorithm                                                                                                               | 3-16     |

| Algorithm 4.1 LD Montgomery point multiplication over $GF(2^m)$                                                                                                                | 4-3      |

| Algorithm 4.2 Proposed combined loop operation of the LD Montgomery point                                                                                                      |          |

| multiplication with careful scheduling                                                                                                                                         | 4-8      |

| Algorithm 5.1 LD Montgomery point multiplication over $GF(2^m)$ [35]                                                                                                           | 5-5      |

| Algorithm 5.2 Proposed combined LD Montgomery point multiplication (with each lo                                                                                               | op for   |

| six clock cycles)                                                                                                                                                              | 5-12     |

| Algorithm 5.3 Proposed combined LD Montgomery point multiplication (main loop)                                                                                                 | 5-19     |

| Algorithm 5.4 Proposed low latency Montgomery point multiplication (with each loop                                                                                             | for      |

| two clock cycles)                                                                                                                                                              | 5-24     |

| Algorithm 6.1 Comba multiprecision multiplication of binary polynomials                                                                                                        | 6-8      |

| Algorithm 6.2 Multiprecision squaring over $GF(2^m)$                                                                                                                           | 6-10     |

| Algorithm 6.3 Proposed parallel Comba multiprecision multiplication of binary polynomials and second control of the comba multiprecision multiplication of binary polynomials. | omials   |

|                                                                                                                                                                                | 6-13     |

| Algorithm 6.4 Fast reduction modulo $(x) = x163 + x7 + x6 + x3 + 1$ (with $W = 8$ )                                                                                            | )). 6-21 |

| Algorithm 6.5 Proposed fast reduction modulo $(x) = x233 + x74 + 1$ (with $W = 8$ )                                                                                            | 6-24     |

| Algorithm 6.6 Proposed multiprecision squaring over $GF(2^{163})$                                                                                                              | 6-30     |

**Glossary**

AES Advance Encryption Standard

ASIC Application Specific Integrated Circuit

BRAM Block RAM

DLP Discrete Logarithmic Problem

ECC Elliptic Curve Cryptography

ECDH Elliptic Curve Diffie-Hellman

ECDSA Elliptic Curve Digital Signature Algorithm

FFs Flip-Flops

FF Finite Field

FPGA Field Programmable Gate Arrays

FLT Fermat's Little Theorem

GF Galois Field

GF2 Galois Field in the field characteristic two

GF2MUL Multiplication in the field characteristic two

HPECC High Performance Elliptic Curve Cryptography

IEEE Institute of Electrical and Electronics Engineers

ISE Integrated Synthesis Environment

LLECC Low Latency Elliptic Curve Cryptography

LSB List Significant Bit

LUT Look Up Table

MD Message Digest

MSB Most Significant Bit

NAF Non-Adjacent Form

NIST National Institute of Standards and Technology

PDA Personal Digital Assistants

PKC Public Key Cryptography

RAM Random Access Memory

RFID Radio Frequency Identification

RSA Rivest-Shamir-Adleman

SHA-1 Secure Hash Algorithm-1

SSL Secure Socket Layer

WSNs Wireless Sensor Nodes

VHDL VHSIC (Very High Speed Integrated Circuit) Hardware Description Language.

VLSI Very Large Scale Integration

XOR Exclusive OR (logical Operation)

τNAF τ-adic Non-Adjacent Forms

WDDL Wave Dynamic Differential Logic

## **Chapter 1 Introduction of Thesis**

This chapter portrays the broad outlines of the thesis that are the general idea on the research topic, objectives of the thesis, the main contributions in the thesis, thesis structure, and a list of published and presentable works. In this chapter, the goal of the thesis is an efficient hardware design and implementation of elliptic curve cryptography is discussed. Moreover, Advantages of the hardware platform particularly FPGA platform is focused. Finally, research outlines and list of presentation of research outputs are included in this chapter.

#### 1.1 Overview

Our daily life is now increasingly involved with the communications over wired and wireless networks. In every instant, a big data of many transactions go on in these communications. The wider applications of the communications mostly deal with sensitive data that are protected by adopting several functionalities, including confidentiality, identification and data authentications [1] [2]. These functionalities have been developed based on a scientific process named cryptography. The cryptography process provides secure communications by hiding the original message.

Cryptography can be categorised as symmetric key cryptography (also called private key cryptography) and asymmetric key cryptography (also called public key cryptography). The symmetric key is a classical method of cryptography based on private key, whereas asymmetric key cryptography is based on public key (publicly published key) and private key to secure communications. The symmetric key cryptography requires key management to distribute the private key before establishing a communication. The key management is a problem in the communication system that is solved by public key cryptography [3]. The sender in the asymmetric cryptography knows the public key of the receiver. The sender uses the public key to encrypt a message at the sender end to send. The receiver uses his private key to decrypts at the receiver-end to get original message of sender. Thus, untrusted environment can be utilised to transfer information (i.e. key exchange). The public key cryptography is, thus, widely adopted in the communications protocol such as the Secure Socket Layer (SSL), signed and encrypted mail, and single sign-on.

The underlying security of the public key cryptography depends on a mathematical hard problem [1]. The hard problem is so difficult to solve by current computing systems in a reasonable given time scale. The hard problem of Elliptic Curve Cryptography (ECC) is discrete logarithmic problem. The high security level of problem-based cryptography is attractive and hence, the ECC is increasing popular in many communication systems due to some advantages over the existing public key cryptography (for example, Rivest, Shamir and Adleman (RSA), and Diffie-Hellmann (DH)) (page 2-6). The ECC has high security per bit when ECC is compared with RSA. The ECC based cryptography needs shorter operand than that of RSA [5]. The computational advantages of the ECC make it suitable for both constrained (low area) environment and high resources (high-speed) environments.

Low resource environments such as RFID tags, personal digital assistants (PDA), sensor networks and smart phones are involved with wireless networks. The problem of the wireless network is that it is vulnerable to eavesdropping. The resource constrained wireless system has low resources such as processing capacity, power consumption, and data rate and memory space. Thus, it is a problem to adopt security in low resources wireless communications [5] [6] For the security in the low resource applications, on one hand, symmetric key cryptography is suitable as it requires low computations. But, the problem of key management in symmetric key cryptography makes it complicated for widespread applications, in particular, in where highly reliable communication is required. On the other hand, public key cryptography in the low resources applications has no special requirement of key management as the key is publicly published. Moreover, public key cryptography is now suitable for encryption and authentication in low resource wireless communications, however it requires more resources as its field size is large. Thus, the low end application requires an effective low cost solution for security. The ECC based cryptography is now feasible to enable high security in the pervasive devices [5] [6].

High-speed communications systems such as web server in the internet require high security along with faster computation flexibility. ECC provides very high security as compared to RSA for server end applications for a given key size. Moreover, the faster calculation and lower bandwidth of ECC makes it superior over RSA for internet based network security [7].

#### 1.2 Motivation

Elliptic Curve Cryptography is going to play an important role in the public key cryptography based secure communications system. The standard body, such as the US National Institute of Standard and Technology (NIST) recommends elliptic curves due to shorter parameter than classical cryptography such as RSA. The shorter key, compact bandwidth and high security per bit to enable it to apply in low area and high speed, commercial and governmental applications, wired and wireless communications. The elliptic curve cryptography utilise complex mathematical calculation to enable protected communications.

The main computation of ECC is scalar point multiplication on the elliptic curve. The point multiplication shares the most time of ECC based cryptography protocol processing. The

point multiplication is the generation of public key Q by multiplying a base point P by a key (integer) k, hence Q = kP. The point multiplication of ECC is now a highly interested topic in the academia and industry to make it fit in the performance to apply at the application level. Based on the applications, the design and implementations of point multiplication can be categorised such as software, software/hardware and hardware implementations. The software implementation of the point multiplications consumes high latency due to high frequency memory operations involved. The software/hardware implementation is an improvement on software implementations, but still the implementation consumes high latency, as the software and software-hardware implementation are associated with word level computations. Nevertheless, the software and software-hardware design consumes very low power, the high latency thwarts to apply in with both low resources and high performance applications. Thus, hardware design and implementation of point multiplications consumes much fewer clock cycles and shows high speed depend on the optimisation techniques. Moreover, the standalone hardware platform is now an interested topic for both academia and industry as the advancement of hardware cells technology (i.e. low power and high speed VLSI integration) offers high security and optimum performance. Thus, hardware implementations will be ultimate efficient solution of ECC is targeted in the throughout of the thesis.

The hardware platforms such as ASIC and FPGA are considered for the ECC implementation. The FPGA based hardware implementation is a bridge between software and ASIC implementations. The advancement of FPGA technology allows FPGA applications from prototyping to medium scale industrial applications. Moreover, FPGA based hardware solution is a popular hardware platform in academia and industrial application due to some advantages over ASIC hardware solutions. The main advantages of the FPGA are, for example, such as reconfigurability, minor time scale of development, and advances in the cell integrations and low power technology. Particularly, standalone ECC hardware on the FPGA are increasing popular in the both academia and industry as the hardware design can show high performance when high security is a prime concern. In this thesis, the hardware implementation of the ECC processors in the FPGA is utilised to evaluate thesis contributions.

Many hardware implementations are presented in the literature [9] [10] [37] [45] [48-51] [53-64] [66] [71-73] [79-82] [90] [91] [93]. The ECC implementations can be two main spaces of design such as low area ECC and high speed ECC. Each design scheme has its own

design approach. For example, a low area implementation utilises low resources but high latency to fit in the target applications. In the case of high-speed design, the speed of the processing is important. The latency of point multiplication must be reduced to speed up the ECC by exploiting large resources.

Highly efficient ECC shows high efficiency in the product of area and time for ECC. There is a lack of high-efficient ECC design in the literature. Most of the hardware implementations in the ligature are straightforward implementation of an algorithm designed for software implementation. The design utilises very large area without gaining significant speed or they consume very low area with very high latency. Thus, there is a requirement of an optimised design from a hardware perspective. The poor efficiency of ECC prevents to fit in the target application for a required security. Thus, a high-efficient ECC is the vital issue for a cryptography system designer.

The main computation of the elliptic curve cryptography is the scalar point multiplication, Q=kP, where k is an integer (a private key) and P is a base point on the elliptic curve and the result of point multiplication is Q, the public key. The efficient point multiplication (kP) design is an important issue in the ECC cryptography. The thesis only focuses on achieving high efficiency point multiplications. The performance of the point multiplications depends on the choice of algorithm, algorithmic modifications on top level and in the low level, arithmetic units. Thus, modifications of algorithm and novel circuit design can yield a highly efficient ECC.

#### 1.3 Thesis Main Contributions

High efficiency ECC offers several advantages to deploy ECC in the different end of applications such as low-end applications (i.e. low area or low-power applications) and highend applications (i.e. high speed applications). Mainly, the efficient ECC consumes a lower area to compute faster point multiplication [8] [9]. An efficient ECC architecture can provide high security and high speed for the given resource. Thus, a high-efficient design can provide better area-time metric, a standard metric (efficiency) to evaluate the engineering merit of a system architecture design and implementation.

Binary curves based ECC are increasingly more popular for hardware implementation than prime field based ECC. The binary field computation has a simple addition operation due to free from carry propagation delay. The circuit based on binary field is thus suitable to design highly efficient ECC. In this thesis, we consider binary curves that are enlisted by the (NIST) [4].

Hardware implementation for low resource application requires a small area to fit in battery run low resources applications. The most of the implementation presented in the literature used either high area along with poor latency or very low area ECC with very high latency. The high latency may incur a problem for power management. Particularly, the applications of high security requirement utilises large key size of ECC. The key size increases latency geometrically that may thwart to apply in low resources applications. We have developed a low resource friendly ECC that capable of providing high security while utilising low area. The proposed low area design involves several contributions:

#### To yield low area ECC:

- We consider very low resources field arithmetic circuits such bit serial multiplier. The bit serial multiplier takes *m* clock cycles for a multiplication; the latency is very much lower than word level computation of the multiplication.

- Projective coordinates is a better choice than affine coordinates due to costly inversion

operation in each iteration of point multiplication. The projective coordinates based point

multiplication need one inversion operation while it is performing projective to affine

coordinates conversion.

- We utilise several point multiplication algorithms (binary, Montgomery, Frobenius Map based NAF) to show their individual merits. In particular, the Montgomery ladder point multiplication is an efficient point multiplication algorithm even for low area.

- Field square circuit can be achieved using a multiplier to save area with an overhead of latency. For a high efficiency ECC, a single clocked based square is considered to reduce latency by utilising a small extra area. This square circuit accelerates final inversion operation when a multiplicative inversion is implemented.

- Memory unit is the largest part of a low area ECC. A high performance memory unit can help to get efficient ECC. The Memory unit can be implemented by using either block

- RAM or distributed RAM. However, block RAM is a popular option, our distributed RAM based memory unit uses very low area to show very high speed.

- Finite state machine based control unit is considered and allows us to modify point

multiplication algorithm to achieve concurrent field operations. Moreover, the dedicated

finite state machine (FSM) can increase speed by reducing instruction delay during field

operations.

- Our Frobenius map based ECC shows very low latency while utilising a very small area for conversion and can be fitted for a low resource application in which latency is a primary concern.

- Binary implementation always takes lower area, but the latency is not fixed. The latency is changed according to the change of the hamming weight of key.

#### *To yield high throughput ECC:*

• High performance (high throughput) ECC for high-speed application, for example, web server needs high performance multiplier. For high-speed applications, there are many works presenting large digit serial multiplier. Most of the work contributes in the high performance ECC by introducing low complexity digit serial multiplier to reduce the latency of point multiplication. Their digit serial multiplier shows poor clock frequency. We implement a novel digit serial multiplier to accelerate ECC operation while the ECC is keeping such area to get the best area time metric. Our novel digit serial multiplier architecture is suitable for the large digit serial multipliers applications where traditional multiplier is still beyond to meet the requirement of area and speed.

#### To yield high speed ECC:

• High-speed ECC implementation where speed is the only main issue needs very large size multiplier. Moreover, parallel operation of the multiplier reduces latency of the point multiplication further to speed up. In the literature, there are many high-speed works presented, targeted to achieve the highest speed by exploiting bit parallel multipliers or parallel multipliers. Most of the work failed to reach target levels of speed due to poor performance of the multipliers and data dependency in the point multiplication. There is also a gap to reach the theoretical limit of the latency due to poor performance of multiplier and overall ECC architecture. We developed a new full precision multiplier architecture

along with smart ECC architecture to reach the theoretical latency limit. Thus, our ECC can manage a new fastest figure of speed to date.

#### To yield low latency scalable ECC:

- Scalability of security options is a popular property of a crypto processor to change security while it is required in the future. Moreover, smart devices (smart phone, PDA, RFID tags and wireless sensor nodes (WSNs)) need low resources scalable processor to meet future security requirement without replacing the crypto processor. To develop low resource scalable ECC, there is a requirement of multiprecision multiplication, for example Comba multiprecision multiplier and multiprecision square operation to include all NIST curves in a single processor. There are several scalable ECC implementations showing very poor performance due to high latency in the arithmetic operations with word level operation. We consider Comba multiprecision multiplier is suitable for highly efficient ECC due to its inherent parallelism to improve latency.

- We develop modified Comba multiprecision multiplier to reduce latency abruptly with small overhead of the area. We evaluate the parallelism of Comba by utilising different sets of parallel multipliers.

- A novel scalable reduction circuit is developed, which can perform reduction operations on all NIST curves on the fly during multiplication. Thus, the latency of multiplication is required to accomplish a field multiplication with reduction.

- We also develop very low latency novel multiprecision square circuit. There is no latency for the reduction operations as like as our proposed multiplication. The square circuit requires only the latency that is required to access data from memory. The proposed square circuit takes only three clock cycles delays to get the first word of the square results.

- We propose a repeated squaring circuit that can start new square operation immediately after a squaring operation is finished. The repeated square operation is flexible for all NIST curves without incurring extra clock cycles for reduction and load-unload operation of data from memory. The repeated operation accelerates point multiplication and multiplicative inversion operation due to low latency and repeated square operation without delay

- The novel multiprecision circuits enable inclusion of all NIST curves in the single ECC

processor. Moreover, a new low cost memory unit and careful scheduling in the point

multiplication is utilised for saving latency to improve the efficiency of the scalable ECC.

The high efficiency of the scalable processor can enable the provision of high security without changing the crypto processor in low-end applications.

#### 1.4 Thesis Outlines

The thesis is organised as follows

Chapter 2 presents necessary preliminaries of the remaining chapters to understand the novel contribution of those chapters. The Galois field arithmetic, elliptic curve arithmetic and application, and hardware platform of ECC such as FPGAs are covered in this background chapter.

In chapter 3, low area elliptic curve cryptography on FPGA is presented. The chapter includes low resources implementation of popular ECC point multiplication algorithms to achieve the best area-time metrics targeted in the low end applications.

A novel digit serial multipliers over  $GF(2^m)$  for curve based cryptography application is introduced in chapter 4. The chapter describes the best high throughput per area architecture of ECC based on the digit serial multiplier.

Chapter 5 reports the fastest figure of ECC point multiplications on FPGA over  $GF(2^m)$ . The pipelining based full-precision multipliers and its parallel operations, and smart pipelined based ECC architecture are presented. The ECC architecture can manage to reach the theoretical limit of latency for the point multiplication utilising careful scheduling in the point operations.

Chapter 6 discusses new modified Comba multiprecision multiplier and new multiprecision square circuit. A novel multiprecision arithmetic based on the two novel circuits drastically reduced latency to achieve the best area-time scalable ECC for the low-end applications.

Finally, the thesis is summarised the main contributions in the conclusions, which is chapter 7 and a discussion of potential future works are included in there as well.

#### 1.5 Published Papers

The contribution of the research work presented in this thesis, the following peer-reviewed academic papers were published/accepted to publish:

- 1. Z. Khan and M. Benaissa, "Low area ECC implementation on FPGA," in Proc. IEEE 20th Int. Conf. Electronics, Circuits, and Systems, Dec. 8-11, 2013, pp. 581-584.

- Zia-Uddin-Ahamed Khan and M. Benaissa, "Throughput/Area Efficient ECC Processor using Montgomery Point Multiplication on FPGA," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 62, no. 11, pp. 1078-1082, Nov. 2015.

- 3. Zia Khan, M. Benaissa, "High Speed ECC Implementation of FPGA over GF(2<sup>m</sup>)," in IEEE 25th International Conference on Field-programmable Logic and Applications (FPL), 2-4 Sept. 2015 pp. 1-6.

- 4. High speed and Low latency ECC implementation on FPGA over GF(2<sup>m</sup>): (Accepted to publish in the IEEE Transactions on Very Large Scale Integration Systems)

### **Chapter 2 Background**

This Chapter discusses elliptic curve cryptography application as a public key cryptography. Again, the chapter explains important terminologies of the Elliptic Curve Cryptography principle along with the underlying finite field theory of the elliptic curve cryptography. Finally, the issues involved in the implementation of Elliptic Curve Cryptography for Point multiplication are demonstrated in the chapter.

#### 2.1 Introduction

Cryptography is a technique to change the original message so that the actual meaning of the message is difficult to retrieve. The technique of cryptography is underlying hardness of complex mathematical problem. No one can solve this problem except the target person to get the actual meaning of the sending message using available computing system in the required time scale. Modern cryptography involves with complex mathematical algorithm under the cryptographic protocol to provide authentic communication systems.

In the modern era of cryptography key exchange method, a cryptography algorithm to solve the problem of private key-based, a new milestone of cryptography became known when Whitefield Diffie and Martin Helman [3] proposed key management problem. The new proposed method and its application are termed as public key cryptography (PKC). PKC has two keys such as public key that is known by all users and private key that is saved in secret by a respective user. The sensitive data transmission among all users is performed by using public key. As the transmission is accomplished by using one way function, only the target person is able to get the transmitted data. Thus, public key becomes the main mechanism to secure data transmission in the cryptography based secure communications.

#### 2.2 Cryptography Basics

In a communications system, the sensitive information that is transmitted between sender and receiver is open to access by all. Eavesdroppers can easily get the transmitted information if there is no protection of information. Thus, there is a requirement of security so that third parties are not able to retrieve actual information. Cryptography algorithms is associated with complex algorithms that provide security in the communication system. It is impossible for a third party to retrieve the original data as there is an exponential time requirement to get the original information. Modern PKC provides secure communication by ensuring the following issues [1], [2], [11]:

Data confidentiality: Confidentiality is a property to secure data so that unauthorised persons cannot receive the transmitted data. Thus, third person cannot eavesdrop the data.

- Data Integrity: the receiver checks the data, whether the data is modified by the eavesdropper (i.e. attacker). In this case, the receiver uses the message to verify the content of the transmitted data has not been altered.

- Data Origin Authentication: The vital secrecy of the transmitted data is authentication. Receiver confirms the original sender identity before data transmission is established.

- Entity Authentication: other users, to authenticate the identity of the user, verify the entity of a user.

- Non-Repudiation: After transmitting data, both sender and receiver cannot reject that they have involved in the communication or denied the content of data in the future.

Fundamentally, cryptography uses keys to encrypt and decrypt information using mathematical techniques so that the above goals are achieved. A typical cryptography based communication system is described below:

Alice (A) wants to send a message (M) is called the plaintext to her friend Bob (B) through a secure communication channel based on cryptography. A third person, Eve (E) is interested to retrieve the message by eavesdropping. Alice wants to ensure security by hiding the plaintext using cryptography tools. The hiding of the plaintext by cryptography tools is performed through a certain algorithm (called cipher) which involves the use of complex mathematical operations. The hiding process of the plaintext is called encryption (Ec). The encrypted plaintext is called chippertext (Ctext). Again, the reverse operation of the encryption is called decryption (Dc). In the decryption process, similar algorithm (decipher) is utilised but operations on the ciphertext to retrieve the plaintext. For encryption and decryption process, the encryption key (Ke) is used for encryption of the plaintext and the decryption key (Kd) is used for decryption of the ciphertext. The mathematical model of the cryptography is shown below:

$$Ctext = Ec(M)$$

where the key is  $Ke$  (2.1)

$$M = Dc(Ctext)$$

where the key is  $Kd$  (2.2)

To achieve the goal of security, a distributed sequence of steps called cryptographic protocol is defined precisely in the interactions between two or multiple parties [2].

#### 2.3 Cryptography Schemes

There are mainly three cryptography schemes such as symmetric key cryptography or private key cryptography, asymmetric key cryptography or public key cryptography and hash functions or no key algorithms. Eq. (2.1) and Eq. (2.2) can be established using the cryptographic schemes.

#### 2.3.1 Symmetric Key Cryptography

The symmetric key cryptography algorithm uses the same key for encryption and decryption process. The symmetric key cryptography is illustrated in Figure 2.1 where Alice want to send a message (plaintext) to Bob over symmetric key cryptography based secure communication channel. If Alice uses a key to encrypt the plaintext, then the key must be sent through a secure channel to Bob. Otherwise, a key exchange is used before encryption and decryption is processed. There are several popular symmetric curve cryptography available such as Advance Encryption Standard (AES), A5, and RC5.

Figure 2.1 Symmetric key cryptography based communication system

Symmetric key cryptography is compact and provides higher security than asymmetric key per bit. Thus, symmetric key cryptography can be used in low end to high speed applications. The advantages of symmetric key cryptography cannot be utilised due some shortcomings [12]. One of the disadvantages of the symmetric key cryptography is the key distribution problem due to both sender and receiver must have same key. If there are few users, then the number key for every two users is less and easy to distribute the keys. But, for a large number of users, the key distribution is not practically suitable. Moreover, the keys are required to be changed frequently which is another problem for key management. Finally, in some cases, authentication and non-repudiation goals are not established by using symmetric key cryptography. The asymmetric key cryptography can overcome the symmetric key cryptography problems is discussed in the next sub-section.

Figure 2.2 Public key cryptography based communication

#### 2.3.2 Public Key Cryptography

Diffie and Hellman proposed public key cryptography. They solved the problem of symmetric key cryptography, including key distribution problem and key management problem [3]. In Figure 2.2, Public key cryptography is explained by using a basic protocol where separate keys are used for encryption (public key,  $K_e$ ) and decryption (private key,  $K_d$ ). The public key of a user is available to every user; hence, it is named public. The private key is kept in secret so that only the user knows the key. In the Figure 2.2, Alice wants to send a message (*Plaintext*) to Bob and Flora. To encrypt the messages, Alice uses the public key of Bob to send message to Bob and also uses public key of Flora to send a message to Flora. Bob and Flora can only decrypt their respective message using their own private key; however, both messages are publicly available. The public key cryptography works in one direction, this action is called "one way function" due to that the computation in the reverse direction is not practical. Thus, it is impossible to know (in the target time scale) the private key of a user (i.e. Bob) by another person (i.e. Flora) from the public key of the user (Bob) except the respective user (Bob).

The advantages of public key cryptography over symmetric key cryptography such as key exchange, key management along with confidentiality. The modern public key cryptography also provides authentication by exploiting digital signature. Thus, public key cryptography can prove one of the user would be involved to generate a message called non-repudiation. A notable feature of public key cryptography is to provide sender non-repudiation that is absent in the symmetric key cryptography scheme. There are several mechanisms involved in the public key crypto system such as key exchange protocol, digital signature algorithm and encryption.

Modern public key cryptography provides all desired goals for a given security protocol of the communications system (i.e, IP encryption (IKE/IPSEC), web traffic SLL/TLS and secure electronic mail). For a given security, public key cryptography takes long computation delay. The large size data are involved in the computation make it lower efficiency than private key cryptography. Thus, standalone public key cryptography is infeasible for some computation sensitive applications (low-end applications). In this case, a hybrid cryptosystem where public key cryptography (for key exchange) and private key cryptography (encryptions) can be used together to improve performance.

Table 2.1 Equivalent key size of AES, ECC and RSA/DH and a comparison of computation cost [96].

| Symmetric key, | ECC key $(GF2^m) / GF(p)$ | RSA/DH key | Ratio of          |

|----------------|---------------------------|------------|-------------------|

| (AES)          |                           |            | DH Cost: ECC Cost |

| 80 bit         | 163 bit / 160 bit         | 1024 bit   | 3:1               |

| 112 bit        | 233 bit / 224 bit         | 2048 bit   | 6:1               |

| 128 bit        | 283 bit / 256 bit         | 3072 bit   | 10:1              |

| 192 bit        | 409 bit / 384 bit         | 7680 bit   | 32:1              |

| 256 bit        | 571 bit / 521 bit         | 15360 bit  | 64:1              |

Now, There are several popular public key cryptography that are considered for high-security communications included: 1. Integer Factorisation Problem (IFL) based RSA (named from the name of inventors – Rivest, Shamir and Adelman) [13], 2. Discrete Logarithm Problem (DLP) based Diffie-Helman (DH) key exchange protocol and DH Digital Signature Algorithm (DSA), and 3. Elliptic Curve Discrete Logarithm Problem (ECDLP) based Elliptic Curve Diffie-Hellman (ECDH) key exchange protocol and Elliptic Curve Digital Signature Algorithm (ECDSA) [4]. Comparatively, older public key cryptography such as RSA and Discrete Logarithm (DL) are involved with a computationally high intensive operation such as modular exponentiation. The modular operation is exploited large size operand to provide high security as compared to Elliptic Curve Discrete Logarithm Problem based crypto system.

A comparison of equivalent key sizes AES, RSA and ECC recommended by NIST is presented in Table 2.1 [5]. The key size of AES is compact to provide high security while comparing with public key cryptography i.e. RSA, ECC. Key size of conventional encryption algorithm i.e AES is a measure of security to protect attack. To provide an equivalent security of 80 bit long key of AES, RSA needs 1024 bit key, whereas ECC needs 163 bits key [1]. For

high security, for example, the security equivalent of 256 bit key size of AES, the key size of RSA increases abruptly as compared to ECC. Thus, ECC offers higher security per bit than RSA or Diffie-Hellman public key cryptography. The right hand column of Table 2.1 computations cost of between Diffie-Hellman public key cryptography over Elliptic Curve Cryptography [96]. For a typical protocol such as key exchanges in the DH requires a large number bit to transmit each way of a communication channel as compared to ECC. Thus, there is an overhead in bandwidth due to large key size of DH. In this case, ECC is suitable for a channel-constrained environment than first generation public key crypto systems (RSA and DH). Thus, ECC is suitable for both low-end applications (i.e. sensor networks, RFID tags, smart card) and High-speed applications (i.e. Server side).

#### 2.3.3 Hash Functions

The hash function is a cryptography algorithm apart from private key and public key. The hash function is a one way function also called message digests. The hash function uses a hash value instead of a key. The hash value is a fixed length that is generated from a given plaintext [12]. The content of plain text or length of the plaintext is impossible to retrieve from the hash value. Hash is widely used for message integrity along with other cryptosystems. There are several hash functions used in the communication system such as SHA1 [14], MD4, MD5 [15] and the newer one is SHA3 are recommended by NIST [16].

For example, Alice wants to send a message to Bob. She calculates hash value of the message using a hash function. She then encrypts the hash value using asymmetric cryptography algorithm which is called a form of digital signature. Alice also creates an arbitrary session key for symmetric encryption. The key is used for encryption of the message. The private key is encrypted using public key of Bob using public key cryptography. Now a digital envelope is formed, including the message and encrypted session key. Alice then sends the digital envelope and digital signature to Bob. Bob retrieves the session key using his private key. Finally, the message of Alice is decrypted with the help of symmetric key algorithm using the session key. Alice also decrypted the hash value using the Alice public key to verify integrity. Bob uses the decrypted message to generate a hash value using hash algorithm and compare with the value of decrypted hash value. The hybrid procedure ensures Bob several goals such private message (symmetric encryption), the message is only for Bob (Bob's private

key used to decrypt), the message is not be altered (by matching hash value) and Alice sent the message(Alice public key is used to generate the same hash value).

#### 2.4 Elliptic Curve Cryptography

Elliptic curves have been used as a key tool to solve several problems in mathematics since the middle of the 19<sup>th</sup> century. The properties of elliptic curves used to solve that are factoring integers, proving Fermat's Theorem, primality testing and currently public key cryptosystems. Koblitz [17] and Miller [18] proposed elliptic curve cryptography in 1985 independently. Since then, elliptic curve cryptography was slowly adopted in commercial industry. Now, ECC is taking place of first generation cryptography, RSA as ECC is adopted by standardizing bodies such as ANSI [19], IEEE [20], ISO [16], and NIST [4].

Elliptic curve cryptography is based on the Discrete Logarithm Problem (DLP). Elliptic curve cryptosystems are implemented in finite field for a group structure. There is a set of elements (points) in the group. The special point,  $\phi$  is a point at infinity is the identity of the group. The elliptic curve operation in the group is addition of points. The point addition operation is performed underlying arithmetic operation in the finite field is called field arithmetic operation. The idea behind the elliptic curve cryptography is to add a point P itself for k times where k is an integer (scalar) to achieve new point on the elliptic curve, Q = kP is called scalar point multiplication as presented in (2.3). It is an easy way to obtain Q = kP using point additions operation. The inverse operation to get the k from the given P and Q is a mathematical problem, Elliptic Curve Discrete Logarithm Problem (ECDLP). Unlike other DLP, ECDLP being a harder problem as until now; there is no sub-exponential time algorithm to solve the ECDLP. In Q = kP, k is called discrete logarithm problem of Q to the base point  $P, k = \log_P Q$ . Thus, Elliptic curve crypto systems provide higher security per bit than that of RSA. As a result, the communications channel requires lower bandwidth for ECC, along with the advantage of lower memory requirement than first generation cryptography. For example, for the symmetric curve key of 256 level security, ECC needs a key of 571 bits as compared to RSA with a key of 15360 bits.

$$Q = k.P = P + P + ... + P + P. \tag{2.3}$$

The main underlying operation of the ECC is scalar point multiplication. The point multiplication is consuming most of the computation time during the ECC protocol (encryption and decryption). Thus, the scalar point multiplication is the main building block to implement the elliptic curve cryptography processor. The hierarchy of elliptic curve cryptography

Figure 2.3 ECC hierarchy diagram

operations is shown in Figure 2.3. The point multiplication is achieved using elliptic curve arithmetic operations that are called point addition and point doubling. The underlying of the point operation is finite arithmetic operations that are represented in the bottom layer of the hierarchy diagram.

#### 2.5 Finite Field Theory

The fundamental theory of cryptography engineering is a finite field theory. To explore the ideas and contributions of a cryptography processor, there are requirements of in depth understanding of finite field arithmetic, elliptic curve operations, point multiplications and their implementation issues. Particularly, as the finite field arithmetic circuit design is the crucial part of the ECC processor design, an extensive understanding of finite theory and circuits are the basics for the complete ECC design. Several resources of finite field theory are available in [1],[18], [22],[23] and [24] to read more details.

Modern finite field theory has developed from Galois field theory since the 19<sup>th</sup> century. The French mathematicians *Evariste Galois* developed the elementary theory, hence, named Galois field. The finite field has been widely considered for the last decades when algebraic geometry and algebra are adopted in the coding theory and cryptographic schemes.

Some fundamental definitions of finite field theory are presented below which will be used in finite field arithmetic in this thesis.

**Definition 1** In the finite field theory, a finite field, F or a Galois field, GF is an algebraic structural group of finite numbers. The algebraic operations such as addition, subtraction, multiplication with and division are performed within elements of the finite field while it is maintaining algebraic laws such as associative, commutative, distributive, existence of an additive identity is 0 and a multiplicative identity is 1, additive inverse, and multiplicative inverse for nonzero elements. The group structure of GF also follows the law is called Group, for example, a group M. The group, M is called a commutative group or Abelian group. Modern cryptography systems are based on the Abelian groups [22].

#### **Definition 2** If *F* is a set of an Abelian group [1] [22]:

- With additive identity, 0 is as identity element.

- With Multiplicative identity element 1.

- Distributive law exists: (a + b)c = ac + bc

**Definition 3** If the elements of F is finite, then the field is called finite. The number of elements is called the order of fields, q [1].

**Definition 4** In a finite field, GF(q), the order of GF, the content of q is a prime power is a form of  $q = p^m$  where p is a prime number is called the characteristic of GF and m is an integer number [22].

In cryptography and coding theory, there are three main fields as shown below:

- If m = 1, then the GF(p) is called prime field

- If  $m \ge 2$ , then the GF is called extension field.

- o If p = 2, m > 1, then the  $GF(2^m)$  is called a binary extension field or characteristic 2 field or simply binary field.

- o If p > 2, m > 1, then the  $GF(p^m)$  is called an optimal extension field.

The binary field is a popular option over the prime field for the hardware design. This thesis covers all contributions based on  $GF(2^m)$ . Thus, the rest of the thesis is mainly concerned with the binary field,  $GF(2^m)$ .

#### 2.5.1 Binary extension field $GF(2^m)$

The field arithmetic operations such as multiplication and addition over a binary extension field are carry free operations. The carry free operation is suitable in the hardware platform as compared to software implementation. Moreover, the carry free operation offers shorter critical path delay and lower resources than a carry based field operation in the hardware platform. Thus, the binary field arithmetic circuit can achieve faster speed with exploiting low resource in any hardware platform. Particularly, the addition over characteristic 2 circuit utilises very simple circuit (exclusive or logic, xor) than an integer arithmetic circuit. It can be noted that the general purpose computing system is more suitable integer arithmetic than that of  $GF(2^m)$ . Thus, binary extension field based arithmetic operations are problematic in the system that is designed for integer arithmetic operations.

In the binary extension field,  $GF(2^m)$  has  $2^m-1$  non-zero elements for a m length of binary vectors. The bases of the m length are  $(a_{m-1}, ..., a_1, a_0)$  as a linear space over  $GF(2^m)$ . A subtraction is equivalent to addition over  $GF(2^m)$  is performed bitwise xor operation.

**Definition 5** A polynomial A(x) over a binary extension field is an algebraic structure is of the form  $a_m x^m + \dots + a_1 x + a_0$ . The coefficients of the polynomial,  $a_i$ 's can be integer, real, or complex [25].

**Definition 6** The polynomial algebraic operations over  $GF(2^m)$  maintains finite field; however the algebraic operations are same as normal polynomial algebraic operations [25].

**Definition 7** If two polynomials  $A(x) = \sum_{i=0}^{m} a_i x^i$  and  $B(x) = \sum_{i=0}^{m} b_i x^i$  over a finite field, GF(q) [25], then

- The addition :  $(A(x) + B(x)) = \sum_{i=0}^{m} (a_i + b_i)x^i$

- The multiplications:  $(A(x).B(x)) = \sum_{l=0}^{m+n} c_{l_i} x^i$ ; where  $c_l = \sum_{i+j} (a_i.b_j)$

**Definition 8** A polynomial f(x) over GF(q) is called an irreducible polynomial when  $f(x) \neq 1$  and  $f(x) = A(x) \cdot B(x)$  where A(x) or B(x) must be unit polynomial or constant polynomial [25].

**Definition 9** If an irreducible polynomial is  $f(x) \in GF(q)$  of degree m, then f(x) is used to create an extension field of GF(q). The order of the extension field m is defined in the field by  $GF(q^m)$  [25].

**Definition 10** There are  $q^m$  elements over the extension field  $(q^m)$ . The element can be expressed by a polynomial of degree m-1 over a subfield GF(q).