# Design and Control of On-board Bidirectional Battery Chargers with Islanding Detection for Electric Vehicle Applications

by

# Narabhaya Chaththa Kalhana Colombage

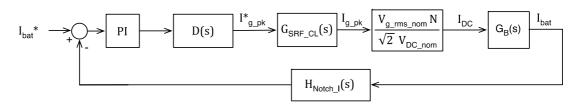

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in Electronic and Electrical Engineering

The University of Sheffield

Faculty of Engineering

Department of Electronic and Electrical Engineering

# **Abstract**

Electric vehicles have gained popularity over the last decade due to concerns regarding climate change as well as depleting fossil fuel reserves. One of the important components of electric vehicles is the battery charging system that has been the focus of recent research interest in terms of vehicle to grid (V2G) power transfer with the aim of providing peak load levelling for the grid as well as a buffer for excess renewable energy. The research addressed in this thesis is focused on single-phase on-board bidirectional chargers for electric vehicle applications where emphasis is given to the design, control and islanding detection aspects.

A comparative study between a low frequency transformer based and high frequency DAB based bidirectional charging system is carried out and the weight, cost and efficiency between the two topologies compared. An optimised LCL filter design method for the two converters is presented which characterises the high frequency current ripple as well as the losses in the damping resistor. Controller design, simulation and experimental validation of the two converters are also presented.

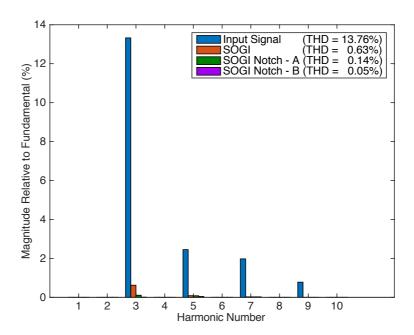

The impact of 3<sup>rd</sup> harmonics on the performance of second order generalised integrator (SOGI) phase locked loops (PLLs) is investigated through an analytical method to predict the resulting output harmonic magnitudes. Two modified SOGI PLLs are presented where the harmonic rejection performance has been improved.

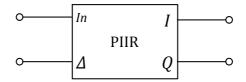

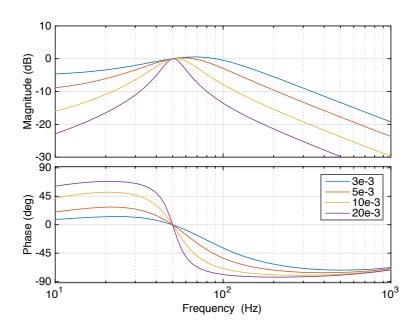

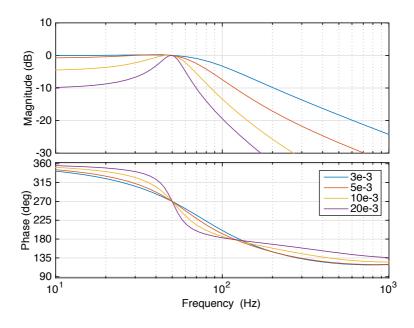

A new PLL structure based on the novel IIR filter proposed by Ed Daw et al. is investigated for application in grid converters. The new PLL is evaluated with hardware-in-the-loop (HIL) simulations for transient and abnormal grid conditions and compared with the SOGI PLL for performance evaluation as well as computational requirements. The new PLL is validated in bidirectional charger hardware.

A new islanding detection algorithm based on the detection of high frequency switching harmonic signature with frequency hopping is presented which has the advantage of multi-inverter compatibility. The difficulty in detection for PWM harmonic based methods when capacitive loads are present is analysed. Furthermore, the algorithm is validated in hardware.

# **Acknowledgements**

First, and foremost, I would like to thank my supervisor Prof. Jiabin Wang for his invaluable guidance, support and kindness throughout my PhD studies. I would also like to thank my other supervisor Prof. Zi-Qiang Zhu for his support and guidance. I'm grateful to Prof. John David for his support during the course of my undergraduate as well as postgraduate studies. I would like to acknowledge The University of Sheffield, the European Commission as well as the Technology Strategy Board for funding this research and I would also like to thank SIEMENS AG and the other project partners for their collaborative support.

My deepest gratitude to Dr. Chris Gould, Dr. Khoa Hoang, Dr. Xibo Yuan, Dr. Tega Edo, Prof. David Stone, Dr. Martin Foster and Dr. Daniel Gladwin for the invaluable help and guidance they provided for this work. My sincere thanks to Mr. Lawrence Obodo, Mr. Richard Garraway, Mr. John Wilkinson and Mr. Andrew Race for their technical support in the lab.

I'm thankful to Chaohui Liu, Bhaskar Sen and my other friends in the EMD group for the technical help as well as the motivation and support they provided. Special thanks go to Vinoth Gurusamy, Hossein Mohanna and Alireza Mehranjani. I'm grateful to all my other friends for their consistent support and encouragement.

Finally, I would like to express my eternal gratitude to my parents and family for their unlimited love, support and encouragement.

# **Table of Contents**

| Abstra  | ct                                                       | III      |

|---------|----------------------------------------------------------|----------|

| Acknov  | vledgements                                              | IV       |

| Table o | f Contents                                               | <b>V</b> |

| Chapte  | r 1 Introduction                                         | 1        |

| 1.1.    | General Introduction                                     | 1        |

| 1.1.    | 1. Electric Vehicles (EVs)                               | 2        |

| 1.1.    | 2. Electric Vehicle Chargers                             | 4        |

| 1.2.    | Motivation                                               | 8        |

| 1.3.    | Main Contributions                                       | 9        |

| 1.4.    | Outline of Thesis                                        | 10       |

| 1.5.    | List of Publications                                     | 12       |

| Chapte  | r 2 On-board Bidirectional Charger Design and Comparison | 13       |

| 2.1.    | Introduction                                             | 13       |

| 2.1.    | 1. Option 1 – Low frequency transformer based charger    | 19       |

| 2.1.    | 2. Option 2 – High frequency transformer based charger   | 21       |

| 2.2.    | Low frequency transformer based bidirectional charger    | 21       |

| 2.2.    | 1. Frontend analysis and design                          | 21       |

| 2.3.    | High frequency transformer based bidirectional charger   | 52       |

| 2.3.    | 1. Frontend analysis and design                          | 52       |

| 2.3.    | 2. Dual active bridge analysis and design                | 64       |

| 2.4.    | Comparison of converter loss                             | 80       |

| 2.5.    | Overall comparison of options                            | 86       |

| 2.6.    | Summary                                                  | 88       |

| Chaptei | r 3 Controller Design, Simulation & Experimental Results        | s of the |

|---------|-----------------------------------------------------------------|----------|

| OBBC S  | ystems                                                          | 89       |

| 3.1.    | Introduction                                                    | 89       |

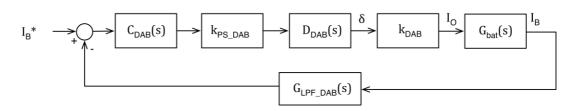

| 3.1.    | 1. Control of Dual Active Bridge Converters                     | 89       |

| 3.1     | 2. Grid converter current control                               | 91       |

| 3.2.    | Controller design for high frequency transformer based charger. | 94       |

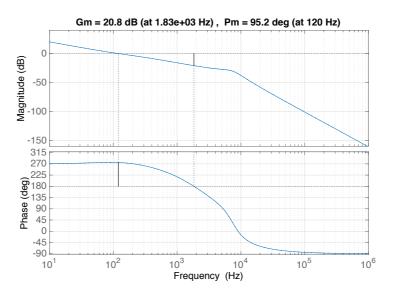

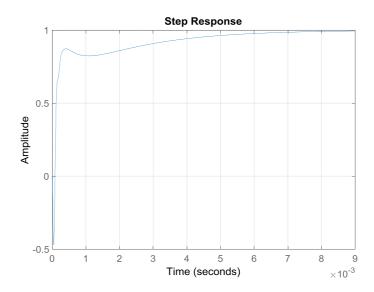

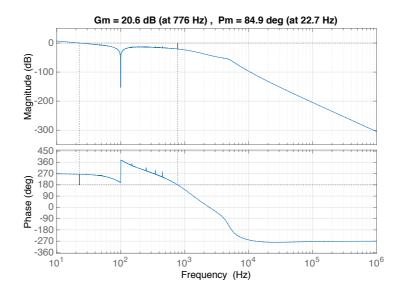

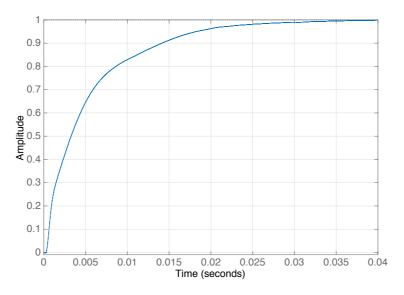

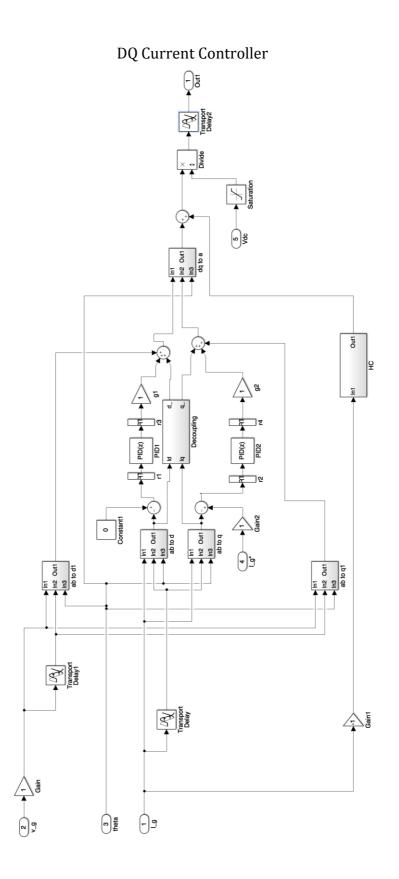

| 3.2.    | 1. DAB current controller design                                | 95       |

| 3.2     | 2. Grid current controller design                               | 99       |

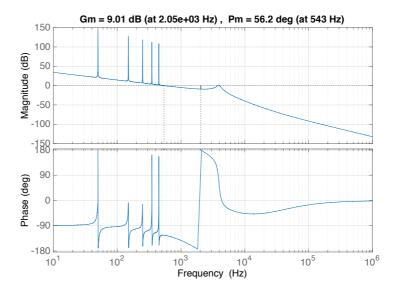

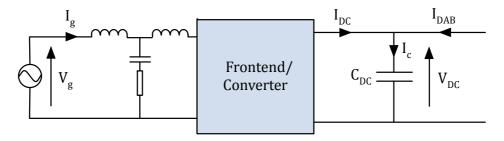

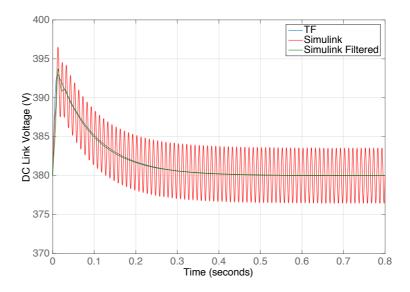

| 3.2     | 3. DC link voltage controller design                            | 105      |

| 3.3.    | Controller design for low frequency transformer based charger   | 109      |

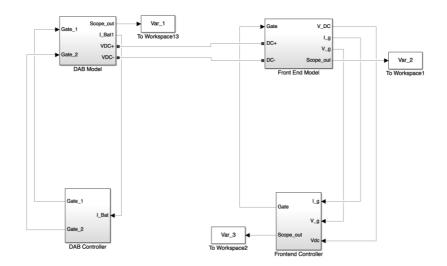

| 3.4.    | Simulation studies                                              | 114      |

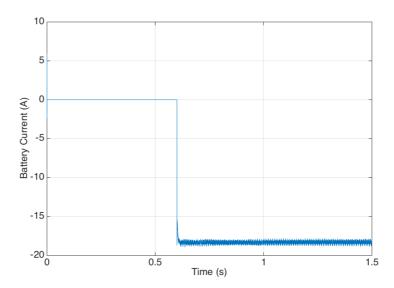

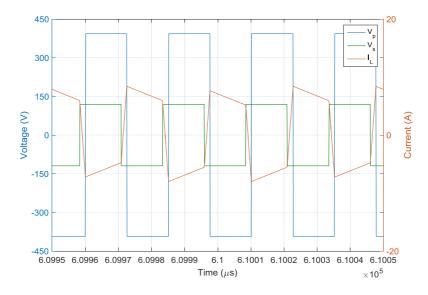

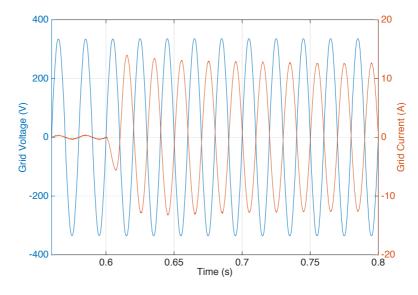

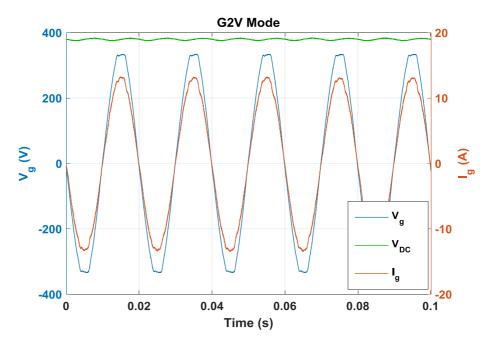

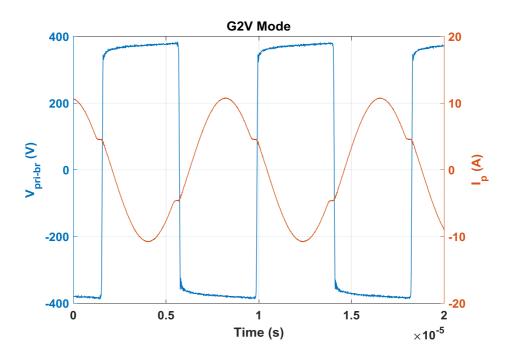

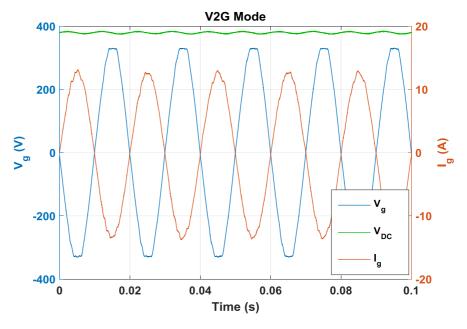

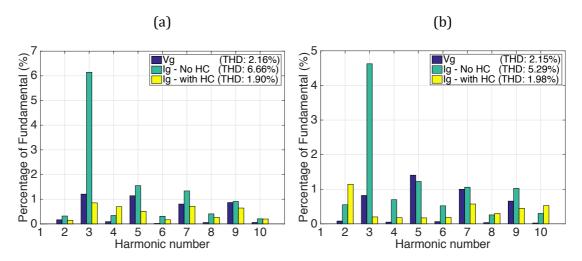

| 3.4.    | 1. HF Transformer based bidirectional battery charging system   | 114      |

| 3.4     | 2. LF transformer based charger simulation                      | 122      |

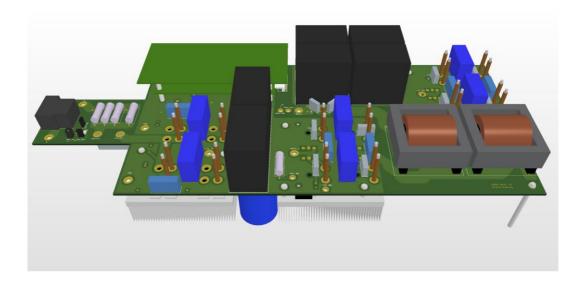

| 3.5.    | Hardware design and setup                                       | 126      |

| 3.6.    | Experimental results and discussion                             | 132      |

| 3.6.    | 1. HF-TF based charger experimental results                     | 132      |

| 3.6     | 2. LF-TF based charger experimental results                     | 137      |

| 3.7.    | Summary                                                         | 144      |

| Chaptei | r 4 Grid Synchronisation in Converters                          | 146      |

| 4.1.    | Introduction                                                    | 146      |

| 4.1.    | 1. Grid synchronisation                                         | 146      |

| 4.1     | 2. The Phase-Locked Loop (PLL)                                  | 148      |

| 4.1     | 3. Synchronous Rotating Frame (SRF) PLL                         | 151      |

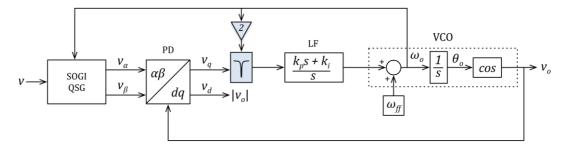

| 4.1.    | 4. Second Order Generalised Integrator (SOGI) based PLL         | 153      |

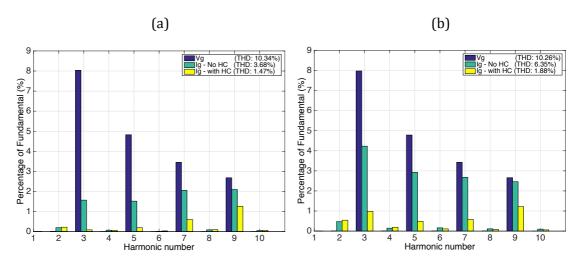

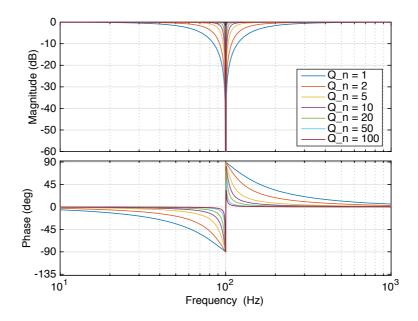

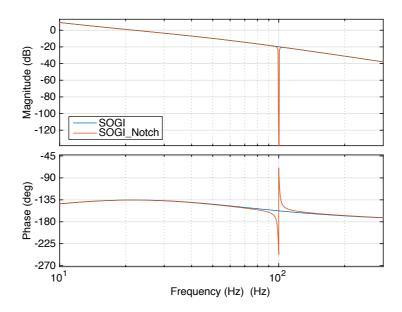

| 4.2.    | Improved SOGI with notch filter                                 | 155      |

| 4.2.    | 1. Analysis of the SOGI PLL harmonic rejection characteristics  | 156      |

| 4.2.2.      | Comparison of analytical prediction of harmonics and time domain   |

|-------------|--------------------------------------------------------------------|

| simul       | lation162                                                          |

| 4.2.3.      | SOGI with notch filter – two different approaches165               |

| 4.2.4.      | Practical implementation and performance comparison171             |

| 4.2.5.      | Summary                                                            |

| 4.3.        | PIIR based PLL for grid synchronisation177                         |

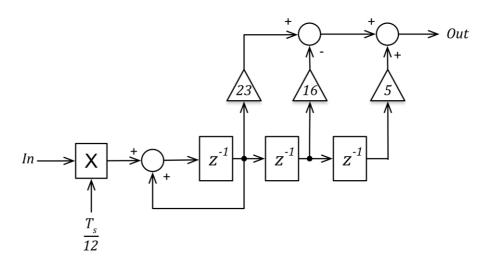

| 4.3.1.      | PIIR filter177                                                     |

| 4.3.2.      | PIIR PLL181                                                        |

| 4.3.3.      | Optimised implementation185                                        |

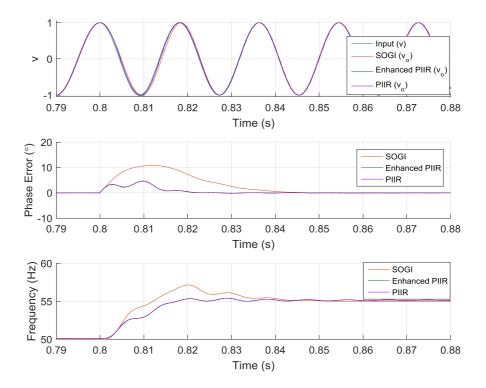

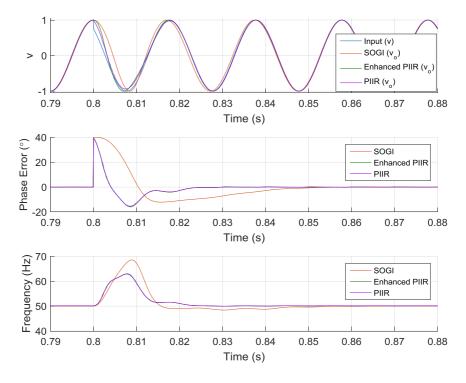

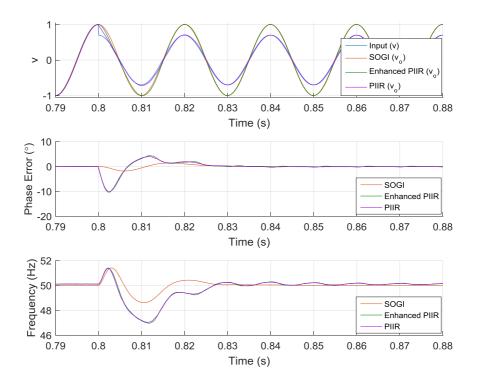

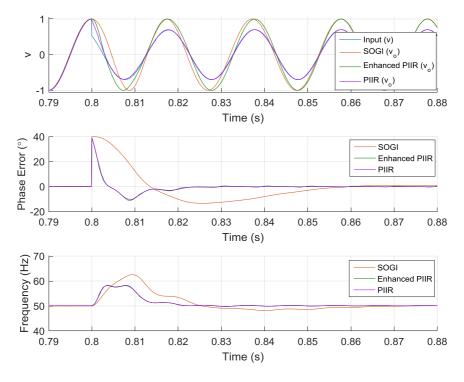

| 4.3.4.      | Practical implementation and performance comparison186             |

| 4.3.5.      | Summary                                                            |

| 4.4.        | Experimental implementation in converter193                        |

| 4.5.        | Conclusions                                                        |

| Chapter     | 5 Islanding Detection197                                           |

| 5.1.        | Introduction197                                                    |

| 5.1.1.      | Islanding197                                                       |

| 5.1.2.      | Anti islanding methods198                                          |

| <i>5.2.</i> | Voltage switching harmonic signature based islanding detection 203 |

| 5.2.1.      | Proposed method of detection203                                    |

| 5.2.2.      | Modelling of inverter LCL filter and utility grid204               |

| 5.2.3.      | Islanding detection zone for varying load impedances207            |

| 5.2.4.      | Islanding detection algorithm210                                   |

| 5.2.5.      | Noise immunity from other switching converters211                  |

| 5.2.6.      | Comparison of detection time212                                    |

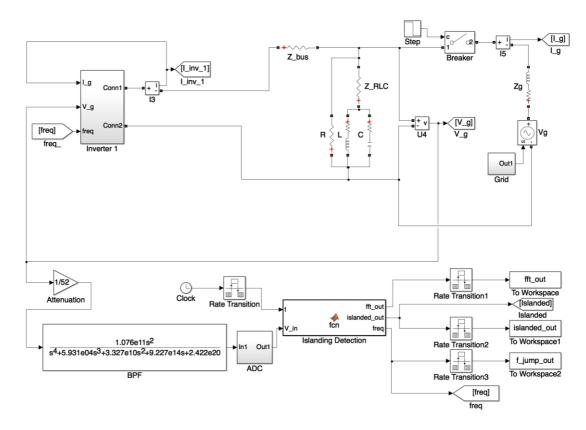

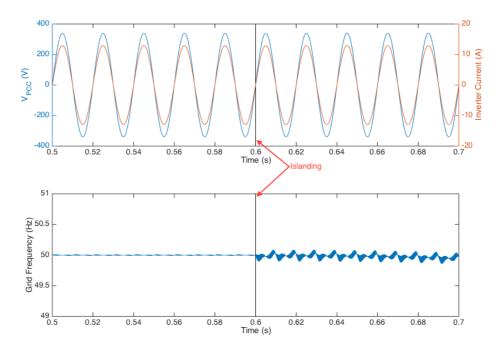

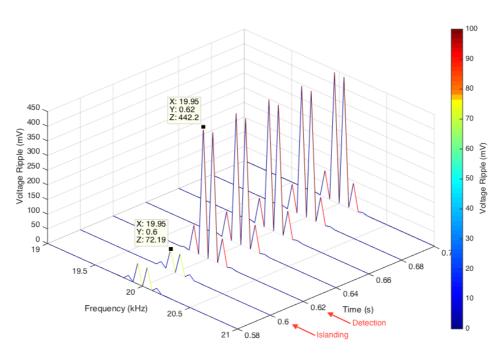

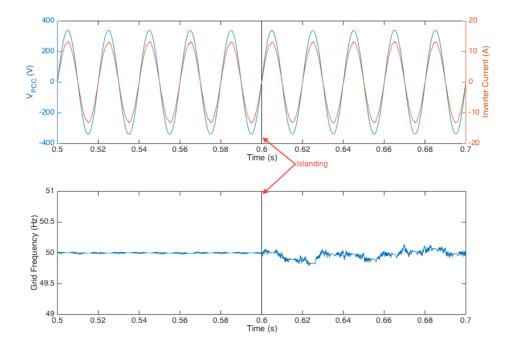

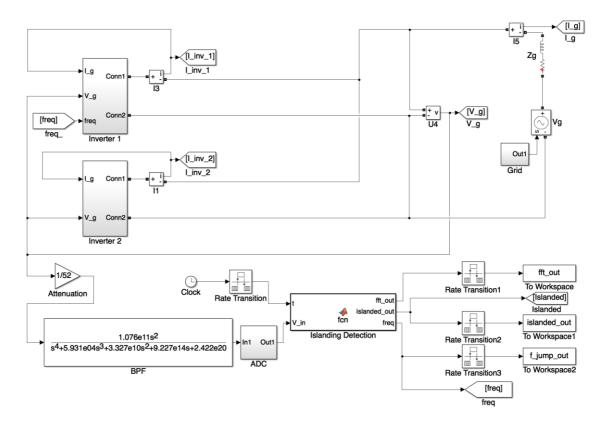

| <i>5.3.</i> | Simulation of islanding algorithm213                               |

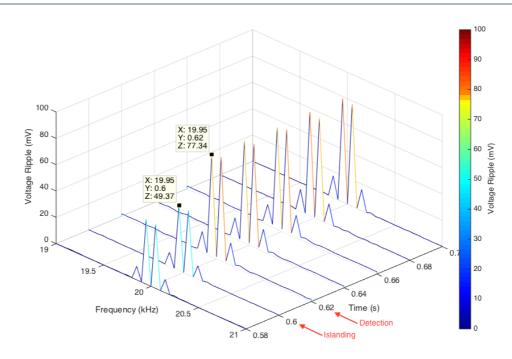

| 5.3.1.      | Simulation case 1 – resistive load215                              |

| 5.3.2.      | Simulation case 2 – RLC resonant load217                           |

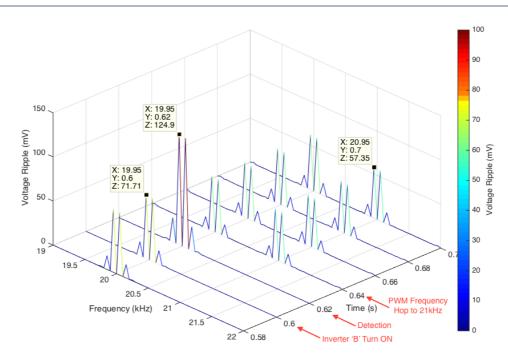

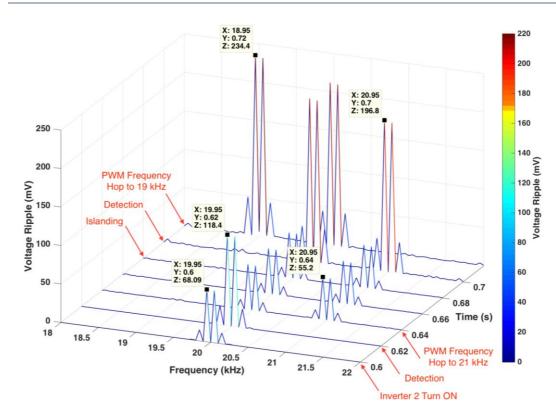

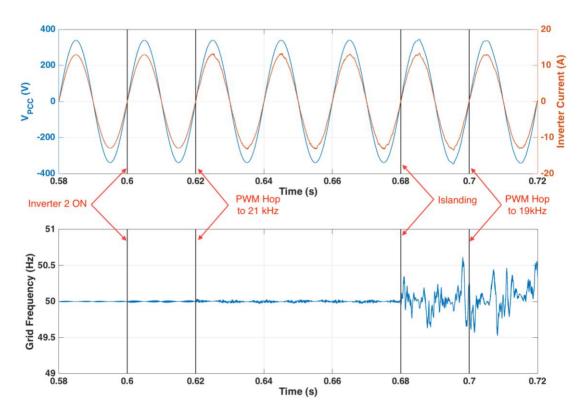

| 5.3.3. Simulation case 3 – connection of a second inverter with | h same PWM     |

|-----------------------------------------------------------------|----------------|

| frequency                                                       | 218            |

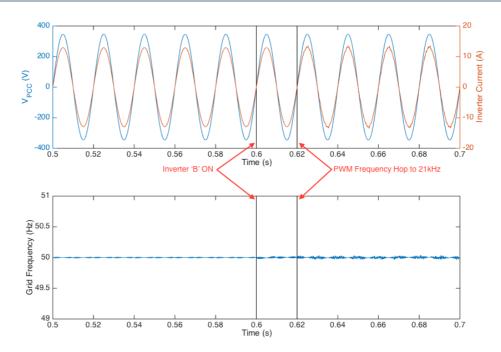

| 5.3.4. Simulation case 4 - detection of islanding under mult    | tiple invertei |

| operation                                                       | 221            |

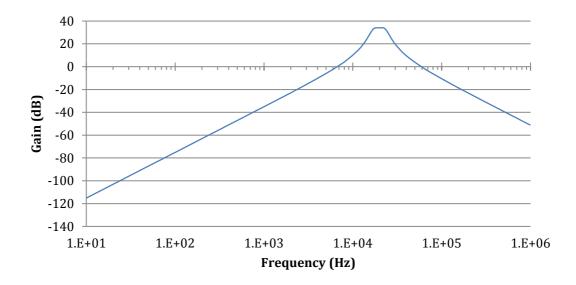

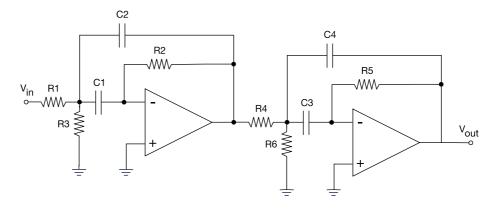

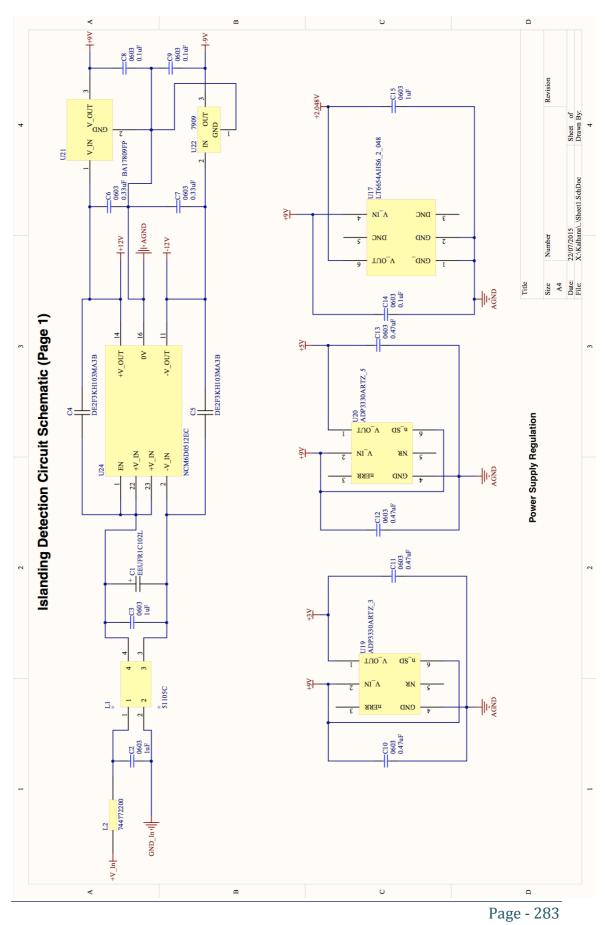

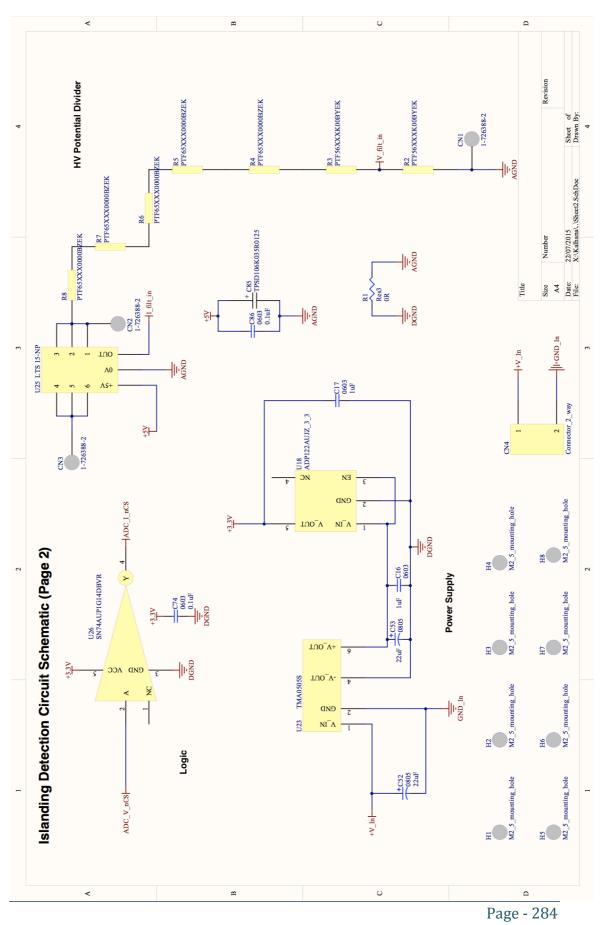

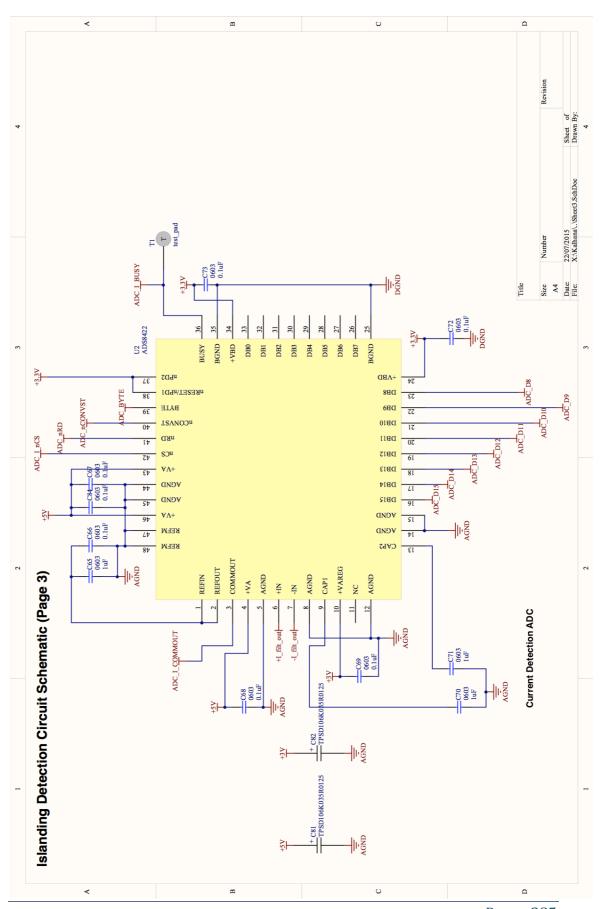

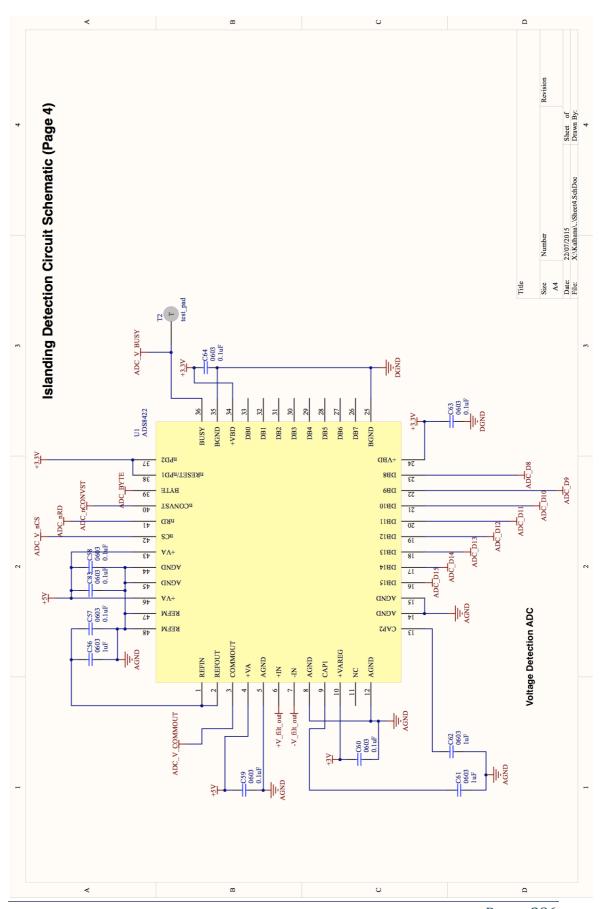

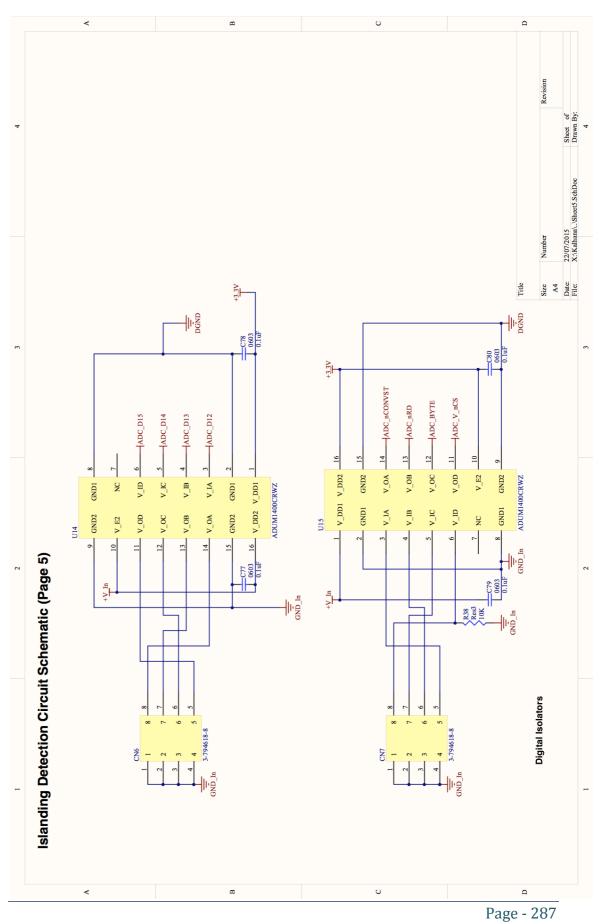

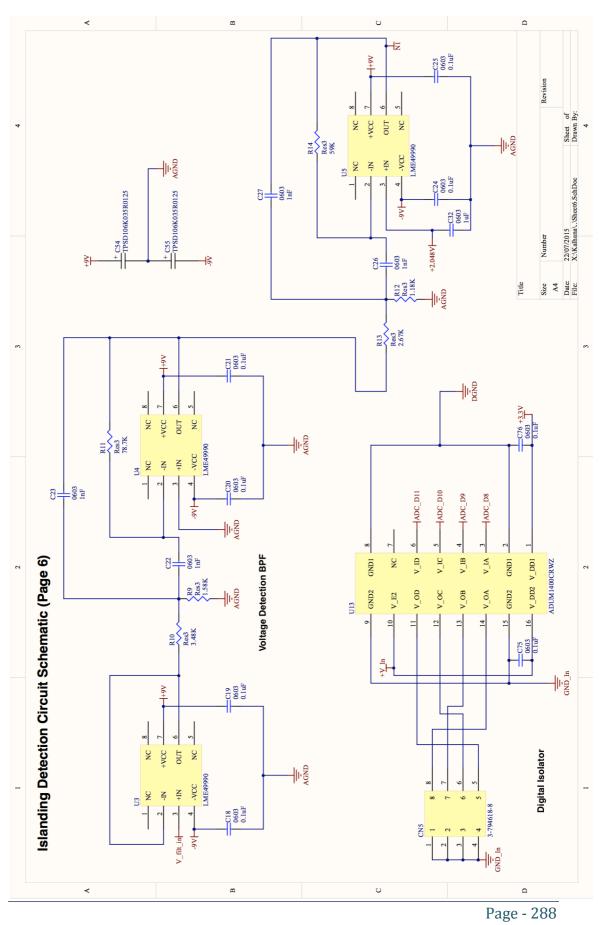

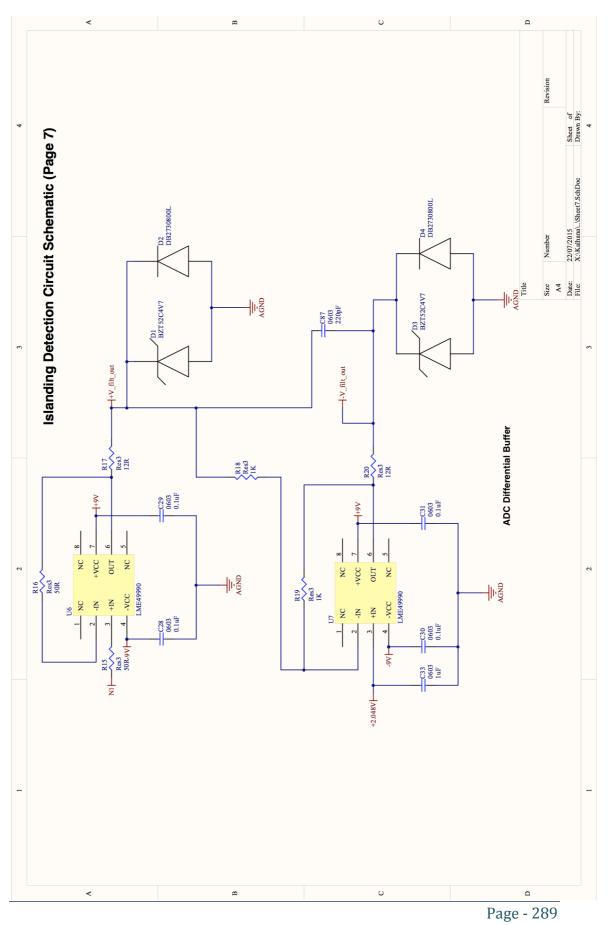

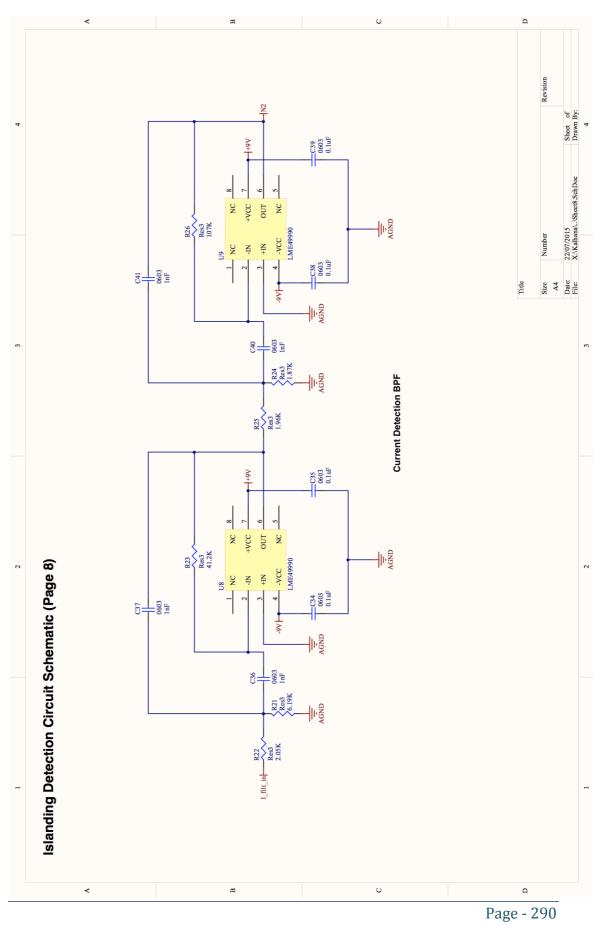

| 5.4. Design of islanding detection hardware                     | 224            |

| 5.4.1. Voltage detection hardware design                        | 224            |

| 5.4.2. Inverter current detection circuit hardware design       | 226            |

| 5.5. Practical implementation                                   | 227            |

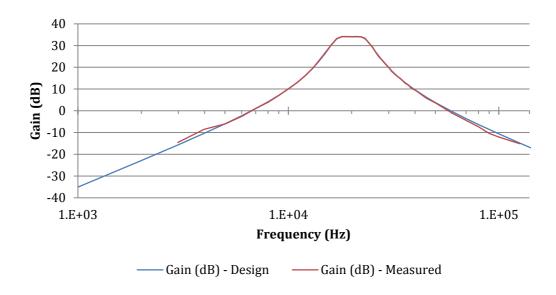

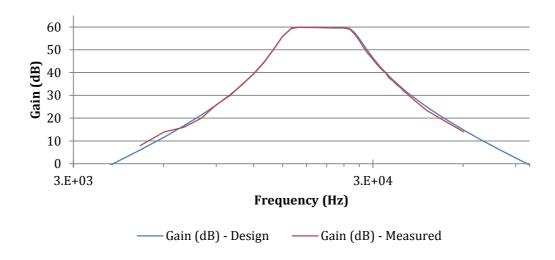

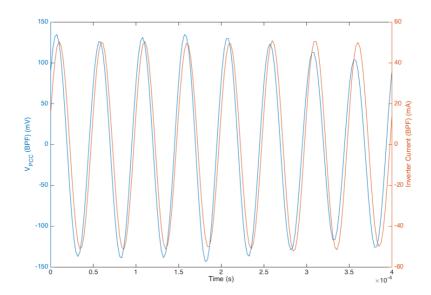

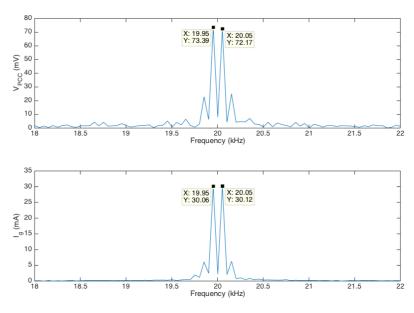

| 5.5.1. Filter performance evaluation                            | 227            |

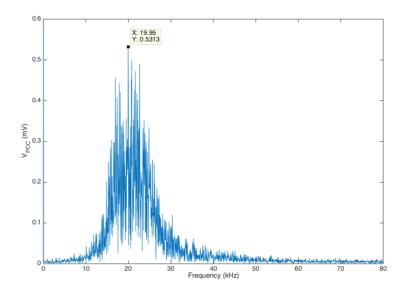

| 5.5.2. Estimation of grid impedance                             | 230            |

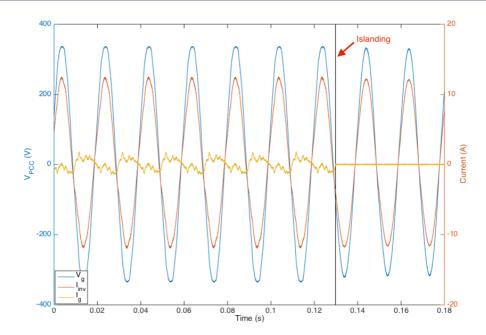

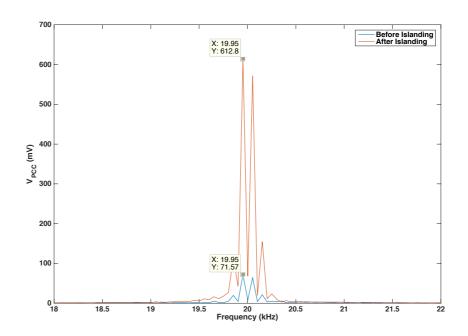

| 5.5.3. Results of islanding detection test                      | 232            |

| 5.6. Discussion and conclusions                                 | 236            |

| Chapter 6 Conclusions and Future Work                           | 237            |

| 6.1. Conclusions                                                | 237            |

| 6.2. Future Work                                                | 239            |

| Appendices                                                      | 240            |

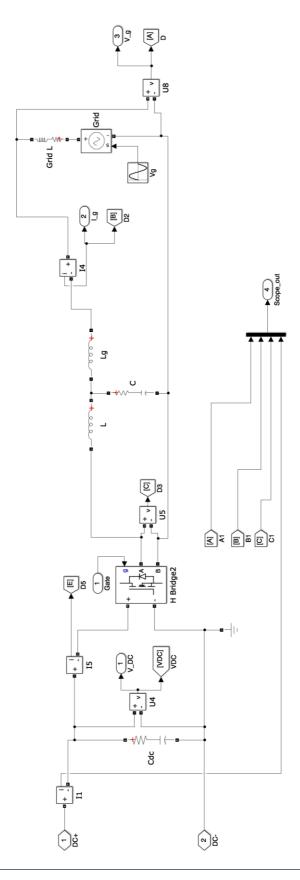

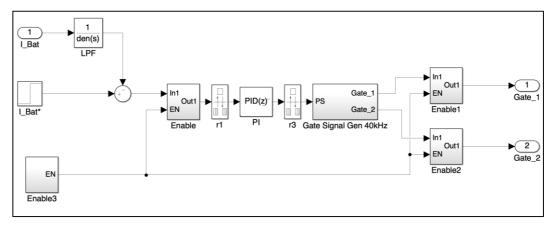

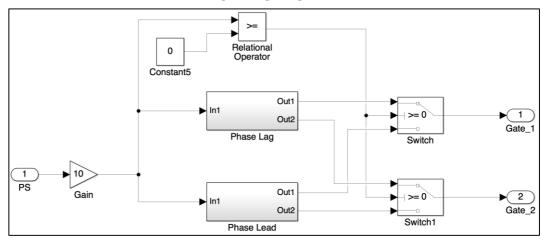

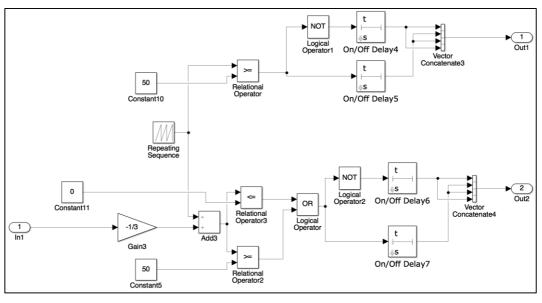

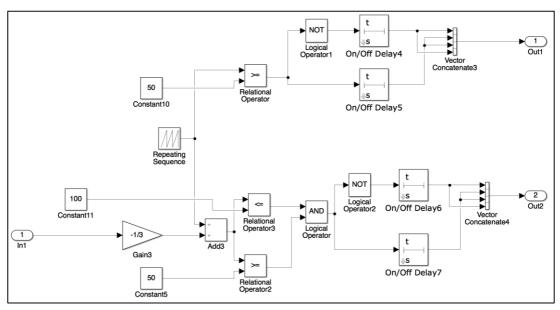

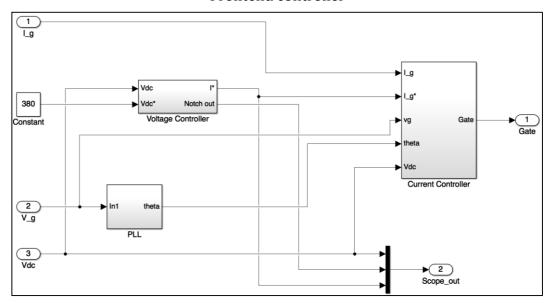

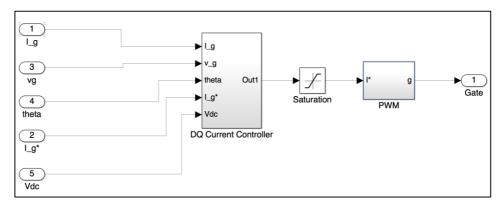

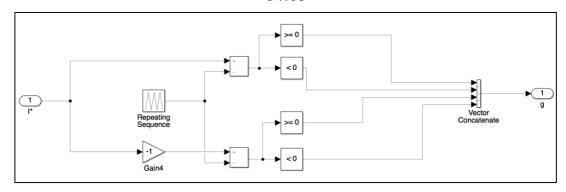

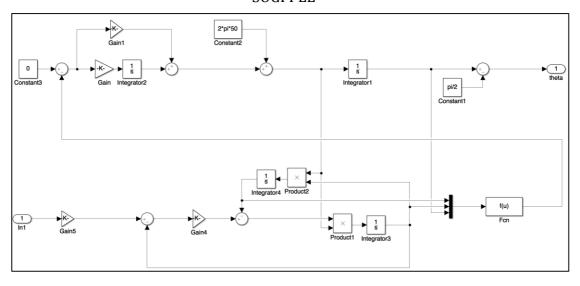

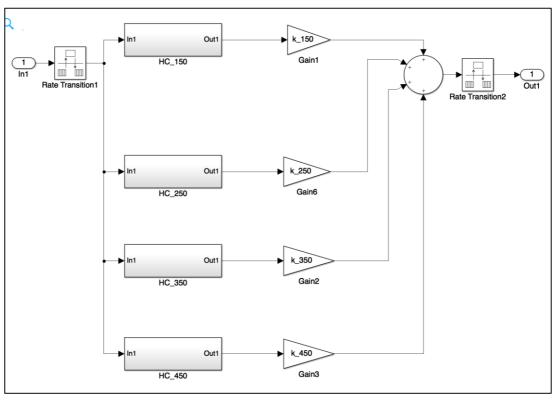

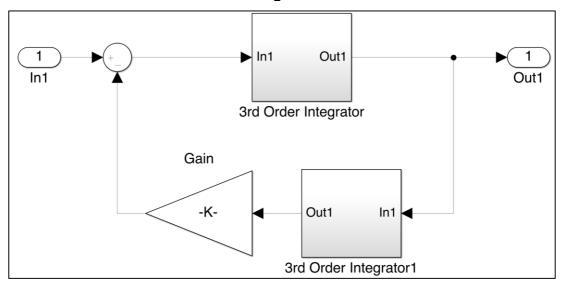

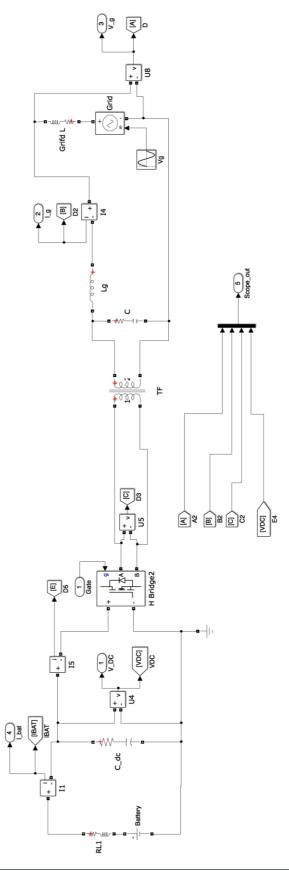

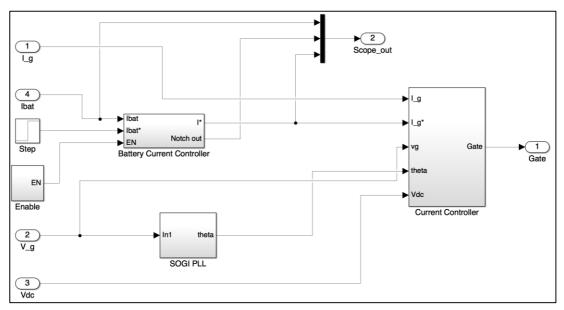

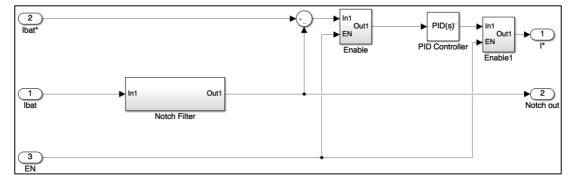

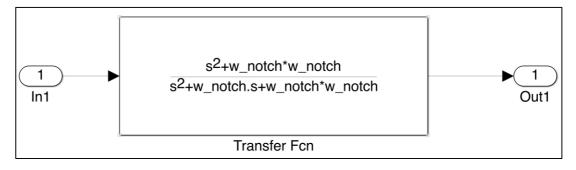

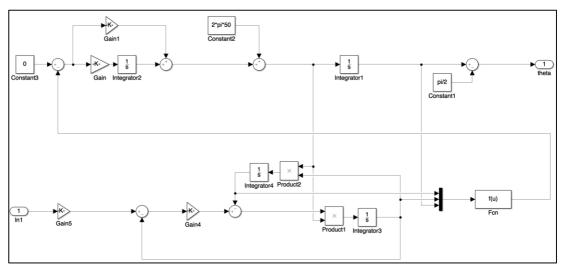

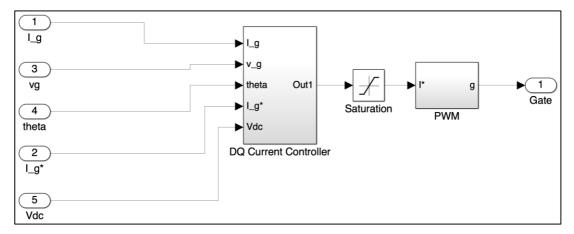

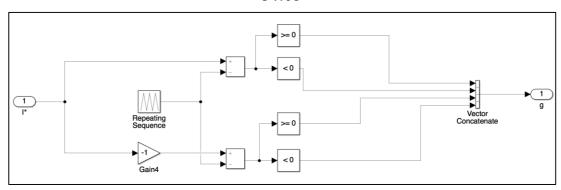

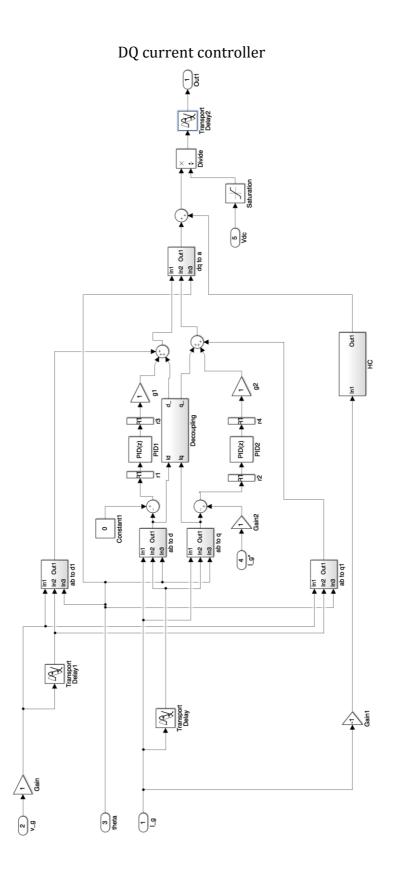

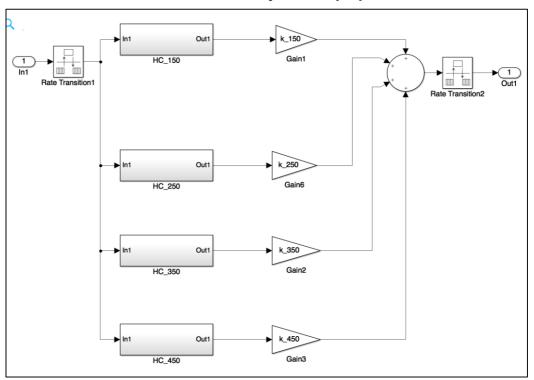

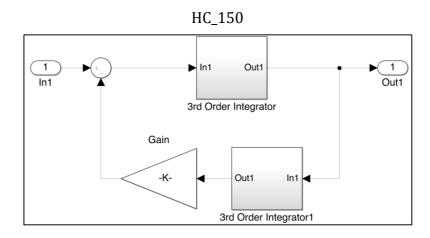

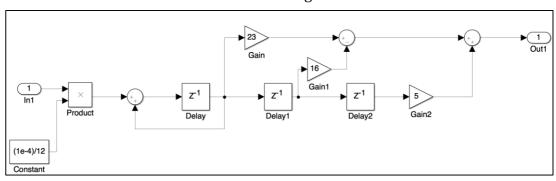

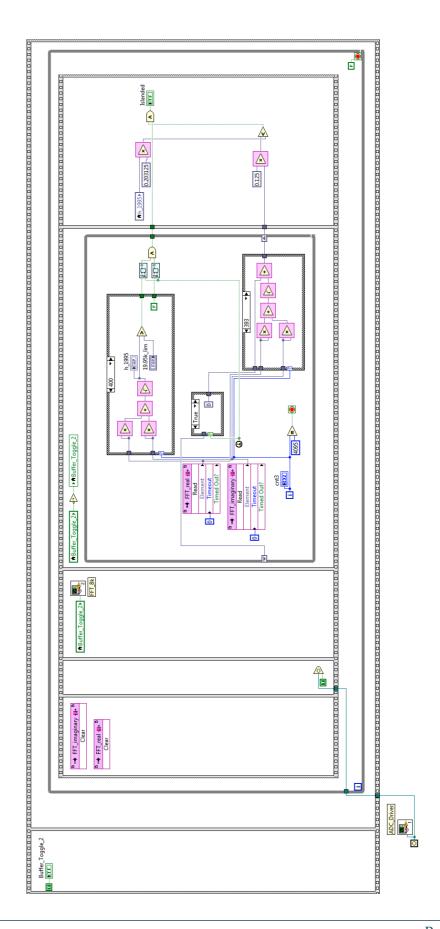

| Appendix A: HF Charger Simulink Diagrams                        | 240            |

| Appendices                                                      | 249            |

| Appendix B: LF Charger Simulink Diagrams                        | 249            |

| Appendices                                                      | 255            |

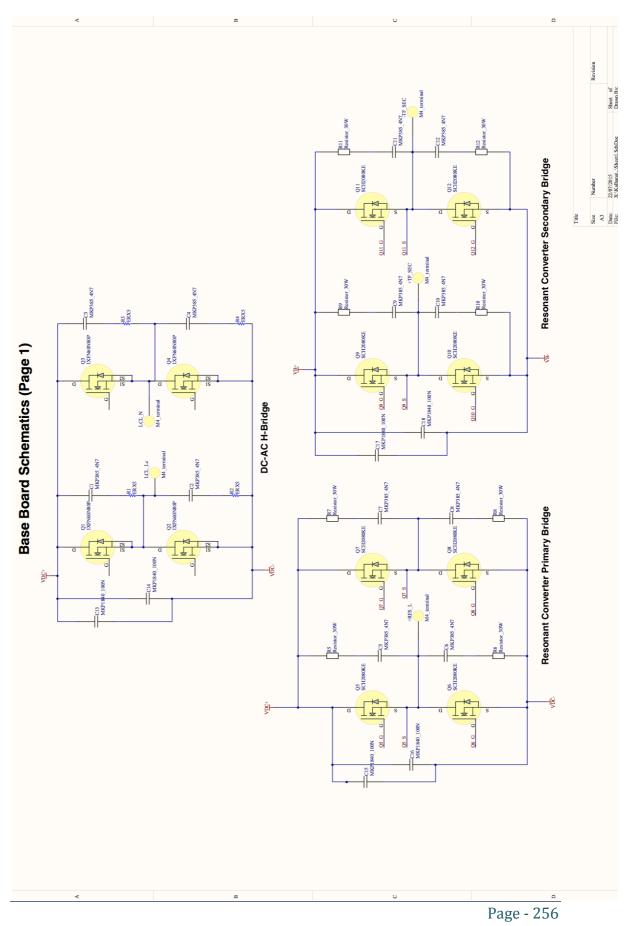

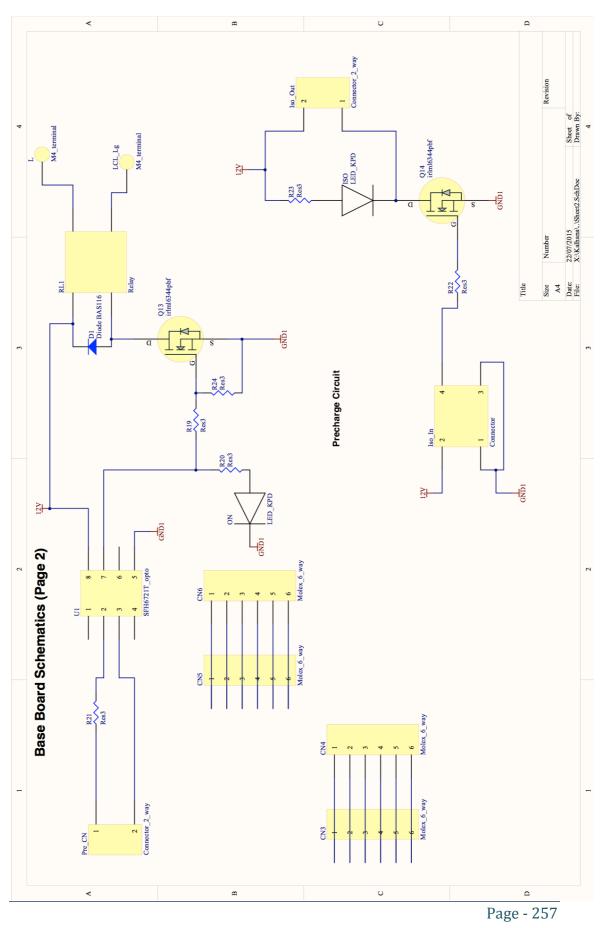

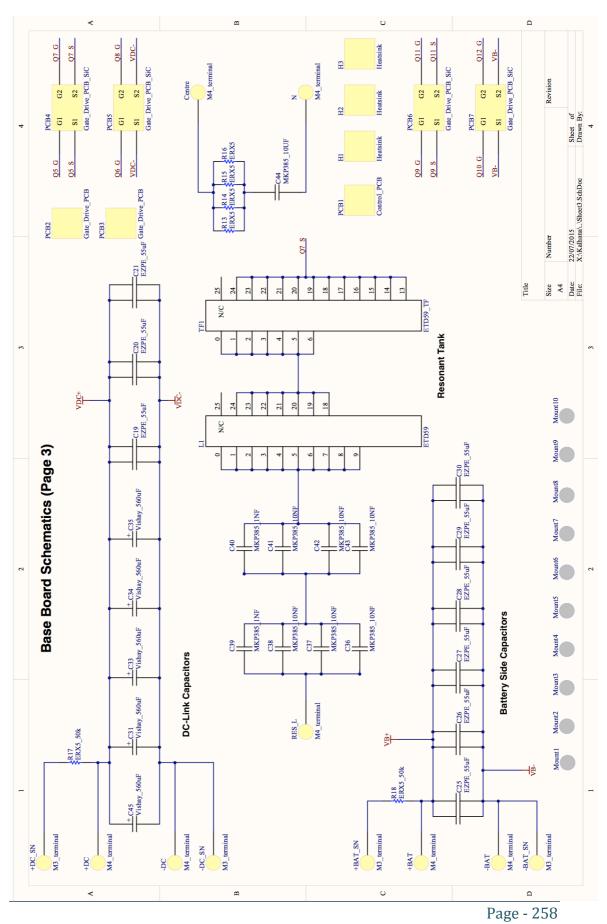

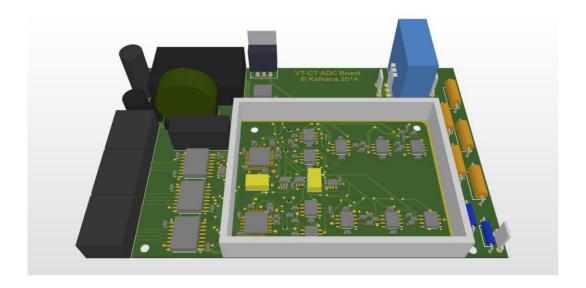

| Appendix C: HF Charger Schematics                               | 255            |

| Appendices                                                      |                |

| Appendix D: Microcontroller Code for PLLs (TI RM46L852)         |                |

| Appendices                                                      |                |

|                                                                 |                |

| Appendix E: Inverter 1 Simulink Diagram                         |                |

| Appendices                                                      | <b>27</b> 5    |

| Appendix F:     | MATLAB Code of Islanding Detection Function   | 275 |

|-----------------|-----------------------------------------------|-----|

| Appendices      |                                               | 278 |

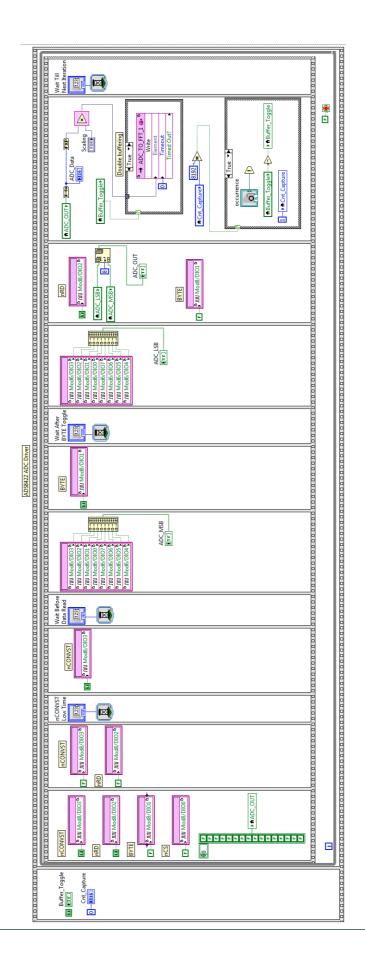

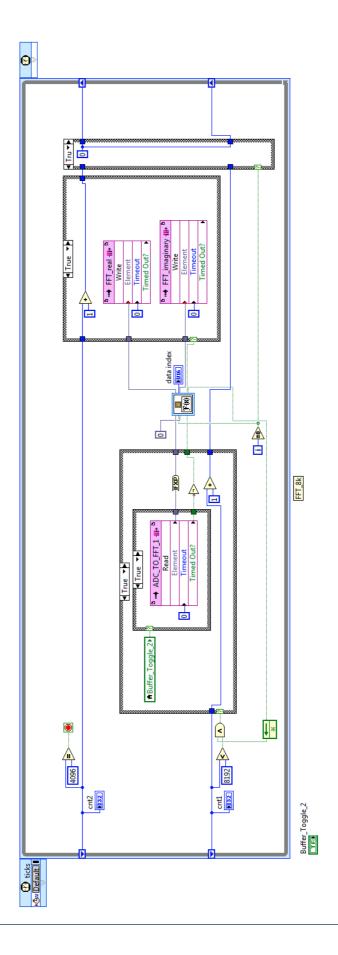

| Appendix G:     | LabView FPGA Code for Islanding Detection     | 278 |

| Appendices      |                                               | 282 |

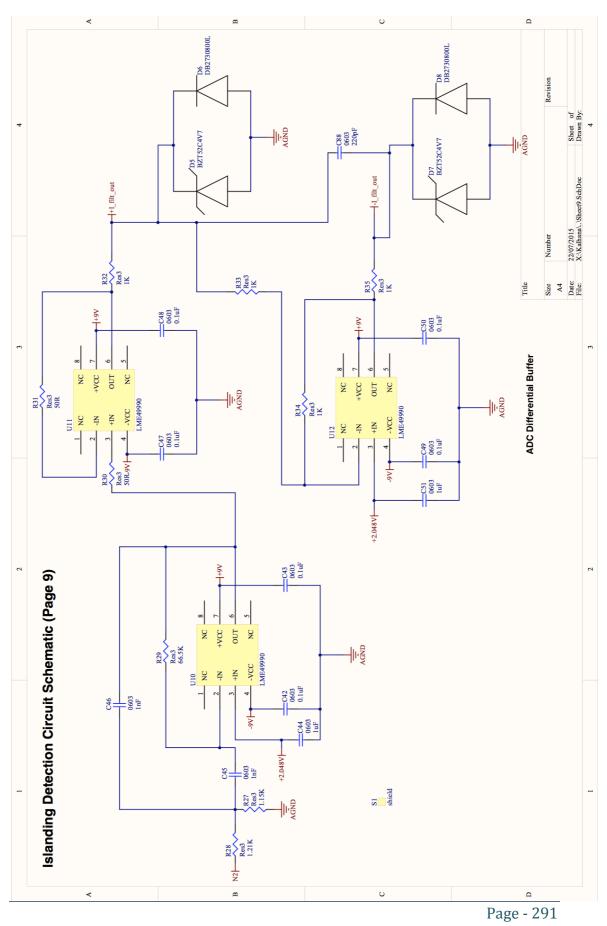

| Appendix H:     | Islanding Detection Circuit Schematics        | 282 |

| Appendices      |                                               | 292 |

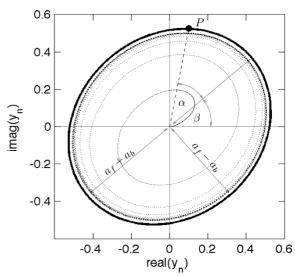

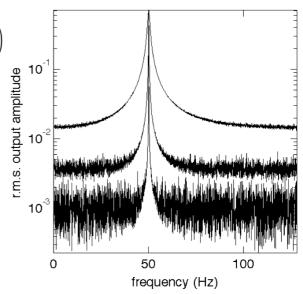

|                 | Complex IIR Filters for Tracking of Sinusoids |     |

| List of Acrony  | ms                                            | 298 |

| References      |                                               | 301 |

| Table of Figur  | es                                            | 323 |

| List of Tables. |                                               | 332 |

# **Chapter 1**

# Introduction

This chapter introduces the general background, context and the motivation for this research. The key contributions of the thesis are also highlighted followed by the outline of the thesis.

#### 1.1. General Introduction

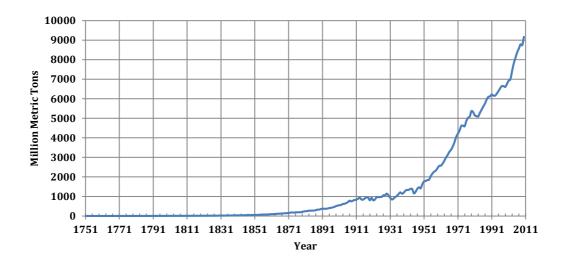

Due to the industrialisation and exponential increase in world population over the previous two centuries, the carbon emissions due to human activity have also seen an exponential increase. For example, the alarming rate of increase of carbon emissions due to the burning of fossil fuels and cement production is depicted in Fig. 1-1. Furthermore, the atmospheric and ocean CO<sub>2</sub> levels have also followed this pattern of increase. This effect has been further compounded by the rapid industrialisation of developing countries.

Fig. 1-1 Total carbon emissions due to the burning of fossil fuels and cement production from 1751 to 2010 (Data from [1])

There is wide consensus in the field of climate science that man-made CO<sub>2</sub> emissions are one of the main causes of the recent increase in global temperatures and the associated anomalies in the climate [2-4]. Furthermore, there has been recent research [5] that suggests that even if all man-made CO<sub>2</sub> emissions were eliminated, the recovery time for the climate could take up to 1000 years.

As a solution for reducing carbon emissions, there has been a different outlook at the ways in which power is generated where more renewable sources of energy are favoured, as well as a trend for more efficient methods of consumption and the storage of the generated energy.

Renewable energy sources include wind, hydro, solar, geothermal, tidal as well as biodiesels that are synthesised from bio matter. Changes to the way that the energy consumed include, the trend for more efficient vehicles as well as the widespread deployment of electric and hybrid electric vehicles in the transportation sector. The sectors of industrial processing as well as the domestic power consumption have also followed a similar path for the optimisation of energy efficiency, driven in part by government regulations (such as the *private rented sector energy efficiency regulations* [6] and the *climate change levy* [7]).

# 1.1.1. Electric Vehicles (EVs)

Due to the concerns regarding climate change which have resulted in tough emission regulations, increase in global demand for energy as well as the rapid depletion of fossil fuel sources, there is a global drive for the development and transition into electric, hybrid as well as fuel cell vehicles [8].

The broad term of "Electric Vehicles" can be categorised into three main types of vehicles, which are battery electric vehicles, hybrid electric vehicles (HEVs) and fuel cell vehicles (FCVs) [8].

#### **Battery EVs**

Battery EVs are powered exclusively with battery (most commonly Lithium based batteries) and ultracapacitor based energy storage technologies, which in turn drives an electric motor(s), and therefore have zero emissions. The disadvantages of battery based EVs are that the typical driving range is short due to the low energy density of batteries, the long recharge time and the high cost of batteries [8].

# **HEVs**

To overcome the issues of battery based EVs, HEVs have been developed which combines an internal combustion engine (ICE) with an electrical drive train in either a series, parallel, series-parallel or complex arrangements. HEVs therefore offer the increased driving range of conventional ICE vehicles with the added advantage of energy efficiency with the use of energy recovery, storage and management strategies.

In the series arrangement, the ICE converts the chemical energy from the conventional fuel source to mechanical energy after which it is converted to electricity through a generator followed by an electric motor(s) for driving the wheels. The efficiency of series HEVs are lower due to the three stage energy conversion process despite the simplicity of the power train architecture [8].

In the parallel HEV arrangement, both the ICE as well as the electric motor drives the wheels at the same time. The advantages of this arrangement include the elimination of the separate generator as well as the smaller size of ICE and motor due to the shared power delivery.

The series-parallel method combines properties of both the series as well as the parallel type HEVs with the goal of incorporating the benefits of both architectures. Series-parallel HEVs differ from parallel HEVs by the addition of a generator that is linked to the ICE. However, the method has the disadvantage of increased complexity and cost [8].

The complex HEV is similar to the series-parallel HEV, but has a more complex design where the generator that is linked to the ICE can also act as a motor. Although the complex HEV offers more flexibility in terms of energy management and therefore efficiency, the downside is the added complexity and cost.

HEVs typically implement regenerative braking by using the motor(s) as a generator(s) to charge the batteries/ultracapacitors as opposed to dissipating the kinetic energy as heat in the brakes.

The method of replenishing the energy in HEVs can either be through conventional refuelling (gasoline/diesel) or by charging the battery externally. The latter type of HEVs is generally referred to as plug-in hybrid electric vehicles (PHEVs).

#### **FCVs**

FCVs are also a zero emission vehicle due to the hydrogen based fuel cell energy source. The power delivery system in a FCV is comprised of a hydrogen storage tank followed by fuel cells where the electricity is generated. This is followed by an electric motor drive system. Although the FCVs have the advantage of zero emissions and reasonable driving range, the disadvantages include the high cost and low cycle life of fuel cells as well as the difficulty in the storage and transport of hydrogen as a fuel.

# 1.1.2. Electric Vehicle Chargers

The charging systems for EVs can be categorised into 2 types, which are, on-board and off-board charger systems. The off-board charger systems are generally capable of providing a higher amount of power that is delivered to the vehicle as DC. By using off-board chargers, it is possible to move the weight of

the AC-DC conversion hardware to the external infrastructure, which is advantageous as it reduces the total weight of the EV.

However, having an on-board charger provides more flexibility since the EV is able to charge in residential as well as many other locations where an AC power source is available. On-board chargers are usually categorised into 2 levels; level 1 being single phase where the power rating is typically under 3 kW and level 2 being 3-phase chargers capable of up to 20 kW (for example, Tesla Model S dual wall charger).

Wireless inductive charger systems for EVs are also available [9, 10] although not as widely used as conductive type chargers due to the issues of lower efficiency and high cost.

# Grid-to-Vehicle (G2V) and Vehicle-to-Grid (V2G)

Although the main goal of an EV charger system is to recharge the battery (G2V), there is also the opportunity to utilise the charger infrastructure to reverse the flow of power so as to provide power to the grid (V2G) even though it seems counterintuitive at first glance.

Since the electric utility system has to keep up with a wide range of demand conditions, the cost of power also varies throughout the day where generally the night-time demand is low and hence the cost is lower. Since EVs are parked and not in use most of the time, EVs as an energy storage mechanism has been proposed [11-16] and is currently under trial in many countries (leading countries include Japan, US, Germany, Denmark, South Korea and the UK).

One of the aims of the V2G concept is to provide power for transient demands "peak load levelling" where traditional generation is not able to react fast enough. Other goals include frequency stabilisation [11, 12] and reactive power compensation [14]. Furthermore, there are proposals [15] where V2G technology could be used for the buffering of excess renewable energy in EV

batteries during low utility demand periods and to provide power for high demand times thereby maximizing the renewable energy production.

Some of the key issues in V2G technology are connection with a polluted grid [17] and the detection of islanding condition as it causes safety problems for utility workers [18]. This thesis addresses these issues for single phase systems with improvements to grid synchronisation as well as islanding detection methods. Other issues in V2G technology include the low overall efficiency due to the charge-discharge losses in batteries; the issue of excess battery wear as well as the absence of a unified standard for communication with the utility system. However, V2G technology has a promising future as battery technologies mature and as utility and vehicle systems are getting more and more integrated through the Internet.

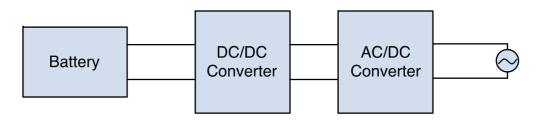

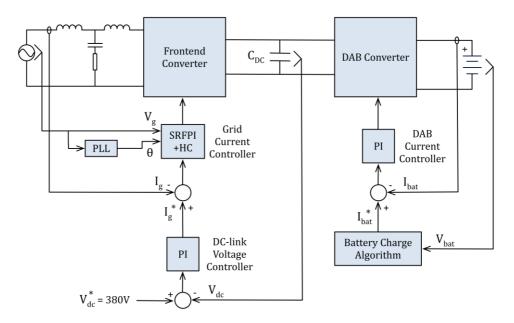

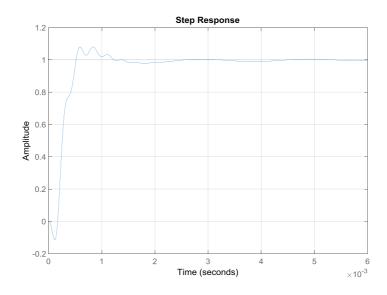

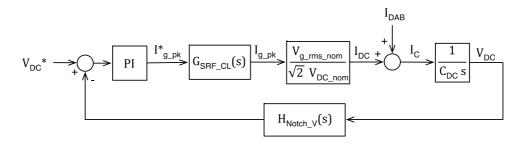

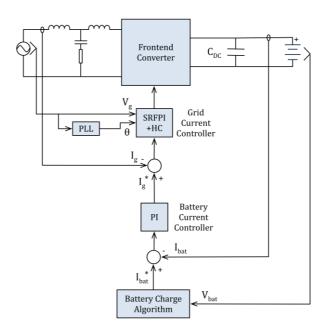

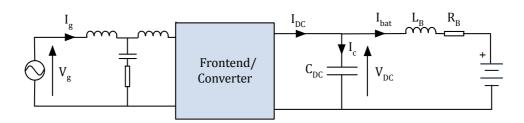

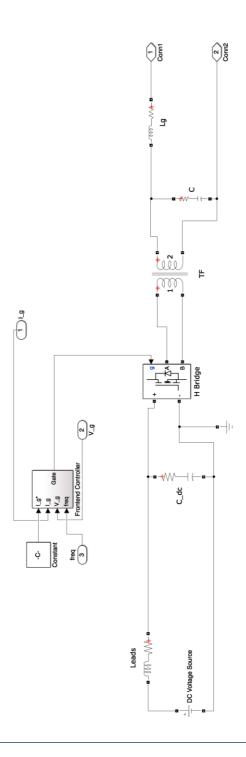

## On-Board Bidirectional Charger (OBBC) topology

In this thesis, the focus will be on single-phase on-board bidirectional charger systems, as single phase utility systems are the most accessible form in a residential environment. The typical topology for such systems is illustrated in Fig. 1-2. The first stage is the AC to DC converter, which facilitates the bidirectional power from the utility to the DC link of the charger system while maintaining unity power factor. The regulation of the battery current is handled through the DC/DC converter [19]. Where galvanic isolation is required, a high frequency transformer is incorporated into the DC/DC converter stage as the transformer weight is reduced with increasing operating frequency.

Fig. 1-2 Typical topology of a bidirectional charger

Examples of non-isolated bidirectional DC-DC converters that are commonly used include half-bridge, Ćuk, SEPIC/Luo and cascade buck-boost converters [20, 21].

Isolated bidirectional DC-DC converters can either be half bridge or full bridge topologies. The dual half bridge converter (DHB) proposed in [22] and the non-regulating half bridge converter presented in [23] are examples of half bridge converters. Examples of full bridge converters are; the dual-active bridge (DAB) converter [24] and full bridge resonant type converters [25-31].

Furthermore, in applications where a wide input/output voltage range is required, a two stage converter consisting of a DAB/resonant and a non-isolated DC/DC converter is utilised in order to achieve the maximum efficiency [32] at the cost of increased complexity.

# **Grid synchronisation**

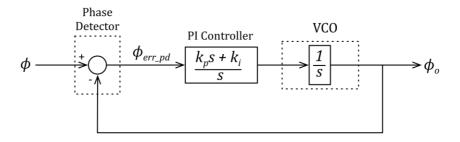

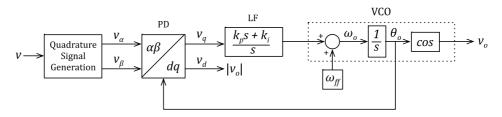

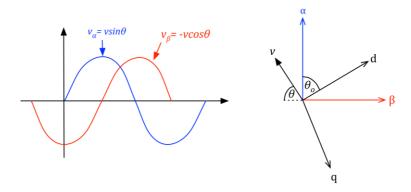

Grid synchronisation is the process obtaining the instantaneous parameters of the grid voltage vector in order to facilitate power transfer in a power converter. The most common method of synchronisation is the phase locked loop (PLL) [33].

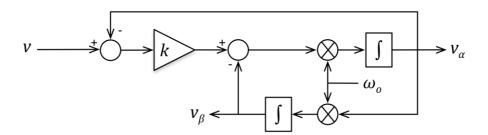

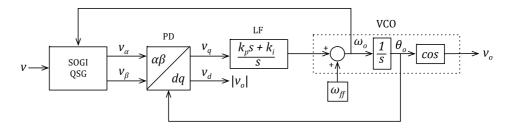

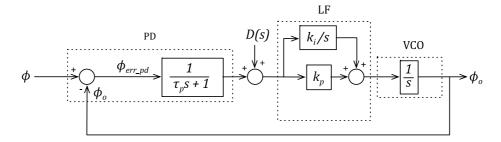

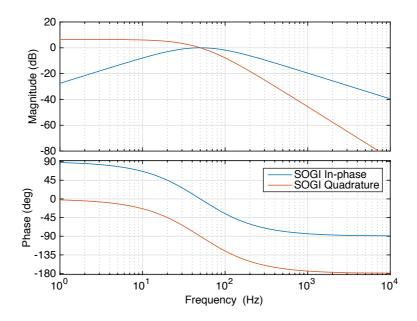

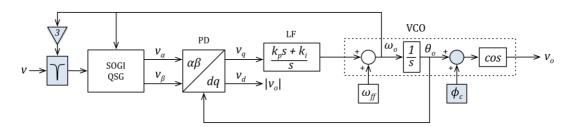

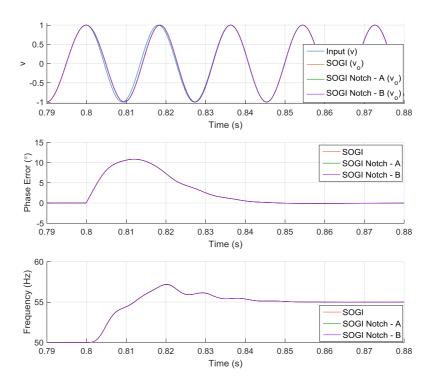

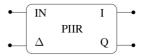

A variety of different PLL algorithms have been developed over the years [17, 34-43] with varying levels of complexity and performance. This thesis focusses on the widely used second order generalised integrator (SOGI) based PLL [38] as well as a new class of discrete time PLL termed the phasor infinite impulse response (PIIR) PLL that has been developed by Ed Daw et al. [Appendix I]. A detailed discussion of the current methods of grid synchronisation is carried out in Chapter 4.

# Islanding detection

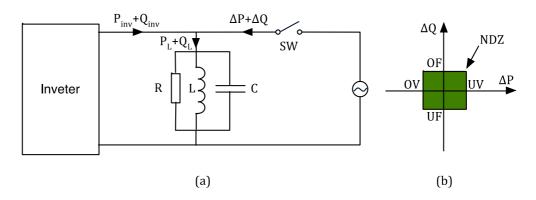

Islanding refers to the condition where the distributed generator (DG) continues to operate with local loads after the utility has been disconnected [44]. Unintentional islanding is undesired since it poses a hazard to utility workers as well as due to the damage that can result to equipment when reclosure of the utility occurs while the DG is out of phase with the utility [18]. IEEE1547 requires that a DG system detects and ceases to energise the area electrical power system (EPS) within 2 seconds of islanding. Since V2G operation of a battery charger constitutes as a distributed generator, islanding detection and prevention is an important consideration in a bidirectional battery charger.

Islanding detection methods are broadly categorised into two methods which are, passive and active methods of detection. Passive methods rely on monitoring various parameters of the grid voltage/current as a means of islanding detection. Active methods in contrast are based on introducing a disturbance to the output of the converter and monitoring the response of the voltage/current. Chapter 5 of the thesis focusses on the development of a passive method of islanding detection.

#### 1.2. Motivation

Since V2G is an emerging technology and has the potential to change the landscape of the utility network, in these times of uncertainty on the future of fossil fuels and climate change, this research aims to contribute to the development of on-board bidirectional charging systems for electric vehicles.

The main aims of the research are highlighted as follows.

1. The investigation, design, simulation and experimental demonstration of an alternative topology of bidirectional charger utilising a low frequency

- transformer integrated with the motor drive and comparison with a DAB based charger system.

- 2. Analysis of the effects of the 3<sup>rd</sup> harmonic distortion on the output of the second-order generalised integrator (SOGI) based phase locked loop (PLL) and methods to mitigate the issue.

- 3. Investigation of the viability of a new class of discrete time PLL that has been proposed by Ed Daw et al. [Appendix C] termed the phasor infinite impulse response PLL (PIIR PLL) in the application of grid converters.

- 4. Development of a new passive islanding detection method for grid converters.

#### 1.3. Main Contributions

The main contributions of the research are outlined as follows.

- 1. A comparative study between a low frequency transformer based and high frequency DAB based bidirectional charging system have been carried out and the weight, cost and efficiency have been compared.

- 2. An optimised LCL filter design method for the two converters has been presented which characterises the high frequency current ripple as well as the losses in the damping resistor.

- 3. Controller design, simulation and experimental validation of the two converters have been carried out.

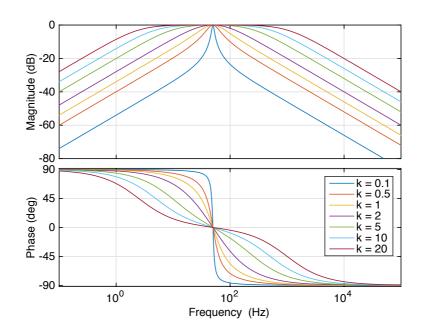

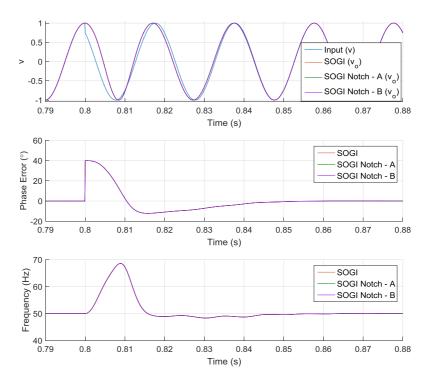

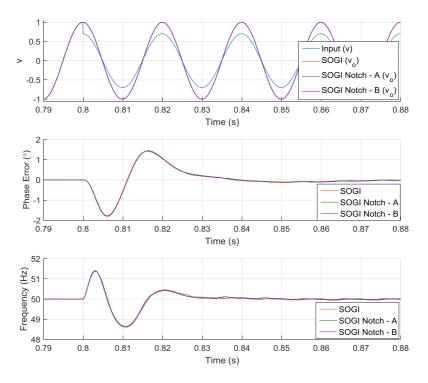

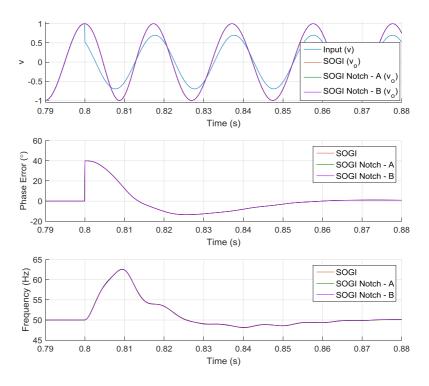

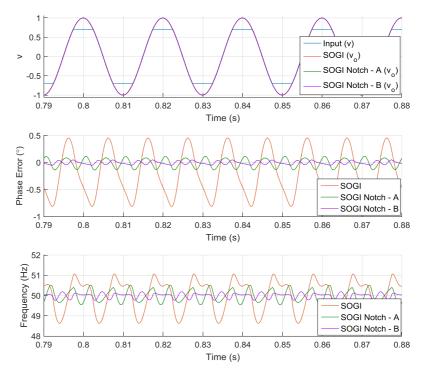

- 4. The impact of 3<sup>rd</sup> harmonic distortion on the performance of SOGI PLLs has been investigated through an analytical method that has been developed to predict the resulting output harmonic magnitudes.

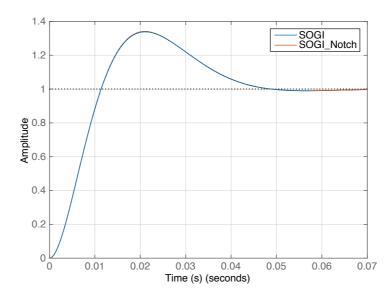

- 5. The 3<sup>rd</sup> harmonic rejection performance of the SOGI PLL has been dramatically improved by the addition of notch filters in either the feedback or pre-filter configurations.

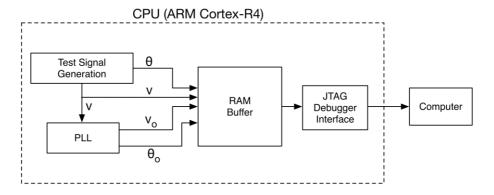

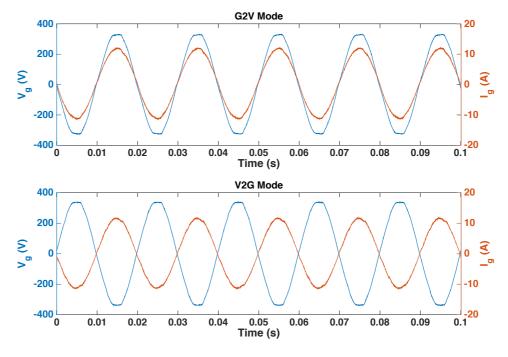

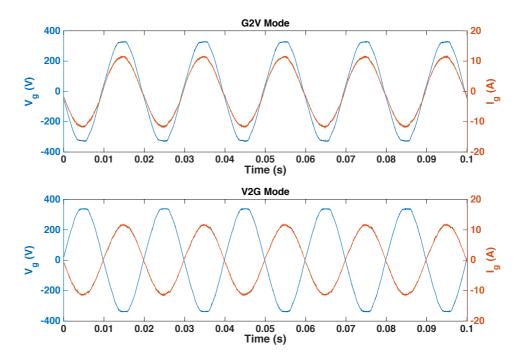

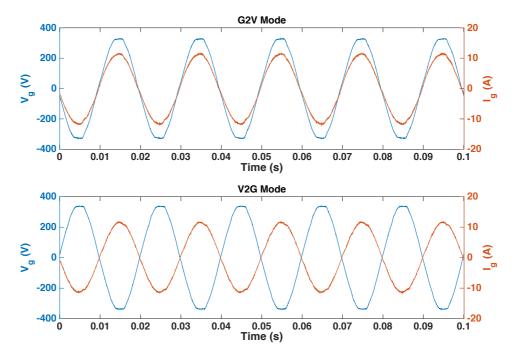

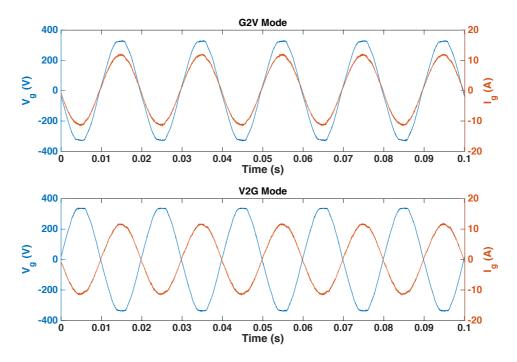

- 6. A new PLL structure based on the novel IIR filter proposed by Ed Daw et al. [Appendix C] has been investigated for application in grid converters. The new PLL has been evaluated with hardware-in-the-loop (HIL) simulations for transient and abnormal grid conditions and compared with the SOGI PLL for performance evaluation as well as computational requirements. Furthermore, the new PLL has been demonstrated in both G2V and V2G modes of operation in the bidirectional charger hardware.

- 7. A new islanding detection algorithm based on the detection of high frequency switching harmonic signature with frequency hopping has been presented which has the advantage of multi-inverter compatibility. Furthermore, the difficulty in detection for PWM harmonic based methods when capacitive loads are present has been analysed. The algorithm has also been demonstrated in hardware.

# 1.4. Outline of Thesis

The outline of the remaining chapters of the thesis is given below.

Chapter 2 – On-board Bidirectional Charger Design and Comparison

- The comparative study of two bidirectional charger topologies is carried out with an emphasis on the design procedure for the magnetic components and switching device selection.

- The optimal LCL filter design method for both converter types is presented.

Chapter 3 – Controller Design, Simulation & Experimental Results of the On-Board Bidirectional Charger Systems

- The controller design methodology for the two converters is presented.

- The two On-Board Bidirectional Charger (OBBC) systems with the controllers are simulated and the results are presented.

• Hardware verification results are presented and discussed.

# Chapter 4 – Grid Synchronisation in Converters

- The performance of the SOGI PLL under 3<sup>rd</sup> harmonic distortion in the input is investigated through an analytical method.

- Two improved topologies of SOGI PLL for the suppression of 3<sup>rd</sup> harmonic interference is presented and simulated in HIL.

- The viability of the PIIR PLL for grid converter applications is investigated and validated in hardware.

# Chapter 5 – Islanding Detection

- A new islanding detection method based on the detection of high frequency switching harmonic signature is presented.

- The difficulty in detection for PWM harmonic based methods when capacitive loads are present has been analysed.

- The new algorithm is demonstrated in hardware.

## Chapter 6 – Conclusions and Future Work

• This chapter summarises the conclusions of the work that is presented in the thesis and discusses the scope for future work.

# 1.5. List of Publications

- K. Colombage, J. Wang, C. Gould, and C. Liu, "PWM Harmonic Signature Based Islanding Detection for a Single-Phase Inverter with PWM Frequency Hopping," in Energy Conversion Congress and Exposition (ECCE), 2015 IEEE, 2015.

- C. Gould, **K. Colombage**, J. Wang, D. Stone, and M. Foster, "A comparative study of on-board bidirectional chargers for electric vehicles to support vehicle-togrid power transfer," in *Power Electronics and Drive Systems (PEDS)*, 2013 IEEE 10th International Conference on, 2013, pp. 639-644.

- C. Liu, J. Wang, **K. Colombage**, C. Gould, B. Sen, and D. Stone, "Current Ripple Reduction in 4kW LLC Resonant Converter Based Battery Charger for Electric Vehicles," in *Energy Conversion Congress and Exposition (ECCE)*, 2015 IEEE, 2015. \*

- X. Yuan, J. Wang, and **K. Colombage**, "Torque distribution strategy for a front and rear wheel driven electric vehicle," in *Power Electronics, Machines and Drives (PEMD 2012)*, 6th IET International Conference on, 2012, pp. 1-6.

The second and third chapter of the thesis presents work carried out under two projects which are, the Personal Mobility (P-MOB) project [45] followed by the Internet of Energy (IoE) project [46]. The work has been done in collaboration with project partners as well as staff at the University of Sheffield.

<sup>\*</sup> The contribution to the publication was the MATLAB coding for obtaining the small signal transfer function of the LLC converter.

# **Chapter 2**

# On-board Bidirectional Charger Design and Comparison

This chapter compares two promising topologies of single-phase on-board bidirectional chargers for use in an electric vehicle, the first with a low frequency transformer (LFT) and the other with a high frequency isolating transformer.

#### 2.1. Introduction

An on-board charger needs to be lightweight, compact and low cost for it to be commercially viable and practical. Furthermore, galvanic isolation between the grid side and battery side is also an important requirement to ensure the safety of the user.

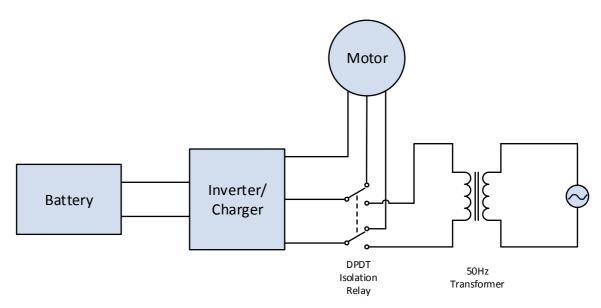

There are a number of converter topologies that match the above-mentioned criteria. In terms of the isolation requirement, the most common implementation today is a high frequency transformer (HFT) operating in a switching frequency range of the 10s of kHz to around 100 kHz depending on the converter topology. In contrast, a LFT operating in the fundamental grid frequency (50 Hz) weighs significantly more and is much larger in size. However, if the power electronics of the traction drive were also to be used for interfacing with the utility grid, there will be the added benefit of cost reduction, as the power electronic components are one of the major costs of a vehicle charger. A similar concept was introduced by S. Lacroix et al., 2010 [47] where the traction drive along with the motor windings were used to form the voltage source inverter and frontend grid filter. However, this method does not meet the requirement for galvanic isolation as the motor winding only act as a

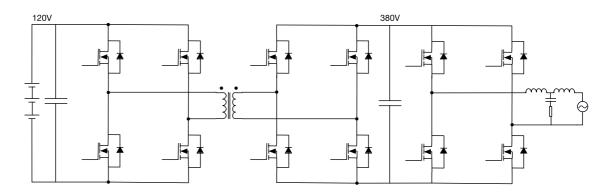

filter stage. The alternate topology that is proposed in this chapter is shown in Fig. 2-1.

Fig. 2-1 Bidirectional charger topology with shared power electronics

The 50 Hz isolation transformer is connected to the traction drive through a double-pole, double-throw (DPDT) relay, which is activated depending on charge mode or traction mode of operation. The 3<sup>rd</sup> phase connection of the motor can be left connected to the motor drive inverter since there is no return path for any current flow from the motor back to the inverter (motor is floating) as well as due to the absence of switching action in the unused leg of the H-bridge. This topology could also be extended for a three-phase charger by connecting all 3 legs of the inverter to a three-phase transformer through an appropriate isolating relay. A comparative study between the proposed topology and a resonant converter based bidirectional charger topology is presented in [48].

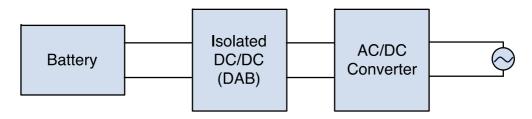

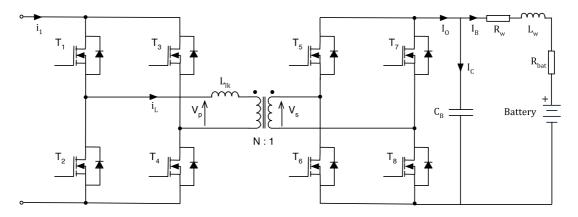

The second option is the HFT based charger and is illustrated in Fig. 2-2. In this topology, a bidirectional DC/DC converter is cascaded with a frontend AC/DC converter. This topology requires more sophisticated control as well as fully independent power electronics.

Fig. 2-2 High frequency dual active bridge based bidirectional charger

Isolated bidirectional DC/DC converters can be implemented in a variety of different topologies ranging from the simplest form which has two switching devices to the more complex topologies such as the dual active bridge and resonant converters which contain eight switching devices. The following table highlights the typical topologies of isolated bidirectional converters based on the number of switching devices [49].

Table 2-1 Isolated bidirectional converter topologies based on number of switches [49]

| Number of switches | Converter type                |

|--------------------|-------------------------------|

|                    |                               |

| <b>Dual-switch</b> | Dual-flyback [50, 51]         |

|                    | Dual-Cuk [52]                 |

| Three-switch       | Forward-flyback [53]          |

| Four-switch        | Dual-push-pull [54]           |

|                    | Push-pull-forward [55]        |

|                    | Push-pull-flyback [56]        |

|                    | Dual-half-bridge [22, 57-59]  |

| Five-switch        | Full-bridge-forward [60]      |

| Six-switch         | Half-full-bridge [61]         |

| Eight-switch       | Dual-active-bridge (DAB) [24] |

|                    | Resonant type [25-31]         |

When using the same type of switching devices, in general, the power capacity of the converter is proportional to the number of switching devices and therefore the eight switch converters have the highest power capacity [49].

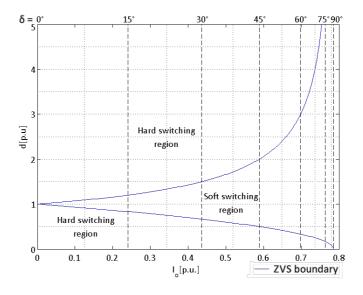

The DAB and resonant type converters have the advantages of soft switching operation as well as being symmetric and modular [49].

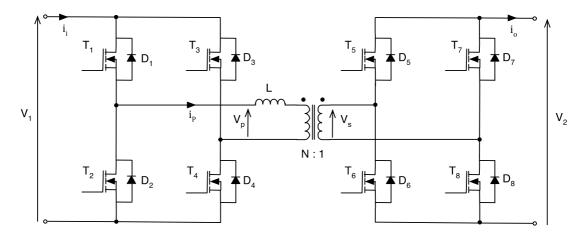

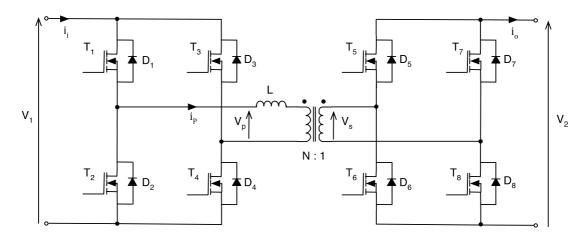

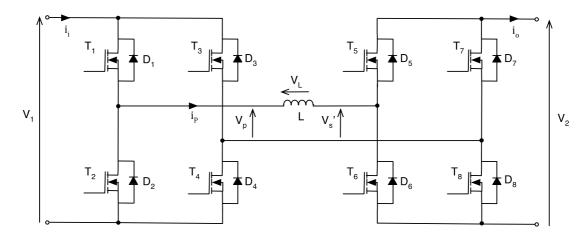

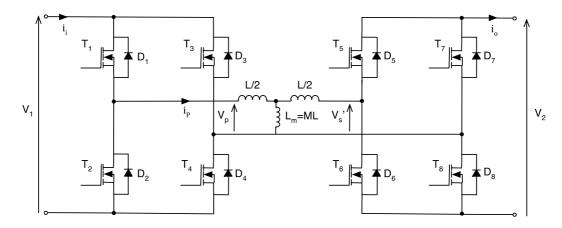

The DAB type converter consists of a transformer between two full active bridges as shown in Fig. 2-3 where the transformer's leakage inductance is depicted as 'L'. The power flow is controlled by changing the phase shift between the two bridges. The DAB converter has the advantage of simplicity in design and control as well as high efficiency [26].

Fig. 2-3 Dual active bridge converter topology

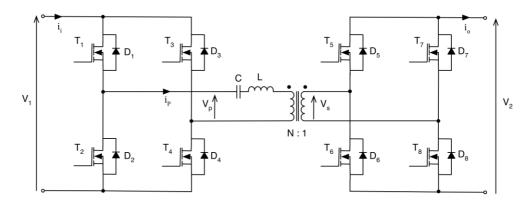

To further improve the efficiency of the DAB converter, various resonant type converters have been developed where the addition of extra capacitors and/or inductors gives a resonant characteristic. The transformer current in a resonant converter is typically a sinusoidal (or quasi-sinusoidal when operating outside the resonant frequency) waveform.

An example of a resonant type converter is the series resonant converter (SRC) [28] which is formed by adding a series capacitor to the primary side of the DAB transformer as illustrated in Fig. 2-4. The capacitor in combination with the transformer's leakage inductance forms an LC resonant network. The SRC has the advantage of zero voltage switching (ZVS) turn-on for the primary bridge under all load conditions and therefore reduced switching losses as well

as reduced electromagnetic interference (EMI), whereas the DAB converter loses ZVS capability at low power levels [28]. The disadvantage of the SRC is the added size and cost due to the additional capacitor [28] as well as the limitation of only being able to operate under buck mode [26].

Fig. 2-4 Series resonant converter topology

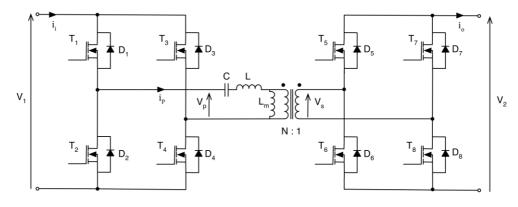

By adding an extra series inductor in addition to the series capacitor, an LLC network is formed with the magnetising inductance of the transformer as depicted in Fig. 2-5. The LLC resonant converter [30] gains some advantages over the SRC such as buck and boost mode operation as well as increased efficiency due to zero current switching (ZCS) turn-off for the secondary bridge, although the reverse mode operation has the limitation of still operating as a series resonant type converter (SRC) due to the asymmetric topology.

Fig. 2-5 LLC resonant converter topology

The addition of an auxiliary inductor to the LLC converter has been shown to achieve a symmetric operation for charge and discharge modes in [26]. Other types of symmetric bidirectional resonant converters include the CLLC converter [25, 27, 31] as well as the CLLLC converter presented in [29] where soft switching for all devices is achieved. However, the addition of the extra L and C components increases the complexity as well as the cost of the system.

Due to P-MOB project [45] requirements, a dual active bridge (DAB) based DC/DC converter was chosen for the high frequency transformer based bidirectional charger. The qualitative trade-offs of the two options are summarised in Table 2-2. However, a more quantitative comparison of the two candidate topologies in terms of performance and cost is essential.

Table 2-2 Comparison of charger options

|               | Option 1 LF transformer & motor inverter                                                                                                                                                                                                                                                                                   | Option 2 HF transformer & DAB                                                                                                                                                                                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advantages    | <ul> <li>No extra switching devices required (uses motor drive)</li> <li>Less complex as only the frontend controller is required</li> <li>Higher reliability due to the absence of extra power electronics</li> <li>Lower cost due to the reuse of power electronic components between charger and motor drive</li> </ul> | <ul> <li>Lighter due to the high frequency transformer</li> <li>Smaller size as a result of the high frequency transformer</li> </ul>                                                                                                                                      |

| Disadvantages | <ul> <li>Heavy due to the low<br/>frequency transformer</li> <li>Larger size due to the low<br/>frequency transformer</li> </ul>                                                                                                                                                                                           | <ul> <li>12 extra switching devices required</li> <li>More complex due to the extra switching and control requirements</li> <li>Lower reliability due to the added DC/DC converter and extra components</li> <li>Higher cost due to the added active components</li> </ul> |

# 2.1.1. Option 1 – Low frequency transformer based charger

The schematic of the LFT based option is shown in Fig. 2-6. Since the charger is single phase, 4 out of the 6 switching devices in the traction drive is utilised. This forms an H-bridge that is connected (through the DPDT relay) to the isolation transformer. The leakage inductance of the transformer forms part of the LCL filter for the grid side. The H-bridge switches are controlled with unipolar sinusoidal modulated PWM signals generated from the traction motor inverter controller. On the DC side, the battery can be directly connected to the DC link of the inverter. This configuration causes the battery charge current to be composed of a DC component and an AC ripple component at twice the grid frequency (100 Hz) due to the single-phase sinusoidal power flow from the grid. Methods to reduce the 100 Hz ripple have been proposed such as resonant filtering [62] and active filtering. However, these methods require additional complexity and weight in the form of inductors. Furthermore, the negative effect of low frequency ripple on Lithium polymer and Lithium Iron Phosphate batteries have been analysed in [63] and [64] respectively and have been concluded that the effect is minimal. On the other hand, pulsed charging and sinusoidal charging of Lithium-Ion batteries have been shown to improve charge time and reduce heating of the battery and therefore increase battery life in [65, 66] and [67]. The reason for the reduced heating compared with the constant current/constant voltage (CC-CV) method is due to electrochemical impedance dependence on frequency and therefore the lower impedance of the battery at higher frequencies. Actual effect on battery life may depend on the exact chemistry used for the application.

The specification for the battery and converter was based on the requirements of the personal mobility (P-MOB) project [45] that was carried out. The specification of the battery and charger system for the small electric vehicle intended for urban transportation is shown in Table 2-3. A transformer ratio of 4 is selected so as to be able to operate over the battery and grid voltage ranges. Although the device switching frequency can be optimised for charger

efficiency and frontend filter weight, in order to reduce the complexity of the design optimisation, a switching frequency of 10 kHz is assumed considering the CPU time requirements for application in a low cost digital signal processor (DSP) platform (TI TMSF28335).

Table 2-3 Battery and converter specifications

| Battery cell               | EiG ePLB C (Li[NiCoMn]O2)                 |

|----------------------------|-------------------------------------------|

|                            | Cell voltage range: 3 V to 4.15 V (20 Ah) |

| Battery Configuration      | 32 series, 4 parallel (32S4P) – 80 Ah     |

| Battery voltage range      | 96 V to 133 V (120 V nominal)             |

| Grid voltage range         | 230 V +10%/-6% (50 Hz)                    |

| Nominal power              | 2.2 kW (4.5 hour charge time)             |

| Nominal grid current (rms) | 9.56 A                                    |

| Maximum battery current    | 23 A                                      |

| Transformer turn ratio     | 4                                         |

| Device switching frequency | 10 kHz                                    |

Fig. 2-6 LFT based bidirectional charger

# 2.1.2. Option 2 – High frequency transformer based charger

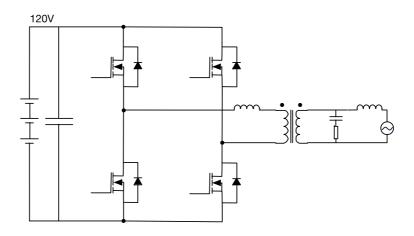

The DAB converter was first proposed by R. W. A. De Doncker et al., 1991 [24]. Fig. 2-7 illustrates the schematic of the DAB based bidirectional charger. 12 power switches are required of which 4 form the frontend and the remaining 8 form the DC/DC converter. The nominal battery voltage is 120 V and the intermediate DC link voltage is 380 V. The HFT provides the isolation as well as the inductance required for power flow by way of the leakage inductance. The grid side filter is chosen to be an LCL filter as it provides high ripple attenuation.

Fig. 2-7 DAB based bidirectional charger

# 2.2. Low frequency transformer based bidirectional charger

## **2.2.1.** Frontend analysis and design

## **2.2.1.1.** Frontend filter design considerations

# *General background of harmonic filtering for grid connection*

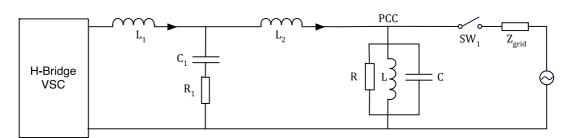

The frontend of an AC/DC grid converter requires a harmonic filter between the voltage source converter (VSC) and the grid to attenuate switching frequency harmonics. The commonly used filter topologies for this purpose are 2<sup>nd</sup> order LC filters and 3<sup>rd</sup> order LCL filters. Other topologies that have been proposed in the past for harmonic filtering include LLCL filters [68] and RLC trap filters [69].

Although a 2<sup>nd</sup> order LC filter can be used for the system being designed, an LCL filter is the practical solution in terms of size and cost in order to meet the IEEE519-1992 and IEEE929-2000 standards [70], [44] which require that grid harmonic orders higher than the 35<sup>th</sup> should be less than 0.3% of the maximum load current. This is due to the increased attenuation provided by the LCL topology relative to an LC topology with same reactance values. The 50 Hz isolation transformer can be designed to have the required leakage inductance for the converter side and an extra grid side inductor can be designed for forming the LCL filter.

The use of a low frequency transformer with integrated reactive components that form the harmonic filtering action have been proposed in the past. In particular, J. Pleite et al. [71] have proposed the integration of the series inductance of the transformer to form an LC harmonic filter. However, the LC filters have lower attenuation compared with LCL filters, the required leakage inductance is large. V. Valdivia et al. [72] have proposed the integration of both inductors of an LCL filter configuration into the leakage inductance of the transformer and this concept [73] has been extended to the design of three phase transformers. This requires a complex magnetic design but the weight, size and cost advantage compared to a standard transformer with an extra inductor has not been proven.

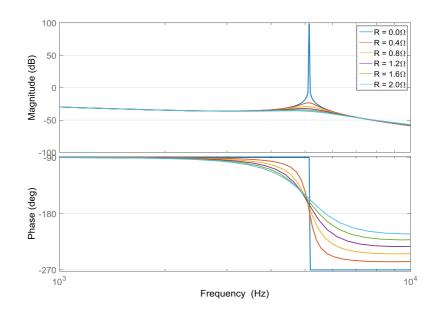

LCL filters for harmonic attenuation have been investigated in literature in the past regarding the choice of components [74], active damping methods [75], [76], [77], optimisation of damping resistor value [78] and overall design procedure [79].

Active damping of LCL filters provide the benefit of increased efficiency due to the absence of the damping resistor which dissipates power. Commonly used active damping methods include the virtual resistor based method [80]

and notch filter based method [81]. The virtual resistor based method emulates the behaviour of a damping resistor though the control of the PWM inverter. However, the method requires additional voltage or current sensors in order to obtain the states of the capacitor and inductors. The notch filter based active damping method consists of adding a notch filter tuned at the resonant frequency of the LCL filter on to the current control loop. Although the notch filter based method eliminates the need for extra voltage or current sensors, it has the disadvantage of stability issues under varying grid impedances as well as complexity in controller design. The selection of active or passive method of damping must be considered based on the increased complexity and cost versus the loss in efficiency. For the purposes of the charger comparison, passive damping is selected and the damping resistance value is optimised in order to provide minimal loss in converter efficiency.

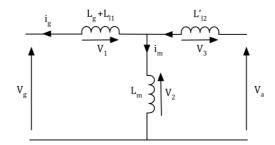

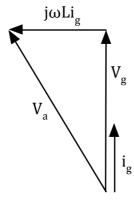

# Design constraints of LCL filter

When designing the filter, there are a number of constraints to the selection of components, the first being the maximum allowable series inductance to the grid which, if exceeded, the converter is no longer able to transfer the required amount of power to/from the grid. The maximum allowable inductance depends on the DC link voltage range, normal operating grid voltage range, the maximum grid current, the dead time in the converter as well as the magnetising inductance of the transformer which acts as a shunt. The transformer equivalent circuit with reference to the frontend is presented in Fig. 2-8 where the leakage inductance of the secondary is referred to the primary side and is denoted by  $L_{12}$  and can be defined by equation (2-1).  $L_{11}$ ,  $L_m$  and  $L_g$  denote the primary leakage inductance, magnetising inductance and grid side LCL inductance respectively (the HF current path through the LCL capacitor is neglected). The peak magnitude of the transformer secondary voltage,  $V_a$ , referred to the primary side can be obtained by equation (2-2) where  $P_{max}$  is the maximum power transferred to the grid (2.2 kW) and  $\omega_0$  is the

angular frequency of the grid voltage. Since the voltage drop in the grid side inductor is negligible, the transformer primary voltage,  $V_g$ , is equal to the grid voltage. For an H-bridge converter, the AC voltage, i.e., the transformer secondary voltage, reaches its maximum, which is equal to the DC link voltage when the modulation index is 1.0. Thus, if a dead time of 2% is considered for the converter, the minimum DC link voltage required is given by equation (2-3), where N is the transformer's winding ratio and is equal to 4.

Fig. 2-8 Simplified transformer equivalent circuit

$$L'_{l2} = \left(\frac{N_1}{N_2}\right)^2 L_{l2} = \left(\frac{N_1}{N_2}\right)^2 L_{l1} \left(\frac{N_2}{N_1}\right)^2 = L_{l1}$$

(2-1)

$$|V_{a\_pk}| = \sqrt{2} \left| \frac{V_g^2(L_m + L_{l1}) + j\omega P_{max} \left( L_g(L_m + L_{l1}) + L_{l1}(2L_m + L_{l1}) \right)}{L_m V_g} \right|$$

(2-2)

$$V_{dc\_min} = \frac{\left| V_{a\_pk} \right|}{0.98N} \tag{2-3}$$

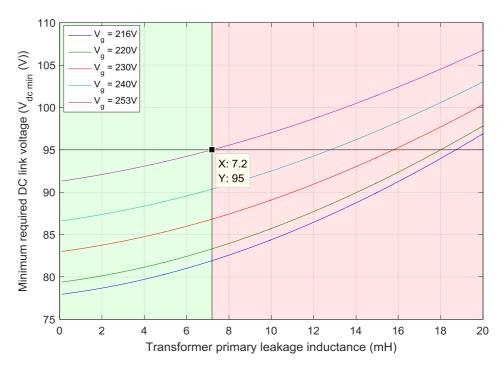

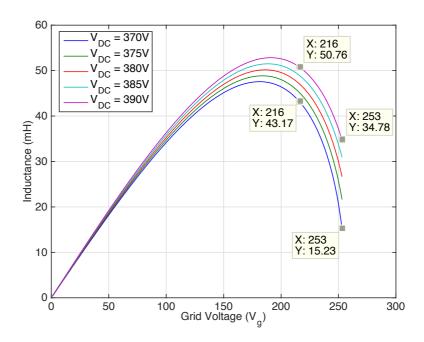

It is therefore possible to plot  $V_{dc\_min}$  as a function of the primary leakage inductance and is illustrated in Fig. 2-9 for different values of  $V_g$  of 230 V +10%, -6% (according to UK legislation [87]) assuming a transformer magnetising inductance of 250 mH. Since the minimum DC link voltage is equal to the minimum battery voltage (when a separate buck-boost bidirectional converter is not used), the maximum primary leakage inductance to the grid is defined as

$L_{11\_max}$  when  $V_{dc}$  = 95 V. Fig. 2-9 shows the minimum required DC link voltage as a function of transformer primary leakage inductance for different grid voltage conditions. The green region in the figure depicts the conditions where full power transfer can take place under all grid voltages, whereas the red zone indicates inability to transfer full power due to the excessive voltage drop across the leakage inductance. It can therefore be observed from Fig. 2-9 that the maximum primary leakage inductance is 7.2 mH (i.e. any value higher than that would result in the inability to transfer power under certain DC link and grid voltage conditions).

Fig. 2-9 Minimum DC link voltage vs. transformer primary leakage inductance

A large value of leakage inductance is preferred as it reduces the switching current ripple that propagates through the LCL filter, therefore resulting in lower core and winding losses associated with the inductances of the LCL filter as well as lower losses in the damping resistor due to the reduced harmonic current. Furthermore, a larger leakage inductance results in a smaller sized grid side inductor. When selecting the leakage inductance of the

transformer, the transformer efficiency and weight must also be considered and it is a trade-off between them. 70% of the maximum allowable leakage inductance is chosen for the design so as to allow operation under weak grid conditions (extra series inductance in the grid) as well as the added inductance of the grid side inductor of the LCL filter. Therefore the transformer is designed with a primary leakage inductance target of 5 mH.

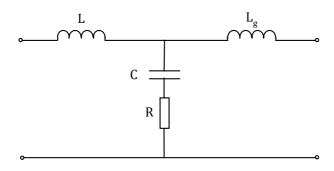

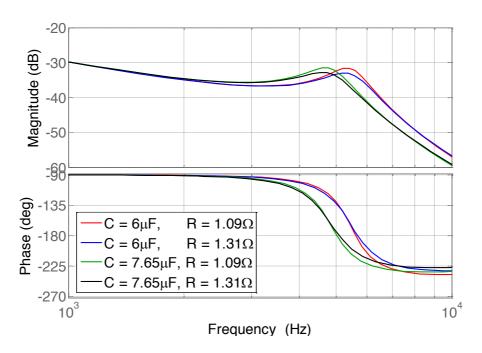

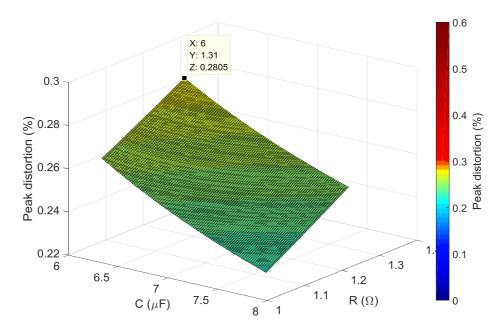

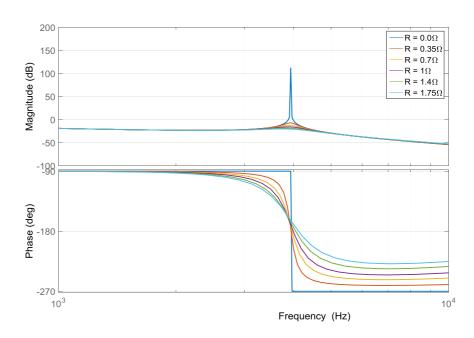

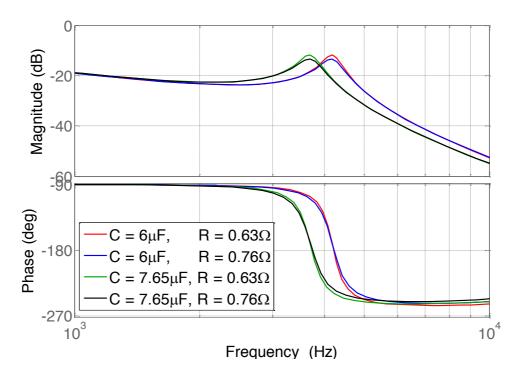

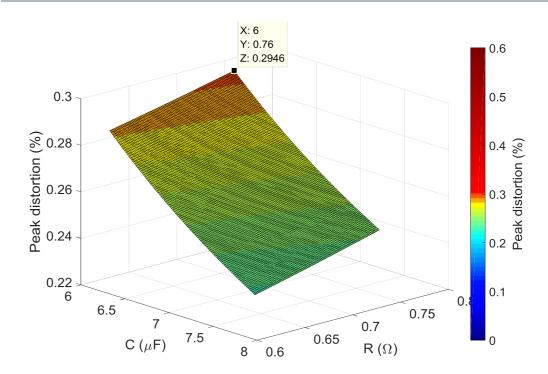

## 2.2.1.2. Optimal LCL filter design

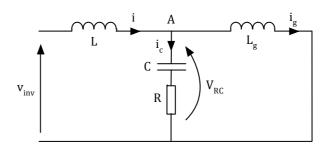

The structure of an LCL filter is illustrated in Fig. 2-10 where 'L' denotes the converter side inductance, or the equivalent transformer leakage inductance seen on the primary side; 'C' the filter capacitance; 'Lg' the grid side inductance and 'R' the damping resistance. The damping resistor is required in order to avoid filter resonance, alternatively active damping can be utilised. The design considerations vary depending on the optimisation criteria such as cost, size and weight or highest efficiency, or their combination. For the purposes of the LF converter design, size/weight and material cost are the primary design emphasis.

Fig. 2-10 Structure of LCL filter

The method proposed by Marco Liserre et al. [79] for designing an LCL filter involves first calculating the base impedance  $(Z_b)$  and capacitance  $(C_b)$  of the system as shown in equations (2-4), (2-5) where  $P_n$  is the active power

absorbed by the converter,  $E_n$  is the line-to-line rms voltage (for a 3 phase system) and  $\omega_0$  is the grid frequency.

$$Z_b = \frac{(E_n)^2}{P_n} \tag{2-4}$$

$$C_b = \frac{1}{\omega_o Z_b} \tag{2-5}$$

The converter side inductance (L) is then selected to reduce the current ripple by 10% and the filter capacitance (C) is selected to further reduce this to 2% with the condition that the maximum capacitance is less than 5% of the base capacitance,  $C_b$  so as to reduce the effect on power factor.

However in the transformer-based system, since the converter side inductance is provided by the transformer leakage inductance, it is possible to select a larger value of leakage inductance so as to reduce the ripple well below 10%. This means that the grid side inductor can be smaller and the losses in the damping resistor can be reduced. A larger value of capacitor also reduces the size of  $L_g$ . Since the weight and cost of capacitors are generally lower than inductors, a higher capacitance value is preferred. The maximum value of capacitance for the system is 6.62  $\mu$ F (5% of  $C_b$  in order to minimise the effect on power factor), however a value of 6.8  $\mu$ F can be chosen to conform to standard capacitance values.

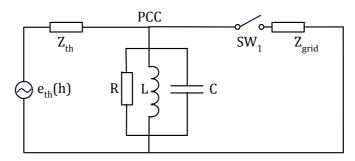

# Switching Harmonics of Grid Current Based on LCL Equivalent Circuit

In order to optimally select the remaining component values of  $L_{\rm g}$  and R to meet the harmonic current limits, the relationship between the reactance values and harmonic distortion must be established. Fig. 2-11 shows the LCL filter equivalent circuit for switching frequency harmonics. It can be observed that for the switching harmonics, the grid acts as a short circuit due to the

negligibly small impedance at high frequencies. The converter side inductance (L) is provided by the leakage inductance of the transformer.

Fig. 2-11 LCL filter equivalent circuit for switching harmonics

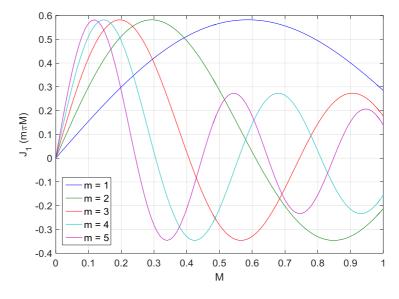

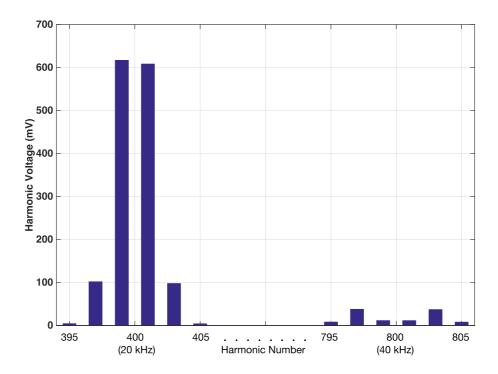

The converter output voltage considering the switching harmonic components for naturally sampled double edge carrier PWM is given by the following equation (2-6) [82], where  $J_{2n-1}$  is the Bessel functions of  $(2n-1)^{th}$  order.

$$\begin{split} V_{inv}(t) &= V_{dc} M cos(\omega_{o}t) \\ &+ \frac{4V_{dc}}{\pi} \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \frac{1}{2m} J_{2n-1}(m\pi M) \\ &* cos([m+n-1]\pi) cos(2m\omega_{sw}t + [2n-1]\omega_{o}t) \end{split}$$

The fundamental component of the voltage is represented by the first term and it is a function of the modulation index (M) and DC link voltage. The second term represents the switching frequency harmonics and its associated sidebands. It can be observed that the switching harmonics occur at frequencies given by,

$$\omega_h = (2m\omega_{sw} + [2n-1]\omega_o) \tag{2-7}$$

The relationship between m, n and harmonic number (h) is as follows,

$$h = \left(2m\left(\frac{f_{sw}}{f_o}\right) + (2n-1)\right)$$

(2-8)

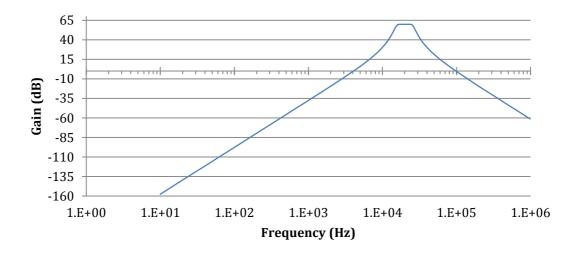

Therefore, the carrier groups appear at  $2mf_{sw}$  multiples (close to 20 kHz, 40 kHz etc.) and the sidebands at  $(2n-1)f_o$  (odd harmonics) where  $f_o$  and  $\omega_o$  is the fundamental frequency and angular frequency, respectively.  $f_{sw}$  and  $\omega_{sw}$  is the voltage source converter (VSC) switching frequency and angular frequency, respectively, m is any integer above 0 and n is any integer. The dominant harmonics appear centred around the first carrier group (20 kHz) and the sidebands reduce with increasing n. Specifically, the two dominant harmonics therefore can be found to be 19950 Hz (h = 399) and 20050 Hz (h = 401) for the 10 kHz VSC switching frequency that is used for the system under investigation. The rms value of each harmonic voltage component can therefore be calculated from equation (2-9).

$$v_{inv}(h) = \frac{1}{\sqrt{2}} \left| \frac{4V_{dc}}{\pi} * \frac{1}{2m} J_{2n-1}(m\pi M) * cos([m+n-1]\pi) \right|$$

(2-9)

Fig. 2-12 Modulation index vs. Bessel function for different carrier groups

It is clear that the value of harmonic voltage depends on the modulation index as well as the values of 'm' and 'n'. As an example, Fig. 2-12 illustrates the value of the Bessel function  $J_1(m\pi M)$  as a function of M for different values of m. Therefore the peak value of the Bessel function and the corresponding modulation index is used for each 'm' and 'n' combination when calculating the worst-case harmonic voltage.

The current through the converter side inductor can be defined as follows,

$$i_{inv}(h) = \frac{v_{inv}(h) - v_{RC}(h)}{j\omega_h L} = \frac{v_{inv}(h) - j\omega_h L_g i_g(h)}{j\omega_h L}$$

(2-10)

Furthermore, the grid side inductor harmonic current can be defined as,

$$i_g(h) = \frac{v_{inv}(h)(1 + j\omega_h RC)}{-\omega_h^2 RC(L_g + L) + j\omega_h(L_g + L) - j\omega_h^3 L_g LC}$$

(2-11)

Therefore, the converter harmonic voltage to grid switching harmonic current transfer function, g(h) can be defined as follows.

$$g(h) = \left| \frac{i_g(h)}{v_{inv}(h)} \right| = \left| \frac{(1 + j\omega_h RC)}{-\omega_h^2 RC(L_g + L) + j\omega_h (L_g + L) - j\omega_h^3 L_g LC} \right|$$

(2-12)

By substituting (2-9) into (2-12), the grid current switching harmonic rms value can be calculated for a given h. Hence the grid current distortion for each harmonic as a percentage of the total maximum load current can be calculated from equation (2-13) where  $i_L$  is the maximum rms load current.

Distortion % (h) =

$$\frac{i_g(h)}{i_L}$$

100 (2-13)

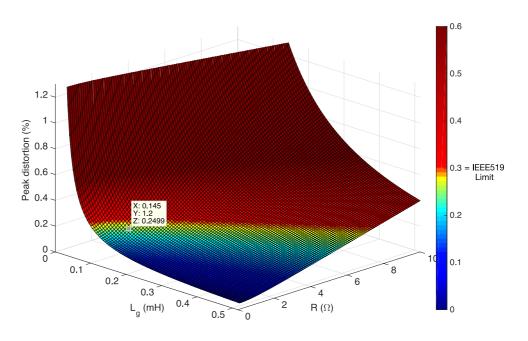

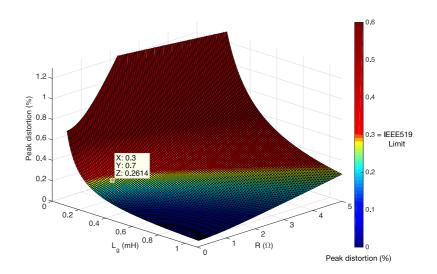

Therefore it follows that by using the above equations, the peak grid current switching harmonic distortion as a function of component values can be quantified. Since the harmonics 399 and 401 are the dominant high frequency components, the components must be chosen to inhibit the two associated harmonics to less than 0.3% of the total load current as per the IEEE519-1992 specification. As a final check, the THD is calculated and verified to be under the maximum limit of 5%.

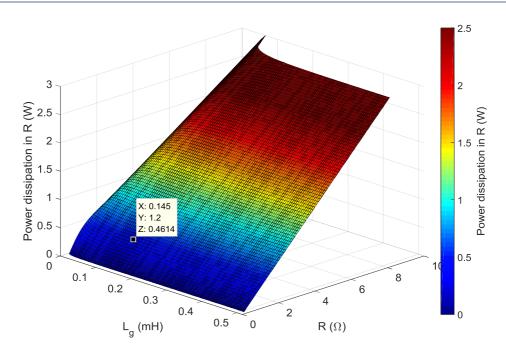

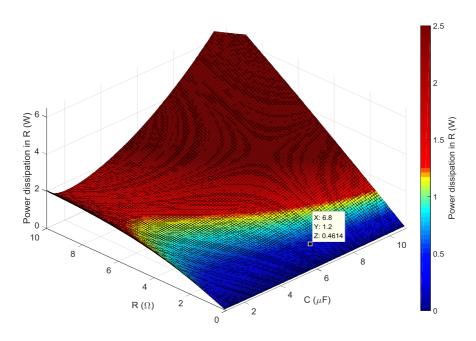

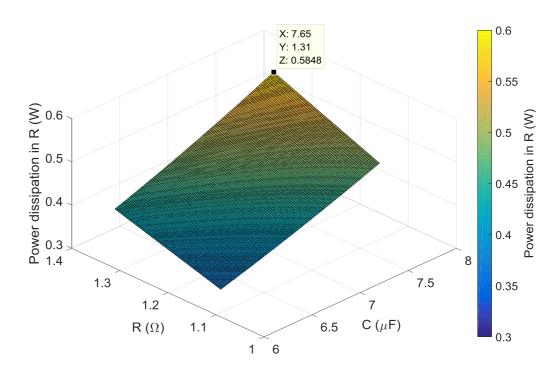

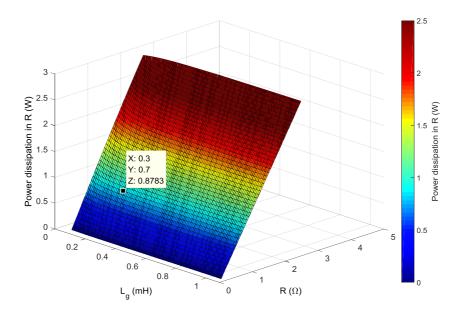

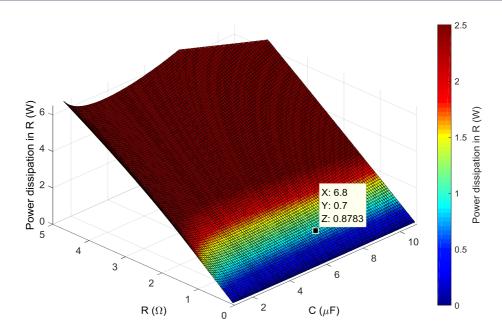

## Power dissipation in damping resistor

In order to minimise the power losses in the damping resistor, it is important to establish the causes of the power dissipation in the resistor. The losses in the resistor are proportional to the square of the total current flow through it and the resistance. For the ease of analysis, it is possible to calculate the losses due to the switching harmonics and the fundamental frequency component separately and sum them. Therefore the losses due to the main switching harmonics in the resistor,  $P_{R\_h}$  is given by equation (2-14) where  $i_{inv}(h)$  and  $i_g(h)$  are given in equations (2-10) and (2-11) respectively.

$$P_{R_{-}h} = \sum_{h=x}^{y} |i_{inv}(h) - i_g(h)|^2 R$$

(2-14)

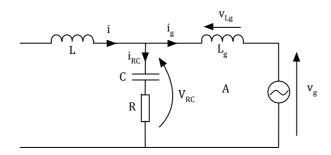

The losses due to the fundamental frequency component occur as part of the grid voltage is seen across the resistor and capacitor. By summing the voltages in loop 'A' of Fig. 2-13, the fundamental frequency component of the capacitor current can be written as shown in equation (2-15) (where  $I_g$  is the fundamental rms grid current given by  $P/V_g$ ).

Fig. 2-13 Losses due to the fundamental component of capacitor current

$$i_{RC\_50Hz} = \frac{\left(j\omega_o L_g I_g + V_g\right)j\omega_o C}{(1 + j\omega_o RC)}$$

(2-15)

The power dissipation due to the fundamental voltage,

$$P_{R_{-}50Hz} = \left| i_{RC_{-}50Hz} \right|^2 R \tag{2-16}$$

Therefore total power loss in resistor,

$$P_{R \ total} = P_{R \ 50Hz} + P_{R \ h}$$

(2-17)

#### 2.2.1.3. Transformer design

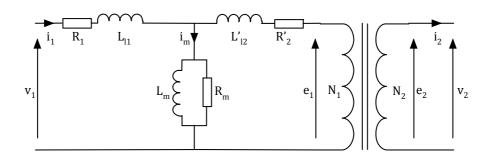

### Transformer equivalent circuit

For the purposes of circuit analysis and magnetic design, the equivalent circuit for the transformer is presented in Fig. 2-14. The equivalent circuit is made up of an ideal transformer combined with reactance components that models the electromagnetic attributes. The magnetising inductance  $L_m$  is in parallel with  $R_m$  that models the core losses. The winding resistances of the primary and secondary are  $R_1$  and  $R_2$  respectively. The secondary leakage inductance and winding resistance is referred to the primary side and are

denoted by  $L'_{l2}$  and  $R'_2$  respectively and can be defined as shown in equations (2-18).

Fig. 2-14 Transformer equivalent circuit

$$L'_{l2} = \left(\frac{N_1}{N_2}\right)^2 L_{l2}$$

|  $R'_2 = \left(\frac{N_1}{N_2}\right)^2 R_2$  (2-18)

The total leakage inductance can be defined by equation (2-19).

$$L_{l_{-}t} = L_{l1} + L'_{l2} (2-19)$$

## Selection of core material

The design criteria for the 50 Hz isolation transformer are weight, size and material cost optimisation. The first step in the design process is to select the material for the core of the transformer. There are two main varieties of magnetic core materials, which are alloy-based materials and ferrite-based materials. Alloy based materials have high conductivity compared with ferrite materials and therefore incur both hysteresis and eddy current losses. The advantage of alloy materials is the high saturation flux density and therefore smaller core size for a given flux density in comparison to ferrites [83].

The alloy-based materials are further subdivided into two main types of core, which are iron alloy materials and powdered iron. The iron alloy materials

are laminated into thin sheets and insulated from each other to reduce electrical conductivity. However, due to the relatively high conductivity, iron alloy cores cannot operate at high frequencies due to eddy current loss. In contrast, powdered iron cores have iron particles suspended in a material that electrically isolates them and therefore the conductivity is significantly less than that of iron alloy laminated cores. Therefore the powdered iron cores can operate at higher frequencies without significant eddy current losses. Ferrite materials on the other hand, have negligibly small conductivity and therefore only exhibit hysteresis losses and as a result are widely used for high frequency applications. However, ferrite materials generally have a low saturation flux density and therefore larger core sizes for a given flux density [83].

The following Table 2-4 presents a quantitative comparison of commonly available magnetic materials [84].

Table 2-4 Properties of commonly available magnetic materials [84]

| Material                      | Max. Flux<br>Density (T) | Resistivity<br>(Ωcm) | Operating<br>Frequencies |

|-------------------------------|--------------------------|----------------------|--------------------------|

| Fe                            | 2.2                      | 1x10 <sup>-5</sup>   | 50Hz - 1kHz              |

| Si-Fe (unoriented)            | 2                        | 5x10 <sup>-5</sup>   | 50Hz - 1kHz              |

| Si-Fe (oriented)              | 2                        | 5x10 <sup>-5</sup>   | 50Hz - 1kHz              |

| 50-50 Ni Fe (grain- oriented) | 1.5                      | 4x10 <sup>-5</sup>   | 50Hz - 1kHz              |

| Kool Mu powder                | 1                        | -                    | <10MHz                   |

| Iron powder                   | 1                        | 1x10 <sup>4</sup>    | 100kHz -<br>100MHz       |

| Ferrite (Mn-Zn)               | 0.3-0.5                  | 10-100               | 10kHz - 2MHz             |

| Ferrite (Ni-Zn)               | 0.3-0.5                  | 1x10 <sup>6</sup>    | 200kHz -<br>100MHz       |

It can be seen that the material of choice for low frequency applications is laminated steel materials due to the high saturation flux density ( $B_{max}$ ) which

allows for a smaller transformer size. Furthermore, grain oriented steel materials offers higher permeability and lower losses when the magnetic flux is in the direction of the orientation. Since eddy current losses increase at higher frequencies, materials that have higher resistivity (powder based and ferrite) is preferred for high frequency applications.

The core of the transformer is composed of two 'E' shaped core halves. The main material cost of the transformer in a production quantity is incurred from the copper cost for the windings and magnetic steel material cost for the core. Since the transformer operates at a frequency of 50 Hz, grain oriented Si-Fe (35M6) material is chosen as it offers a high saturation flux density (2 T) as well as reduced core losses as a result of the grain orientation.

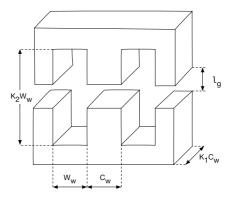

### **Transformer Design**

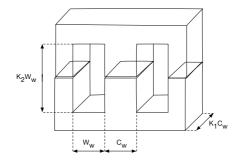

For optimisation of the transformer size, weight and efficiency, the design equations for the physical and magnetic properties are analysed after which an iterative process is used to determine the optimal number of turns for the transformer. The physical structure of the transformer core is illustrated in Fig. 2-15.  $C_w$  and  $W_w$  denote the core width and window width while the aspect ratios of the window and core are denoted by  $K_1$  and  $K_2$ .

Fig. 2-15 Transformer core dimensions

The core area ( $A_{core}$ ) is defined by equation (2-20) where  $I_{pk\_1}$  is the peak primary current,  $V_{rms\_1}$  the primary rms voltage and f the fundamental frequency. Therefore the required core width can be defined as shown in (2-21).

$$A_{core} = \frac{L_m I_{pk\_1}}{B_{max} N_1} = \frac{V_{rms\_1}}{4.44 f N_1 B_{max}} = K_1 C_w^2$$

(2-20)

$$C_{w} = \sqrt{\frac{V_{rms\_1}}{4.44f N_{1} K_{1} B_{max}}}$$

(2-21)

Similarly, the required window width can be defined by the following equation (2-22) where  $K_{cu}$  is the copper filling factor,  $W_{w1}$  the winding thickness and J is the maximum permissible current density.

$$A_w = K_2 W_{w1}^2 = \frac{I_{rms\_1} N_1 + I_{rms\_2} N_2}{K_{cu} J} = \frac{2I_{rms\_1} N_1}{K_{cu} J}$$

(2-22)

In order to estimate the weight of copper and the resistance of each winding, the average length of wire in the bobbin must be defined as follows where  $h_b$  is the thickness of the bobbin and  $P_f$  is the packing factor.

$$l_{av} = 2(C_w + 2h_b)(1 + K_1/P_f) + \pi W_{w1}$$

(2-23)

The weight of the copper can be defined as (2-24) where  $A_{c\_1}$  is the cross sectional area of the primary conductor as given in (2-25) and  $d_{cu}$  is the density of copper.

$$W_{cu} = 2d_{cu}NA_{c} l_{av} (2-24)$$

$$A_{c_{-1}} = \frac{I_{rms_{-1}}}{I} \tag{2-25}$$

The resistance of the two windings can be defined as given in equation (2-26) where  $\rho_{cu}$  is the resistivity of copper.

$$R_{1} = \frac{\rho_{cu}Nl_{av}}{A_{cp}}$$

|  $R_{2} = \frac{R_{1}}{\left(\frac{N_{1}}{N_{2}}\right)^{2}}$  (2-26)

To calculate the weight of the iron core, the volume of the core has to be derived by considering the geometrics, and multiplied by the density of iron  $(d_{iron})$  and is defined as (2-27). Therefore the total weight of the transformer can be defined as (2-28).

$$W_{iron} = d_{iron} K_1 C_w^2 \left[ (2K_2 + 1)W_w + C_w (1 + \pi/4) \right]$$

(2-27)

$$W_t = W_{cu} + W_{iron} (2-28)$$

The next step is to calculate the magnetising inductance and this requires the definition of the average length of the magnetic path ( $l_{fe}$ ) inside the core by considering the geometrics and is given in equation (2-29). The magnetising inductance is therefore defined as (2-30).

$$l_{fe} = 2(K_2 + 1)W_w + \frac{\pi C_w}{2}$$

(2-29)

$$L_m = \mu_0 \mu_r \frac{K_1 C_w^2 N_1^2}{l_{fe}}$$

(2-30)

For the calculation of efficiency, the power dissipated in the copper due to resistive losses and the power dissipated in the core due to hysteresis and eddy current losses must be established as given in equations (2-31) and (2-32) where  $l_d$  is the specific loss for the material at 50 Hz (W/kg).

$$P_{cu} = 2R_1 I_{rms\ 1}^2 \tag{2-31}$$

$$P_{iron} = l_d W_{iron} (2-32)$$

Therefore, the efficiency of the transformer is defined as follows.

$$\eta = \frac{P_{out}}{(P_{out} + P_{cu} + P_{iron})} * 100$$

(2-33)

The final step is the definition of the leakage inductance. The leakage inductance depends on the orientation of the primary and secondary windings. If the windings are wound on top of each other (overlapping), L<sub>l1</sub> is given as in equation (2-34), however if the windings are made separately (top-bottom arrangement), L<sub>l1</sub> is given as shown in (2-35).

$$L_{l1\_overlapping} = \frac{1}{3}\mu_0 N^2 \frac{1}{K_2} l_{av}$$

(2-34)

$$L_{l1\_top\_botton} = \frac{1}{3} \mu_0 N^2 \frac{K_2}{1} l_{av}$$

(2-35)

It can be observed that for K<sub>2</sub>>1, which is the standard configuration, a top bottom winding gives a larger value of leakage inductance. Therefore for the purposes of integrating the converter side inductance into the transformer, it is beneficial to utilise the top-bottom arrangement.

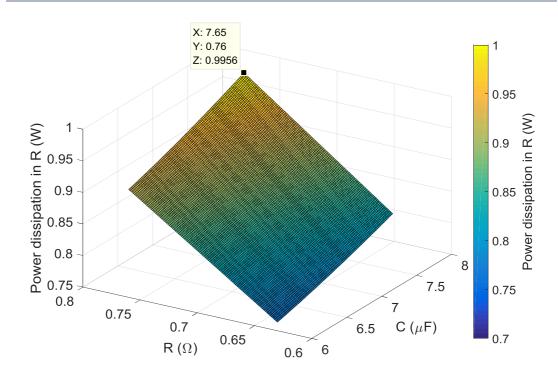

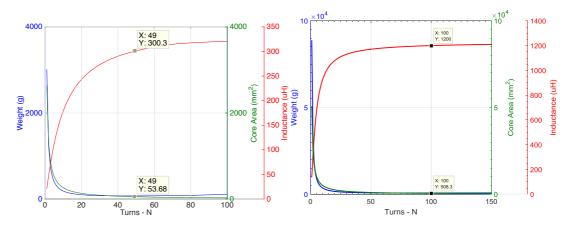

The procedure for designing the transformer consists of calculating the minimum required winding width for a given number of turns (N1) by considering the maximum permissible current density for the associated

winding width according to Table 2-5 and equation (2-22) considering a common set of design parameters as given in Table 2-6. The required core width in order to be below the maximum permitted flux density is calculated from equation (2-21). Thereafter, the associated leakage inductance, total weight and efficiency are also calculated. This process is done for a range of N1 values (100 turns to 240 turns).

Table 2-5 Winding width vs. maximum allowable current density

| J (A/mm²) | 7.00 | 4.85 | 3.5 | 2.55 | 2.00 | 1.85 |

|-----------|------|------|-----|------|------|------|

| Ww1 (mm)  | 10   | 20   | 30  | 40   | 50   | 60   |

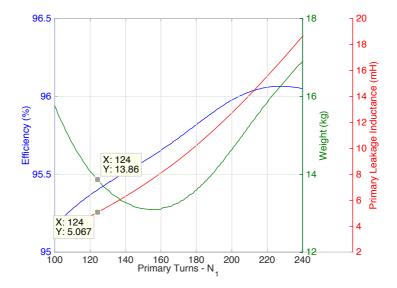

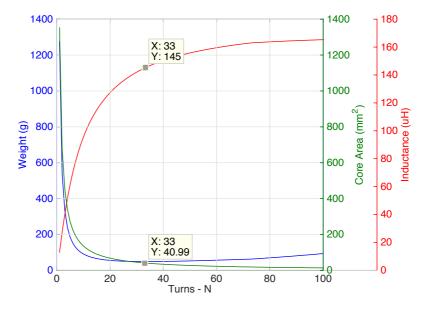

The calculated values of leakage inductance, weight and efficiency as a function of N1 are plotted in Fig. 2-16 based on equations (2-28), (2-33) and (2-35) where the common set of parameters that were used are presented in Table 2-6.

Table 2-6 Transformer design parameters

| Parameter                                 | Symbol           | Value          |

|-------------------------------------------|------------------|----------------|

| Primary voltage                           | $V_{rms\_1}$     | 230 V (50 Hz)  |

| Secondary voltage                         | $V_{rms\_2}$     | 57.5 V (50 Hz) |

| Output power                              | Pout             | 2200 W         |

| Power factor                              | PF               | 0.9            |

| Maximum permissible flux density          | $B_{max}$        | 1.5 T          |

| Specific iron loss at 50 Hz               | $L_{d}$          | 3 W/kg         |

| Aspect ratio of core                      | $K_1$            | 1              |

| Aspect ratio of coil window               | K <sub>2</sub>   | 2              |

| Thickness of bobbin                       | $h_b$            | 1 mm           |

| Copper filling factor                     | $K_{cu}$         | 0.5            |

| Packing factor                            | $P_{\mathrm{f}}$ | 0.96           |

| Relative permeability at B <sub>max</sub> | μr               | 500            |

Fig. 2-16 Leakage inductance, weight and efficiency vs. number of primary turns for top-bottom winding arrangement

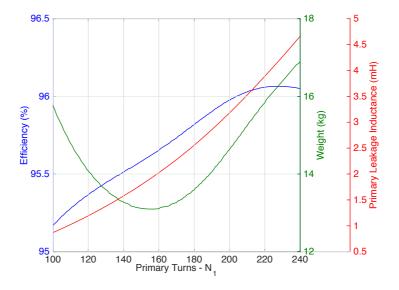

Fig. 2-17 Leakage inductance, weight and efficiency vs. number of primary turns for overlapping winding arrangement

The number of turns must be selected considering the compromise between leakage inductance, weight and efficiency. In section 2.2.1.1 it was determined that the maximum primary side leakage inductance should be under 7.2 mH and therefore, 70% of the maximum (5 mH) was chosen as a

transformer design specification to allow for operation under weak grid conditions.

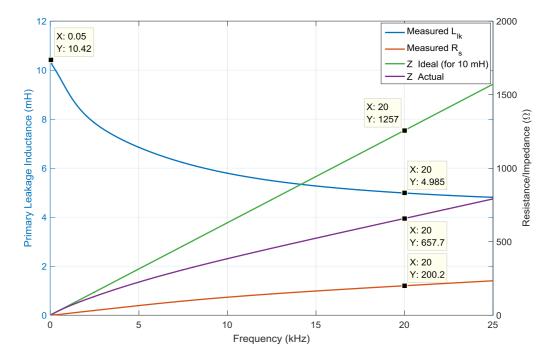

It can be seen from Fig. 2-16 and Fig. 2-17 that the top-bottom winding arrangement gives a leakage inductance value closer to the required 5 mH while minimising weight whereas the overlapping arrangement provides a much smaller value. Therefore, a value of 124 turns is selected for  $N_1$  with a top-bottom arrangement and this yields a primary leakage inductance of 5 mH (for a total primary referred leakage inductance of 10 mH) as per the design target specified in 2.2.1.1 and a total transformer weight of 13.86 kg. The final parameters of the designed transformer are presented in Table 2-7.

Table 2-7 Final transformer design parameters

| Parameter                            | Symbol                         | Value                  |

|--------------------------------------|--------------------------------|------------------------|

| Primary/secondary turns              | N <sub>1</sub> /N <sub>2</sub> | 124/31                 |

| Output power                         | $P_{out}$                      | 2200W                  |

| Turns ratio                          | N                              | 4                      |

| Core material                        | -                              | 35M6 / EE core         |

| Primary/secondary winding diameter   | $A_{cp1}$ / $A_{cp2}$          | 1.85 mm / 3.7 mm       |

| Core width x core length             | $C_w \mathrel{X} K_1 C_w$      | 74.9 mm x 74.9 mm      |

| Window width x window length         | $W_w  x  K_2 W_w$              | 27 mm / 54 mm          |

| Primary/secondary leakage inductance | $L_{l1}/L_{l2}$                | 5 mH / 312.5 μH        |

| Primary side magnetising inductance  | $L_{m}$                        | 190 mH                 |

| Current density                      | J                              | 1.97 A/mm <sup>2</sup> |

| Total weight                         | $W_{t}$                        | 13.86 kg               |

| Efficiency                           | η                              | 95.4%                  |

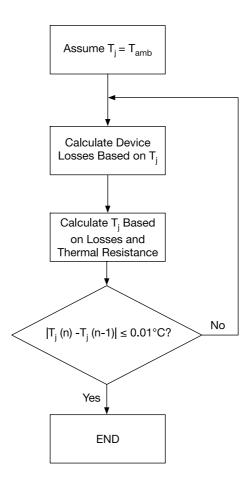

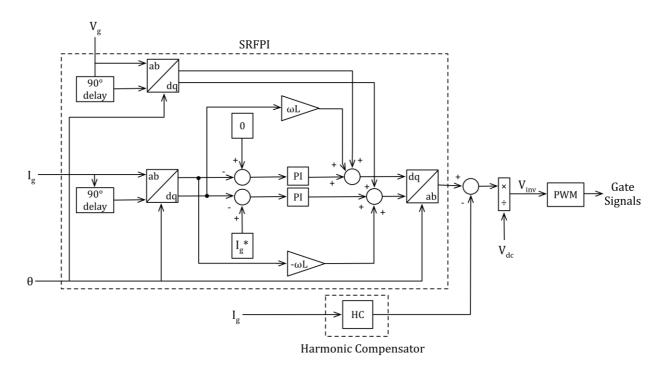

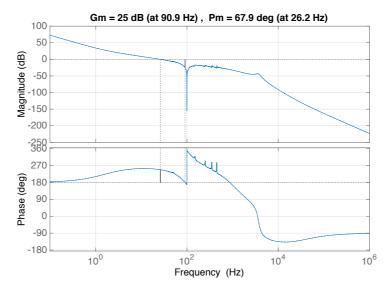

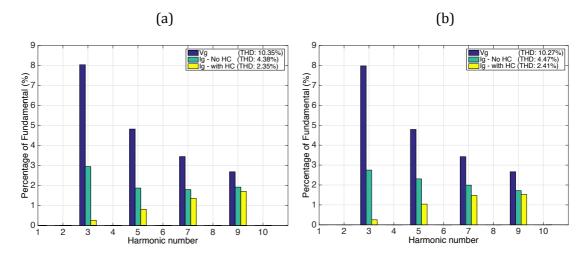

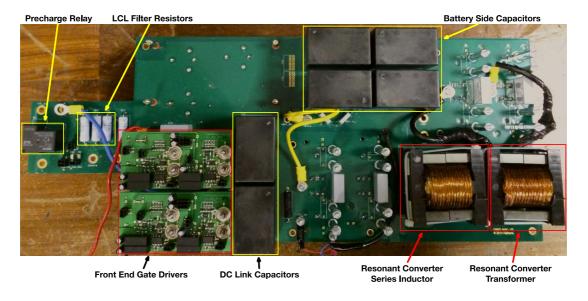

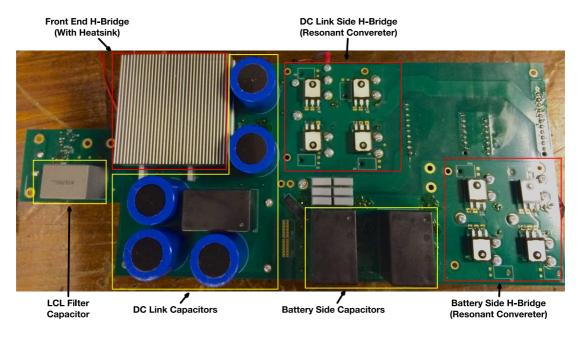

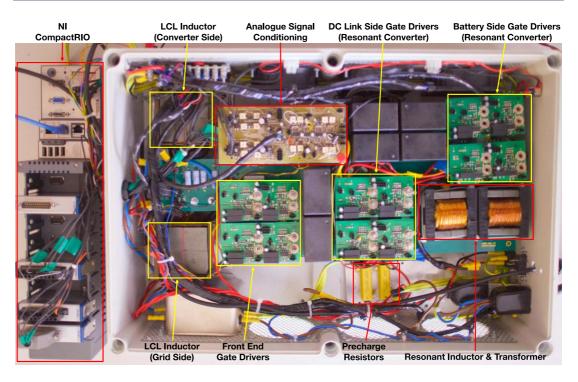

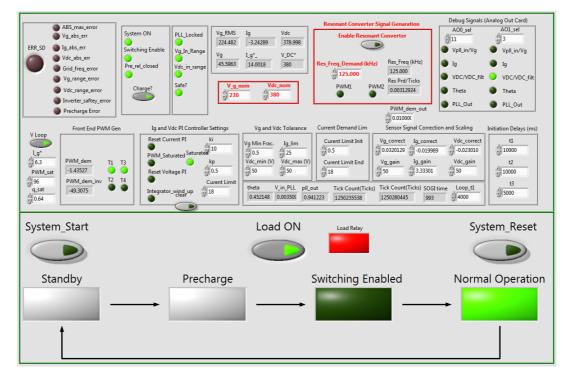

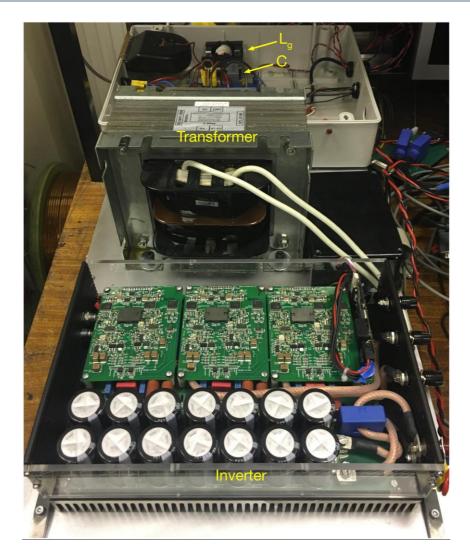

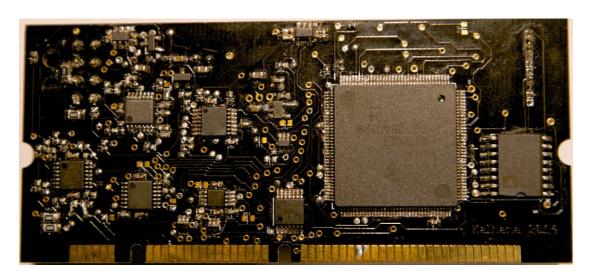

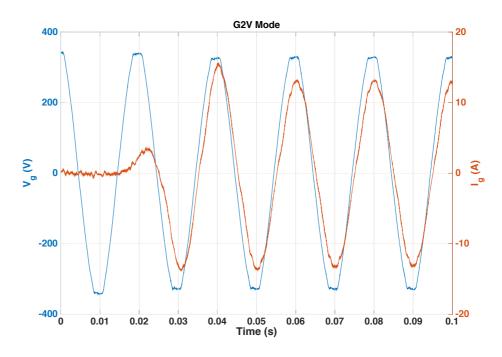

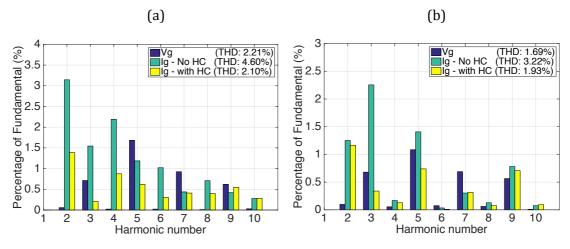

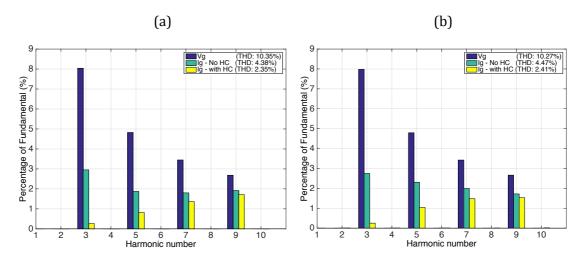

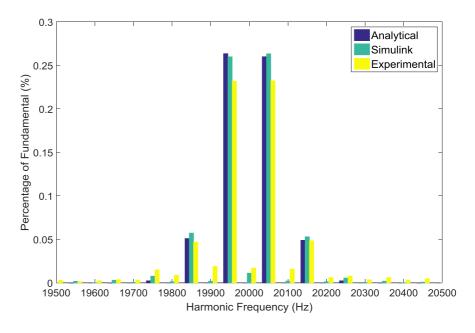

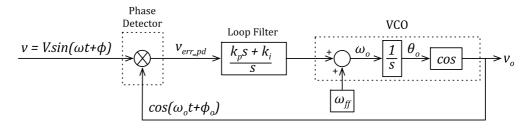

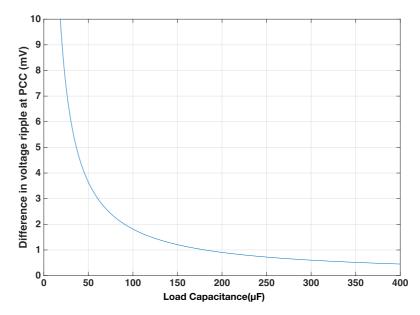

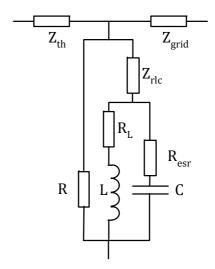

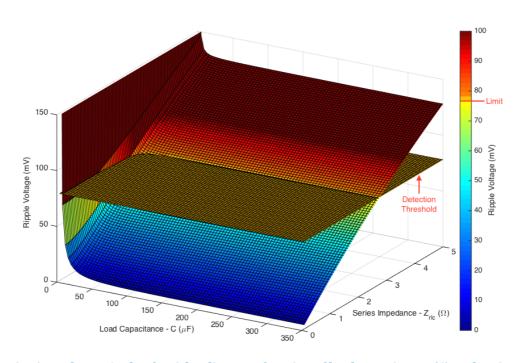

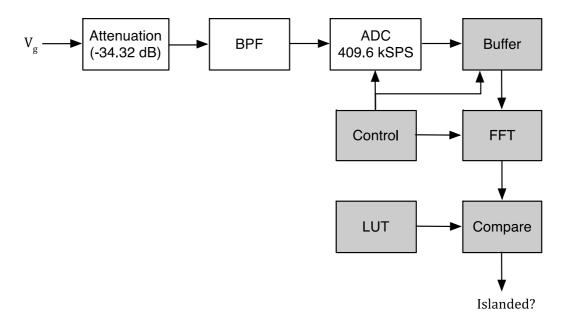

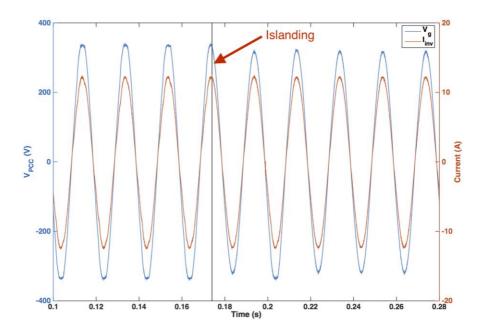

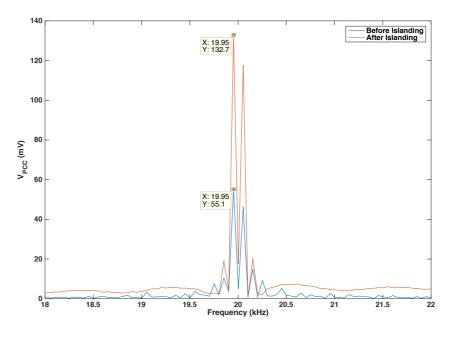

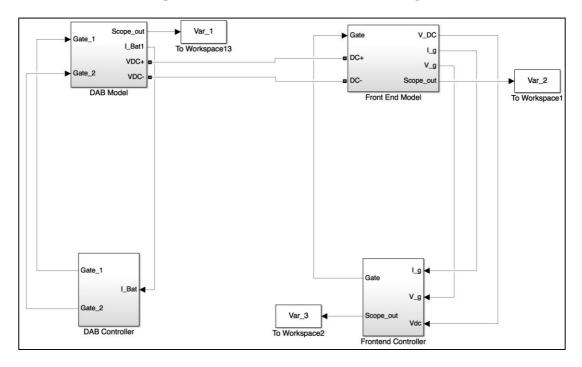

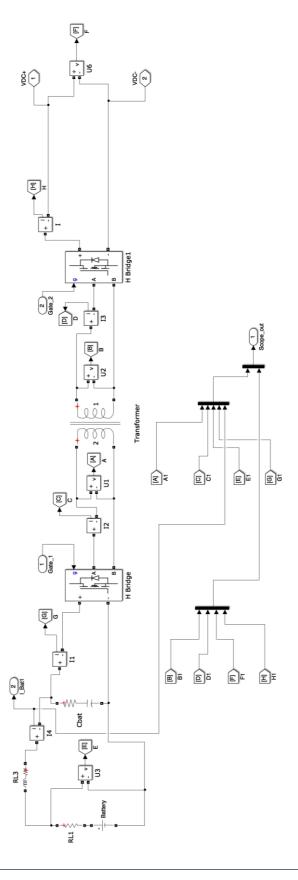

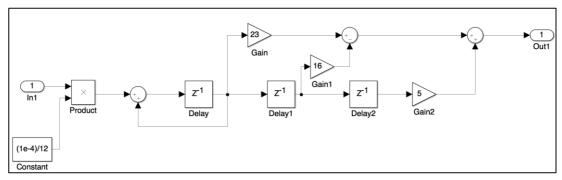

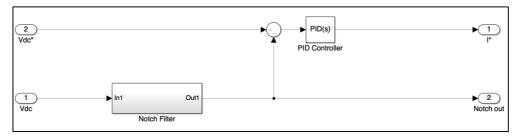

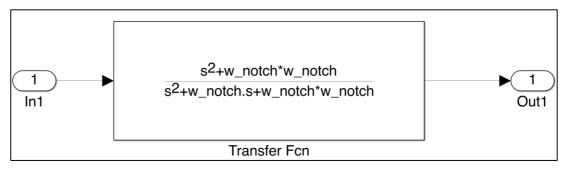

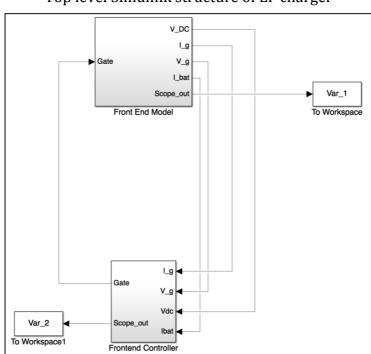

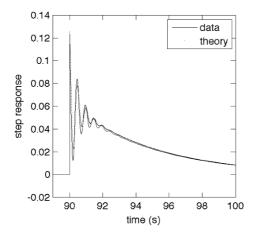

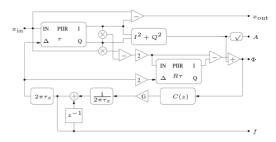

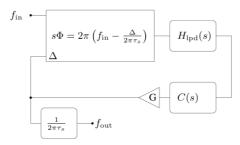

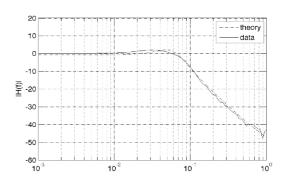

Since the actual value of magnetising inductance is 190 mH (the assumption in section 2.2.1.1 was 250 mH), it is possible to verify that a magnetising inductance of 190 mH still satisfies the maximum series inductance