# Fabrication, Simulation, and Cascading of Electrically Pumped Vertical External Cavity Surface Emitting Lasers (EP-VECSELs)

By

# Xiao Jin

# Department of Electronic and Electrical Engineering

Thesis submitted to the University of Sheffield for the degree of Doctor of Philosophy

June 2015

Intentionally Blank

# **Abstract**

This thesis describes the design, fabrication, simulation, and cascading of electrically pumped external cavity surface emitting lasers (EP-VECSELs) with substrate emission at 980 nm.

Initially, a brief literature review is provided on the history of all types of semiconductor lasers in chapter 1. The design of the wafer structure is discussed in chapter 2, including the characteristics of distributed Bragg reflectors (DBRs), active region geometry, and cavity resonance.

In chapter 3, a full description of the fabrication process of the device is presented, with the development of the etched trench and dielectric layer deposition process. Circular transmission line measurement (CTLM) for measuring contact resistance and the optimisation of contacts is also presented.

Several measurement techniques are introduced in chapter 4, such as beam quality (M<sup>2</sup>) measurement and electroluminescence (EL) mapping of the output beam intensity profile which is subsequently used in chapter 5.

In chapter 5, a model is developed for simulating substrate emitting EP-VECSELs with an etched trench. A good agreement is achieved between the simulation and measurement results which confirm the validity of the model. I then go on to make a parametric study for improving the carrier distribution profile within the EP-VECSEL. New design geometries are highlighted and explored.

A dual chip cascaded EP-VECSELs system is demonstrated in chapter 6. This is a new route to achieve high power EP-VECSELs. Evidence for injection locking is observed from spectral results when two devices have the same cavity resonance wavelength. Also, a dual wavelength cascaded EP-VECSELs system is demonstrated when the cavity resonance wavelengths of the two devices are different.

# **Acknowledgements**

First and most importantly, I would like to thank my supervisor Professor Richard Hogg for his tireless guidance, inspiration, and help since the first day I joined group. Thanks to him for tolerating my ignorance, and teaching me to become a qualified researcher. Without his support I could not make any achievements and I will always be grateful to him.

Secondly, I would like to thank the all the senior members in our group. Thanks to Dr Pavlo Ivanov for his guidance on my simulation works. Thanks to Dr Nasser Babazadeh for teaching me about device fabrication. Thanks to "Big" Dave Childs who patiently answers all my questions with his profound knowledge. Thanks Dr Qi Jiang and Dr Ziyang Zhang for telling me their research experience which saved me a lot of time.

I would like to thank all my colleagues in my office Dr Jon Orchard, Dr David Williams, Dr Siming Chen, Dr Kejia Zhou, Timothy Roberts and Hongchi Lei. Also, I would also like to thank all the colleagues in our group. Especially I would like to thank Dr Xuesong Hu for our deep friendship.

Finally, I would like to thank my respected parents for supporting me both materially and spiritually on my study and life in the UK, without my father's insistence I would not start my research work. I also want to thank my dear wife who has been waiting for me in China for two years.

#### **List of Publications**

# **Journal Papers**

X. Jin, P. Ivanov, D. T. D. Childs, N. Babazadeh, J. Orchard, B. Stevens and R.A. Hogg,

"Simulation of Substrate Emitting EP-VECSELs",

Manuscript in preparation.

X. Jin, JRautiainen, D. T. D. Childs, P. Ivanov, N. Babazadeh, J. Orchard, B. Stevens and R.A. Hogg,

"Cascaded Electrically Pumped Vertical External Cavity Surface Emitting Lasers".

Submitted.

Chen, SM; Zhou, KJ; Zhang, ZY; Wada, O; Childs, DTD; Hugues, M; Jin, X; Hogg,RA,

"Room temperature simultaneous three-state lasing in hybrid quantum well/quantum dotlaser",

Electronics Letters, vol. 48, pp. 644-645, 2012.

## **Conference Proceeding Paper**

X. Jin, P. Ivanov, D. T. D. Childs, N. Babazadeh, J. Orchard, B. Stevens and R.A. Hogg,

"Optimisation of Fundamental Transverse Mode Output in Electrically Pumped Vertical External Cavity Surface Emitting Lasers",

Proc SPIE, vol. 9349, 2015.

#### **Conference Poster**

X. Jin, P. Ivanov, D. T. D. Childs, N. Babazadeh, J. Orchard, B. Stevensand R.A. Hogg,

"Optimisation of Fundamental Transverse Mode Output in Electrically Pumped Vertical External Cavity Surface Emitting Lasers",

SPIE Photonics West, San Francisco, California, USA (2015).

X. Jin, P. Ivanov, D.T.D. Childs, N. Babazadeh, and R.A. Hogg "Study of Factors Limiting Fundamental Transverse Mode Output in Electrically Pumped Vertical External Cavity Surface Emitting Lasers", UK Semiconductor conference, University of Sheffield, UK, July (2014).

# **Contents**

| Ab  | stract                                                                                | iii |

|-----|---------------------------------------------------------------------------------------|-----|

| Ac  | knowledgements                                                                        | V   |

| Lis | t of Publications                                                                     | vi  |

| 1.  | Introduction                                                                          | 1   |

|     | 1.1 Semiconductor lasers                                                              | 1   |

|     | 1.2 Edge emitting lasers                                                              | 1   |

|     | 1.3 Vertical emission lasers                                                          | 2   |

|     | 1.3.1 Vertical cavity surface emitting laser (VCSEL)                                  | 2   |

|     | 1.3.2 Optically pumped vertical external cavity surface emitting laser (OP-VECSEL)    | 4   |

|     | 1.3.3 Electrically pumped vertical external cavity surface emitting laser (EP-VECSEL) | 7   |

|     | 1.3.4 Device geometries                                                               | 8   |

|     | 1.3.5 Comparison between OP- &EP- VECSELs                                             | 11  |

|     | 1.4 Aims of project                                                                   | 12  |

|     | 1.5 Thesis outline                                                                    | 13  |

|     | Reference                                                                             | 16  |

| 2.  | Device Design                                                                         | 21  |

|     | 2.1 Introduction                                                                      | 21  |

|     | 2.2 Distributed Bragg reflectors                                                      | 22  |

|     | 2.3 Active region                                                                     | 29  |

|     | 2.4 Resonant cavity wavelength                                                        | 33  |

|     | 2.5 Final design of the structure                                                     | 38  |

|     | 2.6 Summary                                                                           | 40  |

|     | Reference                                                                             | 42  |

| 3.  | Devices Fabrication Process and Improvement                                           | 45  |

|     | 3.1 Introduction                                                                      | 45  |

|     | 3.2 Fabrication process                                                               | 45  |

|     | 3.3 Fabrication process improvement                                                   | 66  |

|     | 3.3.1 Improvement of trench etching recipe                                            | 67  |

|     | 3.3.2 Improvement of silicon dioxide deposition process                               | 70  |

|     | 3.3.3 Improvement of annealing process                                                | 72  |

|     | 3.4 Conclusion                                                                        | 77  |

|     | 2 5 Euture work                                                                       | 77  |

|    | Reference                                                                    | 78  |

|----|------------------------------------------------------------------------------|-----|

| 4. | Device Characterisation Techniques                                           | 79  |

|    | 4.1 Introduction                                                             | 79  |

|    | 4.2 Device general measurements                                              | 79  |

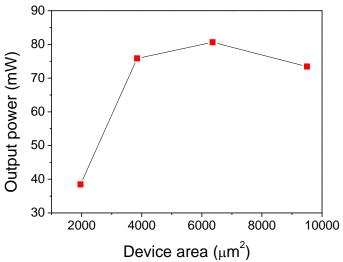

|    | 4.3 Power scaling                                                            | 83  |

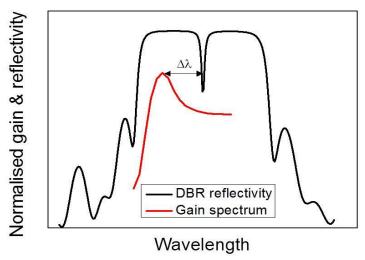

|    | 4.4 Detuning                                                                 | 84  |

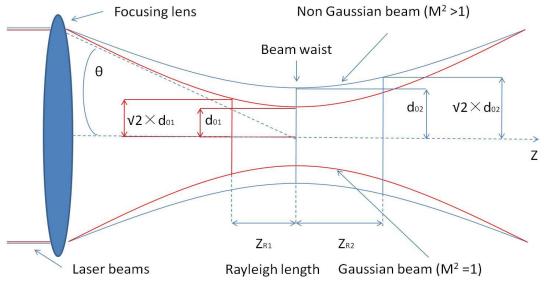

|    | 4.5 Beam quality measurement                                                 | 87  |

|    | 4.6 Electroluminescence mapping                                              | 92  |

|    | 4.7 Summary                                                                  | 94  |

|    | Reference                                                                    | 96  |

| 5. | Modelling Study of Factors Affecting Uniform Carrier Injection in EP-VECSELs | 98  |

|    | 5.1 Introduction                                                             | 98  |

|    | 5.2 The model                                                                | 99  |

|    | 5.2.1 Physical effects included into the model                               | 99  |

|    | 5.2.2 Model calibration                                                      | 101 |

|    | 5.3 Parametric study                                                         | 107 |

|    | 5.4 Summary                                                                  | 115 |

|    | 5.5 Future work                                                              | 116 |

|    | Reference                                                                    | 117 |

| 6. | Cascaded EP-VECSELs                                                          | 119 |

|    | 6.1 Introduction                                                             | 119 |

|    | 6.2 Cavity geometry                                                          | 120 |

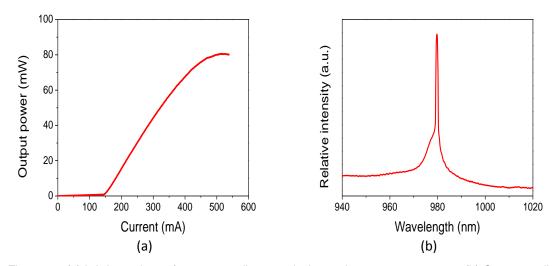

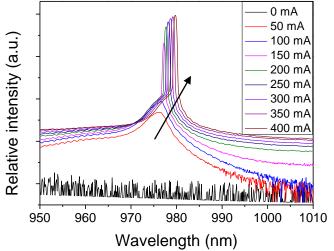

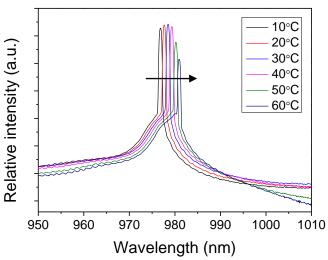

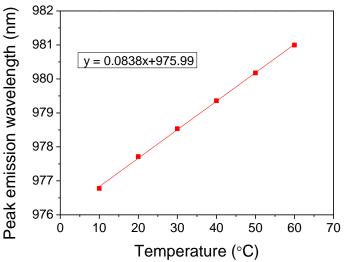

|    | 6.3 Results                                                                  | 123 |

|    | 6.4 Summary                                                                  | 132 |

|    | 6.5 Future Work                                                              | 132 |

|    | Reference                                                                    | 134 |

| 7. | Summary and Future Works                                                     | 136 |

|    | 7.1 Summary                                                                  | 136 |

|    | 7.2 Future works                                                             | 138 |

| Αį | opendix A                                                                    | 140 |

| ^  | opendiy B                                                                    | 1/1 |

# 1. Introduction

#### 1.1 Semiconductor lasers

Since the first laser was demonstrated in 1960 [1], many types of lasers have been developed in the past a few decades. The semiconductor laser has been intensively studied and applied in many kinds of areas due to its flexible emission wavelength achievable by bandgap engineering. Nowadays, one of the most important applications for semiconductor lasers is coupling with fibres in optical fibre communication. Thus, lasers with both fundamental transverse mode and high output power are favoured. In semiconductor lasers, there are two main types of device depending on their emission geometry; one is the edge emitting lasers where the output beam parallel to the chip surface, the other types are vertical emitting lasers where the light output is perpendicular to the chip surface. These lasers will be discussed in the following sections.

### 1.2 Edge emitting lasers

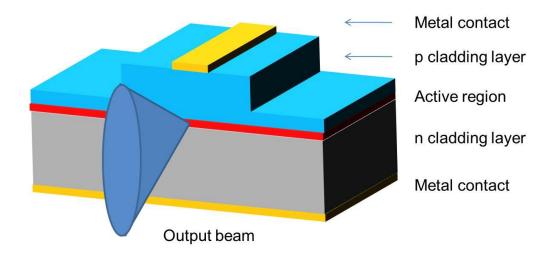

The semiconductor edge emitting laser was developed since the 1960s [2–4]. Fig. 1.1 shows a schematic diagram of the chip structure of the edge emitting laser, where a waveguide is used to guide output light and the two facets act as mirrors to form the Fabry-Perot (F-P) cavity. The length of this cavity is typically in the range of a few hundred micrometres to a few millimetres. To date, the output powers can be up to 20 W from single laser diode with a aperture of 96 µm [5]. The edge emitting lasers can also form 1-D arrays with

over 100 W of total output power being achieved [6]. Fundamental transverse mode output power is about 0.4W [7]. However, due to the nature of the waveguide, the output beam profile from edge emitter lasers has an asymmetric elliptical shape and large divergence; this can be a problem when couples the beam into a fibre and gives a low coupling efficiency. Therefore, the edge emitting lasers are not suitable in applications for optical fibre communications.

Figure 1.1 Schematic diagram of a conventional edge emitting laser with elliptical output beam.

#### 1.3 Vertical emission lasers

#### 1.3.1 Vertical cavity surface emitting laser (VCSEL)

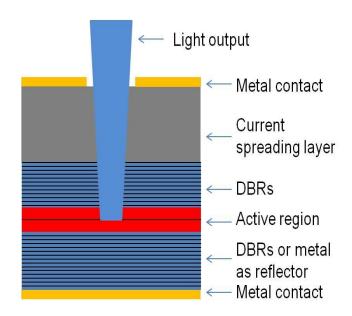

Following on from edge emitting lasers, a new laser structure was conceived by K.Iga in 1977 which is called the vertical cavity surface emitting laser (VCSEL) [8]. The device structure is shown schematically in Fig. 1.2, with the active region being sandwiched between two mirrors; the mirrors can be metal but are often semiconductor multi-layer stacks (distributed Bragg reflectors (DBRs)) which will be discussed in detail in chapter 2. As the gain medium thickness in the vertical devices is only a few hundreds of angstrom, the single

pass gain of the photons is quite small as compared to edge emitting lasers. Thus, the two mirrors require high reflectivity (often larger than 99.9%) to make the photons travel many times inside the cavity to generate enough amplification. Compared to edge emitting lasers, VCSELs have circular beam shape, narrow beam divergence, low fabrication cost, fast modulation rates and naturally form 2D arrays to achieve higher power. Now they are widely used in many areas, such as local area networks (LANs), printers, and smart pixels [9-10].

Figure 1.2 Schematic diagram of VCSEL structure.

After the VCSEL concept was proposed, the first working device was demonstrated in 1979 by using GalnAsP-InP material with an emission wavelength at 1.18 µm [11]. Device lasing under continuous wave drive conditions at room temperature was achieved after a further decade by the use of metal organic chemical vapour phase deposition (MOCVD) to grow the epitaxial layersin 1989 [12]. Recently, single VCSELs with output powers of 380 mW have been reported [13]. Also, the threshold current density of VCSEL has decreased from 162 kA/cm² [14] to about 0.5 KA/cm² [15]. But as

the output power increases by increasing device diameter, the fundamental transverse mode cannot be maintained due to the non-uniform carrier distribution profile generated. The fundamental transverse mode output power is still below 10 mW [16]. Therefore, VCSELs still cannot simultaneously achieve both high power and high quality beam shape and it can be only used in short distance fibre communication.

# 1.3.2 Optically pumped vertical external cavity surface emitting laser (OP-VECSEL)

In order to overcome the drawbacks in VCSELs, a novel type of laser called a vertical external cavity surface emitting lasers (VECSELs) has been developed since the middle of the 1990s [17-18], in order to simultaneously achieve high output power with fundamental transverse mode. Depending on the excitation method, VECSELs are referred to as optically or electrically pumped, and these will be discussed separately in the following section.

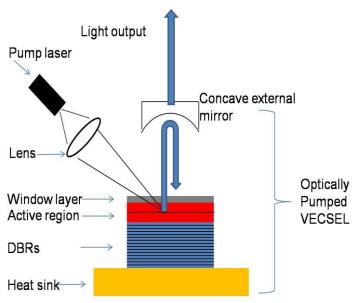

Fig. 1.3 shows aschematic diagram of the optically pumped VECSEL (OP-VECSEL) structure. This device contains a semiconductor chip with an external mirror to form the external cavity, in the semiconductor chip; only one end mirror with high reflectivity is present under the active region. It is worth pointing out that the use of external cavity is one of the most important features in VECSELs. It defines and stabilises the fundamental transverse mode output [19]. As it is optically pumped, a pump laser with shorter emission wavelength is used to pump the gain region of the semiconductor chip. With the use of an optical lens the incident beam spot on the semiconductor chip gain area can be adjusted, achieving power scaling.

Combined with the external mirror, the pumped spot size and the mode size need to be matched with each other, thus both fundamental transverse mode and high output power can be achieved at the same time which is highly challenging for edge emitting lasers and VCSELs. Furthermore, the uniform distribution of the pump beam profile generates a uniform heat distribution within the active region. Hence, the heat can be dissipated by heat sink in a 1-D heat flow [19].

Figure 1.3 Schematic diagram of OP-VECSEL structure with pump laser.

The OP-VECSELs have been proved to achieve high power with single mode simultaneously. So far, a single OP-VECSEL has been reported with a multimode power up to 106 W [20] and single transverse mode at 23.8 W [21]. The formation of the external cavity also provides flexibility in the design of the cavity configuration. Many different shapes of cavity have been demonstrated, such as V shaped cavity [22], Z-shaped cavity [22-23], T shaped cavity and VVV shaped cavity [25]. These different cavity shapes allow the use of various optical elements to achieve different purposes, such as second-harmonic generation with etalon [26], passively mode locking with semiconductor

saturable absorber mirror (SESAM) to generate ultra-short pulses [27-28], dual chips to achieve power scaling [29] and THz generation [30].

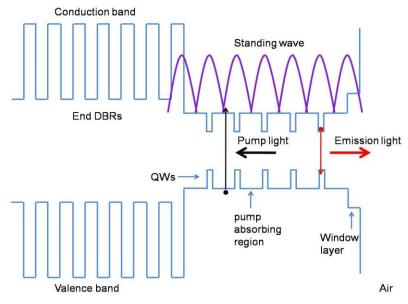

Fig. 1.4 shows a schematic of the band structure of an OP-VECSEL. The beam from the pump laser is incident on the active region of the semiconductor chip, and those photons are absorbed by the pump absorbing region and create electrons and holes. Subsequently, these carriers diffuse into the QWs which have smaller bandgap. The QWs needs to be placed close to the antinodes of the standing wave in order to reduce threshold gain and this structure arrangement will be discussed in detail in chapter 2. Once in the QWs, the electrons and holes can recombine and emit photons with lower energy than the pump laser. The OP-VECSEL can be considered as a power and mode converter, it can transfer a high power, multimode pump beam, into a lower output power with good beam quality [19]. A window layer containing a larger bandgap is on the top of the gain region to minimise non-radiative recombination at the air semiconductor surface.

Figure 1.4 Schematic diagram of bandgap structure for OP-VECSELs.

# 1.3.3 Electrically pumped vertical external cavity surface emitting laser (EP-VECSEL)

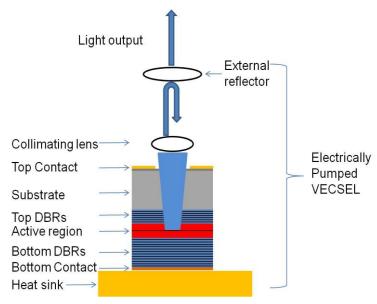

Following on from the OP-VECSELs, VECSELs pumped by electricity were first presented by Novalux Inc in 2001[31]. As shown in the Fig. 1.5, this type of device has a similar structure to a VCSEL but with one of the mirrors having a lower reflectivity and an external mirror forms external cavity.

EP-VECSELs have the same applications as OP-VECSELs. The removal of the pump lasers in EP-VECSELs makes it more compact and lower cost. The EP-VECSEL is therefore attractive in higher volume applications than the OP-VECSEL. A numerical analysis on the design of EP-VECSELs has been reported [32]. But current injection brings some new problems which do not need to be considered in OP-VECSELs, such as the balance between device resistance and doping level must be carefully considered [33], and the current spreading layer thickness should be optimised in order to provide enough diffusion length to carriers while minimising the optical loss [34].

So far, single EP-VECSELs have been reported with output powers of 4.7 W in multimode [35] and ~500 mW in fundamental transverse mode [36]. In order to achieve the same performance of the OP-VECSELs, more research is needed to improve the performance of the EP-VECSELs in order to replace the OP-VECSELs in future. A comparison between two types of VECSELs will be discussed in the next section.

Figure 1.5 Schematic diagram of EP-VECSEL structure.

#### 1.3.4 Device geometries

In electrically pumped vertical lasers, the single transverse mode output is determined by the carrier distribution profile across the active region. Many studies have been carried out in order to achieve this in large diameter devices in order to increase the single mode output power. Several widely applied device geometries for carrier confinement will be introduced in this section. Some of them are applied in both VCSELs and EP-VECSELs.

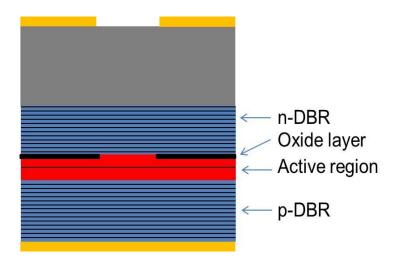

Fig. 1.6 depicts a device structure with an oxide confinement layer. A high Alcontaining layer can be placed above the active region and this layer can form a oxide confinement aperture by wet thermal oxidation [37]. The use of this structure can reduce the threshold current by providing confinement of carriers inside the oxide aperture. Also the reduction of the refractive index in oxide layer provides wave guiding vertically [38]. This structure can be improved using double oxide layer confinement [39]. But in order to meet the requirement of single mode condition, the normalised frequency V is introduced,

$$V = \frac{2\pi r}{\lambda} \sqrt{(n_1)^2 - (n_2)^2},\tag{1.1}$$

Where r is device radius,  $n_1$  is the refractive index on the center of the waveguide;  $n_2$  is the effective refractive index of the cladding layer. Devices can only support fundamental transverse mode when V < 2.405. Therefore, single mode output can be maintained only in ~ few micron diameter devices [40].

Figure 1.6 Device structure with oxide confinement layer.

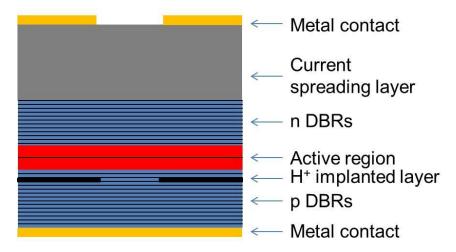

Fig. 1.7 shows the schematic of a device structure with proton implantation. This implanted layer can provide a good lateral confinement of the current by locally changing the conductivity of the semiconductor material. The most attractive point of this technique is that this structure is easy to fabricate and low cost. Also, it can improve power conversion efficiency of devices [41]. But it may introduce lattice defects due to the high energy ions bombarding the device. Thermal lensing effects occur under high output power operation, which will generate high order transverse modes [41-42].

Figure 1.7 Device structure with hydrogen implanted layer.

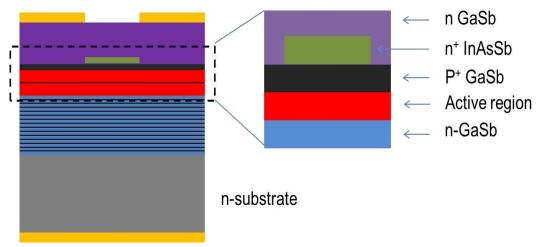

Fig. 1.8 describes a device using buried tunnel junction (BTJ) techniques. This structure is widely used in the shortwave infrared (SWIR) region to provide current confinement. The BTJ needs to be placed at the node of electrical field in order to minimise the absorption loss, also the layers can be modulation doped to reduce the free carrier absorption (FCA) [44]. Unlike the interband absorption, in FCA the carriers which are already in the excited states will absorb photons and jump to higher energy level. Therefore, even the substrate material has higher bandgap it can still absorb photons and reduce the device efficiency. The tunnel junction is formed by the n<sup>+</sup> InAsSb between the n GaSb and P<sup>+</sup> GaSb region. In this case, only the n<sup>+</sup> InAsSb area can conduct current, by using lithographic and etching step the size of the tunnel junction can be defined thus achieving current confinement [45]. Besides the advantages mentioned above, it is worth noting that the BJT requires epitaxial regrowth and a selective etching step which makes the process more difficult.

Figure 1.8 Device structure with buried tunnel junction (BTJ) emitting at 2.34 µm.

Besides the geometries mentioned above, we developed another device structure with etched trench to try to provide a better confinement to carriers which will be discussed in details later in this thesis.

#### 1.3.5 Comparison between OP- &EP- VECSELs

In my thesis only EP-VECSELs are researched, but it is still worthwhile to make a comparison between the two types of VECSELs. In general, both the optically and electrically pumped VECSELs have their own merits and drawbacks. For OP-VECSELs, initially it is obvious to see that only one end mirror contained in the semiconductor chip will simplify the epitaxial process. Optically pumped devices do not require electrical contacts for current injection, thus making the fabrication process easier. Also, due to there being no n or p doping in the semiconductor layers, the OP-VECSELs can avoid free carrier absorption loss which is a main factor in limiting the output power in EP-VECSELs [46]. The self-heating effect is weak because the Joule heat generated by device resistance can be eliminated. Last but not least, in OP-VECSELs a uniform output beam profile can be easily achieved by changing the pump geometry of the gain area of the semiconductor chip. Therefore, a

near perfect beam quality (M<sup>2</sup>≈1) can be maintained even in large diameter devices with high output power which has been difficult to achieve in EP-VECSELs to date.

Simultaneously, the main drawbacks of OP-VECSELs is that it needs additional alignment due to the use of a pump source which will make the setup structure more complicated and the device becomes less compact and more expensive. The quantum defect, which is the energy difference between the incident pump photons and the emitted photons, decreases the overall laser efficiency in OP-VECSELs, and may pose heating issues. It must be admitted that the EP-VECSELs have some technological challenges, but it is an attractive and competitive device which can replace OP-VECSELs in the future.

#### 1.4 Aims of project

Orchard *et al.* have presented EP-VECSELs with etched trenchs in previous work [4-5]. As we are the only research group that uses etched trench in order to confine charge carriers, many issues around the engineering of this structure have not been reported.

Further development of the fabrication process is required in order to reliably and repeatedly realise high quality devices. There is no study reported on the fabrication process for etched trench structures. A trench with straight sidewalls and good coherent dielectric layer plays an important role on the EP-VECSEL performance.

Some models have been used for simulating current distributions in EP-VECSELs. But to date no modeling has been applied to etched trench structures. As a result, a systemic investigation of key factors impacting the carrier distribution profile within the device has not been reported.

In EP-VECSELs, power scaling shows a limitation when the device diameter increases. In OP-VECSELs there are many different types of multi-cavity shapes which have been designed for all kinds of purposes including power scaling. However, in EP-VECSELs only the linear cavity has been applied in experiments so far, and there is no report on using multiple chips to form cascaded system within the same cavity in order to achieve power scaling.

#### 1.5 Thesis outline

This thesis discusses several aspects in the development of EP-VECSELs.

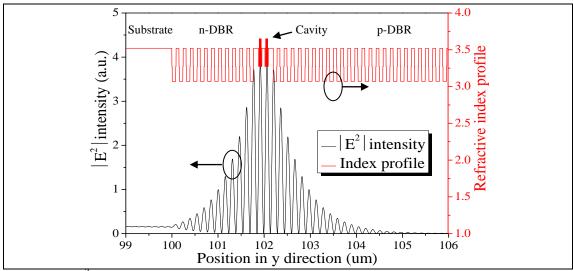

Chapter 2 discuses wafer design issues. Initially simulations using CAMFR [48] were carried out in order to determine the number of DBR pairs on each side of the cavity, also an intermediate layer is added between each DBR material to reduce the series resistance, results show that Al<sub>0.47</sub>Ga<sub>0.53</sub>As with refractive index between the two DBR materials (Al<sub>0.8</sub>Ga<sub>0.2</sub>As/GaAs) with a thickness of 10 nm can maintain good optical properties of the DBR pairs while reducing resistance. Next, the intra-cavity with periodic gain structure (PGS) is introduced; as two groups of three QWs are used for present wafers, 1.8 times of increasing on optical confinement is achieved. Modelling results also shown that the thickness of epitaxial layers should be controlled carefully during the epitaxial process. Especially, the cavity resonant wavelength is

quite sensitive to DBR thickness changes. Reflectivity spectra at the centre wavelength show a minimum when the numbers of DBR pairs at both sides of the active region are the same. The use of the method for wafer characterisation is discussed.

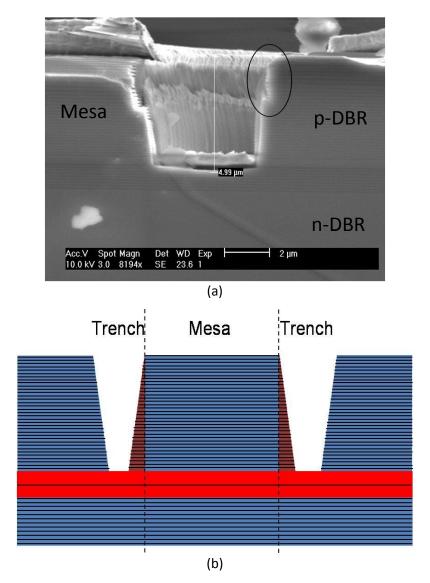

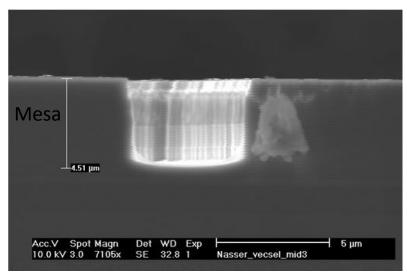

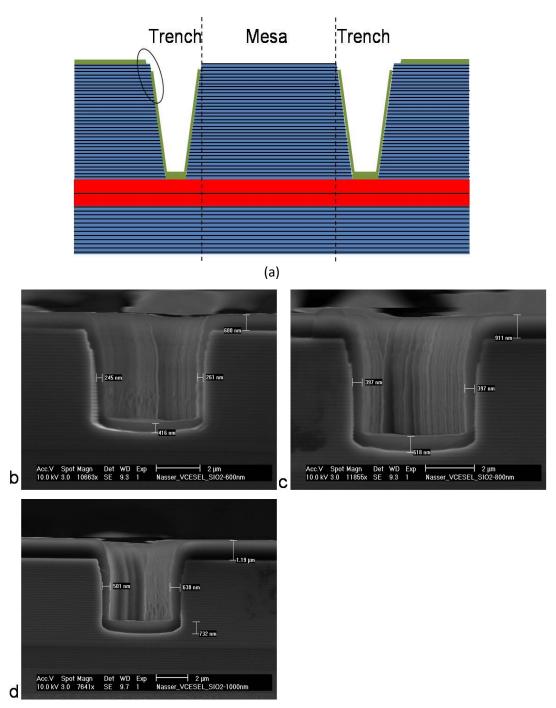

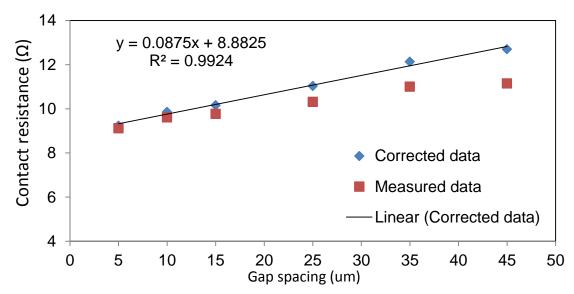

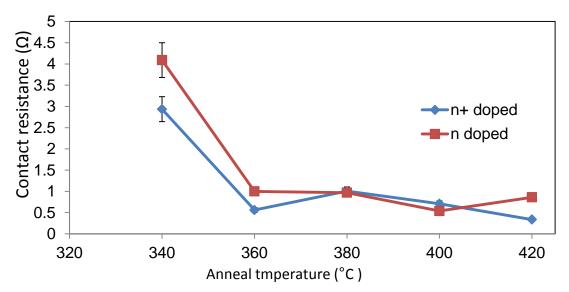

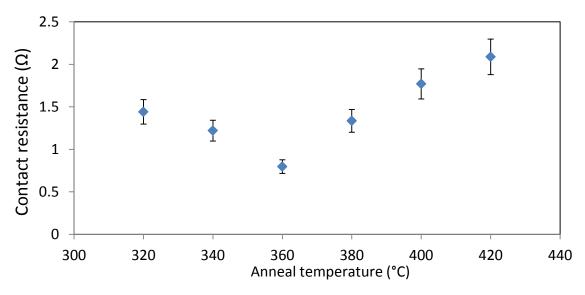

Chapter 3 describes the development of fabrication processes for EP-VECSELs with an etched trench structure. An improvement of the etch profile of the trench is made by carefully changing the etch parameters. Thus a trench with straight side wall can be observed from SEM results. Subsequently, annealing tests were carried out to optimise the contact resistance of the devices. Considering the results of contact resistance versus annealing temperature, and the order that annealing has to be carried out, an annealing temperature of 360 °C is shown to be optimum.

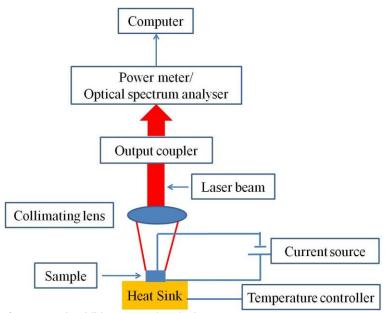

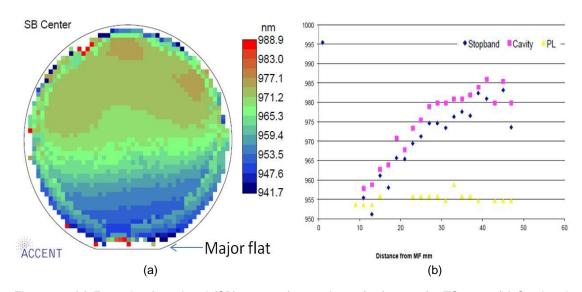

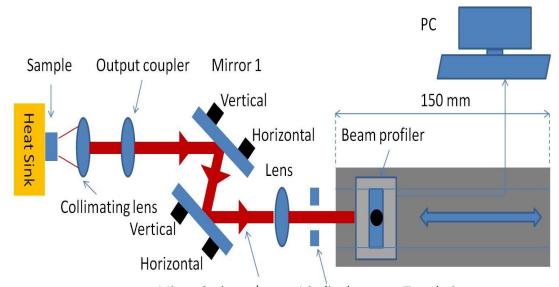

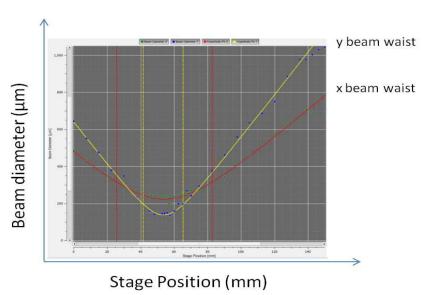

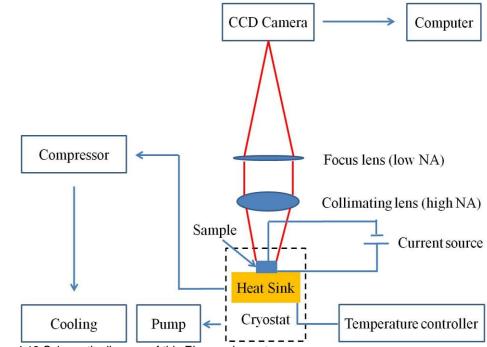

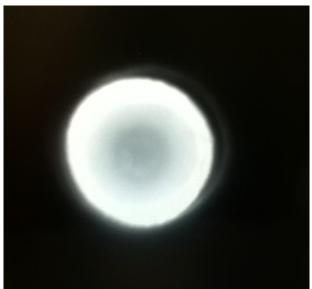

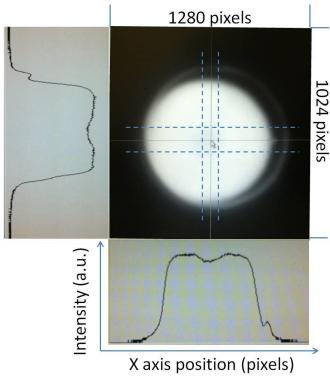

Chapter 4 presents several experimental techniques used for characterizing EP-VECSELs. First the linear cavity setup used for general L-I-V and spectrum measurements for devices is described. Then I discuss the effect of detuning on the performance of EP-VECSELs and briefly introduce an etch method to determine the value of detuning across the whole wafer. After that I discuss the light intensity distribution measurement technique using an electroluminescence (EL) mapping system. This measurement result is then used for assessment of the model developed in chapter 5.

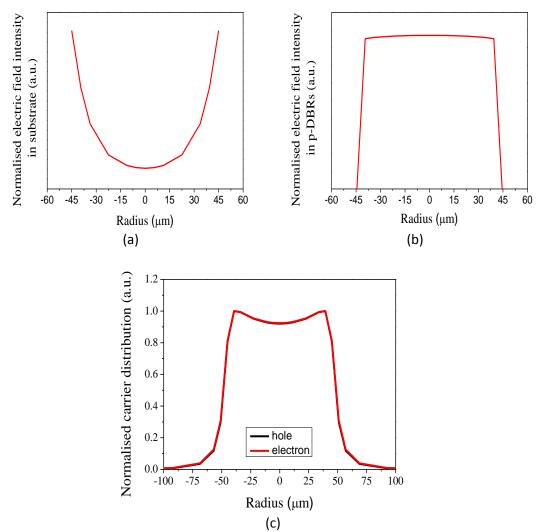

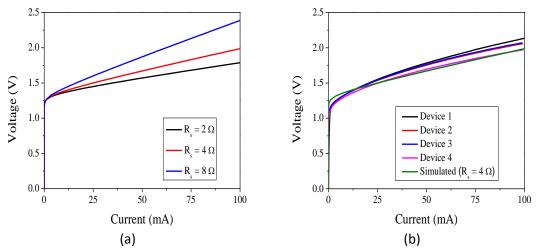

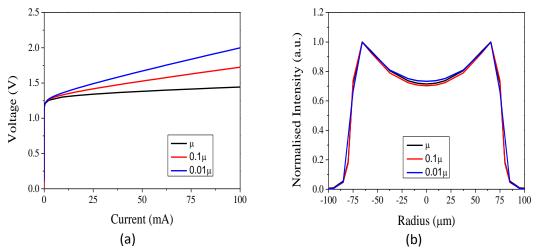

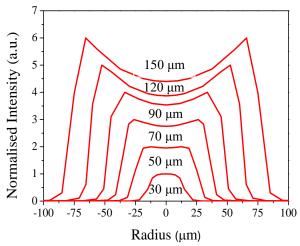

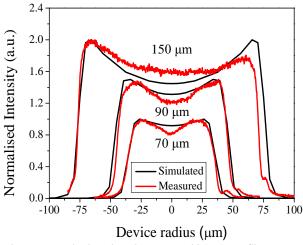

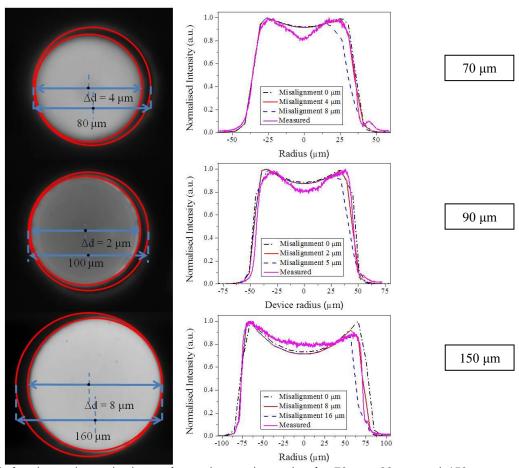

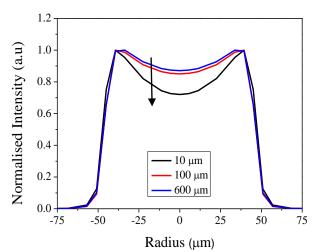

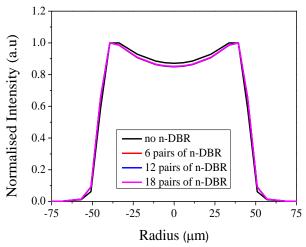

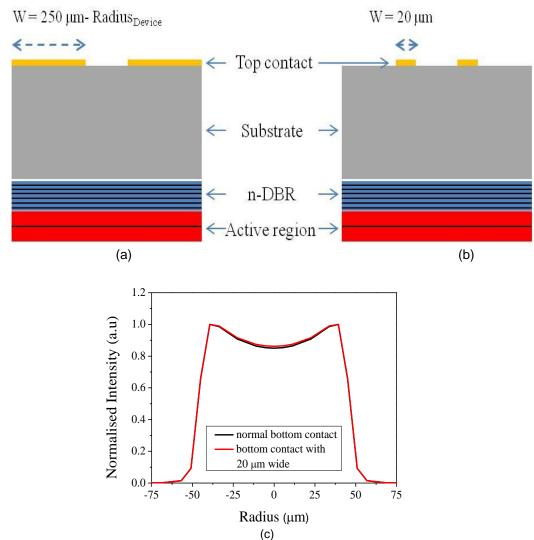

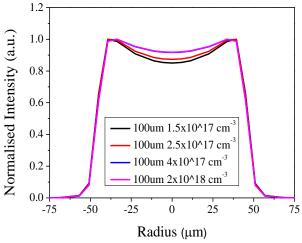

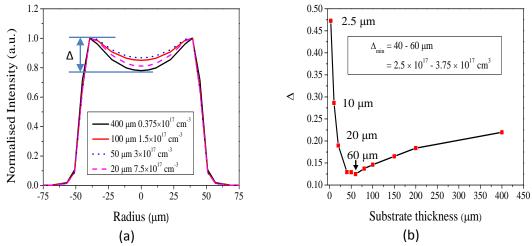

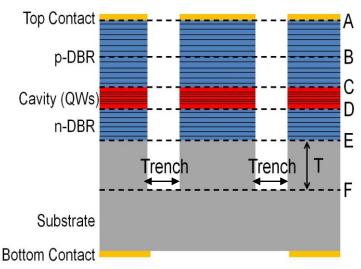

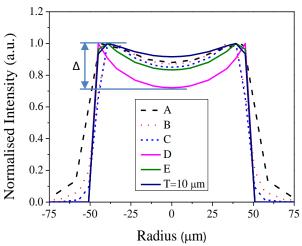

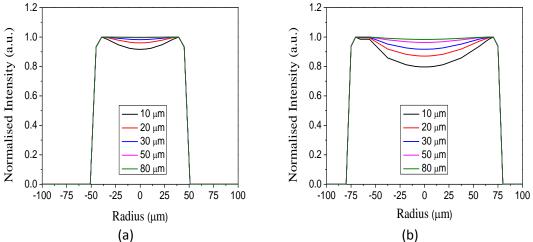

Chapter 5 presents a model of EP-VECSELs for simulating the transverse carrier distribution profile using a commercial software package (Rsoft LaserMod) [49]. This is due to the beam quality (M²) of EP-VECSELs being determined by the charge carrier distribution profile inside the devices. First

the model is calibrated by using the EL measurement data of devices provided in chapter 4, also the effects of contact misalignment are taken into account. A good agreement between simulated and experimental results is achieved, confirming the validity of the model. Subsequently, I investigate parameters which can affect the carrier distribution profile. Analysis of the trench depth indicates that it plays a key role in determining the carrier distribution profile. Results shows that a device structure with thinner substrate thickness compare to present structure and a trench etched into the substrate should improve the carrier distribution profile [50].

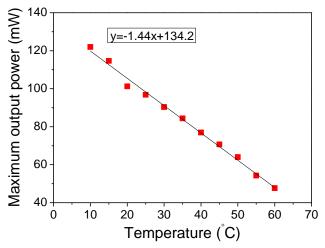

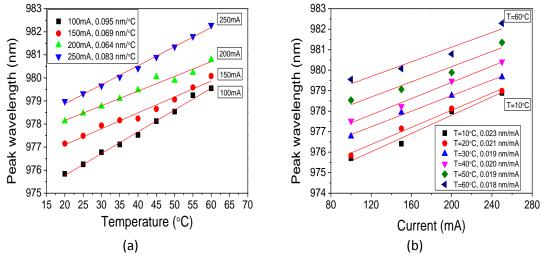

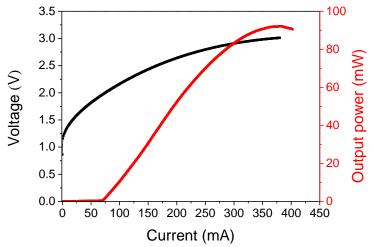

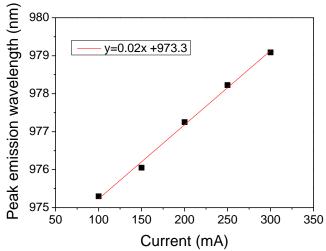

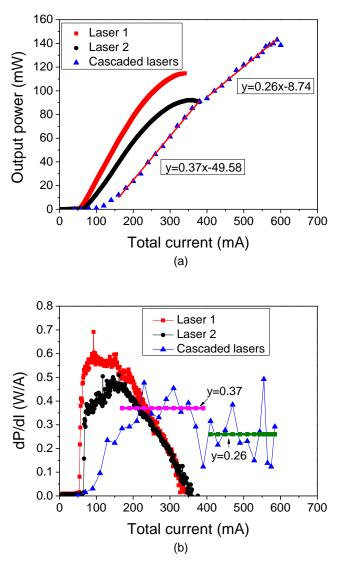

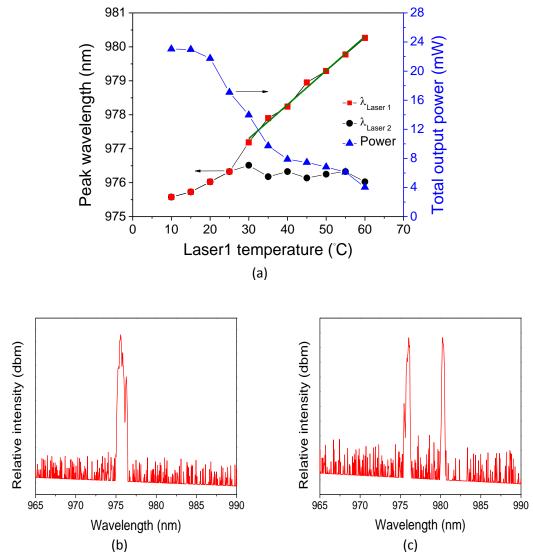

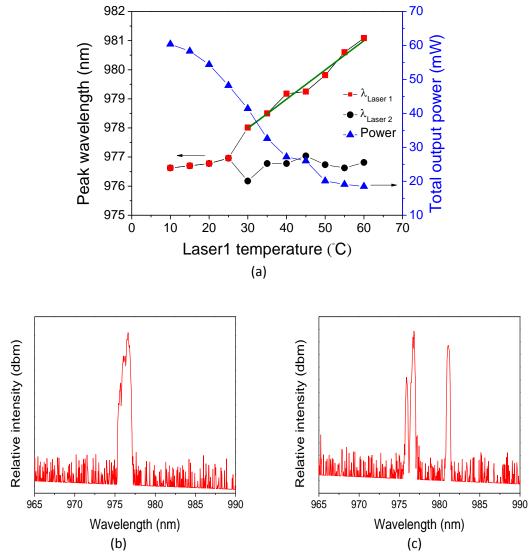

Chapter 6 reports the first demonstration of two cascaded EP-VECSELs within the same cavity. This cascaded system is designed to overcome the power scaling limitation due to the non-uniform carrier distribution in large diameter devices. This cavity has an asymmetric x-shape, with one of the devices being wavelength tuned by a heat sink and the other is tuned by self-heating alone. Initially single devices are measured separately in a simple linear cavity for comparison. 1.4 times the total output power is achieved in cascaded cavity as compared to a single device. Spectral results show evidence that injection locking is observed when the cavity resonance of the two devices is coincident. By changing the temperature of the heat sink, the cavity resonance wavelength of two devices may be made to be different and a dual wavelength cascaded EP-VECSELs system is presented.

Chapter 7 will briefly summarise my whole work in this thesis.

#### Reference

- [1] T. H. Maiman, "Stimulated Optical Radiation in Ruby," *Nature*, vol. 187, no. 4736, pp. 493–494, 1960.

- [2] M. I. Nathan, W. P. Dumke, G. Burns, F. H. Dill, and G. Lasher, "Stimulated emission of radiation from GaAs p-n junctions," *Appl. Phys. Lett.*, vol. 1, no. 3, pp. 62–64, 1962.

- [3] N. Holonyak and S. F. Bevacqua, "Coherent (visible) light emission from Ga(As1-xPx) junctions," *Appl. Phys. Lett.*, vol. 1, no. 4, pp. 82–83, 1962.

- [4] R. N. Hall, G. E. Fenner, J. D. Kingsley, T. J. Soltys, and R. O. Carlson, "Coherent light emission from GaAs junctions," *Phys. Rev. Lett.*, vol. 9, no. 9, pp. 366–368, 1962.

- [5] P. Crump, G. Blume, K. Paschke, R. Staske, a. Pietrzak, U. Zeimer, S. Einfeldt, a. Ginolas, F. Bugge, K. Häusler, P. Ressel, H. Wenzel, and G. Erbert, "20W continuous wave reliable operation of 980nm broad-area single emitter diode lasers with an aperture of 96μm," *Proc. SPIE*, vol. 7198, pp. 719814–1–9, 2009.

- [6] Roland Diehl, *High power diode lasers: fundamentals, technology, applications.* Spinger, 2000.

- [7] M. Yuda, T. Sasaki, J. Temmyo, M. Sugo, and C. Amano, "High-power highly reliable 1.02-1.06-/spl mu/m InGaAs strained-quantum-well laser diodes," *IEEE J. Quantum Electron.*, vol. 39, no. 12, pp. 1515–1520, 2003.

- [8] K. Iga, "Surface-emitting laser-its birth and generation of new optoelectronics field," *IEEE J. Sel. Top. Quantum Electron.*, vol. 6, no. 6, pp. 1201–1215, 2000.

- [9] J. Geske, V. Jayaraman, T. Goodwin, M. Culick, M. Macdougal, T. Goodnough, D. Welch, and J. E. Bowers, "2.5-Gbs Transmission over 50 km with a 1.3-um Vertical-Cavity Surface-Emitting Laser," *photonics Technol. Lett.*, vol. 12, no. 12, pp. 1707–1709, 2000.

- [10] H. Kosaka, "Smart integration and packaging of 2-D VCSEL's for high-speed parallel links," *IEEE J. Sel. Top. Quantum Electron.*, vol. 5, no. 2, pp. 184–192, 1999.

- [11] C. K. and Y. S. Haruhisa Soda, Ken-ichi Iga, "GalnAsP / InP Surface Emitting Injection Lasers," *Jpn. J. Appl. Phys.*, vol. 18, no. 12, pp. 2329–2330, 1979.

- [12] F. Koyama, S. Kinoshita, and K. Iga, "Room-temperature continuous wave lasing characteristics of a GaAs vertical cavity surface-emitting laser," *Appl. Phys. Lett.*, vol. 55, no. 3, pp. 221–222, 1989.

- [13] A. Higuchi, H. Naito, K. Torii, M. Miyamoto, T. Morita, J. Maeda, H. Miyajima, and H. Yoshida, "High power density vertical-cavity surface-emitting lasers with ion implanted isolated current aperture: erratum," *Opt. Express*, vol. 20, no. 4, pp. 4206–4212, 2012.

- [14] K. Iga, S. Ishikawa, S. Ohkouchi, and T. Nishimura, "Room temperature pulsed oscillation of GaAlAs/GaAs surface emitting junction laser," *Appl. Phys. Lett.*, vol. 45, no. 4, pp. 348–350, 1984.

- [15] Y. Ding, W. J. Fan, D. W. Xu, C. Z. Tong, Y. Liu, and L. J. Zhao, "Low threshold current density, low resistance oxide-confined VCSEL fabricated by a dielectric-free approach," *Appl. Phys. B Lasers Opt.*, vol. 98, no. 4, pp. 773–778, 2010.

- [16] J. W. Shi, K. L. Chi, J. H. Chang, Z. R. Wei, J. W. Jiang, and Y. J. Yang, "Single-mode vertical-cavity surface-emitting laser array with high power and narrow far-field divergence angle," *IEEE Photonics J.*, vol. 5, no. 6, p. Art. ID 1502508, 2013.

- [17] M. Kuznetsov, F. Hakimi, and A. Sprague, R and Mooradian, "High-Power (>0.5-W CW) Diode-Pumped Vertical-External-Cavity Surface-Emitting Semiconductor Lasers with Circular TEM00 Beams," *IEEE Photonics Technol. Lett.*, vol. 9, no. 8, pp. 1063–1065, 1997.

- [18] M. Kuznetsov, F. Hakimi, R. Sprague, and A. and Mooradian, "Design and characteristics of high-power (0.5-W CW) diode-pumped verticalexternal-cavity surface-emitting semiconductor lasers with circular TEM00 beams," *IEEE Photonics Technol. Lett.*, vol. 5, no. 3, pp. 561– 573, 1999.

- [19] O. G. Okhotnikov, Semiconductor Disk Lasers: Physics and Technology. Weinheim: Wiley-VCH Verlag GmbH & Co. KGaA, 2010.

- [20] B. Heinen, T. L. Wang, M. Sparenberg, A. Weber, B. Kunert, J. Hader, S. W. Koch, J. V. Moloney, M. Koch, and W. and Stolz, "106 W continuous-wave output power from vertical-external-cavity surface-emitting laser," *Electron. Lett.*, vol. 48, no. 9, pp. 516–U102, 2012.

- [21] T. L. Wang, Y. Kaneda, J. M. Yarborough, J. Hader, J. V. Moloney, A. Chernikov, S. Chatterjee, S. W. Koch, B. Kunert, and W. Stolz, "High-Power Optically Pumped Semiconductor Laser at 1040 nm," *IEEE Photonics Technol. Lett.*, vol. 22, no. 9, pp. 661–663, May 2010.

- [22] L. Fan, M. Fallahi, J. Hader, A. R. Zakharian, J. V. Moloney, W. Stolz, S. W. Koch, R. Bedford, and J. T. Murray, "Linearly polarized dual-

- wavelength vertical-external-cavity surface-emitting laser," *Appl. Phys. Lett.*, vol. 90, no. 18, pp. 1811241–3, 2007.

- [23] B. Rosener, M. Rattunde, R. Moser, C. Manz, K. Kohler, and J. Wagner, "GaSb-Based Optically Pumped Semiconductor Disk Laser Using Multiple Gain Elements," *IEEE Photonics Technol. Lett.*, vol. 21, no. 13, pp. 848–850, 2009.

- [24] E. J. Saarinen, A. Härkönen, S. Suomalainen, and O. G. Okhotnikov, "Power scalable semiconductor disk laser using multiple gain cavity," *Opt. Express*, vol. 14, no. 26, pp. 12868–12871, 2006.

- [25] S. Operation, S. Kaspar, M. Rattunde, T. Tino, S. Adler, C. Manz, K. Klaus, and J. Wagner, "Recent Advances in 2- μ m GaSb-Based Semiconductor Disk Laser Power Scaling, Narrow-Linewidth and Short-Pulse Operation," *IEEE J. Sel. Top. QUANTUM Electron.*, vol. 19, no. 4, 2013.

- [26] M. a. Holm, D. Burns, a. I. Ferguson, and M. D. Dawson, "Actively stabilized single-frequency vertical-external-cavity\nAlGaAs laser," *IEEE Photonics Technol. Lett.*, vol. 11, no. 12, pp. 1551–1553, 1999.

- [27] U. Keller, K. J. Weingarten, F. X. Kärtner, D. Kopf, B. Braun, I. D. Jung, R. Fluck, C. Hönninger, N. Matuschek, and J. Aus Der Au, "Semiconductor saturable absorber mirrors (SESAM's) for femtosecond to nanosecond pulse generation in solid-state lasers," *IEEE J. Sel. Top. Quantum Electron.*, vol. 2, no. 3, pp. 435–451, 1996.

- [28] S. Hoogland, S. Dhanjal, A. C. Tropper, J. S. Roberts, R. Häring, R. Paschotta, and U. Keller, "Passively Mode-Locked Diode-Pumped Surface-Emitting Semiconductor Laser," *IEEE Photonics Technol. Lett.*, vol. 12, no. 9, pp. 1135–1137, 2000.

- [29] L. Fan, M. Fallahi, J. Hader, A. R. Zakharian, J. V Moloney, J. T. Murray, R. Bedford, W. Stolz, and S. W. Koch, "Multichip vertical-external-cavity surface-emitting lasers: a coherent power scaling scheme," *Opt. Lett.*, vol. 31, no. 24, pp. 3612–3614, 2006.

- [30] M. Scheller, J. M. Yarborough, J. V Moloney, M. Fallahi, M. Koch, and S. W. Koch, "Room temperature continuous wave milliwatt terahertz source," *Opt. Express*, vol. 18, no. 26, pp. 27112–27117, 2010.

- [31] J. G. McInerney, A. Mooradian, A. Lewis, A. V. Shchegrov, E. M. Strzelecka, D. Lee, J. P. Watson, M. K. Liebman, G. P. Carey, A. Umbrasas, C. a. Amsden, B. D. Cantos, W. R. Hitchens, D. L. Heald, V. V. Doan, J. L. Cannon, and K. L. Lear, "High brightness 980 nm pump lasers based on the Novalux Extended Cavity Surface-Emitting Laser (NECSEL) concept," SPIE Proc., vol. 4947, no. 2003, pp. 240–251, 2003.

- [32] P. Kreuter, B. Witzigmann, D. J. H. C. Maas, Y. Barbarin, T. Südmeyer, and U. and Keller, "On the design of electrically pumped vertical-external-cavity surface-emitting lasers," *Appl. Phys. B*, vol. 91, no. 2, pp. 257–264, Mar. 2008.

- [33] J. R. Orchard, D. T. D. Childs, D. Williams, L.-C. Lin, B. J. Stevens, J. S. Roberts, and R. a. Hogg, "Trade-offs in the realization of electrically pumped vertical external cavity surface emitting lasers," *Semicond. Laser Conf. (ISLC), 2010 22nd IEEE Int.*, vol. 17, no. 6, pp. 1745–1752, 2010.

- [34] Y.-Y. Lai, T.-C. Lu, T.-L. Ho, S.-C. Huang, and S.-C. Wang, "Numerical analysis on current and optical confinement of III-nitride vertical-cavity surface-emitting lasers," *Opt. Express*, vol. 22, no. 8, pp. 9789–9797, 2014.

- [35] P. Zhao, B. Xu, R. Van Leeuwen, T. Chen, L. Watkins, D. Zhou, and P. Gao, "Compact 4.7 W, 18.3% wall-plug efficiency green laser based on an electrically pumped VECSEL using intracavity frequency doubling," *Opt. Lett.*, vol. 39, no. 16, pp. 4766–4768, 2014.

- [36] J. G. McInerney, A. Mooradian, A. Lewis, A. V. Shchegrov, E. M. Strzelecka, D. Lee, J. P. Watson, M. Liebman, G. P. Carey, B. D. Cantos, W. R. Hitchens, and D. and Heald, "High-power surface emitting semiconductor laser with extended vertical compound cavity," *Electron. Lett.*, vol. 39, no. 6, pp. 523–525, 2003.

- [37] Y. Laaroussi, C. Chevallier, F. Genty, N. Fressengeas, L. Cerutti, T. Taliercio, O. Gauthier-Lafaye, P.-F. Calmon, B. Reig, J. Jacquet, and and G. Almuneau, "Oxide confinement and high contrast grating mirrors for Mid-infrared VCSELs," *Opt. Mater. Express*, vol. 3, no. 10, pp. 1576–1585, 2014.

- [38] C. Degen, W. Elsaber, and I. Fischer, "Transverse modes in oxide confined VCSELs: Influence of pump profile, spatial hole burning, and thermal effects," *Opt. Express*, vol. 5, no. 3, pp. 38–47, 1999.

- [39] S. F. Yu, Analysis and design of vertical cavity surface emitting lasers, vol. 7. A JOHN WILEY & SONS, INC., 2003.

- [40] G. P. Agrawal, *Fiber-Optic Communication Systems*. New York:Wiley, 2002.

- [41] K. L. Lear, S. P. Kilcoyne, and S. a. Chalmers, "High power conversion efficiencies and scaling issues for multimode vertical-cavity top-surface-emitting lasers," *IEEE Photonics Technol. Lett.*, vol. 6, no. 7, pp. 778–781, 1994.

- [42] and K. L. L. M. Hagerott Crawford, R. P. Schneider, Jr., K. D. Choquette, "Temperature-Dependent Characteristics and Single-Mode

- Performance of AlGaInP-B ased 670-690-nm Vertical-Cavity Surface-Emitting Lasers," *IEEE Photonics Technol. Lett.*, vol. 7, no. 7, pp. 724–726, 1995.

- [43] G. R. Hadley and S. W. Lear, K.L.; Warren, M.E.; Choquette, K.D.; Scott, J.W.; Corzine, "Comprehensive numerical modeling of vertical-cavity surface-emitting lasers," *EEE J. ofQuantum Electron.*, vol. 32, no. 4, pp. 607–616, 1996.

- [44] M. Müller, T. Gründl, M. Horn, R. D. Nagel, W. Wiedmeier, E. Rönneberg, G. Böhm, and M. Amann, "Small-Signal Analysis of High-Temperature Stable 1550nm High-Speed VCSELs," in *Proceedings of 6th Joint Symposium on Opto- and Microelectronic Devices and Circuits*, 2010.

- [45] A. Harkonen, A. Bachmann, S. Arafin, K. Haring, J. Viheriala, M. Guina, and M.-C. Amann, "2.34 um electrically pumped VECSEL with buried tunnel junction," *SPIE Photonics Eur.*, vol. 7720, pp. 7720151–7, 2010.

- [46] Y. Barbarin, M. Hoffmann, W. P. Pallmann, I. Dahhan, P. Kreuter, M. Miller, J. Baier, H. Moench, M. Golling, S. Thomas, B. Witzigmann, and U. and Keller, "Electrically Pumped Vertical External Cavity Surface Emitting Lasers Suitable for Passive Modelocking," *IEEE J. Sel. Top. QUANTUM Electron.*, vol. 17, no. 6, pp. 1779–1786, 2011.

- [47] J. R. Orchard, D. T. D. Childs, L. C. Lin, B. J. Stevens, D. M. Williams, and R. A. and Hogg, "Design Rules and Characterisation of Electrically Pumped Vertical External Cavity Surface Emitting Lasers," *Jpn. J. Appl. Phys.*, vol. 50, no. 4, Apr. 2011.

- [48] P. Bienstman, "CAMFR manual v1.3." pp. 1–70.

- [49] RSoft Design Group, "LaserMod 9 User guide," 2012.

- [50] X. Jin, P. Ivanov, D. T. D. Childs, N. Babazadeh, J. Orchard, S. Ben, and R. A. and Hogg, "Optimisation of Fundamental Transverse Mode Output in Electrically Pumped Vertical External Cavity Surface Emitting Lasers," *Proc SPIE*, vol. 9349, 2015.

# 2. Device Design

#### 2.1 Introduction

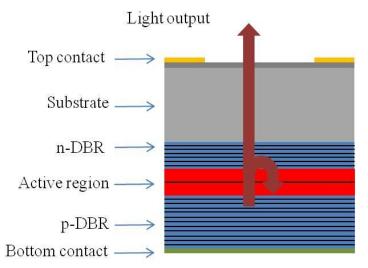

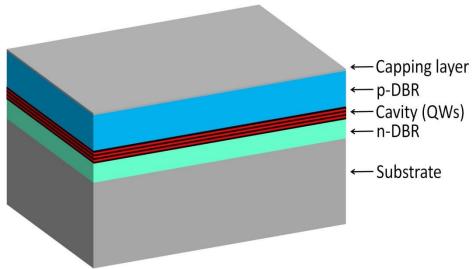

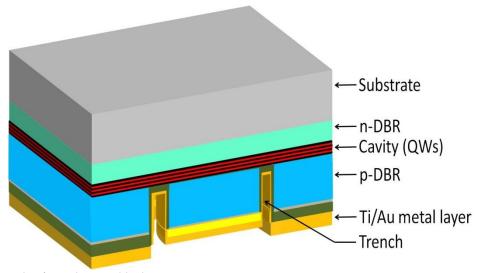

In this chapter, the design of the EP-VECSEL structure will be discussed. Fig. 2.1 shows a schematic diagram of the chip in a substrate emitting EP-VECSELs. Though an output reflector is needed to form the external cavity with the device in order to achieve lasing, no design issue is needed for the output reflector. Thus the design of the structure mostly concerns at the semiconductor chip.

The main parts in the semiconductor chip include a n-doped substrate, n-doped DBR, the intracavity with quantum wells (QWs), p-doped DBR, and top and bottom metal contact for injecting current. Both the n- and p-doped DBRs form the cavity surrounding the QW active zone. The substrate here acts as a current spreading layer in order to try to obtain a nearly uniform carrier distribution across the device. It is worth noting that optically pumped VECSELs can contain only one DBR to provide 100% reflectance and form cavity with the external output mirror [1–3], while generally in EP-VECSELs one more DBRs stack is added to form an intracavity in order to compensate both the optical absorption loss in the thick substrate and reduce the threshold current [4-5].

In EP-VECSELs, the series resistance may limit the device performance [6]. Hence, the first design objective of this chapter is to develop a highly reflective DBR with low series resistance. The second objective is to explore the geometry of the active region inside the cavity that can provide low threshold

gain. Following this is the study of factors affecting the resonant reflectivity spectrum of the intracavity. This chapter ends with a summary.

Figure 2.1 Schematic diagram of semiconductor part of a substrate-emitting EP-VECSEL.

### 2.2 Distributed Bragg reflectors

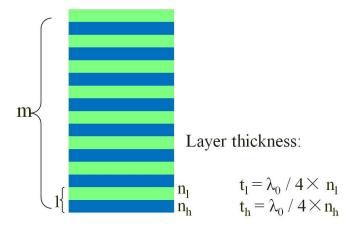

The cavity length in surface emitting semiconductor laser devices is usually a few microns thick. Thus, the single pass gain is small compared with edge emitter devices. Two distributed Bragg reflectors (DBRs) around the gain material can form an intracavity and provide sufficient amplification by strongly confining photons inside the cavity. Fig. 2.2 shows the schematic diagram of a DBR structure. It can be seen that the DBR pairs are composed of two materials with high and low refractive index and stacked periodically. DBRs can provide a high reflectance up to 100% [7] and have been widely applied in many semiconductor structures.

Figure 2.2 Schematic diagram of DBR stack made of two materials repeated in layers of a thickness of  $t_{l/h} = \lambda_0/4n_{l/h}$ .

The DBR materials used in the 980 nm EP-VECSELs described here are  $AI_{0.8}Ga_{0.2}As$  and GaAs, the thickness of each layer  $t_{l/h}$  is quarter wavelength in that material such that  $t_{l/h} = \lambda_0/4n_{l/h}$ , where  $\lambda_0$  is the emission wavelength in vacuum,  $n_{l/h}$  is the refractive index of high-index (h) or low-index (l) material consisting a DBR layer. The refractive indices of  $AI_{0.8}Ga_{0.2}As$  and GaAs are  $n_l = 3.07$  and  $n_h = 3.52$ , respectively. Hence, the quarter wavelength thickness for  $AI_{0.8}Ga_{0.2}As$  layer in each pair of DBR is 79.8 nm while the thickness for GaAs layer is 69.6 nm.

In this section, the total reflectance of the DBR versus the number of DBR pairs has been investigated. Usually the transfer matrix method (TMM) can be used for calculating the total reflectance of the multi-layer stack [8-9]. This method was implemented in CAMFR [10] software as well as a simple estimation of the peak reflectance.

Assuming normal incidence of the light, a simple equation can be used to estimate the total reflectance of the DBR which can be expressed as [11]

$$R = \left[\frac{1 - \left(\frac{n_l}{n_h}\right)^{2m}}{1 + \left(\frac{n_l}{n_h}\right)^{2m}}\right]^2, \tag{2.1}$$

where m is the number of DBR pairs.

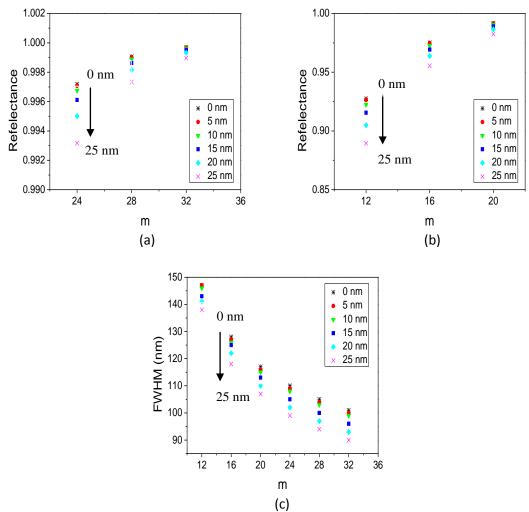

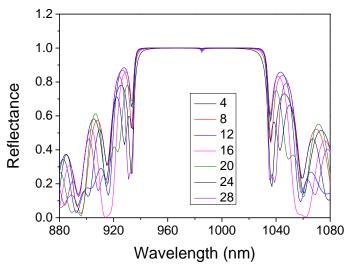

The peak reflectance has been calculated using both equation (2.1) and the TMM; and the full width at half maximum (FWHM) has been calculated using a TMM. These results are shown in Fig. 2.3(a). Fig. 2.3(b) shows reflectance spectra versus m by TMM matrix method, it also illustrates that the reflectance spectra within the stop band becomes flatter as m increases. Also, it is worth noting that all interfacial reflections will add in phase in the TMM method, while this part is not considered in equation (2.1). Therefore, the results calculated by equation (2.1) are always an under estimate as compared to result from CAMFR software.

Figure 2.3 (a) Peak reflectance calculated using (2.1) and transmission matrix method; and FWHM calculated using transmission matrix method versus m; (b) reflectance spectra as a function m ranging from 4 to 32.

It can be seen from Fig. 2.3(a) that the peak reflectance increases up to almost unity as m increases. The reflectivity increases quite rapidly when m is small. But after m exceeds 20, the reflectance increase becomes smaller as it asymptotically reaches its maximum value.

Another important characteristic from Fig. 2.3(a) is the FWHM of the reflectance spectra. The FWHM is observed to be inversely proportional to the number of DBR pairs, and it is about 100 nm wide when m exceeds  $\sim$  25. Though the larger FWHM was favoured in the design study [12], this 100 nm width is sufficient to cover the detuning between gain peak and cavity resonance wavelengths existing in the wafer which will be discussed in detail later.

The FWHM bandwidth can be approximately calculated using the following equation [13]:

$$\Delta\lambda \approx \frac{2\lambda_B \Delta \bar{n}_B}{\pi \bar{n}},$$

(2.2)

where  $\bar{n}$  =3.28 is the average refractive index value of DBR layers. It can be obtained a bandwidth  $\Delta\lambda$  about 86 nm as  $\Delta\bar{n}_B$  =0.45, which is get agreements with the value in Fig. 2.3a under. Equation 2.2 above does not show the relationship between FWHM and the number of DBR pairs. But both equation 2.1 and 2.2 indicate that materials used in DBR should have a large refractive index contrast in order to achieve high peak reflectance and wider stopband whilst keeping the number of DBR pairs small.

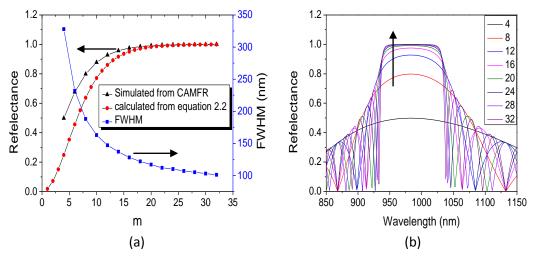

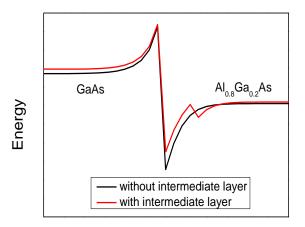

It is known that there is a difference between the Al<sub>0.8</sub>Ga<sub>0.2</sub>As and GaAs bandgap energies. As a uniform Fermi level should be generated when these two semiconductors are connected, a discontinuity of the band structure appears at the interface of these two materials. This change of band energy is schematically shown in Fig. 2.4. The band discontinuity results in a potential spike and prevents the carrier from passing through the DBR area. Therefore, the total electric resistance of the device will be increased.

Figure 2.4 Energy band discontinuities at interface of a pair of Al<sub>0.8</sub>GaAs and GaAs p-DBR.

The EP-VECSEL described here emits through the n-doped substrate and therefore the p-doped DBR needs to provide a nearly 100% reflectivity. In this case, according to the result in Fig 2.3(a), more than 30 pairs of p-doped DBR need to be epitaxially grown on the wafer. Also, the holes have lower mobility and larger free carrier absorption loss compared to electrons in the n-doped region. Thus the stack of a large number of p-doped DBR pairs may have a high resistance and can generate a large amount of Joule heating resulting in a deterioration of the device performance [14]. Therefore, the reduction of resistance in the p-DBR becomes even more important.

Many studies have been carried out and several methods have been applied to solve this problem. One of the methods is to add a layer with an intermediate Al constitution between the main layers of the DBR [15-16]. The aim of depositing this intermediate layer is to improve carrier transport in the DBRs whilst maintaining its optical characteristics. Fig. 2.5 shows the valence band energy diagram with and without the intermediate layer. It can be seen that the incorporation of the layer reduces the discontinuity of the band which results in a reduction of the total resistance of the DBR. It has been reported that a linearly graded intermediate layer in the DBR can significantly reduce the series resistance [17], but it is quite difficult to achieve the linear change of material composition in the epitaxial process. Therefore, in this work, a step intermediate layer was applied.

Figure 2.5 Energy band diagram of valence band of the DBR with and without intermediate layer.

The thicknesses of each DBR pair should remain the same in order to maintain the optical properties of the DBR. Hence, the thickness of each DBR layer will change from t (material) to  $t = t_i$  (intermediate) + t' (material). This newly added intermediate layer also requires having an average refractive

index of  $Al_{0.8}Ga_{0.2}As$  and GaAs. In this work we use  $Al_{0.47}Ga_{0.53}As$  (n=3.28) as the intermediate layer material.

The transmission matrix model was used to calculate the DBR optical characteristics with different thickness of intermediate layer, and this is shown in Fig. 2.6. The intermediate layer thickness was varied from 5 nm to 25 nm. The result indicates that the increase of intermediate layer thickness will reduce both peak reflectance and FWHM of the DBR. The intermediate layer will change the effective refractive index contrast ( $\Delta$ n) in DBR pairs. Hence, equations 2.1 and 2.2 suggest that the thicker the intermediate layer, the worse the optical characteristics of the DBRs. In order to achieve a lower resistance whilst keeping a high peak reflectance of the DBR, an  $Al_{0.47}Ga_{0.53}As$  intermediate layer with 10 nm thickness was selected for this work.

In order to meet the requirement of device, the p-doped DBR needs to provide reflectance of more than 99.9% and 90% for n-doped DBR. Thus, according to results shown in Fig. 2.6(a) and (b), 32 pairs of p-DBR and 12 of n-DBR with 10 nm of intermediate layer have been chosen.

Figure 2.6 (a) and (b) Peak reflectance. (c) FWHM versus intermediate layer thickness ranging from 5nm to 25nm.

## 2.3 Active region

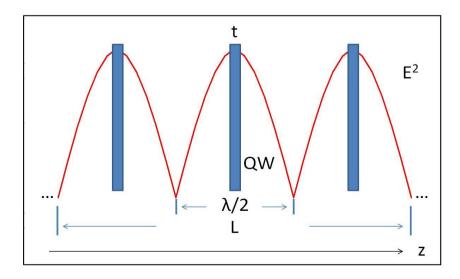

An active zone containing a periodic gain structure (PGS) is applied in the VECSEL design. In this PGS, as shown in the Fig. 2.7 below, the gain material (usually QW) has been placed at each antinode of the electric field pattern in the intracavity [18]. As the PGS is periodic, It can be obtained that the total gain material thickness  $d = n \times t$  and the total cavity length  $L = n \times (\lambda/2)$ , where n is a integer number that represents the number of PGS periods. The advantage of using this structure is that it can increase the overlap between

the gain material and electric field pattern, and, hence, reduce the threshold current of the devices [19].

Figure 2.7 Gain material with thickness t placed at each antinodes of the electric field pattern in PGS in z direction, the total gain material thickness is  $d = n \times t$  and the total cavity length  $L = n \times (\lambda/2)$ , n is a integer number, the arrow below is z direction.

In order to analyse the PGS, we start from the material gain required at the threshold g<sub>th</sub> which can be expressed as [20]

$$g_{th} = \frac{1}{\Gamma} \left( \alpha_i + \frac{1}{L} \ln \left( \frac{1}{\sqrt{R_1 R_2}} \right) \right), \tag{2.3}$$

where the  $\Gamma$  is the optical confinement factor,  $\alpha_i$  is the internal loss and L is the cavity length.  $\Gamma$  is defined as the ratio between the squared electric field in the active zone and total squared electric field [21]. As the device is a three dimensional structure,  $\Gamma$  equals to  $\Gamma_x \times \Gamma_y \times \Gamma_z$  and z axis is defined parallel to the epitaxial direction. In surface-emitting laser devices the  $\Gamma_x$   $\Gamma_y$  of the fundamental mode approaches unity.  $\Gamma_z$  is defined as the longitudinal confinement factor which is the longitudinal overlap between the gain medium and the field intensity in the cavity, and then the  $\Gamma_z$  can be expressed as [20]

$$\Gamma_Z = \frac{\int_{active} E^2(z) dz}{\int_L E^2(z) dz},$$

(2.4)

in the intracavity of EP-VECSELs [20],

$$E(z) = E_0 cos(\frac{2\pi}{\lambda}z), \tag{2.5}$$

where  $\lambda$  is the wavelength in vacuum,  $E_0$  is the amplitude.

Due to the periodicity of the PGS, we can calculate  $\Gamma_z$  in one of the  $\lambda/2$  sections. Substituting equation (2.5) into (2.4) and changing the range of integration in (2.4) yields

$$\Gamma_{Z} = \frac{\frac{d}{t} \int_{t} \cos^{2}(kz) dz}{\frac{L}{\lambda_{2}} \int_{\lambda_{2}} \cos^{2}(kz) dz}$$

$$= \frac{d}{L} \left( 1 + \frac{\sin\left[\pi\left(\frac{t}{\lambda/2}\right)\right]}{\pi\left(\frac{t}{\lambda/2}\right)} \right) \equiv \frac{d}{L} \Gamma_r, \tag{2.6}$$

where  $\Gamma_r$  is defined as the relative confinement factor.

From Fig. 2.7 it can be seen that the thickness of the gain region can be changed from 0 to  $\lambda/2$ , and then the corresponding  $\Gamma_r$  value can be in the range from 2 to 1. In the case of  $\Gamma_r$  equals 1 when  $t=\lambda/2$  meaning a continuous gain region is used in the cavity.

From the previous definition, we have  $d = n \times t$  and  $L = n \times (\lambda/2)$  for the whole intracavity. Thus it can be obtained [20]

$$\frac{d}{t} = \frac{L}{\lambda/2}. (2.7)$$

Then the equation (2.6) can be expressed as:

$$\Gamma_r = 1 + \frac{\sin(\pi \frac{d}{L})}{\pi \frac{d}{L}}.$$

(2.8)

Equation 2.8 illustrates that with the same total thickness of the gain medium; the overlap between gain material and field intensity can be doubled by dividing the gain medium into several segments with same thickness and placing them at the each antinode of electric field pattern. As a factor of two can be achieved for the optical confinement factor  $\Gamma_z$ , the threshold material gain in equation (2.1) can be reduced by a factor of two for PGS [20].

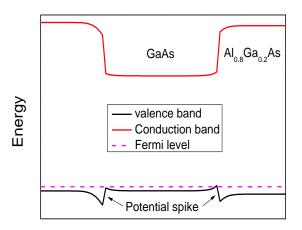

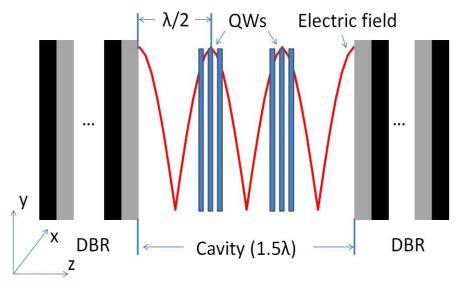

Fig. 2.8 shows a schematic diagram of the intracavity structure used in this thesis. The cavity has a length of 1.5 periods of standing wave; thus two groups of three In<sub>0.15</sub>Ga<sub>0.85</sub>As QWs can be placed at each of the antinodes of the electric field pattern in the intracavity. The QWs each have a thickness of 8 nm sandwiched by GaAs<sub>0.9</sub>P<sub>0.1</sub> barrier layer in order to achieve a balance of compressive strain [22].

Figure 2.8 Schematic diagram of cavity design with periodic gain structure (PGS) placed between two DBR for 980 nm substrate emitting EP-VECSELs.

In this case, multiple QWs are placed in one antinode of the electric field pattern. In this case, we can still get an increase of about 1.8 for relative confinement factor  $\Gamma_r$  [23]. Hence, devices with both higher gain and lower threshold gain can be achieved by using the PGS.

## 2.4 Resonant cavity wavelength

In EP-VECSELs, the intracavity is sandwiched between the two highly reflective DBRs and those two DBRs create a cavity that can resonate at a specific wavelength. As this resonant wavelength determines the emission wavelength of the device [24], it is important to study the factors effecting the resonant wavelength.

As the true layer thickness and alloy composition (if not a binary) of epitaxial laser structures are always slightly different compared to the designed thickness due to unavoidable growth errors. Therefore, thicknesses of the DBR and cavity layers are factors that can affect the resonant wavelength. It

is necessary to analyse the different epitaxial layer thickness variation on the reflectance spectra to feed back to the growth process.

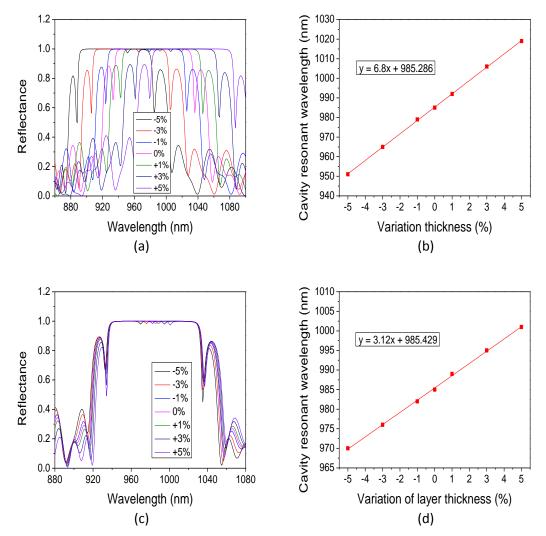

The structure contains 12 and 32 pairs of DBR at two side of the intracavity. Fig. 2.9(a) shows the reflectance spectra with growth errors in the DBR alone (i.e. the cavity is of constant thickness) with thickness variation in a range from -5% to +5%. Fig. 2.9(b) shows the corresponding cavity resonant wavelength shift rate which is 6.8 nm/%. Fig. 2.9(c) plots the reflectance spectra with constant DBR thicknesses but on error in cavity layer thickness from -5% to +5% and (d) is the corresponding cavity resonant wavelength shift rate in (c) which is 3.12 nm/%. This result indicates that growth errors of the structure will be twice as important with regard to the cavity resonant wavelength due to the operation of the DBR. Thus, a good control of the DBR layer thickness during the epitaxial process is critical for the achieving the desired wafer characteristics. On the other hand, after the wafer epitaxial process, its cavity resonant wavelength can be measured in order to estimate and compensate for any the growth error.

Figure 2.9 Reflectance spectra versus DBR and cavity layer thickness growth errors ranging from -5% to +5%: (a) Reflectance spectra versus DBR layer thickness growth errors. (b) Corresponding cavity resonant wavelengths shift rate in (a). (c) Reflectance spectra versus cavity layer thickness growth errors. (d) Corresponding cavity resonant wavelengths shift rate in (c).

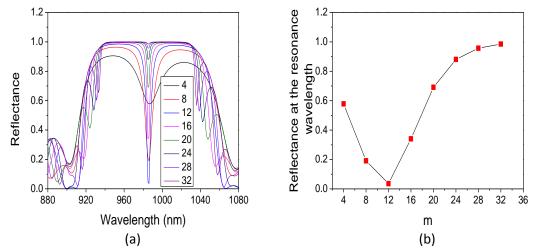

On the other hand, it is worth investigating the effect of the number of pairs of n- and p-doped DBRs on the reflectance spectra. Fig. 2.10 shows the dependence of the reflectance spectra versus the number of n-doped DBR pairs whilst keeping the p-doped DBR pairs fixed at 32 by using CAMFR software. As it can be seen, the reflectance spectra are almost constant while the numbers of n-doped pairs increase from 4 to 28. Both the reflectance stopband width and the resonant wavelength of the spectra are independent

with number of n-DBR pairs in this case. It indicates that a ~100% mirror (the p-DBR) will determine the cavity reflectance curve no matter the number of n-DBR pairs at other side of the cavity. As the high reflectance p-DBR is growth at the top of the wafer, reflectivity measurement cannot show any growth error on the number of n-DBR pairs. Therefore, the number of p-DBR pairs should be reduced in order to see the change of reflectance spectra.

Figure 2.10 Reflectance spectra of the device with 32 pairs of p-DBR versus the number of n-DBR pairs in the range from 4 to 28.

Fig. 2.11(a) shows the reflectance spectra dependence on the number of p-DBR pairs with a fixed number of 12 pairs of n-DBR. This time the reflectance spectra shape varies with the p-DBR pair number. Fig. 2.11(b) plots the corresponding reflectance at cavity resonant wavelength versus p-DBR pairs.

Figure 2.11 (a) Reflectance spectra of the device with 12 pairs of n-DBR versus the number of p-DBR pairs in the range from 4 to 32. (b) Reflectance at cavity resonant wavelength versus number of p-DBR pairs.

It can be seen from Fig. 2.11 that the cavity reflectance curve achieves a minimum value at the resonant wavelength when the number of p-DBR and n-DBR is equal to each other. To explain this effect, let us look at the transmittance of a cavity which can be expressed as [25]:

$$T = \frac{T_1 T_2}{1 + R_1 R_2 - 2\sqrt{R_1 R_2} \cos 2\Phi},\tag{2.9}$$

where T=1-R is the transmittance of the DBR and the  $\Phi$  is the phase change which can be neglected. This equation shows that the maximum of the transmittance will be achieved when the two DBR have same number of pairs:

$$T_{max} = \frac{T_1 T_2}{(1 - \sqrt{R_1 R_2})^2}. (2.10)$$

Therefore, the minimum value of DBR reflectance is obtained when both DBRs have 12 pairs. Fig. 2.11 also indicates that in order to give the wafer characteristic measurement on the number of n-DBR pairs, the two DBRs

should have the same numbers of pairs as the reflectance spectra show the most sensitivity to the number of DBR pairs. A 12 p-DBR, 12 n-DBR test structure is highlighted as being optimal in developing 980 nm GaAs, InGaAs, AlGaAs VCSELs and VECSELs.

### 2.5 Final design of the structure

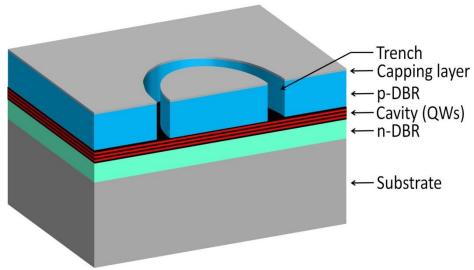

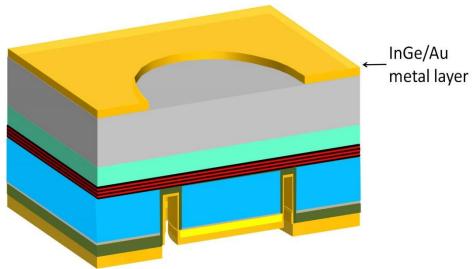

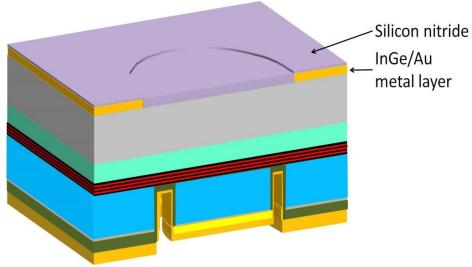

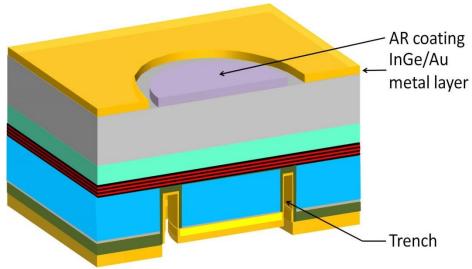

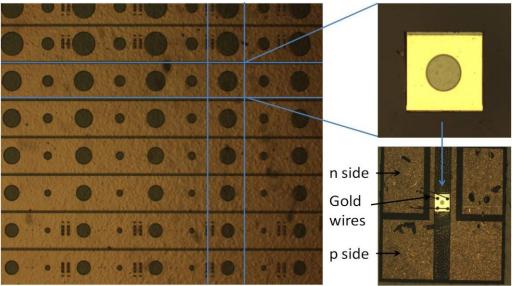

The final semiconductor chip structure for the substrate-emitting EP-VECSEL with etched trench is designed taking into account all the design conclusions drawn above. This laser structure has been manufactured at the University of Sheffield and its schematic diagram is shown Fig. 2.12 [26-27].

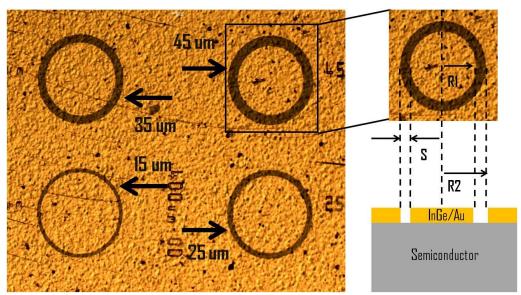

From top to bottom, the top layer is a layer of silicon nitride deposited on the GaAs substrate that acts as an AR coating to reduce the reflection at the semiconductor-air interface. The n-side InGe/Au contact layer is fabricated around the AR-coated area leaving a 5- $\mu$ m-wide gap of un-coated material between them. The GaAs substrate layer is used as the current spreading layer with a thickness of 100  $\mu$ m. It is n-doped at 1.5 × 10<sup>17</sup> cm<sup>-3</sup> to avoid high free carrier absorption loss whilst providing a low resistance.

The n-doped and p-doped DBRs with the intracavity between them are situated beneath the GaAs current spreading region. The top n-DBR contains 12 pairs of Al<sub>0.8</sub>Ga<sub>0.2</sub>As/GaAs with quarter-wave length to provide a reflectivity of 90%. The bottom p-DBR contains 32 pairs and provides a reflectance close to unity. A 10 nm Al<sub>0.47</sub>Ga<sub>0.53</sub>As intermediate layer is used in both of them. The active zone inside the cavity contains two groups of In<sub>0.15</sub>Ga<sub>0.85</sub>As quantum

wells of an 8 nm thickness placed at the antinodes of the electric field pattern and GaAs<sub>0.9</sub>P<sub>0.1</sub> barrier layers between them to provide strain compensation.

A trench is etched in the p-DBR region to confine carriers in the transverse plane across the device to enforce a uniform gain distribution across the device. A layer of SiO<sub>2</sub> dielectric is deposited upon the trench to electrically insulate the contact from the active zone inside the trench area.

Figure 2.12 Schematic illustration of the  $\lambda$  = 980 nm EP-VECSEL device (not in scale).

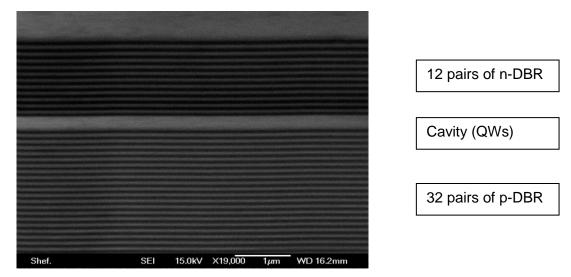

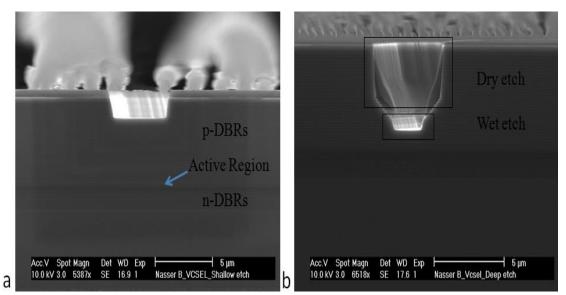

Fig. 2.13 shows a scanning electron microscope (SEM) picture of the sample's cross section with the above design. The two stacks of DBR and intracavity are clearly observed. In the next chapter, the fabrication process based on this semiconductor chip structure to make working EP-VECSELs will be discussed in detail.

Figure 2.13 The SEM image of cross-sectional of cavity and DBR regions.

#### 2.6 Summary

In this chapter, the main parts in the epitaxial structure design were introduced. Then the characteristic of DBR such as peak reflectivity and FWHM dependent on the number of DBR pairs was investigated using the transfer matrix method which was implemented using CAMFR software.

Results have shown that a 10 nm thick of Al<sub>0.47</sub>Ga0<sub>.53</sub>As intermediate layer between each of DBR material should be inserted to reduce the series resistance in the DBR whilst maintaining its optical properties. In the intracavity, the PGS was applied. It has been shown that three QWs as a group placed at the antinodes of the electric field pattern can reduce the threshold gain up to 1.8 times while provide more gain in this design.

Results also have shown that the thickness of epitaxial layers should be controlled carefully during the epitaxial process. Shifts in the cavity wavelength are more sensitive to change in the DBR thickness than the cavity itself. The devices structure with different numbers of n-and p-DBR pairs were

modelled in order to investigate their effects on the reflectance spectra. Result shows that reflectance spectra can be obtained a maximum different at centre wavelength when n and p DBR have the same pairs. This can be applied in future wafer characterisation techniques, such as detuning measurement which will be discussed in later chapters.

#### Reference

- [1] M. Kuznetsov, F. Hakimi, R. Sprague, and A. and Mooradian, "High-Power (>0.5-W CW) Diode-Pumped Vertical-External-Cavity Surface-Emitting Semiconductor Lasers with Circular TEM00 Beams," *IEEE Photonics Technol. Lett.*, vol. 5, no. 3, pp. 561–573, 1999.

- [2] M. Jacquemet, M. Domenech, G. Lucas-Leclin, P. Georges, J. Dion, M. Strassner, I. Sagnes, and a. Garnache, "Single-frequency cw vertical external cavity surface emitting semiconductor laser at 1003 nm and 501 nm by intracavity frequency doubling," *Appl. Phys. B Lasers Opt.*, vol. 86, no. 3, pp. 503–510, 2007.

- [3] H. Dyball, "New high for quantum dot VECSELs," *Electron. Lett.*, vol. 46, no. 12, p. 807, 2010.

- [4] O. G. Okhotnikov, *Semiconductor Disk Lasers: Physics and Technology*. Weinheim: Wiley-VCH Verlag GmbH & Co. KGaA, 2010.

- [5] Y. Barbarin, M. Hoffmann, W. P. Pallmann, I. Dahhan, P. Kreuter, M. Miller, J. Baier, H. Moench, M. Golling, S. Thomas, B. Witzigmann, and U. and Keller, "Electrically Pumped Vertical External Cavity Surface Emitting Lasers Suitable for Passive Modelocking," *IEEE J. Sel. Top. QUANTUM Electron.*, vol. 17, no. 6, pp. 1779–1786, 2011.

- [6] K. Kojima, R. A. Morgan, T. Mullaly, G. D. Guth, M. W. Focht, R. E. Leibenguth, and M. T. and Asom, "Reduction of p-doped mirror electrical resistance of GaAs / AlGaAs vertical-cavity surface-emitting lasers by delta doping," *Electron. Lett.*, vol. 29, no. 20, pp. 1771–1772, 1993.

- [7] R. L. Thornton, R. D. Burnham, and W. Streifer, "High reflectivity GaAs-AlGaAs mirrors fabricated by metalorganic chemical vapor deposition," *Appl. Phys. Lett.*, vol. 45, no. 10, p. 1028, 1984.

- [8] L. Brovelli and U. Keller, "Simple analytical expressions for the reflectivity and the penetration depth of a Bragg mirror between arbitrary media," *Opt. Commun.*

- [9] H. Kwong, H. Choy, and A. C. Smith, "Design and Fabrication of Distributed Bragg Reflectors for Vertical-Cavity Surface-Emitting Lasers," 1998.

- [10] P. Bienstman, "CAMFR manual v1.3." pp. 1–70.

- [11] M.Born and E. Wolf, *Principles of Optics*. 1986.

- [12] H.E.Li K.Iga, *Vertical-Cavity Surface-Emitting Laser Devices*. Springer-Verlag Berlin Heidelberg GmbH, 2003.

- [13] A. N. Zhiming M. Wang, *Nanoscale Photonics and Optoelectronics*. Springer Science+Business Media, 2010.

- [14] G. W. Yoffe, "Rectification in heavily doped p-type GaAs/AlAs heterojunctions," *J. Appl. Phys.*, vol. 70, no. 2, pp. 1081–1083, 1991.

- [15] M. Hong, J. P. Mannaerts, J. M. Hong, R. J. Fischer, K. Tai, J. Kwo, J. M. Vandenberg, Y. H. Wang, and J. Gamelin, "A simple way to reduce series resistance in p-doped semiconductor distributed Bragg reflectors," *J. Cryst. Growth*, vol. 111, pp. 1071–1075, 1991.

- [16] K. Tai, L. Yang, Y. H. Wang, J. D. Wynn, and a. Y. Cho, "Drastic reduction of series resistance in doped semiconductor distributed Bragg reflectors for surface-emitting lasers," *Appl. Phys. Lett.*, vol. 56, no. 18, pp. 2496–2498, 1990.

- [17] M. Linnik and A. Christou, "Effects of Bragg mirror interface grading and layer thickness variations on VCSEL performance at 1.55 μm," *Proc. SPIE*, vol. 4286, pp. 162–171, 2001.

- [18] M. Y. a Raja, S. R. J. Brueck, M. Osinski, C. F. Schaus, J. G. McInerney, T. M. Brennan, and B. E. Hammons, "Resonant periodic gain surfaceemitting semiconductor lasers," *IEEE J. Quantum Electron.*, vol. 25, no. 6, pp. 1500–1512, 1989.

- [19] M. Y. a Raja, S. R. J. Brueck, M. Osiński, C. F. Schaus, J. G. McInerney, T. M. Brennan, and B. E. Hammons, "Surface-emitting, multiple quantum well GaAs/AlGaAs laser with wavelength-resonant periodic gain medium," *Appl. Phys. Lett.*, vol. 53, no. 1988, pp. 1678–1680, 1988.

- [20] S. W. Corzine, R. S. Geels, J. W. Scott, R. H. Yan, and L. A. and Coldren, "Design of Fabry-Perot Surface-Emitting Lasers with a Periodic Gain Structure," *IEEE J. Quantum Electron.*, vol. 25, no. 6, pp. 1513– 1524, 1989.

- [21] Y. Z. Huang, Z. Pan, and R. H. Wu, "Analysis of the optical confinement factor in semiconductor lasers," *J. Appl. Phys.*, vol. 79, no. 8, pp. 3827–3830, 1996.

- [22] G. Zhang and A. Ovtchinnikov, "Strain-compensated InGaAs/GaAsP/GaInAsP/GaInP quantum well lasers ( $\lambda \sim 0.98~\mu m$ ) grown by gas-source molecular beam epitaxy," *Appl. Phys. Lett.*, vol. 62, no. 14, pp. 1644–1646, 1993.

- [23] Rainer Michalzik, VCSELs: Fundamentals, Technology and Applications of Vertical-Cavity Surface-Emitting Lasers, vol. 166. Springer-Verlag Berlin Heidelberg, 2013.

- [24] D. B. Young, J. W. Scott, F. H. Peters, M. G. Peters, M. L. Majewski, B. J. Thibeault, S. W. Corzine, and L. a. Coldren, "Enhanced performance of offset-gain high-barrier vertical-cavity surface-emitting lasers," *IEEE J. Quantum Electron.*, vol. 29, no. 6, pp. 2013–2022, 1993.

- [25] E.Fred Schubert, *Light Emitting Diodes*. Cambridge University Press, 2003.

- [26] J. R. Orchard, D. T. D. Childs, D. Williams, L.-C. Lin, B. J. Stevens, J. S. Roberts, and R. a. Hogg, "Trade-offs in the realization of electrically pumped vertical external cavity surface emitting lasers," *Semicond. Laser Conf. (ISLC), 2010 22nd IEEE Int.*, vol. 17, no. 6, pp. 1745–1752, 2010.

- [27] X. Jin, P. Ivanov, D. T. D. Childs, N. Babazadeh, J. Orchard, B. Stevens and R.A. Hogg, "Optimisation of Fundamental Transverse Mode Output in Electrically Pumped Vertical External Cavity Surface Emitting Lasers," *Proc SPIE*, vol. 9349, 2015.

# 3. Devices Fabrication Process and

# **Improvement**

# 3.1 Introduction

In this chapter, first the EP-VECSEL device fabrication process will be introduced in detail. Then improvements in trench etching and deposition of the silicon dioxide dielectric layer process will be discussed. Next the circular transmission line model (CTLM) measurement results are discussed with regard to optimising the annealing temperature during the process, towards realising low resistance devices.

## 3.2 Fabrication process

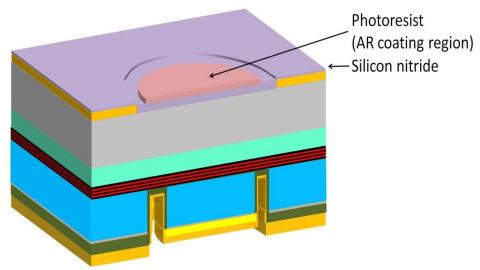

The fabrication process of EP-VECSELs will be described step by step in this section. To start with, one part of the sample (about ~1/6<sup>th</sup> of a 2 inch wafer) is cleaved from the wafer using a diamond tipped scriber. Then an optical microscope is used to check the wafer surface for defects and dirt. After that cotton buds were used to clean the excess dirt off of the wafer by using warm n-butyl acetate, acetone, and isopropyl alcohol (IPA) solution in order. This method is called a 3-stage clean and will be used in later cleaning steps, but the cotton buds are only used in this step. After each 3-stage clean the sample is checked using a microscope. This clean step is repeated until there is less than one particle per field of view on 100x magnification under the microscope. Fig. 3.1 shows an example epitaxial structure with the key

#### features labeled.

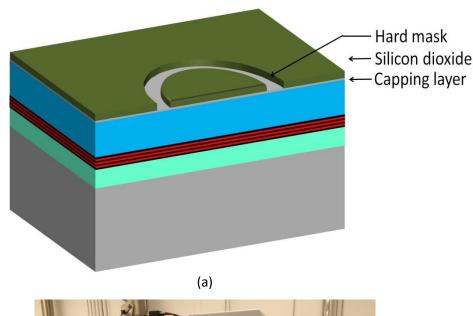

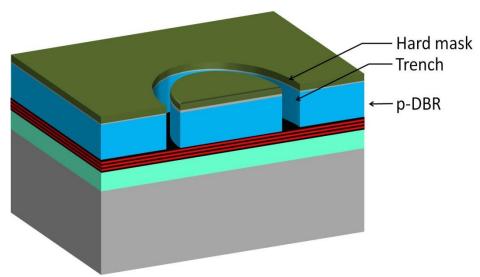

Figure 3.1 Epitaxial structure of the wafer grown by MOCVD (not to scale).

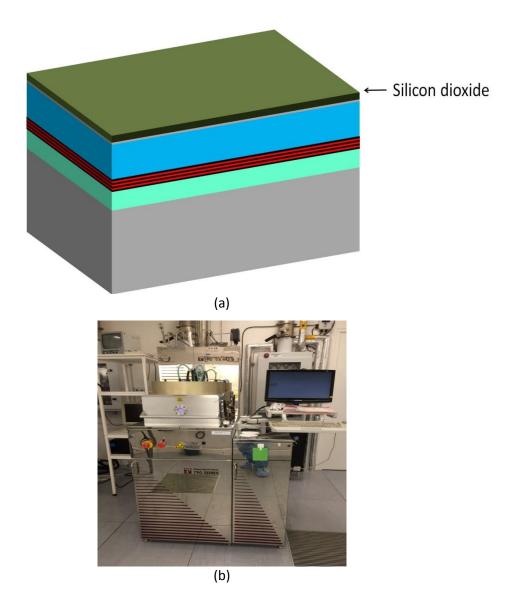

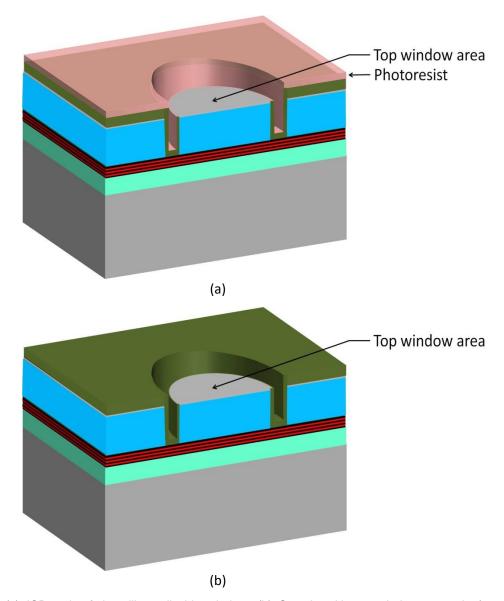

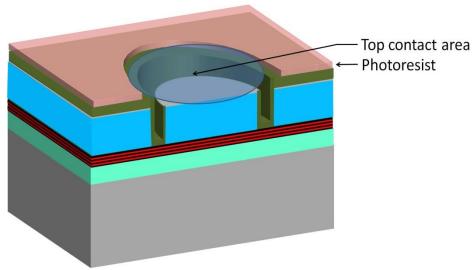

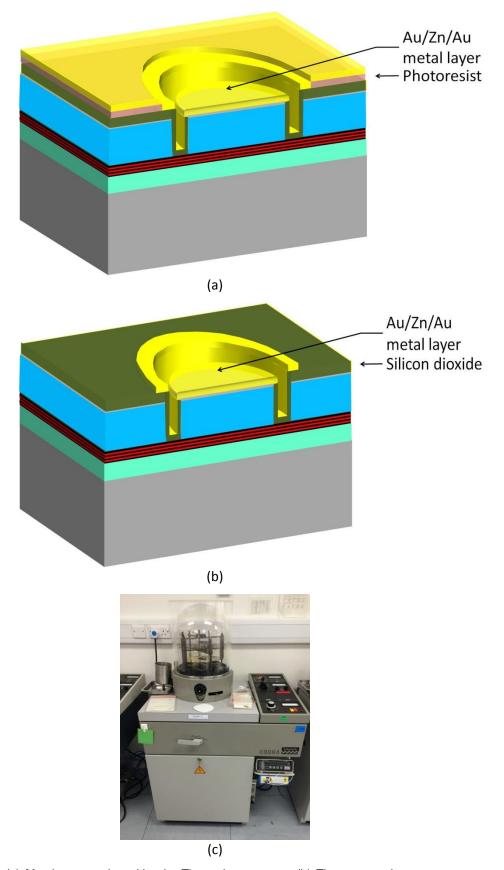

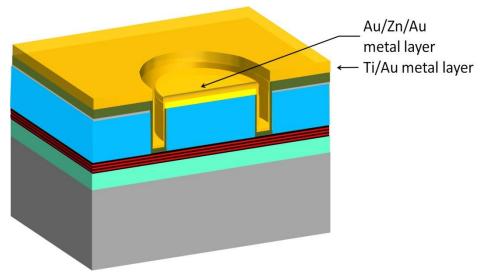

The epi-side fabrication process commenced with the deposition of a layer of silicon dioxide as a hard mask for future trench etching. The use of this hard mask can provide a straight sidewall during trench etching because photoresist may distort due to the high temperature generated during the etching process. Before the deposition of silicon dioxide the sample is cleaned in the O<sub>2</sub> plasma asher for 3 minutes in order to remove dust on the sample surface. Then the sample is placed in 19:1, DIW: Annular Ammonia solution for 30s to remove the surface oxide, then rinsed in DI water and blown dry using the nitrogen blow gun. The sample is now clean and ready for the oxide deposition.

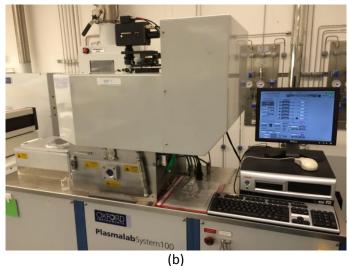

Plasma-enhanced chemical vapour deposition (PECVD) was used to deposit ~ 400 nm thick silicon dioxide on the epi-side (p-doped). This is shown schematically in Fig. 3.2(a). The PECVD in our cleanroom is shown in Fig. 3.2(b). In order to make sure the deposited silicon dioxide is without impurities, a clean and preparation step is needed due to other unwanted materials that may be left in the chamber by other deposition recipes run previously.

Figure 3.2 (a) Deposition of silicon dioxide by PECVD. (b) PECVD in the cleanroom of the University of Sheffield.

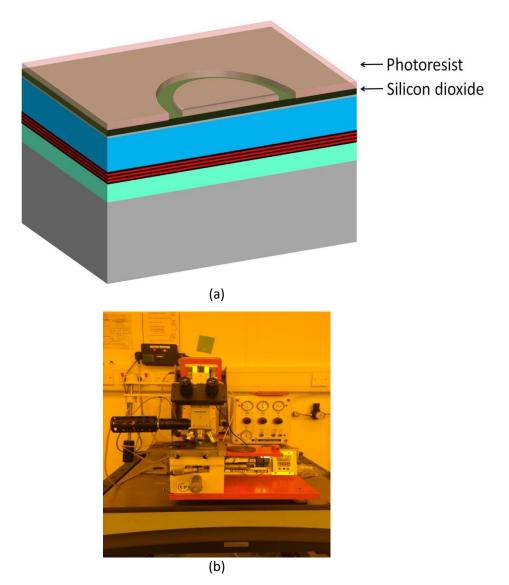

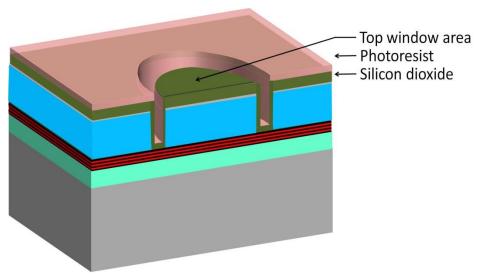

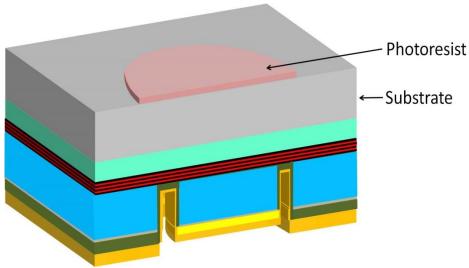

After silicon dioxide deposition the next step was photolithography to define the hard mask pattern. This photoresist pattern is shown in Fig. 3.3(a). First a 3-stage clean was used and then blown dry, but in order to make sure that no residual solvent is left on the sample surface, the sample needs to be placed on hotplate at 100 °C for 1 minute to dry the sample surface. The sample was then put on the vacuum chuck of the spinner by sticking on to a piece of blue tacky paper and spun at 4000 rpm. A nitrogen blow gun was used to clean any dirt and residual particle from the surface and then the sample is covered

with hexamethyl disilizane (HMDS) which is an adhesion promoter for photoresist to ensure good adhesion on the silicon dioxide surface. The next step was to spin photoresist (SPR350) on the sample. Once deposited on the sample the sample is spun for another 30 seconds at 4000 rpm in order to get the required deposition thickness across the wafer surface. After that the sample was baked on the hotplate at 100 °C for another 1 minute to drive off the solvent from the photoresist leaving a firm layer of photoresist. However spinning the sample on spinner also causes an edge bead which means a greater thickness of photoresist at the edges of the wafer. A scrap wafer was used to cover the wafer and expose the edges to UV light. This exposure time should be 4-5 times longer than the standard exposure time for that photoresist in order to remove all the resist at the edges. After this the sample is developed in MF26a developer for 1 minute, then rinsed in DI water and dried.

The trench etch mask was put into the mask aligner and the sample loaded into the aligner. After the sample was aligned it can then be exposed to UV light with a controlled exposure time. Once exposed the sample is then developed for 1 minute, rinsed in DI water and blown dry. The exposure result and alignment accuracy of the sample was checked under the optical microscope. There must be no photoresist left in the trenches and the alignment marks on the sample should be clear. Fig. 3.3(b) shows the mask aligner used in the University of Sheffield.

Figure 3.3 (a) The hard mask pattern defined by the photoresist. (b) Mask aligner in the cleanroom of the University of Sheffield.

The next step was using inductively coupled plasma (ICP) etching to transfer the trench pattern from the photoresist to the dielectric layer which can be seen in the Fig. 3.4(a), with the photo of ICP used in the cleanroom in Fig. 3.4(b). Firstly the ICP was prepared using the cleaning programme for 10 minutes and then another 10 minutes to run the etch programme without a sample for preparation. After that the sample was put into the chamber with a tiny amount of fomblin oil on the back of the sample to give good heat dissipation. The etch recipe consisted of a gas flow of CHF<sub>3</sub> of 20 sccm and

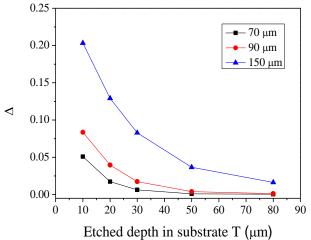

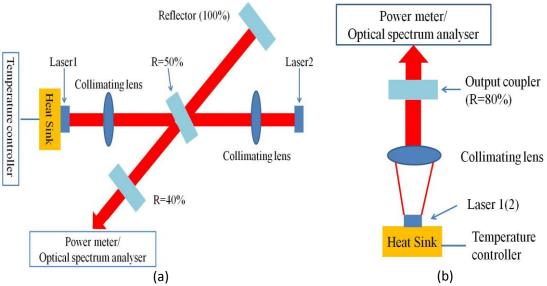

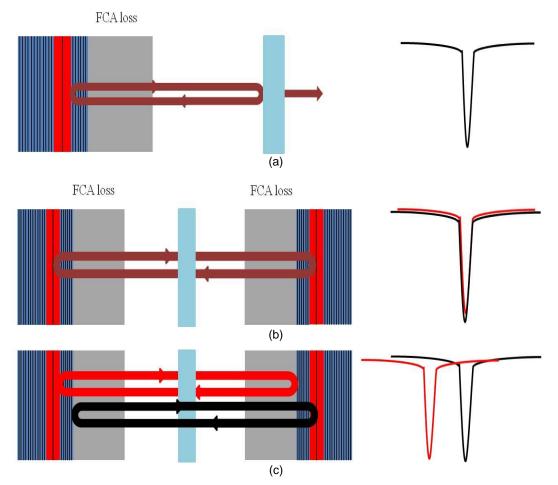

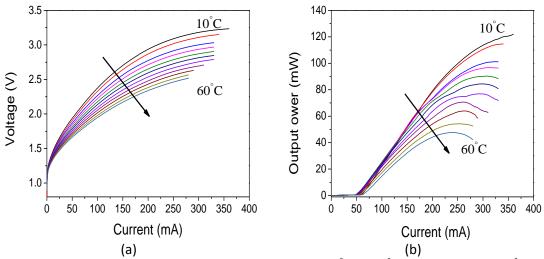

$Ar_2$  of 30 sccm, with RF power of 150 W and ICP 200 W, at a pressure of 25 mT at 20°C. The etch time is dependent on the required etch depth and in this case for 400 nm of silicon dioxide is about 25 minutes. After etching an optical microscope was used to check the quality of the etching. If the trenches are clear of silicon dioxide then the photoresist can be removed.