# High Performance Real-Time Scheduling Framework for Multiprocessor Systems

NAN CHEN

# PhD

UNIVERSITY OF YORK COMPUTER SCIENCE

October 2023

# Abstract

Embedded systems, performing specific functions in modern devices, have become pervasive in today's technology landscape. As many of these systems are real-time systems, they necessitate operations with stringent time constraints. This is especially evident in sectors like automotive and aerospace. This thesis introduces a High Performance Real-time Scheduling (HPRTS) framework, which is designed to navigate the multifaceted challenges faced by multiprocessor real-time systems.

To begin with, the research attempts to bridge the gap between system reliability and resource sharing in Mixed-Criticality Systems (MCS). In addressing this, a novel fault-tolerance solution is presented. Its main goal is to enhance fault management and reduce blocking time during fault tolerance. Following this, the thesis delves into task allocation in systems with shared resources. In this context, we introduce a distinct Resource Contention Model (RCM). Using this model as a foundation, our allocation strategy is formulated with the aim to reduce resource contention. Moreover, in light of the escalating system complexity where tasks are represented using Directed Acyclic Graph (DAG) models, the research unveils a new Response Time Analysis (RTA) for multi-DAG systems. This particular analysis has been tailored to provide a safe and more refined bound.

Reflecting on the contributions made, the achievements of the thesis highlight the potency of the HPRTS framework in steering real-time embedded systems toward high performance.

# Contents

| A        | bstra | $\mathbf{ct}$ |                                     | 1        |

|----------|-------|---------------|-------------------------------------|----------|

| Li       | st of | Tables        | 5                                   | <b>5</b> |

| Li       | st of | Figure        | es                                  | 7        |

| A        | cknov | wledgn        | nent                                | 8        |

| D        | eclar | ation         |                                     | 9        |

| 1        | Intr  | oducti        | ion                                 | 10       |

|          | 1.1   | Motiva        | ation                               | 11       |

|          | 1.2   | Thesis        | Aim                                 | 13       |

|          | 1.3   | Thesis        | Hypothesis                          | 15       |

|          | 1.4   | Succes        | ss Criteria and Contributions       | 16       |

|          | 1.5   | Thesis        | Outline                             | 17       |

| <b>2</b> | Rev   | view of       | Existing Literature                 | 18       |

|          | 2.1   | Gener         | al Definitions of Real-Time Systems | 19       |

|          |       | 2.1.1         | Real-Time Task and System Models    | 19       |

|          |       | 2.1.2         | Task Scheduling Mechanisms          | 23       |

|          |       | 2.1.3         | Schedulability Analysis             | 27       |

|          |       | 2.1.4         | Summary                             | 30       |

|          | 2.2   | Resou         | rce Sharing in Real-Time Systems    | 30       |

|          |       | 2.2.1         | Shared Resources                    | 31       |

|          |       | 2.2.2         | Lock-Based Mechanisms               | 32       |

|          |       | 2.2.3         | Resource Sharing Protocols          | 36       |

|          |       |               |                                     |          |

|   |     | 2.2.4   | RTA for Shared Resources                           | 41  |

|---|-----|---------|----------------------------------------------------|-----|

|   |     | 2.2.5   | Summary                                            | 51  |

|   | 2.3 | Real-7  | Fime Mixed Criticality Systems                     | 51  |

|   |     | 2.3.1   | Definitions of MCS                                 | 52  |

|   |     | 2.3.2   | Conventional MCS Model                             | 53  |

|   |     | 2.3.3   | Fault Tolerance Approaches                         | 55  |

|   |     | 2.3.4   | Fault-Tolerance and Shared Resources in MCS        | 58  |

|   |     | 2.3.5   | Summary                                            | 61  |

|   | 2.4 | Task A  | Allocation Methods                                 | 61  |

|   |     | 2.4.1   | Evolution of Task Allocation Methods               | 62  |

|   |     | 2.4.2   | Resource-Aware Task Allocation Methods             | 63  |

|   |     | 2.4.3   | Summary                                            | 68  |

|   | 2.5 | DAG     | Tasks in Real-Time Systems                         | 69  |

|   |     | 2.5.1   | Generic DAG Task Model                             | 69  |

|   |     | 2.5.2   | DAG Task Scheduling                                | 72  |

|   |     | 2.5.3   | RTA for DAG Tasks                                  | 78  |

|   |     | 2.5.4   | Summary                                            | 86  |

|   | 2.6 | Summ    | ary of Existing Literature                         | 87  |

| 3 | Rel | iable F | Resource Sharing in Mixed-Criticality Systems      | 89  |

|   | 3.1 | A Fau   | lt-Tolerant Solution for MCS with Shared Resources | 90  |

|   |     | 3.1.1   | The Proposed System Model                          | 91  |

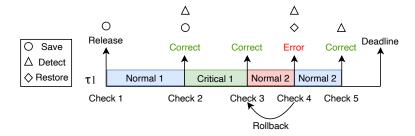

|   |     | 3.1.2   | Fault-Tolerance of Normal Sections                 | 92  |

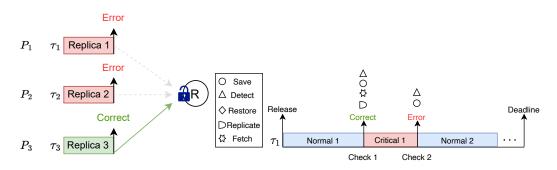

|   |     | 3.1.3   | Fault-Tolerance of Critical Sections by MSRP-FT    | 94  |

|   | 3.2 | Sched   | ulability Analysis                                 | 100 |

|   |     | 3.2.1   | Analysis of Systems with A Stable Mode             | 100 |

|   |     | 3.2.2   | Analysis of Systems under A Mode Switch            | 108 |

|   | 3.3 | Evalua  | ation                                              | 109 |

|               | 3.4   | Summary                                                                                                                             | 6  |

|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 4             | Cor   | ention-Aware Task Allocation 117                                                                                                    | 7  |

|               | 4.1   | Resource Contention Model                                                                                                           | 8  |

|               | 4.2   | Contention-Aware Task Allocation                                                                                                    | 21 |

|               |       | 4.2.1 Task Grouping Based on Resource Contention                                                                                    | 2  |

|               |       | 4.2.2 Allocation of Task Groups on Processors $\ldots \ldots \ldots \ldots 12^4$                                                    | 4  |

|               | 4.3   | Evaluation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $12'$                                            | 27 |

|               |       | 4.3.1 Experimental Setup                                                                                                            | 27 |

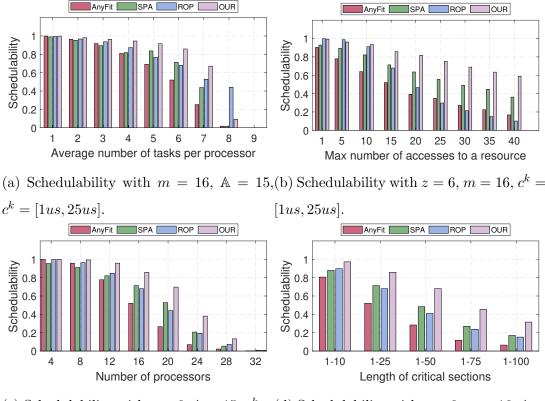

|               |       | 4.3.2 Performance Evaluation for Homogeneous Architecture 129                                                                       | 9  |

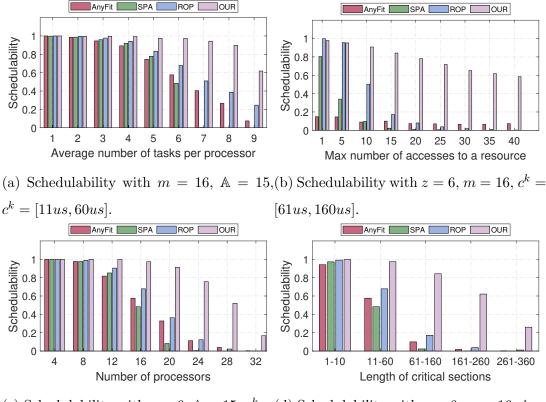

|               |       | 4.3.3 Performance Evaluation for Heterogeneous Architecture 132                                                                     | 2  |

|               | 4.4   | Summary $\ldots \ldots 13^{4}$    | 4  |

| <b>5</b>      | Pre   | ise Response Time Analysis for Multiple DAG Tasks 136                                                                               | 6  |

|               | 5.1   | Response Time Analysis for DAG Tasks                                                                                                | 7  |

|               |       | 5.1.1 RTA for Single-DAG Systems                                                                                                    | 8  |

|               |       | 5.1.2 RTA for Multi-DAG Systems                                                                                                     | :5 |

|               | 5.2   | Evaluation                                                                                                                          | :6 |

|               |       | 5.2.1 Evaluation for Single-DAG Systems                                                                                             | :8 |

|               |       | 5.2.2 Evaluation for Multi-DAG Systems                                                                                              | 2  |

|               | 5.3   | Summary $\ldots \ldots 154$       | 4  |

| 6             | Cor   | clusion 150                                                                                                                         | 6  |

|               | 6.1   | Contributions $\ldots \ldots 15'$ | 7  |

|               | 6.2   | Future Research                                                                                                                     | 0  |

|               | 6.3   | Concluding Remarks                                                                                                                  | 5  |

| $\mathbf{Li}$ | st of | Abbreviations 160                                                                                                                   | 6  |

# List of Tables

| Table of Notations for Real-Time Tasks and Models22                   |

|-----------------------------------------------------------------------|

| Notations of Shared Resources                                         |

| Table of Notations for Original MSRP    44                            |

| Table of Notations for Advanced MSRP    49                            |

| Table of Notations for Advanced MSRP $(B_i)$                          |

| Notations for MCS                                                     |

| List of Notations for DAG Task                                        |

| Notations for Bounding the Resource Accessing Time 104                |

| Table of Notations for RCM    121                                     |

| Table of Notations for Task Allocation Algorithm                      |

| Computation cost (in ms) with $\mathbb{A} = 15$ , $c^k = [1us, 25us]$ |

| Table of Notations for Single DAG Anlaysis                            |

| The Comparison of Makespan with He2021                                |

| The Comparison of Makespan with Serrano2016                           |

|                                                                       |

# List of Figures

| 1  | The execution chart for priority inversion                    |

|----|---------------------------------------------------------------|

| 2  | The execution chart for tasks under PCPs                      |

| 3  | The back-to-back hit                                          |

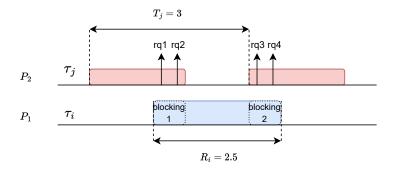

| 4  | Resource contention analysis for one shared resource          |

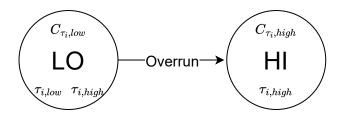

| 5  | The AMC model                                                 |

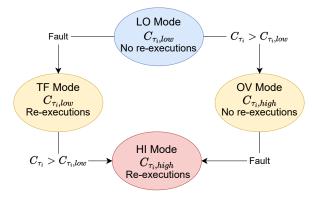

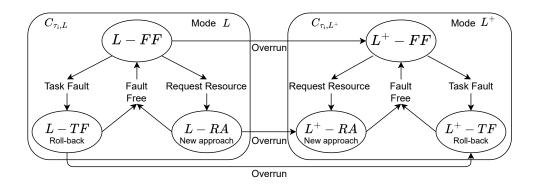

| 6  | The four-mode model $[1]$                                     |

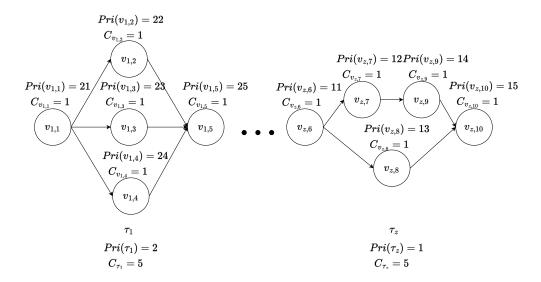

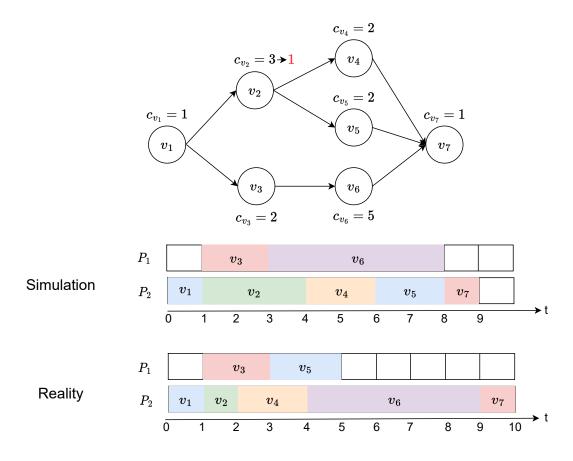

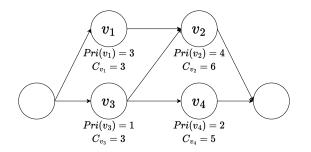

| 7  | An example of multiple DAG tasks                              |

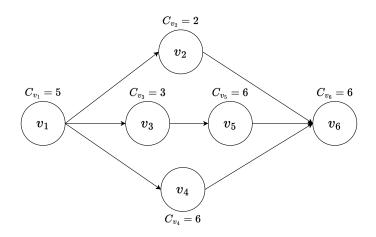

| 8  | An example of a DAG task $\tau_i$                             |

| 9  | An example of timing anomaly                                  |

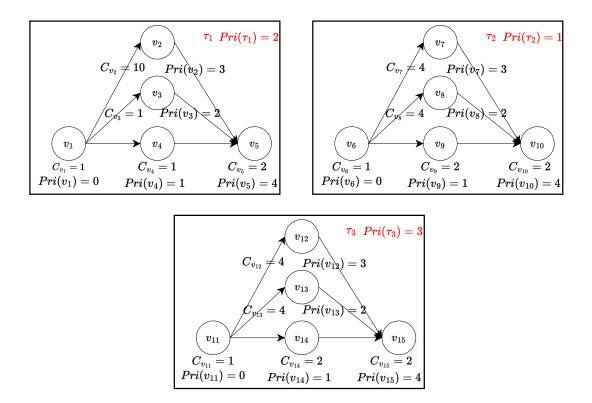

| 10 | Three DAG tasks with different priorities                     |

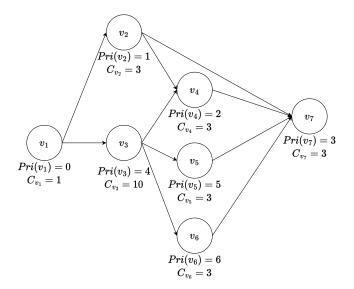

| 11 | An example of a DAG                                           |

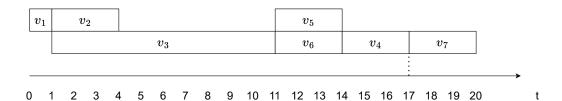

| 12 | The simulation graph of the DAG in Figure 11                  |

| 13 | The proposed system model                                     |

| 14 | Fault-tolerance in normal sections                            |

| 15 | Fault tolerance in critical sections                          |

| 16 | Fault-tolerance in a critical section                         |

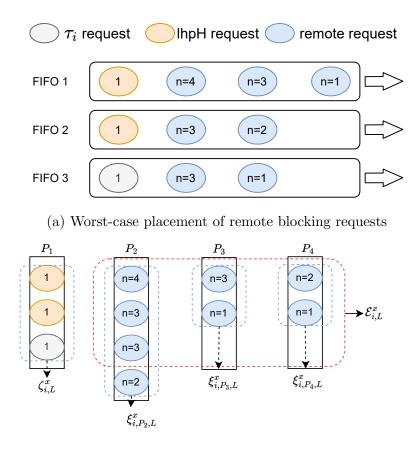

| 17 | A comparison between two fault-tolerance approaches under the |

|    | same checkpoints setting                                      |

| 18 | Worst-case spin delay                                         |

| 19 | LO mode                                                       |

| 20 | HI mode                                                       |

| 21 | Mode switch                                                   |

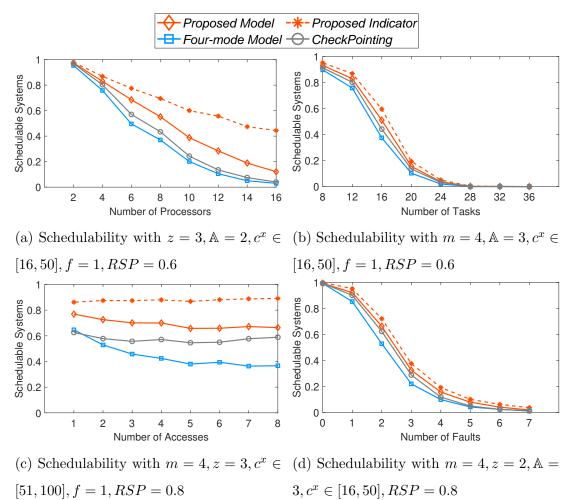

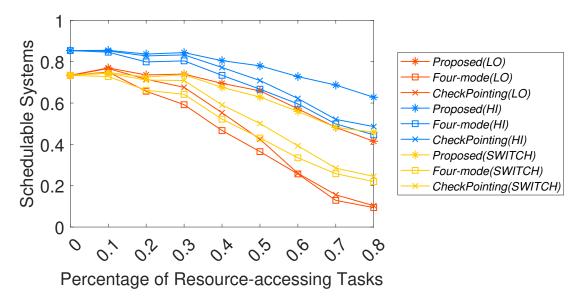

| 22 | Schedulability with $m = 6, z = 3, A = 3, c^x \in [51, 100]$  |

| 23 | Homogeneous schedulability figures                            |

| 24 | Heterogeneous schedulability figures                          |

| 25 | An example of the interference-free execution                                                                                                     |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 26 | An example of a DAG task                                                                                                                          |

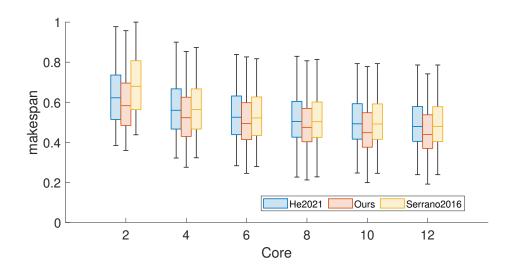

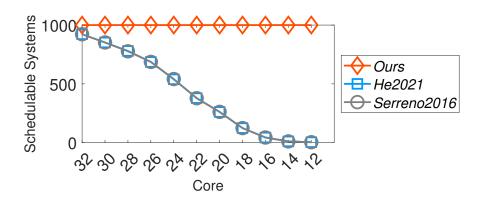

| 27 | The makespan of a single DAG with varied $m$ , Parallelism = 8                                                                                    |

|    | and Length = $7149$                                                                                                                               |

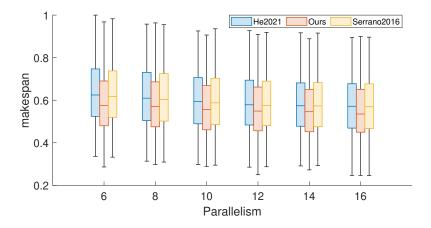

| 28 | The makespan of a single DAG with varied degree of parallelism,                                                                                   |

|    | m = 6 and Length = 7                                                                                                                              |

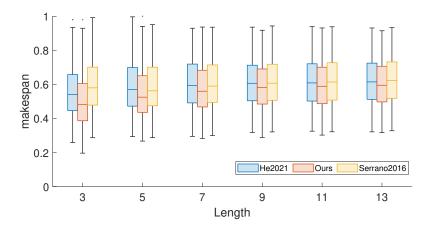

| 29 | The makespan of a single DAG with varied length, $m = 6$ , and                                                                                    |

|    | $Parallelism = 12. \dots \dots$             |

| 30 | The system schedulability for multi-DAGs under a varied $m$ , Par-                                                                                |

|    | allelism = 6, and Length = 6. $\dots \dots \dots$ |

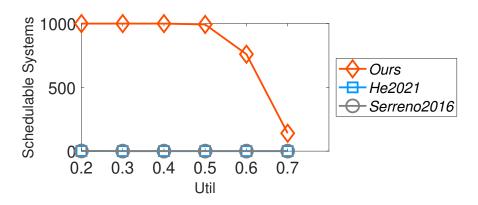

| 31 | The system schedulability for multi-DAGs under varied $\frac{\sum U}{m}$ , $m =$                                                                  |

|    | 4, Parallelism = 6, and Length = $6. \ldots 153$                                                                                                  |

# Acknowledgment

I extend my heartfelt gratitude to the University of York for seven transformative years, transitioning from undergraduate to doctoral studies.

My deepest appreciation goes to my supervisors: Prof. Alan Burns, Prof. Wanli Chang, and Dr. Siyuan Ji. Their unwavering support and expertise have been instrumental in my academic journey.

I am profoundly thankful to Dr. Zhishan Guo for his role as my external examiner. His insights and thorough examination have significantly contributed to the depth and quality of this research.

I am also grateful to the Real-Time Distributed Systems group, including Ian Gray, Iain Bate, Shuai Zhao, Xiaotian Dai, Jie Zou, Haitong Wang, and others. Their collaboration and feedback have been invaluable. Special mention to Shuai Zhao for our joint achievements and to Ian Gray for his insightful thesis review.

To my parents, your unwavering support and sacrifices have been the foundation of my academic success. I also thank my friends: Xinyi Hu, Zhiheng Hu, and Qianyi Xu, for their constant emotional support.

In closing, my sincere thanks to everyone who contributed to this research. Your collective efforts have made this thesis possible.

# Declaration

I declare that the work presented in this thesis is entirely my own creation. While some portions of the content have been featured in published articles, submissions, and other formal documents, they are explicitly detailed as follows:

- W. Chang, S. Zhao, S. Burton, T. Chen, N. Chen, N. Audsley. Hardware/-Software Co-Synthesis and Co-Optimization for Autonomous Systems. *Design Automation Conference (DAC)*. 2021.

- N. Chen, S. Zhao, I. Gray, A. Burns, S. Ji, W. Chang. MSRP-FT: Reliable Resource Sharing on Multiprocessor Mixed-Criticality Systems. *Real-Time and Embedded Technology and Applications Symposium (RTAS)*. 2022

- N. Chen, S. Zhao, I. Gray, A. Burns, S. Ji, W. Chang. Precise Response Time Analysis for Multiple DAG Tasks with Intra-task Priority Assignment. *Real-Time and Embedded Technology and Applications Symposium (RTAS)*. 2023.

- W. Chang, N. Chen, S. Zhao, X. Dai. Evolvement of Scheduling Theories for Autonomous Vehicles. Book Chapter. Springer. 2023.

- G. Xie, Y. Zhang, N. Chen, W. Chang. A High-Flexibility CAN-TSN Gateway with a Low-Congestion TSN-to-CAN Scheduler. *Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD).* 2023.

- S. Zhao, N. Chen, Y. Fang, Z. Li, W. Chang. A Universal Method for Task Allocation on FP-FPS Multiprocessor Systems with Spin Locks. *Design Automation Conference (DAC)*. 2023.

This work has not been previously submitted for an award at this or any other university. All sources have been duly acknowledged as references.

# Chapter 1 Introduction

Embedded systems are computer systems integrated into other devices or products to perform specific functions. According to [90], embedded systems can be described as a combination of hardware and software components that work together to control the device or product it is integrated with. The hardware component includes a microprocessor or microcontroller and various peripheral devices, such as sensors, actuators, and memory. The software component includes an operating system and applications, which control the hardware and provide the necessary functionality for the system to perform its designated task. As the field of embedded systems continues to evolve, new developments in technology are driving innovation in this area. For example, the increasing use of wireless communication technologies, such as Wi-Fi and Bluetooth, and the growth of the Internet of Things (IoT) are enabling the development of new types of embedded systems that can interact with other devices and systems [85].

Many embedded systems are designed to operate in real-time environments. Real-time systems are characterized by their ability to respond to inputs and events within strict time constraints, making them ideal for use in critical applications where timely and accurate processing is required [30]. The integration of embedded systems with real-time capabilities is critical in industries, such as automotive, aerospace, and telecommunications [46]. For example, in the automotive industry, embedded systems are used in real-time to control various systems within the vehicle, such as engine management and safety systems, to ensure reliable and efficient operation [32].

In a real-time system, tasks that fail to complete within the allotted time

are referred to as *deadline miss*. According to the cost of the outcome, realtime systems can be broadly categorized as *hard* or *soft*. Hard real-time systems have zero tolerance for *deadline miss* and the occurrence of one will result in the complete failure of the system and have catastrophic consequences. Conversely, *deadline miss* in soft real-time systems generally do not result in severe outcomes, but persistent missed deadlines will affect the Quality of Service (QoS) of the system. Taking the example of an embedded system in an automobile, a *deadline miss* in the multimedia system will only result in a subpar customer experience. However, if the Anti-lock Braking System (ABS), which prevents the vehicle from losing control due to locked brakes, experiences a *deadline miss*, the consequences can be devastating, potentially leading to loss of life.

## 1.1 Motivation

Driven by applications such as autonomous vehicles, spacecraft, robotics, and industrial automation, real-time systems are required to implement ever more complex functionalities with high performance while maintaining conventional timing predictability, reliability, and cost-effectiveness. These systems often contain a large number of shared resources, including elements like memory sections, data structures, Input/Output (I/O) devices, storage media, network sockets, and hardware components, all of which require coordinated mechanisms such as locks and semaphores [50] to ensure mutually exclusive access. This coordination is crucial for maintaining data integrity and system stability while preventing conflicts and ensuring efficient, reliable operations. However, the need for mutually exclusive access to shared resources can lead to blocking due to contention. In this context, the conventional requirements of timing predictability and reliability still need to be satisfied. That is, the deadlines of tasks must be met while failures during task executions must be resolved which is particularly hard. Several multiprocessor resource-sharing protocols have been proposed to bound and minimize blocking time, including Multiprocessor Stack Resource Protocol (MSRP) [41] and Multiprocessor resource sharing Protocol (MrsP) [22]. However, reliability has not been accounted for i.e., handling task faults, which is imperative in mission-critical scenarios. Existing fault-tolerance methods are based on redundancy, and they may be directly applied to shared resources by scheduling repeated task executions and resource accesses a sufficient number of times to get the correct output. However, this leads to severe resource contention and undermines system schedulability.

To address the issue of resource contention across processors, there has been significant focus on resource-aware task allocation in fully-partitioned multiprocessor systems. There are many resource-aware task allocation methods available, as cited in [48,49,55,62,97]. These methods cater to various scheduling techniques and resource-sharing protocols, such as Fixed-Priority Scheduling (FPS) and the MSRP [42]. Unlike conventional allocation methods such as Worst-Fit (WF) and Best-Fit (BF), these methods focus on discovering the resource-access relationships between tasks and reduces contention by localizing the shared resources. They can be generally categorized into two major approaches, which execute critical sections (i) on the host processor of tasks or (ii) on dedicated processors. The first approach aims to allocate tasks with the same shared resources to one processor to reduce contention. However, for complex systems with intensive resource sharing, the methods in this approach become ineffective due to the utilization of coarse-grained analysis of contention levels between tasks [49,62,97]. The second approach circumvents the aforementioned issues by designating a set of processors specifically for resource access. Yet, this approach relies on a search-based method, aided by schedulability tests, which results in high computation times. Additionally, it introduces extra migration overhead

and is less advantageous with frequent resource accesses [109].

Furthermore, as system complexity increases, tasks may need to adhere to specific execution orders due to functional dependencies between them. These dependencies are represented using Directed Acyclic Graph (DAG) models. For optimal performance, multiple DAGs must be scheduled, and their Worst-Case Response Times (WCRT) must be bounded. This schedulability analysis during the design phase is crucial for estimating the necessary hardware resources. Research into the Response Time Analysis (RTA) of DAGs encompasses a broad spectrum of scheduling schemes, including global [38,74], fully-partitioned [37], and federated [9]. When focusing on a typical setup where multiple DAGs operate on a homogeneous multi-core system using a global scheme, there have been significant research efforts aimed at establishing bounds for worst-case execution scenarios through RTA. Broadly, the existing analysis techniques fall into two categories: the generic bound [36, 74, 86] and the priority-explicit bound [53, 54, 107, 108]. Generic bounds can be overly conservative without knowledge of the intra-task (node-level) priority. In contrast, the priority-explicit bound, which is based on intra-task priority knowledge, reduces unnecessary interference and blocking calculations. However, it retains some pessimism due to the overlooked parallelism between nodes. Given the pessimistic nature of current DAG analysis methods, system engineers often resort to substantial resource over-provisioning. This tendency has become a significant hurdle for implementing the RTA of DAG tasks in real-world systems.

## 1.2 Thesis Aim

The aforementioned limitations hinder the advancement of real-time systems towards high performance. In this thesis, we introduce a High Performance Real-Time Scheduling (HPRTS) framework. This framework tackles intricate challenges in multiprocessor architectures with FPS scheduling, including reliable resource sharing, contention-aware allocation, and RTA for multi-DAG systems—all crucial for propelling real-time systems to higher performance levels.

The initial step of the proposed HPRTS framework seeks to bridge the gap between reliability and resource sharing. We focus on Mixed-Criticality Systems (MCS), which are prevalent in practical applications [59, 101]. Their intricate execution model makes the problem more challenging to address. We introduce the first fault-tolerant solution for multiprocessor MCS with shared resources. This proposed solution should be suitable for MCS with any number of criticality levels. New fault-tolerant techniques must be proposed to efficiently handle faults in the presence of shared resources, with the aim of reducing blocking time during fault tolerance. Concurrently, a schedulability test must be introduced to ensure the timing predictability of the proposed solution.

In the second step of the HPRTS framework of the thesis, we address the task allocation problem in the presence of shared resources. To mitigate resource contention in multiprocessor systems, a comprehensive contention-aware model is essential. This model should accurately capture task resource-access behaviors, guiding allocation to minimize contention effectively. It must be efficient, avoiding the need for repeated schedulability tests, ensuring both reduced computational costs and adaptability for run-time applications. The allocation strategy will prevent tasks from migrating, thus avoiding additional migration overheads.

In the concluding step of the proposed HPRTS, we embark on an exploration of a sophisticated task model. The objective is to curtail resource overprovisioning during the design phase of systems employing DAG tasks, recognizing that such over-provisioning can hinder the pursuit of high performance in real-time systems. Our attention is centered on systems equipped with knowledge at the node level, a feature that is directly applicable in practical scenarios. Following this, we present an analytical bound through RTA tailored to encapsulate the worst-case execution scenarios, thereby safeguarding the system's timing predictability. The proposed analytical bound is crafted to explore the parallelism inherent in the execution of DAG tasks. It aims to minimize unnecessary interference and blocking delay computations, leading to a reduction in pessimistic estimations and effectively addressing the challenges of resource over-provisioning.

## **1.3** Thesis Hypothesis

The thesis hypothesis posits that integrating reliable resource sharing, contentionaware task allocation, and RTA for multi-DAG systems will significantly enhance real-time embedded system performance. This hypothesis is grounded in the following assumptions:

**Reliable resource sharing**: While resource contention complicates the adherence to timing constraints in real-time embedded systems, current fault-tolerance methods further intensify this contention, thereby diminishing system schedulability. Our proposed fault-tolerant solution aims to shorten the fault-tolerance process, thereby improving system schedulability over existing methods by at least 10%.

**Contention-aware task allocation**: Effective task allocation is pivotal for systems with intensive resource sharing. Our proposed algorithm, cognizant of task resource usage, is designed to diminish resource contention and outperform existing allocation methods in enhancing system performance by alleviating the computation speed and schedulability by at least 10%.

**RTA for multi-DAG systems**: Applications in modern real-time embedded systems are often modeled as DAG tasks. A precise RTA bound can mitigate hardware resource over-provisioning challenges. Our proposed RTA for multi-DAG systems is designed to offer a safe and tight bound, scheduling at least 10% more systems than current bounds.

In summary, the hypothesis suggests that by synergizing these three components, the overall efficiency and efficacy of real-time embedded systems will see marked improvement, leading to superior performance. Experimental and simulation methods will be employed to validate this hypothesis.

## **1.4** Success Criteria and Contributions

To evaluate the effectiveness of the proposed framework in this thesis, a set of Success Criterias (SC) have been established. To validate the hypothesis stated in Section 1.3, the following must be developed:

SC-1: A system execution model compatible with an arbitrary number of criticality levels is constructed in which faults occurring in normal sections (i.e., without shared resources accessed) and critical sections (i.e., with shared resources accessed) are treated separately.

SC-2: A novel protocol is proposed to address faults during accessing shared resources, aiming to minimize blocking time following a schedulability analysis to provide the timing guarantees.

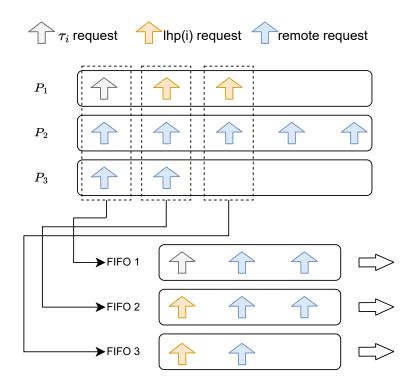

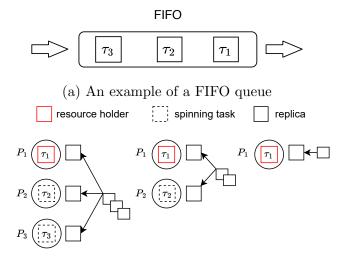

SC-3: A Resource Contention Model (RCM) that approximates the degree of resource contention between tasks in the context of FIFO-spin locks.

SC-4: A contention-ware task allocation algorithm based on the RCM, where shared resources are accessed by tasks from their host processor.

SC-5: An RTA for multi-DAG systems, utilizing novel analysis techniques, effectively harnesses node-level parallelism. It safely eliminates redundant calculations and workloads that cannot contribute to delays, hence ensures a tighter bound.

# 1.5 Thesis Outline

The thesis is structured as follows:

**Chapter 2**: This chapter offers an in-depth overview of real-time systems, covering task classifications, scheduling methodologies, and the intricacies of multiprocessor environments. It places emphasis on synchronization in resource sharing, the role of MCS in scheduling, and the evolution of task allocation. The importance of DAG tasks is underscored, and current research limitations are addressed, paving the way for deeper exploration in the subsequent chapters.

**Chapter 3**: Here, the first fault-tolerant solution tailored for multiprocessor MCS with shared resources is introduced. A system execution model compatible with any number of criticality levels is presented, along with innovative resourcesharing protocols that adeptly manage faults while ensuring real-time guarantees. The content satisfies Success Criteria 1 and 2 (SC-1 and SC-2) and addresses the Limitations 1, 2, and 3 highlighted in Chapter 2.

**Chapter 4**: This chapter presents the proposed RCM, which estimates the degree of competition for resources among tasks. Allocation strategies based on the RCM are also discussed, demonstrating the thesis's alignment with SC-3 and SC-4, address the Limitations 4, 5 and 6 that pointed out in Chapter 2.

**Chapter 5**: An RTA with novel techniques for DAG tasks is showcased. These techniques harness node-level parallelism and exclude non-contributory workloads when determining intra-task and inter-task delays. The content validates SC-5 and resolves the Limitations 7 and 8 that pointed out in Chapter 2.

Chapter 6: The thesis concludes by summarizing its main points, revisiting its contributions and central hypothesis, and suggesting potential avenues for future research.

# Chapter 2 Review of Existing Literature

This literature review explores the foundational concepts of real-time systems, covering fundamental definitions, task models, and scheduling mechanisms, with an emphasis on Response Time Analysis (RTA).

We then discuss shared resources in real-time systems, introducing basic resource models and lock-based mechanisms essential for data integrity. Resourcesharing protocols, which offer guidelines for task interactions, are also explored, along with the evolution of RTA in this context.

Our focus shifts to Mixed-Criticality Systems (MCS), detailing task definitions within MCS and the evolution of RTA. We also touch upon conventional fault-tolerance approaches in embedded systems, leading to a holistic examination of fault-tolerance, resource-sharing, and MCS. The limitations of current research are addressed which set the stage for Chapter 3. The review further dissects task allocation algorithms, both traditional and those considering shared resources. A gap in resource-aware task allocation is highlighted, addressed in Chapter 4. We also explore the task model represented as Directed Acyclic Graphs (DAG), clarifying its core concepts and current research directions. The RTA of DAG tasks, especially in relation to RTA with intra-task priority assignment, is detailed, leading to our contributions in Chapter 5.

The review's structure is as follows: Section 2.1 offers an overview of realtime systems research. Section 2.2 focuses on shared resources and protocols. Section 2.3 covers MCS and fault-tolerance. Section 2.4 discusses task allocation challenges, and Section 2.5 provides an in-depth analysis of DAG tasks.

### 2.1 General Definitions of Real-Time Systems

In this section, we explore the core concepts of real-time systems, focusing on their definition, task models, and scheduling schemes. We will examine the intricacies of task scheduling in multiprocessor environments and conclude with an analysis of schedulability to ensure system reliability and efficiency. This overview will provide a foundational understanding of the critical components and operations in real-time systems.

#### 2.1.1 Real-Time Task and System Models

Real-time systems, chiefly distinguished by their stringent timing requirements, play an integral role in numerous critical applications, ranging from autonomous vehicles to avionics systems [23]. These systems are not just defined by their processing speed but more importantly, by their determinism in fulfilling timebased commitments [63].

#### **Real-Time Task Models**

A real-time system typically contains a set of tasks  $\Gamma$ , in which the  $i^{\text{th}}$  task is denoted as  $\tau_i$ . A task  $\tau_i$  often contains a series of recurrent job instances  $\{j_1, j_2, \ldots, j_n\}$ . Each task  $\tau_i$  can generally be defined by the following tuples:  $\{T_i, D_i, Pri(\tau_i), P(\tau_i), C_{\tau_i}, U_{\tau_i}\}$ .

- $T_i$  represents the period of a task in real-time systems, referring to the time interval between consecutive instances of that task.

- $D_i$  denotes the deadline by which each task must be completed.

- $Pri(\tau_i)$  indicates the priority of  $\tau_i$  which is the ranking assigned to a task in an operating system, determining its execution order relative to other tasks. In this thesis, a larger number indicates a higher priority.

- $P(\tau_i)$  signifies the core on which the task is allocated.

- $C_{\tau_i}$  represents the pure Worst-Case Execution Time (WCET) of a task. This is the time the task computes on a core without considering interferences, blocking, or any other delays.

- $U_{\tau_i}$  is the utilization of the task  $\tau_i$ , defined as the ratio of its computation time  $C_{\tau_i}$  to its period  $T_i$ . Mathematically,  $U_{\tau_i} = \frac{C_{\tau_i}}{T_i}$ .

Based on their release patterns or periods tasks can be categorized into periodic, aperiodic, and sporadic tasks [23].

*Periodic tasks*, as the name implies, recur at constant time intervals. Every instance of such a task, or a *job*, carries a deadline that it must meet. For instance, the control loop in an autopilot system is a periodic task, which consistently reads sensor data and adjusts controls based on the readings.

In contrast, *aperiodic tasks* do not follow a fixed pattern and can occur spontaneously. A user command in a computer system, such as a mouse click or a keyboard press, serves as an example of an aperiodic task.

Finally, *sporadic tasks*, while resembling aperiodic tasks in their irregular occurrence, differ in that they enforce a minimum separation requirement between consecutive jobs and often come with hard deadlines. A safety monitor in a factory provides an apt example, requiring checks on machinery status following unpredictable events, with a requisite minimum time lapse between checks to avoid system overloading.

In addition, real-time tasks can be further classified as implicit-deadline, constrained-deadline, or arbitrary-deadline tasks, based on the relationship between a task's period and its deadline [68].

Implicit-deadline tasks have deadlines that coincide with the period. In mathematical terms, for each task i, this relationship can be expressed as:  $D_i = T_i$ . These tasks are frequently encountered in periodic systems, such as control loops in embedded systems.

Constrained-deadline tasks have deadlines that are either equal to or less than the period. Mathematically, for each task i, this relationship is expressed as:  $D_i \leq T_i$ .

Conversely, arbitrary-deadline tasks may have deadlines that are shorter, equal to, or longer than the period. For these tasks, the mathematical relationship for each task with index i can be expressed as:  $D_i \leq T_i$  or  $D_i > T_i$ , and are typically associated with complex, event-driven systems such as modern aviation control systems.

#### **Real-Time System Models**

As described by [68], real-time systems are further classified into hard and soft real-time systems based on the criticality of adhering to these deadlines. Hard real-time systems demand strict adherence to task deadlines, with any deviation potentially leading to catastrophic consequences. An exemplary instance is an air traffic control system, which must process radar data and relay updated aircraft positions to air traffic controllers within stringent time frames. Any lapse could result in dire events, such as mid-air collisions.

On the other hand, soft real-time systems offer a degree of leniency, where occasional missed deadlines might lead to a decrease in performance but remain within acceptable bounds. The in-flight entertainment system in aircraft serves as an example; while prompt responses enhance the passenger experience, minor delays will not have grave repercussions.

In the computing domain, the architecture of the processor plays a pivotal role in determining system performance and efficiency. Two primary architectures have emerged: homogeneous and heterogeneous [43].

| Notation      | Description                                        |

|---------------|----------------------------------------------------|

| Γ             | Set of tasks in a real-time system                 |

| $	au_i$       | <i>i</i> -th task in the set $\Gamma$              |

| $T_i$         | Period of task $\tau_i$                            |

| $D_i$         | Deadline of task $\tau_i$                          |

| $Pri(\tau_i)$ | Priority of task $\tau_i$                          |

| $P(	au_i)$    | Core on which task $\tau_i$ is allocated           |

| $C_{\tau_i}$  | WCET of task $\tau_i$                              |

| $U_{\tau_i}$  | Utilization of task $\tau_i$                       |

| Λ             | Set of processors in a multiprocessor architecture |

| m             | Number of cores in the system                      |

| $P_a$         | <i>a</i> -th processor in the set $\Lambda$        |

| $\Gamma(P_a)$ | Set of tasks allocated to core $P_a$               |

Table 1: Table of Notations for Real-Time Tasks and Models

**Homogeneous Architecture**: In this setup, all cores are functionally and performance-wise identical. They are capable of executing the same set of instructions, facilitating a streamlined programming and task scheduling environment. Such architectures are commonly found in traditional multi-core processors.

Heterogeneous Architecture: This design integrates diverse core types within a single system. For instance, a system might incorporate high-performance cores for demanding tasks alongside energy-efficient cores for less intensive operations. This configuration provides versatility, balancing performance and energy consumption.

Tasks are assumed to be scheduled on a multiprocessor architecture represented by a set of processors,  $\Lambda$ , and the number of cores in the system is denoted as m (the terms "core" and "processor" are used interchangeably in this thesis). The  $a^{\text{th}}$  processor in  $\Lambda$  is denoted as  $P_a$ .  $\Gamma(P_a)$  returns the set of tasks allocated to core  $P_a$ . While most parts of this thesis centers on the homogeneous architecture, we also transition our evaluation to a basic heterogeneous setup in Chapter 4, where identical cores operate at varying frequencies during runtime. Necessary notations for task and system models are summarized in Table 1.

### 2.1.2 Task Scheduling Mechanisms

Task scheduling is fundamental in real-time systems, dictating the order and timing of task executions. It guarantees timely and efficient task execution, ensuring the system adheres to its stringent time constraints.

### Preemptive vs. Non-preemptive Scheduling

Task scheduling is central to a system's efficiency and responsiveness. Two key methodologies in this domain are preemptive and non-preemptive scheduling [30].

- **Preemptive Scheduling**: In this type of scheduling, the currently executing task can be interrupted (preempted) by a higher-priority task. Once the higher-priority task completes its execution or is blocked, the preempted task can resume its execution. This approach ensures that high-priority tasks are executed as soon as they become available, making it suitable for real-time systems where timely task execution is crucial. However it inevitably cause more frequent context switches.

- Non-preemptive Scheduling: Once a task starts its execution, it runs to completion without being interrupted. Even if a higher-priority task becomes available, it has to wait until the currently executing task completes. This approach can lead to longer waiting times for high-priority tasks but

ensures that once a task starts, it will not be interrupted, which can be beneficial in scenarios where task interruptions can lead to complications or inefficiencies.

### **Fixed-Priority and Dynamic Scheduling**

Task scheduling can further be categorized into Fixed-Priority Scheduling (FPS) and dynamic scheduling. FPS, characterized by its fixed task execution order, brings predictability to the system. In contrast, dynamic scheduling adapts task priorities in real-time, offering the system flexibility to respond to changing conditions.

**FPS**: In this thesis, we focus on FPS, a scheduling scheme that is one of the most commonly employed in real-time systems due to its compelling features. Under FPS, tasks are assigned static priorities at the initial phase of system configuration. These priorities, which remain constant throughout the tasks' lifecycle, dictate the order in which tasks are selected for execution by the scheduler [68].

One of the principal advantages of FPS is the predictability it imparts to the scheduling process [30]. This predictability is invaluable in real-time environments, where guaranteeing the timely execution of tasks is paramount. It simplifies the system analysis, as the behavior of tasks under a set of known conditions can be assessed deterministically. This, in turn, makes both operations and system management more straightforward and robust.

Additionally, FPS is known for its relatively lower runtime overhead. Without the need for frequent, potentially complex recalculations of task priorities, the system can execute tasks efficiently, which is a crucial characteristic for systems where computational resources are at a premium [33].

Within the FPS paradigm, several specific algorithms exist for priority as-

signment:

- Rate-Monotonic Priority Assignment (RMPA): RMPA assigns priority to tasks based on their period, with shorter periods indicating higher priority. This method is particularly useful in systems that handle periodic tasks, as it prioritizes tasks that demand more frequent attention [67].

- Deadline-Monotonic Priority Assignment (DMPA): DMPA is a variation of RMPA optimized for systems where task periods and deadlines differ. DMPA prioritizes tasks with shorter relative deadlines, superseding the shortest period criteria [64].

- Audsley's Optimal Priority Assignment (AOPA): AOPA is a sophisticated algorithm for optimal priority assignment under static-priority scheduling. It operates iteratively, assigning the lowest priority to the feasible task at that level, thereby excluding it from future consideration [4].

**Dynamic Scheduling:** Contrary to FPS methods, dynamic strategies decide task priorities at runtime. These priorities are subject to change during the system operation depending on various factors, such as task deadlines, task arrival times, or remaining computation time. These strategies generally manage aperiodic and sporadic tasks more effectively as they adapt to the evolving state of the system.

• Earliest Deadline First (EDF): The EDF scheme is a dynamic scheduling strategy where the task with the nearest deadline is given the highest priority [23]. Specifically, EDF is proven to be optimal for uniprocessor systems, meaning that if a set of tasks with arbitrary arrival times is schedulable (i.e., all tasks can meet their deadlines) on a uniprocessor system under any scheduling algorithm, then that task set is guaranteed to be schedulable under EDF. This optimality holds as long as the total CPU utilization of all tasks in the system is less than or equal to 1 (100%) [68].

• Least Laxity First (LLF): Similar to EDF, LLF is a dynamic scheduling strategy that gives priority to tasks based on their laxity or slack time, assigning the highest priority to the task with the least remaining time after its execution time is subtracted from its deadline. This strategy is particularly beneficial in systems with variable execution times to prevent tasks from missing their deadlines [61].

However, dynamic scheduling can lead to increased overhead due to frequent task switching as priorities change with approaching deadlines. Handling these shifting priorities can be challenging, especially in systems with numerous tasks or variable behavior. While EDF works well for single-processor systems, its effectiveness can differ in multi-processor systems, which may require added synchronization [6].

### Scheduling Paradigms in Multiprocessor Systems

Over the years, various scheduling methods have been developed to efficiently manage task execution within real-time multiprocessor systems, each offering unique advantages [7,69,71].

- Fully-Partitioned Scheduling [69]: Tasks are assigned to specific processors and remain there throughout their lifecycle. This approach is predictable and reduces overhead due to the absence of inter-processor communication for task migrations. However, it demands careful task allocation to avoid imbalances in processor utilization.

- Semi-Partitioned Scheduling [71]: While tasks are primarily assigned

to individual processors, certain tasks can migrate between processors, providing better flexibility and potentially improved processor utilization.

- Global Scheduling [65]: Tasks are placed in a system-wide queue and can be executed by any available processor. This approach offers flexibility but may introduce overhead due to frequent task migrations.

- Global List Scheduling [76]: A specific type of global scheduling where tasks are organized in a priority list. Processors pick tasks based on their priority, ensuring that high-priority tasks are executed first.

- Federated Scheduling [7]: A hybrid approach that combines partitioning and global scheduling. Larger tasks are partitioned onto specific processors, while smaller tasks are globally scheduled, optimizing resource utilization.

The selection among these strategies depends on the specific requirements of the system being designed, underscoring the significance of a deep understanding of each method.

### 2.1.3 Schedulability Analysis

In the sphere of real-time systems, the reliable execution of tasks within their stipulated deadlines is of paramount importance. To certify this essential attribute, a robust approach known as schedulability analysis [30], typically enacted through schedulability tests, is employed. These tests represent sophisticated analytical procedures designed to ascertain whether a particular set of tasks, under a predetermined scheduling policy, can invariably fulfill their deadlines.

The types of schedulability tests is multi-faceted, with a principal categorization based on the form of assurance they furnish [29]: *necessary*, *sufficient*, and *exact* (or optimal) conditions. A necessary condition, if left unsatisfied, unequivocally confirms the non-schedulability of a task set. Conversely, even upon meeting this condition, a task set's schedulability cannot be confirmed, necessitating further analysis. Sufficient conditions, if met, provide the assurance of a task set's schedulability. However, an inability to satisfy this condition does not conclusively pronounce the task set as unschedulable. An exact or optimal condition, serving as both a necessary and sufficient determinant, delivers a definitive verdict: a task set that satisfies this condition is categorically schedulable, while those failing to meet this criterion are deemed non-schedulable.

The utilization test serves as a foundational test for determining the schedulability of tasks in real-time systems. However, its specific criteria vary across different scheduling algorithms. In *sufficient* scenarios, fixed-priority scheduling algorithms, such as RMPA and DMPA, assign tasks a static priority that remains unchanged over time. The derived schedulability tests for these algorithms, particularly for periodic tasks, are rooted in worst-case scenarios. Specifically, the formula  $n(2^{1/n} - 1)$ , as proposed by Liu and Layland [67], establishes an upper bound on CPU utilization for a set of n tasks. This threshold, which is notably less than 100%, accounts for the worst-case interference from higher-priority tasks that can potentially delay the execution of those ranked lower. As the task count escalates, this bound asymptotically approaches a value below 100%, approximately 69.3%, ensuring that all tasks can meet their deadlines even in the most adverse conditions.

Conversely, dynamic scheduling algorithms, exemplified by the EDF method, exhibit a more fluid approach, adjusting task priorities based on specific criteria, such as impending deadlines. The 100% utilization criterion for EDF suggests that if tasks collectively do not demand more than the available CPU time, they are feasibly schedulable. This is attributed to the algorithm's strategy of always prioritizing the task with the most imminent deadline. However, a caveat exists: while a CPU utilization below 100% does not universally guarantee schedulability due to variables like task phasing, surpassing this threshold unequivocally renders a task set non-schedulable. In this case, utilization test is deemed as *necessary* test.

More intricate scenarios, characterized by task dependencies, blocking times, and resource sharing, necessitate the formulation of advanced schedulability tests. Often grounded in RTA, these tests primarily are *sufficient* tests which focus on computing a task's Worst-Case Response Time (WCRT) and comparing it to its designated deadline [13].

In systems devoid of shared resources, a series of tasks exists, each with a distinct priority. The RTA for a task  $\tau_i$  is exemplified. As depicted in Equation (1),  $R_i$  denotes the WCRT of  $\tau_i$ .

$$R_i = C_{\tau_i} + B_i + \sum_{\tau_h \in \text{lhp}(i)} \left\lceil \frac{R_i}{T_h} \right\rceil C_{\tau_h}$$

(1)

More specifically,  $C_{\tau_i}$  represents the WCET of  $\tau_i$ . Without shared resources, tasks might be blocked due to non-preemptive (NP) segments run by the underlying RTOS. This halts certain tasks as the system operates within an NP segment. Since such blocking can occur only once during the release of a real-time task, the blocking duration can be directly bounded by the longest non-preemptive segment in the RTOS, as shown in Equation (2). Here,  $B_i$  signifies the maximum duration of the RTOS's NP segments. In  $\sum_{\tau_h \in \text{lhp}(i)} \left\lceil \frac{R_i}{T_h} \right\rceil C_{\tau_h}$ , lhp(i) denotes the set of tasks on the same processor with a priority higher than  $\tau_i$ , and  $\frac{R_i}{T_h}$  represents the number of times the highe-priority task  $\tau_h$  can be released during the period  $R_i$ . The overall notation indicates the total interference incurred by  $\tau_i$ from tasks on the same processor that have a higher priority [21].

$$B_i = \max(NP_1, NP_2, \dots, NP_n) \tag{2}$$

In situations where an analytical approach is deemed impractical due to system intricacies, simulation-based testing methods emerge as a practical alternative. These methods involve simulating the system's function over a set duration, often a hyperperiod, followed by identifying potential deadline breaches [16].

To sum up, schedulability tests are a cornerstone in the domain of realtime systems. They provide essential guarantees of temporal accuracy, a trait crucial in many applications, especially those with strict safety or performance requirements. This field remains an active area of research, with novel methods continually emerging to address the challenges of increasingly intricate system models.

### 2.1.4 Summary

In this section, we provide an overview of real-time systems, emphasizing their defining attributes, task models, and the mechanisms that govern their operation. Central to our discussion is the FPS method, a prevalent approach in real-time systems due to its predictability and efficiency. We also spotlight the RTA, a critical tool for assessing task schedulability and ensuring that tasks meet their deadlines. Through this exploration, we aim to offer a foundational understanding of the key components and methodologies that underpin the reliable functioning of real-time systems.

# 2.2 Resource Sharing in Real-Time Systems

In this section, we introduce the shared resources model central to our thesis, outlining the specific resources we focus on. We will examine lock-based mechanisms that govern access to these resources, ensuring orderly task execution. Additionally, we will discuss the protocols that regulate task interactions with shared resources, a crucial step in maintaining system integrity. Lastly, we will undertake a schedulability analysis incorporating shared resources and the applied protocols, aiming to assess a system's ability to meet task deadlines effectively. This discussion lays a robust groundwork for further explorations in this thesis.

#### 2.2.1 Shared Resources

Shared resources play a pivotal role in the realm of computer science and programming, especially in real-time systems where tasks have strict timing constraints [110]. These resources include data structures, such as arrays, lists, and trees, which are systematic ways of organizing and storing data. They also consist of variables, essential memory storage locations that hold data values, and specialized memory spaces like buffers or caches tailored for specific purposes. These spaces can speed up data access or provide intermediary storage.

In real-time systems, managing concurrent access to shared resources is challenging. When multiple tasks or processes need simultaneous access to a resource, they enter a *critical section* of the code. It is essential to ensure mutual exclusivity within this critical section, allowing only one task to access the shared resource at a time.

To guarantee safe and efficient concurrent access, synchronization mechanisms like locks, semaphores, or critical section protocols are used. But in realtime contexts, these mechanisms must be carefully designed to ensure tasks do not miss their deadlines while waiting for resource access [88].

In this thesis, we explore the intricacies of shared resources in multicore realtime systems. We posit that within the system, there exists a set of resources, denoted as  $\mathbb{R}$ . Every resource in this set can be accessed by all tasks, but only in a mutually exclusive manner. This exclusivity is achieved by executing the associated *critical section*. A shared resource with index x, represented as  $r^x$ , is defined by two notations:  $c^x$  and  $N_i^x$ . Here,  $c^x$  denotes the computation time required to access the shared resource  $r^x$ . In contrast,  $N_i^x$  quantifies the number of requests from  $\tau_i$  within a single release. The function  $F(\cdot)$  specifies the set of resources requested by the given tasks.

In addition, due to the presence of shared resources in the system, the total computation time for  $\tau_i$  (denoted as  $\hat{C}_{\tau_i}$ ) must also account for the resource computation time. This is given by

$$\widehat{C}_{\tau_i} = C_{\tau_i} + \sum_{r^x \in F(\tau_i)} N_i^x \cdot c^x \tag{3}$$

where  $C_{\tau_i}$  denotes the pure WCET of  $\tau_i$  when executed on a processor without accessing shared resources. The term

$$\sum_{r^x \in F(\tau_i)} N_i^x \cdot c^x \tag{4}$$

represents the total time  $\tau_i$  spends accessing shared resources. Here,  $F(\tau_i)$  returns the set of resources requested by  $\tau_i$ , and  $N_i^x \cdot c^x$  computes the total time  $\tau_i$  spends accessing resource  $r^x$ . The utilization of a task,  $U_{\tau_i}$ , is subsequently determined by

$$U_{\tau_i} = \frac{\widehat{C}_{\tau_i}}{T_i} = \frac{C_{\tau_i} + \sum_{r^x \in F(\tau_i)} N_i^x \cdot c^x}{T_i}$$

(5)

which is the total computation time divided by the task's period. For clarity, the notations of shared resources are provided in Table 2 below.

#### 2.2.2 Lock-Based Mechanisms

In the field of real-time systems, ensuring data integrity and the predictability of task behaviors is paramount. One prevalent method for safeguarding data and mitigating race conditions is the lock-based synchronization technique. This

| Symbol          | Meaning                                                                    |

|-----------------|----------------------------------------------------------------------------|

| $\mathbb{R}$    | Set of shared resources in the system                                      |

| $r^x$           | A shared resource with index $x$                                           |

| $c^x$           | Computation time to access the resource $r^x$                              |

| $N_i^x$         | Number of requests from $\tau_i$ to resource $r^x$ within a single release |

| $F(\cdot)$      | Function specifying the set of resources requested by a task               |

| $\widehat{C}_i$ | Total computation time for $\tau_i$ considering shared resources           |

Table 2: Notations of Shared Resources

approach works harmoniously alongside non-blocking strategies to create a cohesive synchronization system. In the lock-based paradigm, specific locks guard critical sections. Tasks can only enter these sections upon acquiring the relevant lock. When one task holds a lock, others must patiently await its release.

This strategy encompasses several locking primitives, including mutex locks, semaphores, and monitors [25]. Based on a task's behavior during its waiting period, these primitives can be classified as [104]:

- 1. Suspension-based Locks: Under this mechanism, tasks wanting an engaged lock will temporarily step back, yielding the processor. They transition to an idle state and join a priority queue. Upon the lock's release, the task at the queue's forefront, usually with the highest priority, resumes and claims the lock.

- 2. Spin Locks: Contrary to the suspension-based locks, tasks with spin locks stay active, even if the required lock is unavailable. They remain in a *busy-wait* state, repeatedly checking the lock's status. Though often governed by a First-in-First-out (FIFO) methodology, a priority-based system can also serve them. This type of locking is particularly favored in kernel-level

operations.

However, the lock-based approach is not devoid of challenges [77]. *Deadlocks* present a significant concern. In such scenarios, tasks, intertwined in a nested quest for resources, reach a standstill due to mutual dependencies. Additionally, there's the menace of livelocks, where tasks continuously defer lock acquisition to each other, achieving no progress. Real-time systems counteract these pitfalls by introducing additional rules such as not allowing a task to hold resources while waiting for others to avoid *deadlocks* and set strict request order to avoid *livelocks*. It is important to note that this thesis does not consider nested resource sharing. In other words, a task can interact with only one resource at any given time. However, this limitation can be circumvented using group locks, as discussed in [109].

Nevertheless, the incorporation of locks, while indispensable, introduces its own set of complexities. One prominent challenge is priority inversion, which could significantly disrupt the predictable functioning of a real-time system. When a high-priority task finds itself stalling due to a lower-priority task's operations, unpredictability ensues, risking missed task deadlines. For clarity, consider the following illustrative example:

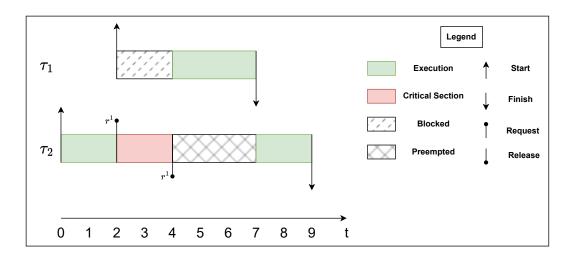

### Example 1.

$au_1$ : A task with high priority.  $au_2$ : Holding a priority lower than  $au_1$ .  $r^1$ : A resource desired by  $au_2$ .

Based on the tasks and resource setup, Figure 1 presents an execution scenario that demontrates what priority inversion is.

τ<sub>2</sub> initiates its operation at time point t = 0 and acquires r<sup>1</sup>, then remains non-preemptive from t = 2 to t = 4.

Figure 1: The execution chart for priority inversion

- During τ<sub>2</sub>'s execution with r<sup>1</sup>, τ<sub>1</sub> readies for execution at t = 2, and aims to execute on the processor.

- Given that  $\tau_2$  currently possesses  $r^1$ ,  $\tau_1$ , despite its higher priority, is blocked from t = 2 to t = 4.

- This situation, wherein τ<sub>1</sub> is hindered by τ<sub>2</sub> due to a shared resource access, epitomizes priority inversion.

- After  $\tau_2$  releases  $r^1$  at t = 4,  $\tau_1$  preempts it and executes until t = 7

- $\tau_2$  resumes its execution at t = 7 and finishes executing at t = 9 in this example

The presented scenario highlights the behaviors of priority inversion. It represents a divergence from the expected sequence of task execution based on priority. When a high-priority task is compelled to stand by because a low-priority task accesses a shared resource, the system's predictable feature faces disruption. Such a disturbance can lead to missed deadlines, especially for pivotal high-priority tasks. Completely eliminating priority inversion may appear as an aspirational target, but it is not always the primary aim. The objective is to limit the duration and effects of these inversions. In doing so, real-time systems can ensure all tasks to meet their deadlines.

## 2.2.3 Resource Sharing Protocols

The pivotal role of shared resources in fostering concurrent task interactions highlights the imperative for dependable protocols. These protocols are crucial not only to ensure smooth access but also to prevent race conditions, safeguard data integrity, and maintain the system's overall dependability. Historically, the field of resource sharing in single-core and multicore real-time systems has benefited from comprehensive research, leading to the development of numerous resource sharing protocols [2, 22, 41]. For an in-depth review of these protocols can be found in survey presented in [15].

#### **Protocols for Uniprocessor Systems**

In single-processor systems, the Priority Ceiling Protocol (PCP) is widely used to control how tasks access shared resources. Two main adaptations of PCP are well-documented in [81]: the Original Priority Ceiling Protocol (OPCP) and the Immediate Priority Ceiling Protocol (IPCP).

In the OPCP, there are two distinct ceiling priorities: the resource ceiling and the system ceiling. The resource ceiling priority is set to the priority of the highest-priority task that may request the resource. Meanwhile, the system ceiling priority reflects the highest resource ceiling priority of any resource currently in use. With OPCP in place, a task can only acquire a lock if its priority is higher the current system ceiling. If not, the task will be blocked until it can meet this condition. With the IPCP, each shared resource has an assigned ceiling priority, which is determined by the highest priority of tasks that might request the resource. Within the IPCP protocol, when a task secures a shared resource, its priority is temporarily elevated to match the resource's ceiling priority. This elevation in priority ensures that, while in possession of a shared resource, the task remains immune to preemption by other tasks that have priorities lower than the ceiling. An execution example of PCPs is demonstrated below.

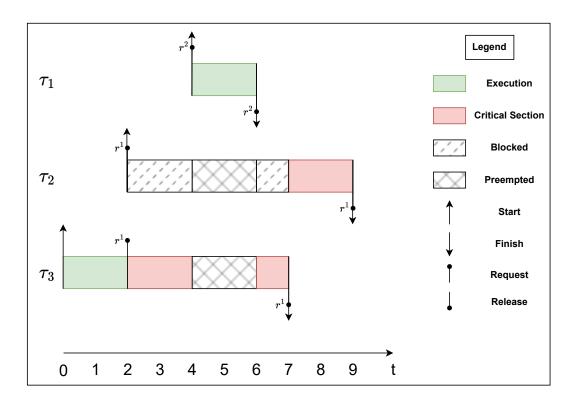

**Example 2.** Consider three tasks and their associated priorities:

$au_1$ : Priority 3 (highest)  $au_2$ : Priority 2  $au_3$ : Priority 1 (lowest)

We also have the following resources with their respective resource ceilings:

$r^{1}$ : Ceiling Priority 2 (accessed by  $\tau_{2}$  and  $\tau_{3}$ )  $r^{2}$ : Ceiling Priority 3 (accessed by  $\tau_{1}$ )

Given this system setup, with assistance of Figure 2, we demonstrate an execution scenario of tasks under OPCP:

- τ<sub>3</sub> starts at t = 0, requests r<sup>1</sup> at t = 2 and successfully locks the resource. The system ceiling is then raised to 2.

- $\tau_2$  starts and requests  $r^1$  at t = 2, but blocked by  $\tau_3$  as its priority 2 is not higher than the current system ceiling.

- Subsequently,  $\tau_1$  starts and requests  $r^2$  at t = 4. As its priority 3 is higher than the current system ceiling, it preempts  $\tau_3$  and lock  $r^2$  successfully.

- $\tau_3$  resumes its execution at t = 6 as  $\tau_1$  releases the resource and finishes executing, then it releases  $r^1$  and finishes executing at t = 7.

Figure 2: The execution chart for tasks under PCPs

• In the mean time,  $\tau_2$  finally secures  $r^1$  at t = 7 and finishes executing at t = 9.

With the same system setup, the task behaviors under IPCP is similar to OPCP and can so be described by referencing Figure 2.

- τ<sub>3</sub> starts at t = 0 and requests r<sup>1</sup> at t = 2 and successfully lock the resource.

Its priority is immediately boosted to 2.

- $\tau_2$  starts and requests  $r^1$  at t = 2, but blocked by  $\tau_3$  as its priority 2 is not higher than the boosted priority of  $\tau_3$ .

- Subsequently,  $\tau_1$  starts and requests  $r^2$  at t = 4. As its priority 3 is higher than  $\tau_3$ 's, it preempts  $\tau_3$  and locks  $r^2$  successfully with unchanged priority (its priority is equal to the ceiling priority of  $r^2$ ).

- $\tau_3$  resumes its execution still with boosted priority at t = 6 as  $\tau_1$  releases the resource and finishes its execution. At t = 7,  $\tau_3$  releases the resource, retrieves its base priority and exists the system

- $\tau_2$  finally secures  $r^1$  at t = 7 and exists the system at t = 9.

The primary differentiation between IPCP and OPCP lies in the dynamic elevation of priority inherent to IPCP. While protocols like OPCP inhibit tasks based on the prevailing system ceiling, IPCP uniquely elevates the priority of the task in question. This ensures that the task remains impervious to preemption by tasks of intermediary priorities that do not necessitate the locked resource.

#### **Resource-Sharing Protocols for Multiprocessor Systems**

In the multiprocessor aspect, out of the many existing protocols, the Multiprocessor Stack Resource Protocol (MSRP) [41] merits special attention. Specifically crafted for fully-partitioned systems, MSRP is a FIFO spin-based resourcesharing protocol. Under MSRP, each globally shared resource is linked with a FIFO queue. Tasks requesting such a resource are added to the queue and busywait (spin) non-preemptively until they reach the queue's head, upon which the resource is assigned to them. Once a task is granted a resource, it carries on its non-preemptive execution until the resource is relinquished. In contrast, when dealing with a local resource (i.e., a resource shared within one core), the IPCP is employed. The MSRP is examplified below.

**Example 3.** Consider a two-core computer system,  $P_1$  and  $P_2$ , dedicated to managing tasks in a computational environment.

Tasks and Resources:

$au_1$  on  $P_1$ : Requires  $r^1$ .  $au_2$  on  $P_2$ : Requires both  $r^1$  and  $r^2$ .  $au_3$  on  $P_2$ : Requires  $r^2$ .  $r^1$ : Globally shared computational module.  $r^2$  on  $P_2$ : Local computational unit exclusive to  $P_2$ .

Scenario 1 - Accessing the Global Resource  $r^1$ :

- $\tau_1$  on  $P_1$  initiates its operation and locks  $r^1$ .

- Simultaneously, τ<sub>2</sub> on P<sub>2</sub> requires r<sup>1</sup>. Since τ<sub>1</sub> is currently using the resource, τ<sub>2</sub> enters the FIFO queue and spins on P<sub>2</sub> non-preemptively.

- After τ<sub>1</sub> releases r<sup>1</sup>, τ<sub>2</sub> becomes the head of the FIFO queue and starts accessing r<sup>1</sup> non-preemptively on P<sub>2</sub>.

- Concurrently, if τ<sub>3</sub> is released, it will be blocked by τ<sub>2</sub> from computing on P<sub>2</sub>, regardless of its priority.

Scenario 2 - Accessing the Local Resource  $r^2$ :

- $\tau_2$  wants to access  $r^2$ . Due to the priority ceiling protocol, its priority is elevated.

- $\tau_3$  is subsequently blocked from executing until  $\tau_2$  finishes its operation regardless of its priority.

In this structure, MSRP ensures efficient access to both global and local resources, reducing delay for low-priority tasks and ensuring smooth task executions.

## 2.2.4 RTA for Shared Resources

The implementation of resource-sharing protocols can prevent race conditions among tasks in the system which in turn safeguards data integrity. However, the timely behavior of tasks, especially during resource sharing, can lead to additional waiting times or priority inversion—termed as *blocking*—owing to the mutually exclusive nature of resource access. Capturing the intricacies of these protocols accurately is vital to ensure the timing correctness of tasks.

The blocking effect is primarily divided into *spin delay* and *arrival blocking* [109]. *Spin delay* can further be categorized into *Direct* and *Indirect spin delay*.

Direct spin delay occurs when a task is directly obstructed from accessing a shared resource due to other concurrent remote accesses. For instance, under MSRP, when task  $\tau_1$  requests a resource  $r^1$ , tasks on other processors, say  $\tau_2$  and  $\tau_3$ , are ahead of  $\tau_1$  in the FIFO queue because they requested  $r^1$  earlier. The time  $\tau_1$  spends waiting for  $r^1$  before it can lock it is referred to as direct spin delay.

In contrast, *indirect spin delay* arises when a task is preempted by a higherpriority local task that is itself directly blocked. For example, under MSRP, when  $\tau_1$  is executing on the processor normally without accessing any shared resource, a higher-priority task  $\tau_2$  preempts  $\tau_1$  to compute on the processor and requests for a global shared resource. Here,  $\tau_1$  can only resume its computation when  $\tau_2$  finishes its execution. Therefore, the *spin delay* experienced by  $\tau_2$  will transitively cause a delay to  $\tau_1$ , termed as *indirect spin delay*.

Arrival blocking, on the other hand, transpires when a newly released highpriority task, like  $\tau_2$ , is immediately blocked by a lower-priority task,  $\tau_1$ . This can be because  $\tau_1$  is either currently requesting or locking a shared resource. As a result, it remains non-preemptive under MSRP until it completes its operation and releases the lock. Thus, a higher-priority task like  $\tau_2$  cannot preempt  $\tau_1$  directly, leading to a delay known as *arrival blocking*.

#### Original RTA for MSRP

The RTA designed to capture the system's worst-case timely behavior under fully-partitioned systems scheduled by preemptive FPS with the application of MSRP was first developed by [41]. As shown in Equation (6), the analysis aims to calculate the WCRT of each task, denoted as  $R_i$ , which comprises the total WCET ( $\hat{C}_i$ ), the arrival blocking ( $B_i$ ), and the interference imposed by the set of local tasks with a higher priority than  $\tau_i$ , represented as  $\sum_{\tau_h \in \text{lhp}(i)} \left\lceil \frac{R_i}{T_h} \right\rceil \cdot \hat{C}_h$ .

$$R_{i} = \widehat{C}_{i} + B_{i} + \sum_{\tau_{h} \in lhp(i)} \left\lceil \frac{R_{i}}{T_{h}} \right\rceil \cdot \widehat{C}_{\tau_{h}}$$

$$(6)$$

Further exploring  $R_i$ , as illustrated in Equation (7), the term  $\widehat{C}_i$  comprises the pure WCET of  $\tau_i$  without accessing any shared resources, denoted as  $C_{\tau_i}$ , and the time spent accessing resources, given by  $\sum_{r^x \in F(\tau_i)} N_i^x \cdot e^x$ . Here,  $F(\tau_i)$  represents the set of resources requested by  $\tau_i$ ,  $N_i^x$  indicates the number of requests that  $\tau_i$ sends to  $r^x$  during a single release, and  $e^x$  denotes the total time spent on each access to  $r^x$ .

$$\widehat{C}_i = C_{\tau_i} + \sum_{r^x \in F(\tau_i)} N_i^x \cdot e^x \tag{7}$$

The amount of time that a task can spend accessing  $r^x$  once is illustrated in Equation 8. In this equation, the function  $map(G(r^x))$  is utilized to identify the set of processors that contain tasks requesting access to  $r^x$ . The notation ||indicates the size of this set of processors, representing the maximum number of requests that can be sent to  $r^x$  concurrently. This analysis assumes a worst-case scenario wherein  $\tau_i$  is perpetually placed at the end of the FIFO queue, forcing it to wait until requests from other processors have been fully serviced. Consequently,  $e^x$  is determined by multiplying the maximum number of concurrent requests by the time needed to access  $r^x$ , denoted as  $c^x$ .

$$e^x = |map(G(r^x))| \cdot c^x \tag{8}$$

The arrival blocking is denoted by  $B_i$ , as illustrated in Equation (9). Here,  $\hat{e}_i$ signifies the maximum arrival blocking that  $\tau_i$  can experience, while  $\hat{b}$  represents the non-preemptive section of the operating system, as previously discussed. The arrival blocking of  $\tau_i$  takes place when  $\tau_i$  is released but is hindered from execution by a local low-priority task (e.g.,  $\tau_{ll}$ ). This hindrance arises when the latter is in the process of requesting or utilizing a shared resource and hence, cannot be preempted by  $\tau_i$ .

$$B_i = max\{\hat{e}_i, b\} \tag{9}$$

Equation (10) aims to discern the peak arrival blocking, which can also be perceived as the maximum time  $\tau_{ll}$  can allocate to accessing a shared resource  $r^x$ , essentially the upper limit of  $e^x$ . As indicated in Equation (10), the resource should be sought by  $\tau_{ll}$ ; thus, the count of requests from  $\tau_{ll}$  to  $r^x$  should be non-zero, or in mathematical terms,  $N_{ll}^x > 0$ .

Furthermore, the resource resulting in the blocking effects can be global, attributed to the MSRP's provision that  $\tau_{ll}$  maintains its non-preemptive status during both request and execution phases. Conversely, the said resource might be local, boasting a ceiling priority surpassing that of  $\tau_i$ . This allows  $\tau_{ll}$  to perform under an elevated priority, in turn obstructing  $\tau_i$ . This scenario is symbolized by the condition  $Pri(r^x, P(\tau_i)) \geq Pri(\tau_i)$ , where  $Pri(r^x, P(\tau_i))$  reveals the priority ceiling of  $r^x$  when the resource is specific to the processor that  $\tau_i$  is allocated  $(P(\tau_i))$ . Necessary notations are concluded in Table 3.

| Notation              | Definition                                                             |  |

|-----------------------|------------------------------------------------------------------------|--|

| $\widehat{C}_i$       | Worst-case execution time of task $\tau_i$ including shared resource   |  |

|                       | access time                                                            |  |