# Modelling and Simulation for Power Distribution Grids of 3D Tiled Computing Arrays

# Pakon Thuphairo

PhD

University of York

Computer Science

April 2023

## **Abstract**

This thesis presents modelling and simulation developments for power distribution grids of 3D tiled computing arrays (TCAs), a novel type of paradigm for HPC systems, and tests the feasibility of such systems for HPC systems domains.

The exploration of a complex power-grid such as those found in the TCA concept requires detailed simulations of systems with hundreds and possibly thousands of modular nodes, each contributing to the collective behaviour of the system. In particular power, voltage, and current behaviours are critically important observations.

To facilitate this investigation, and test the hypothesis, which seeks to understand if scalability is feasible for such systems, a bespoke simulation platform has been developed, and (importantly) validated against hardware prototypes of small systems.

A number of systems are simulated, including systems consisting of arrays of 'balls'. Balls are collections of modular tiles that form a ball-like modular unit, and can then themselves be tiled into large scale systems. Evaluations typically involved simulation of cubic arrays of sizes ranging from 2x2x2 balls up to 10x10x10.

Larger systems require extended simulation times. Therefore models are developed to extrapolate system behaviours for higher-orders of systems and to gauge the ultimate scalability of such TCA systems. It is found that systems of 40x40x40 are quite feasible with appropriate configurations.

Data connectivity is explored to a lesser degree, but comparisons were made between TCA systems and well known comparable HPC systems, and it is concluded that TCA systems can be built with comparable data-flow and scalability, and that the electrical and engineering challenges associated with the novelty of 3D tiled systems can be met with practical solutions.

## Author's declaration

I declare that this thesis is a presentation of original work and has been done in collaboration with the following:

Pakon Thuphairo: Under supervision for the design and implementation of the models and simulation framework, and prototype discussions, in this thesis.

Christopher Crispin-Bailey (Supervisor): Previous theoretical investigation of TCA concept, contributions to prototype designs and measurements, assisted with the design entry and 3D-printing of hex-tile frames.

Anthony Moulds: Senior experimental officer, assisted with the prototype PCB implementation and electrical measurements due to the requirements for a high wattage bench-testing setup.

Jim Austin: We acknowledge the previous work and patents as published by Professor James Austin (Retired).

This work has not previously been presented for a degree or other qualification at this University or elsewhere. All sources are acknowledged as references.

Aspects of the tile modelling and a brief introduction of the simulation framework in this thesis, have been published in the following paper by this PhD candidate and co-authors:

continued...

P. Thuphairo, C. Bailey, A. Moulds and J. Austin, "Investigating Novel 3D Modular Schemes for Large Array Topologies: Power Modeling and Prototype Feasibility," 2022 25th Euromicro Conference on Digital System Design (DSD), Maspalomas, Spain, 2022, pp. 268-275, doi: 10.1109/DSD57027.2022.00044.

"In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of the University of York's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink. If applicable, University Microfilms and/or ProQuest Library, or the Archives of Canada may supply single copies of the dissertation."

Submitted manuscripts and additional technical reports relating to the Hex-tile project are given in Appendix A.

# **Acknowledgements**

First of all, I would like to express thanks to my supervisor, Dr Christopher Crispin-Bailey, for his continuous supervision, guidance, efforts, and support for many things from the beginning of my PhD journey with the COVID-19 pandemic starting just after my first PhD year. Without him, it would have never led to this thesis completion.

Anthony Moulds, a senior experimental officer, who joint the TCA project during the COVID-19. I would also like to thank him, and also with my supervisor, in the collaborative work on significant parts in building hardware prototypes. I really appreciate not only his collaboration in the hardware prototypes, but also the board model with the switching regulator employed in the prototypes, and his advice regarding SPICE designs and simulations.

In addition, I would also thank all the departmental members of technical staff involved with assembly of the hardware prototypes and anything in the research project. In fact, not only the departmental level, much appreciation will also go to the University of York's IT support team who constantly helped me with simulation-related resources, (IGGI machines), which more than one time, went wrong unintentionally by myself. Viking - University of York Research Computing Cluster), was also part of the simulation activities in this thesis. Unfortunately, with the limited time-frame and some complications in the simulation issues, the cluster simulation framework is still in an experimental stage. However, the experience of interacting with a high performance computing cluster is extremely valuable.

continued...

I would also like to thank the Royal Thai Government for awarding me a full PhD scholarship. Some parts of this scholarship also contribute to partial components in the hardware prototypes and also the equipment for some hardware experiments in this thesis.

I would also like to thank everyone from Rajamangala University of Technology Rattanakosin, the university I have been working for since before I started my PhD degree, who has supported me for all the preparation processes before coming to the UK for my PhD course.

Apart from the above, I wish to thank my father and mother who have always been supporting me with many things since birth. Without their kindness, it would have never been me so far. I would also like to thank everyone else both in Thailand and the UK that helped me before and throughout years of my PhD journey.

# **List of Contents**

#### **List of Contents**

| 1 | Intro | oductio  | n                                                             | 1  |

|---|-------|----------|---------------------------------------------------------------|----|

|   | 1.1   | Synops   | iis                                                           | 1  |

|   | 1.2   | Motiva   | tion                                                          | 2  |

|   | 1.3   | Thesis   | Scope                                                         | 3  |

|   | 1.4   | Researc  | ch Hypothesis and Objectives                                  | 4  |

|   |       | 1.4.1    | Definition                                                    | 5  |

|   |       | 1.4.2    | Research Objectives                                           | 6  |

|   | 1.5   | Contrib  | outions                                                       | 8  |

|   |       | 1.5.1    | Methodology                                                   | 8  |

|   |       | 1.5.2    | Findings                                                      | 9  |

|   | 1.6   | Thesis   | Organisation                                                  | 10 |

| 2 | Field | l Surve  | y and Literature Review                                       | 11 |

|   | 2.1   | Existing | g Concepts and Principles Relating to TCA                     | 15 |

|   |       | 2.1.1    | Short Introduction to TCA                                     | 15 |

|   |       | 2.1.2    | TCA-concept Definition                                        | 16 |

|   |       | 2.1.3    | Geometrical Properties of Ball Arrays                         | 17 |

|   | 2.2   | Mappir   | ng Between Logical and Physical Topologies                    | 20 |

|   | 2.3   | Paralle  | I/Distributed Computer Packaging                              | 25 |

|   |       | 2.3.1    | Rack-mount Packaging                                          | 25 |

|   |       | 2.3.2    | Non rack-mount Packaging                                      | 27 |

|   | 2.4   | TCA P    | Physical Scalability: Possible Constraints                    | 36 |

|   |       | 2.4.1    | Power Networks in TCA Systems                                 | 36 |

|   |       | 2.4.2    | Physical Engineering Factors                                  | 37 |

|   | 2.5   | Related  | d Concepts for Power Modelling                                | 39 |

|   |       | 2.5.1    | Overview of Power Modelling in Parallel/Distributed Computers | 39 |

|   |     | 2.5.2               | Typical Inter-board Level Power Delivery in Parallel/Distributed |    |

|---|-----|---------------------|------------------------------------------------------------------|----|

|   |     |                     | Computers                                                        | 40 |

|   |     | 2.5.3               | Power Modelling at the Computing-board Level                     | 42 |

|   |     | 2.5.4               | Voltage Regulators                                               | 43 |

|   |     | 2.5.5               | Switching Regulator: Average VS Complex Models                   | 46 |

|   | 2.6 | SPICE               | Simulators                                                       | 48 |

|   | 2.7 | Маррі               | ng Tasks Into a Parallel/Distributed Machine                     | 48 |

|   | 2.8 | Summ                | ary and Implications for Hypothesis                              | 50 |

| 3 | Har | dware a             | and Model Development                                            | 53 |

|   | 3.1 | Releva              | nt Research Objectives                                           | 54 |

|   |     | 3.1.1               | Objective 1: Employing and Designing Models and Simulation       |    |

|   |     |                     | Tools                                                            | 54 |

|   |     | 3.1.2               | Objective 2: Hardware Validation                                 | 55 |

|   | 3.2 | Hardw               | are Prototypes                                                   | 57 |

|   | 3.3 | Arbitra             | ary Electrically-conductive Media Designs                        | 62 |

|   | 3.4 | Protot              | ype Models                                                       | 67 |

|   |     | 3.4.1               | Tile Modelling                                                   | 67 |

|   |     | 3.4.2               | Connector-pin Resistance Modelling                               | 68 |

|   |     | 3.4.3               | Board Modelling                                                  | 70 |

|   |     | 3.4.4               | Voltage Regulator Modelling                                      | 76 |

|   |     | 3.4.5               | Regulated Load Modelling                                         | 77 |

|   |     | 3.4.6               | Ball-array Modelling                                             | 77 |

|   |     | 3.4.7               | Power Source Modelling                                           | 79 |

|   | 3.5 | Valida <sup>-</sup> | tion Work and Results                                            | 79 |

|   |     | 3.5.1               | Study 1) Hardware Versus System Modelling                        | 79 |

|   |     | 3.5.2               | Study 2) Simplified Versus Switching Models                      | 81 |

|   | 3.6 | Chapte              | er Summary                                                       | 85 |

| 4 | TC  | A Powe              | r-grid Simulation Tools                                          | 87 |

|   | 4.1 | Releva              | nt Research Objectives                                           | 87 |

|   |     | 4.1.1               | Objective 1: Employing and Designing Models and Simulation       |    |

|   |     |                     | Tools                                                            | 87 |

|   |      | 4.1.2   | Objective 4: Optimised Power Distribution                | 89  |

|---|------|---------|----------------------------------------------------------|-----|

|   |      | 4.1.3   | Objective 6: Simulation Framework Documentation          | 90  |

|   | 4.2  | Overall | Simulation Framework                                     | 91  |

|   | 4.3  | Tile Na | aming Convention                                         | 93  |

|   |      | 4.3.1   | Facet Naming Convention                                  | 94  |

|   |      | 4.3.2   | Edge Numbering Convention                                | 94  |

|   |      | 4.3.3   | Further Detail                                           | 94  |

|   | 4.4  | Connec  | ctor-pin Terminal-name Replacement Convention            | 96  |

|   | 4.5  | System  | Generator                                                | 97  |

|   |      | 4.5.1   | Ball-array Generator                                     | 98  |

|   |      | 4.5.2   | External Power/ground Rails Renaming                     | 101 |

|   | 4.6  | Manua   | I SPICE-file Editing                                     | 102 |

|   | 4.7  | Simula  | tion Modules                                             | 103 |

|   |      | 4.7.1   | Power-network Simulator                                  | 103 |

|   |      | 4.7.2   | Power Allocation Schemes                                 | 109 |

|   |      | 4.7.3   | Uniform Power Simulator                                  | 118 |

|   |      | 4.7.4   | Non-uniform Power Simulator                              | 118 |

|   | 4.8  | SPICE   | Simulator                                                | 128 |

|   | 4.9  | Chapte  | er Summary                                               | 128 |

| 5 | Scal | ability | Evaluations                                              | 131 |

|   | 5.1  | Releva  | nt Research Objectives                                   | 133 |

|   |      | 5.1.1   | Objective 3: Fundamental Simulation Experiments          | 133 |

|   |      | 5.1.2   | Objective 4: Optimised Power Distribution                | 135 |

|   |      | 5.1.3   | Objective 5: Scalability Evaluations                     | 136 |

|   | 5.2  | Uniforn | m Power Allocation                                       | 137 |

|   | 5.3  | Non-ur  | niform Power Allocation                                  | 150 |

|   |      | 5.3.1   | Brute-force Simulation for Relative-position Scheme      | 150 |

|   |      | 5.3.2   | System-level Regulated Load-power and Connector-pin Cur- |     |

|   |      |         | rent Optimisations                                       | 155 |

|   |      | 5.3.3   | System-level Power Efficiency                            | 163 |

|   | 5 4  | Total 9 | System Power                                             | 169 |

| Re | References 223 |                                         |                                                              |       |

|----|----------------|-----------------------------------------|--------------------------------------------------------------|-------|

| В  | Exai           | mple SI                                 | PICE File                                                    | 219   |

|    | A.3            | Hex-tile                                | e PCB Layouts                                                | 217   |

|    | A.2            |                                         | Report for Internal Funding Award (Hex-tile Project)         |       |

|    | A.1            | Submit                                  | ted Manuscript of DSD2022 Paper                              | 202   |

| Α  | Pub            | lished \                                | Vork                                                         | 201   |

| •  |                |                                         |                                                              |       |

| Aı | ppen           | dices                                   |                                                              | 199   |

|    | 0.5            | rillal N                                | emarks                                                       | 190   |

|    | 6.3            |                                         | Other Engineering Concerns                                   |       |

|    |                | <ul><li>6.2.10</li><li>6.2.11</li></ul> | Cooling Systems                                              |       |

|    |                | 6.2.9                                   | Simulation on Computing Cluster                              | 195   |

|    |                | 6.2.8                                   | Hardware Prototype Improvements                              |       |

|    |                | 6.2.7                                   | System Computing Performance Analysis                        |       |

|    |                | 6.2.6                                   | Improved Visualisations                                      | 194   |

|    |                | 6.2.5                                   | Multiple Optimisation Algorithms for Power Allocation        | 194   |

|    |                | 6.2.4                                   | Node Power Model                                             | 194   |

|    |                | 6.2.3                                   | Arbitrary Inter and Intra-unit Level Power Media             | 194   |

|    |                | 6.2.2                                   | Investigation of External Power Designs                      |       |

|    |                | 6.2.1                                   | Lower Hop Counts                                             | 193   |

|    | 6.2            |                                         | e Future Work                                                | 192   |

|    |                | 6.1.4                                   | Limitations and Assumptions                                  | 191   |

|    |                | 6.1.3                                   | Tool Design Experiences                                      | 189   |

|    |                | 6.1.2                                   | Contributions                                                | 188   |

|    |                | 6.1.1                                   | Research Hypothesis and Objectives                           | 183   |

|    | 6.1            | Conclu                                  | sions                                                        | 183   |

| 6  | Con            | clusions                                | s and Future Work                                            | 183   |

|    | 5.6            | Compa                                   | rison of Large-scale Traditional Rack-mount Systems with TCA | s1/9  |

|    | 5.5            |                                         | nary Topological Analyses, Simulations, and Comparisons      |       |

|    |                | ь                                       | T                                                            | 4 = 0 |

# **List of Figures**

| 1.1 | Mapping a couple of separate groups of tasks into different packaging          |    |

|-----|--------------------------------------------------------------------------------|----|

|     | systems. (b) is a representation of the two groups mapped into three           |    |

|     | horizontal computing-boards, each with 9 PEs, in a rack-mount system.          |    |

|     | (c) represents a mapping of the tasks into 27 tiles in a TCA system            | 2  |

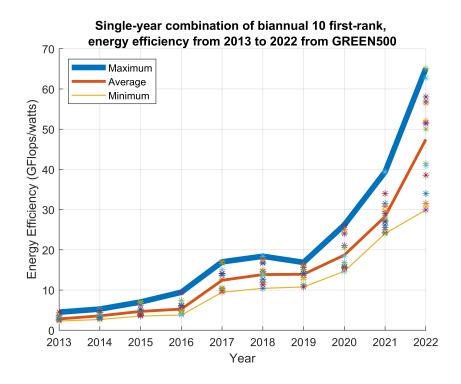

| 2.1 | Energy efficiency trends reported by [9]. Each year in the graph is a com-     |    |

|     | bination of biannual 10 first-rank reports in June and November                | 13 |

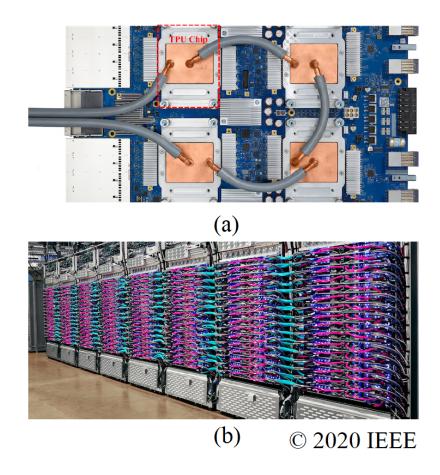

| 2.2 | Examples of large scale system cooling, showing (a) TPU v3 unit, (b) TPU       |    |

|     | v3 Pod. (reprinted from Figure 1(b-c) in [10])                                 | 14 |

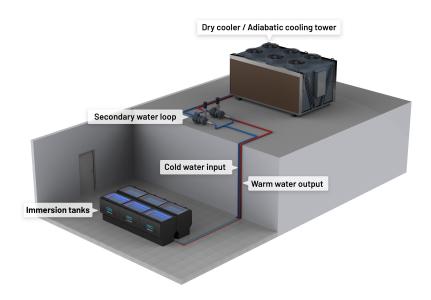

| 2.3 | Submer Immersive cooling system. (reprinted from [11])                         | 14 |

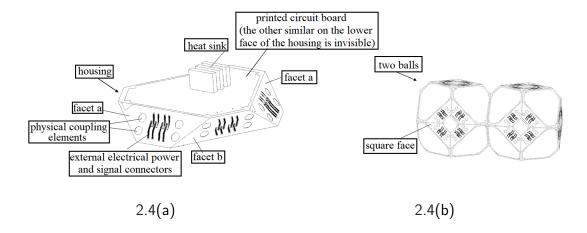

| 2.4 | Example of a TCA design proposed as 'Computing devices' in [12]. (a)           |    |

|     | shows tile structure, (b) shows ball structure, composed from tiles. (adapted  |    |

|     | from Figure 1 and 5 in [12], respectively)                                     | 15 |

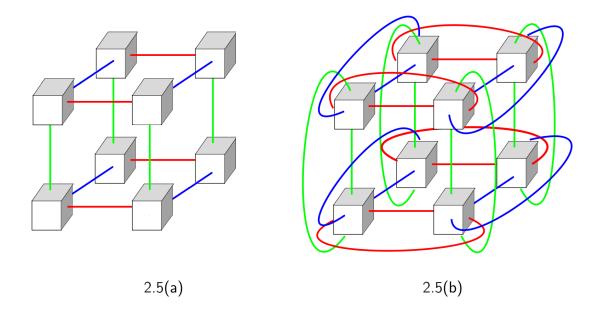

| 2.5 | Logical views of a 2x2x2 3D-mesh and 3D-torus topologies. (a) depicts a        |    |

|     | 3D-mesh topology (adapted from [13]), and (b) depicts a 3D-torus topol-        |    |

|     | ogy [13].)                                                                     | 17 |

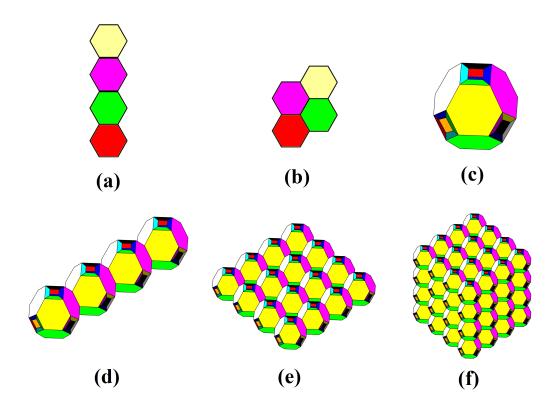

| 2.6 | Example implementation alternatives of the TCA concept. (a) shows 1D           |    |

|     | tile-level array of 4 modules, whilst (b) shows a group of tile-level 2D array |    |

|     | of 2x2 modules, and a possible 3D construction from the tile level can be      |    |

|     | seen in (c) as a complete 3D array of 2x2x2 modules. Instead of tile-level     |    |

|     | composition, each module may also be alternatively implemented as a            |    |

|     | single ball-shaped object. (d) depicts a row of 1D array of 4 modules. (e)     |    |

|     | constructs a 2D-array of 4x4 modules, whilst a 3D-array of 4x4x4 modules       |    |

|     | can be constructed as shown in (f)                                             | 18 |

| 2.7 | A logical (machine-packaging independent) computing topology of 10 tasks.      | 21 |

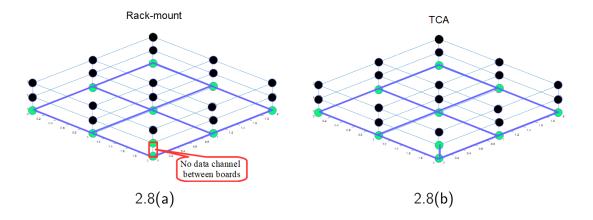

| 2.8  | Black dots represent occupied nodes, and green dots are the tasks being        |    |

|------|--------------------------------------------------------------------------------|----|

|      | mapped. (a) Mapping a set of tasks on a plane of 3x3 nodes, and a single       |    |

|      | node on a different board in a rack-mount system. (b) The same mapping         |    |

|      | on a TCA system with the same system size. As the last task is mapped          |    |

|      | on an adjacent node above, and with the availability of a channel in the       |    |

|      | physical third dimension, the logical computing topology can be maintained.    | 22 |

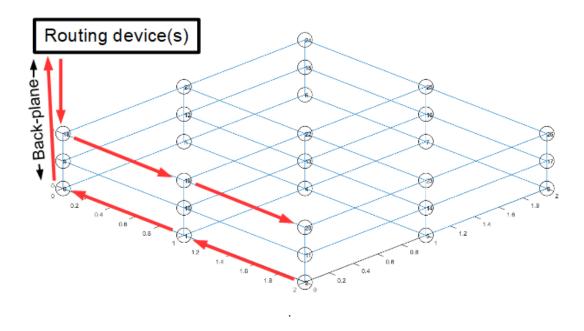

| 2.9  | The shortest route of a data unit travelling from node 2 to node 20 between    |    |

|      | computing boards in a rack-mount system, resulting in a hop count, at          |    |

|      | least, of 6. It is assumed that all the nodes at the far-end of each board     |    |

|      | are directly connected to a routing system                                     | 23 |

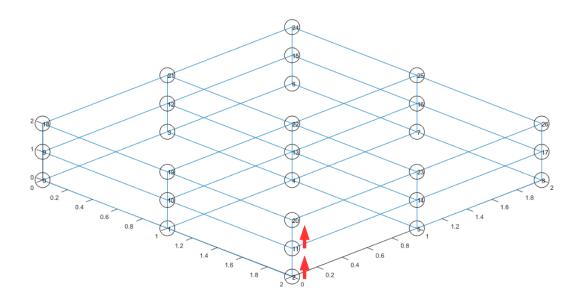

| 2.10 | The shortest route of a data unit travelling from node 2 to node 20 between    |    |

|      | a couple of adjacent balls in a TCA system (node 2 and node 11 reside in       |    |

|      | the same ball, as a ball consists of eight tiles), resulting in a hop count of |    |

|      | 2. A single hop count can be achieved on 3D-torus implementation with          |    |

|      | a wrap-around channel                                                          | 24 |

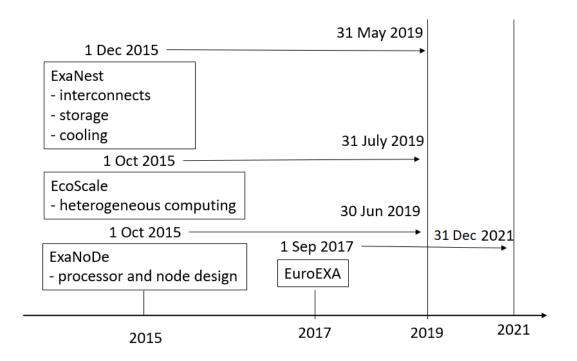

| 2.11 | Timeline of four recent examples of Exascale projects. The period of each      |    |

|      | project duration can be found in [20], [21], [16], [22]                        | 26 |

| 2.12 | Frontier supercomputer. (reprinted from [26])                                  | 26 |

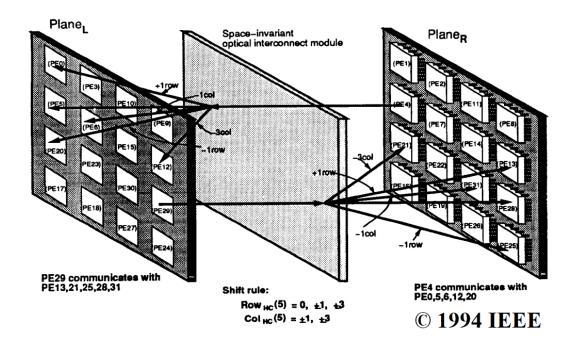

| 2.13 | A conceptual optical realization of the space-invariant five-cube network.     |    |

|      | (reprinted from Figure 7(b) in [31])                                           | 29 |

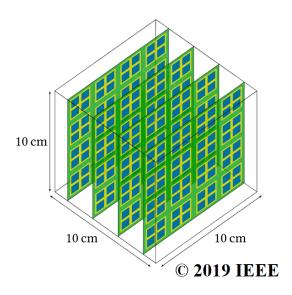

| 2.14 | Sketch of the HAEC Box. (reprinted from Figure 2(a) in [33])                   | 29 |

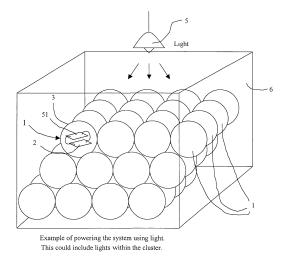

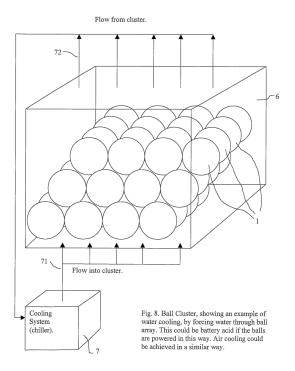

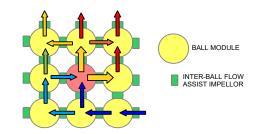

| 2.15 | An illustration of a cluster of ball-shaped computing devices. (reprinted      |    |

|      | from [35])                                                                     | 31 |

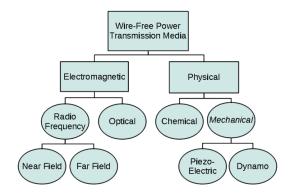

| 2.16 | Wire-free power transmission media. (reprinted from Figure 3.1 in [36]) .      | 32 |

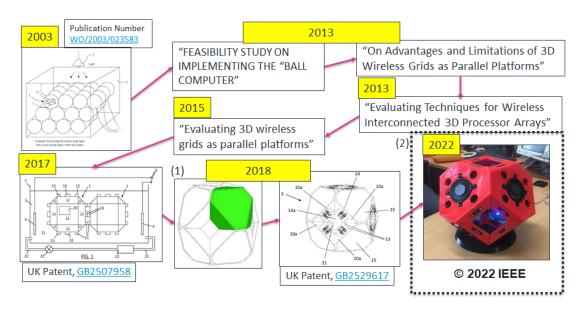

| 2.17 | Timeline of TCA concepts and its prior work in the series of development.      |    |

|      | All the details in the timeline can be found in [35], [36], [39], [34], [40],  |    |

|      | [41], [14], [12], and [42]. ( (1)-(2) reprinted from Figure 7 in [14], and     |    |

|      | Figure 8(c) in [42], respectively)                                             | 33 |

| 2.18 | A panorama of the SpiNNaker 1 million core machine. (reprinted from [43])      | 34 |

| 2.19 | Example water cooling system for the ball-shaped computing devices dis-        |    |

|      | cussed in Subsection 2.3.2. (reprinted from Figure 8 in [35])                  | 38 |

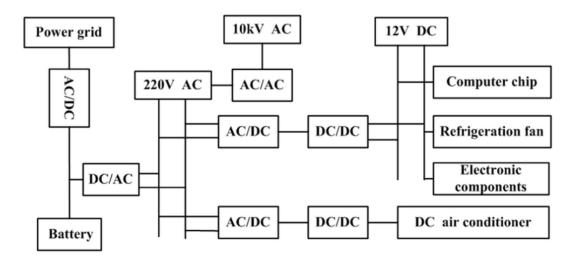

| 2.20 | Traditional data centre supply system. (reprinted from Figure 1 in $[54]$ ) .  | 41 |

|      |                                                                                |    |

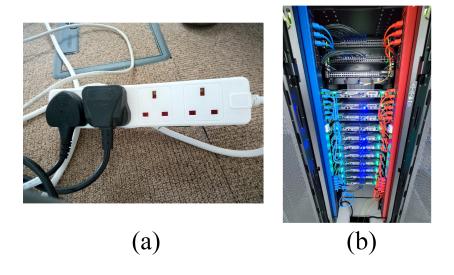

| 2.21 | Examples of power distribution units. (a) shows a power strip for AC power,   |    |

|------|-------------------------------------------------------------------------------|----|

|      | and (b) shows two rails of back-plane PDUs which can be found in a rack       |    |

|      | or cabinet. ((b) is reprinted from [55])                                      | 41 |

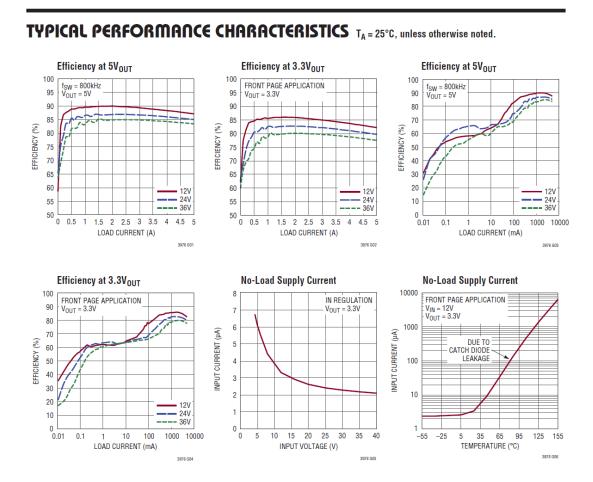

| 2.22 | Examples of switching regulator efficiencies with varying input voltages      |    |

|      | and load currents. (reprinted from 'Typical Performance Characteristics',     |    |

|      | page 4 in [65])                                                               | 45 |

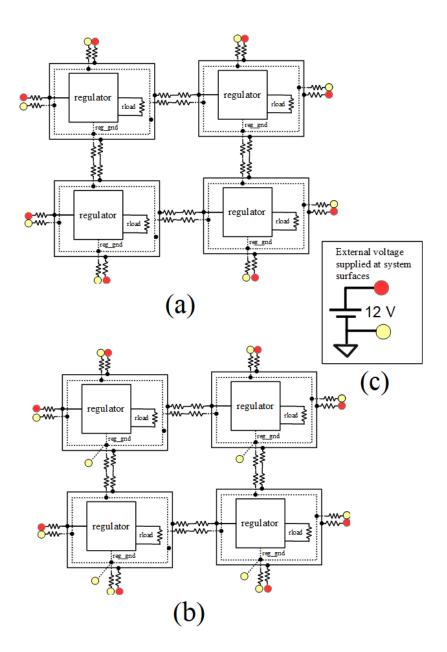

| 2.23 | B Example of grounding issue for a voltage regulator simulation model on      |    |

|      | a 2x2 conceptual computing boards in a TCA. Each of the resistors sur-        |    |

|      | rounding each module represents inter-node power medium resistance. (a)       |    |

|      | shows a correct modelling, whilst in (b), the ground of each regulator        |    |

|      | model is directly tied to the global ground of the SPICE simulation. (c)      |    |

|      | shows the global positive and negative (ground) rails. This example is only   |    |

|      | for illustrative purpose. In the actual TCA systems, it is considered much    |    |

|      | more complex due to the 3D meshed power network                               | 47 |

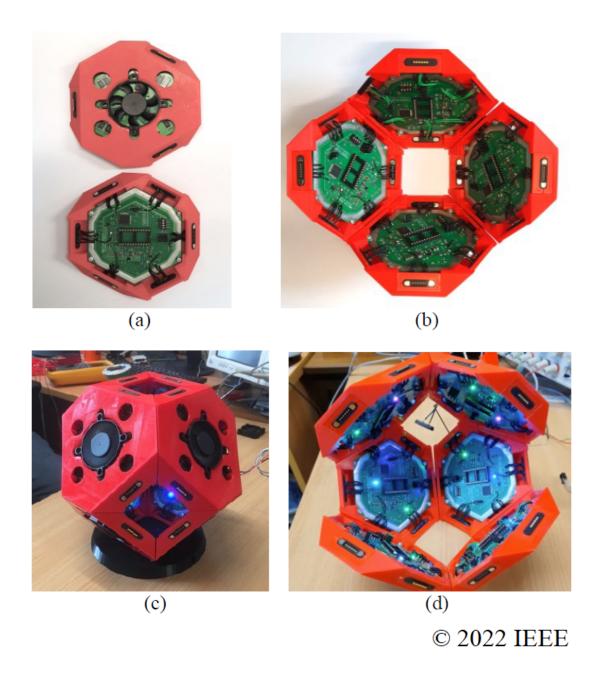

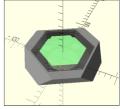

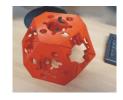

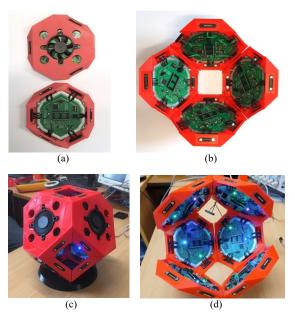

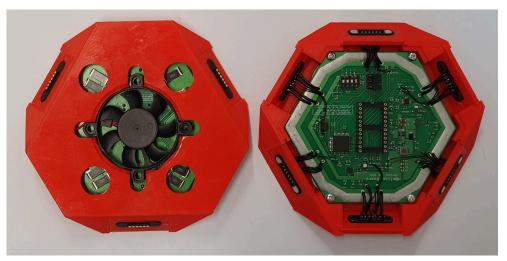

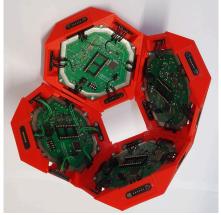

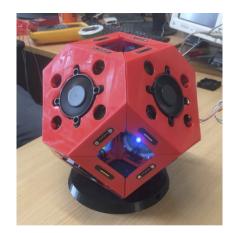

| 3.1  | (a) shows top and bottom views of a hex-tile prototype. (b) shows a half-     |    |

|      | ball (petal) composition. (c) shows eight tile-frames composed as a ball      |    |

|      | upon a power base-plate providing power via the trapezoidal faces. (d)        |    |

|      | illustrates a ball with two tiles removed, being powered and demonstrating    |    |

|      | different power loading by LED colours. (reprinted from Figure 8 in [42])     | 58 |

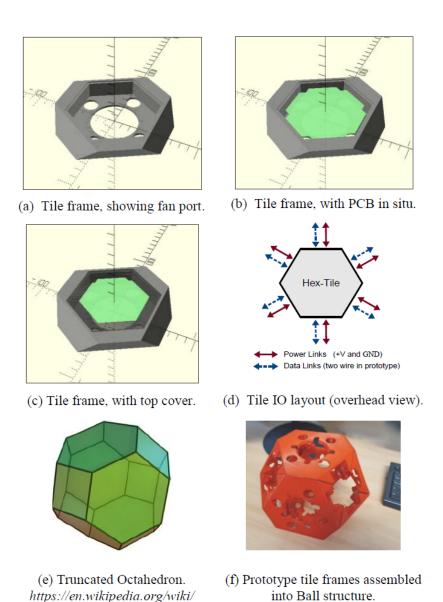

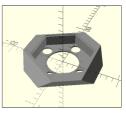

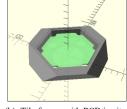

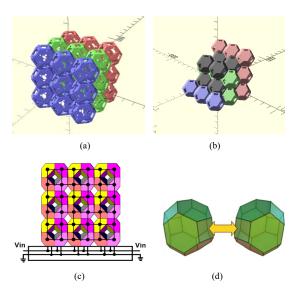

| 3.2  | Illustrations of conceptual designs and a hardware prototype. (a) illustrates |    |

|      | a conceptual model of the tile frame. Examples of possible materials are      |    |

|      | plastic or ceramic. In (b), the tile frame is shown with an embedded PCB      |    |

|      | or Multi-Chip-Module (MCM). As shown in (c), a tile may also be covered       |    |

|      | with a partially transparent material, allowing the visibility of components  |    |

|      | inside. (d) shows a possible data $I/O$ connectivity upon each tile edge,     |    |

|      | represented by the dashed/blue lines, whilst solid/red arrows show power      |    |

|      | and ground rails. Having composed a group of eight tiles in 3D, it can        |    |

|      | make up a truncated octahedron, a ball-like volume shown in (e). Finally,     |    |

|      | (f) illustrates a ball-frame prototype. (reprinted from Figure 1 in [42], (e) |    |

|      | is adapted from [71])                                                         | 59 |

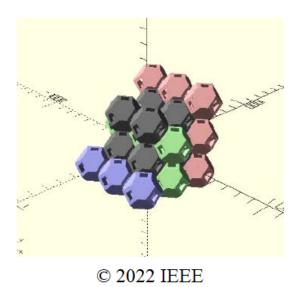

| 3.3 | Example of a double packed internal array of $2 \times 2 \times 2$ grey balls embedded   |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | in between the existing $3\times3\times3$ array. Some of the balls are removed to        |    |

|     | expose the internal balls. (reprinted from Figure 2(b) in [42])                          | 60 |

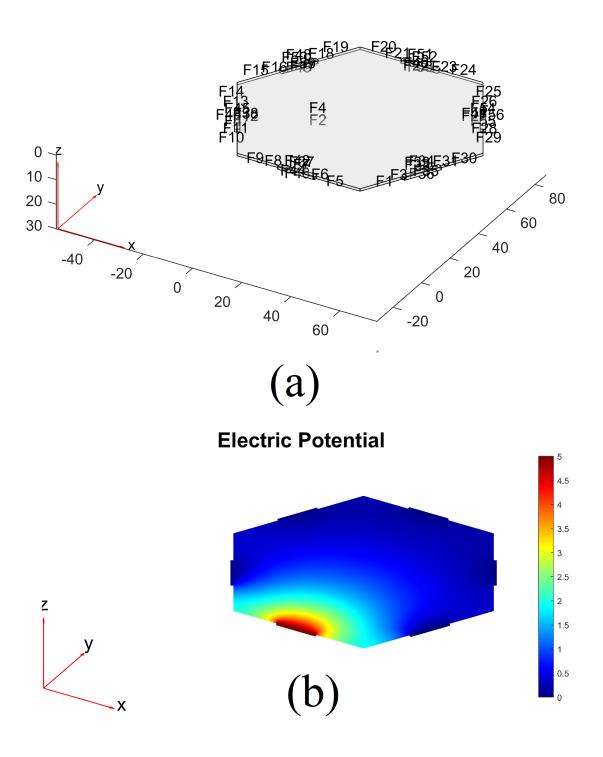

| 3.4 | Example DC conduction analysis (Electrical Potential) on a hexagonal-                    |    |

|     | shaped conductive medium. (a) shows a frame view with face numbers.                      |    |

|     | (b) gives an electrical potential distribution on the object. In this particular         |    |

|     | case, an electric potential of 5V is applied on a single rectangular edge,               |    |

|     | which can be obviously seen in the red area. All the other edges are applied             |    |

|     | with an electric potential of 0V                                                         | 64 |

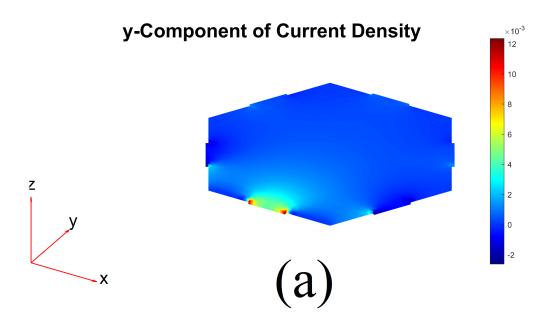

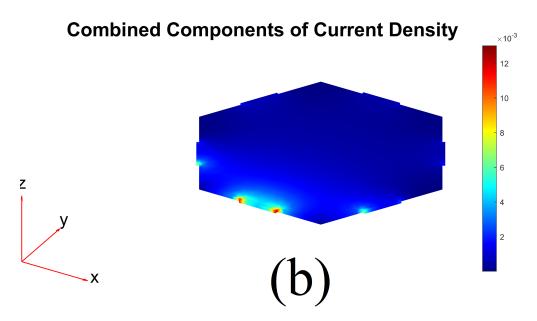

| 3.5 | Example DC conduction analysis (Current Density) on a hexagonal-shaped                   |    |

|     | conductive medium. (a) shows only the y-component of the current den-                    |    |

|     | sity, and (b) combines all the $x$ , $y$ , and $z$ components, of the hexagonal          |    |

|     | medium. As this medium shape is a thin 3D object, it can be roughly                      |    |

|     | considered that most of the currents flowing in this object are only in $\boldsymbol{x}$ |    |

|     | and y axes                                                                               | 65 |

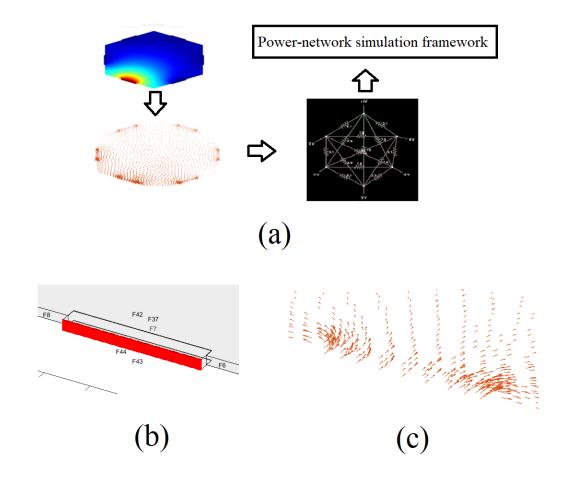

| 3.6 | Experimental custom electrically conductive medium shape modelling. a                    |    |

|     | possible design flow starts from modelling a custom shape, followed by                   |    |

|     | (a), electrical potential/DC conduction analysis, and finally building an                |    |

|     | equivalent lumped-resistor network. (b) illustrates an edge of the object                |    |

|     | showing an area for current flows. (c) shows a vector-field plot of current              |    |

|     | flows in the object. This experimental design can be part in the future                  |    |

|     | simulation framework                                                                     | 66 |

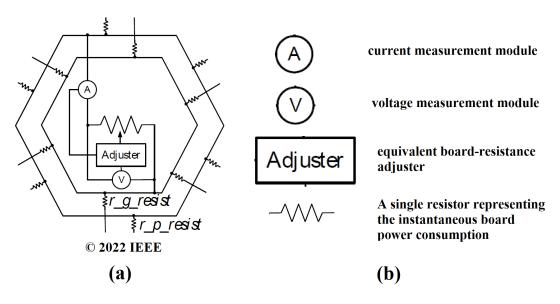

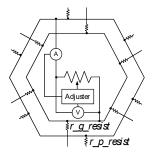

| 3.7 | (a) shows conceptualised tile model. (cropped from Figure 4 in [42]). The                |    |

|     | resistors named r_p_resist and r_g_resist represent positive and ground                  |    |

|     | rails of an edge power-connection. This inter-tile electrical medium resis-              |    |

|     | tance model can also be found in Figure 3.9. In (b), a legend describes                  |    |

|     | the rest of the simulation components                                                    | 68 |

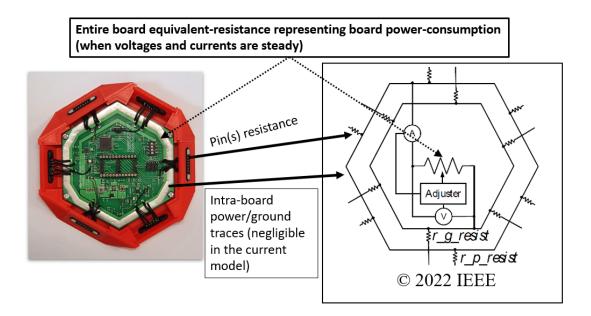

| 3.8 | Comparison of a tile prototype with the conceptualised tile model (cropped               |    |

|     | from Figure 4 in [42]). Although the voltage and current measurement                     |    |

|     | modules are added for simulation purposes, these modules can also be                     |    |

|     | optionally implemented in a physical tiled computing unit for power man-                 |    |

|     | agement purposes                                                                         | 69 |

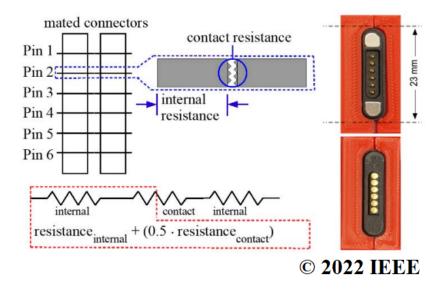

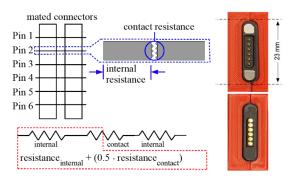

| 3.9  | Connector-pin resistance model. The resistor symbol named 'contact' par-             |    |

|------|--------------------------------------------------------------------------------------|----|

|      | tially framed with the red dashed line does not exist in the actual model            |    |

|      | used in a SPICE simulation file, but added in this figure for illustration           |    |

|      | purposes. The contact resistance occurring between a mated pin-pair can              |    |

|      | be split into halves and equally be added to the 'internal' resistances on           |    |

|      | both sides for simulation purposes. A photograph of the red-edge connec-             |    |

|      | tor detachable housing taken from the prototypes. (reprinted from Figure             |    |

|      | 3 in [42]))                                                                          | 70 |

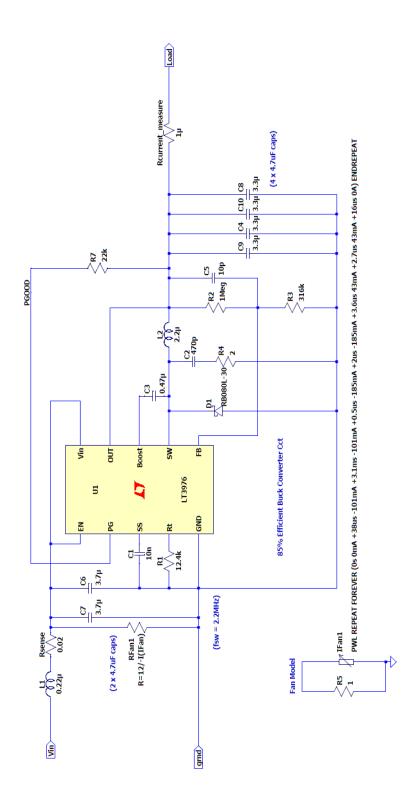

| 3.10 | Board model with the switching regulator model                                       | 73 |

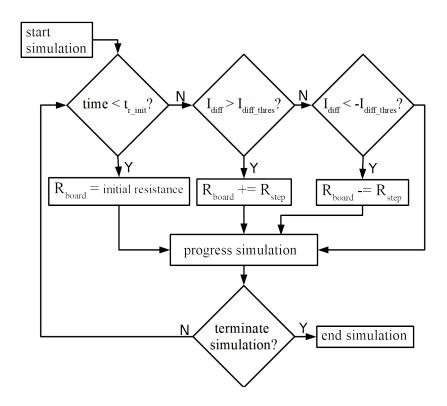

| 3.11 | Overall mechanism of the circuit-based board resistance adjuster during a            |    |

|      | SPICE simulation.                                                                    | 74 |

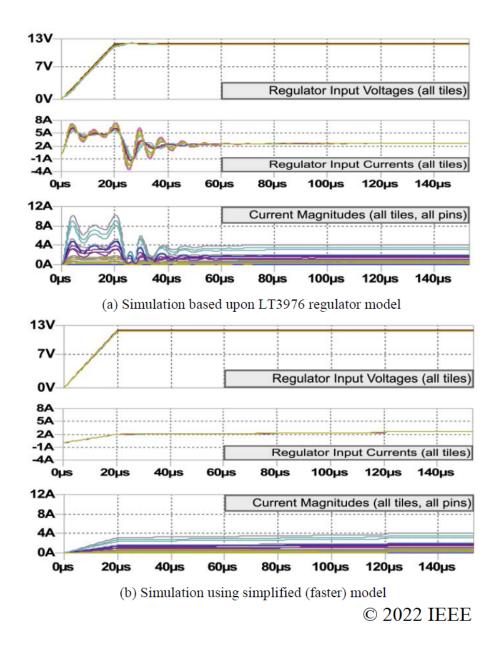

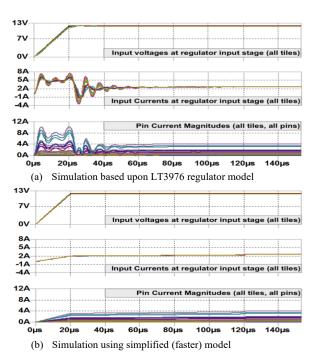

| 3.12 | Simulation results used for validating the simplified board model (curve-            |    |

|      | fitted model), compared against the same board model using the full man-             |    |

|      | ufacturer's precise $LT^{\text{!`}}3976$ regulator SPICE representation, as shown in |    |

|      | Figure 3.10. In this validation, a system of 3x3x3-ball was used for both            |    |

|      | simulations, as this is the smallest ball-array to contain at least an in-           |    |

|      | ner ball to reflect voltage drops. (a) shows the simulation result of the            |    |

|      | full prototype-board model, and (b) shows the simulation result of the               |    |

|      | simplified board model. (reprinted from Figure 5 in [42])                            | 84 |

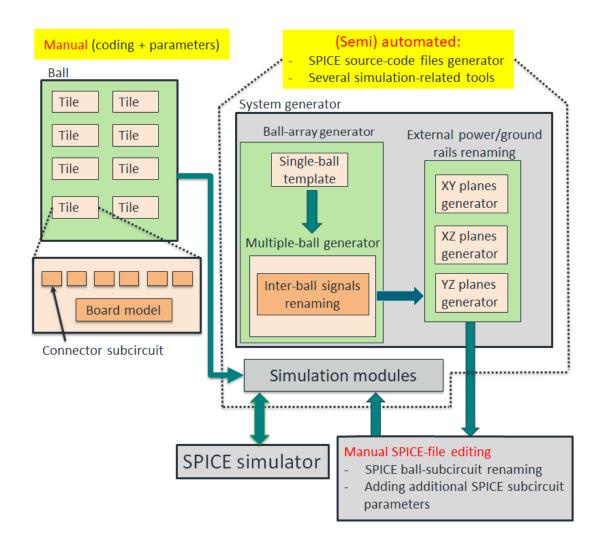

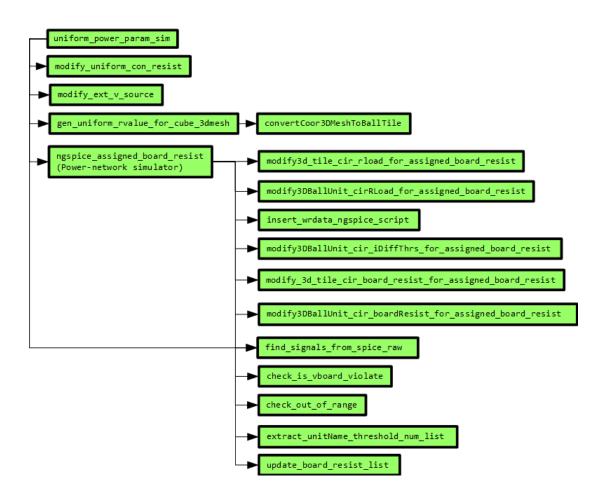

| 4.1  | Overall simulation framework. Some details in the automated area are                 |    |

|      | omitted and encapsulated for a concise view of the whole framework                   | 93 |

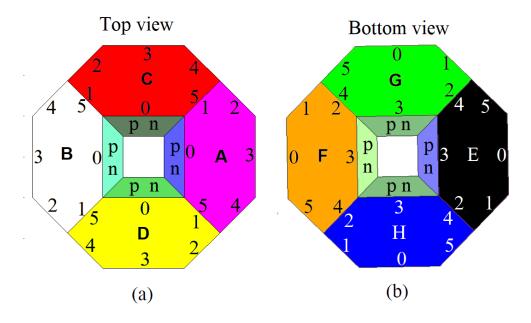

| 4.2  | Visualisation of tile naming convention. (a) visualises the top view of a ball,      |    |

|      | whilst (b) is for the bottom view, where Facet 'E' is directly underneath            |    |

|      | Facet 'A' when a ball is viewed from above, and the same positions for               |    |

|      | the rest. The square at the centre is one of the six holes for cooling. p and        |    |

|      | n are the names for positive and negative (ground) rails on a trapezoidal            |    |

|      | facet                                                                                | 95 |

|      |                                                                                      |    |

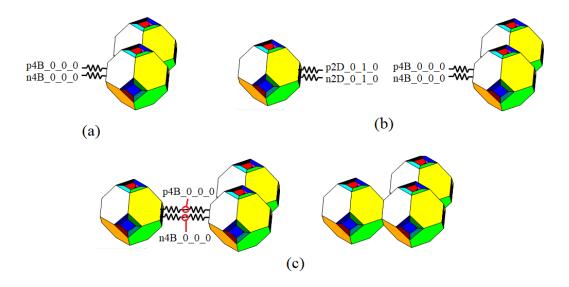

| 4.3 | Example of connector-pin resistance terminal name change of a ball group.           |     |

|-----|-------------------------------------------------------------------------------------|-----|

|     | (a) shows only a couple of resistor names. In (b), a newly added ball is            |     |

|     | generated with its own resistor names at the edge to be coupled. In (c),            |     |

|     | The names of the new-ball resistors replaced with the ball to which it is           |     |

|     | coupled, finally modelling a new ball coupled to an existing system                 | 97  |

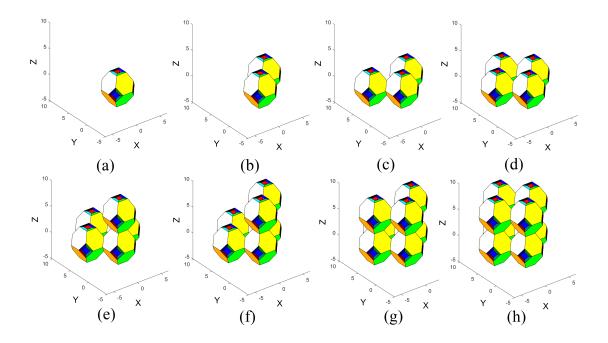

| 4.4 | Step-by-step example of balls coupled in a SPICE-file of a system gener-            |     |

|     | ation, starting from (a) towards a complete system in (h), respectively.            |     |

|     | When a ball is added, the SPICE node names of the connector-pin resistor            |     |

|     | model at the ball-edge connected to a previously generated ball in each             |     |

|     | dimension will be replaced                                                          | 99  |

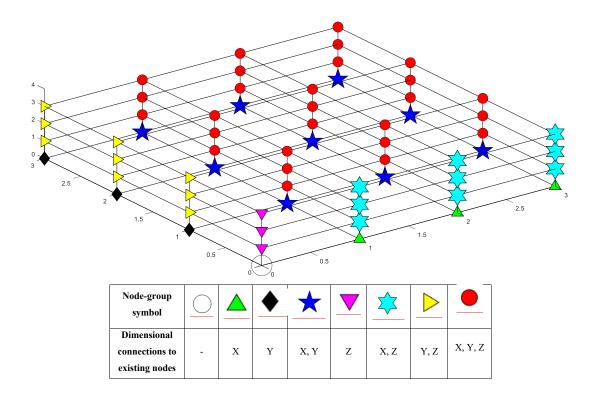

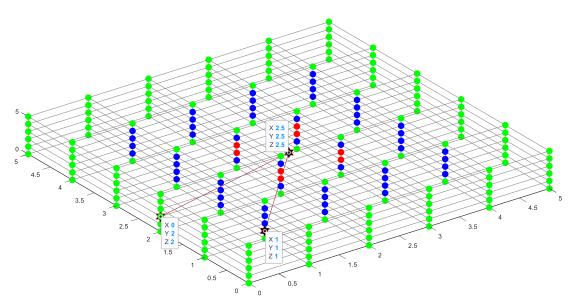

| 4.5 | 4x4x4-ball connection cases during a SPICE-file generation, and a leg-              |     |

|     | end table. Except a transparent circle illustrating the first node generated        |     |

|     | at the coordinates $(0,0,0)$ , when adding a node represented by a unique           |     |

|     | colour/symbol shown in the legend table, it will be coupled with at least           |     |

|     | one existing node, depending on which location it is added to. For instance,        |     |

|     | a red circle node is coupled to the existing nodes in X, Y, and Z dimensions.       | 100 |

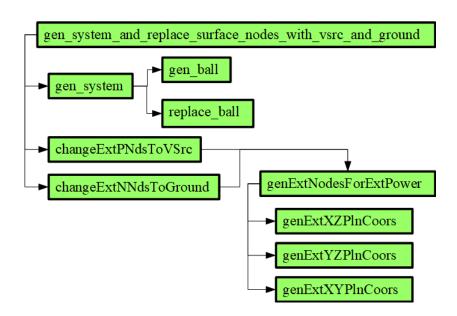

| 4.6 | Function calls of TCA system generator and external voltage-source re-              |     |

|     | naming                                                                              | 101 |

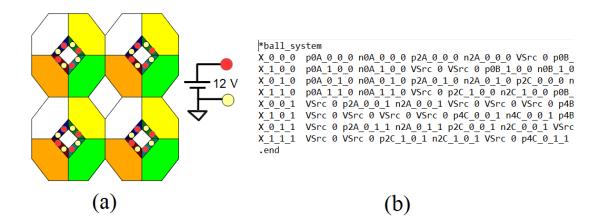

| 4.7 | External rails renaming. In (a), this particular case, a single voltage-source      |     |

|     | of 12V is applied to all of the external pins (some external pins are invisible     |     |

|     | due to a 2D surface illustration). In real implementation, multiple pins at         |     |

|     | each edge can be used for each power/round rail to allow more current               |     |

|     | tolerance. (b) shows an incomplete code-snippet of the generated system.            | 102 |

| 4.8 | An $LTspice^{\mathbb{R}}$ implementation of the whole board model with the circuit- |     |

|     | based board-resistance adjuster in this thesis. This implementation is re-          |     |

|     | ferred to as 'adjuster' published in [42], and supports only one regulated          |     |

|     | load-resistance (power) during a simulation. Thus, a separate simulation            |     |

|     | board-model file is needed for another load power consumption. Except               |     |

|     | 'r_board_resistance', the rest of the block modules and lines of code are           |     |

|     | part of the adjuster. '+' sign at the beginning is for the continuation of          |     |

|     | the line. The line with 'b_i_diff' implements the curve-fitting equation. $\ .$     | 106 |

|     |                                                                                     |     |

| 4.9  | Illustration of the last three data-points of board resistance for calculating      |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | 'rate of change' in the variable R-step mode. (a) shows the case that the           |     |

|      | third data-point resides in the bounding up range, resulting in reverting           |     |

|      | the latest Rstep to the previous one. (b) is the acceptable range to double         |     |

|      | the Rstep value, accelerating the reduction of board-resistance to more             |     |

|      | quickly approach the board input voltage-current profile                            | 109 |

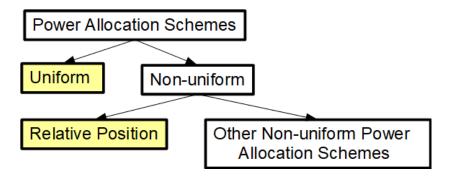

| 4.10 | Possible hierarchical power allocation schemes in TCA                               | 110 |

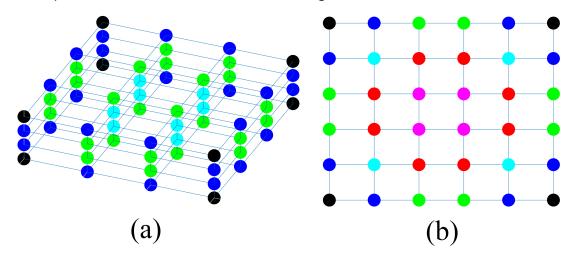

| 4.11 | Visualisations of a couple of relative-position schemed TCAs. (a) shows a           |     |

|      | 3D-view of a 4x4x4-tile, and (b) shows only a 2D-surface of a 6x6x6-tile            |     |

|      | due to the abundant quantity of relative coloured-groups of internal 3D             |     |

|      | layers. The same colours in each of the arrays in (a) and (b) represent the         |     |

|      | same allocated amount of power.                                                     | 111 |

| 4.12 | Example showing that a two-point distance in a TCA is not valid for check-          |     |

|      | ing whether nodes (tiles) are equally impacted by external fully connected          |     |

|      | power. Even though the two coordinates of $(0,2,2)$ and $(1,1,1)$ have the          |     |

|      | same two-point distance of 2.5981 units from the system-centre coordi-              |     |

|      | nates (2.5, 2.5, 2.5), the first node is in the outermost layer, whilst the         |     |

|      | second node is in the first inner one. It is noted that the coloured nodes          |     |

|      | in this example show cubic layers, whilst Figure 4.11 explains a different          |     |

|      | subset node grouping, relative-position scheme                                      | 112 |

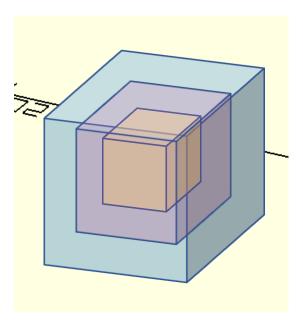

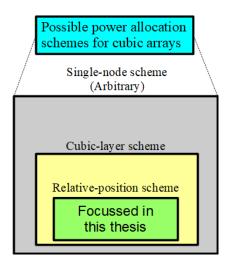

| 4.13 | Example three cubic layers of nodes as a possible power allocation scheme           |     |

|      | for TCA systems                                                                     | 113 |

| 4.14 | Diagram showing relations amongst power allocation schemes for cubic-               |     |

|      | array systems.                                                                      | 113 |

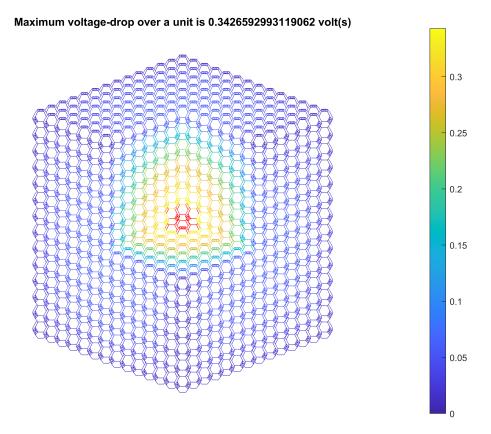

| 4.15 | TCA system illustrating voltage drops over the entire system. In this par-          |     |

|      | ticular system, for an illustrative purpose a ball is implemented as the            |     |

|      | smallest unit. Whilst this thesis focuses on a tile as the smallest unit. $\ \ .$ . | 116 |

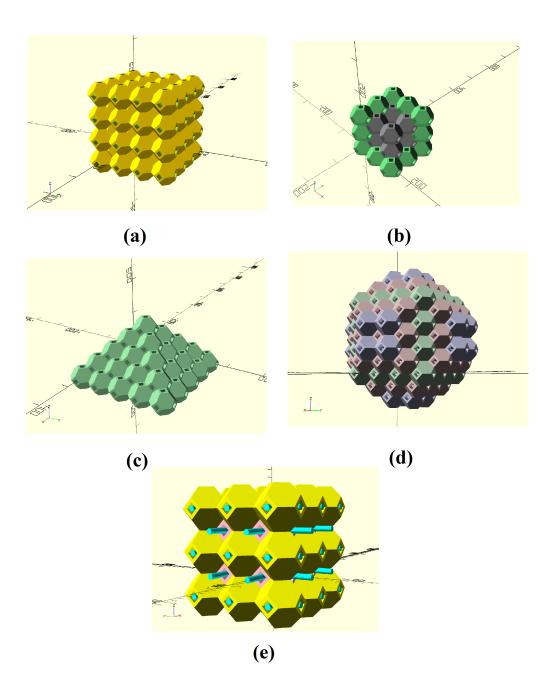

| 4.16 | Examples of different system shapes. (a) simple 3D mesh. (b) non-                   |     |

|      | complete 3D mesh with partial outer layer nodes removed. (c) pyramid                |     |

|      | shaped system (d) sphere (e) simple 3D mesh similar to (a) but using a              |     |

|      | double-packed array (pink nodes packed between yellow), and showing the             |     |

|      | flow channels for cooling highlighted in blue.                                      | 117 |

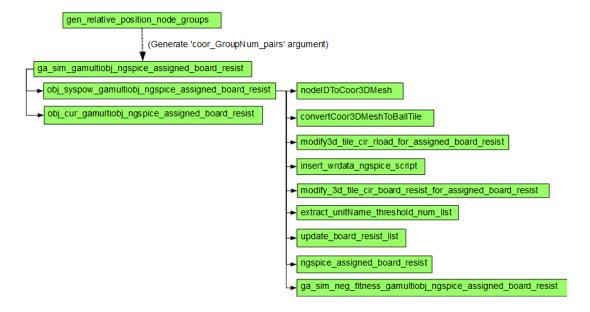

| 4.17 | Function calls of TCA system uniform power simulator                                                 | 119 |

|------|------------------------------------------------------------------------------------------------------|-----|

| 4.18 | Function calls of TCA system non-uniform (GA) power simulator                                        | 119 |

| 4.19 | Mechanism of the objective 1 and 2 associating with each other for SPICE-                            |     |

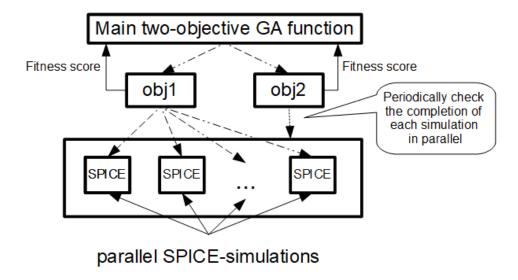

|      | simulation instances                                                                                 | 122 |

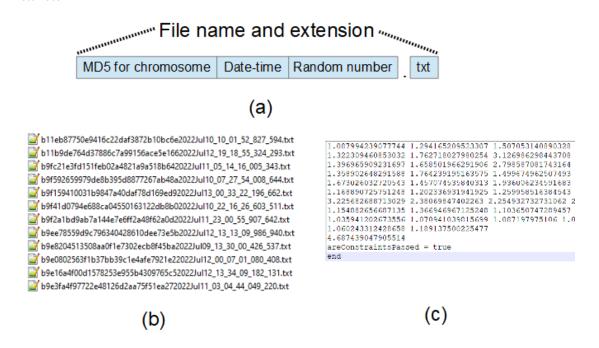

| 4.20 | (a) TCA multiple-objective simulation result file name and extension for-                            |     |

|      | mat. (b) examples of generated result files. (c) the content format of a GA                          |     |

|      | report file. Due to a long length of chromosome (the tile regulated-side                             |     |

|      | load-resistance values), some of the values are omitted. The last line with                          |     |

|      | a numerical value reports the worst-case maximum pin current. The line                               |     |

|      | with 'areConstraintsPassed $=$ true', can be used for post processing to                             |     |

|      | check whether any constraint, e.g., voltage drop is within the acceptable                            |     |

|      | range                                                                                                | 122 |

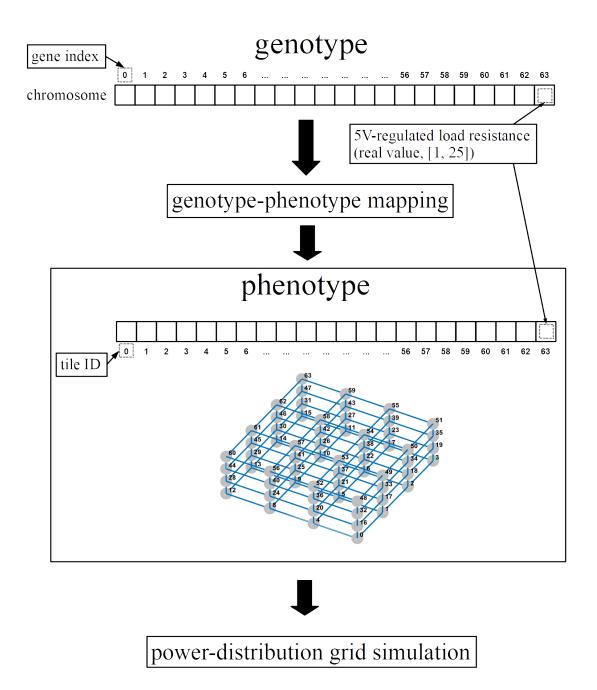

| 4.21 | Conventional mapping of tile-by-tile power of a 2x2x2-ball to a chromo-                              |     |

|      | some in the genetic algorithm employed                                                               | 124 |

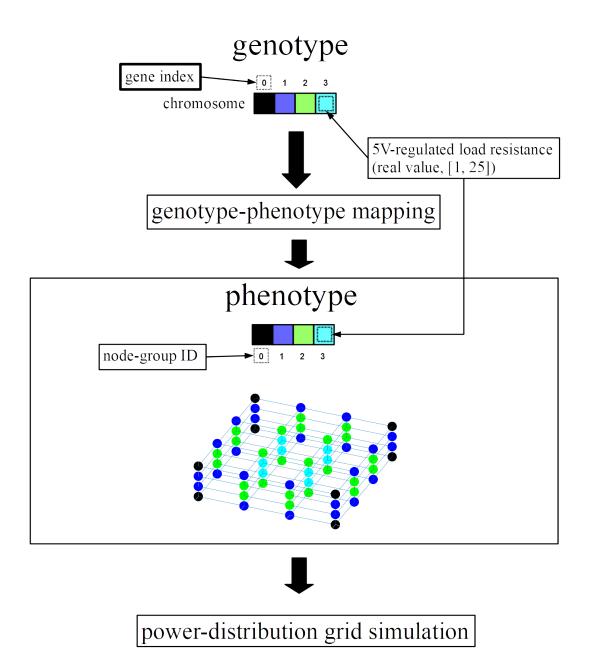

| 4.22 | The reduction of the chromosome size compared to the mapping in Figure                               |     |

|      | 4.21 when using relative-position scheme. Further more reductions can                                |     |

|      | also be seen in larger sizes shown in Figure 5.11                                                    | 125 |

| 4.23 | Example list of the MATLAB $^{\!\scriptscriptstyle{(\!R\!)}}$ gamultiobj's parameter named 'options' |     |

|      | [85] used for the $6x6x6$ -ball system simulated in this thesis                                      | 126 |

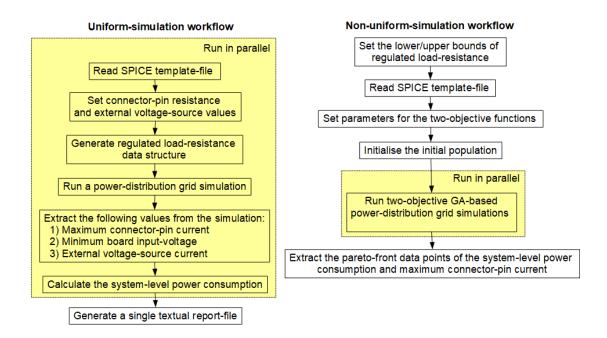

| 4.24 | Workflows of uniform and non-uniform power allocation simulations                                    | 127 |

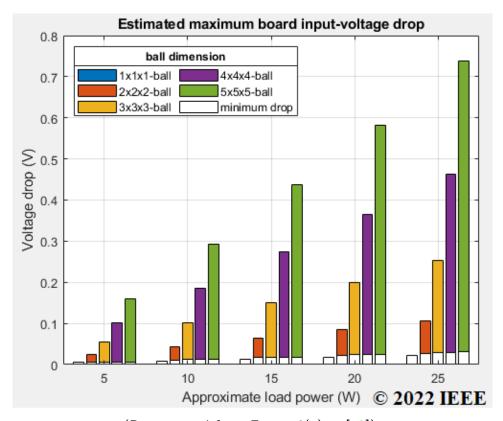

| 5 1  | Estimated best and worst-case voltage drop simulations for uniform power-                            |     |

| J.1  | allocation with 101mA assumed supply side 12V fan load                                               | 138 |

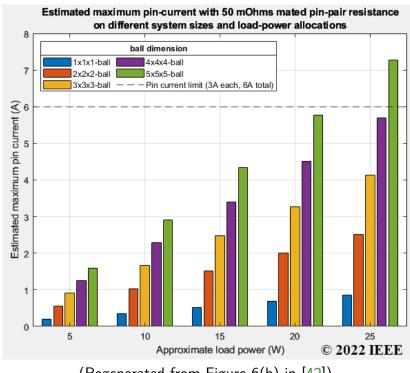

| 5 2  | Estimated maximum connector-pin currents for uniform power-allocation                                | 100 |

| J.Z  | with 101mA assumed supply side 12V fan load                                                          | 139 |

|      | with tother assumed supply side tzv lall load                                                        | 109 |

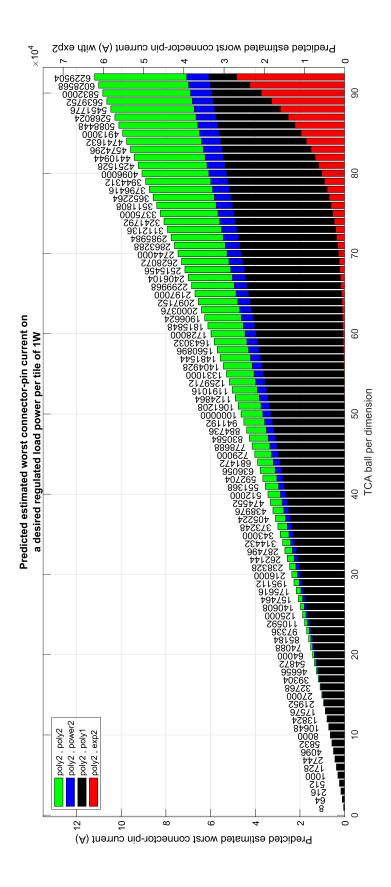

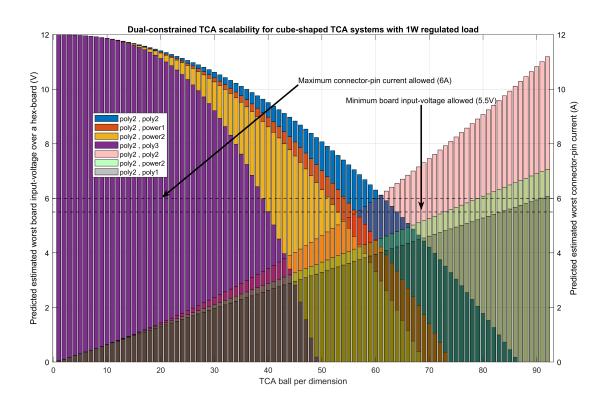

| 5.3 | Predicted estimated worst connector-pin currents for 1W regulated load       |     |

|-----|------------------------------------------------------------------------------|-----|

|     | per tile on various cubic sizes. The number above each bar represents        |     |

|     | the total number of tiles in each system. To estimate the feasibility of     |     |

|     | a TCA system, this connector-pin currents report can be used together        |     |

|     | with the worst-case voltage drops report as shown in Figure 5.6, which       |     |

|     | represents the difference between the supply voltage at all of the surface   |     |

|     | power connectors of the grid array (12V in this case) and the worst-case     |     |

|     | voltage drop (loss) of all of the board input voltages. A combined plot can  |     |

|     | also be seen in Figure 5.8                                                   | 144 |

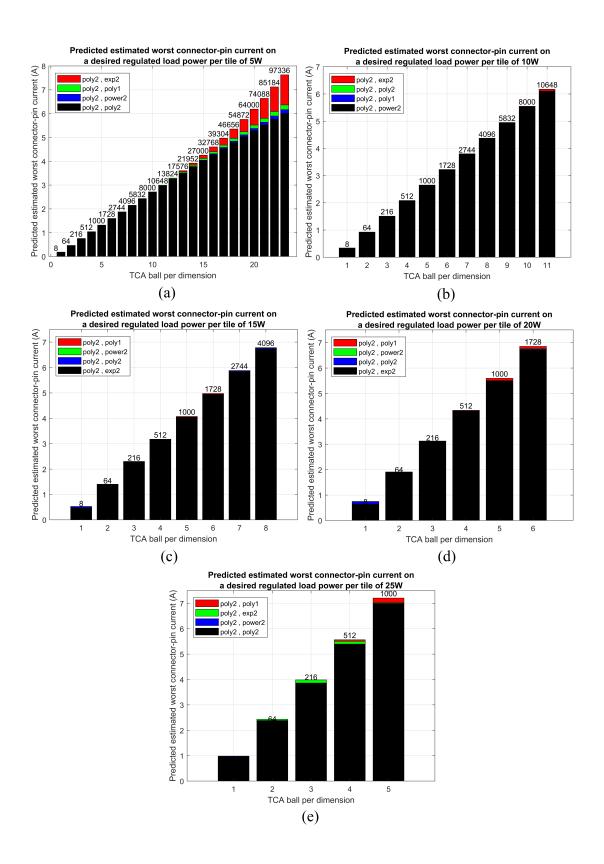

| 5.4 | Predicted estimated worst connector-pin currents for 5W (a) to 25w (e)       |     |

|     | regulated load per tile on various cubic sizes. The number above each bar    |     |

|     | represents the total number of tiles in each system. The sizes in each case  |     |

|     | are limited when the the worst connector-pin currents exceed the current     |     |

|     | limit of 6A                                                                  | 145 |

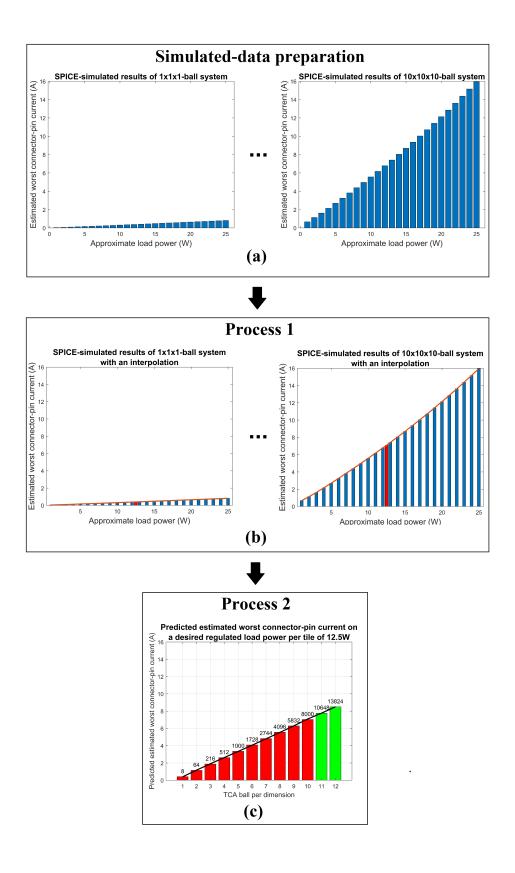

| 5.5 | Detailed processes for predicting arbitrary regulated load wattages and ball |     |

|     | cubic-size systems. (a) shows an example of simulated-data preparation       |     |

|     | for a desired regulated load wattage of 12.5W. The sizes of 2x2x2 to         |     |

|     | 9x9x9 are omitted. (b) details the process 1 generating 10 interpolated      |     |

|     | worst connector-pin currents. (c) shows process 2, with an example of        |     |

|     | extrapolation of a couple of desired cubic sizes of 11x11x11 and 12x12x12-   |     |

|     | ball systems (shown in green) from the data generated by process $1$ (shown  |     |

|     | in red)                                                                      | 146 |

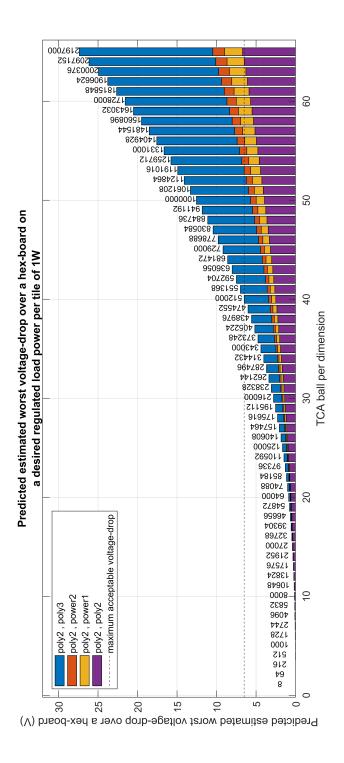

| 5.6 | Predicted worst-case voltage drops for 1W regulated load per tile on vari-   |     |

|     | ous cubic sizes. The number above each bar represents the total number       |     |

|     | of tiles in each system. To estimate the feasibility of a TCA system, this   |     |

|     | voltage drops report can be used together with the worst-case connector-     |     |

|     | pin currents report as shown in Figure 5.3, which represents the highest     |     |

|     | current experienced from all of the lumped resistors modelling single (or    |     |

|     | parallel) tile-edge power (or ground) pins. A combined plot can also be      |     |

|     | seen in Figure 5.8                                                           | 147 |

|     |                                                                              |     |

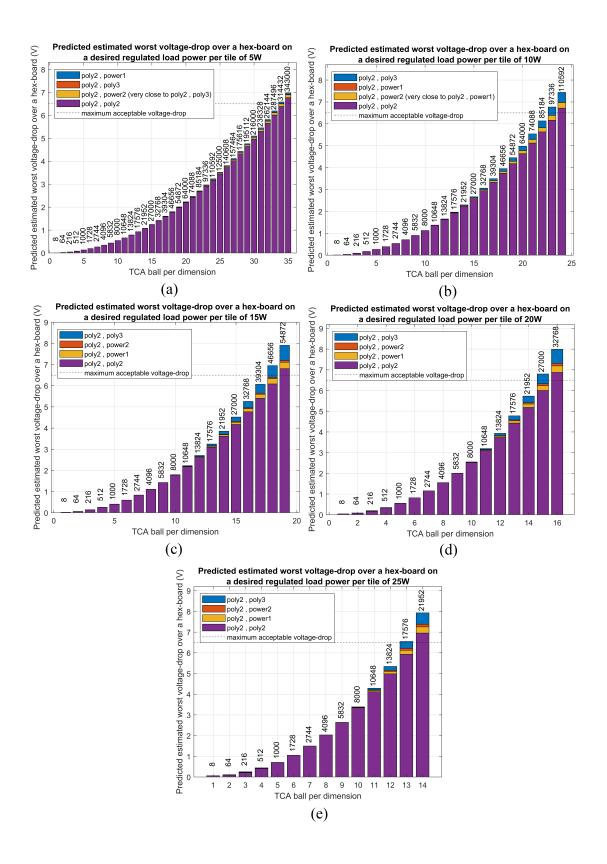

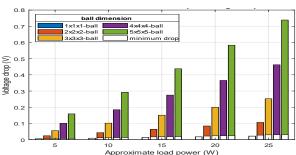

| 5.7          | Predicted estimated worst voltage drops for 5W (a) to 25w (e) regulated      |     |

|--------------|------------------------------------------------------------------------------|-----|

|              | load per tile on various cubic sizes. The number above each bar repre-       |     |

|              | sents the total number of tiles in each system. The sizes in each case are   |     |

|              | limited when the the worst voltage drop exceeds the voltage drop limit of    |     |

|              | 6.5V (due to the external voltage supplied of 12V and the minimum input      |     |

|              | voltage of 5.5V specified in the regulator data-sheet)                       | 148 |

| 5.8          | Dual-constrained TCA scalability for cube-shaped TCA systems with 1W         | 1.0 |

| 5.0          | regulated load                                                               | 149 |

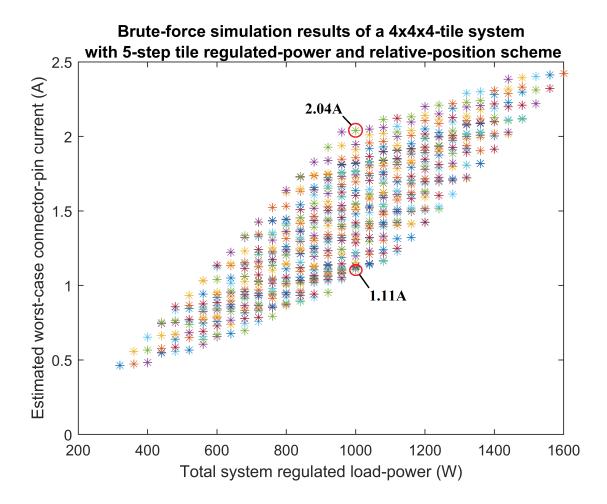

| 5.9          | Example of brute-force simulation for the relation of worst-case connector-  | 173 |

| 5.9          | pin currents and system-level regulated load-power                           | 151 |

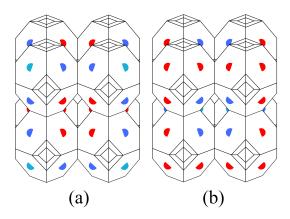

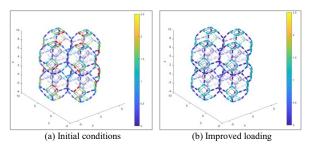

| 5 1 <b>0</b> | Visualisation of a 64-tile TCA comparing the same system-level regulated     | 131 |

| 5.10         |                                                                              |     |

|              | 1000W load-power but different node-level power allocations. The red         |     |

|              | dots represent highest-wattage nodes, and the lower ones are highlighted     |     |

|              | in blue. (a) shows the worst case, whilst (b) is the best one obtained shown | 4-0 |

|              | in Figure 5.9                                                                | 153 |

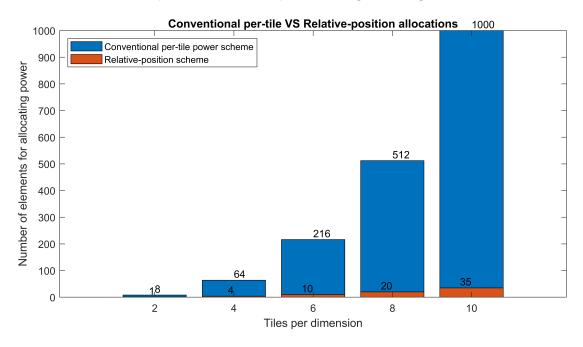

|              | Conventional per-tile vs Relative-position allocations                       | 154 |

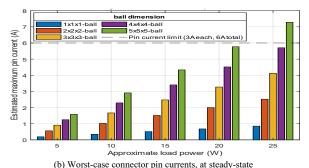

| 5.12         | (a) uniform and GA-optimised power allocation, (b) improvement percent-      |     |

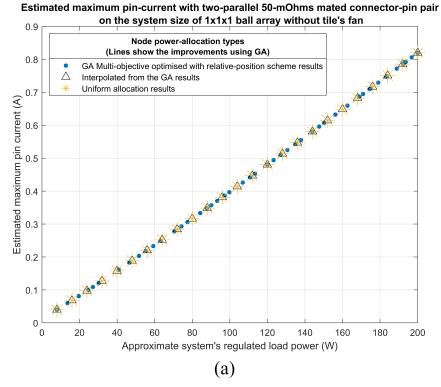

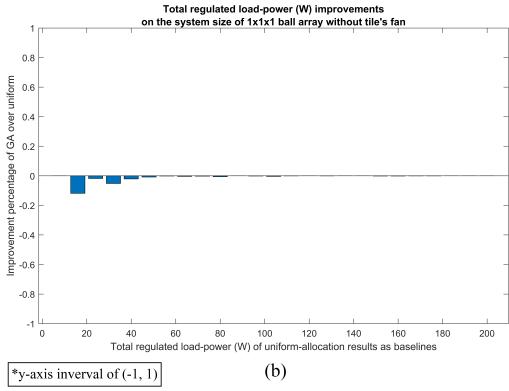

|              | ages, of a 1×1×1-ball system                                                 | 156 |

| 5.13         | (a) uniform and GA-optimised power allocation, (b) improvement percent-      |     |

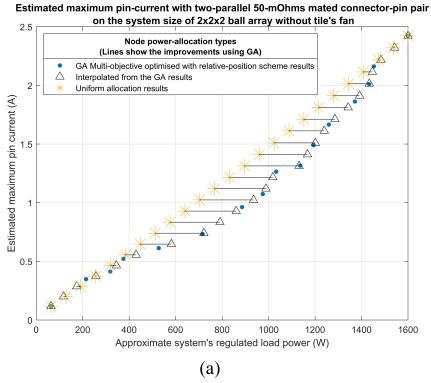

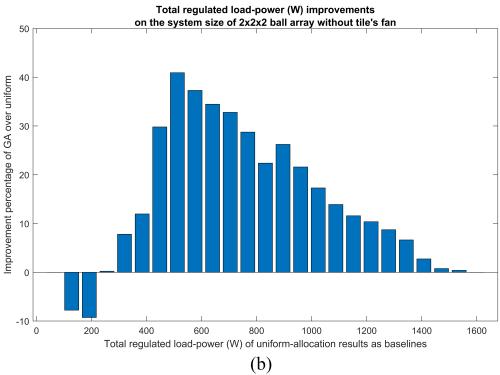

|              | ages, of a 2x2x2-ball system                                                 | 157 |

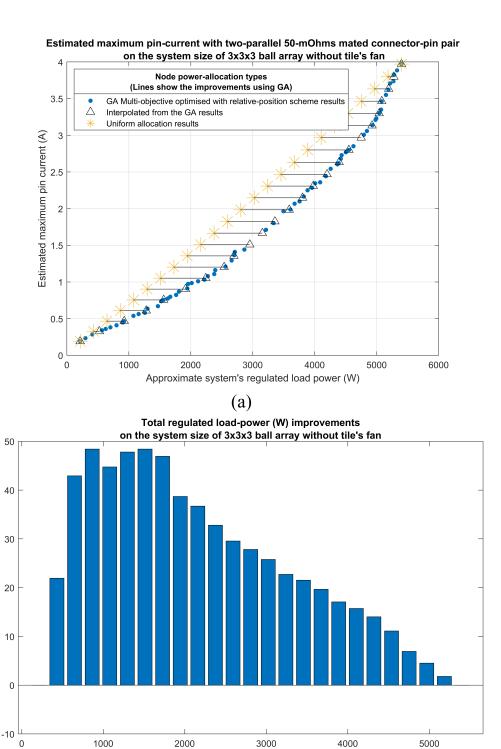

| 5.14         | (a) uniform and GA-optimised power allocation, (b) improvement percent-      |     |

|              | ages, of a 3x3x3-ball system                                                 | 158 |

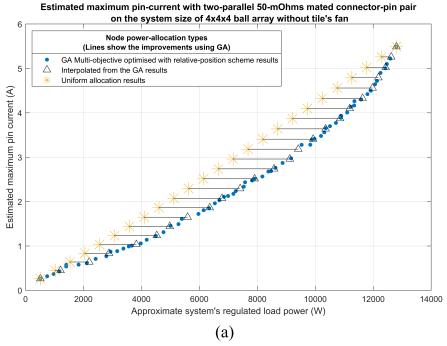

| 5.15         | (a) uniform and GA-optimised power allocation, (b) improvement percent-      |     |

|              | ages, of a 4x4x4-ball system                                                 | 159 |

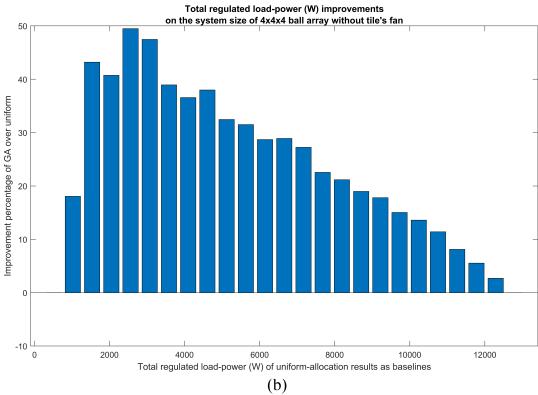

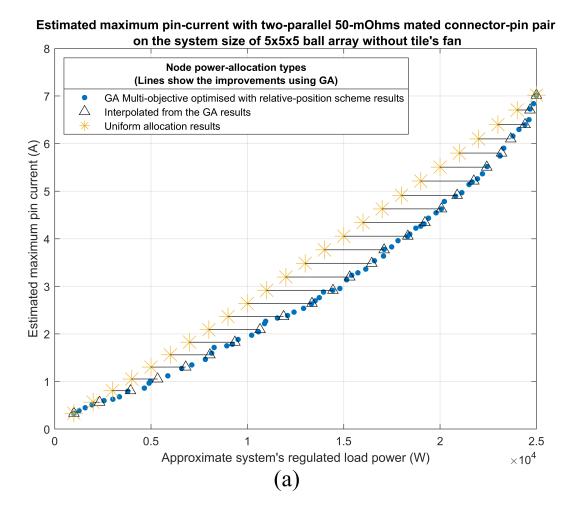

| 5.16         | (a) uniform and GA-optimised power allocation, (b) improvement percent-      |     |

|              | ages, of a 5x5x5-ball system                                                 | 160 |

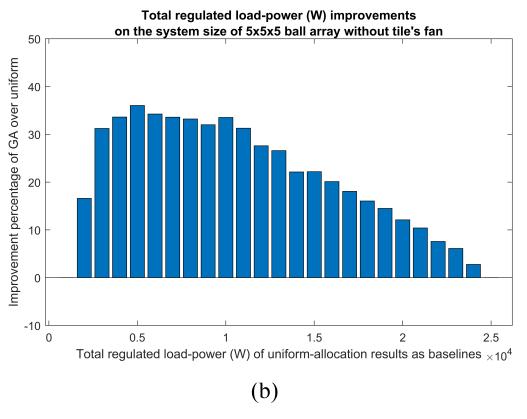

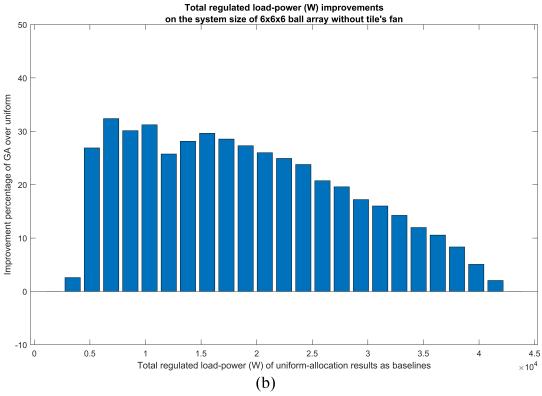

| 5.17         | (a) uniform and GA-optimised power allocation, (b) improvement percent-      |     |

|              | ages, of a 6x6x6-ball system                                                 | 161 |

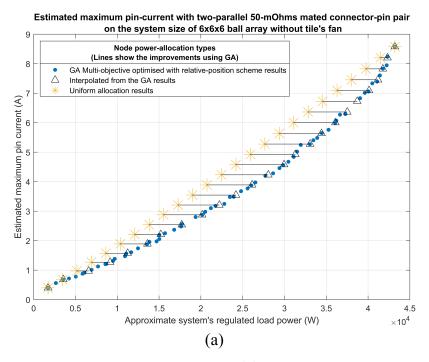

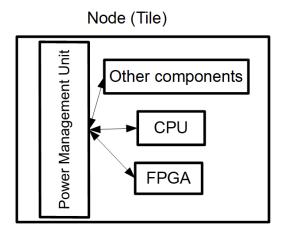

| 5.18         | Example of a conceptual power-managed node with a CPU and an FPGA.           |     |

|              | The other components consist of any circuitry that consume power. The        |     |

|              | power management unit communicates with all the sub-units to maintain        |     |

|              | the node-level power consumption within the upper-bound power budget.        | 163 |

|              |                                                                              |     |

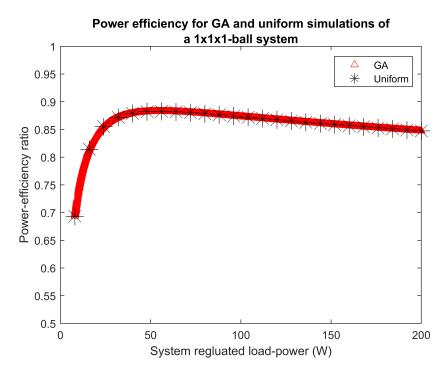

| 5.19 | 1x1x1-ball system-level power efficiency on GA and uniform allocation           |     |

|------|---------------------------------------------------------------------------------|-----|

|      | schemes                                                                         | 164 |

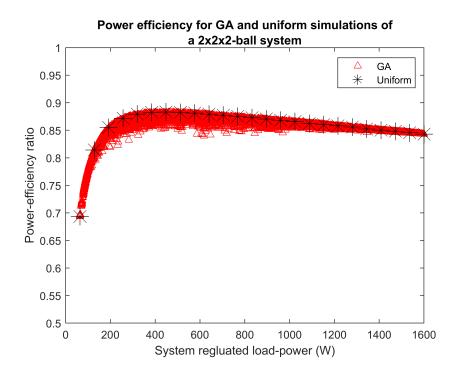

| 5.20 | 2x2x2-ball system-level power efficiency on GA and uniform allocation           |     |

|      | schemes                                                                         | 165 |

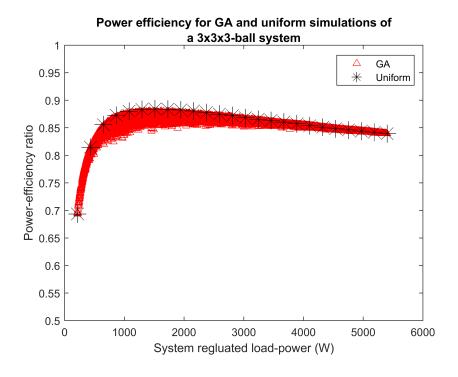

| 5.21 | 3x3x3-ball system-level power efficiency on GA and uniform allocation           |     |

|      | schemes                                                                         | 165 |

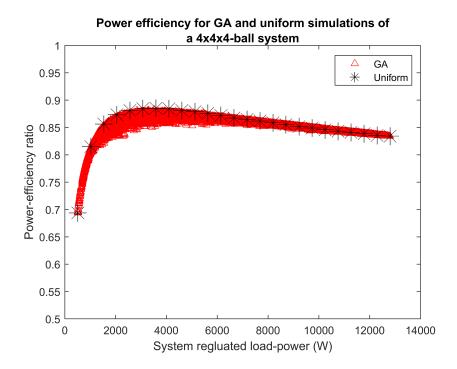

| 5.22 | 4x4x4-ball system-level power efficiency on GA and uniform allocation           |     |

|      | schemes                                                                         | 166 |

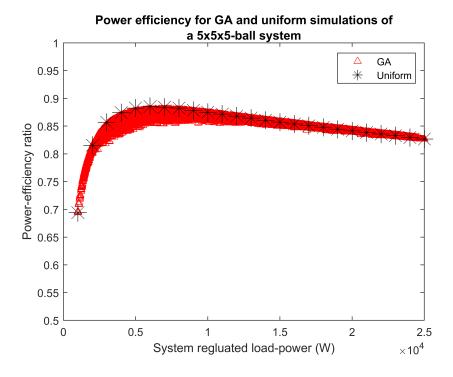

| 5.23 | 5x5x5-ball system-level power efficiency on GA and uniform allocation           |     |

|      | schemes                                                                         | 166 |

| 5.24 | 6x6x6-ball system-level power efficiency on GA and uniform allocation           |     |

|      | schemes                                                                         | 167 |

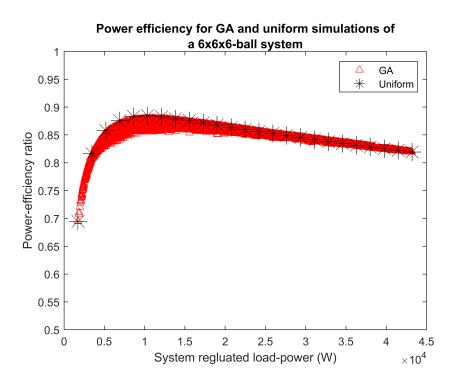

| 5.25 | 7x7x7-ball to $10x10x10$ -ball system-level power efficiency on the uniform     |     |

|      | allocation scheme.                                                              | 168 |

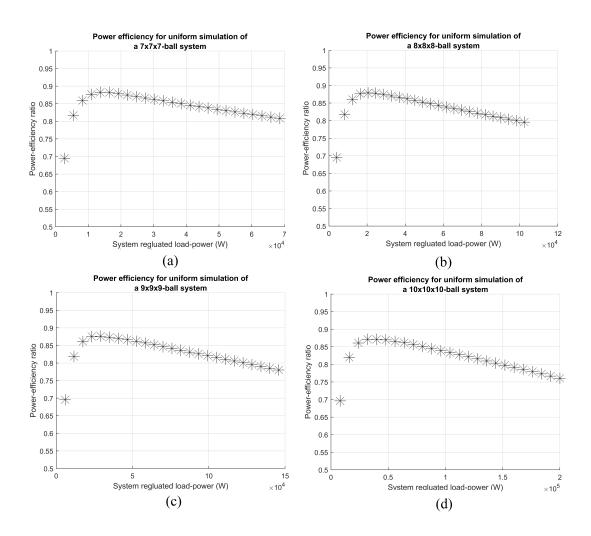

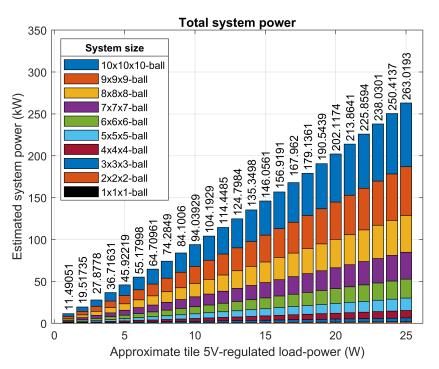

| 5.26 | Estimated TCA system power of various cubic sizes based on the simplified       |     |

|      | board model, showing the additional power contributed by each increment         |     |

|      | of array size n (and thus total power for the final case), for a range of       |     |

|      | component tile power loads. Total ball power in each case will be 8 times       |     |

|      | tile load.                                                                      | 170 |

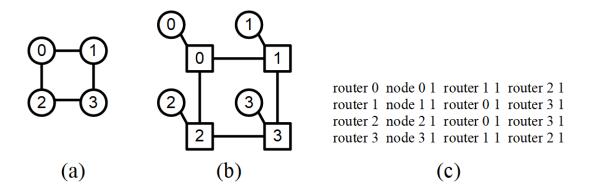

| 5.27 | (a) a logical representation of nodes and bi-directional channels forming       |     |

|      | a 2D-mesh topology. (b) the same network with explicit routers shown.           |     |

|      | (c) example of BookSim2's anynet user-file constructing the network with        |     |

|      | uniform latency of 1 cycle. All the channel latencies in this example file      |     |

|      | are uni-directional                                                             | 173 |

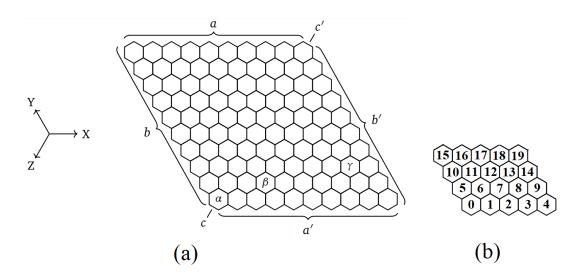

| 5.28 | (a) A hexagonal torus topology employed in a SpiNNaker system. (reprinted       |     |

|      | from Figure 2.7 in [5]). (b) Example of node-number convention for hop-         |     |

|      | count simulations in this thesis.                                               | 174 |

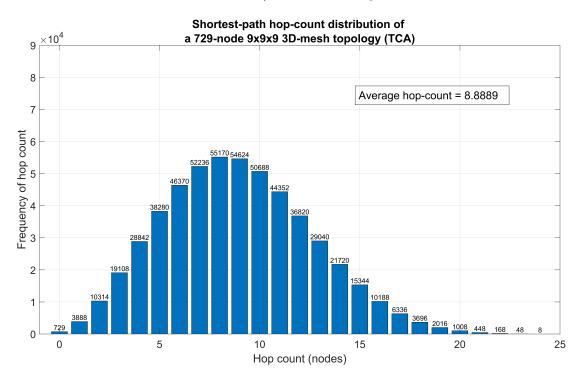

| 5.29 | Hop-count distribution of a 729-node, 9x9x9, 3D mesh topology                   | 175 |

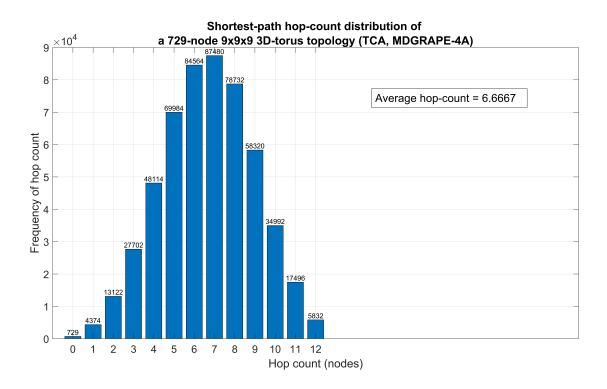

| 5.30 | Hop-count distribution of a 729-node, 9x9x9, 3D torus topology                  | 176 |

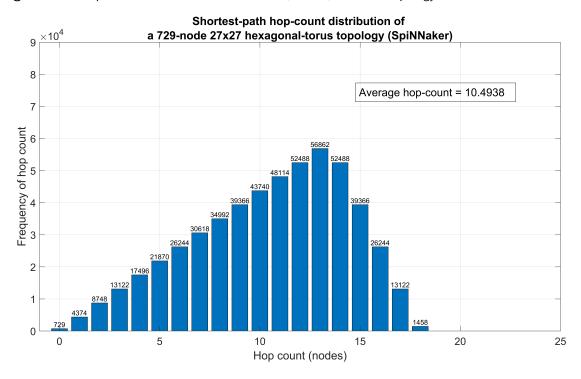

| 5.31 | Hop-count distribution of a 729-node, 27x27, hexagonal-torus topology           | 176 |

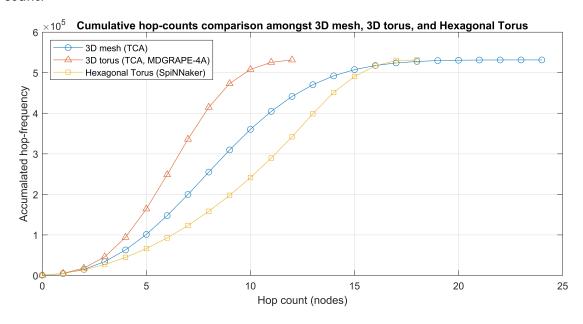

| 5.32 | $Cumulative\ hop-counts\ comparison\ amongst\ 3D-mesh,\ 3D-torus,\ and\ hexag-$ |     |

|      | onal torus                                                                      | 177 |

| 6.1 | Examples of power connectors and enhanced designs. Left: Existing pro-                      |     |  |  |

|-----|---------------------------------------------------------------------------------------------|-----|--|--|

|     | totype connector 22mm length, 6-pin (2xVcc, 2xGND, 2xData). Middle:                         |     |  |  |

|     | Larger connector (approx. 30mm length), 12 pins, example: 4xVcc, 4xGnd,                     |     |  |  |

|     | 4xData, giving double the power capacity. Right: Bespoke Design $\ensuremath{\mathbb{C}}$ C |     |  |  |

|     | Crispin-Bailey, University of York, Diameter 25mm, 30-way connector, ex-                    |     |  |  |

|     | ploiting connections via hexagonal H-Facets rather than trapezoidal T-                      |     |  |  |

|     | Facets                                                                                      | .84 |  |  |

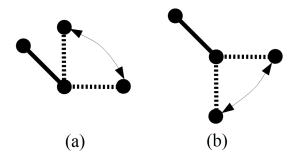

| 6.2 | A conceptual design for a bypass channel between second-immediate hops.                     |     |  |  |

|     | The black line shows a dedicated line medium implemented on the same                        |     |  |  |

|     | or a different PCB layer of existing components                                             | .86 |  |  |

| Λ 1 |                                                                                             | 110 |  |  |

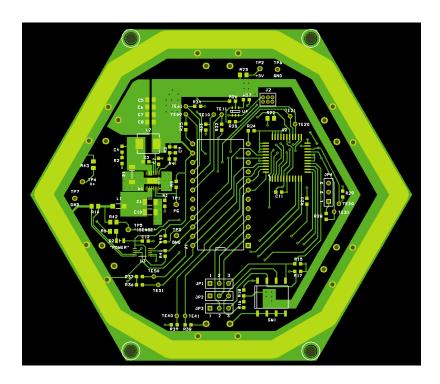

| A.I | Hex-Tile Board Topside, showing main component layouts                                      | .18 |  |  |

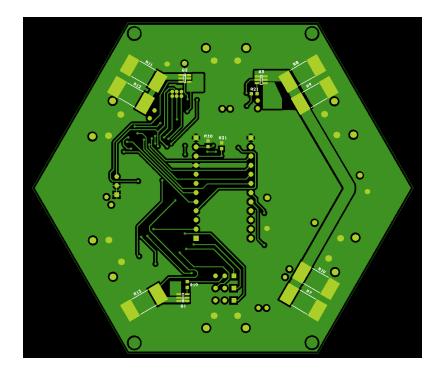

| A.2 | Hex-Tile Board Underside, showing Power resistor PCB pads (Larger square                    |     |  |  |

|     | areas), and other component layouts                                                         | 18  |  |  |

# **List of Tables**

| 2.1 | Single packed cubic array quantitative equations                                                   | 19 |

|-----|----------------------------------------------------------------------------------------------------|----|

| 2.2 | Double packed cubic array quantitative equations                                                   | 20 |

| 2.3 | "Critical length of common wires at 2 GHz (without equalization)." (re-                            |    |

|     | produced from Table 3.2 in [15])                                                                   | 23 |

| 2.4 | List of hardware and network configurations in the surveyed parallel/dis-                          |    |

|     | tributed computers                                                                                 | 35 |

| 2.5 | "Network traffic patterns. Random traffic is described by a traffic matrix,                        |    |

|     | $\Lambda$ , with all entries $\lambda_{sd}=1/N$ . Permutation traffic, in which all traffic from   |    |

|     | each source is directed to one destination, can be more compactly repre-                           |    |

|     | sented by a permutation function $\pi$ that maps source to destination. Bit                        |    |

|     | permutations, like transpose and shuffle, are those in which each bit $d_i$ of                     |    |

|     | the $b$ -bit destination address is a function of one bit of the source address,                   |    |

|     | $\boldsymbol{s}_j$ where $j$ is a function of $i$ . In digit permutations, like tornado and neigh- |    |

|     | bor, each (radix- $k$ ) digit of the destination address $d_{x}$ is a function of a                |    |

|     | digit $\mathit{s}_{\mathit{y}}$ of the source address. In the two digit permutations shown here,   |    |

|     | x=y. However, that is not always the case." (reproduced from Table 3.1                             |    |

|     | in [15])                                                                                           | 50 |

| 3.1 | Comparison of approximate simulation times and file sizes between the full                         |    |

|     | prototype-board model and the simplified board model, for the 3x3x3-ball                           |    |

|     | validation case shown in Figure 3.12.                                                              | 71 |

| 3.2 | The differences between the two alternative fitting techniques for the board                       |    |

|     | modelling proposed in this thesis.                                                                 | 75 |

| 3.3 | Prototype/Model: Single tile, Single connector. ( $\bigcirc$ 2022 IEEE, regenerated                |    |

|     | from Table II(a) in [42])                                                                          | 80 |

| 3.4 | Prototype/Model: 8-tile ball, 2 co-located power connectors. (© 2022                               |    |

|     | IEEE, regenerated from Table II(b) in [42])                                                        | 81 |

| 3.5 | Prototype: grid stability (worst case voltage drop, 10W load, 12V supply).                                      |     |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

|     | (© 2022 IEEE, regenerated from Table II(c) in [42]. Note that there are                                         |     |

|     | an average of one power connector for every four tiles in all three cases,                                      |     |

|     | to ensure uniformity and also to ensure that connector pins per connector                                       |     |

|     | are not overloaded).                                                                                            | 82  |

| 3.6 | Simple vs complex simulation test case. Accuracy of the hypothetical test                                       |     |

|     | case of 3x3x3-ball TCA system shown in Figure 3.12 for non-negligible                                           |     |

|     | current flows of the validation of simplified versus complex manufacturer                                       |     |

|     | switching models                                                                                                | 82  |

| 3.7 | LTspice $^{\mathbb{R}}$ example code and parameters. ( $\mathbb{C}$ 2022 IEEE, regenerated from                 |     |

|     | Table III in [42])                                                                                              | 83  |

| 4.1 | Example of TCA SPICE-code template generation                                                                   | 100 |

| 4.2 | Advantages and disadvantages of the two adjuster types categorised in                                           |     |

|     | this thesis.                                                                                                    | 108 |

| 4.3 | Overview of the details of the two-objective GA used in this thesis. Addi-                                      |     |

|     | tional details specifically in one of the MATLAB $^{\! (\! \! \! \! \! \! \! \! \! \! \! \! \! \! \! \! \! \! $ |     |

|     | named 'options' can be found in Figure 4.23                                                                     | 126 |

| 5.1 | Two-step extrapolation processes and curve fitting formulae used in Figures                                     |     |

|     | 5.3 to 5.8                                                                                                      | 141 |

| 5.2 | Example of a uniform simulator report file for a size of 7x7x7-ball TCA                                         |     |

|     | with the board model based-on the tile prototypes in this thesis without                                        |     |

|     | fan for cooling. Two parallel pins are dedicated for each of power and                                          |     |

|     | ground rails, and the connector-pin parameter is set for 50m-Ohm mated                                          |     |

|     | pin-pair. The highlighted case represents the nearest equivalent power load                                     |     |

|     | to that of the 65kW MDGRAPE-4A system                                                                           | 171 |

| 5.3 | Comparison of nodes per dimension and the total number of nodes of 3D                                           |     |

|     | mesh, 3D torus, and hexagonal torus                                                                             | 178 |

| 5.4 | Comparison of the selected existing systems concerning given total system                                       |     |

|     | power and estimated PE-related configurations                                                                   | 180 |

| 5.5 | Estimation of the required number of TCA tiles with a power budget of         |

|-----|-------------------------------------------------------------------------------|

|     | 25W regulated-load per tile, to mimic the whole power consumed at rack        |

|     | level for a given system as described in Table 5.4 using Equations 5.1 to     |

|     | 5.3                                                                           |

| 5.6 | Required cube-sizes of the approximate numbers of TCA tiles in Table 5.5. 182 |

Introduction 1

# 1.1 Synopsis

In undertaking the research work and preparation of this thesis, Modelling and Simulation for Power Distribution Grids of 3D Tiled Computing Arrays, a number of research questions have focused around the novel concept of multi-dimensional tiled computing arrays (TCAs), and a hypothesis with respect to their feasibility and scalability. In particular this concept envisages a modular computing device, a core, or node in other terms, which is capable of interfacing directly with other computing nodes in one dimensional (1D), two dimensional (2D) or three dimensional (3D) structures, simply by connecting nodes directly together by means of convenient connectors. The intention of such modules is to eliminate all of the supporting printed circuit board structure, and the associated limitations of traditional back-plane systems, where 3D computing topologies are obliged to map onto primarily 2D structures, racks, back-planes, etc.

From another observational perspective, the design principle of the TCA concept is physical 3D inter-node data-centric, allowing significant freedom concerning internode data I/Os for direct neighbouring connection in 3D. This contradicts traditional rack-based computing approaches, which might be described as back-plane centric for both data and power connectivity. Back-plane-centric models limit both inter-board power and data I/O paths routed via one or more of hierarchical back-plane levels, with inherently 2D properties. However, with 3D inter-node data-centric models, whilst data flow has the advantage of true 3D connectivity, power distribution has to conform to the same model, leading to the specific novel problems of 3D cascaded power grids, as presented in this thesis for the investigated TCA systems. In the literature review, it will be seen that some other attempts to overcome back-plane centric limitations have been explored, to gain similar benefits. It is therefore valuable to explore the TCA model thoroughly at this time.

## 1.2 Motivation

Performing computing tasks on any parallel or distributed computer systems require mapping the tasks with their own logical topologies into given physical machines. By doing this, the physical topology enforced by the implementation of the system dictates the number of inter-node communication hops.

Traditionally, parallel or distributed rack-mount computers lack the availability of the third physical-dimension of communication channels between processing elements (PEs), e.g., inter-chip communication typically possible only on a 2D-plane of printed circuit board. This is a potential issue which degrades the result of mapping a set of logical tasks into a physical system, meaning the communication hops may not be achieved as optimally as they are implied in the logical representation. An example case of mapping is shown in Figure 1.1.

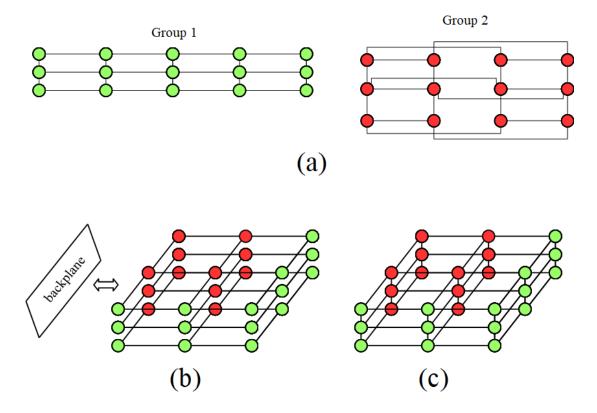

**Figure 1.1:** Mapping a couple of separate groups of tasks into different packaging systems. (b) is a representation of the two groups mapped into three horizontal computing-boards, each with 9 PEs, in a rack-mount system. (c) represents a mapping of the tasks into 27 tiles in a TCA system.

In Figure 1.1, two separate groups of tasks as shown in Figure 1.1(a) are mapped into a single set of 27 computing PEs. At first glance, both of Figures 1.1(b) and (c) seem to give an identical system performance. However, it can be seen in Figure 1.1(b) that every single node suffers from the lack of vertically physical data channels. This results in some source-to-destination pairs in a group shown in Figure 1.1(a) requiring additional physical communication-hops via other nodes and/or a communication back-plane, instead of ideally single immediate-hops. On the contrary, the two logical groups can be perfectly mapped into a TCA system as it provides the equivalent physical communication channels available for each group of the tasks.

Therefore, this advantage of the TCA packaging is the direct motivation to investigate the power-distribution grid of the tiled computing array in this thesis.

# 1.3 Thesis Scope

The 3D-TCA concept can be physically implemented into many practical hardware alternatives. However, in this thesis, only some aspects, abstraction levels for modelling, simulation framework, and hardware prototypes are investigated due to some research limitations such as the time-frame and financial budget for hardware building. The scope of this thesis is as follows:

#### ► Hardware prototypes:

- 1) TCA unit-shape: A TCA unit for building a large-scale computing array is possible with many shapes, e.g., cube, triangle, hexagon. In this thesis, only a hexagonal-shaped tile is focused.

- **2) Power connector:** Only an off-the-self connector model is employed for inter-tile power and intercommunication to demonstrate a possible practical hardware design. Whilst other practical connectors or alternative designs are also possible, however, are not in the scope for prototype implementation.

- 3) Voltage regulator: Whilst the voltage control at tile level is possible with the implementation of many types and numbers of voltage regulators, in this

thesis, at tile level, it consists of only a single regulator, which is a step-down switching regulator model.

#### ▶ Models:

- 1) External (surface) power sources: In practice, many separate power-sources such as multiple connectors with different acceptable voltage ranges are possible to feed power into the whole system. However, for simplicity and to reduce the complexity of large-scale simulations, only a single voltage-source of 12V is assumed to be connected to all the surface input-power connections in the simulations.

- 2) Power-distribution grid resistance: In a power-distribution grid, resistance can technically exist in any electrically conductive media, including, the printed circuit board's trace resistance. However, only an inter-tile power medium type with a straight and uniform cross-sectional shape, e.g., circle or rectangular, along the medium, and also with the same resistance value, are assumed. Also, the heat arising from any component that may impact on resistance changes is not in the scope of this thesis.

- 3) Board-level power model: The power consumption at both the whole board level and also at the output-voltage of the regulator can vary over time due to various factors, for instance, the type of regulator employed and the behaviour of the onboard power loads. However, for large-scale TCA-size simulations, only constant power consumption at these two levels are assumed in this thesis for acceptable requirements such as simulation times and the machines required for simulations using a simplified board model. Also, as described earlier regarding the voltage regulator employed in the hardware prototypes, currently the board model also focuses upon the use of a single regulator and a single regulated load.

# 1.4 Research Hypothesis and Objectives

This thesis explores the feasibility of such systems in terms of scalability of power delivery networks, an aspect that is itself unusual as a result of the unique approaches taken in TCA systems. An overall hypothesis for this thesis may be defined as follows:-

It is feasible to build a physical large-scale Tiled Computing Array with the power-grid constraints given, whilst still scaling up the system computing performance.

#### 1.4.1 Definition

Regarding the research hypothesis, there are two key terms to be defined as follows:

- ▶ large-scale: The term *large-scale* is considered a comparative definition. In this thesis, it is defined, for a TCA system, as an estimation to achieve at least 10,000 tiles when constructed as a cube-size TCA to contain the same amount of processing-element power at rack/cabinet level of a recent traditional rackmount system existing since a decade ago, whilst also considering the given two constraints for the power-distribution grid in this thesis. A comparison metric regarding this term will be elaborated in Chapter 5.

- ➤ constraints: There can be several electrical constraints when designing and implementing computing devices. However, the following two key constraints are focused in this thesis:

- 1) voltage drop: In this thesis, *voltage drop* is defined as the amount of voltage reduction, dropping from the voltage of the external (surface) power sources. In many cases, this term will be frequently used when discussing the board input-voltage.

- **2) connector-pin current:** This term refers to an electrical current flowing through either a power (positive) or a ground (negative) pin, on a tile-edge connector.

In order to determine if this hypothesis is valid, several important research questions are investigated:

- ▶ What are the necessary design choices for constructing tileable modules?

- ▶ What are the component characteristics of the power grid in a TCA array?

► How is system computing performance influenced by the power grid design and limitations?

These questions are addressed in this thesis, and a number of methodologies are utilised in order to achieve clear conclusions. In particular, the use of complex modelling via MATLAB® [1] and circuit modelling/simulation tools, and the construction of validation prototypes has been employed in order to calibrate models if needed, and to permit deeper exploration of the topic. It will be demonstrated that power grids are feasible in TCA systems and that they may potentially scale to many thousands of computing nodes.

## 1.4.2 Research Objectives

Given the research hypothesis, in this subsection, the research objectives will be briefly given. There are two requirements prior to set out the research objectives for the modelling and simulation towards testing the research hypothesis. First, the critical components in a TCA which contribute to the limit of the power-distribution grid's scalability and computing performance need to be understood. This ensures that only relevant components will be focused upon for modelling and simulation developments.

Second, due to the existing research field of power modelling in parallel/distributed computer systems, relevant models and simulation tools should be surveyed to be employed or modified, if any exist, for the purpose of TCA scalability evaluations, thus avoiding any re-invention of existing toolsets. These two requirements will be carried out in Chapter 2. After considering the critical components, and the survey of existing relevant models and simulation tools, the research objectives carried out throughout this thesis are to be designed towards testing the research hypothesis, which are as follows:

▶ Objective 1: Employing and designing models and simulation tools

After the survey of the existing models and tools, if it is found that they are not suitable for the intended research investigation, new model designs and simulation tools need to be built for representation of the novel TCA architecture.

#### ► Objective 2: Hardware validation

Whilst the models and the simulation framework are being built, both should be verified and validated. This would initially be in comparison with expected results, but simulation results should then also be validated for accuracy by comparing with real hardware prototypes as far as resources permit.

#### **▶** Objective 3: Fundamental simulation experiments

With the simulation platform having been validated, experimental cases are to be designed to evaluate the scalability of the TCA concept in various scenarios.

#### **▶** Objective 4: Optimised power distribution

This objective can be considered an advanced capability in simulation experiments. With heterogeneous node implementation in a parallel/distributed machine, non-uniform power allocation may be involved and this also impacts upon the behaviour of the power network in TCA systems. The optimisation performed in the non-uniform simulation adjusts each tile's regulated load-power, trying to achieve the system-level goal, i.e., the summation of all the regulated load-power from all the tiles in the system should be as high as possible, whilst all the connector-pin currents are still within the desired current limit. Non uniform power allocation might also occur where an external power connector is unplugged or has some form of failure. So this capability is useful for predicting system resilience and reliability.

#### ▶ Objective 5: Scalability evaluations

This objective can be considered the product of the collective efforts of the preceding objectives defined, and is ultimately the purpose of the simulation platform in exploring the hypothesis. Evaluation of the data, test cases, and implications in the context of the stated hypothesis and research questions are the key aims here.

#### **▶** Objective 6: Simulation framework documentation