# INSULATED GATE BIPOLAR TRANSISTOR'S AGEING AND ITS IMPACTS ON THE ELECTROMAGNETIC CONDUCTED EMISSIONS

Evan J. Dimech

Doctor of Philosophy

University of York Electronics

January 2022

To my wife Corinne and my daughter Marta, For their patience, reassurance, and love.

# Abstract

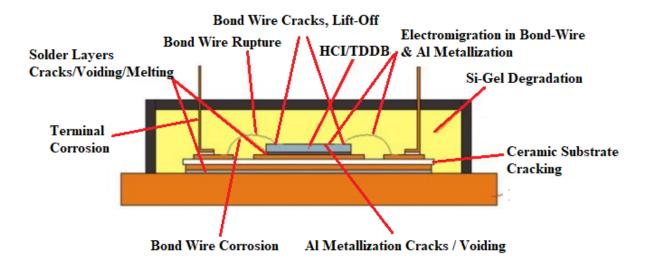

Insulated Gate Bipolar Transistors (IGBTs) have become key electronic components in many applications, including life critical or mission critical products. The understanding of the failing mechanisms and the reliability aspects of the IGBT have become important to semiconductor manufacturers and application engineers, to provide reliable solutions especially in enhanced lifetime (thirty to forty years) applications. Since the IGBT is employed at elevated power scenarios, its substructures can be prone to multiple failure mechanisms which can lead to the general IGBT failure. The IGBT's failure mechanisms can be mainly divided into two categories: die-related failure mechanisms and package-related failure mechanisms. These will contribute to gate oxide degradation, bond-wire lift-off, bond-wire cracks, bond-wire ruptures, solder delamination, solder cracking, and the degradation of the metallization layers. The presented work tried to address the current gap in knowledge, by studying the relationship between specific degradation within the IGBT (primarily the degradation of the die-attach layer and the gate's oxide contamination), the static and dynamic operation of the IGBT, and hence the consequential influence this degradation has, on the EM conducted disturbances. For this purpose, accelerated ageing was conducted on commercially available 600V, 16A IGBTs. This was achieved through the development of a power cycling accelerated ageing system (PCAS), which subjects the IGBT to thermo-electrical overstress. The degree of the inflicted degradation was analysed through X-Ray inspection. Moreover, the static electrical parameters of tested IGBTs, were characterized before, during and after accelerated ageing, noting significant changes.

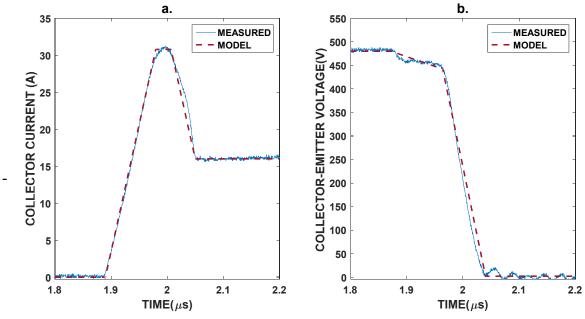

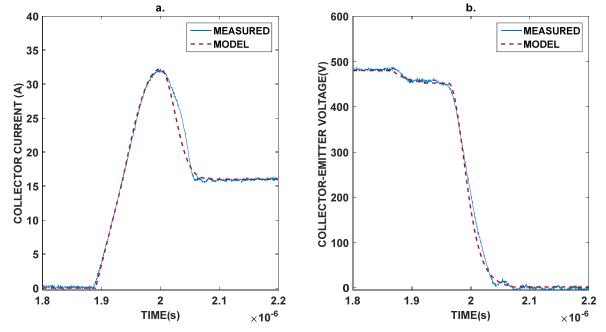

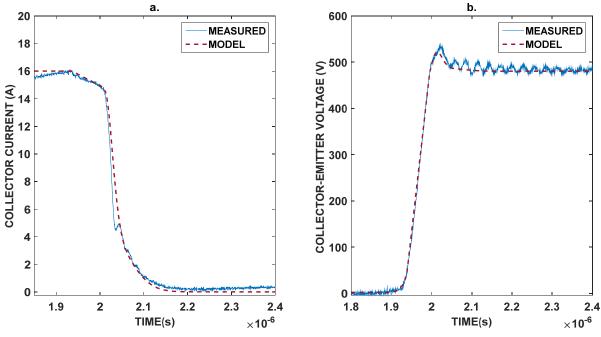

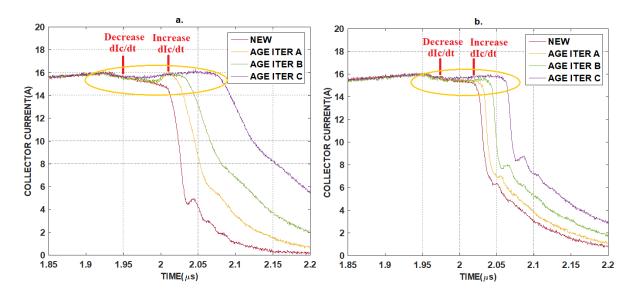

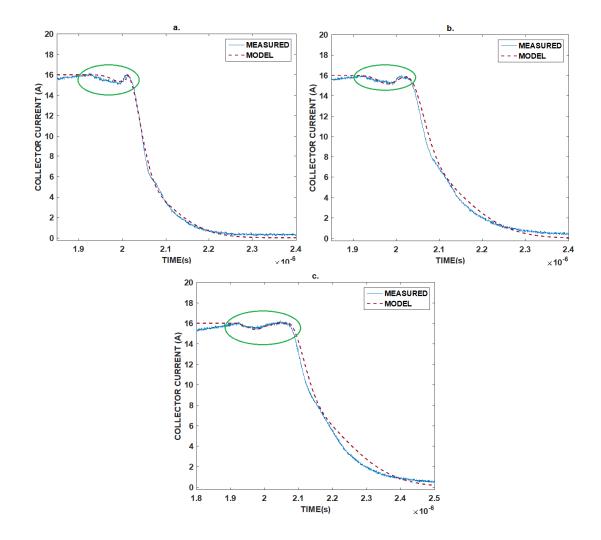

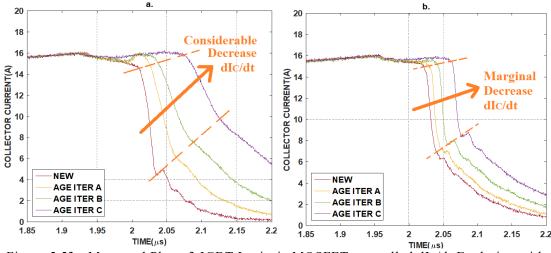

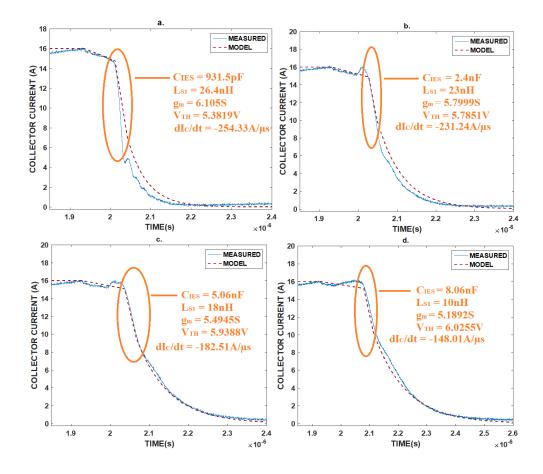

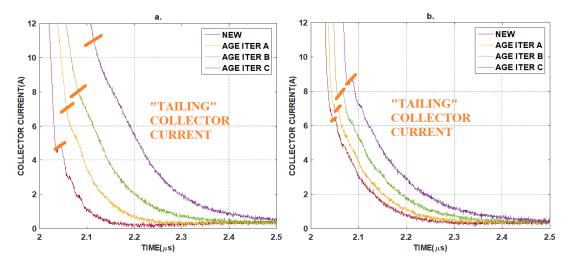

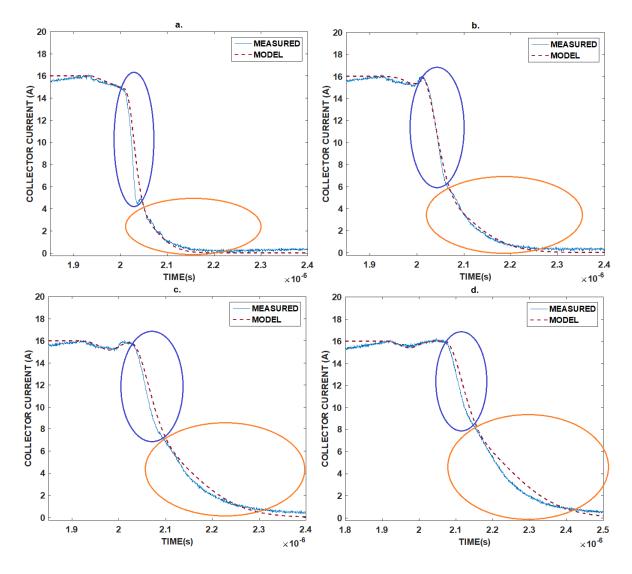

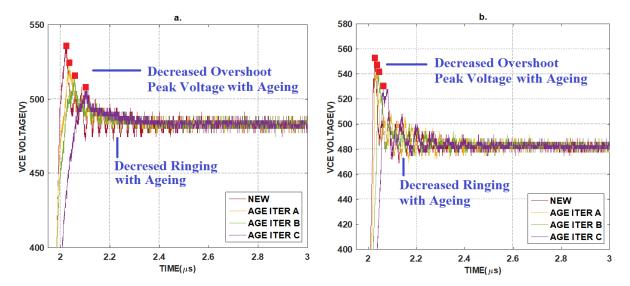

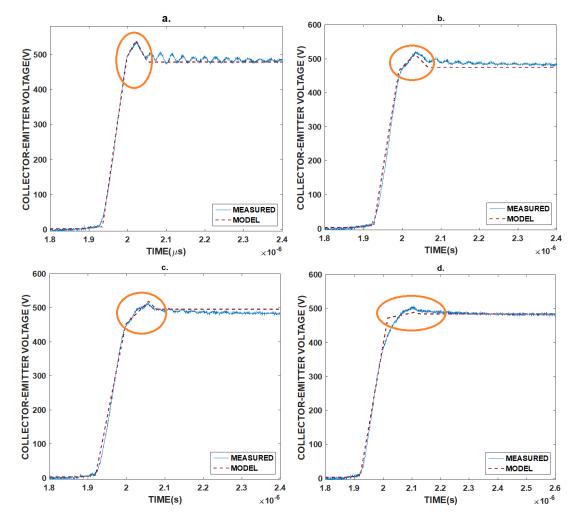

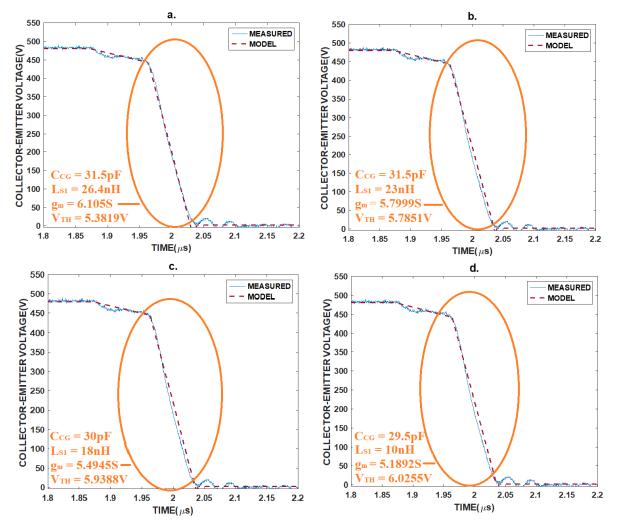

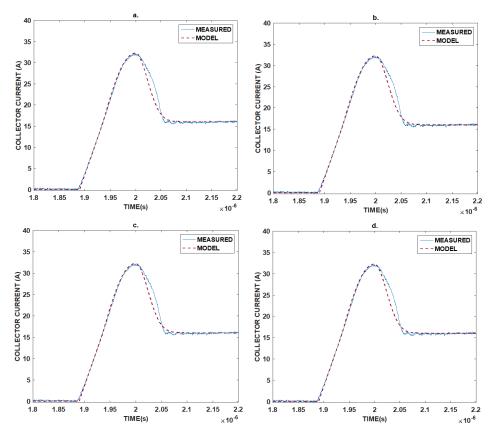

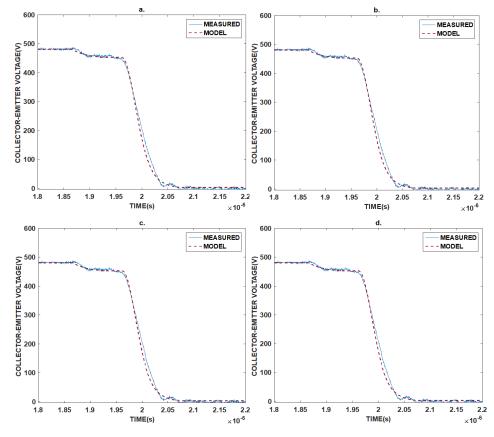

Consecutively the switching transients of the aged IGBTs were studied, by developing a Double-Pulse characterization system. This evidenced that the employed accelerated ageing, contributed to significant slow-down of the IGBT's turn-off transients, while producing minimal changes in the IGBT's turn-on transients. This led to the modelling of the IGBT's switching transients' evolution with ageing, effectively evidencing that the die-attach degradation together with the monitored contamination of the gate's oxide, were contributing to a more pronounced turn-off "tail current", and changes in the IGBT's parasitic elements predominantly the Miller capacitance. Finally, an EM conducted emissions experimental setup was developed, where it was determined that there is a direct correlation between the inflicted degradation, the switching transients, predominantly the collector current (Ic) turn-off transient, and the measured decrease in the EM conducted disturbances.

# Contents

| ABSTRACT                                                               | I    |

|------------------------------------------------------------------------|------|

| CONTENTS                                                               | II   |

| LIST OF TABLES                                                         | VIII |

| LIST OF FIGURES                                                        | v    |

|                                                                        |      |

| ACKNOWLEDGEMENTSX                                                      | (VII |

| DECLARATIONX                                                           | VIII |

| CHAPTER 1 INTRODUCTION                                                 | 1    |

| 1.1 Research Background                                                | 1    |

| 1.2 Research Scope                                                     | 2    |

| 1.3 MAIN RESEARCH QUESTION AND ADDRESSED RESEARCH PATHS                | 3    |

| 1.4 Research Objectives and Methodology                                | 4    |

| 1.5 Research Main Findings                                             | 6    |

| 1.6 Research Outline                                                   | 7    |

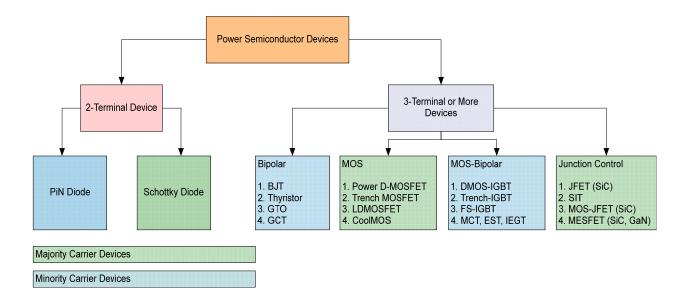

| 1.7 INTRODUCTION TO POWER SEMICONDUCTOR DEVICES (PSDs)                 | 9    |

| 1.7.1 Power Devices Classification                                     | 10   |

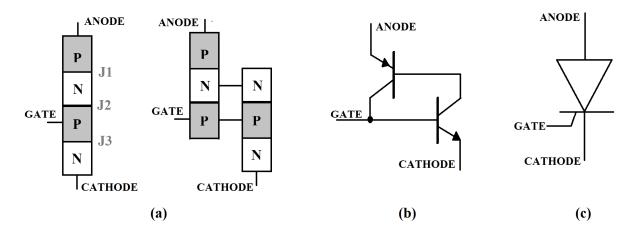

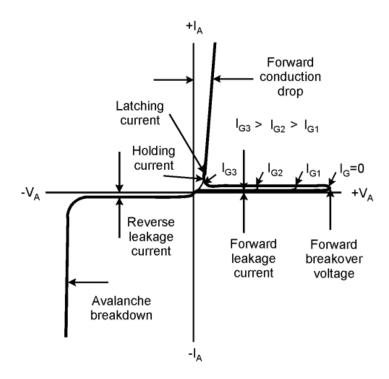

| 1.8 Thyristors                                                         | 11   |

| 1.8.1 Thyristors Physical Structure & Operation                        | 11   |

| 1.8.2 Thyristor Failure Modes                                          | 13   |

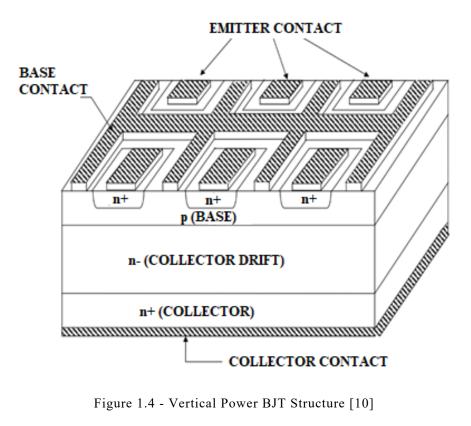

| 1.9 Power BJT                                                          | 14   |

| 1.9.1 Power BJT's Physical Structure                                   | 14   |

| 1.9.2 Power BJT Characteristics                                        |      |

| 1.10 Power MOSFETs                                                     | 18   |

| 1.10.1 Depletion vs Enhancement Type MOSFETs                           | 19   |

| 1.10.2 Power MOSFETS Physical Structure & Operation                    |      |

| 1.11 INSULATED GATE BIPOLAR TRANSISTOR (IGBTS)                         | 24   |

| 1.11.1 IGBT Physical Structure and Operation                           | 25   |

| CHAPTER 2 LITERATURE REVIEW OF IGBT DEGRADATION AND FAILURE MECHANISMS | 27   |

| 2.1 Semiconductor Physics of Failure                                   | 27   |

| 2.1.1 Electro Migration (EM)                                           | 28   |

| 2.1.1 Basic Physics of Electro Migration                               | 29   |

| 2.1.2 Electro Migration Statistical Modelling                          | 31   |

| 2.2 Ho  | T CARRIER DEGRADATION                                             |    |

|---------|-------------------------------------------------------------------|----|

| 2.2.1   | Hot Carrier Injection Mechanisms                                  |    |

| 2.2.2   | Channel Hot Electron (CHE) Injection                              |    |

| 2.2.3   | Drain Avalanche Hot Carrier (DAHC) Injection                      |    |

| 2.2.4   | Secondary Generated Hot Electron (SGHE) Injection                 |    |

| 2.2.5   | Hot Carrier Injection Reliability Implications                    |    |

| 2.3 TIM | ie Dependent Dielectric Breakdown (TDDB)                          |    |

| 2.3.1   | Entrapped Charges in SiO <sub>2</sub> and corresponding Interface |    |

| 2.3.2   | Current Tunneling and TDDB                                        |    |

| 2.4 NEG | GATIVE BIAS TEMPERATURE INSTABILITY                               |    |

| 2.4.1   | NBTI Physics                                                      |    |

| 2.5 IGE | 3T STRUCTURE AND MANUFACTURING                                    | 42 |

| 2.5.1   | IGBT Cell Structures                                              |    |

| 2.5.2   | IGBT Cell Manufacturing Process Flow                              |    |

| 2.5.3   | IGBT Die Design and Fabrication                                   | 47 |

| 2.5.4   | IGBT Packaging and Modules                                        |    |

| 2.6 LIT | ERATURE REPORTING IGBT FAILURE MECHANISMS, EFFECTS AND ANALYSIS   | 53 |

| 2.6.1   | IGBT Die Related Failure Mechanisms, Effect and Analysis          |    |

| 2.6.2   | IGBT Die Catastrophic Overstress Failure Mechanisms               | 55 |

| 2.6.3   | IGBT Die PoF Wear-out Mechanisms                                  |    |

| 2.6.4   | IGBT Package Related Failure Mechanisms, Effects and Analysis     |    |

| 2.6.5   | IGBT Application Related Failure Mechanisms, Effects and Analysis |    |

| 2.6.6   | Combining IGBT Failure Mechanisms                                 |    |

| 2.7 IGE | 3T RELIABILITY AND ACCELERATED AGEING TESTING                     | 69 |

| 2.7.1   | IGBT High Temperature Gate Bias (HTGB) Test                       | 69 |

| 2.7.2   | IGBT High Temperature Storage Life (HTSL) Test                    |    |

| 2.7.3   | IGBT Low Temperature Storage Life (LTSL) Test                     |    |

| 2.7.4   | IGBT Temperature Humidity Bias Stress (THBS) Test                 |    |

| 2.7.5   | IGBT Unbiased High Humidity Accelerated Stress Test (UHAST)       |    |

| 2.7.6   | IGBT Steady State Operation (SSO) Test                            |    |

| 2.7.7   | IGBT Thermal Cycling (TC) Test                                    |    |

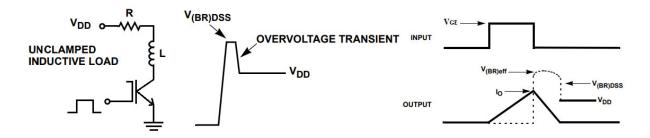

| 2.7.8   | IGBT Single-Shot Unclamped Inductive Switching (UIS) Test         |    |

| 2.7.9   | IGBT Repetitive Unclamped Inductive Switching (RUS) Test          |    |

| 2.8 IGE | 3T Power Cycling                                                  | 75 |

| 2.8.1   | Power Cycling Ageing Systems (PCAS)                               |    |

| 2.8.2   | DC PCAS Procedures                                                |    |

| 2.8.3   | Junction Temperature Measurement and Estimation                   |    |

| 2.   | .8.4  | Other Accelerated Ageing Procedures                                                                  | 84  |

|------|-------|------------------------------------------------------------------------------------------------------|-----|

| 2.9  | IGB   | T PRECURSORS TO FAILURE                                                                              | 84  |

| 2.   | .9.1  | IGBT Collector-Emitter Saturation Voltage (V <sub>CE_SAT</sub> )                                     | 85  |

| 2.   | .9.2  | IGBT Gate Threshold Voltage (V <sub>GE_THRES</sub> )                                                 | 86  |

| 2.   | .9.3  | IGBT Temperature Precursor Parameters                                                                | 87  |

| 2.   | .9.4  | IGBT Transient Time-Domain and Frequency Domain Precursors                                           | 89  |

| 2.   | .9.5  | IGBT Conducted and Radiated EMI as a Degradation Precursor                                           | 93  |

| 2.   | .9.6  | Other IGBT Condition Monitoring Techniques                                                           | 97  |

| 2.10 | IGE   | BT REMAINING USEFUL LIFETIME (RUL) MODELLING                                                         | 99  |

| 2.   | .10.1 | IGBT Model-Based RUL                                                                                 | 99  |

| 2.   | .10.2 | IGBT Model Based RUL at Product Development Stage                                                    | 100 |

| 2.   | .10.3 | IGBT Model-Based RUL Applied in the Field                                                            | 102 |

| 2.   | .10.4 | Data Driven Prognostic Techniques                                                                    | 105 |

| 2.   | .10.5 | Applicability of IGBT RUL Estimation                                                                 | 106 |

| 2.11 | CON   | CLUSIONS                                                                                             | 107 |

| СНАР | TER 3 | B IGBT ACCELERATED AGEING & CHARACTERIZATION SYSTEM                                                  | 108 |

| 3.1  | Aim   | OF THE PROPOSED ACCELERATED AGEING SYSTEM                                                            | 108 |

| 3.2  | Acc   | ELERATED AGEING SYSTEM REQUIREMENTS                                                                  | 108 |

| 3.3  | Impi  | EMENTED PCAS DESIGN                                                                                  | 110 |

| 3.   | .3.1  | PCAS Commercial Instrumentation                                                                      | 110 |

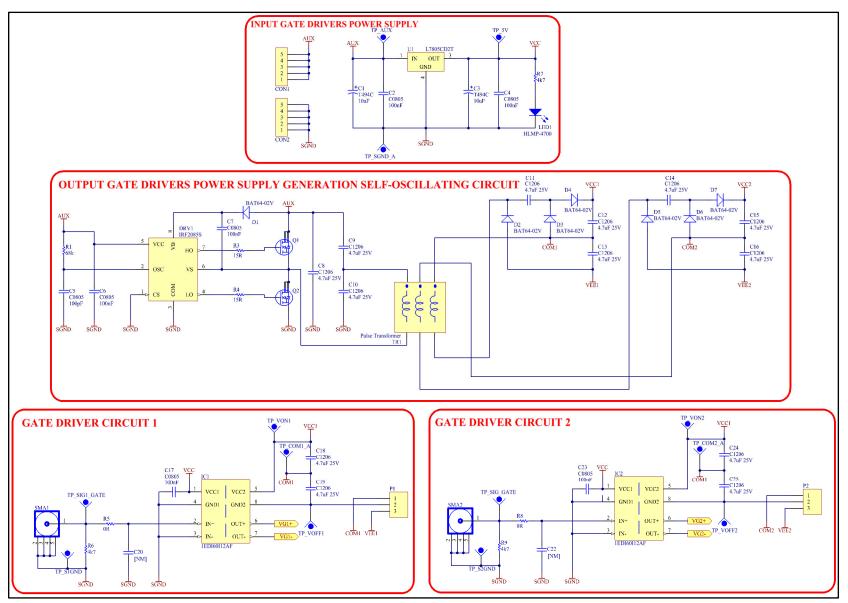

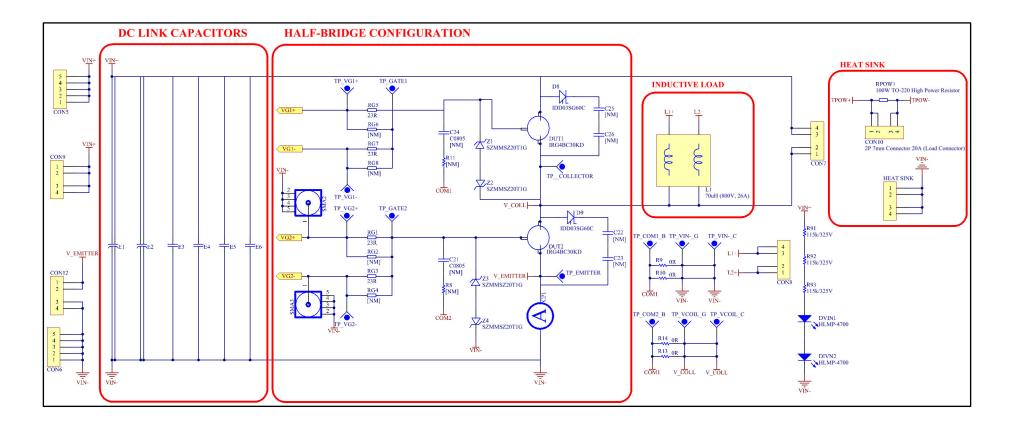

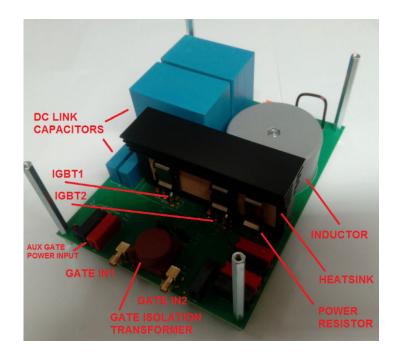

| 3.   | .3.2  | PCAS Custom-Built Hardware                                                                           | 111 |

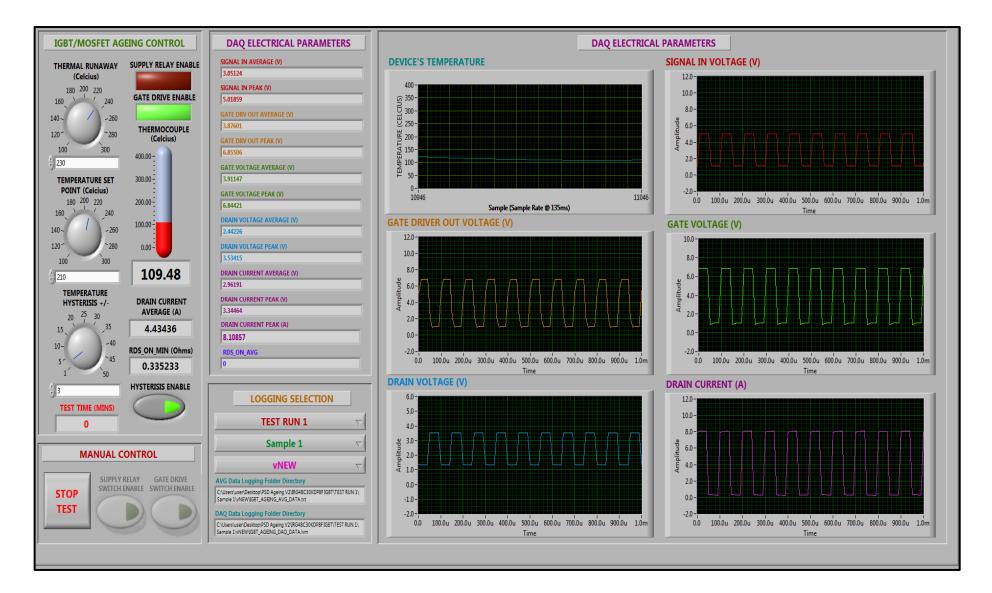

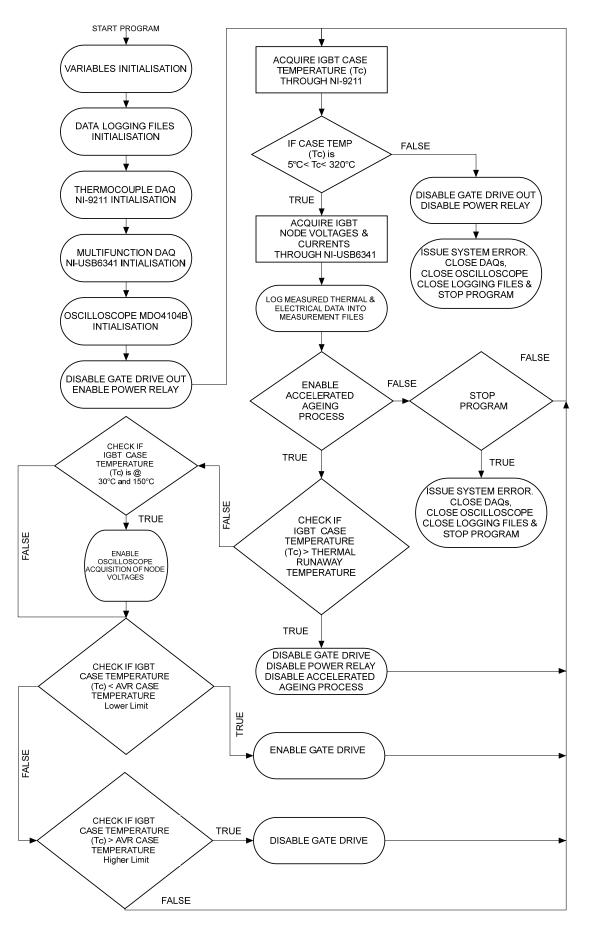

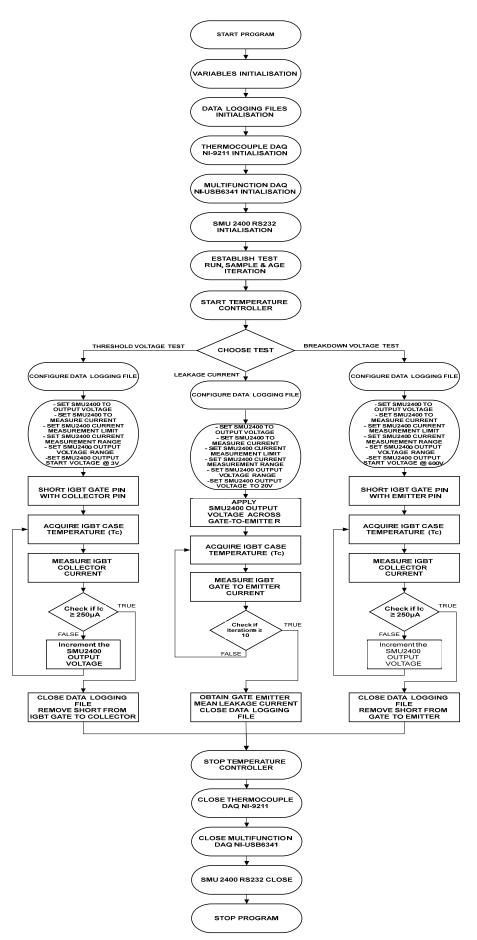

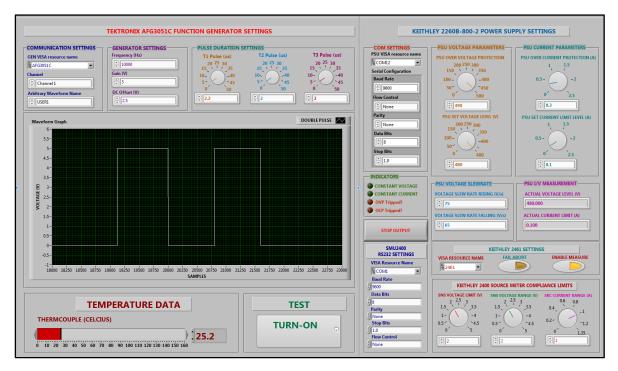

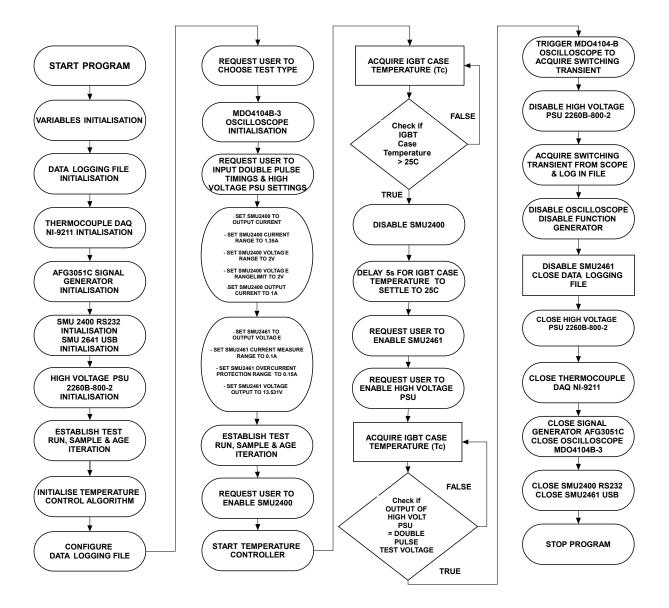

| 3.   | .3.3  | IGBT DC PCAS Software                                                                                | 116 |

| 3.   | .3.4  | IGBT Accelerated Ageing Experimental Procedure                                                       | 120 |

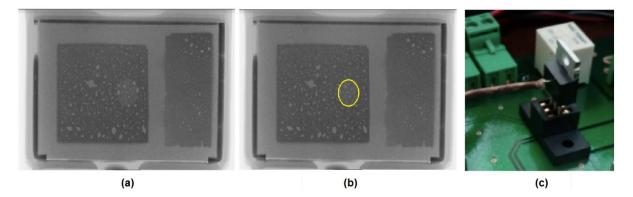

| 3.   | .3.5  | IGBT Ageing Mechanical (X-Ray) Characterization                                                      | 128 |

| 3.4  | IGB   | T'S STATIC ELECTRICAL PARAMETERS CHARACTERIZATION SETUP                                              | 135 |

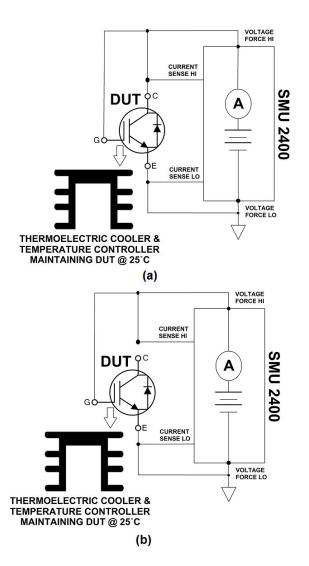

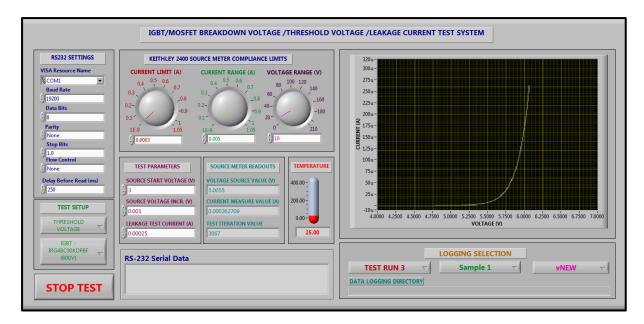

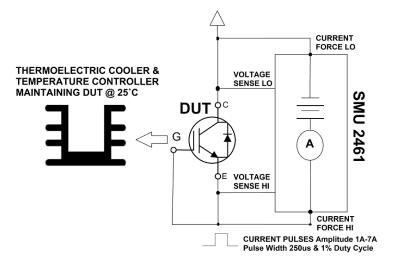

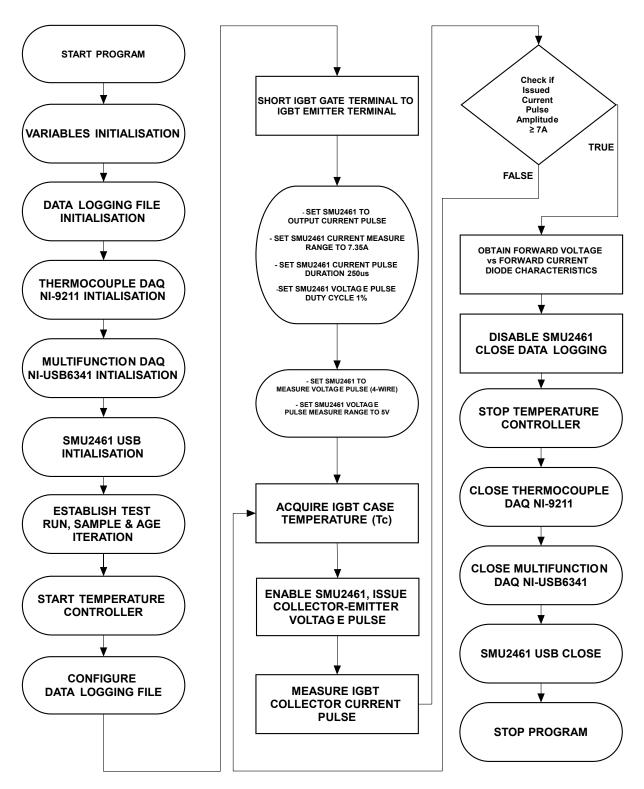

| 3.   | .4.1  | IGBT Threshold Voltage & Leakage Current Characterization Hardware & Software Setup                  | 136 |

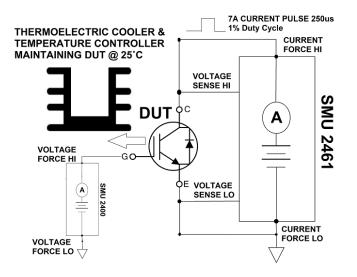

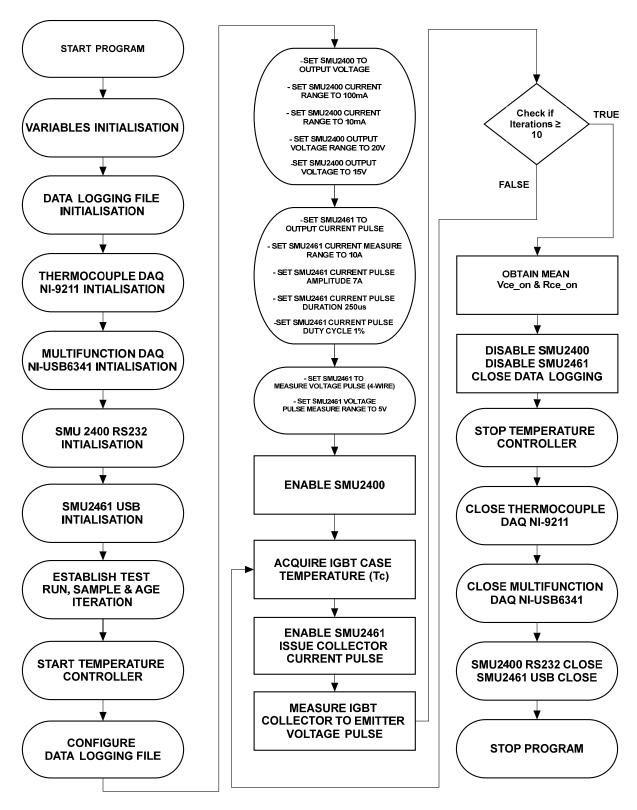

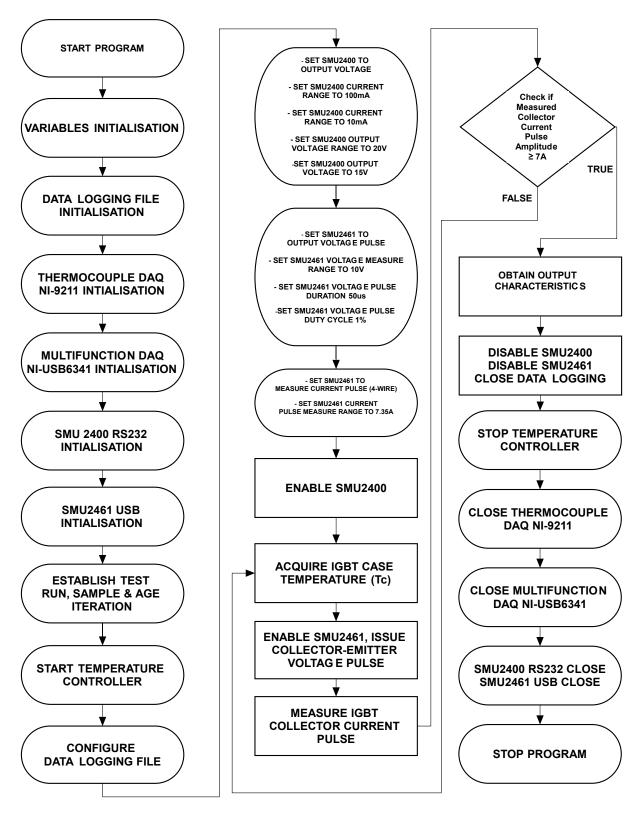

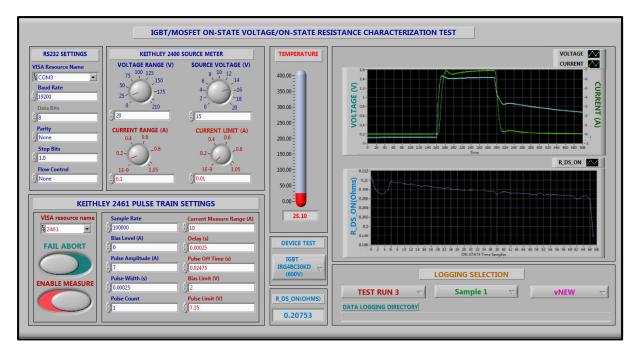

| 3.   | .4.2  | IGBT On-State Voltage (V <sub>CE_ON</sub> ), On-State Resistance and Output Characterization Setup   | 139 |

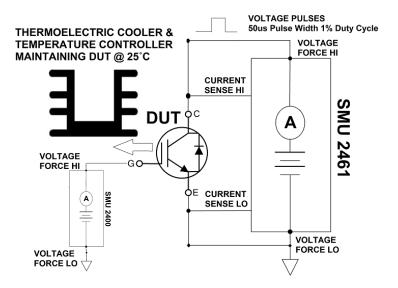

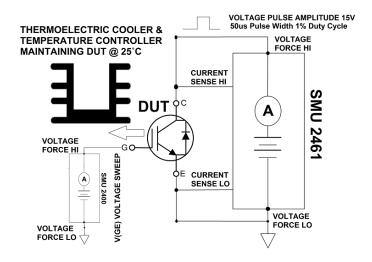

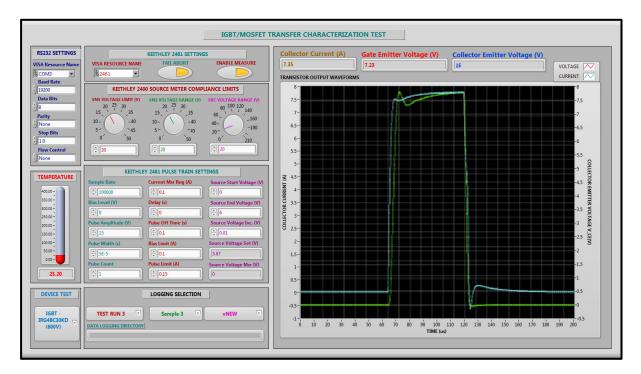

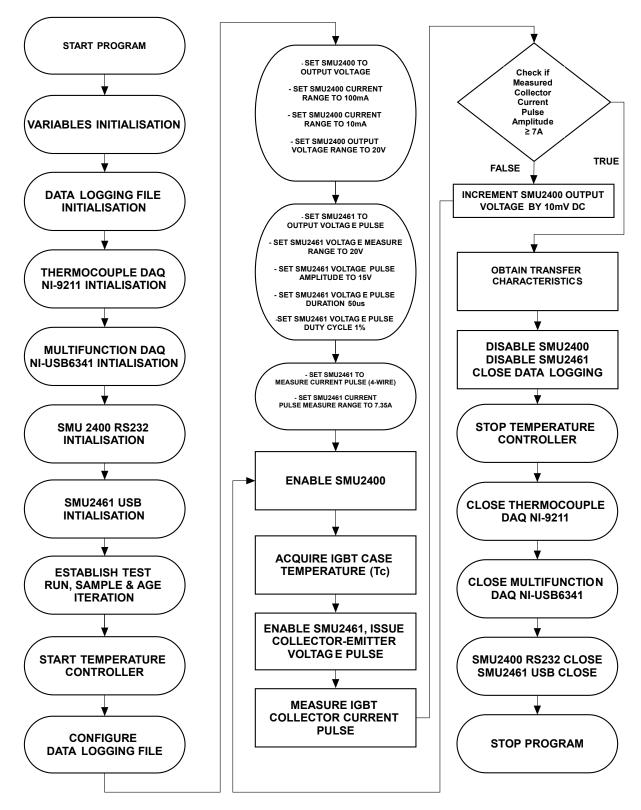

| 3.   | .4.3  | IGBT Transfer Characteristics and Forward Transconductance Characterization Setup                    | 144 |

| 3.   | .4.4  | IGBT Internal Diode Forward Voltage Drop ( $V_{FM}$ ) Characterization Setup                         | 147 |

| 3.5  | IGB   | T'S STATIC ELECTRICAL PARAMETERS CHARACTERIZATION RESULTS                                            | 149 |

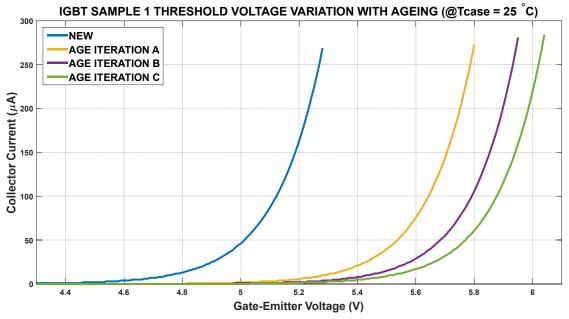

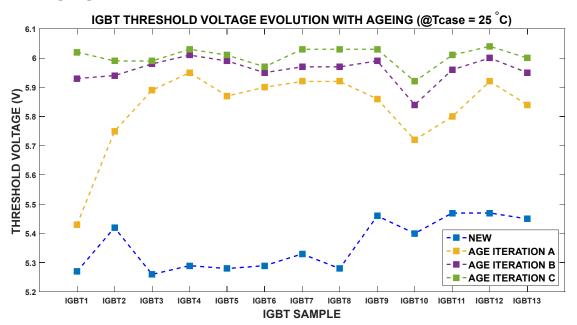

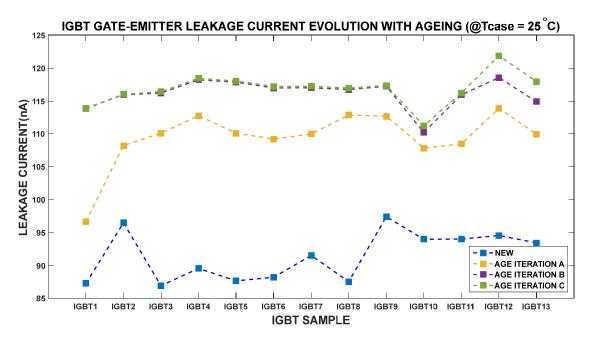

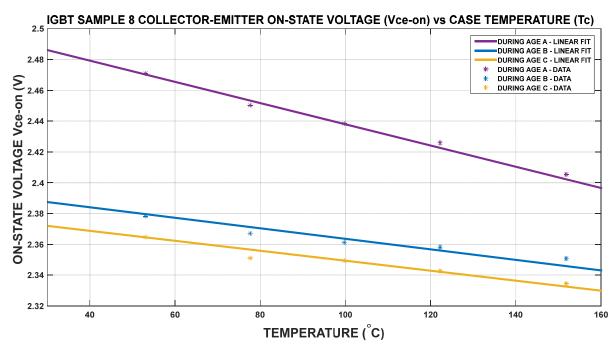

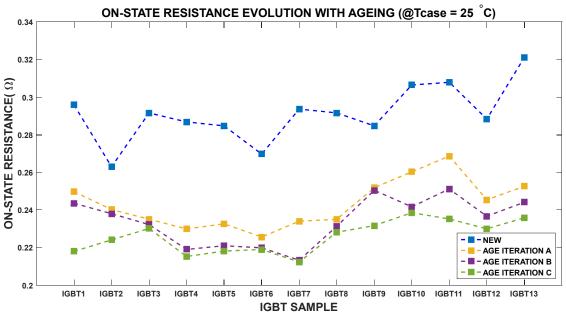

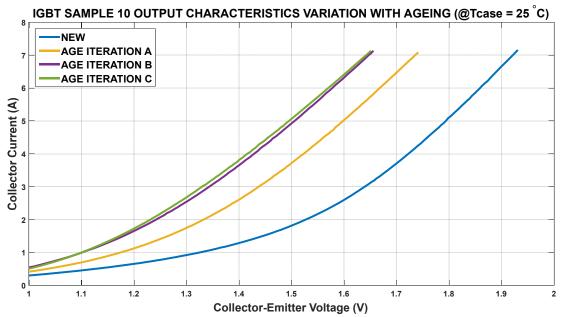

| 3.   | .5.1  | IGBT Threshold Voltage & Leakage Current Characterization Results                                    | 149 |

| 3.   | .5.2  | IGBT On-State Voltage (V <sub>CE_ON</sub> ), On-State Resistance and Output Characterization Results | 152 |

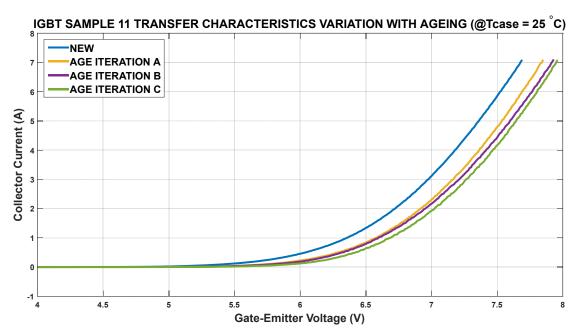

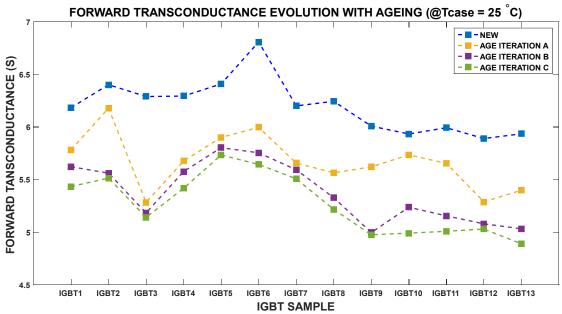

| 3.   | .5.3  | IGBT Transfer Characteristics and Forward Transconductance Characterization Results                  | 157 |

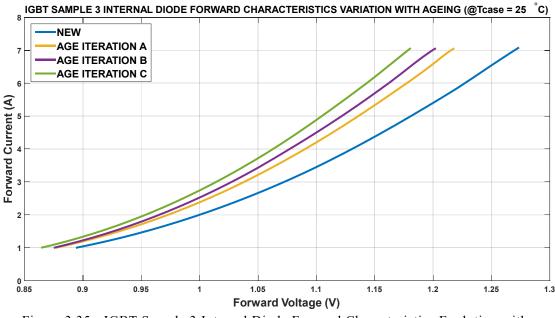

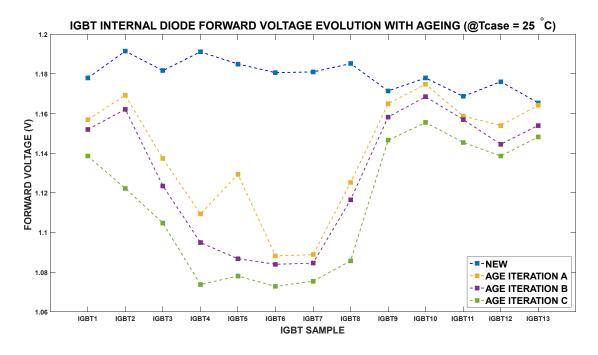

| 3.   | .5.4  | IGBT Internal Diode Forward Voltage Drop Characterization Results                                    | 158 |

| 36   | CON   | CLUSIONS                                                                                             |     |

| СНА | PTER    | 4 SWITCHING PARAMETERS CHARACTERIZATION OF AGED IGBTS                                                                                                 |                            |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 4.1 | l Aim   | OF THE PROPOSED IGBT SWITCHING PARAMETERS CHARACTERIZATION SYSTEM                                                                                     | 163                        |

| 4.2 | 2 SPC   | 'S Requirements                                                                                                                                       | 163                        |

| 4.3 | B DOU   | JBLE-PULSE TEST PROCEDURE                                                                                                                             | 165                        |

| 4.4 | 4 Impi  | LEMENTED IGBT SWITCHING PARAMETERS CHARACTERIZATION SYSTEM (SPCS)                                                                                     | 167                        |

|     | 4.4.1   | SPCS Commercial Instrumentation                                                                                                                       | 167                        |

|     | 4.4.2   | SPCS Custom Hardware                                                                                                                                  | 169                        |

|     | 4.4.3   | SPCS Custom-Built Software                                                                                                                            | 173                        |

|     | 4.4.4   | IGBT Switching Parameters Characterization Experimental Procedure                                                                                     | 176                        |

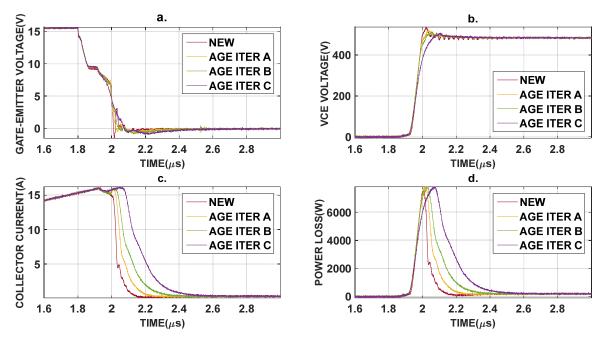

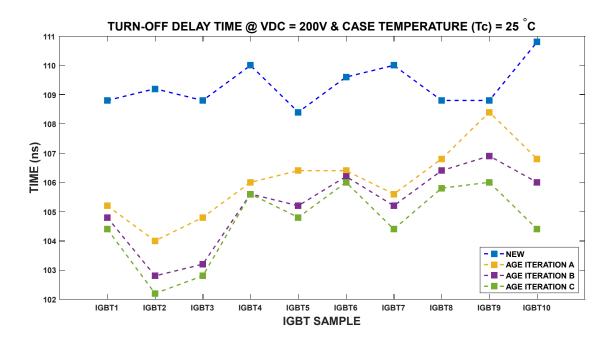

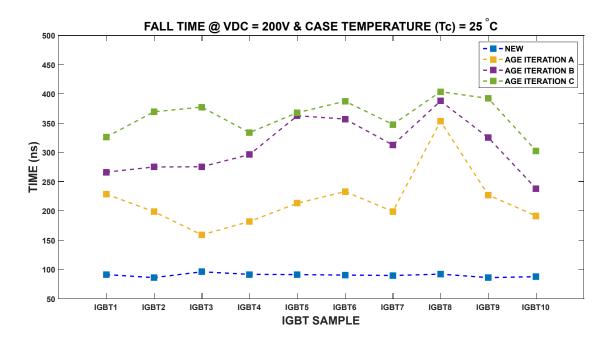

| 4.5 | 5 IGB   | T ACCELERATED AGEING SWITCHING PARAMETERS CHARACTERIZATION RESULTS                                                                                    | 177                        |

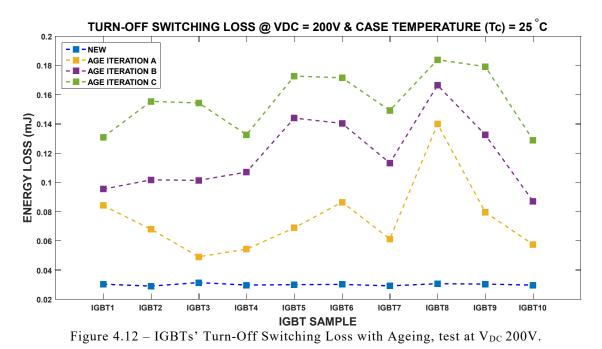

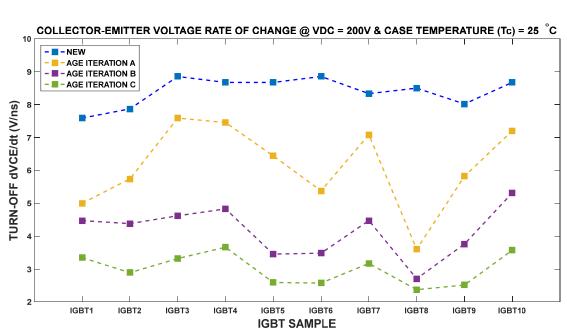

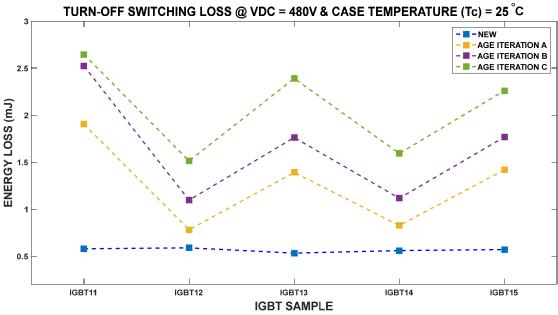

|     | 4.5.1   | <i>Turn-Off Delay Time (t<sub>D_OFF</sub>), Fall-Time (t<sub>F</sub>), Turn-On Switching Loss (E<sub>OFF</sub>) and Collector</i>                     | r-Emitter                  |

|     | Voltage | e Rate of Change during Turn-Off ( $dV_{CE}/dt_{OFF}$ )                                                                                               | 178                        |

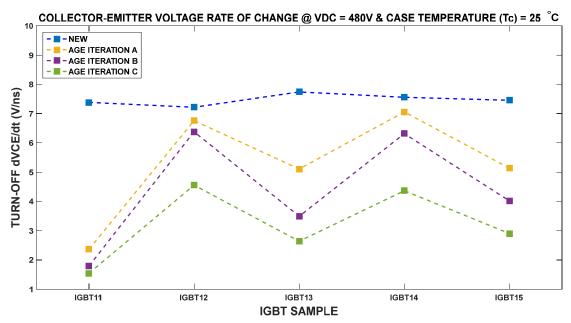

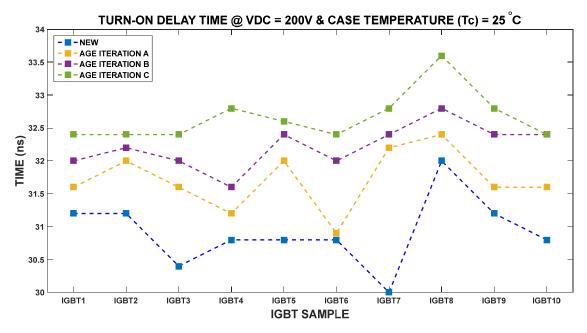

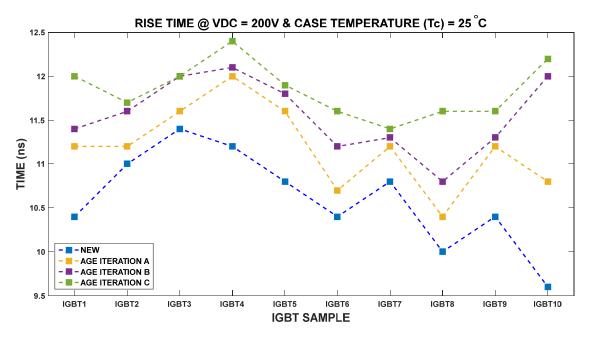

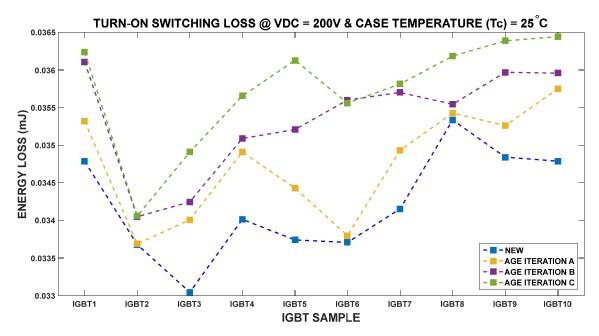

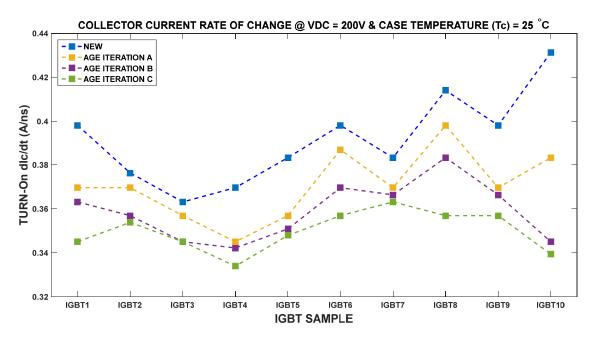

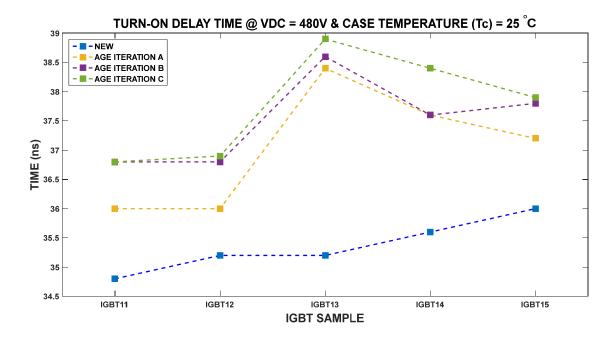

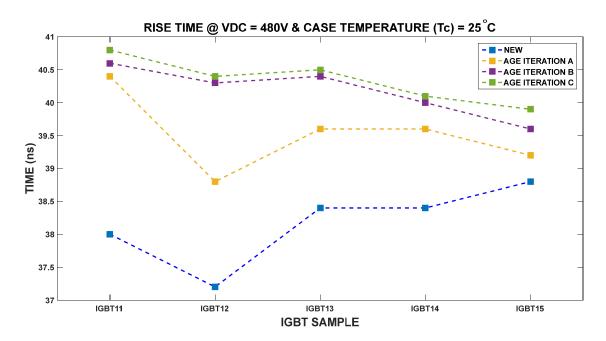

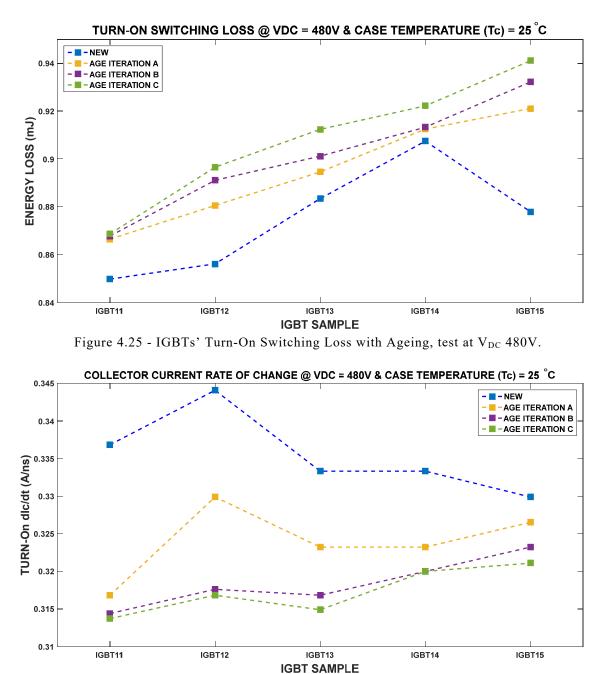

|     | 4.5.2   | <i>Turn-On Delay Time</i> $(t_{D_ON})$ , <i>Rise-Time</i> $(t_R)$ , <i>Turn-On Switching Loss</i> $(E_{ON})$ and Collector                            | Current                    |

|     | Rate of | Change during Turn-On (dI <sub>C</sub> /dt <sub>ON</sub> )                                                                                            | 183                        |

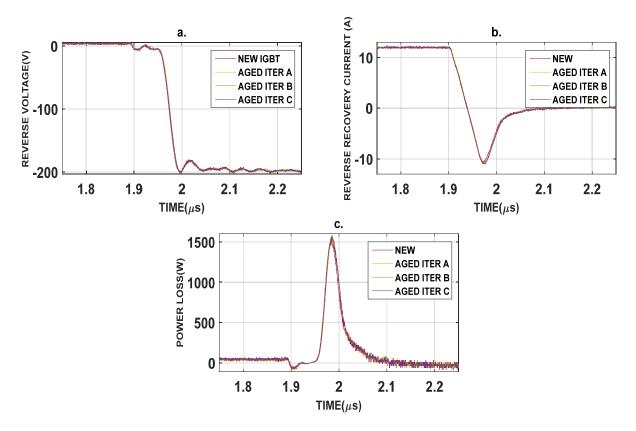

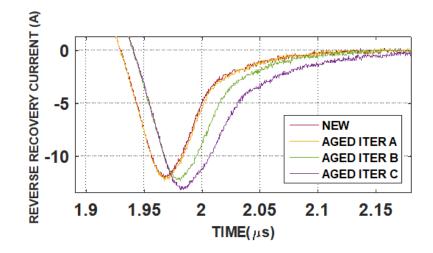

|     | 4.5.3   | IGBT's Internal Diode Reverse Recovery Time $(t_{RR})$ , Diode Peak Reverse Recovery Current                                                          | ıt (I <sub>PRR</sub> ) 189 |

| 4.6 | 5 IGB   | TS SWITCHING PARAMETERS AGEING EVOLUTION FOR A DIFFERENT IGBT MODEL.                                                                                  | 195                        |

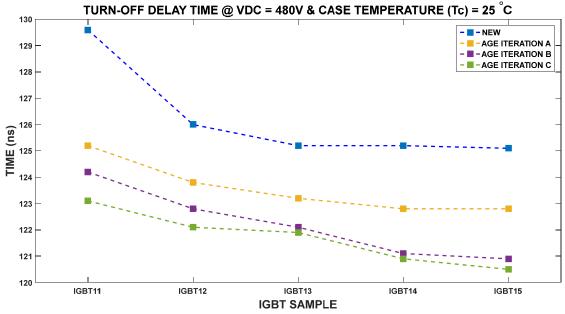

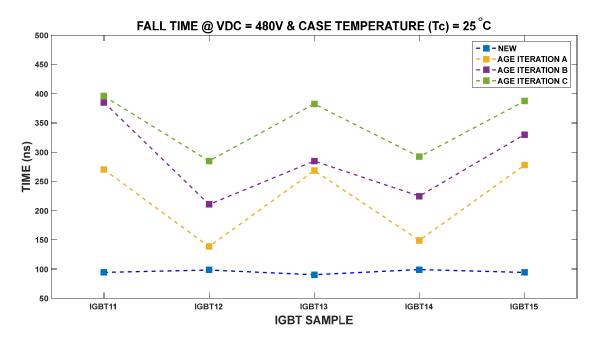

|     | 4.6.1   | <i>Turn-Off Delay Time (t</i> <sub>D_OFF</sub> ), <i>Fall-Time (t</i> <sub>F</sub> ), <i>Turn-On Switching Loss (E</i> <sub>OFF</sub> ) and Collector | r-Emitter                  |

|     | Voltage | e Rate of Change during Turn-Off (dV <sub>CE</sub> /dt <sub>OFF</sub> )                                                                               | 195                        |

|     | 4.6.2   | <i>Turn-On Delay Time</i> $(t_{D_ON})$ , <i>Rise-Time</i> $(t_R)$ , <i>Turn-On Switching Loss</i> $(E_{ON})$ and Collector                            | Current                    |

|     | Rate of | Change during Turn-On $(dI_C/dt_{ON})$                                                                                                                | 197                        |

|     | 4.6.3   | IGBT's Internal Diode Reverse Recovery Time $(t_{RR})$ , Diode Peak Reverse Recovery Current                                                          | ıt (I <sub>PRR</sub> ) 199 |

| 4.7 | 7 CON   | ICLUSIONS                                                                                                                                             | 202                        |

| СНА | PTER    | 5 MODELLING SWITCHING TRANSIENTS OF AGED IGBTS                                                                                                        | 203                        |

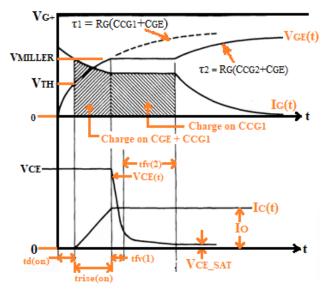

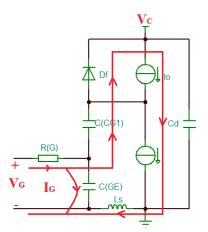

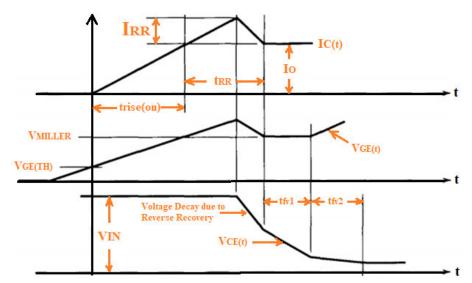

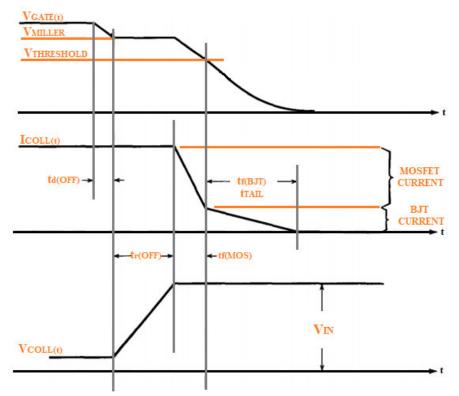

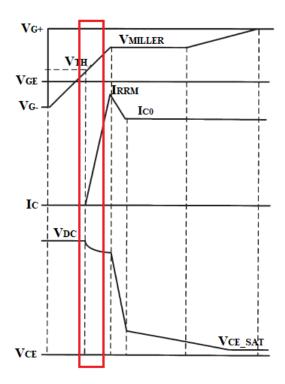

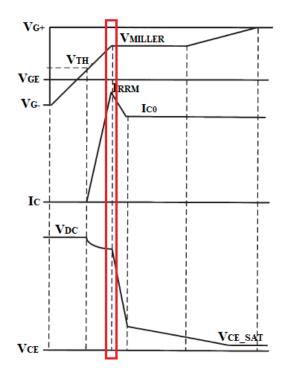

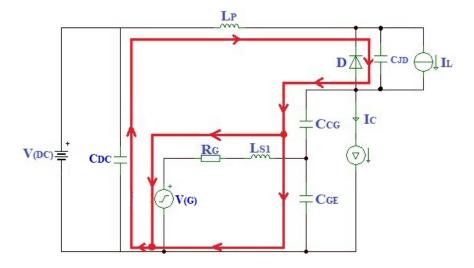

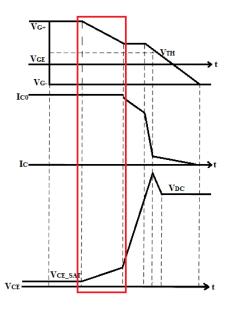

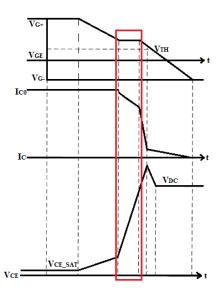

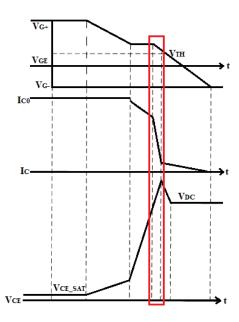

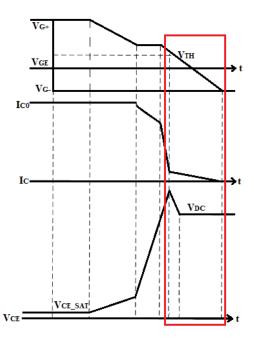

| 5.1 | l IGB   | T's Switching Transients General Analysis                                                                                                             | 204                        |

|     | 5.1.1   | IGBT General Turn-On Behaviour                                                                                                                        |                            |

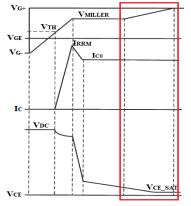

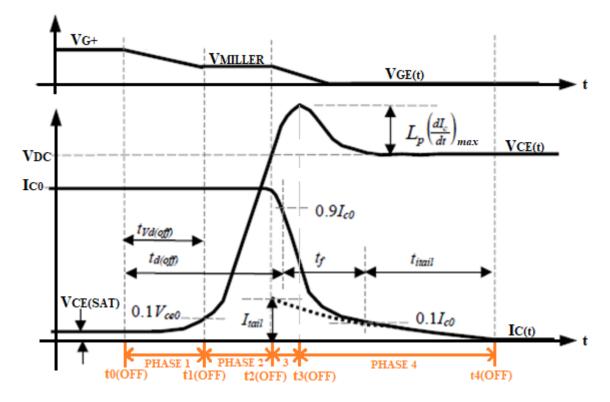

|     | 5.1.2   | IGBT General Turn-Off Behavior                                                                                                                        | 210                        |

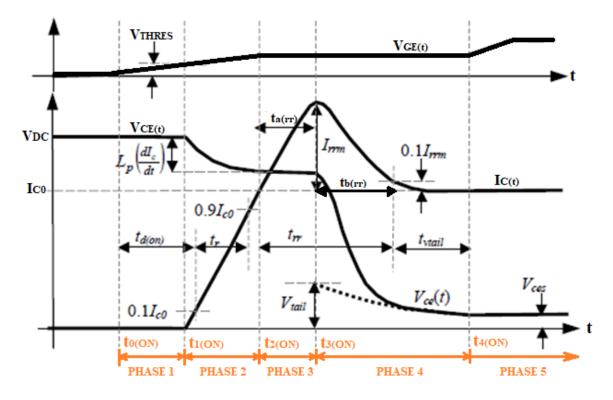

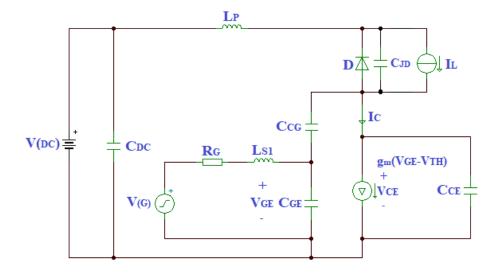

| 5.2 | 2 IGB   | T Switching Transients Linear Piecewise Modelling                                                                                                     | 211                        |

|     | 5.2.1   | IGBT Piecewise Linear Model for Turn-On Transients during Phase 1                                                                                     |                            |

|     | 5.2.2   | IGBT Piecewise Linear Model for Turn-On Transients during Phase 2                                                                                     |                            |

|     | 5.2.3   | IGBT Piecewise Linear Model Turn-On Transients during Phase 3                                                                                         | 214                        |

|     | 5.2.4   | IGBT Piecewise Linear Modelling for Turn-On Transients during Phase 4                                                                                 |                            |

|     | 5.2.5   | IGBT Piecewise Linear Model Turn-On Transients during Phase 5                                                                                         |                            |

|     | 5.2.6   | IGBT Piecewise Linear Model Turn-Off Transients during Phase 1                                                                                        |                            |

|     | 5.2.7   | IGBT Piecewise Linear Model Turn-Off Transients during Phase 2                                                                                        |                            |

|     | 5.2.8   | IGBT Piecewise Linear Model Turn-Off Transients during Phase 3                                                                                        |                            |

|     | 5.2.9   | IGBT Model Turn-Off Transients during Phase 4                                                                                                         |                            |

|     |         |                                                                                                                                                       |                            |

| 5.2.10  | IGBT Piecewise Linear Model Parameters Extraction and Results                       |     |

|---------|-------------------------------------------------------------------------------------|-----|

| 5.2.11  | Limitations of the IGBT Linear Piecewise Model                                      |     |

| 5.3 IGE | T Switching Transients Non-Linear Modelling                                         | 237 |

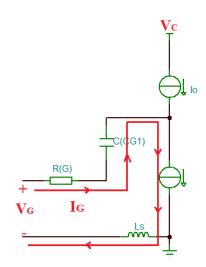

| 5.3.1   | IGBT Non-Linear Model for Turn-On Transients during Phase 1                         | 237 |

| 5.3.2   | IGBT Non-Linear Model for Turn-On Transients during Phase 2                         | 237 |

| 5.3.3   | IGBT Non-Linear Model for Turn-On Transients during Phase 3                         | 239 |

| 5.3.4   | IGBT Non-Linear Model for Turn-On Transients during Phase 4                         | 242 |

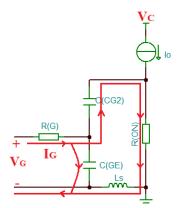

| 5.3.5   | IGBT Non-Linear Model for Turn-Off Transients during Phase 1 and Phase 2            | 245 |

| 5.3.6   | IGBT Non-Linear Model for Turn-Off Transients during Phase 3 and Phase 4            | 249 |

| 5.3.7   | IGBT Non-Linear Model Parameters and Results                                        | 253 |

| 5.4 IGE | T PARASITIC CAPACITANCES                                                            |     |

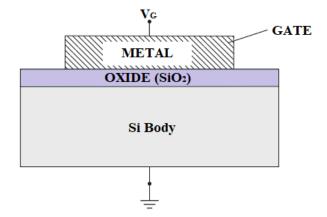

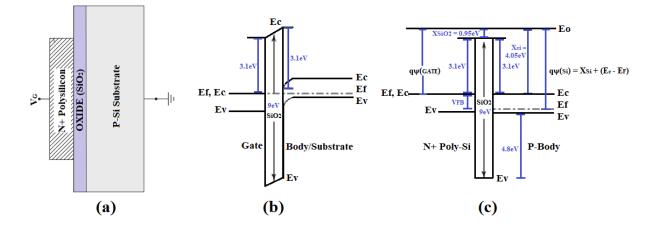

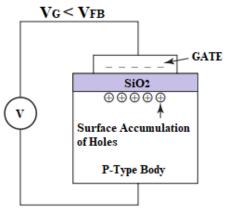

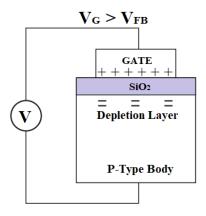

| 5.4.1   | MOS Capacitance Structure and the Flat-Band Condition                               | 256 |

| 5.4.2   | MOS Structure during Surface Accumulation                                           | 257 |

| 5.4.3   | MOS Structure during Surface Depletion                                              | 259 |

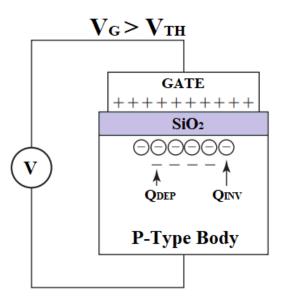

| 5.4.4   | MOS Structure during Threshold Condition                                            |     |

| 5.4.5   | MOS Structure during Strong Inversion                                               |     |

| 5.4.6   | MOS Structure under high frequency AC                                               |     |

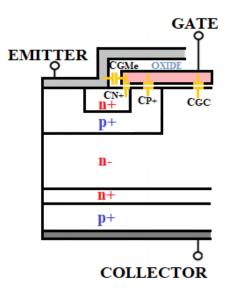

| 5.4.7   | IGBT Input Capacitances in relation to the MOS Structure                            |     |

| 5.5 IGE | T MODELLING OF THE TURN-ON AND TURN-OFF TRANSIENTS' EVOLUTION WITH AGEING           |     |

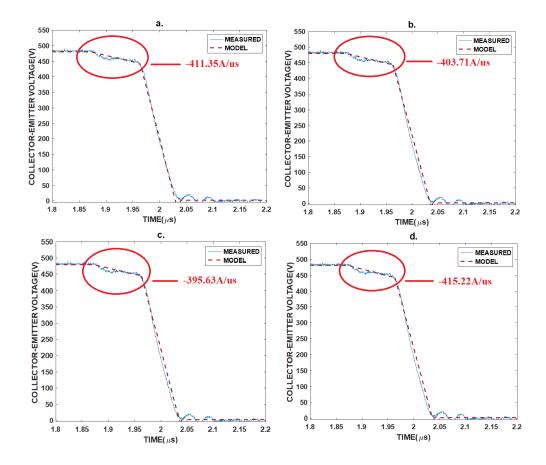

| 5.5.1   | IGBT Turn-Off Transient during Phase 1                                              |     |

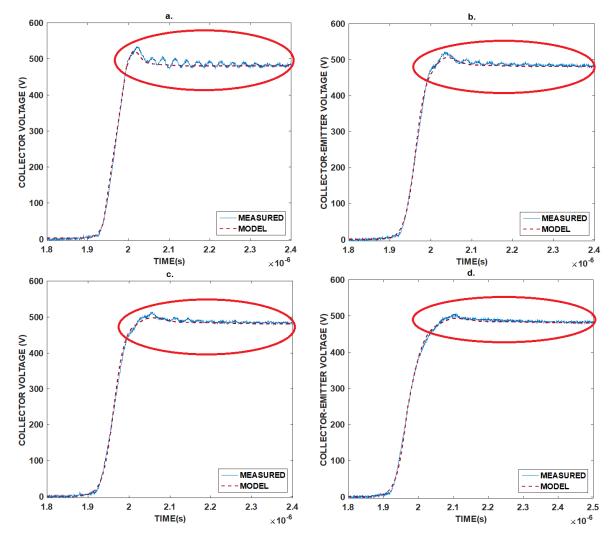

| 5.5.2   | IGBT Collector-Emitter Voltage (V <sub>CE</sub> ) Turn-Off Transient during Phase 2 |     |

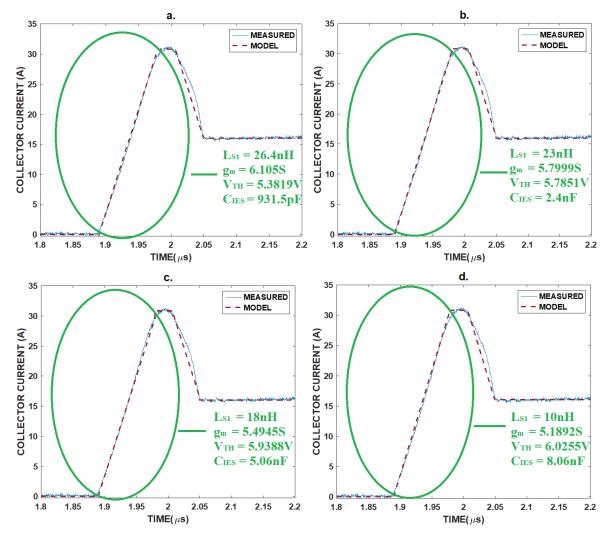

| 5.5.3   | IGBT Collector Current ( $I_C$ ) Turn-Off Transient during Phase 2                  | 277 |

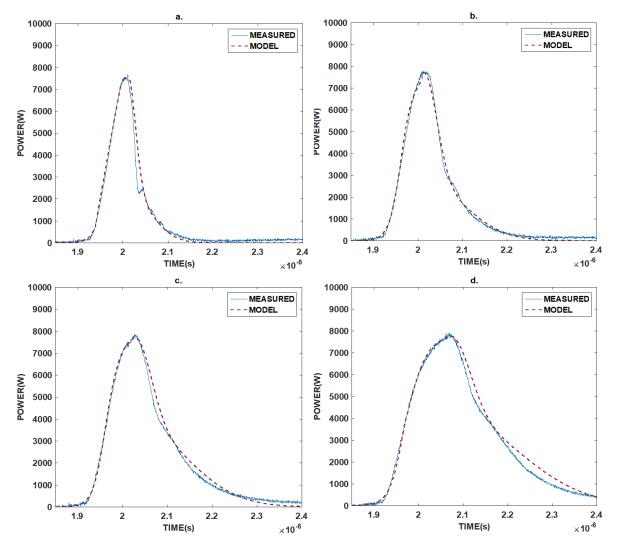

| 5.5.4   | IGBT Collector Current ( $I_C$ ) Turn-Off Transient during Phase 3 and Phase 4      |     |

| 5.5.5   | IGBT Collector-Emitter Voltage (V <sub>CE</sub> ) Turn-Off Transient Phase 3 & 4    |     |

| 5.5.6   | IGBT Turn-Off Energy Loss                                                           |     |

| 5.5.7   | IGBT Turn-On Transients Evolution with Accelerated Ageing                           |     |

| 5.6 Con | ICLUSIONS                                                                           |     |

| CHAPTER | 6 IGBT'S AGEING AND EM CONDUCTED EMISSIONS                                          |     |

| 6.1 INT | RODUCTION                                                                           |     |

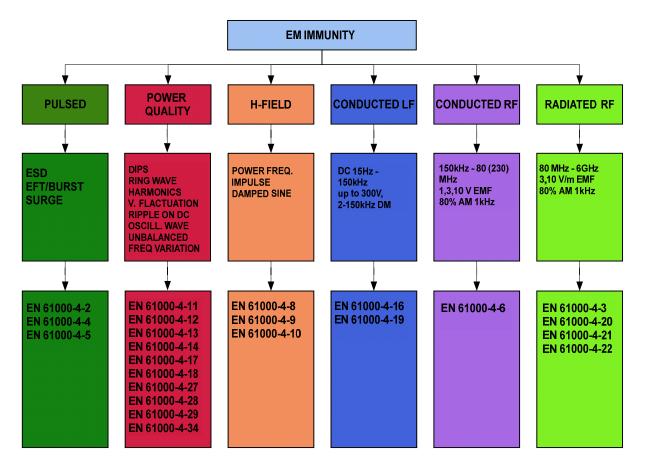

| 6.1.1   | EM Emissions Testing                                                                |     |

| 6.1.2   | EM Immunity Testing                                                                 |     |

| 6.2 EM  | CONDUCTED EMISSIONS                                                                 |     |

| 6.2.1   | Line Impedance Stabilization Network (LISN)                                         |     |

| 6.2.2   | General Conducted Emissions Test Setup                                              | 311 |

| 6.3 IGE | T'S AGEING AND ITS IMPACTS ON CONDUCTED EMISSIONS                                   |     |

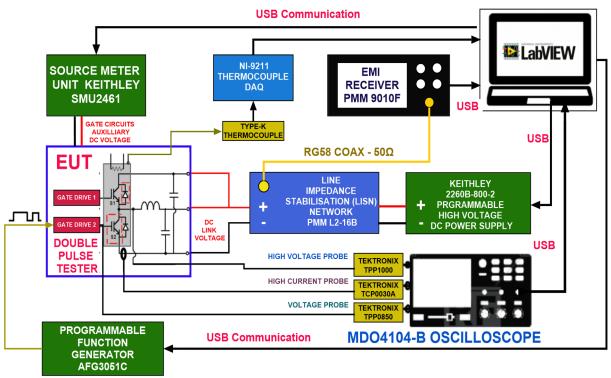

| 6.3.1   | Implemented EM Conducted Emissions Test Setup                                       | 314 |

| 6.3.2   | EM Conducted Emission Implemented Test Procedure                                    |     |

| REF | ERENC  | 'ES                                                                                    |  |

|-----|--------|----------------------------------------------------------------------------------------|--|

|     |        | S                                                                                      |  |

|     |        | URE WORK                                                                               |  |

|     |        | CLUSIONS                                                                               |  |

| СНА | PTER ' | 7 CONCLUSION AND FUTURE WORK                                                           |  |

| 6.  | 5 CON  | CLUSIONS                                                                               |  |

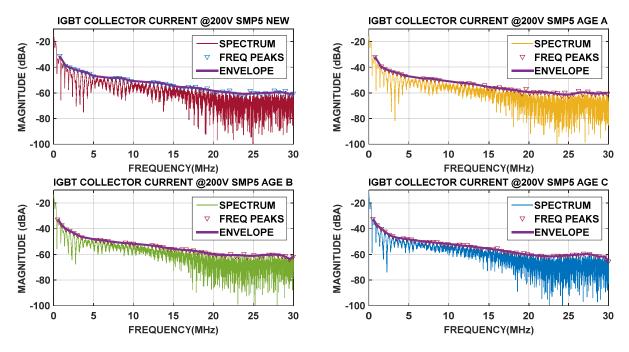

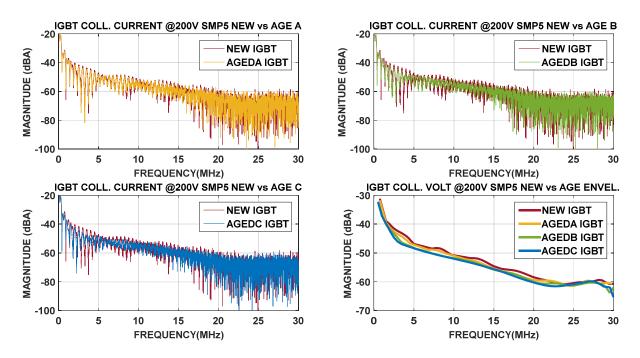

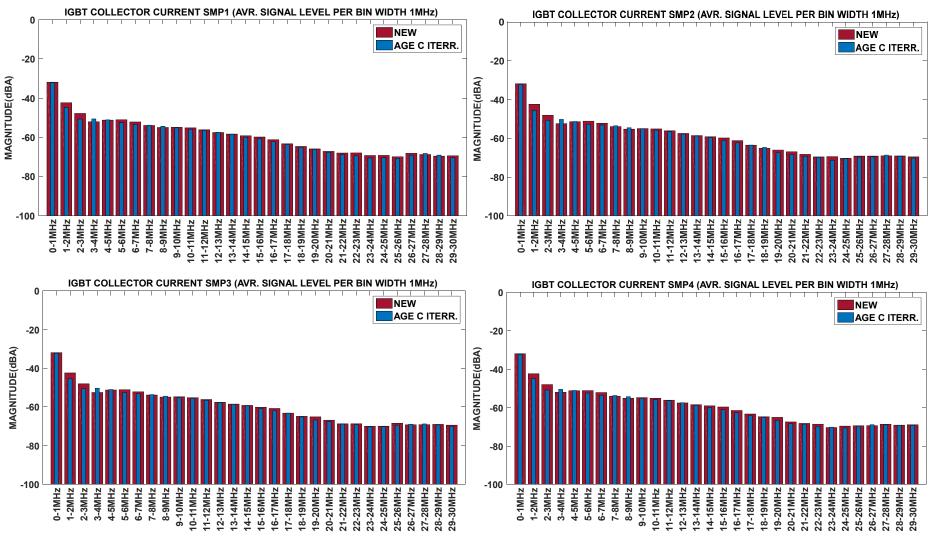

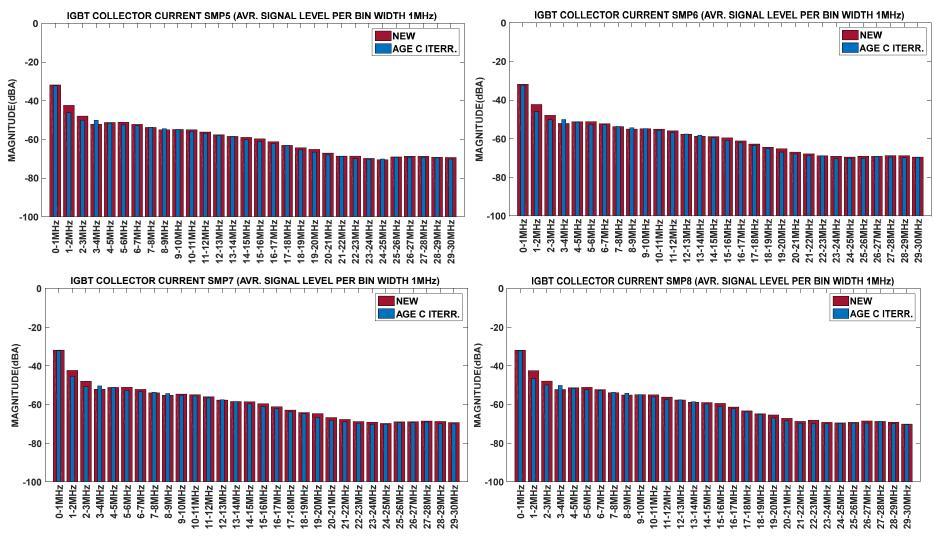

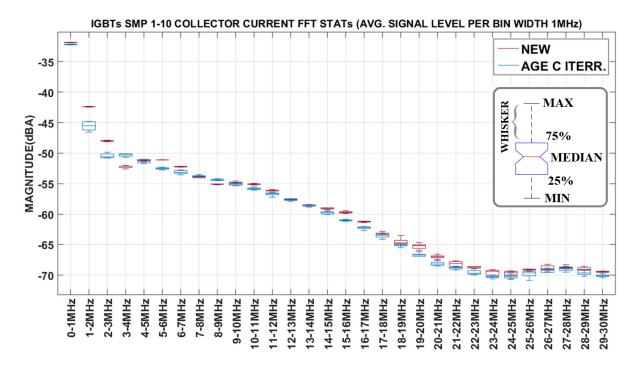

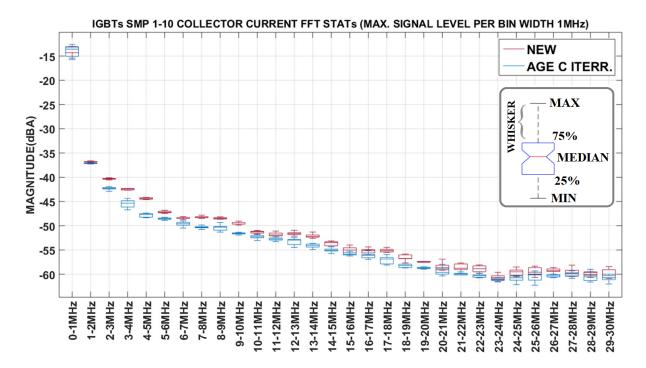

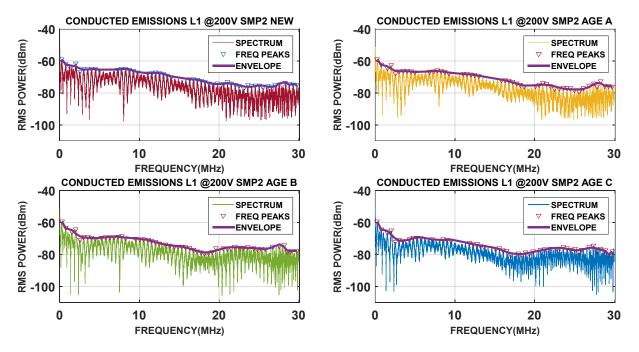

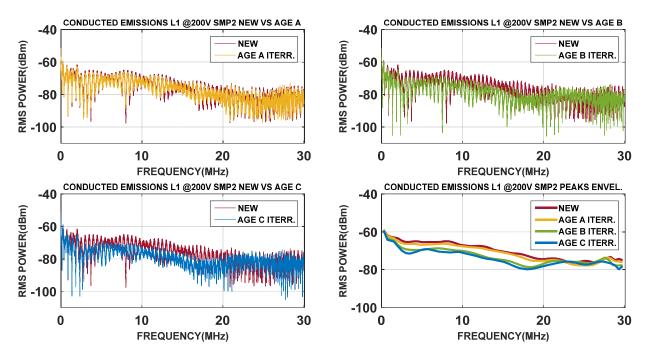

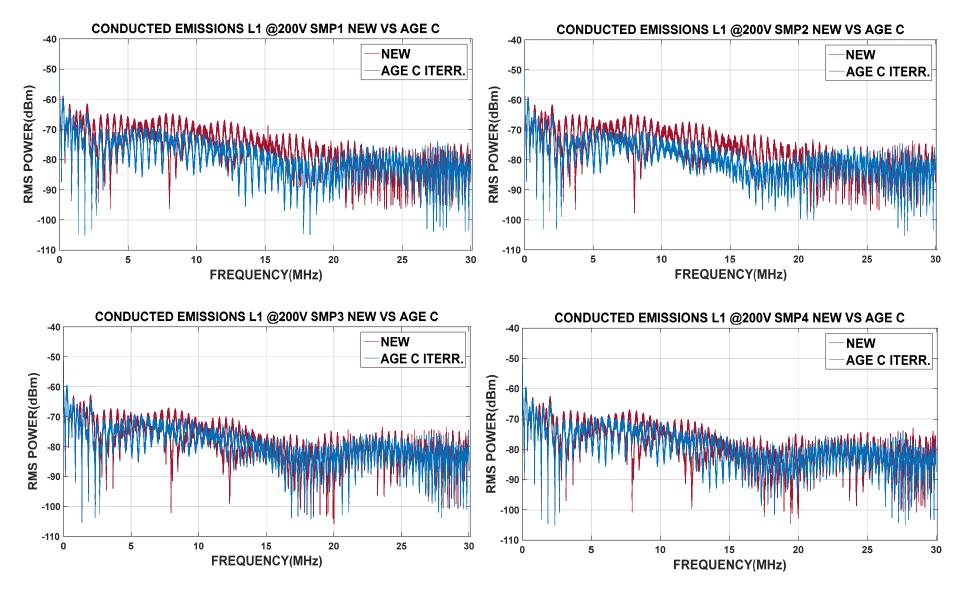

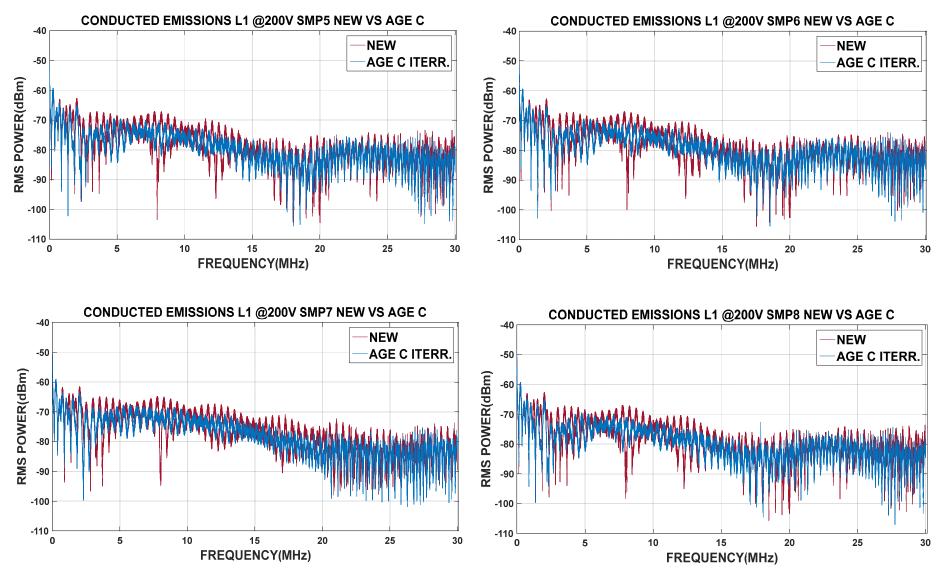

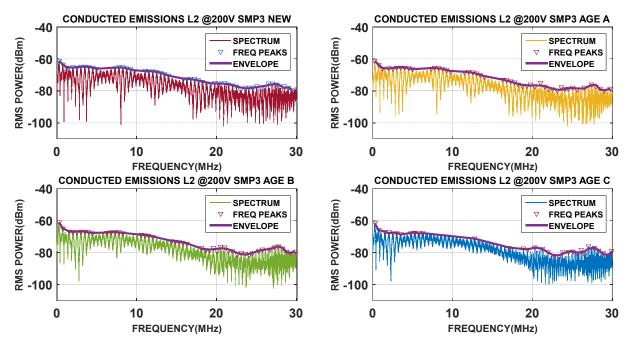

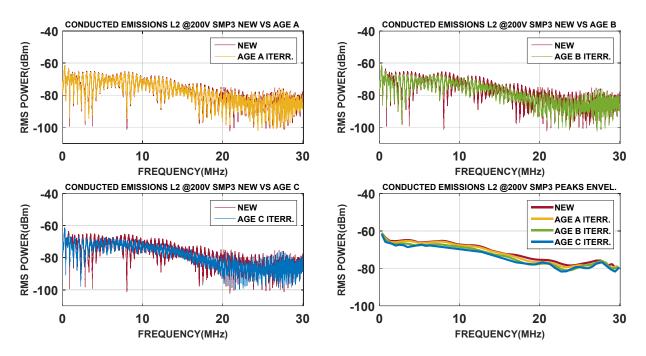

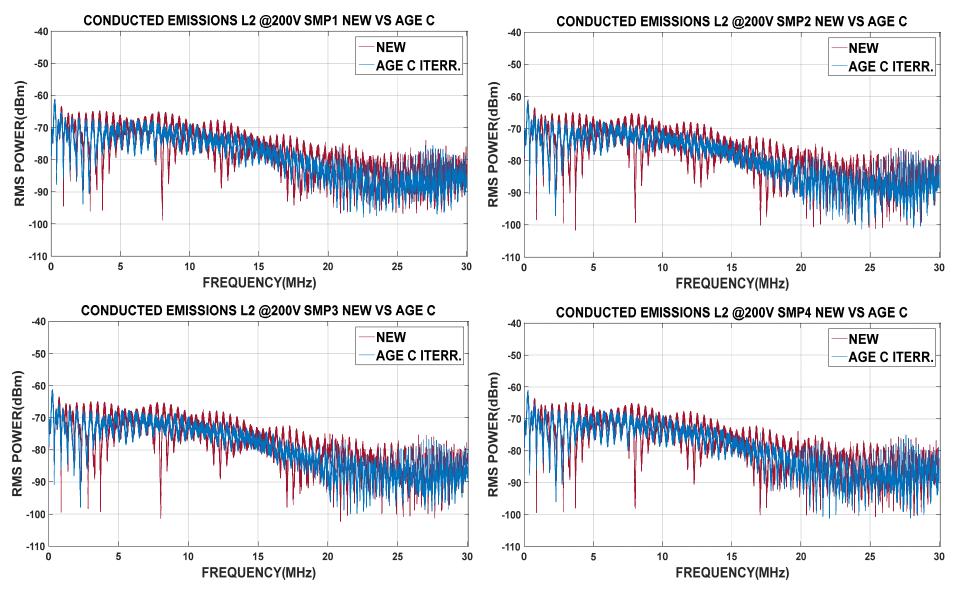

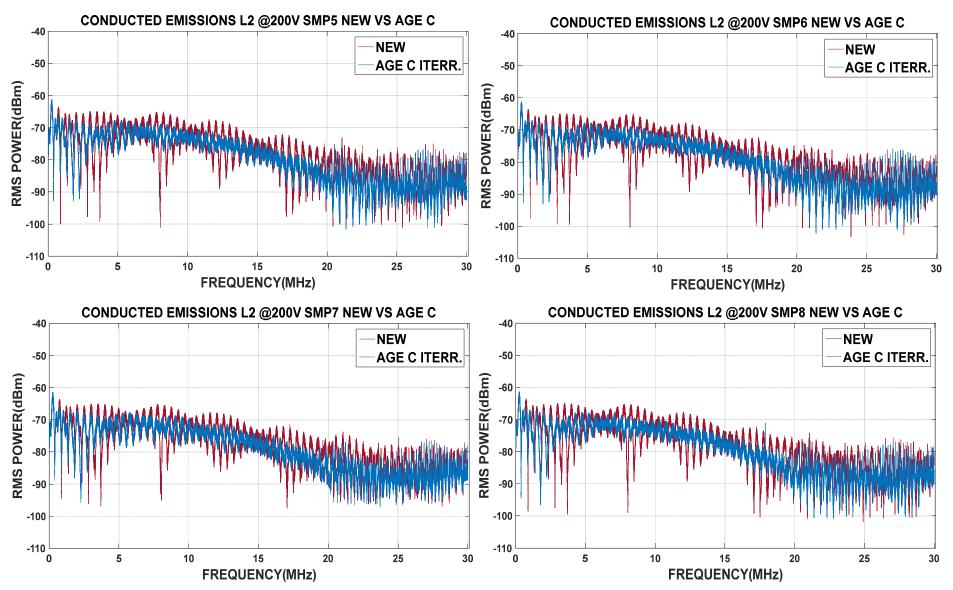

|     | 6.4.1  | EM Conducted Emissions Evolution with Ageing Results                                   |  |

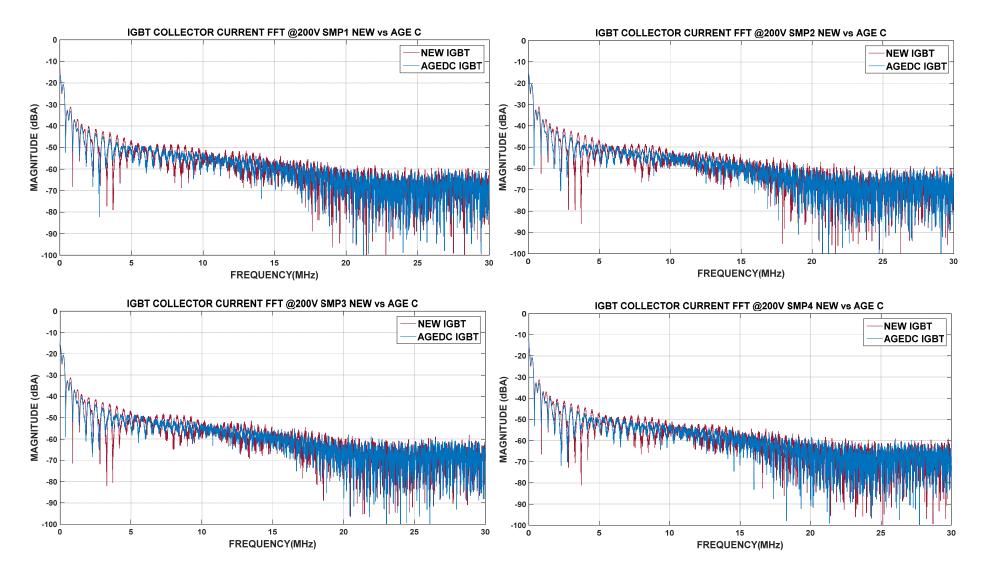

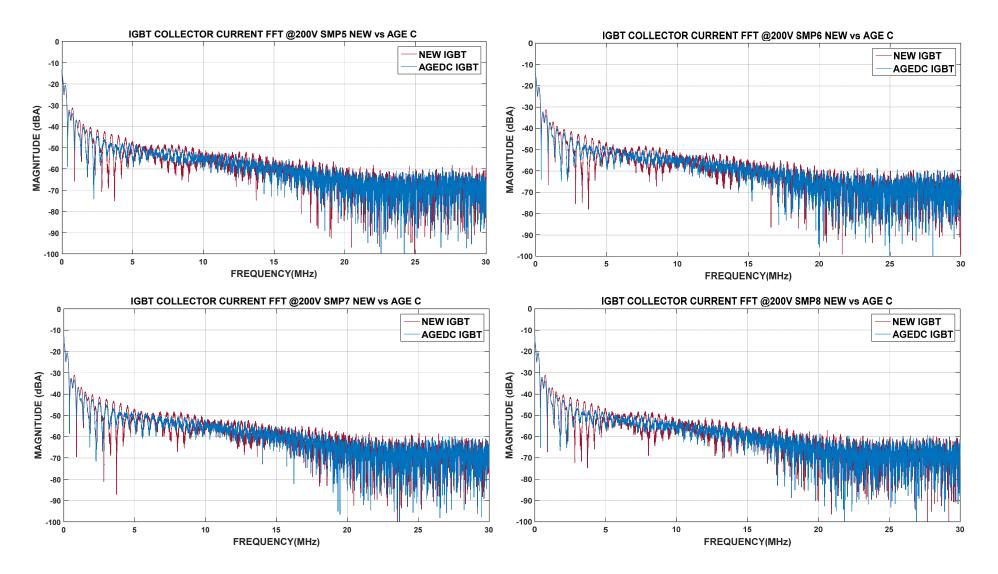

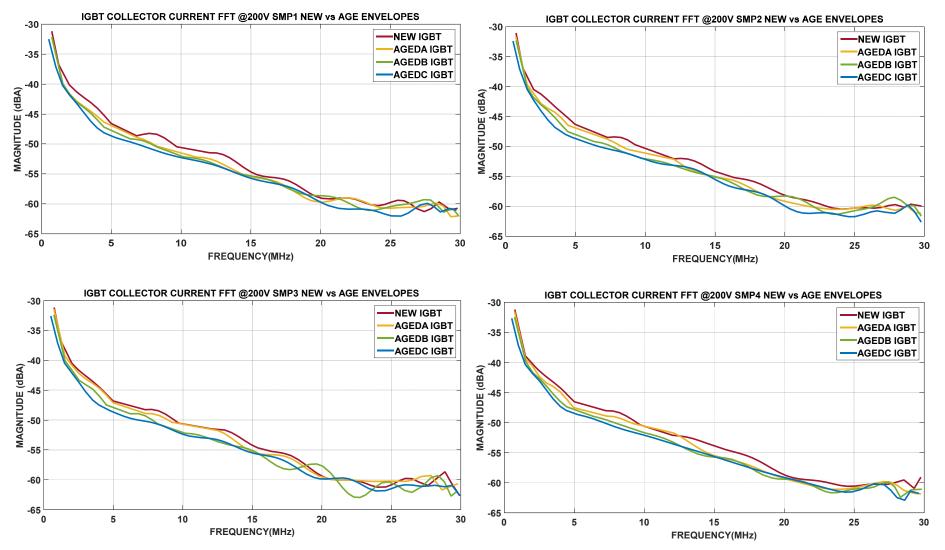

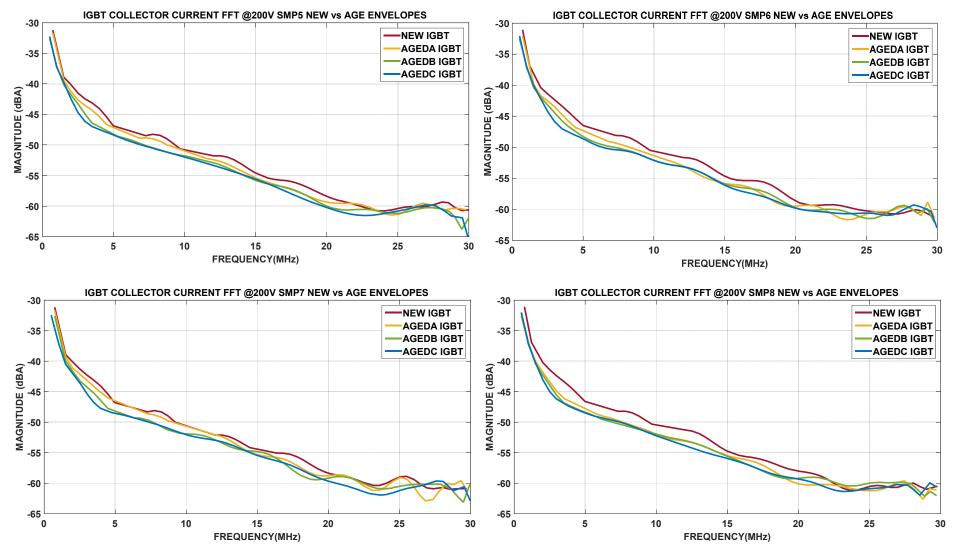

|     | 6.4.2  | Collector Current (I <sub>C</sub> ) Fast Fourier Transform (FFT) Evolution with Ageing |  |

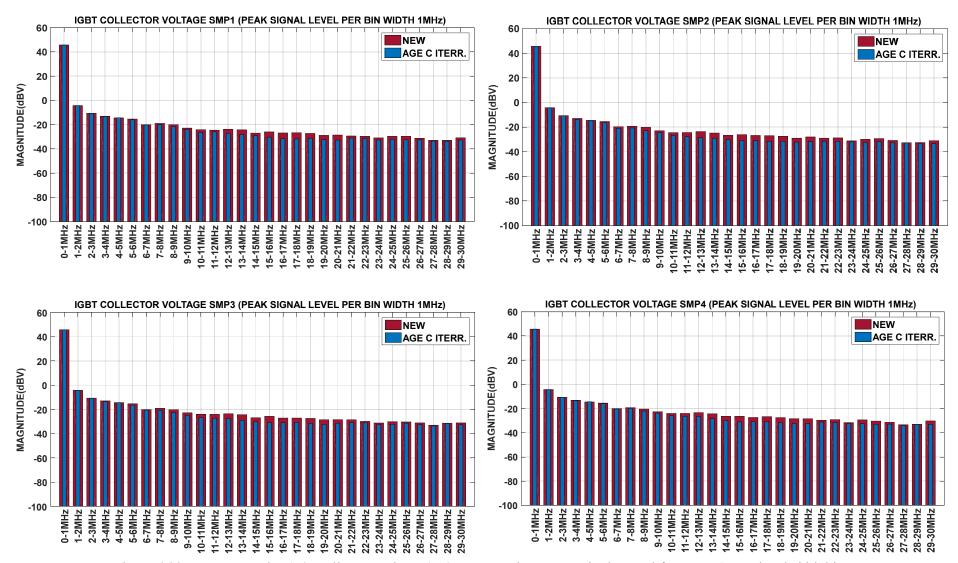

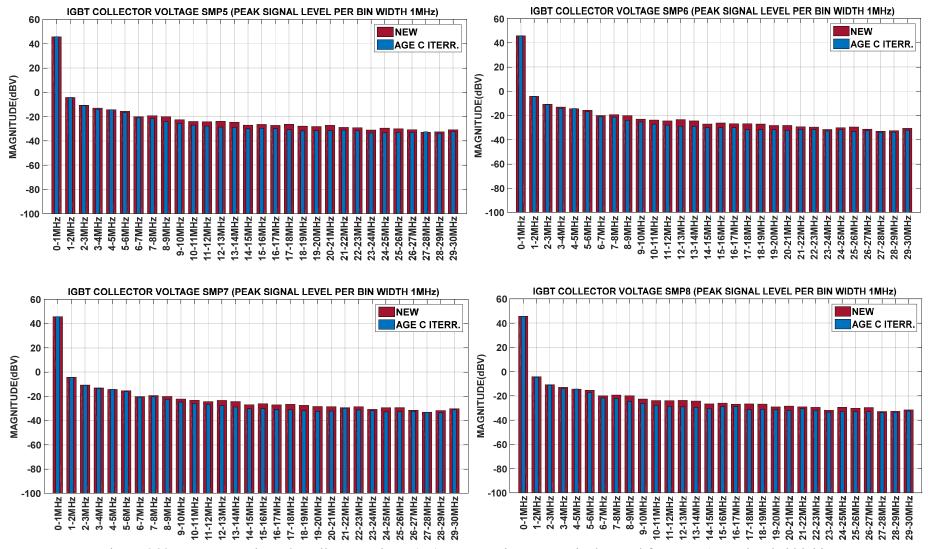

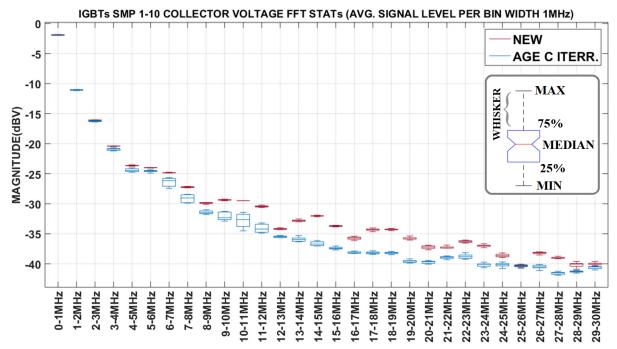

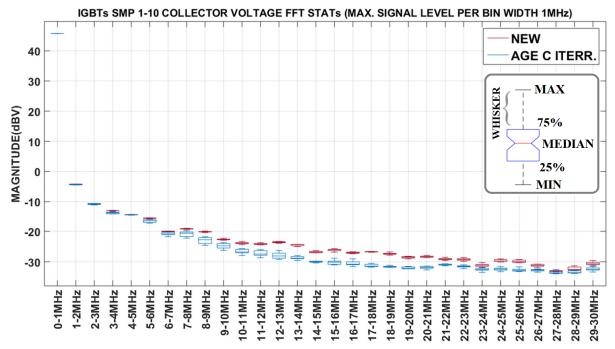

|     | 6.4.1  | IGBTs' Collector Voltage ( $V_C$ ) Frequency Domain Evolution with Ageing              |  |

| 6.  | 4 IGB  | T'S AGEING AND EM CONDUCTED EMISSIONS CHARACTERIZATION RESULTS                         |  |

# List of Tables

| Table 2-1 - IGBT Failure Mode, Effect and Analysis Table 1                                             | 66  |

|--------------------------------------------------------------------------------------------------------|-----|

| Table 2-2 - IGBT Failure Mode, Effect and Analysis Table 2                                             | 67  |

| Table 2-3 - IGBT Failure Mode, Effect and Analysis Table 3                                             | 68  |

| Table 2-4 – IGBT Industrial Reliability Tests & Corresponding Test Conditions                          | 74  |

| Table 3-1 - Proposed DC PCAS Requirements                                                              | 109 |

| Table 3-2 - IGBTs' Age Iteration A Failure Parameters.                                                 | 125 |

| Table 3-3 - IGBTs' Age Iteration B Failure Parameters.                                                 | 125 |

| Table 3-4 - IGBTs' Age Iteration C Failure Parameters.                                                 | 125 |

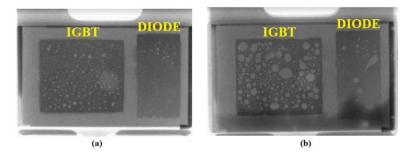

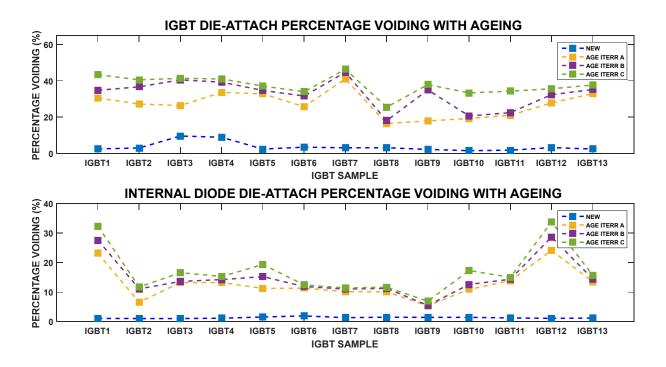

| Table 3-5 – Mean Percentage Voiding and corresponding Standard Deviation for all 13 IGBTs              | 129 |

| Table 3-6 - X-Ray Imagery of IGBT & Internal Diode Die-Attach Degradation with Ageing                  | 130 |

| Table 3-7 - X-Ray Imagery of IGBT & Internal Diode Die-Attach Degradation with Ageing                  | 131 |

| Table 3-8 - X-Ray Imagery of IGBT Die-Attach Threshold Image with Ageing New to Age Iteration C)       | 132 |

| Table 3-9 - X-Ray Imagery of IGBT Die-Attach Threshold Image with Ageing New to Age Iteration C)       | 133 |

| Table 3-10 - X-Ray Diode Die-Attach Threshold Image (IGBT 1-10, New to Age Iteration C)                | 134 |

| Table 3-11 – IGBTs Average Threshold Voltage & Standard Deviation (σ) with Ageing                      | 149 |

| Table 3-12 – IGBTs Average Threshold Voltage & σ, Percentage Variation Compared to New                 | 150 |

| Table 3-13 - IGBTs Average Gate-Emitter Leakage Current & Standard Deviation (σ) with Ageing           | 151 |

| Table 3-14 - IGBTs Average Leakage Current & σ Percentage Variation Compared to New                    | 152 |

| Table 3-15 - IGBTs' Collector-Emitter On-State Voltage (VCE_ON) Ageing Evolution @50°C                 | 154 |

| Table 3-16 - IGBTs' Collector-Emitter On-State Voltage (VCE_ON) Ageing Evolution @100°C                | 154 |

| Table 3-17 - IGBTs' Collector-Emitter On-State Voltage (VCE_ON) Ageing Evolution @150°C                | 154 |

| Table 3-18 - IGBTs Average Collector-Emitter On-State Voltage Case Temperature Coefficient with Ageing | 155 |

| Table 3-19 – IGBTs Average On-State Resistance Evolution with Ageing                                   | 155 |

| Table 3-20 – IGBTs Average On-State Resistance & σ, Percentage Variation Compared to New               | 155 |

| Table 3-21 – IGBTs Average Forward Transconductance Evolution with Ageing                              | 157 |

| Table 3-22 – IGBTs Average Transconductance (gfe) & σ, Percentage Variation Compared to New.           | 158 |

| Table 3-23 - IGBTs Average Internal Diode Forward Voltage Evolution with Ageing                        | 159 |

| Table 3-24 – IGBTs Average Transconductance (gfe) & σ, Percentage Variation Compared to New            | 160 |

| Table 4-1 - IGBT Switching Parameters Characterization System (SPCS) requirements                      | 164 |

| Table 4-2 - IGBTs Turn-Off Parameters Average & Standard Deviation Test @ VDC 200V                     | 179 |

| Table 4-3 - IGBTs Turn-Off Parameters Average & Std. Dev. Percentage Variation @ VDC 200V              | 179 |

| Table 4-4 - IGBTs Turn-Off Parameters Average & Standard Deviation Test @ VDC 480V                     | 181 |

| Table 4-5 - IGBTs Turn-Off Parameters Average & Std. Dev. Percentage Variation @ VDC 480V              | 182 |

| Table 4-6 - IGBTs Turn-On Parameters Average & Standard Deviation Test @ VDC 200V                      | 185 |

| Table 4-7 - IGBTs Turn-On Parameters Average & Std. Dev. Percentage Variation @ VDC 200V               | 186 |

| Table 4-8 - IGBTs Turn-On Parameters Average & Standard Deviation Test @ V <sub>DC</sub> 480V          | 187 |

| Table 4-9 - IGBTs Turn-On Parameters Average & Std. Dev. Percentage Variation @ VDC 480V                          | 188 |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Table 4-10 - IGBTs Reverse Recovery Parameters Average & Standard Deviation Test @ VRR 200V                       | 192 |

| Table 4-11 - Reverse Recovery Parameters Avg. & Std. Dev. Percentage Variation @ VRR 200V                         | 193 |

| Table 4-12 - IGBTs Average Rate of Fall of Current (dI <sub>F</sub> /dt) & σ Evolution with Ageing                | 194 |

| Table 4-13 - IGBTs Average Rate of Fall of Current (dI <sub>F</sub> /dt) & σ, Percentage Variation with Ageing    | 194 |

| Table 4-14 - IGBTs STGP19NC60KD Turn-Off Parameters Average & Std. Dev. Test @ VDC 480V.                          | 196 |

| Table 4-15 - IGBTs STGP19NC60KD Turn-Off Parameters Average & Std. Dev. Perc. Variation @ V <sub>DC</sub> 480V    | 196 |

| Table 4-16 - IGBTs IRG4BC30KD vs STGP19NC60KD Turn-Off Parameters Evol. with Ageing @ VDC 480V                    | 197 |

| Table 4-17 - IGBTs STGP19NC60KD Turn-On Average & Standard Deviation Test @ VDC 480V                              | 198 |

| Table 4-18 - IGBTs STGP19NC60KD Turn-On Average & Standard. Deviation Perc. Variation @ VDC 480V                  | 198 |

| Table 4-19 - IGBTs IRG4BC30KD vs STGP19NC60KD Turn-On Evolution with Ageing @ VDC 480V.                           | 198 |

| Table 4-20 - IGBTs STGP19NC60KD Reverse Recovery Parameters @ V <sub>RR</sub> 200V.                               | 200 |

| Table 4-21 - IGBTs STGP19NC60KD Reverse Recovery Parameters @ V <sub>RR</sub> 200V.                               | 200 |

| Table 4-22 - IGBTs IRG4BC30KD vs STGP19NC60KD Recovery Parameters Evol. with Ageing @ VRR 200V                    | 200 |

| Table 5-1 – IGBT Turn-On Transient Linear Model Equations Summary                                                 | 228 |

| Table 5-2 - IGBT Turn-On Transient Linear Model Equations Summary                                                 | 229 |

| Table 5-3 - IGBT Piecewise Linear Model Parameters (Measured values for IGBT Sample 14 NEW)                       | 231 |

| Table 5-4 - Measured Time Parameters for IGBT Sample 14 (vNEW) Turn-On and Turn-Off Transients                    | 233 |

| Table 5-5 - Collector Current Rate of Change (dIc/dt) for IGBT Sample 14 Measured vs Model                        | 233 |

| Table 5-6 - Collector-Emitter Voltage Rate of Change (dVCE/dt) for IGBT Sample 14 Measured vs Model               | 233 |

| Table 5-7 – Reverse Recovery Parameters for IGBT Sample 14 Measured vs Model                                      | 234 |

| Table 5-8 - Reverse Recovery Current Modelling Dependence on the Forward Current                                  | 236 |

| Table 5-9 - Summary of Reverse Recovery Collector Current (I <sub>C</sub> ) general non-linear function modelling | 240 |

| Table 5-10 - Summary of the Non-Linear Turn-On VCE and IC Transient Model Equations.                              | 252 |

| Table 5-11 - Summary of the Non-Linear Turn-Off V <sub>CE</sub> and I <sub>C</sub> Transient Model Equations      | 253 |

| Table 5-12 – IGBT Turn-On and Turn-Off Transient Model Parameters                                                 | 254 |

| Table 5-13 - IRG4BC30KD IGBT Turn-Off Phase 1 Collector-Emitter Voltage and Collector Current with Age            | 266 |

| Table 5-14 – Measured and Modelled IGBT Sample 14 dV <sub>CE</sub> /dt Phase 2 Evolution with Ageing              | 267 |

| Table 5-15 - IRG4BC30KD IGBT Sample 14 Measured and Linear Piecewise Model Parameters with Ageing                 | 268 |

| Table 5-16 - Measured Phase 3 IGBT Intrinsic MOSFET controlled dIc/dt Evolution with Ageing                       | 281 |

| Table 5-17 - STGP19N60KD IGBT Sample 1 Threshold Voltage and Transconductance evolution with ageing,              | 282 |

| Table 5-18 - IGBT Sample 14 Turn-Off Phase 3 and Phase 4 collector current non-linear transient with ageing       | 287 |

| Table 5-19 - IGBT IRG4BC30KD Smp 14 Turn-Off Switching Energy Loss, Measured and Non-Linear Model                 | 292 |

| Table 5-20 - IGBT Collector Current Rate of Change turn-on Phase 2, Measured vs Linear Piecewise Model            | 295 |

| Table 5-21 - IGBT Collector-Emitter Voltage Rate of Change turn-on Phase 4, Measured vs Linear Model              | 299 |

| Table 6-1 - RG58 Cable and Panoma 4108-20 20dB attenuator characterization.                                       | 320 |

# List of Figures

| Figure 1.1 - Classification of Power Semiconductor Devices                                                              | . 10 |

|-------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2 - Thyristor's Layout Structure and Equivalent Circuit (a) layout structure (b) equivalent circuit (c) symbol | . 11 |

| Figure 1.3 – Thyristor's Volt-Ampere Characteristics [1]                                                                | . 13 |

| Figure 1.4 - Vertical Power BJT Structure [10]                                                                          | . 15 |

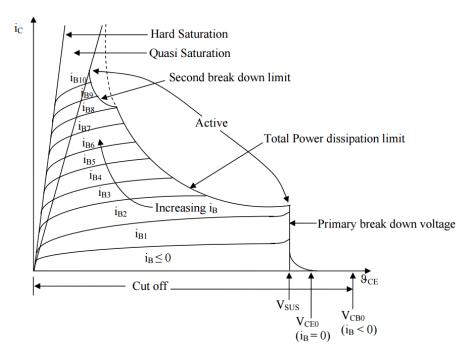

| Figure 1.5 - Output V-I Characteristics of a Power BJT [11]                                                             | . 16 |

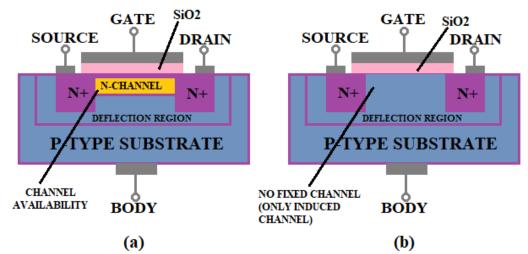

| Figure 1.6 - N-Channel (a) depletion MOSFET (b) enhancement MOSFET                                                      | . 19 |

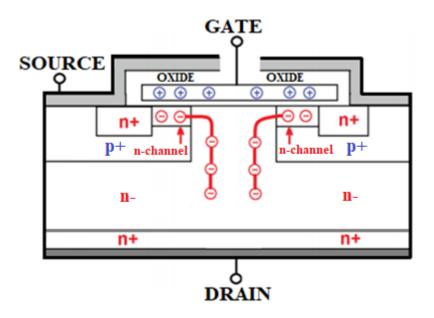

| Figure 1.7 - VDMOS Cell Structure                                                                                       | . 20 |

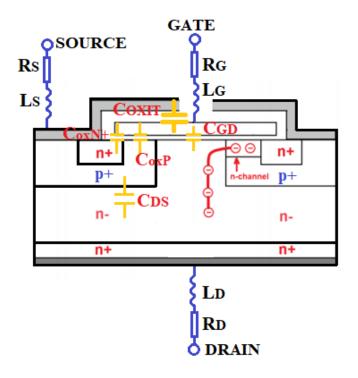

| Figure 1.8 – Power MOSFET Parasitic Inductances and Capacitances [2].                                                   | . 23 |

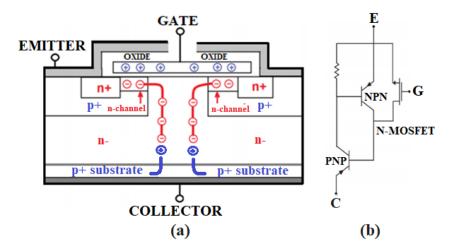

| Figure 1.9 - IGBT (a) Cell Structure (b) Equivalent Circuit [1]                                                         | . 25 |

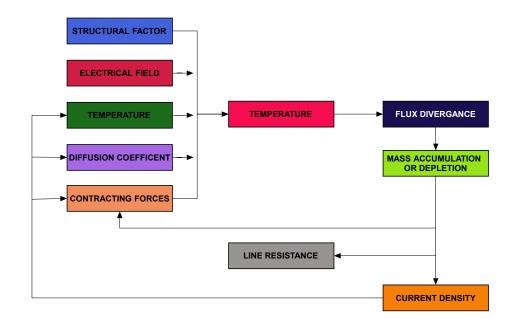

| Figure 2.1 - Electromigration Failure Mechanisms [24]                                                                   | . 30 |

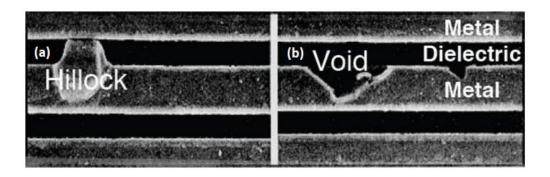

| Figure 2.2 – Microscope imagery demonstrating the development of Hillock, Void through electromigration [28]            | . 30 |

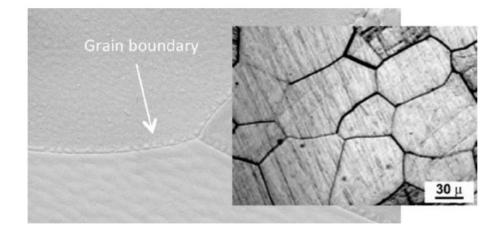

| Figure 2.3 – Grains and corresponding Grain Boundaries of a metal surface [32]                                          | . 31 |

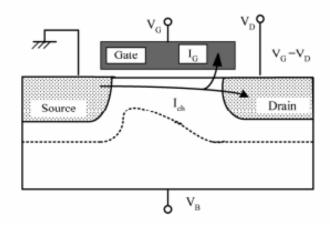

| Figure 2.4 - N-MOSFET CHE Injection manifesting @ $V_G \approx V_D$ [40]                                                | . 34 |

| Figure 2.5 – I <sub>G</sub> vs V <sub>G</sub> characteristics manifesting CHE Injection [40]                            | . 35 |

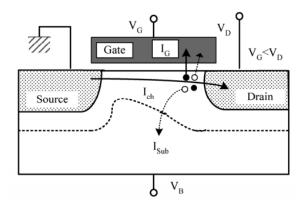

| Figure 2.6 – Drain Avalanche Hot Carrier Injection [40]                                                                 | . 36 |

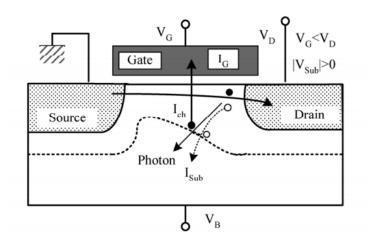

| Figure 2.7 - Secondary Generated Hot Electron (SGHE) Injection [40]                                                     | . 36 |

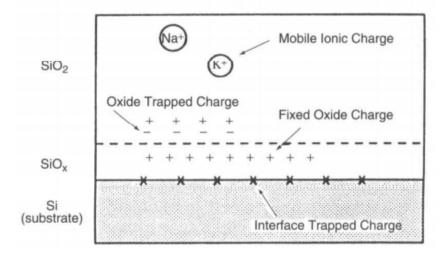

| Figure 2.8 - Charges within SiO2 and Si-SiO2 interface [40]                                                             | . 38 |

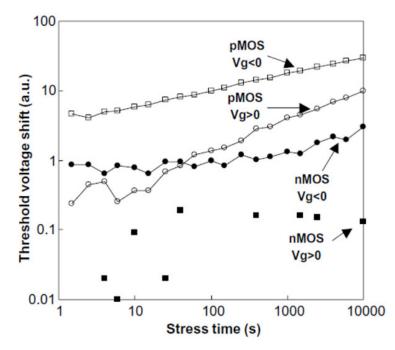

| Figure 2.9 - Effects of NBTI for p- and n-channel MOS structures [53]                                                   | . 42 |

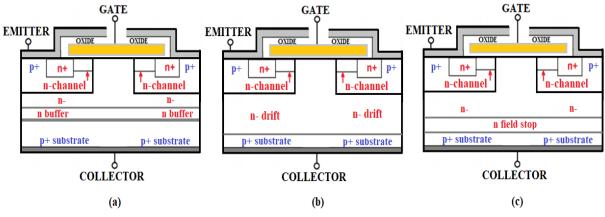

| Figure 2.10 - IGBT Cell Structure (a) PT IGBT (b) NPT IGBT (c) Field Stop [61]                                          | . 44 |

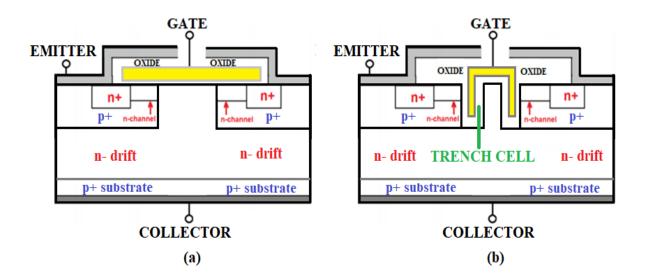

| Figure 2.11 - IGBT Cells Categorized by Gate Structure (a) Planar (b) Trench                                            | . 44 |

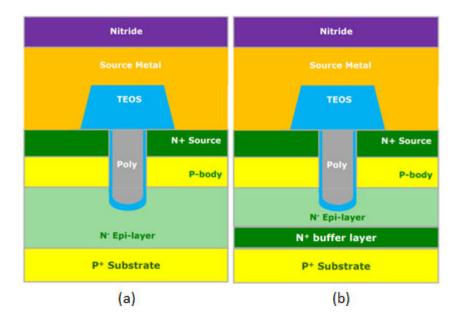

| Figure 2.12 - (a) NPT IGBT Cell Structure (b) PT IGBT Cell Structure [65]                                               | . 46 |

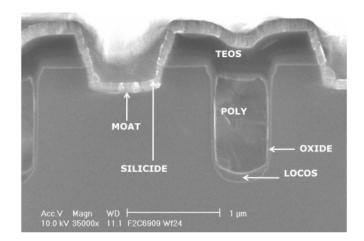

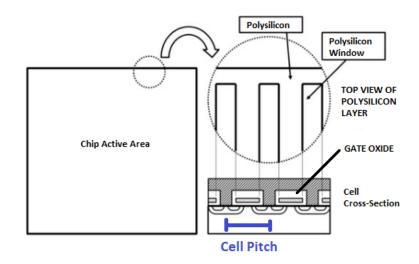

| Figure 2.13 – Scanning Electron Microscope Imagery of Trench-Gate Technology [64]                                       | . 47 |

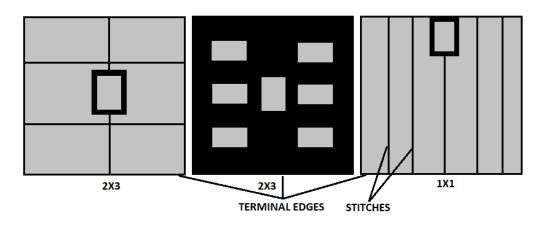

| Figure 2.14 – IGBT Die Active Area [5]                                                                                  | . 48 |

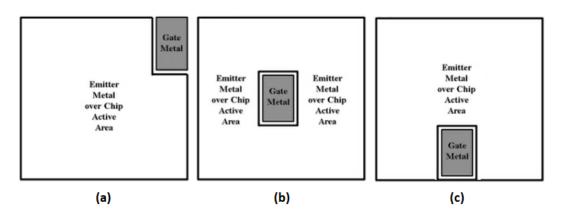

| Figure 2.15 – Gate Metallization Configurations (a) Corner (b) Centre (c) Edge [5]                                      | . 48 |

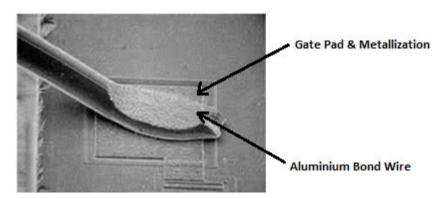

| Figure 2.16 - Gate Pad & Metallization and corresponding Al Bond Wire [5]                                               | . 49 |

| Figure 2.17 - Emitter metallization matrix designs [65]                                                                 | . 50 |

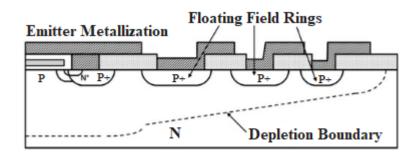

| Figure 2.18 – Side View of Planar Gate IGBT Edge Termination Design [5]                                                 | . 50 |

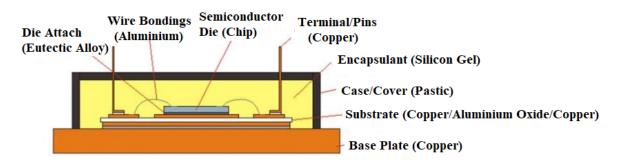

| Figure 2.19 - Generic IGBT Package Structure [68]                                                                       | . 52 |

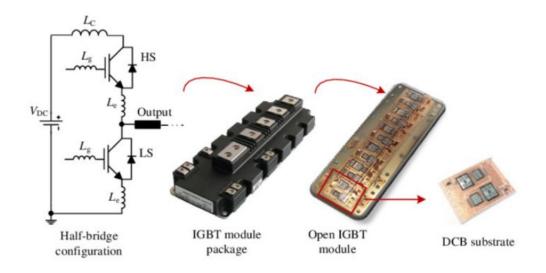

| Figure 2.20 – 1.7kV/1kA Half-Bridge IGBT Module and corresponding DCB [72]                                              | . 53 |

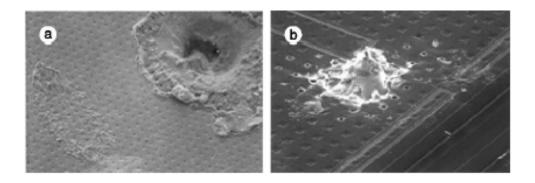

| Figure 2.21 - Scanning Electron Microscope (SEM) Imagery of IGBT Melted Pit [73]                                        | . 57 |

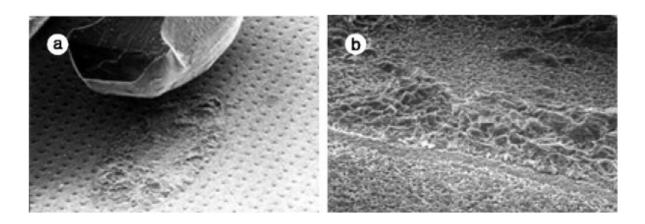

| Figure 2.22 – Scanning Electron Microscope (SEM) Imagery of (Al Bond-Wire Lift-Off [73]                                 | . 58 |

| Figure 2.23 - Scanning Electron Microscope (SEM) Imagery of Bond Wire Heel Cracks [73]                                  | . 58 |

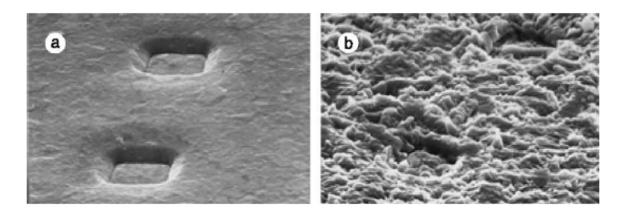

| Figure 2.24 - X-Ray Imagery evidencing IGBT dies and corresponding free-wheeling diode die-attach voiding [[73]         | . 61 |

| Figure 2.25 - Scanning Electron Microscope (SEM) Imagery of Emitter Metallization of IGBT [73]                          | . 62 |

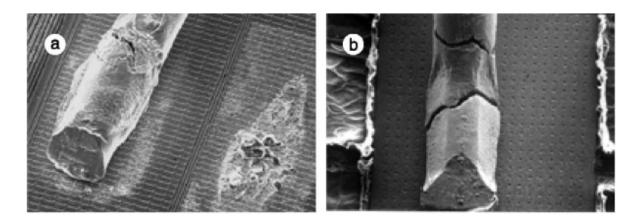

| Figure 2.26 - Scanning Electron Microscope (SEM) Imagery of Ruptured Emitter Bond [73].                                 | . 62 |

| Figure 2.27 - Scanning Electron Microscope (SEM) Imagery of Al <sub>2</sub> O <sub>3</sub> ceramic layer [73]           | . 63 |

|                                                                                                                         |      |

| igure 2.29 – IGBT Failure Mechanisms and Corresponding Locations                                                           |

|----------------------------------------------------------------------------------------------------------------------------|

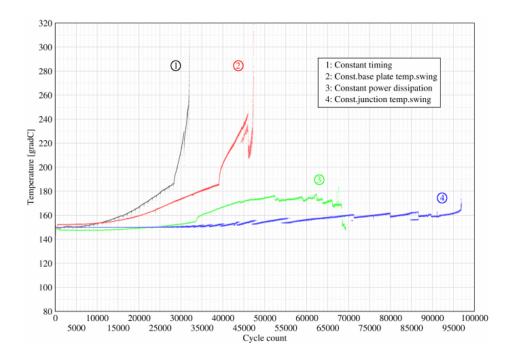

| igure 2.31 – Comparison of different DC PCAS procedures T <sub>J</sub> vs Age Cycles [125]                                 |

| igure 2.32 - Method 1 Accelerated Ageing Procedure highlighting the onset of thermal runaway [135]                         |

| igure 2.32 - Method 1 Accelerated Ageing Procedure highlighting the onset of thermal runaway [135]                         |

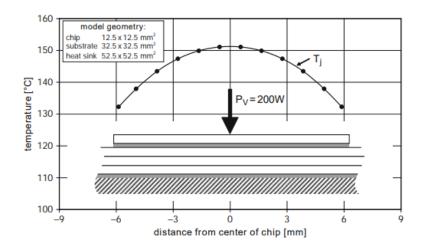

| igure 2.34 – Thermal Simulation of Silicon Die and Corresponding Layers [13]                                               |

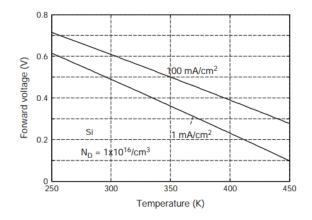

| igure 2.35 – PN-Junction Forward Voltage (V <sub>F</sub> ) Dependence on Temperature at Constant Current Density [13]      |

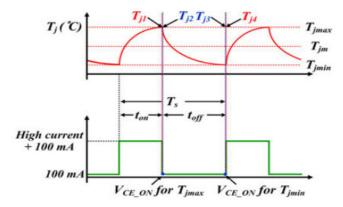

| igure 2.36 – $V_{CE\_SAT}$ measurement sequence during power cycling [92]                                                  |

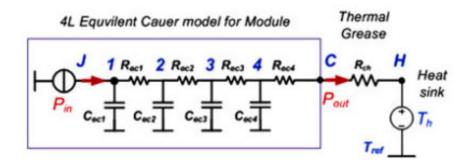

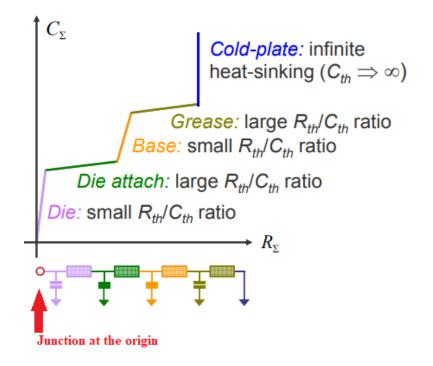

| igure 2.37 – IGBT module Equivalent 4L Cauer Thermal Network describing Thermal Flow [160]                                 |

| igure 2.38 – Caeur Thermal Impedance Model Structure Function [159]                                                        |

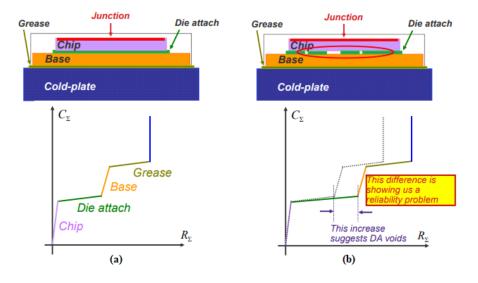

| igure 2.39 – Thermal Impedance Structure Function (a) Healthy (b) Degraded Die-Attach [159]                                |

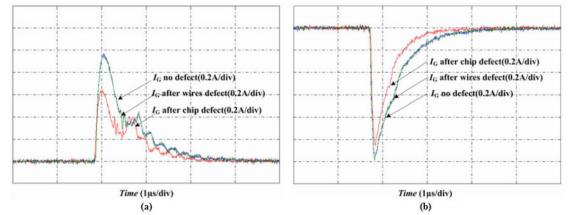

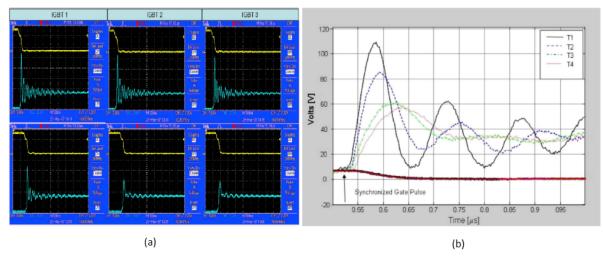

| igure 2.40 - IGBT Gate Current Waveforms due to different degradation (a) Turn-On (b) Turn-Off                             |

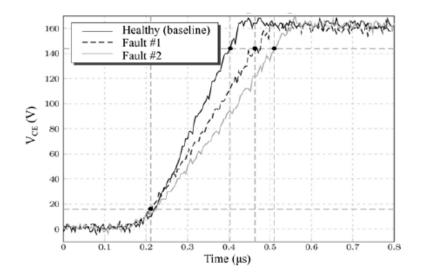

| igure 2.41 – Collector-Emitter Voltage (V <sub>CE</sub> ) waveforms during Turn-Off [161]                                  |

| igure 2.42 - Ringing of (top) New and (bottom) Aged IGBTs [133]                                                            |

| igure 2.43 – IGBT's Ringing Frequencies Components in relation to ageing progress (top to bottom)                          |

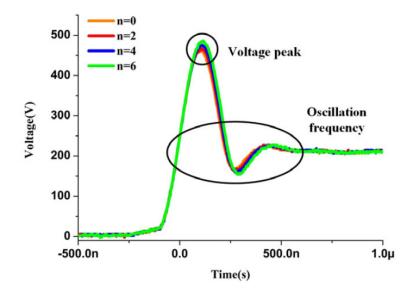

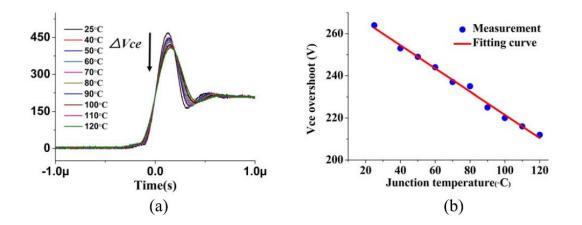

| igure 2.44 – IGBT Module $V_{CE}$ ringing overshoot vs n (number of broken bond wires) [169]                               |

| igure 2.45 – IGBT Module V <sub>CE</sub> ringing overshoot vs T <sub>J</sub> (a) Waveform (b) Fitted Curve [169]           |

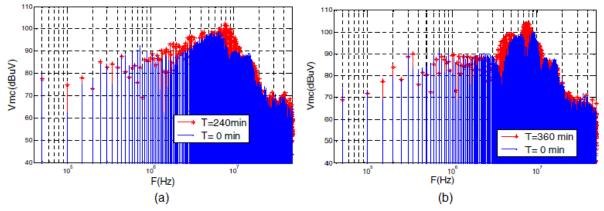

| igure 2.46 – IGBT Conducted Emissions, Ageing Time (a) 240 minutes (b) 360 minutes [167]                                   |

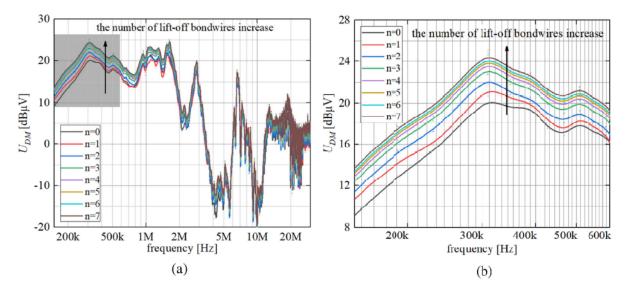

| igure 2.47 – Relationship between the number (n) of lifted-off bond-wires and Conducted EMI [168]                          |

| igure 2.48 – Relationship between Conducted EMI and Junction Temperature (TJ) [168]                                        |

|                                                                                                                            |

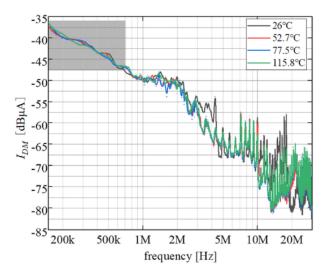

| igure 2.49 – (a) Collector Current (b) Collector-Emitter Voltage Evolution with Ageing [179]                               |

|                                                                                                                            |

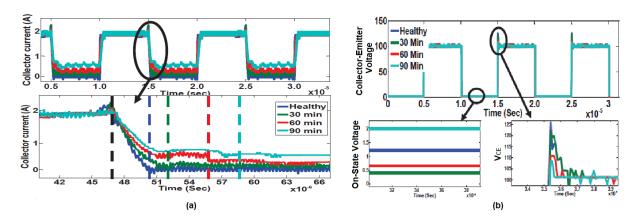

| igure 2.50 – (a) EMR power spectrum evolution with ageing (b) EMR Detection Setup [179]                                    |

| igure 2.51 – Experimental Setup utilizing a linear array of near-field magnetic probes [180]                               |

| igure 2.52 - Diagram depicting IGBT Module including sensor integration and redundant emitter bond wires [181] 98          |

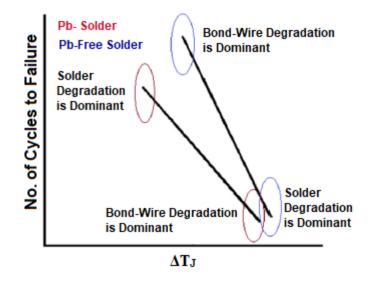

| igure 2.53 - Relationship Thermal cycles and (Pb) Solder and (Pb)-Free Solder IGBTs [202] 104                              |

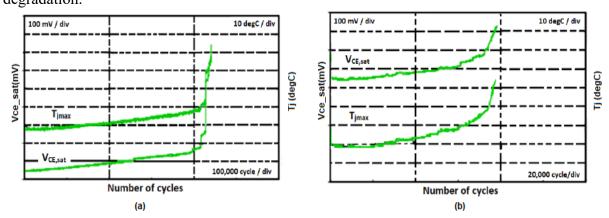

| igure 2.54 - V <sub>CE_SAT</sub> & T <sub>J</sub> relationships with cycles (a) Bond Wire (b) Solder Degradation [202] 104 |

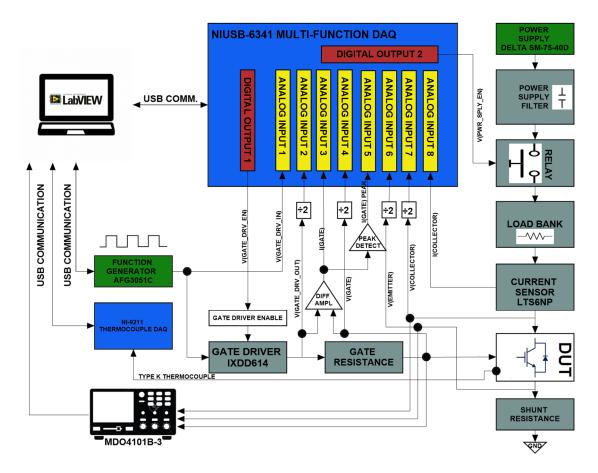

| igure 3.1 - Overview of the Accelerated Ageing & Characterization System                                                   |

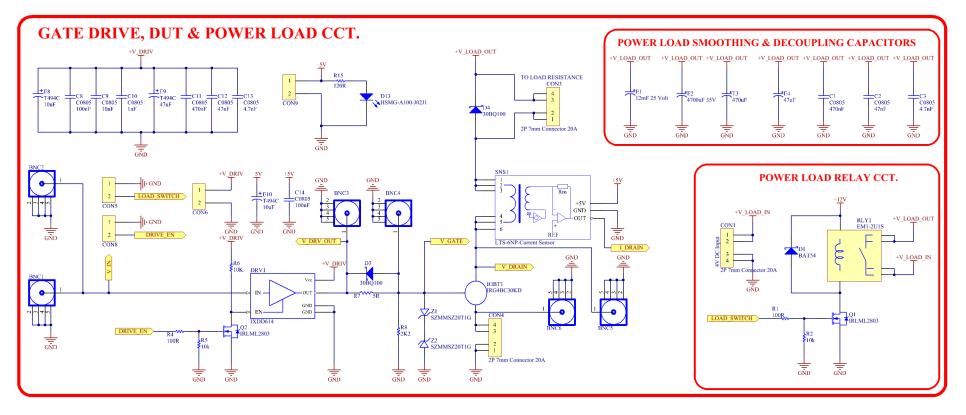

| igure 3.2 - IGBT DC PCAS Custom-Built Hardware, Control and Power Circuit Section                                          |

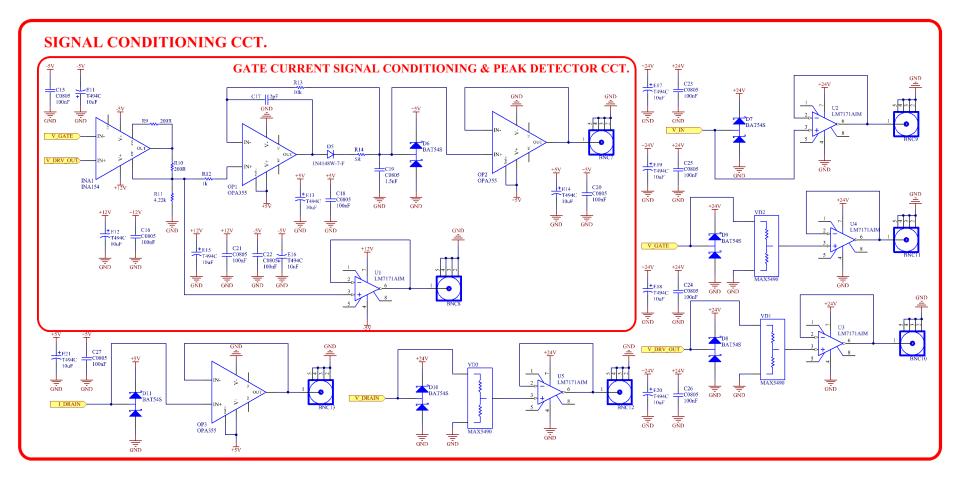

| igure 3.3 - IGBT DC PCAS Custom-Built Hardware Signal Conditioning Circuit 114                                             |

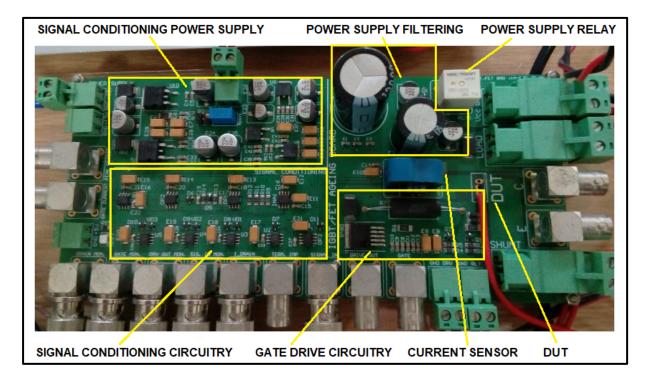

| igure 3.4 - IGBT DC PCAS Custom-Built Hardware PCB 115                                                                     |

| igure 3.5 - Developed IGBT DC PCAS Software GUI 118                                                                        |

| igure 3.6 – Developed IGBT DC PCAS Software Flowchart 119                                                                  |

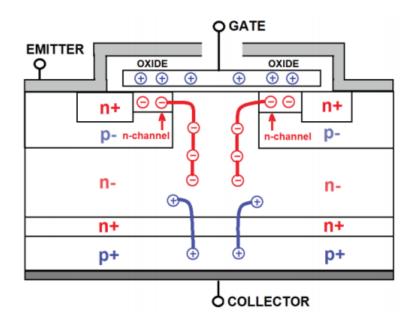

| igure 3.7 – Utilized PT IGBTs' Cell Structure                                                                              |

| igure 3.8 – X-Ray Image of New IGBT including drilled hole shade 122                                                       |

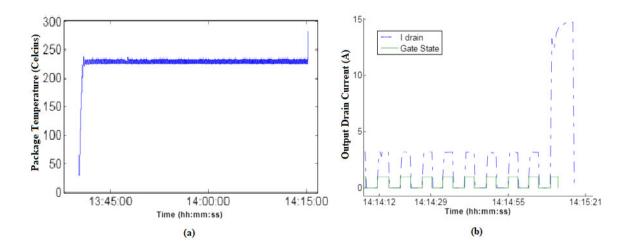

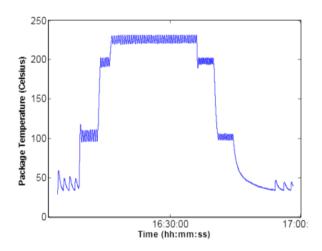

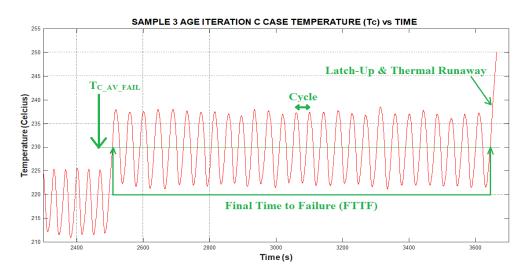

| igure 3.9 – IGBT Case Temperature (Tc) Plot, highlighting relevant failing parameters                                      |

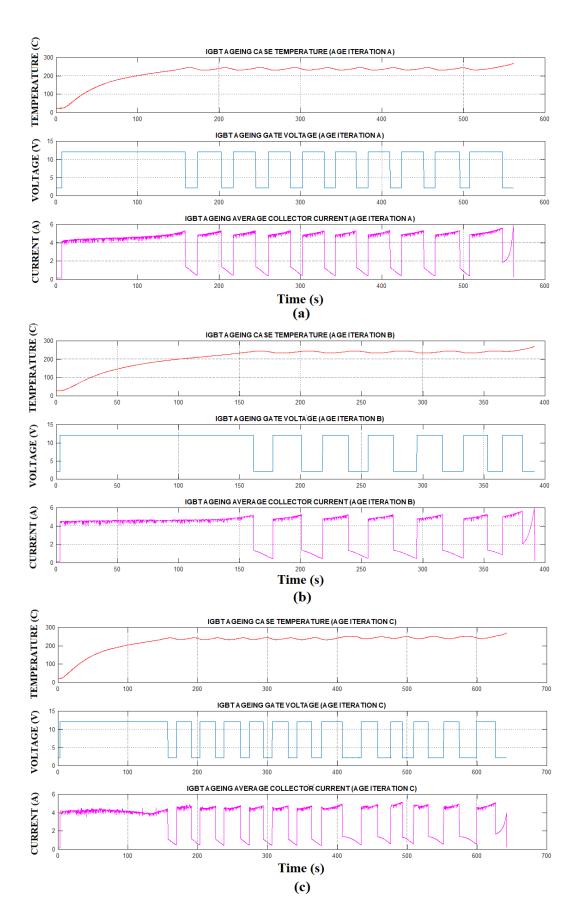

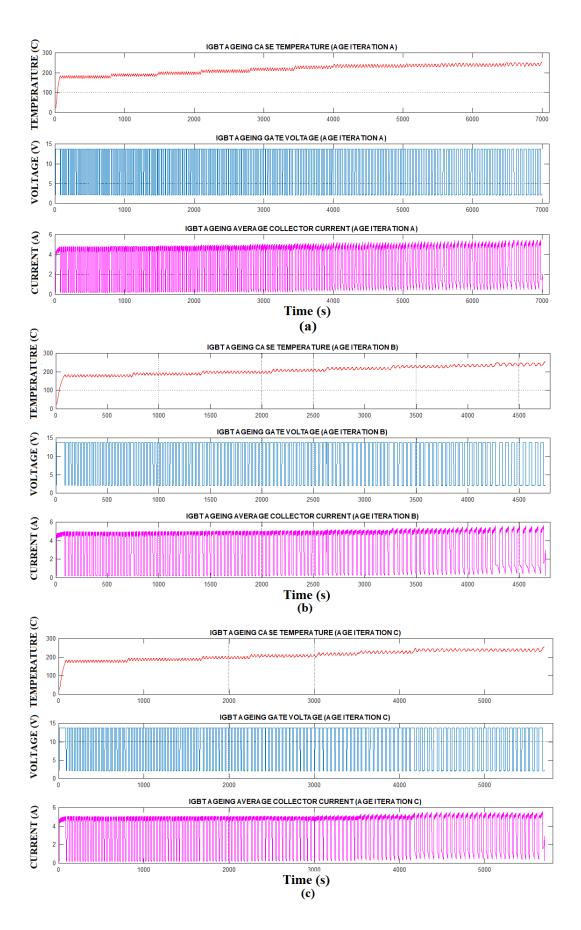

| igure 3.10 - IGBT Sample 9 DC PCAS Case Temperature (Tc), Gate Voltage (VG) & Collector Current (Ic) 126                   |

| igure 3.11 - IGBT Sample 8 DC PCAS Case Temperature (Tc), Gate Voltage (VG) & Collector Current (Ic) 127                   |

| igure 3.12 - X-Ray Image of the IGBT & Internal Diode Die-Attaches (a) New (b) Aged 128                                    |

| Figure 3.13 - IGBT & Internal Diode Die-Attaches' Voiding Evolution with Ageing                                          |     |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.14 – IGBT (a) Threshold Voltage (V <sub>THRES</sub> ) (b) Leakage Current, Characterization Setup               |     |

| Figure 3.15 - IGBT Threshold Voltage and Leakage Current Measurement Software GUI                                        |     |

| Figure 3.16 - IGBT Threshold Voltage and Leakage Current Measurement Software Flowchart                                  |     |

| Figure 3.17 – IGBT Collector-Emitter On-State Voltage (V <sub>CE_ON</sub> ) characterization setup.                      |     |

| Figure 3.18 – IGBT ON-State Voltage and ON-State Resistance Measurement Software Flowchart                               |     |

| Figure 3.19 - IGBT Output Characteristics Measurement Software Flowchart                                                 |     |

| Figure 3.20 - IGBT Collector-Emitter On-State Voltage (V <sub>CE_ON</sub> ) Measurement Software GUI                     |     |

| Figure 3.21 - IGBT Output Characteristics characterization setup                                                         |     |

| Figure 3.22 - Transfer Characteristics and Forward Transconductance (gfe) characterization setup                         |     |

| Figure 3.23 – Transfer Characteristics and Forward Transconductance (gfe) Software GUI                                   |     |

| Figure 3.24 - Transfer Characteristics and Forward Transconductance (gfe) Software Flowchart                             |     |

| Figure 3.25 – Internal IGBT Diode's Forward Voltage (VFD) characterization setup.                                        |     |

| Figure 3.26 - Internal IGBT Diode's Forward Voltage (VFD) software flowchart                                             |     |

| Figure 3.27 – IGBT Sample 1 Threshold Voltage Gate-Emitter Voltage (VGE) vs Collector Current (IC)                       |     |

| Figure 3.28 - IGBTs Gate-Emitter Threshold Voltage (V <sub>GE_TH</sub> ) Evolution with Accelerated Ageing               | 150 |

| Figure 3.29 - IGBTs Gate-Emitter Leakage Current (IGES) Evolution with Accelerated Ageing                                | 151 |

| Figure 3.30 – IGBT Sample 3 Collector-Emitter On-State Voltage (VCE) vs Case Temperature (TC)                            | 153 |

| Figure 3.31 - IGBTs On-State Resistance Evolution with Accelerated Ageing                                                |     |

| Figure 3.32 - IGBT Sample 10 Output Characteristics Evolution with Accelerated Ageing                                    | 156 |

| Figure 3.33 - IGBT Sample 11 Transfer Characteristics Evolution with Accelerated Ageing                                  |     |

| Figure 3.34 - IGBTs Forward Transconductance (gfe) Evolution with Accelerated Ageing                                     | 158 |

| Figure 3.35 - IGBT Sample 3 Internal Diode Forward Characteristics Evolution with Accelerated Ageing                     | 159 |

| Figure 3.36 - IGBTs' Internal Diode Forward Voltage (VFM) Evolution with Accelerated Ageing                              |     |

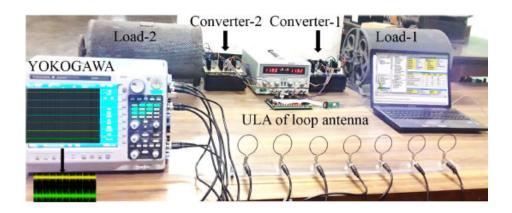

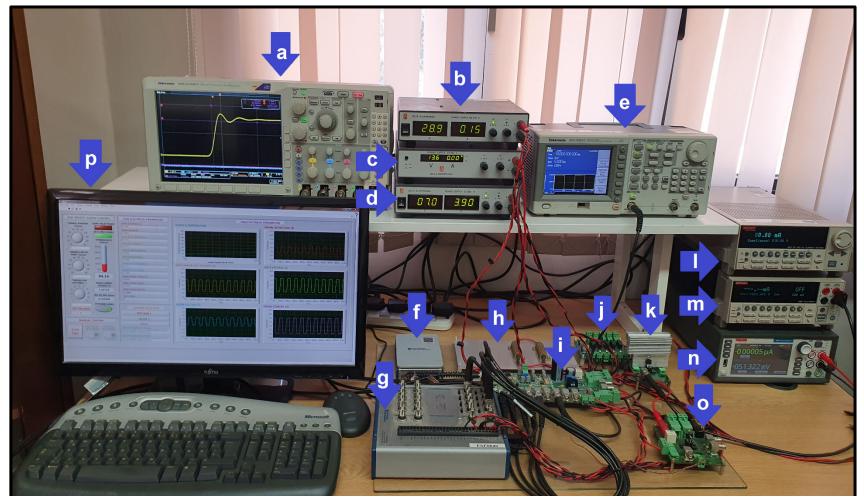

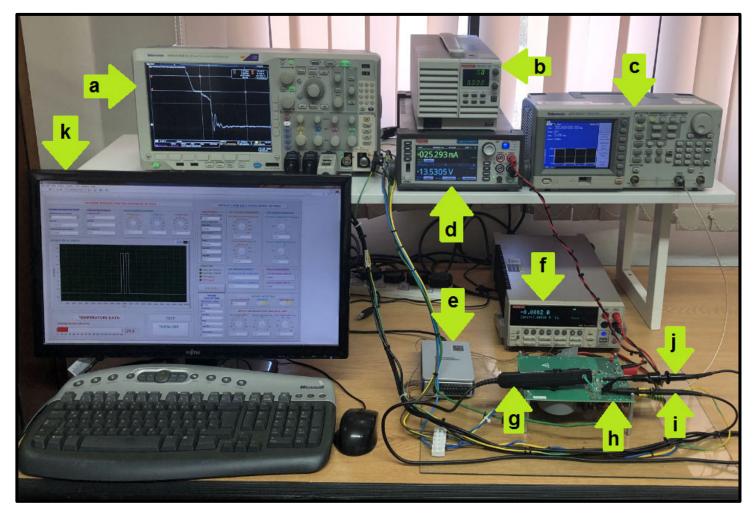

| Figure 3.37 – IGBT DC PCAS & Characterization System                                                                     |     |

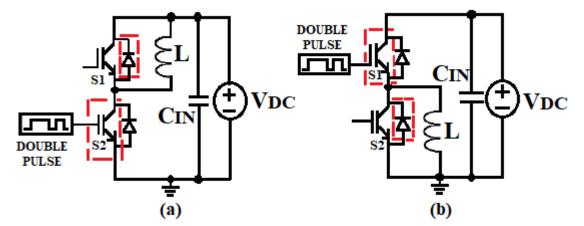

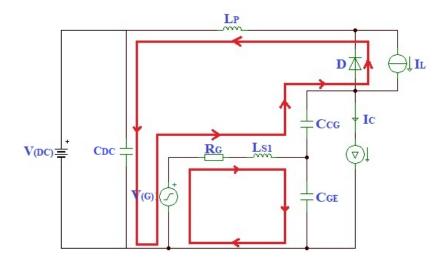

| Figure 4.1 - Double Pulse Test Circuit in Half-Bridge Configuration                                                      |     |

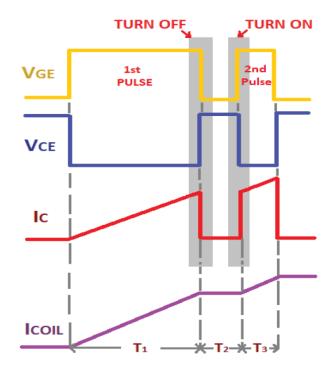

| Figure 4.2 – Double Pulse Technique Test Waveforms                                                                       |     |

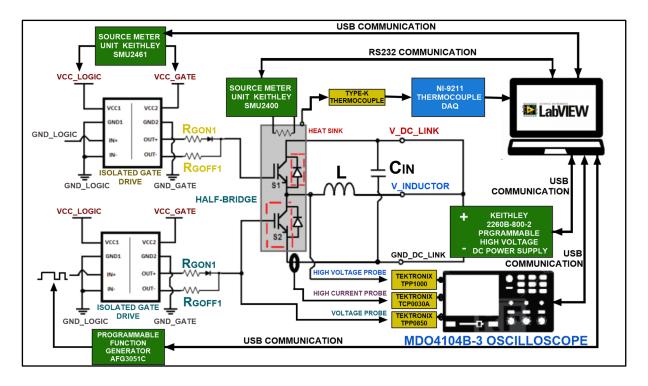

| Figure 4.3 – Switching Parameters Characterization System Architecture                                                   |     |

| Figure 4.4 - SPCS Custom Hardware Gate Drive Circuit [210]                                                               |     |

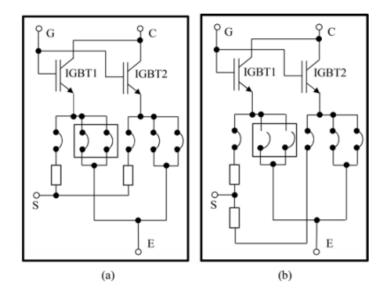

| Figure 4.5 - SPCS Custom Hardware Half-Bridge Power Circuit [210].                                                       |     |

| Figure 4.6 – SPCS Custom Hardware Mounted PCB                                                                            | 173 |

| Figure 4.7 - SPCS Double-Pulse Test Custom Built Software GUI                                                            |     |

| Figure 4.8 - SPCS Double-Pulse Test Custom Built Software Flowchart                                                      |     |

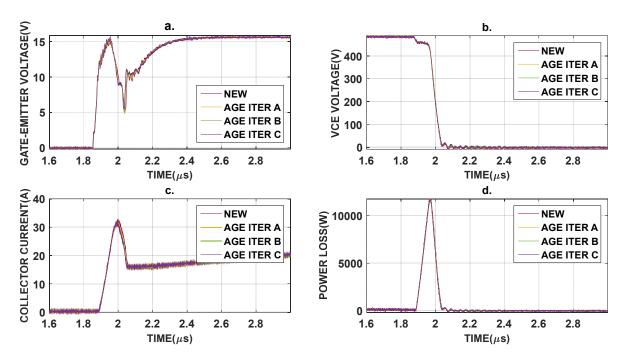

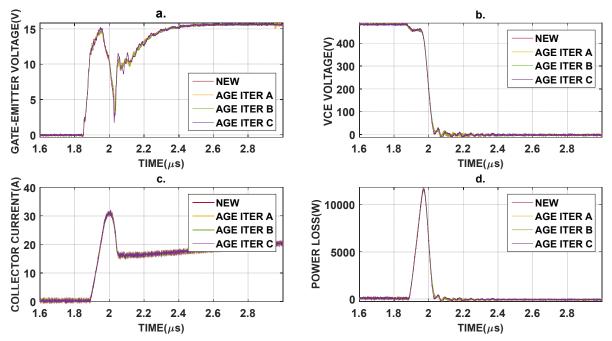

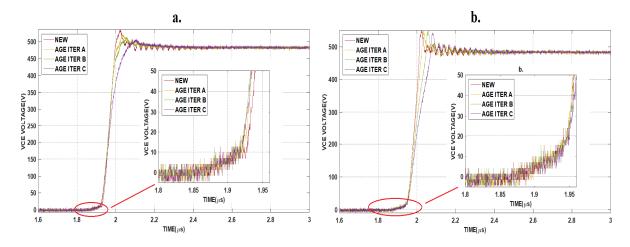

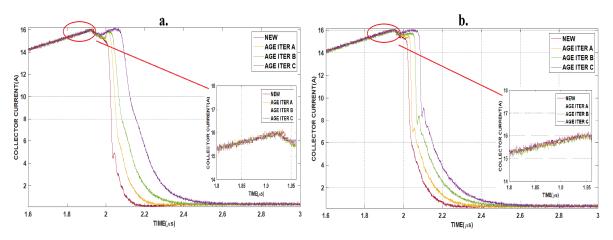

| Figure 4.9 - Turn-Off Transients Comparison NEW vs AGED (3 Age Iterations) IGBT Sample 14                                |     |

| Figure 4.10 – IGBTs' Turn-Off Delay Time with Ageing, at $V_{\rm DC} 200V$                                               |     |

| Figure 4.11 – IGBTs' Fall Time with Ageing, test at V <sub>DC</sub> 200V                                                 |     |

| Figure 4.12 – IGBTs' Turn-Off Switching Loss with Ageing, test at $V_{DC} 200V$ .                                        |     |

| $Figure \ 4.13 - Turn - Off \ Collector - Emitter \ Voltage \ Rate \ of \ Change \ (dV_{CE}/dt) \ at \ V_{DC} \ 200V. \$ |     |

| Figure 4.14 – IGBTs' Turn-Off Delay Time with Ageing, at V <sub>DC</sub> 480V                                            |     |

| Figure 4.15 – IGBTs' Fall Time with Ageing, test at VDC 480V                                                                    | . 182 |

|---------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 4.16 – IGBTs' Turn-Off Switching Loss with Ageing, test at $V_{DC}$ 480V.                                                | . 183 |

| Figure 4.17 – Turn-Off Collector-Emitter Voltage Rate of Change (dV <sub>CE</sub> /dt <sub>OFF</sub> ) at V <sub>DC</sub> 480V. | . 183 |

| Figure 4.18 - Turn-On Transients Comparison NEW vs AGED (3 Age Iterations) IGBT14                                               | . 184 |

| Figure 4.19 – IGBTs' Turn-On Delay Time with Ageing, at $V_{DC}$ 200V.                                                          | . 185 |

| Figure 4.20 – IGBTs' Rise-Time with Ageing, at $V_{DC} 200V$ .                                                                  | . 186 |

| Figure 4.21 – IGBTs' Turn-On Switching Loss with Ageing, test at $V_{DC}$ 200V.                                                 | . 186 |

| Figure 4.22 – IGBTs' Turn-On Collector Current Rate of Change (dIc/dton) at VDC 200V                                            | . 187 |

| Figure 4.23 – IGBTs' Turn-On Delay Time with Ageing, at $V_{DC}$ 480V.                                                          | . 188 |

| Figure 4.24 – IGBTs' Rise-Time with Ageing, at $V_{DC}$ 480V.                                                                   | . 188 |

| Figure 4.25 - IGBTs' Turn-On Switching Loss with Ageing, test at V <sub>DC</sub> 480V.                                          | . 189 |

| Figure 4.26 - IGBTs' Turn-On Collector Current Rate of Change (dIc/dton) at VDC 480V.                                           | . 189 |

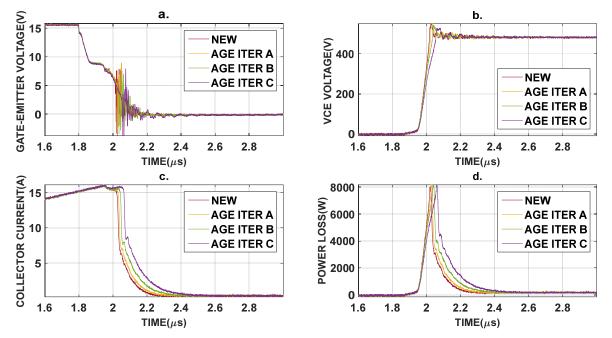

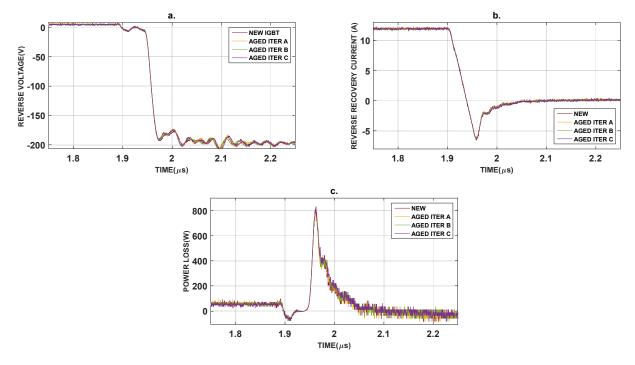

| Figure 4.27 – Reverse Recovery Transients Comparison NEW vs AGED (3 Age Iterations) IGBT Sample 12                              | . 190 |

| Figure 4.28 - Reverse Recovery Current Transient Comparison NEW vs AGED (3 Age Iterations) IGBT Sample 11                       | . 191 |

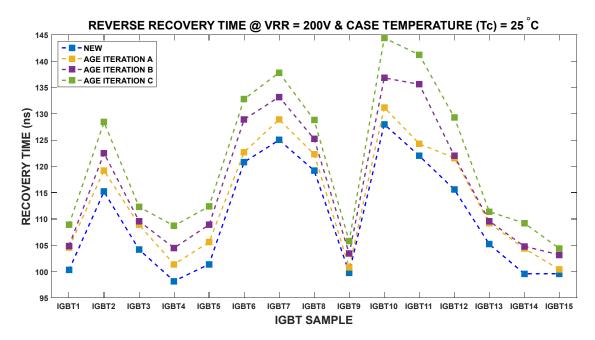

| Figure 4.29 - IGBTs' Internal Diode Reverse Recovery Time (t <sub>RR</sub> ) evolution with Ageing                              | . 191 |

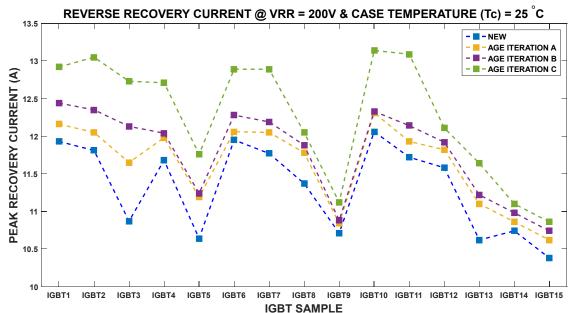

| Figure 4.30 - IGBTs' Internal Diode Peak Reverse Recovery Current (IPRR) evolution with Ageing                                  | . 192 |

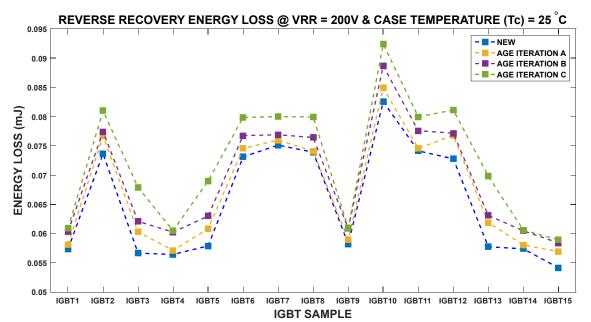

| Figure 4.31 - IGBTs' Internal Diode Energy Loss during Reverse Recovery (E <sub>RR</sub> ) with Ageing                          | . 193 |

| Figure 4.32 - Turn-Off Transients Comparison NEW vs AGED (3 Age Iterations) IGBT STGP19NC60KD Sample 1.                         | . 195 |

| Figure 4.33 - Turn-On Transients Comparison NEW vs AGED (3 Age Iterations) IGBT STGP19NC60KD Sample 1                           | . 197 |

| Figure 4.34 - Reverse Recovery Transients Comparison NEW vs AGED (3 Age Iterations) IGBT Sample 3                               | . 199 |

| Figure 4.35 - IGBT Double Pulse Switching Parameters Characterization System                                                    | . 201 |

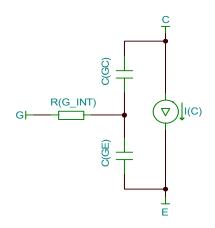

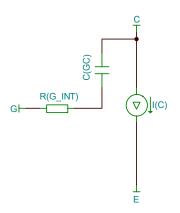

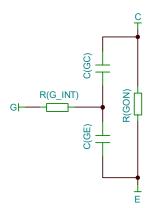

| Figure 5.1 – IGBT Stage 1 Turn-On Equivalent Circuit.                                                                           | . 204 |

| Figure 5.2 - IGBT Stage 2 Turn-On Equivalent Circuit                                                                            | . 205 |

| Figure 5.3 - IGBT Stage 3 Turn-On Equivalent Circuit                                                                            | . 205 |

| Figure 5.4 – IGBT Stage 4 Turn-On Equivalent Circuit.                                                                           | . 206 |

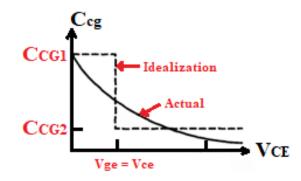

| Figure 5.5 - IGBT's Intrinsic Collector-Gate Capacitance variation with the Collector-Emitter Voltage (VCE) [11]                | . 207 |

| Figure 5.6 – Generic IGBT Turn-On $V_{CE}$ and $I_C$ [11]                                                                       | . 207 |

| Figure 5.7 – IGBT Turn-On Transient Equivalent Circuit during t <sub>RISE(ON)</sub> [11]                                        | . 208 |

| Figure 5.8 - IGBT Turn-On Transient Equivalent Circuit during the Miller Plateau [11]                                           | . 208 |

| Figure 5.9 - IGBT Turn-On Transient Equivalent Circuit during and beyond tfv2 [11].                                             | . 209 |

| Figure 5.10 – Generic IGBT Turn-On Transient Waveforms including Reverse Recovery [11]                                          | . 209 |

| Figure 5.11 – Generic IGBT Turn-Off Transient Waveforms [11]                                                                    | . 210 |

| Figure 5.12 - IGBT Turn-On Transient Reference Waveforms for Piecewise Linear and Non-Linear Modelling [213].                   | . 211 |

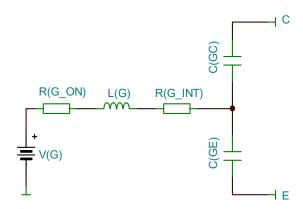

| Figure 5.13 – IGBT Behavioral Circuit for Piecewise Linear Modelling [215]                                                      | . 212 |

| Figure 5.14 – IGBT Equivalent Circuit during Turn-On Transients [215]                                                           | . 213 |

| Figure 5.15 - IGBT Piecewise Linear Model Phase 2 Turn-On Waveforms (t10N-t20N) [215]                                           | . 214 |

| Figure 5.16 - IGBT Piecewise Linear Model Phase 3 Turn-On Waveforms (t <sub>20N</sub> -t <sub>30N</sub> ) [215]                 | . 215 |

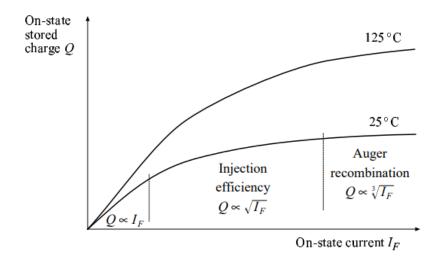

| Figure 5.17 - Theoretical relationship of diode stored charge with on-state current, dominant physical mechanism [219           | )]217 |

| Figure 5.18 - IGBT Piecewise Linear Model Phase 4 Turn-On Waveforms (t <sub>30N</sub> -t <sub>40N</sub> ) [215]                 | . 220 |

| Figure 5.19 - IGBT Piecewise Linear Model Phase 4 Turn-On Waveforms (t40N onwards) [215].                             | 222   |

|-----------------------------------------------------------------------------------------------------------------------|-------|

| Figure 5.20 - IGBT Turn-Off Transient Reference Waveforms for Piecewise Linear and Non-Linear Modelling [213].        | . 223 |

| Figure 5.21 - IGBT Equivalent Circuit during Turn-Off Transients [215]                                                | 224   |

| Figure 5.22 - IGBT Piecewise Linear Model Phase 1 Turn-Off Waveforms (t <sub>0(ON)</sub> - t <sub>1(ON)</sub> ) [215] | 225   |

| Figure 5.23 - IGBT Piecewise Linear Model Phase 2 Turn-Off Waveforms (t <sub>1(ON)</sub> - t <sub>2(ON)</sub> ) [215] | 226   |

| Figure 5.24 - IGBT Piecewise Linear Model Phase 3 Turn-Off Waveforms (t <sub>2(ON)</sub> - t <sub>3(ON)</sub> ) [215] | 227   |

| Figure 5.25 - IGBT Piecewise Linear Model Phase 2 Turn-Off Waveforms (t <sub>3(ON)</sub> - t <sub>4(ON)</sub> ) [215] | 228   |

| Figure 5.26 – IGBT Turn-On Piecewise Linear Model for IGBT Sample 14 (vNEW)                                           | 232   |

| Figure 5.27 - IGBT Turn-Off Piecewise Linear Model for IGBT Sample 14 (vNEW)                                          | 232   |

| Figure 5.28 - Reverse Recovery Collector Current (Ic) general non-linear function plot.                               | 240   |

| Figure 5.29 - Reverse Recovery Collector Current (I <sub>C</sub> ) decay general non-linear function plot.            | 243   |

| Figure 5.30 - Phase 1 & Phase 2 General V <sub>CE</sub> Model Equation                                                | 246   |

| Figure 5.31 - IGBT Turn-On Non-Linear Model for IGBT Sample 14 (vNEW)                                                 | 253   |

| Figure 5.32 - IGBT Turn-Off Non-Linear Model for IGBT Sample 14 (vNEW)                                                | 255   |

| Figure 5.33 - Generic MOS Capacitor Structure [230].                                                                  | 256   |

| Figure 5.34 - MOS capacitor structure [230].                                                                          | 257   |

| Figure 5.35 – MOS structure under surface accumulation [230]                                                          | 257   |

| Figure 5.36 - MOS structure under surface depletion [230].                                                            | 259   |

| Figure 5.37 – MOS structure under strong inversion [230].                                                             | 262   |

| Figure 5.38 – IGBT cell structure input parasitic capacitances.                                                       | 263   |

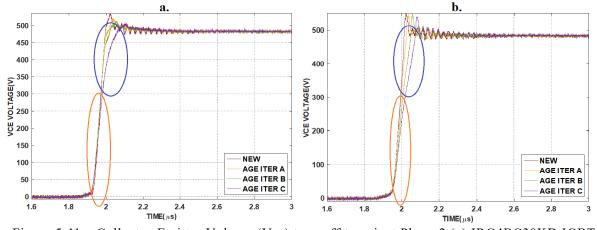

| Figure 5.39 - IGBT Collector-Emitter Voltage Transient Turn-Off Phase 1 (a) IRG4BC30KD (b) STGP19N60KD                | 266   |

| Figure 5.40 - IGBT Collector Current (Ic) Transient Turn-Off Phase 1                                                  | 266   |

| Figure 5.41 - Collector-Emitter Voltage (V <sub>CE</sub> ) turn-off transient Phase 2                                 | 267   |

| Figure 5.42 - Collector-Emitter Voltage (VCE) turn-off transient, Phase 1, and Phase 2                                | 268   |

| Figure 5.43 - Gate Voltage (V <sub>G</sub> ) turn-off transient, IRG4BC30KD IGBT Sample 14, Linear Piecewise Model    | 269   |

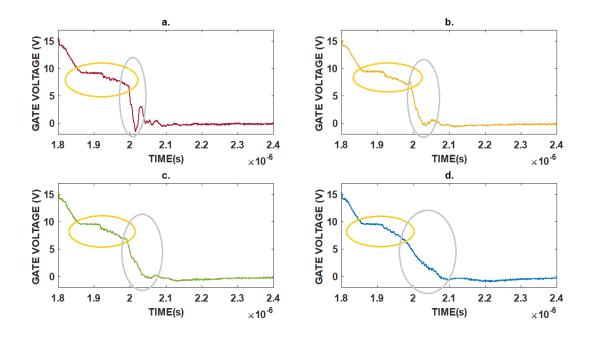

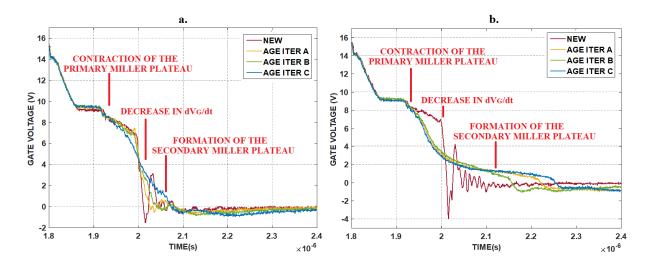

| Figure 5.44 –Gate Voltage (VG) turn-off transient evolution with ageing                                               | 270   |

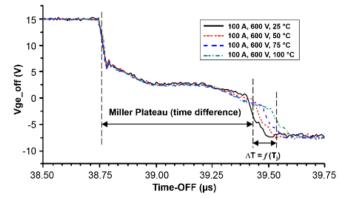

| Figure 5.45 – Elongation of the IGBT's Miller Plateau during turn-off [221].                                          | 271   |

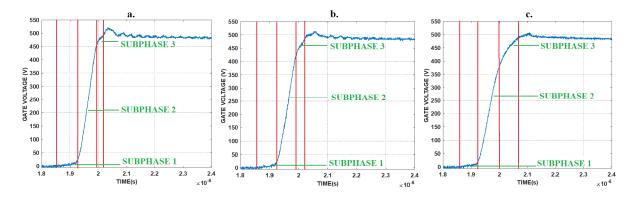

| Figure 5.46 - IGBT IRG4BC30KD Sample 14 highlighting the different subphases                                          | 273   |

| Figure 5.47 – IGBT Turn-Off Phase 1 & Phase 2 General V <sub>CE</sub> Model Function                                  | 274   |

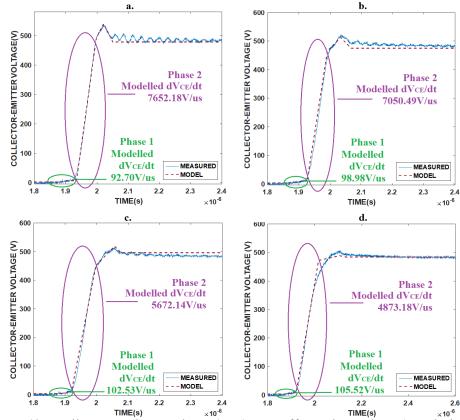

| Figure 5.48 - Collector-Emitter Voltage (VCE) turn-off transient, Phase 1, and Phase 2                                | 275   |

| Figure 5.49 - Collector-Emitter Voltage (V <sub>CE</sub> ) turn-off transient, Phase 1, and Phase 2                   | 276   |

| Figure 5.50 - Collector Current (Ic) turn-off transient Phase 2, Linear Piecewise Model                               | 278   |

| Figure 5.51 – Collector Current (I <sub>C</sub> ) turn-off transient Phase 2                                          | 278   |

| Figure 5.52 - Collector Current (Ic) turn-off transient, Phase 2, Non-Linear Model                                    | 280   |

| Figure 5.53 - Measured Phase 3 IGBT Intrinsic MOSFET controlled dIc/dt Evolution with Ageing                          | 281   |

| Figure 5.54 – IGBT Intrinsic MOSFET controlled Collector Current (Ic) turn-off transient Phase 3                      | 283   |

| Figure 5.55 - Measured Phase 4 IGBT Intrinsic BJT "Tailing" Current Evolution with Ageing                             | 287   |

| Figure 5.56 - IGBT Collector Current (IC) turn-off transient Phase 3 and Phase 4                                      | 288   |

| Figure 5.57 - Measured Phase 3 and Phase 4 IGBT Collector-Emitter Evolution with Ageing.                              | 289   |

| Figure 5.58 - IGBT Collector-Emitter Voltage (VCE) turn-off transient Phase 3 & 4                               | 290 |

|-----------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.59 - IGBT Collector-Emitter Voltage (VCE) turn-off transient Phase 3 and Phase 4                       | 291 |

| Figure 5.60 - IGBT Turn-Off Switching Power Loss, Measured and Non-Linear Model                                 | 292 |

| Figure 5.61 - IGBT Collector Current (Ic) turn-on transient Phase 2, Linear Piecewise Model                     | 294 |

| Figure 5.62 - IGBT Collector-Emitter Voltage (VCE) turn-on transient Phase 2 & 3, Linear Piecewise Model        | 296 |

| Figure 5.63 - IGBT Collector-Emitter Voltage (VCE) turn-on transient Phase 4, Linear Piecewise Model            | 299 |

| Figure 5.64 - IGBT Collector Current (I <sub>C</sub> ) turn-on transient, IRG4BC30KD IGBT Sample 14             | 300 |

| Figure 5.65 - IGBT Collector-Emitter Voltage (VCE) turn-on transient, Non-Linear Model                          | 300 |

| Figure 6.1 – EMC immunity tests and corresponding standards                                                     | 307 |

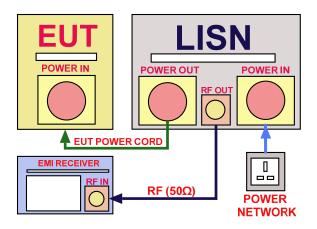

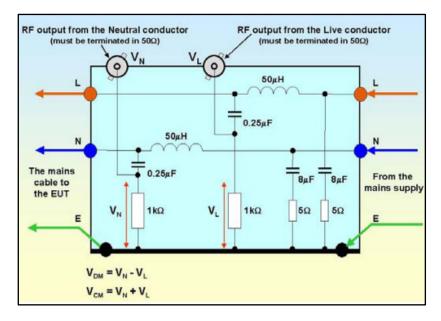

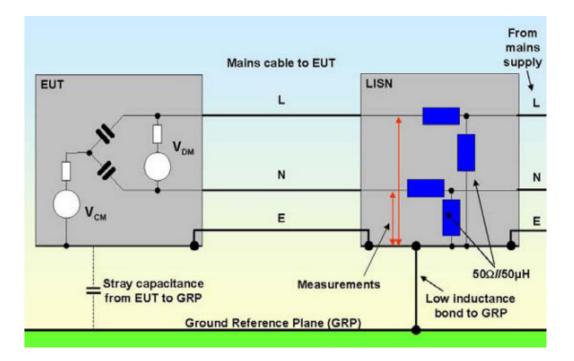

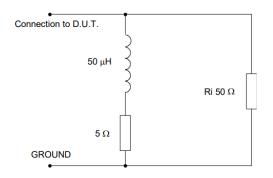

| Figure 6.2 - Generic connection of the LISN within an EM conducted emissions test setup                         | 308 |

| Figure 6.3 - Internal schematic of a $50\Omega/50\mu$ H+5 $\Omega$ LISN [248].                                  | 309 |

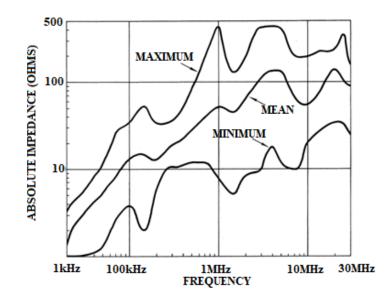

| Figure 6.4 - Power line impedance variation 0.02-30MHz [244]                                                    | 310 |

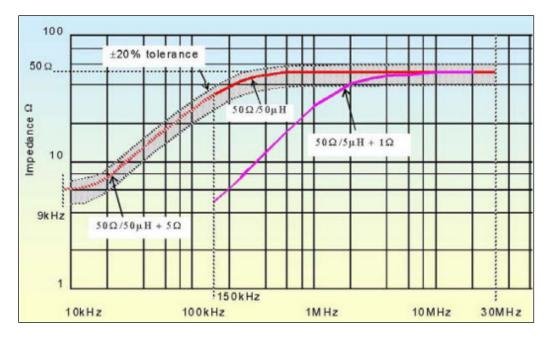

| Figure 6.5 – LISN Impedance Curve [248]                                                                         | 310 |

| Figure 6.6 – EM conducted emissions single phase test setup equivalent circuit [238]                            | 312 |

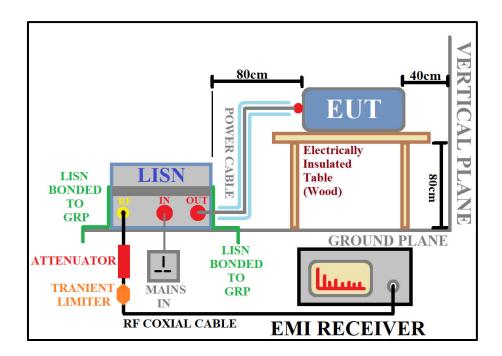

| Figure 6.7 – Representation of the typical EM conducted emissions test setup as provided in [250].              | 313 |

| Figure 6.8 – High level EM conducted emissions, experimental setup.                                             | 315 |

| Figure 6.9 – NARDA PMM L2-16B LISN CISPR Equivalent Circuit [254].                                              | 316 |

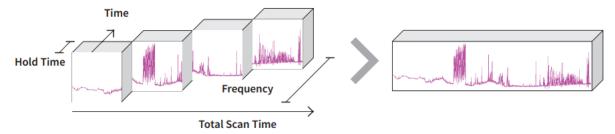

| Figure 6.10 - NARDA PMM-EMI-9010Freceiver, FFT based, gapless direct conversion measurement method [250]        | 317 |

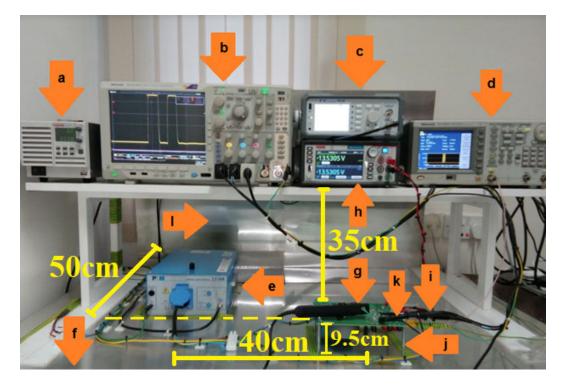

| Figure 6.11 – Conducted Emissions experimental setup.                                                           | 318 |

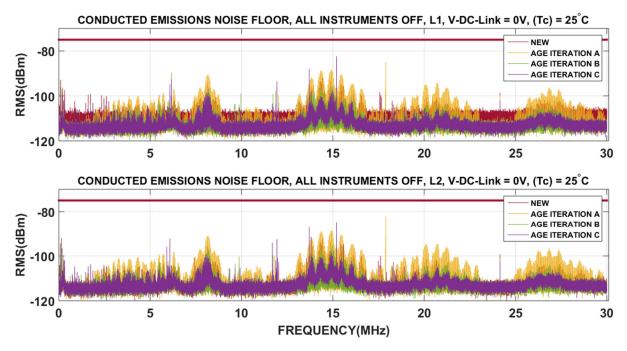

| Figure 6.12 – IGBT Sample 3, conducted emissions noise floor, all instruments off                               | 322 |

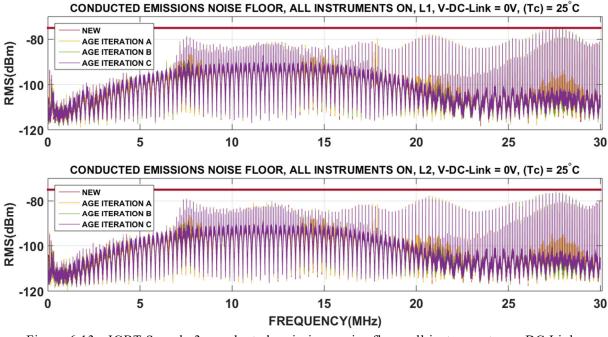

| Figure 6.13 - IGBT Sample 3, conducted emissions noise floor, all instruments on, DC Link Voltage at 0V         | 324 |

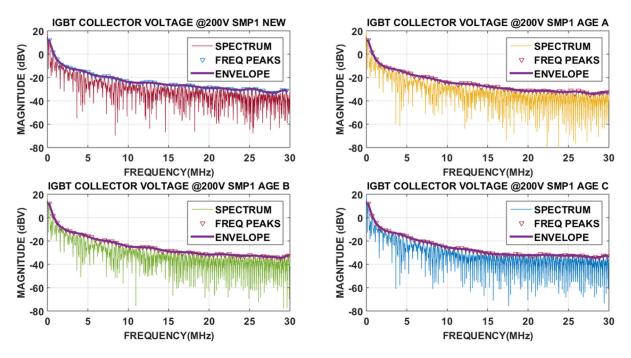

| Figure 6.14 - IGBT Sample 1 Collector Voltage (Vc) FFT, Frequency Peaks, and corresponding Peaks Envelopes      | 326 |

| Figure 6.15 - IGBT Sample 1 Collector Voltage (V <sub>C</sub> ) FFT                                             | 326 |

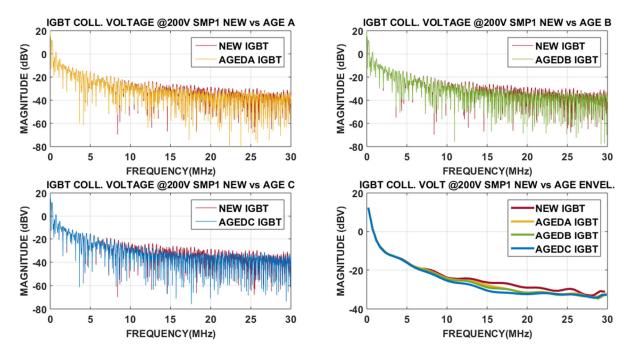

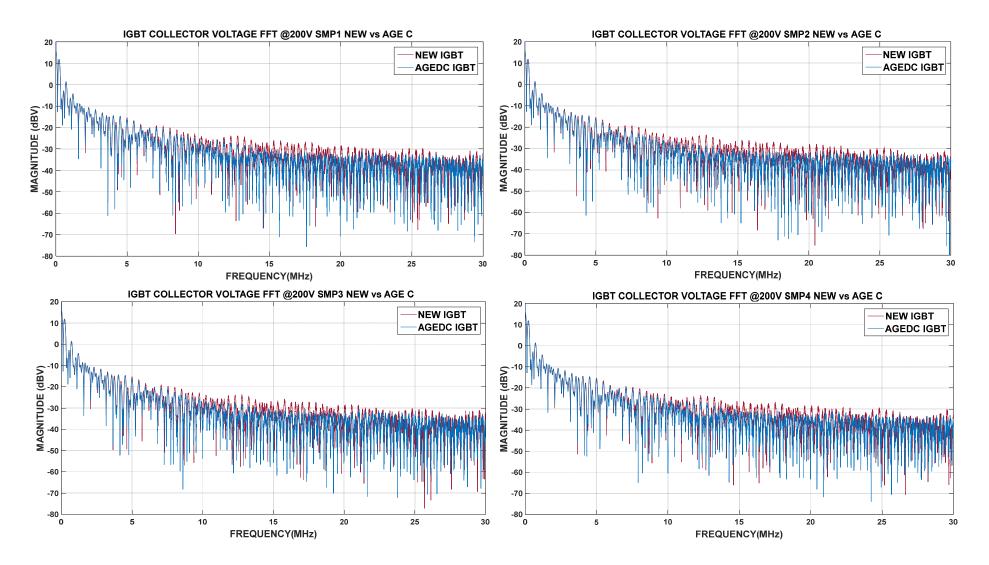

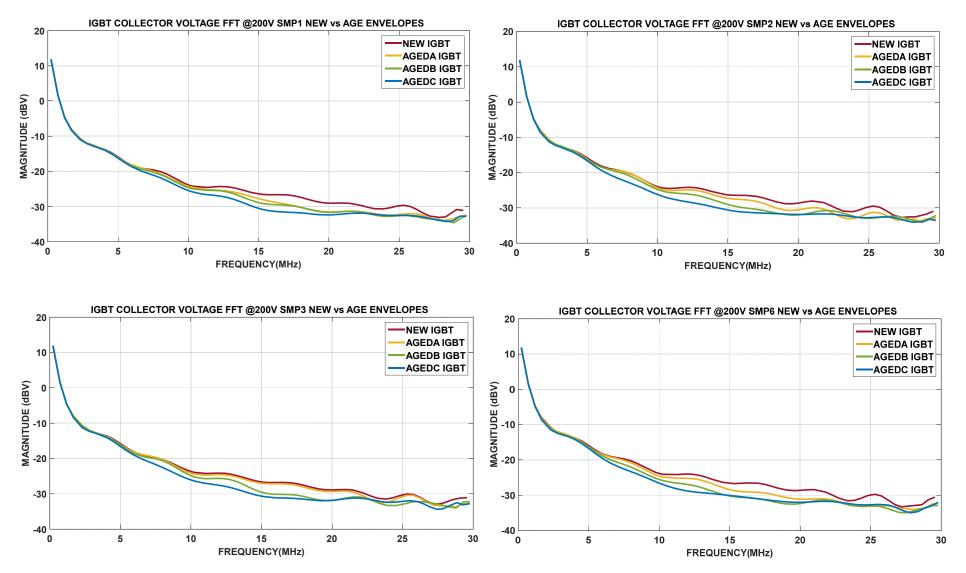

| Figure 6.16 - IGBT Samples 1 to 4, Collector Voltage (Vc) FFT, New vs Age Iteration C                           | 327 |

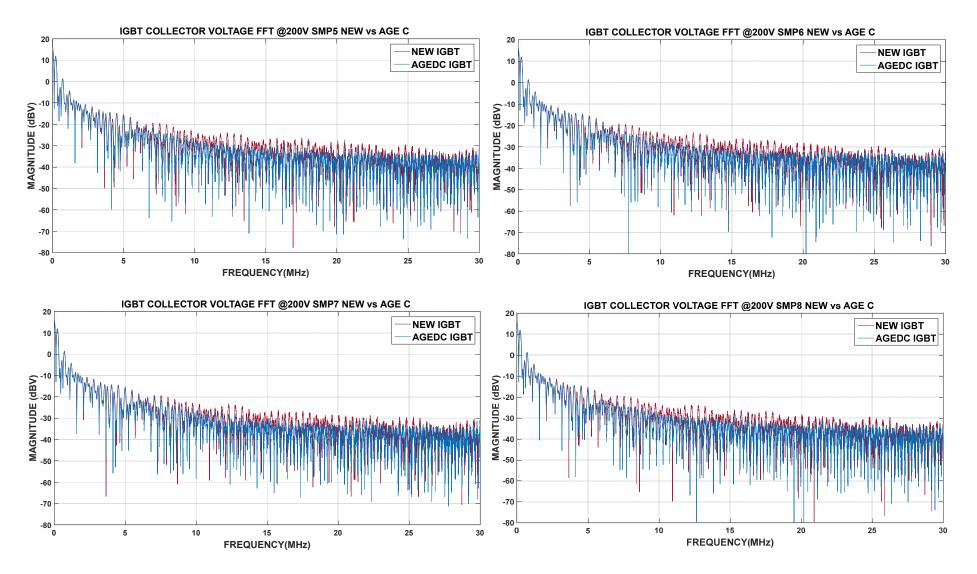

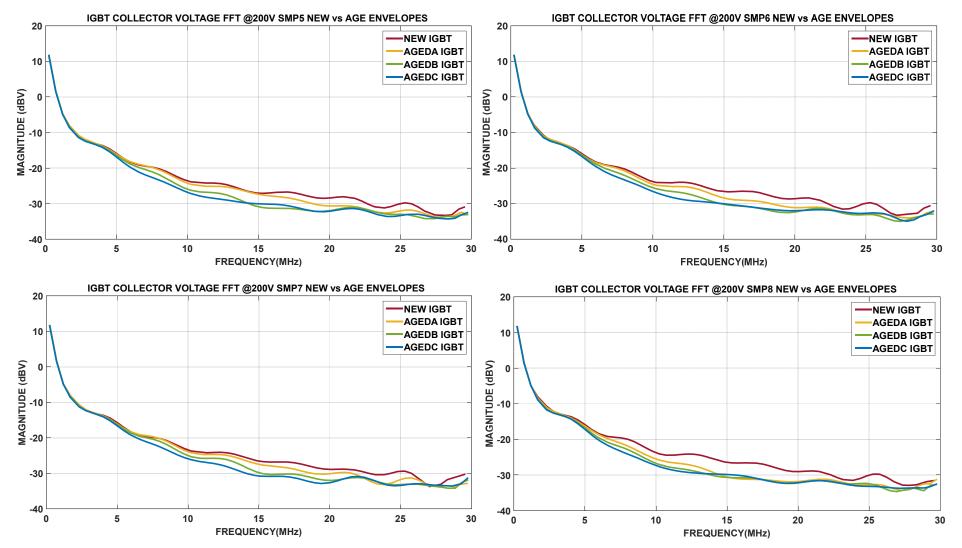

| Figure 6.17 - IGBT Samples 5 to 8, Collector Voltage (V <sub>C</sub> ) FFT, New vs Age Iteration C              | 328 |

| Figure 6.18 - IGBT Samples 1 to 4, Collector Voltage (Vc) FFT, Frequency Peaks Envelopes                        | 329 |

| Figure 6.19 - IGBT Samples 5 to 8, Collector Voltage (V <sub>C</sub> ) FFT, Frequency Peaks Envelopes           | 330 |

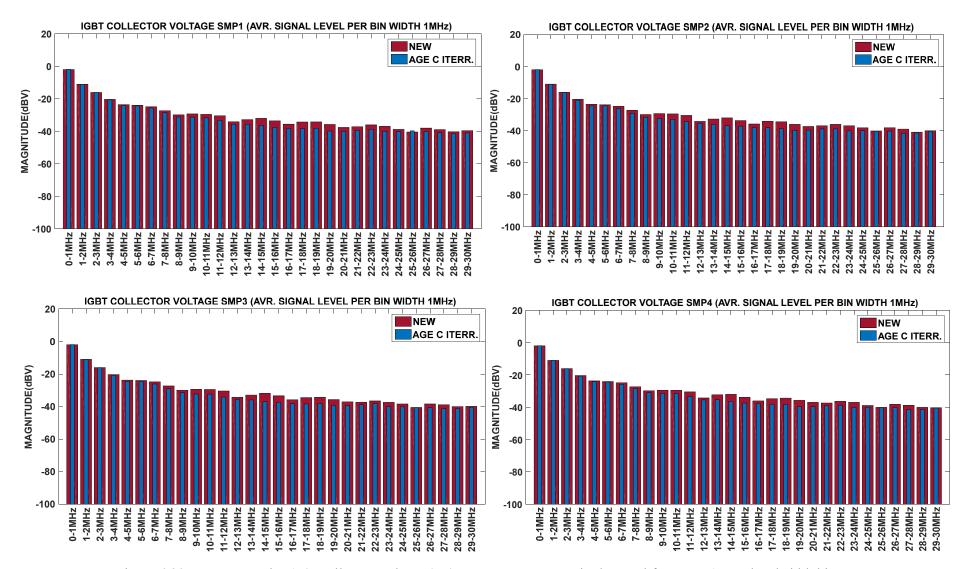

| Figure 6.20 - IGBT Samples 1-4, Collector Voltage (Vc) FFT, Average Magnitude Level for every 1MHz              | 331 |

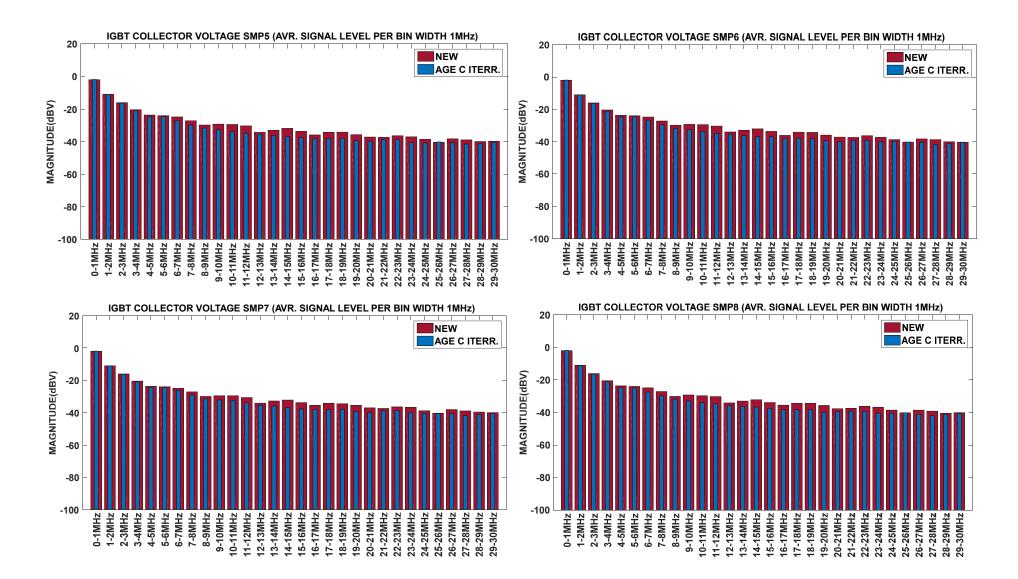

| Figure 6.21 - IGBT Samples 5-8, Collector Voltage (V <sub>C</sub> ) FFT, Average Magnitude Level for every 1MHz | 332 |

| Figure 6.22 - IGBT Samples 1-4, Collector Voltage (Vc) FFT, Maximum Magnitude Level for every 1MHz              | 333 |

| Figure 6.23 - IGBT Samples 5-8, Collector Voltage (V <sub>C</sub> ) FFT, Maximum Magnitude Level for every 1MHz | 334 |

| Figure 6.24 - Combined Statistics of IGBTs Samples 1-10, Collector Voltage (Vc) FFT, Average Magnitude          | 335 |

| Figure 6.25 - Combined Statistics of IGBTs Samples 1-10, Collector Voltage (Vc) FFT, Maximum Magnitude          | 335 |

| Figure 6.26 - IGBT Sample 5 Collector Current (Ic) FFT, Frequency Peaks, and corresponding Peaks Envelopes      | 338 |

| Figure 6.27 - IGBT Sample 5 Collector Voltage (Vc) FFT                                                          | 338 |

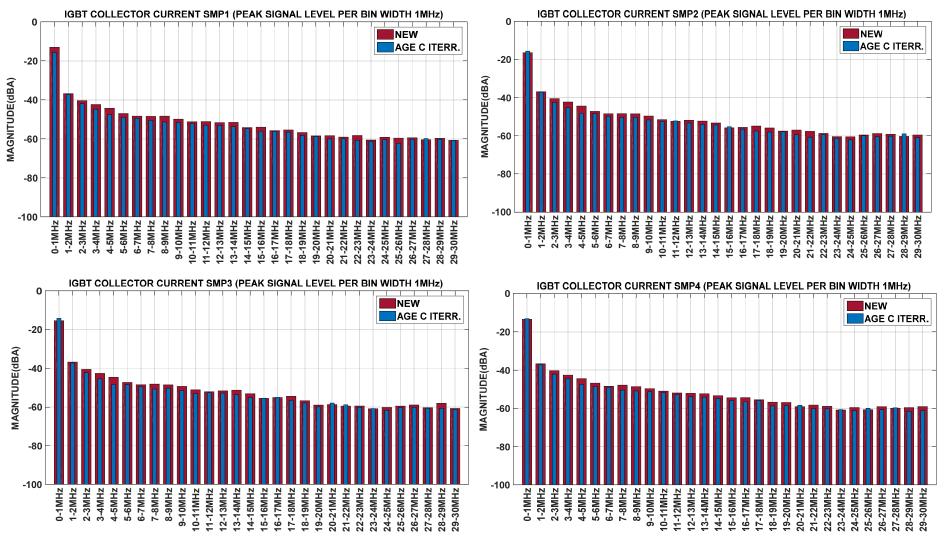

| Figure 6.28 - IGBT Samples 1 to 4, Collector Current (Ic) FFT, New vs Age Iteration C                           | 339 |

| Figure 6.29 - IGBT Samples 5 to 8, Collector Current (Ic) FFT, New vs Age Iteration C                           | 340 |

| Figure 6.30 - IGBT Samples 1 to 4, Collector Current (Ic) FFT, Frequency Peaks Envelopes                        | 341 |

| Figure 6.31 - IGBT Samples 5 to 8, Collector Current (Ic) FFT, Frequency Peaks Envelopes                        | 342 |

|                                                                                                                 |     |

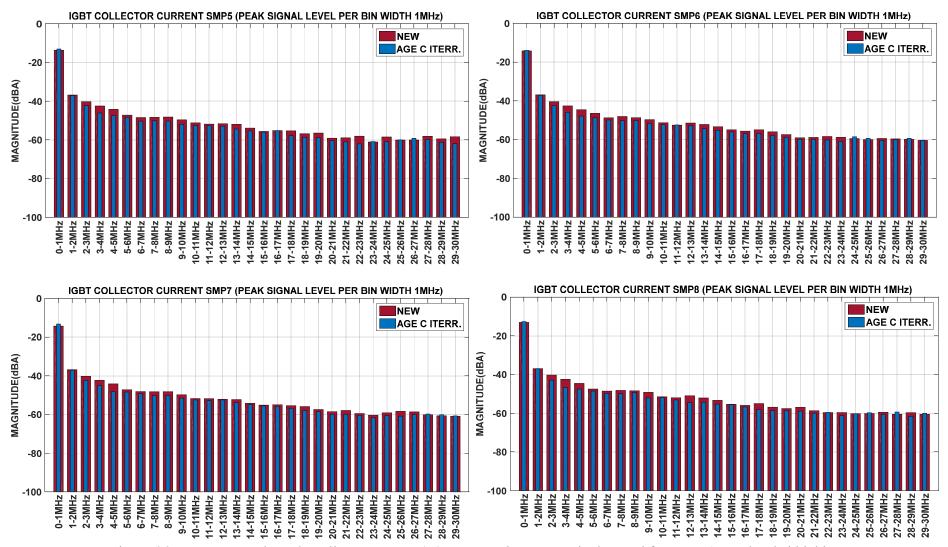

| Figure 6.32 - IGBT Samples 1-4, Collector Current (Ic) FFT, Average Magnitude Level for every 1MHz                      | . 343 |

|-------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 6.33 - IGBT Samples 5-8, Collector Current (Ic) FFT, Average Magnitude Level for every 1MHz                      | . 344 |

| Figure 6.34 - IGBT Samples 1-4, Collector Current (Ic) FFT, Maximum Magnitude Level for every 1MHz                      | . 345 |

| Figure 6.35 - IGBT Samples 5-8, Collector Current (Ic) FFT, Maximum Magnitude Level for every 1MHz                      | . 346 |

| Figure 6.36 - Combined Statistics of IGBTs Samples 1-10, Collector Current (Ic) FFT, Average Magnitude                  | . 347 |

| Figure 6.37 - Combined Statistics of IGBTs Samples 1-10, Collector Current (Ic) FFT, Maximum Magnitude                  | . 347 |

| Figure 6.38 - IGBT Sample 2 CISPR16-1-1 A&B Bands, L1 (Forward Line), Conducted Emissions Spectra.                      | . 352 |

| Figure 6.39 - IGBT Sample 2 CISPR16-1-1 A&B Bands, L1 (Forward Line), Conducted Emissions Spectra                       | . 352 |

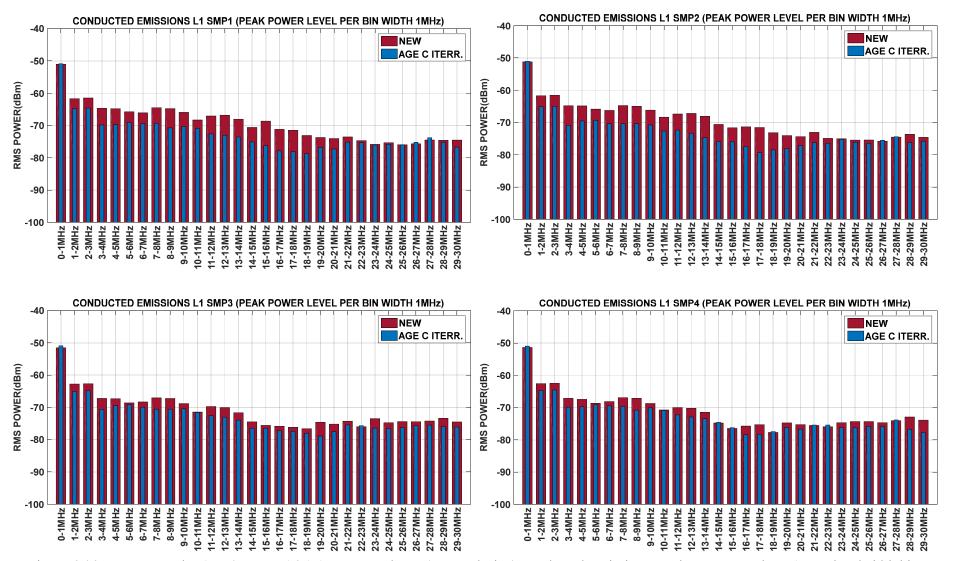

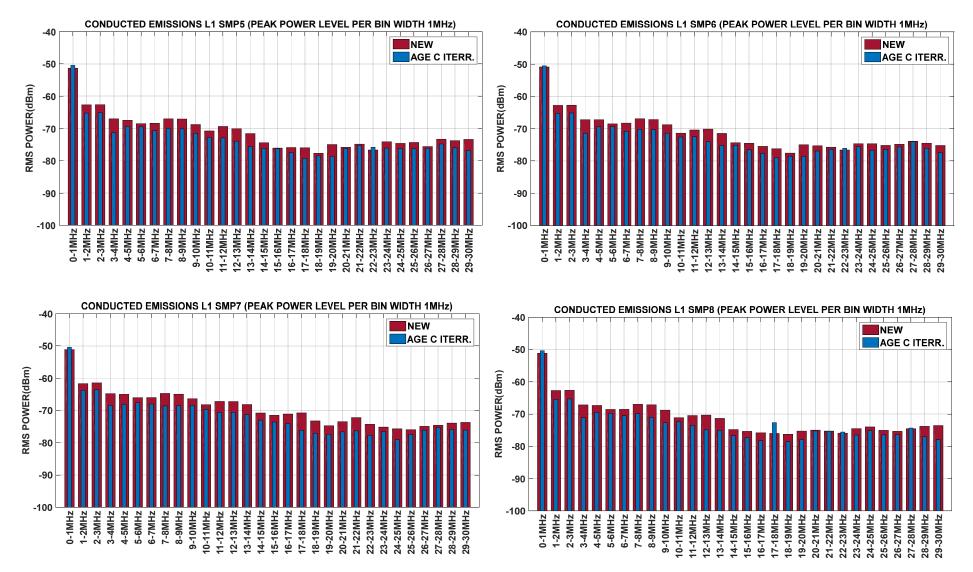

| Figure 6.40 - IGBT Samples 1 to 4, CISPR16-1-1 A&B Bands Conducted, L1 (Forward Line) Conducted Emissions               | . 353 |

| Figure 6.41 IGBT Samples 5 to 8, CISPR16-1-1 A&B Bands Conducted, L1 (Forward Line) Conducted Emissions.                | . 354 |

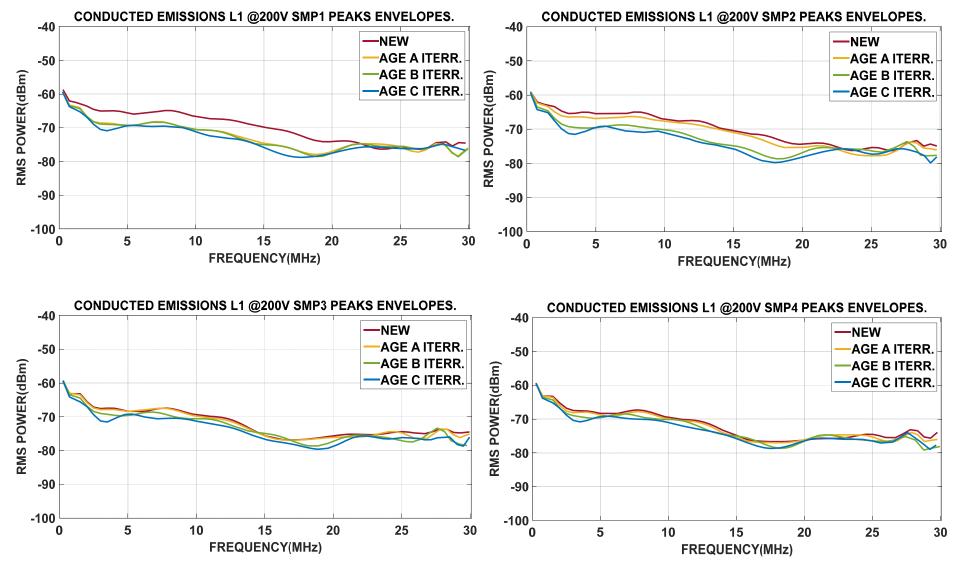

| Figure 6.42 - IGBT Samples 1 to 4, L1 Conducted Emissions Frequency Peaks Envelopes, All Age Iterations                 | . 355 |

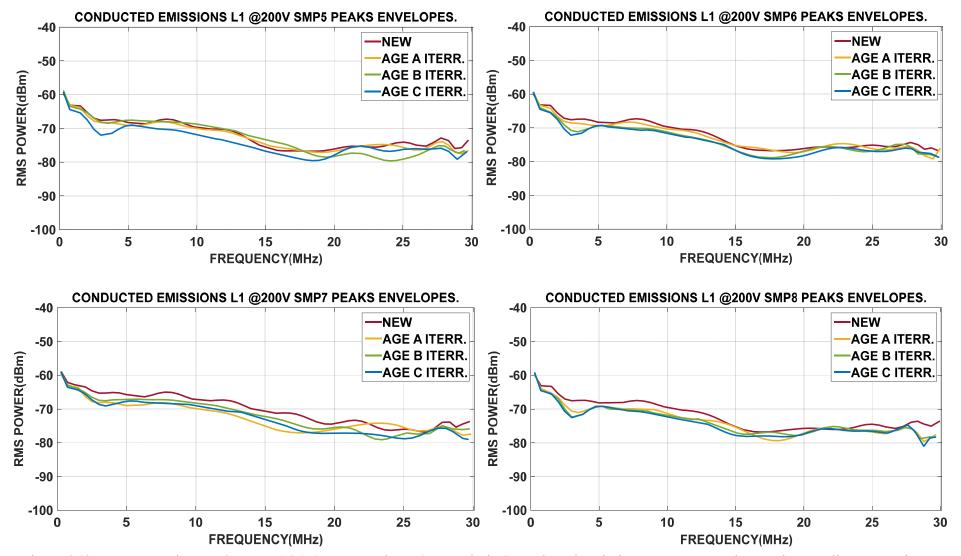

| Figure 6.43 - IGBT Samples 5 to 8, L1 Conducted Emissions Frequency Peaks Envelopes, All Age Iterations                 | . 356 |

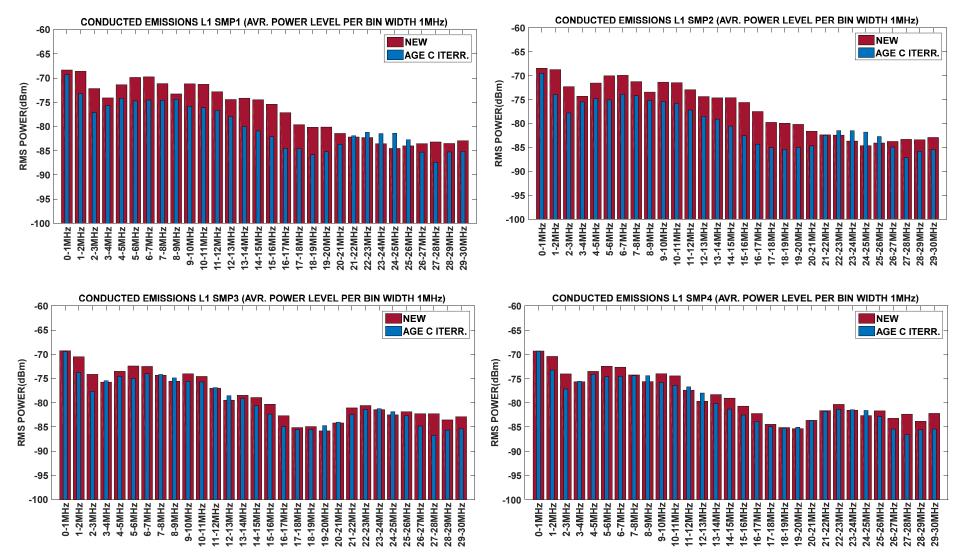

| Figure 6.44 - IGBT Samples 1 to 4, L1 (Forward Line) Conducted Emissions, Average Power Level.                          | . 357 |

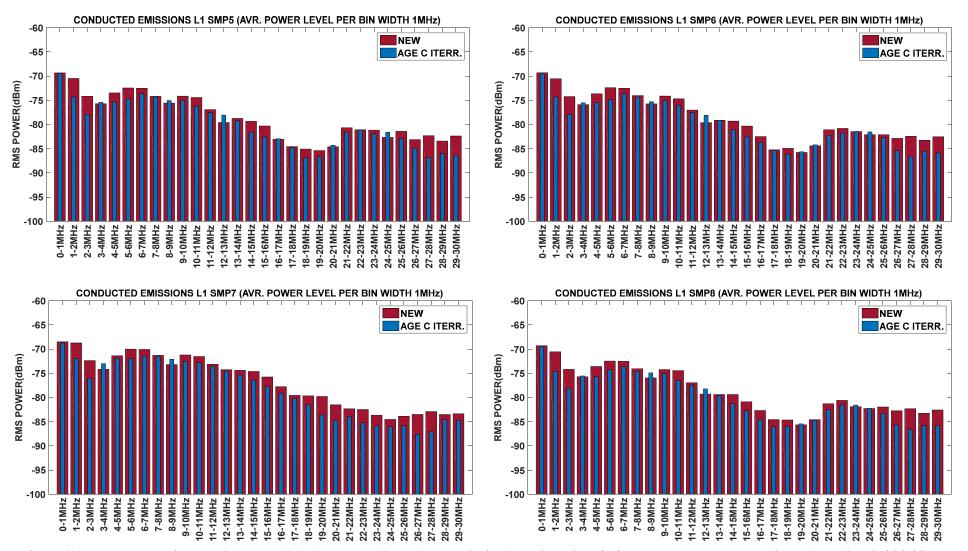

| Figure 6.45 - IGBT Samples 5 to 8, L1 (Forward Line) Conducted Emissions, Average Power Level.                          | . 358 |

| Figure 6.46 - IGBT Samples 1 to 4, L1 (Forward Line) Conducted Emissions, Peak Power Level.                             | . 359 |

| Figure 6.47 - IGBT Samples 5 to 8, L1 (Forward Line) Conducted Emissions, Peak Power Level.                             | . 360 |

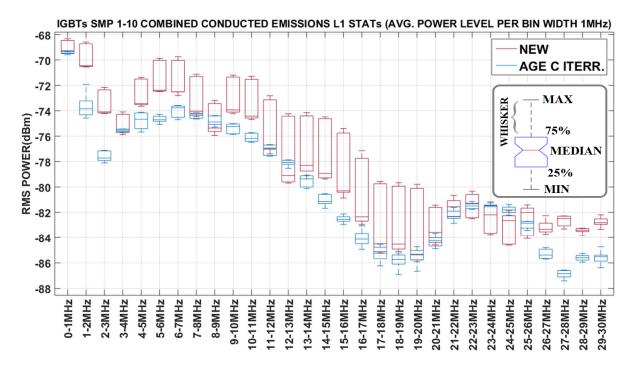

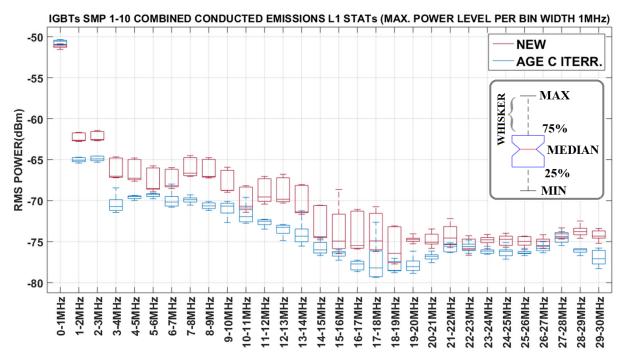

| Figure 6.48 - Combined Statistics of IGBTs Samples 1-10, , L1 (Forward Line), Average Power Level.                      | . 361 |

| Figure 6.49 - Combined Statistics of IGBTs Samples 1-10, L1 (Forward Line), Peak Power Level                            | . 361 |

| Figure 6.50 - IGBT Sample 3, L <sub>2</sub> , Conducted Emissions Spectra, Frequency Peaks.                             | . 362 |

| Figure 6.51 - IGBT Sample 2, L <sub>2</sub> ,Conducted Emissions Spectra.                                               | . 362 |

| Figure 6.52 - IGBT Samples 1 to 4, L2, Conducted Emissions Spectra, New vs Age Iteration C.                             | . 363 |

| Figure 6.53 - IGBT Samples 5 to 8, L <sub>2</sub> , Conducted Emissions Spectra, New vs Age Iteration C                 | . 364 |

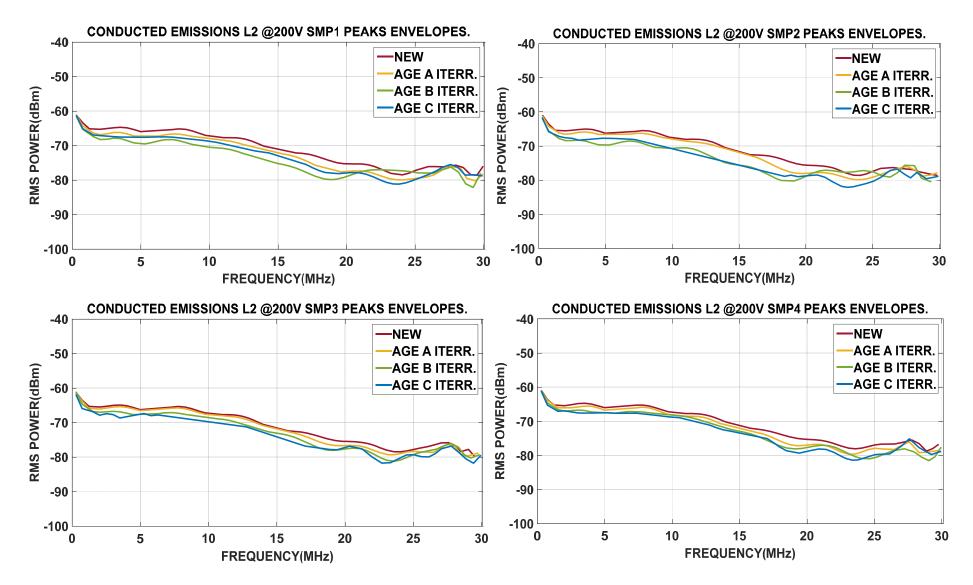

| Figure 6.54 - IGBT Samples 1 to 4, L <sub>2</sub> , Conducted Emissions, Frequency Peaks Envelopes, All Age Iterations. | . 365 |

| Figure 6.55 - IGBT Samples 5 to 8, L2, Conducted Emissions, Frequency Peaks Envelopes, All Age Iterations.              | . 366 |

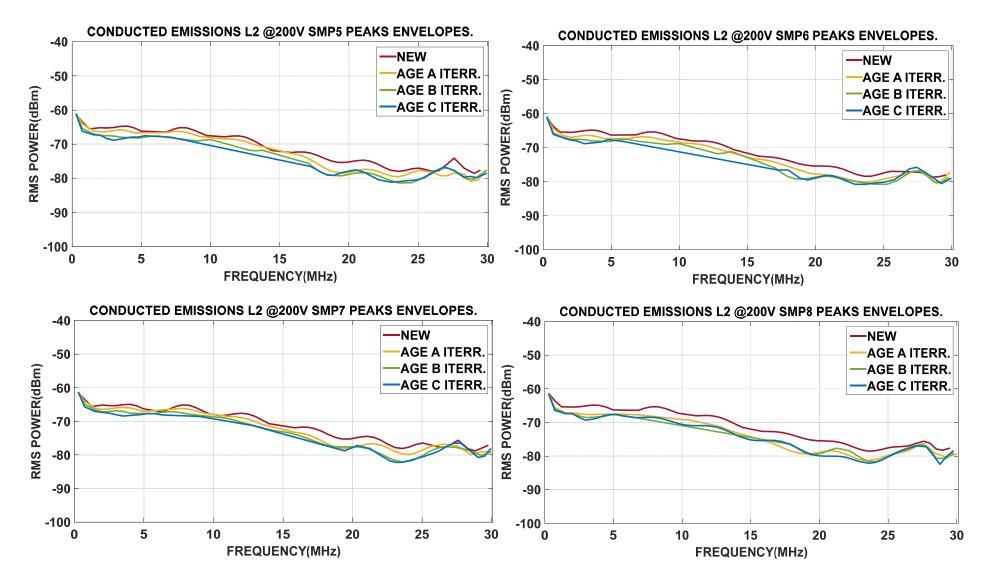

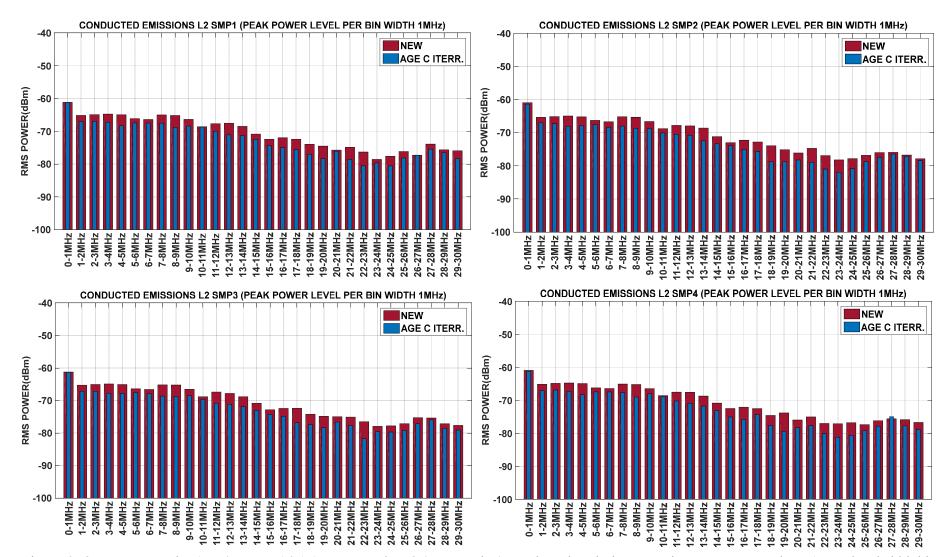

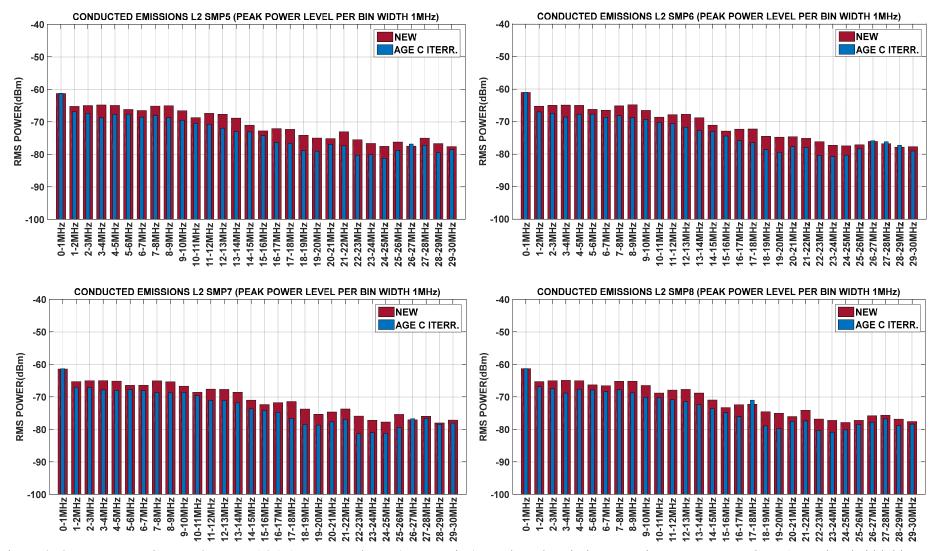

| Figure 6.56 - IGBT Samples 1 to 4, L <sub>2</sub> , Conducted Emissions, Average Power Level per 1MHz bandwidth bin     | . 367 |

| Figure 6.57 - IGBT Samples 5 to 8, L2 Conducted Emissions, Average Power Level per 1MHz                                 | . 368 |

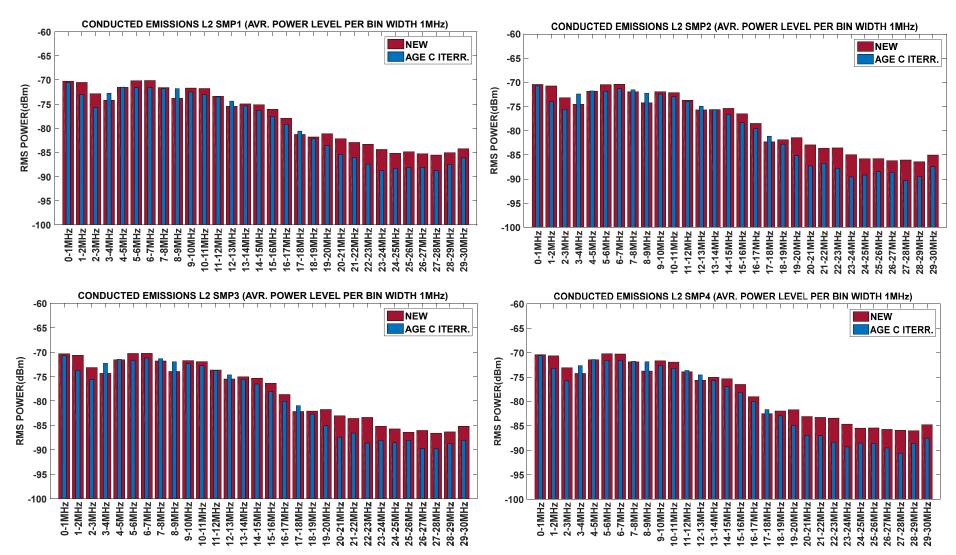

| Figure 6.58 - IGBT Samples 1 to 4, L2 Conducted Emissions, Maximum Power Level per 1MHz bandwidth bin                   | . 369 |

| Figure 6.59 - IGBT Samples 5 to 8, L2 Conducted Emissions, Maximum Power Level per 1MHz bandwidth bin                   | . 370 |

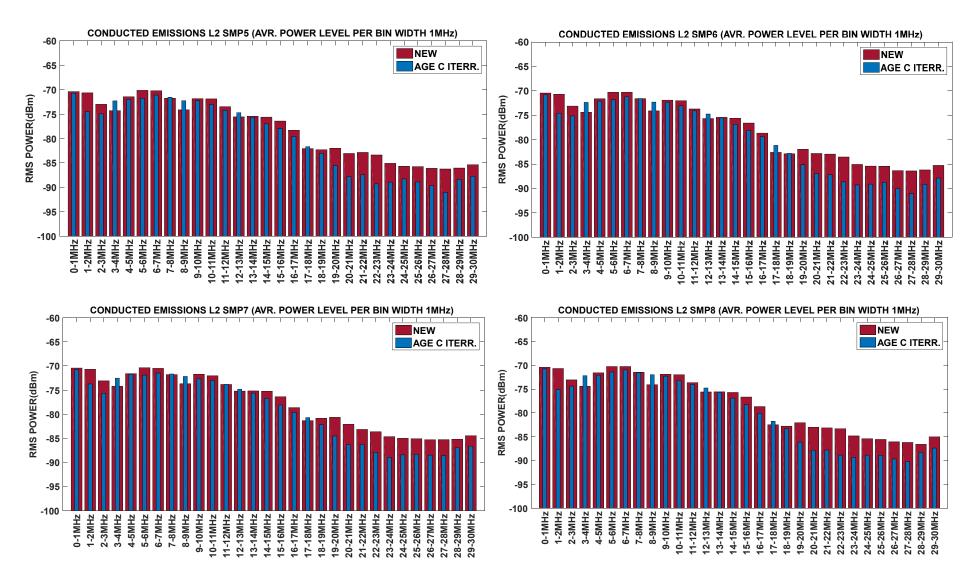

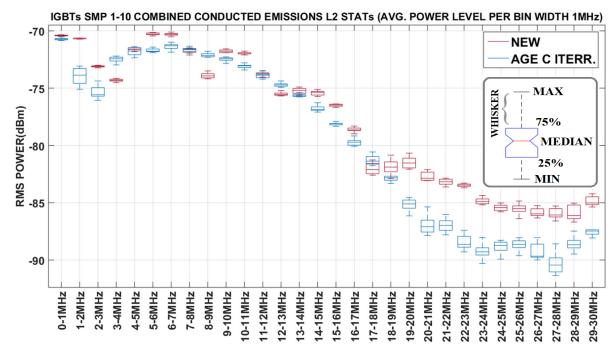

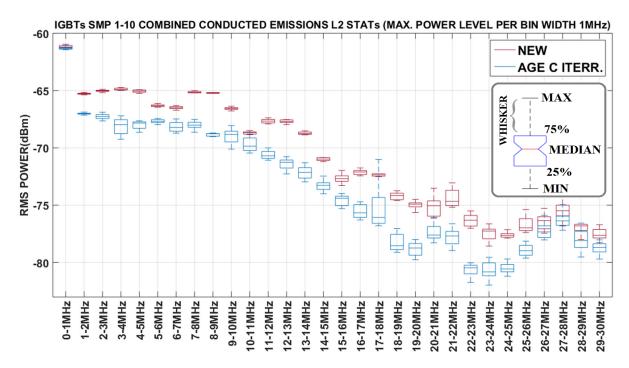

| Figure 6.60 - Combined Statistics of IGBTs Samples 1-10, L2 Average Power Level for every 1MHz bandwidth bin            | . 371 |

| Figure 6.61 - Combined Statistics of IGBTs Samples 1-10, Conducted Emissions, L <sub>2</sub> , Peak Power Level.        | . 371 |

# Acknowledgements

First and foremost, I am grateful to my supervisor Dr. John Fredrick Dawson, for his constant guidance and unrelenting support throughout this journey.

I would like to thank Ing. Reuben Debono, Mr. Donald Vella, Mr. Kevin Caruana Montaldo and Mr. Stephen Spiteri, responsible for the electronics laboratory at the Department of Electronic Systems, Faculty of Engineering, University of Malta, for their constant support during this research.

My sincere thanks go to Professor Ing Andrew Sammut, Head of the Department of Electronic Systems, Faculty of Engineering, University of Malta, for the help and support throughout this work.

I would like to thank the University of Malta represented by the Rector Professor Alfred Vella, for funding this research.

Finally, my sincere appreciation goes to my family, my daughter Marta, my wife Corinne, my parents Joseph and Doris, and my in-laws Oliver and Mariella, for their continuous encouragement and support.

# Declaration

I declare that this thesis is a presentation of original work, and I am the sole author. This work has not previously been presented for an award at this, or any other, University. All sources are acknowledged as References.

# Copyright © 2022 University of York.

"The copyright of this report rests with the author and the University of York. No quotations from it should be published without prior written consent and information derived from it should be acknowledged".

# Chapter 1 Introduction

## 1.1 Research Background

Today power electronics play a significant role in the operation and performance of ships, aircraft, electric or hybrid electric vehicles, utility interfaces, renewable energy sources, power transmission and many other industrial applications. These power-electronics based systems, utilize power semiconductor devices (PSDs) for power loads activation and control. Degradation or failure of these devices can reduce system efficiency or may lead to system failure, which can yield to monetary losses, mission abandonment, or life-threatening accidents. Hence, the reliability of power-electronic systems and more specifically the reliability of PSDs, has become crucial and has recently drawn more attention and more research. In this regard, Yang et al. [14], conducted an industrial survey related to the reliability of power electronic converters, where 31% of those interviewed classified PSDs as the "most fragile component". In another study [10], it was reported that PSD related failures, constitute 38% of the failures happening within Variable Speed Drives (VSDs), while according to Wolfgang [8], 34% of power-electronic systems' failures are attributed to failures occurring within PSDs.

Insulated Gate Bipolar Transistors (IGBTs) are PSDs which combine the low-on-state capabilities of a Bipolar Junction Transistor (BJT) (at increased breakdown voltage levels), with the facilitated input voltage control of a MOSFET. These characteristics, in conjunction with the enhanced switching capabilities, promoted the employment of the IGBT, in various power electronic systems, thus becoming one of the most widely used PSDs. This is evidenced in the same study conducted by Yang et al. [10], where it was reported by those interviewed, that the IGBT is the most utilized PSD in industrial applications. During their lifetime, PSDs and hence IGBTs, can be influenced by many degradation and failure mechanisms, which can be divided into two categories: semiconductor (die) related failures and package related failures. These can be triggered by various causes, such as harsh environmental conditions, electrical overstresses, chemical contamination, electromagnetic (EM) radiation, cosmic rays, or through regular usage leading to device's ageing. The construction of an IGBT involves multiple chemical, electrical, and mechanical processes and hence the employment of various materials. Thus, the IGBT's sub-structures can be prone to multiple failure mechanisms which

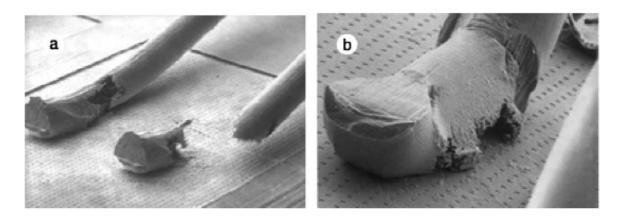

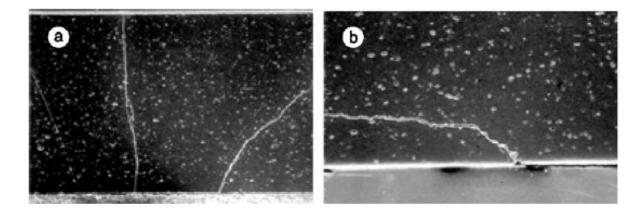

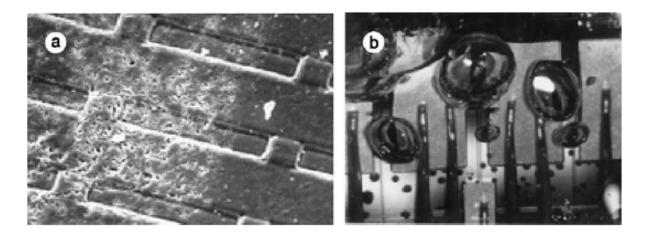

can lead to the general IGBT failure. Ciappa [73], provided an important study in relation to IGBT failures namely, bond wire fatigue, substrate cracking, interconnections corrosion and solder voiding. Another important study in this regard, was the one conducted by Busca et al. [74]. This study analyzed IGBT failing mechanisms associated with bond wire lift-off, solder voiding and bond wire cracking due to non-uniform thermal expansion coefficients.

### **1.2 Research Scope**

A failure precursor is an event (or series of events) that is indicative of a looming failure. The identification of failure precursors and the monitoring of their extent of deviation, from the expected normal operation, can contribute to establish the health state of a device or a system, and hence determine lifetime parameters such as the Remaining Useful Life (RUL) or the Mean Time to Failure (MTTF). Failure precursor parameters can be identified by performing Failure Modes and Effects Analysis (FMEA). Moreover, PSDs' manufacturers and systems' engineers, perform accelerated ageing procedures, hence inflicting controlled degradation that is normally inflicted over a prolonged period. Throughout accelerated ageing procedures, the device or system, is characterized to identify those parameters are utilized to diagnose degradation, by implementing prognostic algorithms, with the aim of predicting when the device or system will no longer perform its intended functionality, hence issuing important alerts and preventing catastrophic failures.

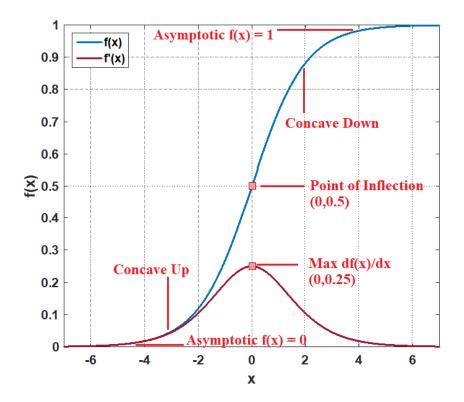

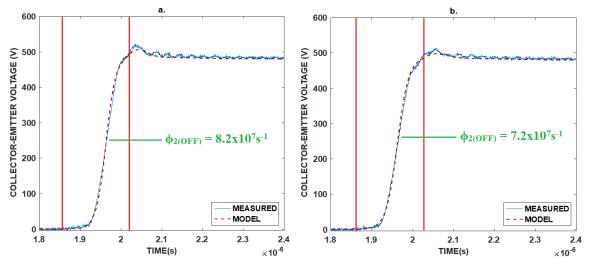

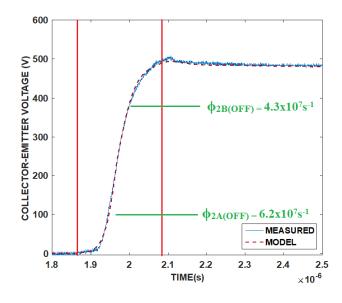

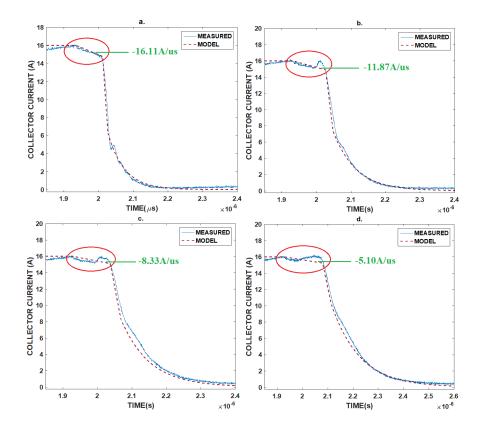

There are different studies in literature, which deal with different IGBT's failure precursors, where the latter include both mechanical and electrical parameters. Yang et al. [75], conducted a study which delved in diagnosis and prognosis methods to determine the health state of the IGBT. Patil et al. [81] conducted a thorough FMEA of IGBT related failures, correlating failures mechanisms, to failure causes, modes, and failure area within the IGBT, while identifying corresponding failure precursors. A more complete and updated review of the IGBT failure mechanisms was conducted by Abuelnaga et al. [67]. This study short listed the different failure mechanisms and analysis, and different test setups to perform accelerated controlled degradation. Moreover, it reviewed the different diagnostic IGBT parameters indicating failure, and the corresponding lifetime modelling found in literature to determine the IGBT's health state.