## THE UNIVERSITY OF SHEFFIELD

# **Current Limiting Devices for Short-Circuit Protection of DC Systems in Aerospace Applications**

By

## **Mahmood Alwash**

A Thesis submitted for the degree of Doctor of Philosophy in the Department of Electronic and Electrical Engineering, The University of Sheffield.

October 2018

#### **Abstract**

The use of DC systems to power high-power loads offers many advantages over AC in terms of efficiency and flexibility. Due to the increasing demand for electric power in aircrafts, the need for wider adoption of DC-based networks has been growing. This demand for higher power has originated from various efforts to electrify aircrafts ranging from replacing some of the mechanical components of jet engines with lighter electrical alternatives up to completely replacing jet engines with electric propulsors. Most of these efforts have been experimental, and no electric or "moreelectric" aircrafts are commercially available as of the writing of this thesis. One of the main challenges hindering wider adoption of DC-based networks in aircraft systems is addressing concerns pertaining to system reliability. These concerns are emphasized by the lack of detailed analyses of possible fault scenarios and appropriate technologies for fault protection. This thesis aims to address these concerns by first presenting detailed analyses of the most severe fault scenario in AC/DC power converters, which are common components in DC-based power systems used to interface with AC networks or electric machines. Then, using the information provided by the analyses, current limiting devices are developed for fault protection. These are unique devices which take advantage of recent developments in Silicon Carbide materials that have produced Junction Field Effect Transistors (JFETs) with significantly higher performance than their Silicon counterparts. The resistance of the JFET is varied with the magnitude of current so that the circuit experiences the most amount of resistance under a fault condition and the least amount of resistance under nominal conditions. Two circuit configurations are presented one having the least complexity (maximum reliability) and one which is more complex but offers significant performance benefits.

## Acknowledgements

I would like to extend my sincere gratitude to everyone who has supported me through this study. To my parents Abdulrazzaq Alwash & Intissar Muneeb and siblings Zina, Zain, & Zahraa Alwash.

I would like to thank my academic and industrial supervisors Professor Shankar Madathil and Dr Graham Bruce for their guidance and support through the course of this work. I would also like to thank Dr Mark Sweet for his technical expertise and thorough review of this thesis.

Finally, I would like to thank Rolls-Royce plc for providing financial and technical support, and the University of Sheffield for facilitating this study. I would like to also thank Aurora Flight Sciences, a Boeing Company for providing me with an amazing internship experience during the summer of 2016.

# **Table of Contents**

| Chapter | : 1: Introduction                                                     | 1        |

|---------|-----------------------------------------------------------------------|----------|

| 1.1.    | The Uprising of DC: Historical Background and Technology Influence    | 1        |

| 1.2.    | Advantages and Shortcomings of DC-based Power System Architectures    | 2        |

| 1.3.    | DC in Aircrafts Power Systems                                         | 3        |

| 1.4.    | Fault Analyses of DC-based Power Systems                              | 5        |

| 1.5.    | Fault Protection Technologies for DC-based Power Systems              | 7        |

| 1.5.    | DC Solid-State Circuit Breakers                                       | 8        |

| 1.5.    | 2. Current Limiting Diodes                                            | 13       |

| 1.6.    | Aims and Objectives                                                   | 19       |

| 1.7.    | Outline of Thesis                                                     | 19       |

| 1.8.    | List of Publications                                                  | 20       |

| 1.9.    | References                                                            | 21       |

| Chapter | 2: Analyses of Voltage Source Converters DC Line-to-line Fault F 25   | Response |

| 2.1.    | Introduction                                                          | 25       |

| 2.2.    | DC Side Contributions                                                 | 27       |

| 2.2.    | 1. Diode Blocking Stage                                               | 28       |

| 2.2.2   | 2. Diode Conduction Stage                                             | 31       |

| 2.3.    | AC Side Contributions                                                 | 34       |

| 2.3.    | Phase Currents Under Steady-State Condition                           | 35       |

| 2.3.    | 2. Phase Currents Under Steady-State and Transient Condition          | 35       |

| 2.4.    | Combined AC and DC Side Contributions                                 | 38       |

| 2.4.    | DC-Link Voltage Considering Both AC and DC Side Contributions         | 39       |

| 2.4.2   | 2. Phase Currents Considering Both AC and DC Side Contributions       | 39       |

| 2.4.    | 3. Fault Branch Current Considering Both AC and DC Side Contributions | 44       |

| 2.4.    | 4. Capacitor Branch Current Considering AC and DC Side Contributions  | 44       |

| 2.4.    | 5. Diodes Currents Considering AC and DC Side Contributions           | 44       |

| 2.5.    | Simulation Validation of Short-Circuit Fault Analyses                 | 45       |

| 2.5.    | 1. Extraction of Fault Impedance Parameters Error! Bookmark not       | defined. |

| 2.5.    | 2. Extraction of Diodes SPICE Parameters                              | 49       |

| 2.5.    | 3. Simulation Analyses of DC Side Contributions                       | 50       |

| 2.5.4   | 4. Simulation Analysis of AC Side Contributions                       | 55       |

| 2.5.5<br>Contributions |                                                                                        | and DC Side |

|------------------------|----------------------------------------------------------------------------------------|-------------|

| 2.5.6                  | 5. Diodes Temperatures Rise                                                            | 79          |

| 2.6.                   | Conclusions                                                                            | 85          |

| 2.7.                   | References                                                                             | 87          |

| _                      | 3: Experimental Validation of Voltage Source Converters' le Fault Response Analyses    |             |

| 3.1.                   | •                                                                                      |             |

|                        | Introduction                                                                           |             |

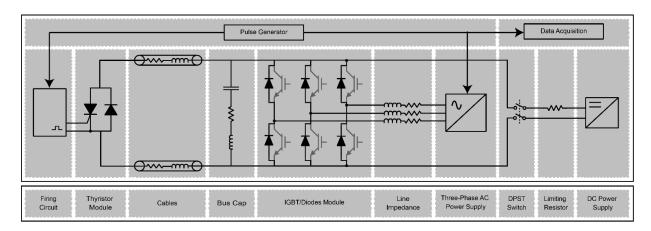

| 3.2.                   | Experiment Setup Components                                                            |             |

| 3.2.1                  |                                                                                        |             |

| 3.2.2                  |                                                                                        |             |

| 3.2.3                  | 1                                                                                      |             |

| 3.2.4                  |                                                                                        |             |

| 3.2.5                  |                                                                                        |             |

| 3.2.6                  | 1                                                                                      |             |

| 3.2.7                  |                                                                                        |             |

| 3.3.                   | Experiment Results                                                                     |             |

| 3.3.1                  |                                                                                        |             |

| 3.3.2                  |                                                                                        |             |

| 3.3.3                  | •                                                                                      |             |

| 3.4.                   | Conclusions                                                                            |             |

| 3.5.                   | References                                                                             |             |

| -                      | 4: DC Short-Circuit Fault Protection of Power Converters Ubide Current Limiting Diodes | 0           |

| 4.1.                   | Introduction                                                                           | 127         |

| 4.2.                   | Physics-based Silicon Carbide Current Limiting Diode Model                             | 129         |

| 4.2.1                  | . Current Limiting Diode's Model Derivation                                            | 131         |

| 4.2.2                  | Current Limiting Diode Model Implementation                                            | 135         |

| 4.3.                   | Analyses of Current Limiting Diodes' Fault Response                                    | 138         |

| 4.3.1                  | . Fault Response Under Isothermal Condition                                            | 139         |

| 4.3.2                  | 2. Fault Response Under Thermal Condition                                              | 144         |

| 4.4.                   | Simulation Validation                                                                  | 146         |

| 4.4.1                  | . Isothermal Condition                                                                 | 146         |

| 442                    | Thermal Condition                                                                      | 151         |

| 4.5. Conclusions                                                          | 161  |

|---------------------------------------------------------------------------|------|

| 4.6. References                                                           | 162  |

| Chapter 5: Silicon Carbide Current Limiting Diode Demonstrator for Sh     | ort- |

| Circuit Protection of Power Converters                                    | 163  |

| 5.1. Introduction                                                         | 163  |

| 5.2. Design                                                               | 165  |

| 5.2.1. Components Selection                                               | 165  |

| 5.2.2. Performance Analyses                                               | 169  |

| 5.3. Construction                                                         | 180  |

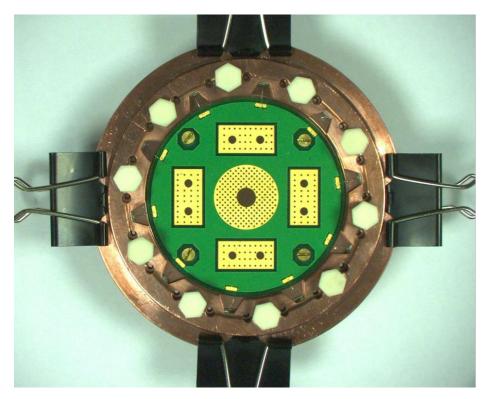

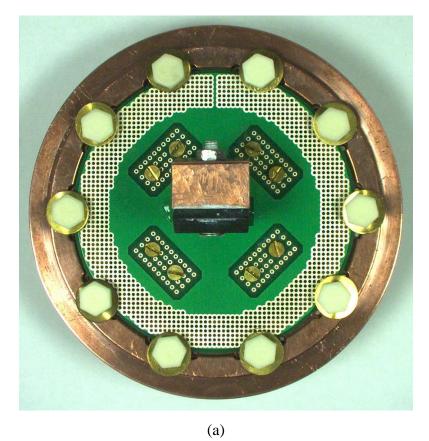

| 5.3.1. Built Components                                                   | 180  |

| 5.3.2. Current Limiter Assembly                                           | 183  |

| 5.4. Current Limiter Testing                                              | 186  |

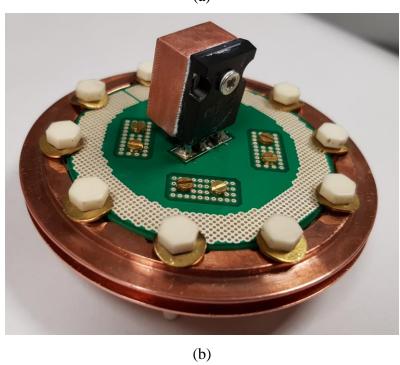

| 5.4.1. Experiment Setup                                                   | 186  |

| 5.4.2. Test Result                                                        | 193  |

| 5.5. Conclusions                                                          | 197  |

| 5.6. References                                                           | 198  |

| Chapter 6: An Integrated Current Limiting Diode for Extended Operation    | 200  |

| 6.1. Introduction                                                         | 200  |

| 6.2. Design                                                               | 202  |

| 6.2.1. Components Selection                                               | 202  |

| 6.2.2. Performance Analyses                                               | 211  |

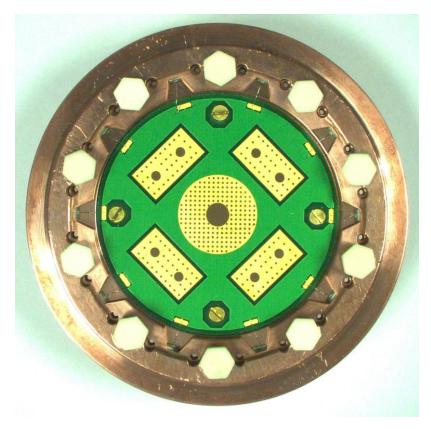

| 6.3. Fabrication                                                          | 214  |

| 6.3.1. Components                                                         | 214  |

| 6.3.2. Assembly                                                           | 218  |

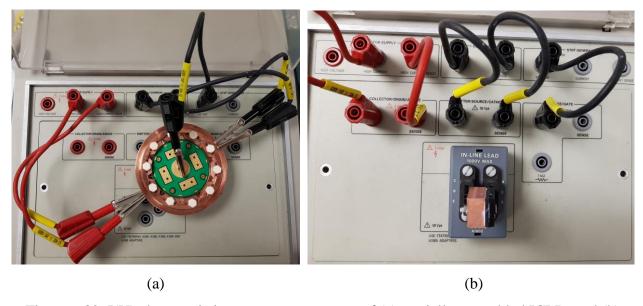

| 6.4. Testing                                                              | 224  |

| 6.5. Testing of Partially Assembled ICLD                                  | 224  |

| 6.6. Testing of Fully Assembled ICLD                                      | 225  |

| 6.7. Summary and Conclusions                                              | 227  |

| Chapter 7: Contributions and Future Work                                  | 228  |

| Appendix A: MATLAB Instrument Control Toolbox Power Supply Setup Trigger  |      |

| Appendix B: Silicon Carbide Junction Field Effect Transistor SPICE Models | 233  |

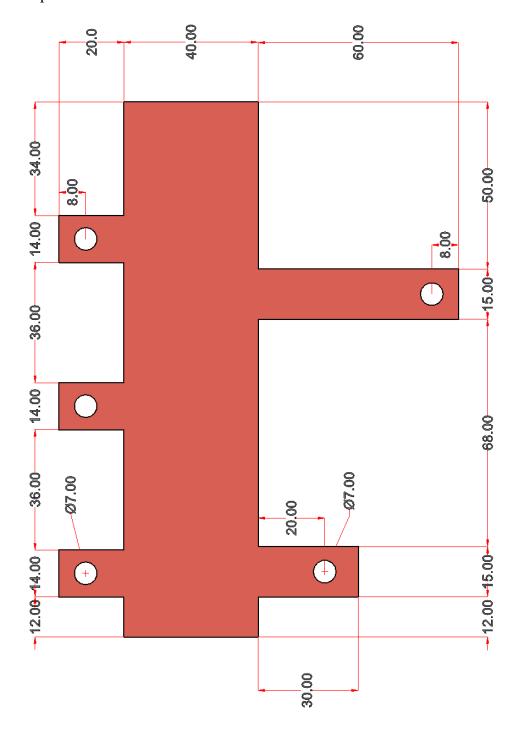

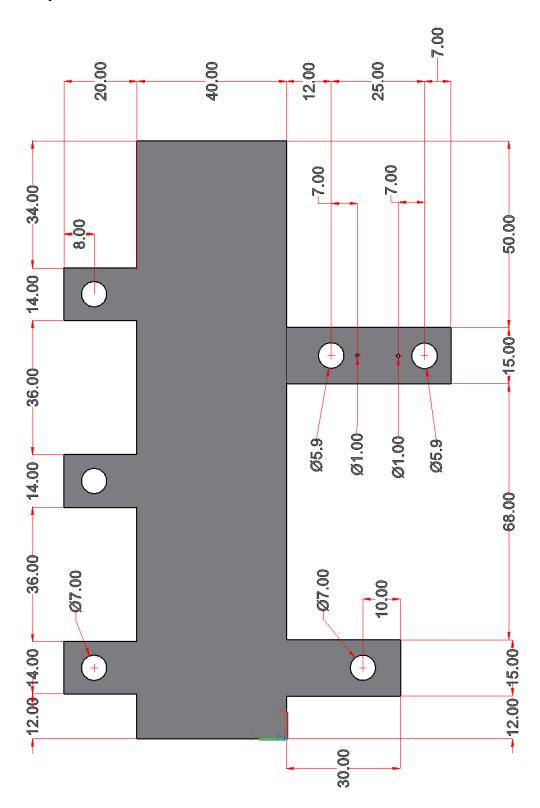

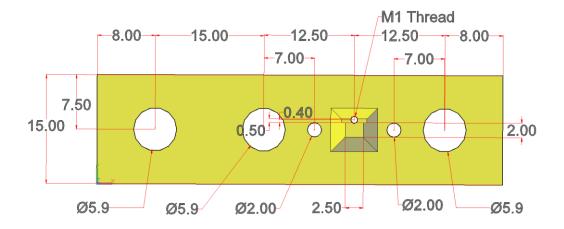

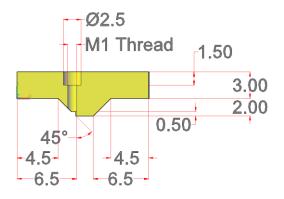

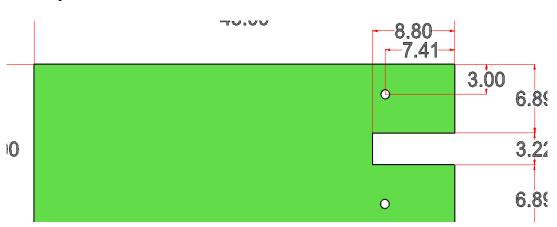

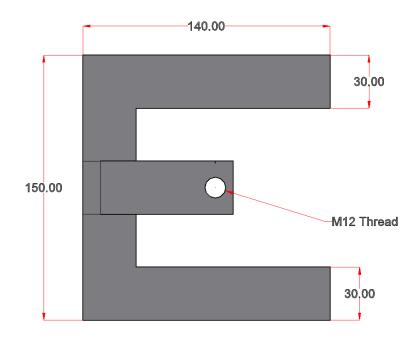

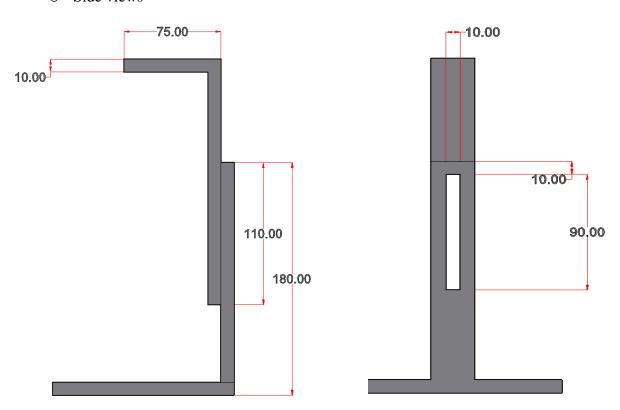

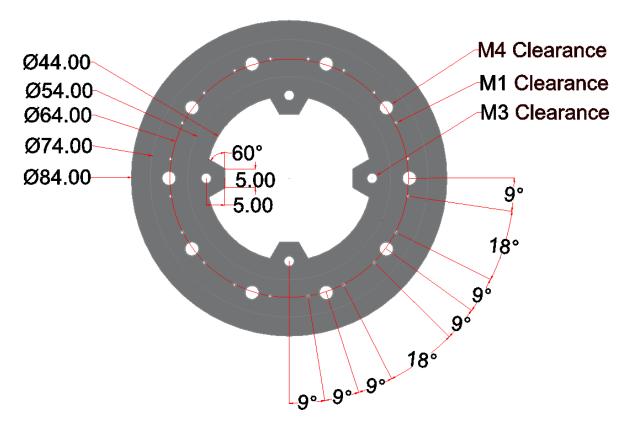

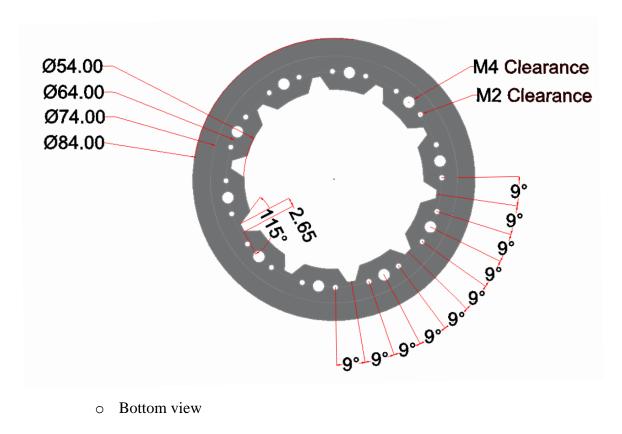

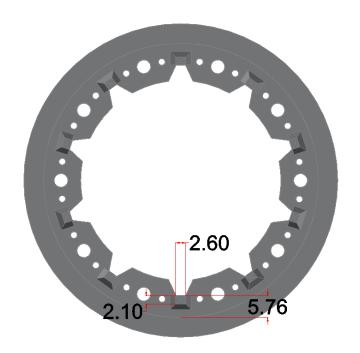

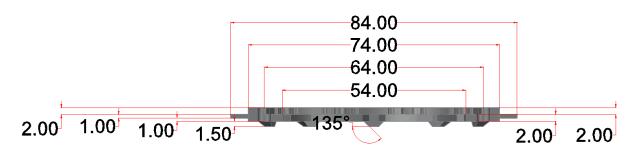

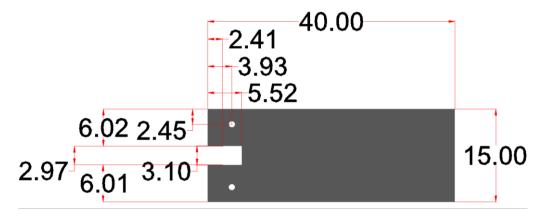

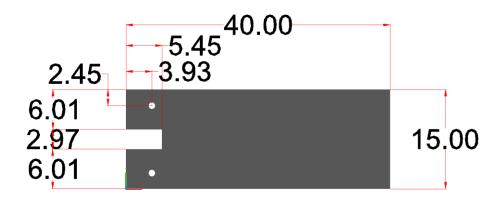

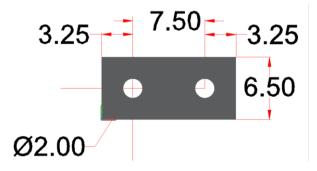

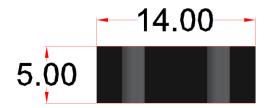

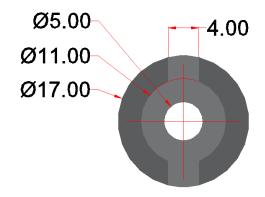

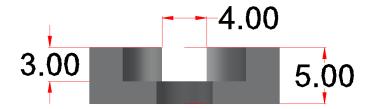

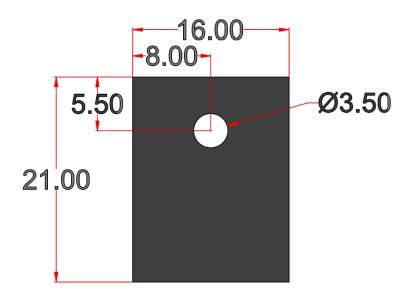

| Appendix C: Dimensions of Manufactured CLD Testing Parts (in mm)          | 237  |

# **List of Figures**

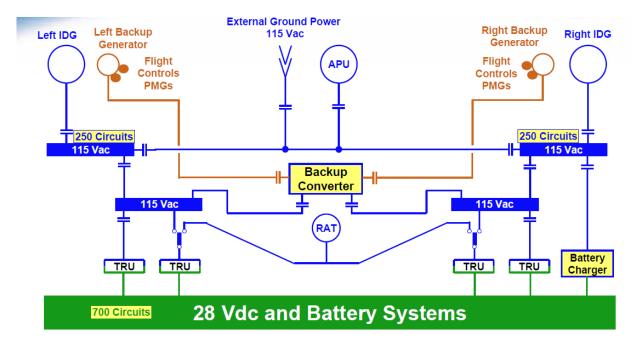

| FIGURE 1.1: ELECTRICAL SYSTEM ARCHITECTURE OF BOEING 777 [5]                                  | 4          |

|-----------------------------------------------------------------------------------------------|------------|

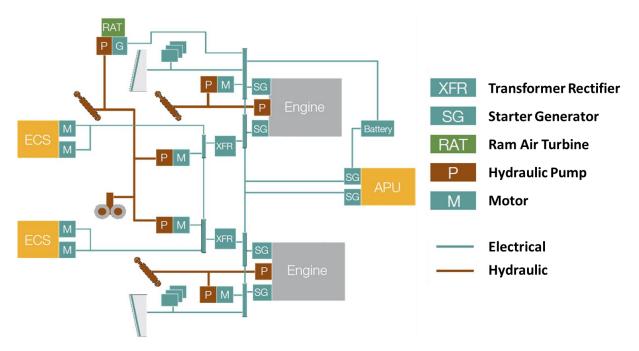

| FIGURE 1.2: SYSTEM ARCHITECTURE OF BOEING 787 DREAMLINER, SIMPLIFIED FROM [7]                 | 5          |

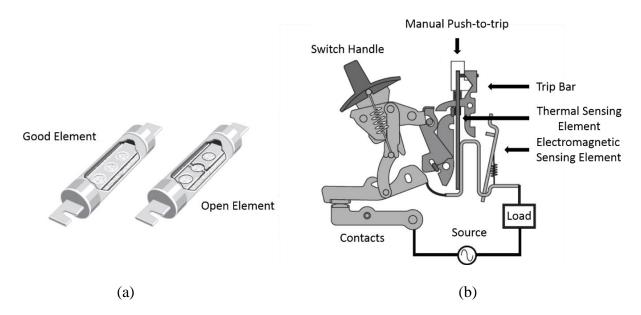

| FIGURE 1.3: (A) TYPICAL FUSE AND (B) CIRCUIT BREAKER STRUCTURES [24]                          | 7          |

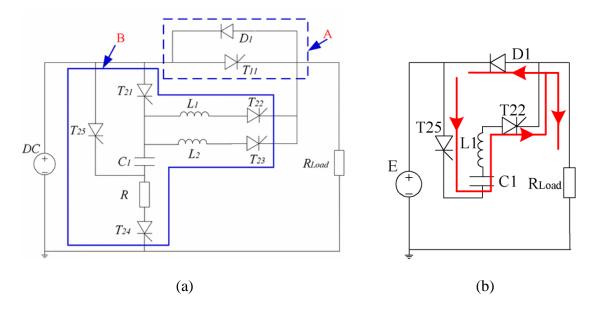

| FIGURE 1.4: (A) THYRISTOR BASED SSCB TOPOLOGY WITH RESONANCE, AND (B) ITS EQUIVALE            | ENT        |

| CIRCUIT DURING TURN-OFF [26, 27]                                                              | 9          |

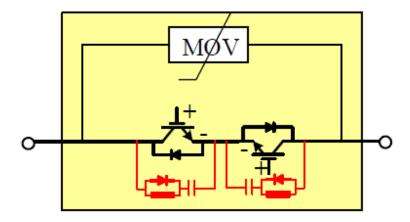

| FIGURE 1.5: BIDIRECTIONAL IGBT BASED SCCB TOPOLOGY WITH MOV AND SNUBBERS [28]                 | 10         |

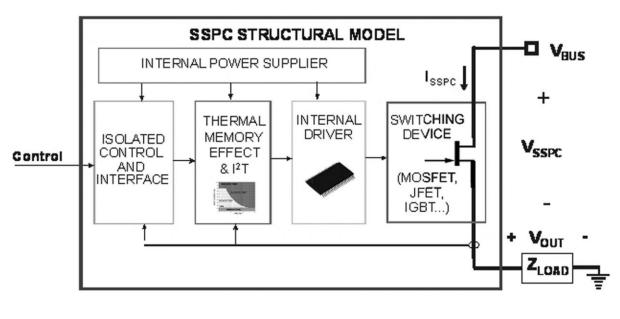

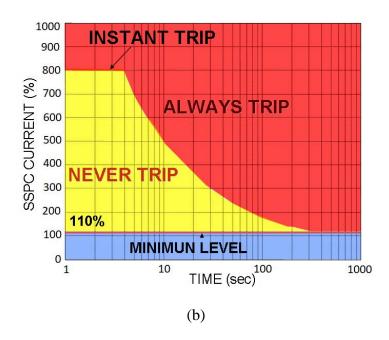

| FIGURE 1.6: (A) TYPICAL SSPC MODEL, AND (B) I <sup>2</sup> T BASED TRIP CURVES [29, 30]       | 11         |

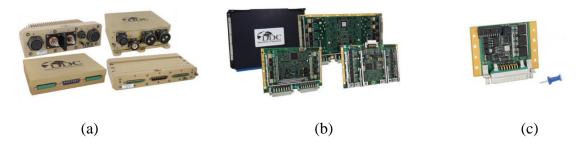

| FIGURE 1.7: COMMERCIAL SSPCS (A) POWER DISTRIBUTION UNITS (B) CARDS, AND (C) POINT-O          | F-         |

| LOAD MODULES [36]                                                                             | 11         |

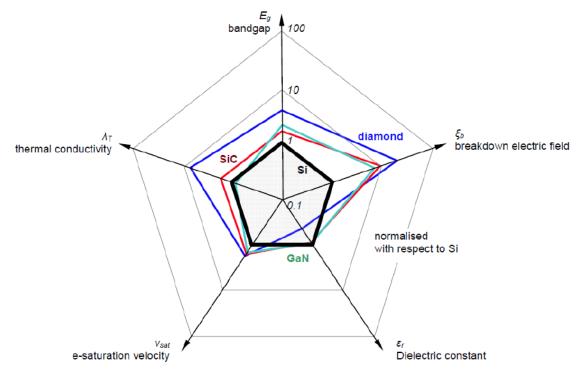

| FIGURE 1.8: NORMALIZED COMPARISON OF WIDE BAND-GAP MATERIALS' PROPERTIES                      |            |

| COMPARED WITH SILICON [37]                                                                    | 12         |

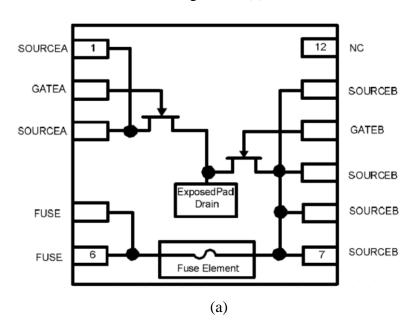

| FIGURE 1.9: (A) STRUCTURE OF REPORTED DEVICE [52], (B) SUGGESTED CONNECTION, AND (C)          |            |

| PACKAGE [53]                                                                                  | 15         |

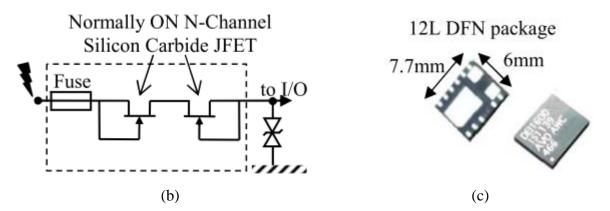

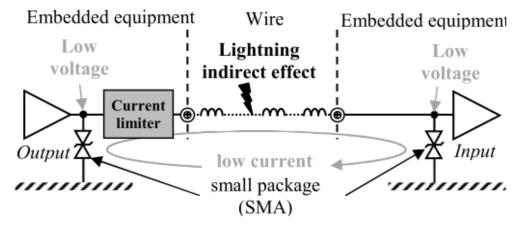

| FIGURE 1.10: LOCATION OF CLD IN THE SYSTEM ON LINES CONNECTING EMBEDDED EQUIPMEN              | NT         |

| [53]                                                                                          | 15         |

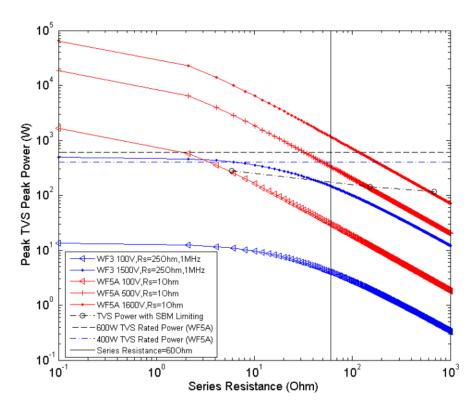

| FIGURE 1.11: REQUIRED TVS POWER RATING VS. SERIES RESISTANCE UNDER FAULT CONDITIO             | N          |

| [51]                                                                                          | 16         |

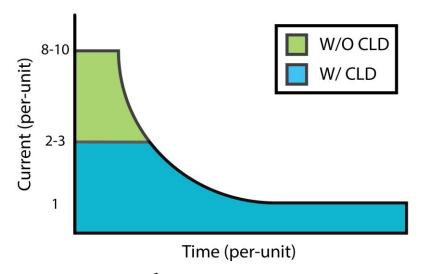

| FIGURE 1.12: EXPECTED POWER SYSTEM I <sup>2</sup> T CURVES WITH AND WITHOUT A CLD (FROM ROLLS | <b>3</b> - |

| ROYCE PLC)                                                                                    | 17         |

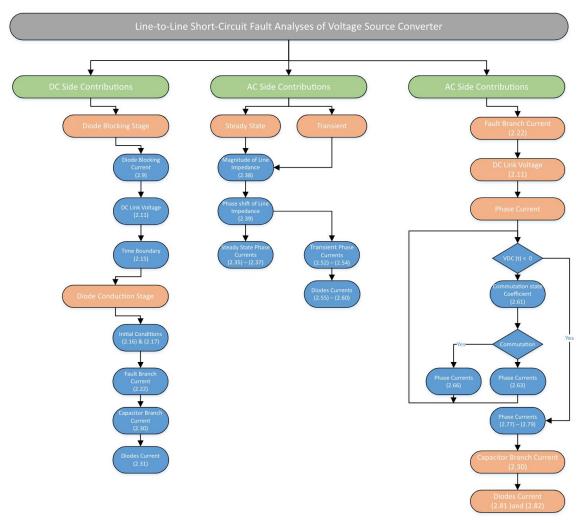

| FIGURE 2.1: FAULT RESPONSE CALCULATIONS FLOWCHART                                             | 27         |

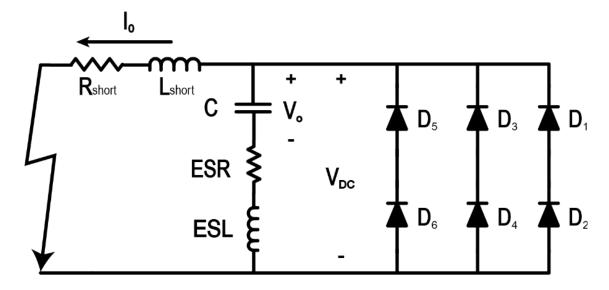

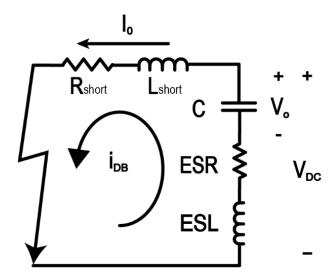

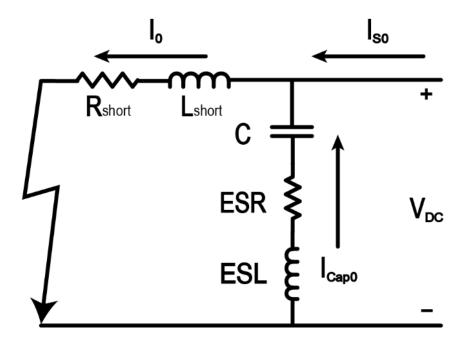

| FIGURE 2.2: EQUIVALENT CIRCUIT OF CONVERTER DUE TO DC SIDE FAULT CONTRIBUTION                 | 28         |

| FIGURE 2.3: EQUIVALENT CIRCUIT DURING DIODE BLOCKING STAGE                                    | 29         |

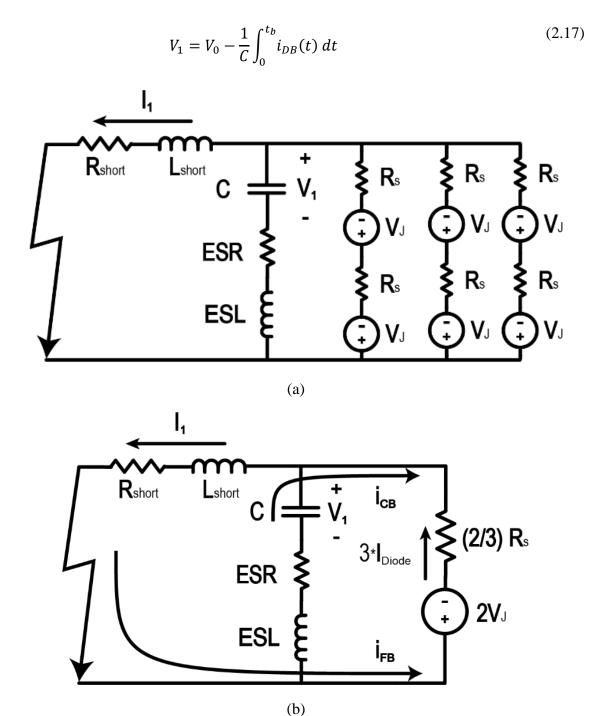

| FIGURE 2.4: (A) EQUIVALENT CIRCUIT DURING DIODE CONDUCTION STAGE, AND (B) FURTHER             |            |

| SIMPLIFIED CIRCUIT                                                                            | 32         |

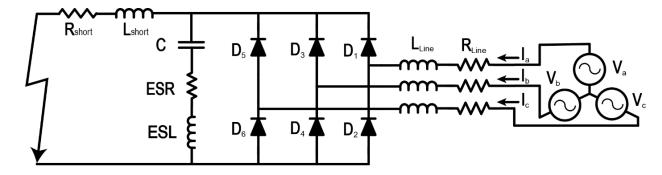

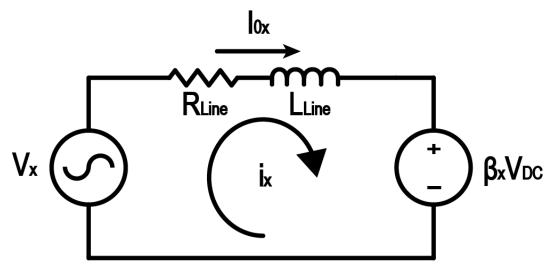

| FIGURE 2.5: SCHEMATIC OF EQUIVALENT AC SIDE CONTRIBUTION CIRCUIT                              | 35         |

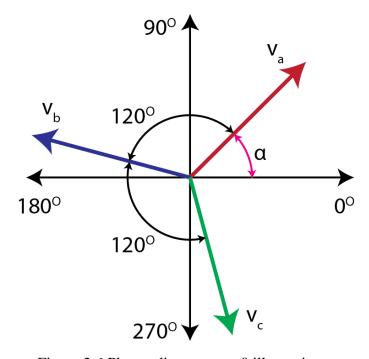

| FIGURE 2.6:PHASOR DIAGRAM AT T=0 ILLUSTRATING A                                               | 36         |

| FIGURE 2.7: ILLUSTRATION OF INITIAL CURRENTS ON DC SIDE ACCOUNTING FOR RECTIFIED A            | .C         |

| SIDE CURRENT                                                                                  | 39         |

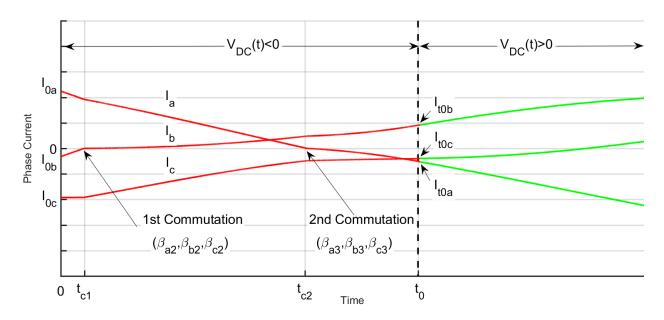

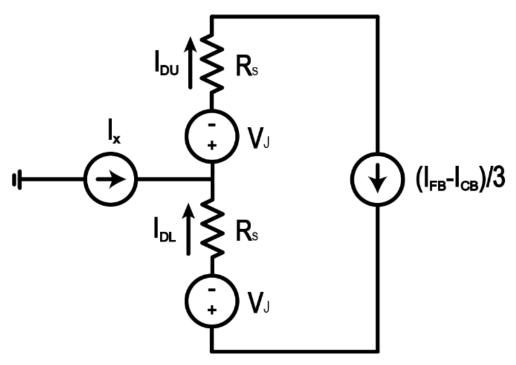

| FIGURE 2.8: EQUIVALENT CIRCUIT DURING PHASE CURRENTS TRANSITION STAGE                         | 40         |

| FIGURE 2.9: ILLISTARTION OF PHASE CURRENT COMMUTATION STAGES                                  | 40         |

| FIGURE 2.10: EQUIVALENT DIODE CONDUCTION CIRCUIT ACCOUNTING FOR BOTH AC AND DC                |    |

|-----------------------------------------------------------------------------------------------|----|

| SIDE CONTRIBUTIONS                                                                            | 45 |

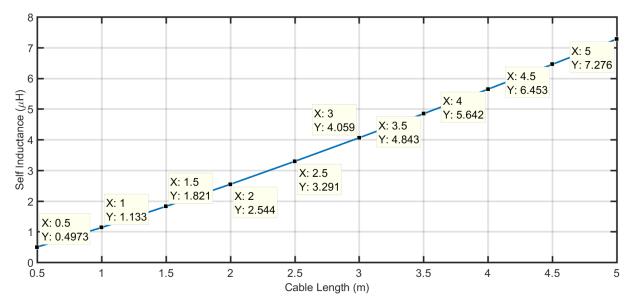

| FIGURE 2.11: SELF-INDUCTANCE VS. CABLE LENGTH FOR 2 AWG CABLE                                 | 48 |

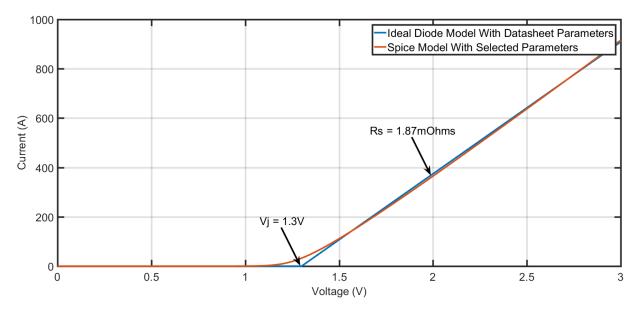

| FIGURE 2.12: IDEAL DIODE WITH DATASHEET PARAMETERS VS. SPICE DIODE WITH SELECTED              |    |

| PARAMETERS                                                                                    | 49 |

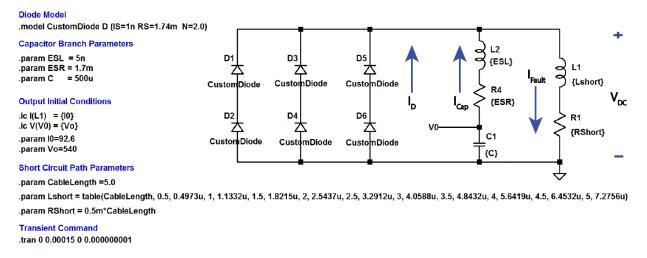

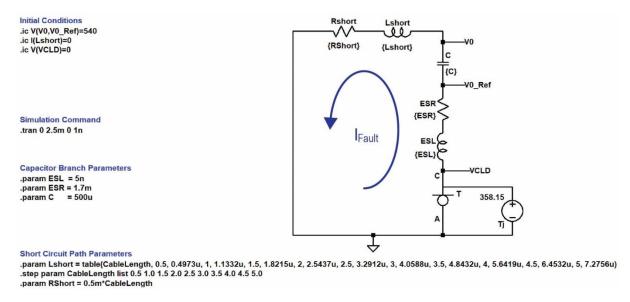

| FIGURE 2.13: SCHEMATIC OF DC SIDE CONTRIBUTIONS SIMULATION CIRCUIT                            | 50 |

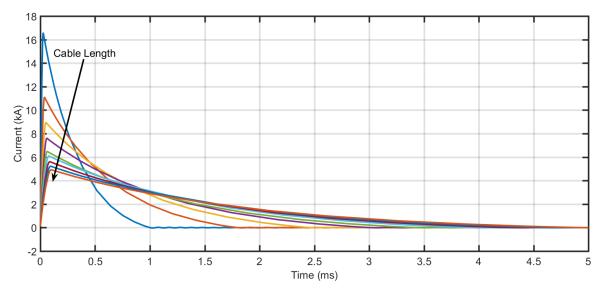

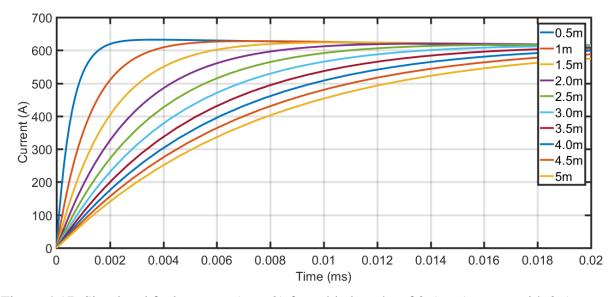

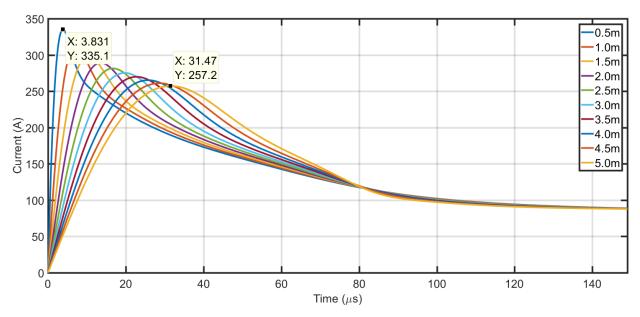

| FIGURE 2.14: SIMULATED FAULT CURRENT ( $\it IFault$ ) FOR 0.5M-5M CABLE FAULT WITH 0.5M STEPS | 51 |

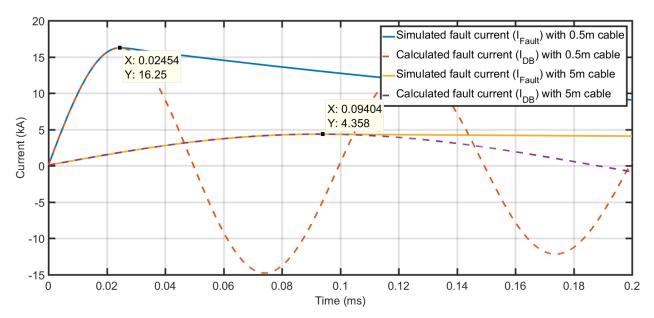

| FIGURE 2.15: COMPARISON OF SIMULATED AND CALCULATED FAULT CURRENT ( $I_{FAULT}$ ) DURING      |    |

| DIODE BLOCKING STAGE                                                                          | 52 |

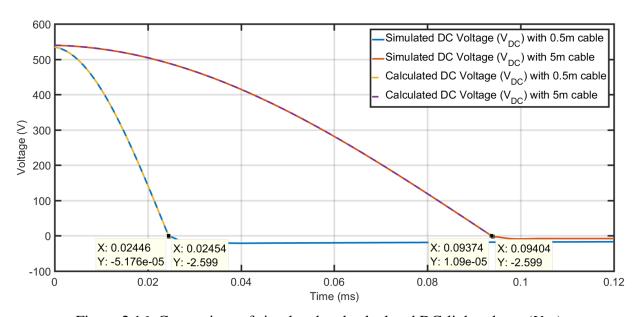

| FIGURE 2.16: COMPARISON OF SIMULATED AND CALCULATED DC-LINK VOLTAGE $(V_{DC})$                | 52 |

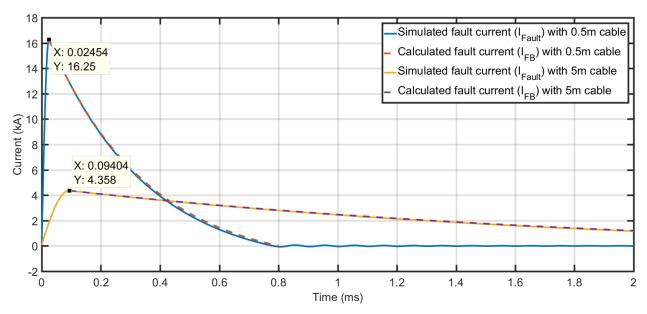

| FIGURE 2.17: COMPARISON OF SIMULATED AND CALCULATED FAULT BRANCH CURRENT DURIN                | G  |

| DIODE CONDUCTION STAGE                                                                        | 53 |

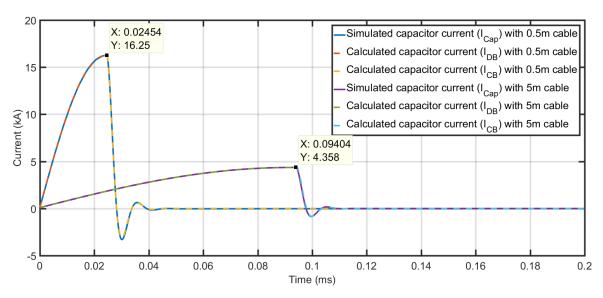

| FIGURE 2.18: COMPARISON OF SIMULATED AND CALCULATED CAPACITOR BRANCH CURRENT                  |    |

| DURING DIODE CONDUCTION AND BLOCKING STAGES                                                   | 54 |

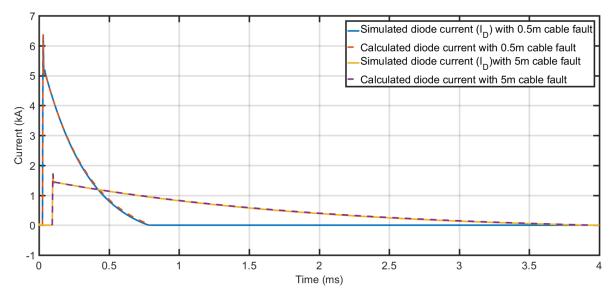

| FIGURE 2.19: COMPARISON OF SIMULATED AND CALCULATED DIODES CURRENT DURING DIODE               | Ĺ  |

| CONDUCTION STAGE                                                                              | 54 |

| FIGURE 2.20: COMPARISON OF SIMULATED AND CALCULATED DIODE CURRENT DURING DIODE                |    |

| CONDUCTION STAGE (ENLARGED)                                                                   | 55 |

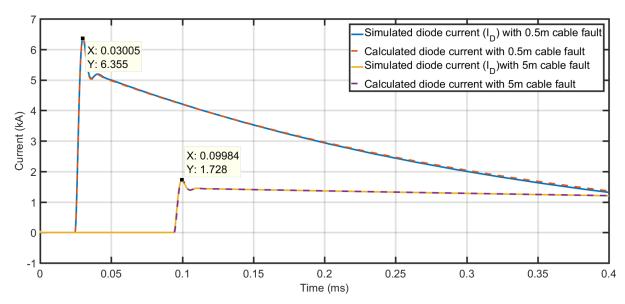

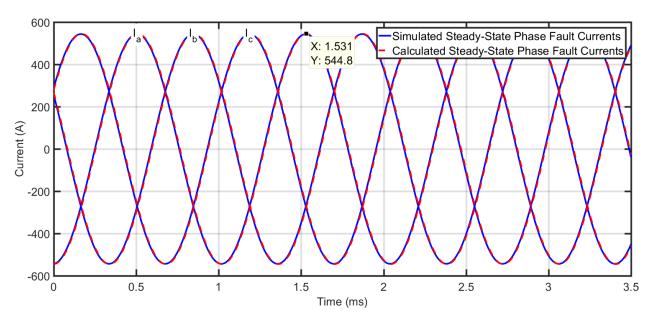

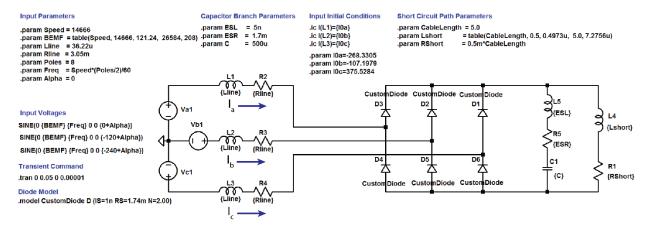

| FIGURE 2.21: STEADY-STATE RESPONSE SIMULATION CIRCUIT SHOWING 26,584RPM (MAX SPEED            | )  |

| AND 0.5M CABLE FAULT CASE                                                                     | 56 |

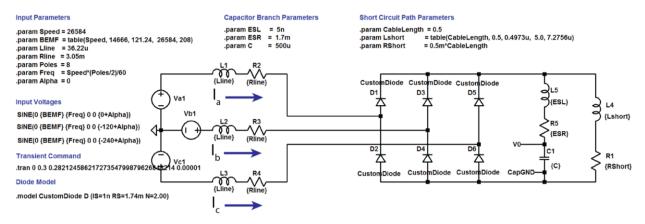

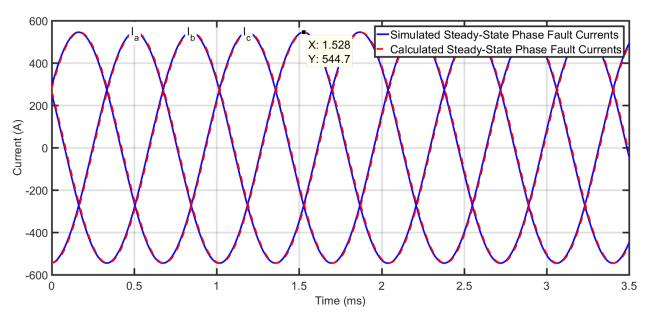

| FIGURE 2.22: COMPARISON OF SIMULATED AND CALCULATED STEADY-STATE PHASE CURRENTS               | 3  |

| FOR 0.5M CABLE FAULT AT IDLE SPEED                                                            | 56 |

| FIGURE 2.23: COMPARISON OF SIMULATED AND CALCULATED STEADY-STATE PHASE CURRENT                |    |

| FOR 5M CABLE FAULT AT IDLE SPEED                                                              | 57 |

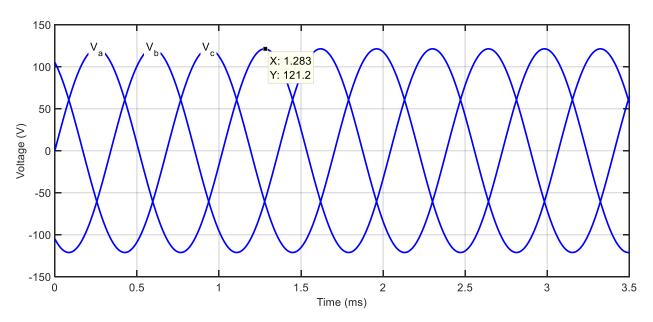

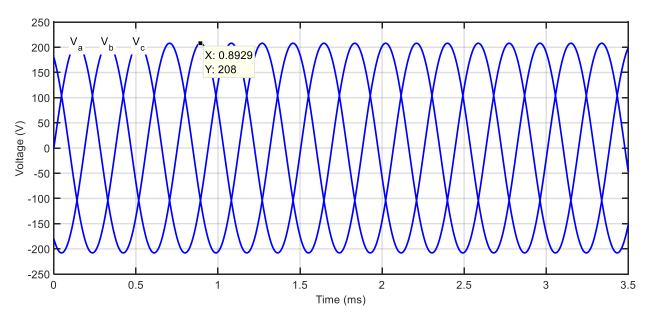

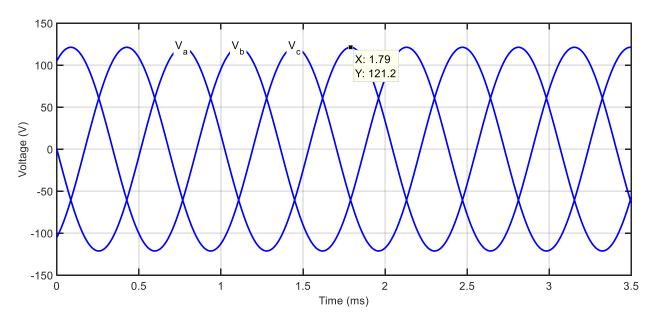

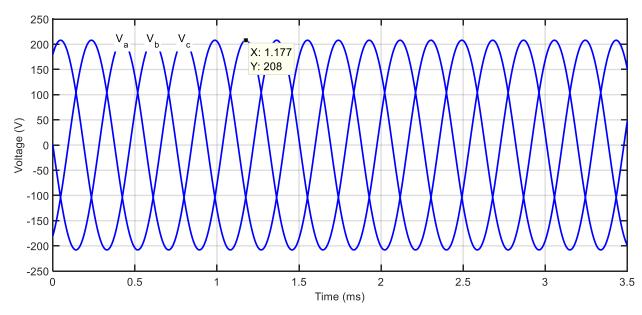

| FIGURE 2.24: PHASE VOLTAGES AT IDLE SPEED AND $A = 0^{\circ}$                                 | 57 |

| FIGURE 2.25: COMPARISON OF SIMULATED AND CALCULATED STEADY-STATE PHASE CURRENTS               | 3  |

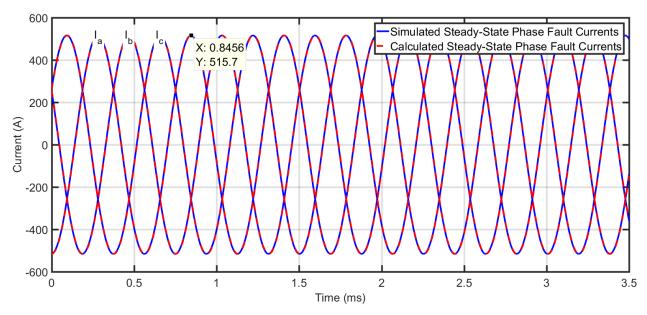

| FOR 0.5M CABLE FAULT AT MAX SPEED                                                             | 58 |

| FIGURE 2.26: COMPARISON OF SIMULATED AND CALCULATED STEADY STATE PHASE CURRENTS               | }  |

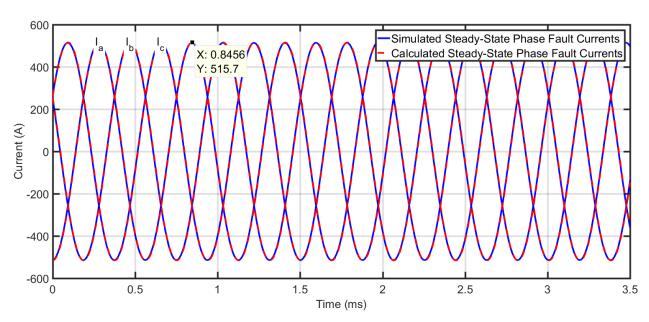

| FOR 5M CABLE FAULT AT MAX SPEED                                                               | 58 |

| FIGURE 2.27: PHASE VOLTAGES AT MAXIMUM SPEED AND $A = 0^{\circ}$                              | 59 |

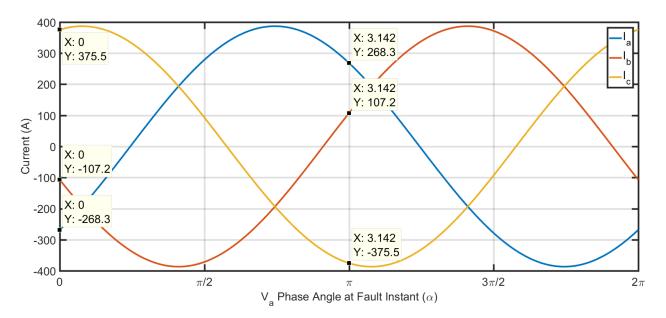

| FIGURE 2.28: INITIAL PHASE CURRENTS VS. A AT THE IDLE SPEED CONDITION                         | 60 |

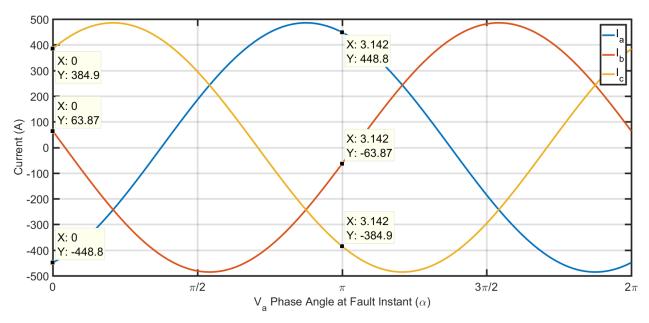

| FIGURE 2.29: INITIAL PHASE CURRENTS VS. A AT MAX SPEED CONDITION                              | 61 |

| FIGURE 2.30: AC COMPLETE RESPONSE SIMULATION CIRCUIT SHOWING IDLE SPEED, A=0, AND 51          | M  |

| CABLE FAULT CASE                                                                              | 61 |

| FIGURE 2.31: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS AT IDLE SPEED              | ١, |

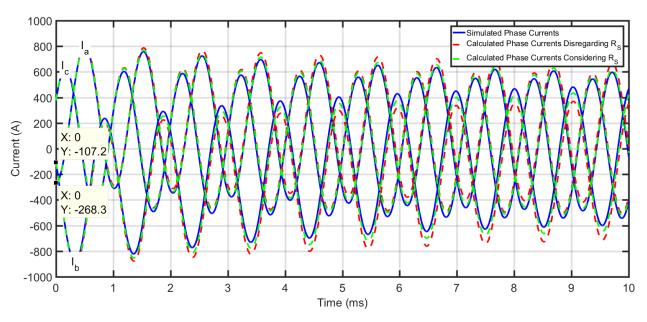

| $A=0$ . AND 0.5M CABLE FAULT, ALSO SHOWING REDUCED ERROR WHEN $R_S$ IS CONSIDERED.            | 62 |

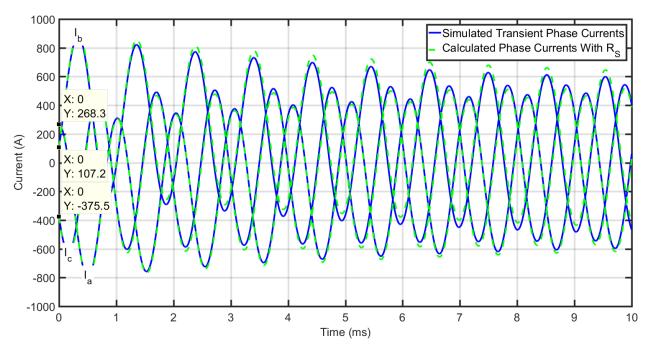

| FIGURE 2.32: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS AT IDLE SPEE                            | D,  |

|------------------------------------------------------------------------------------------------------------|-----|

| $A=\Pi$ , AND 0.5M CABLE FAULT                                                                             | 63  |

| FIGURE 2.33: PHASE VOLTAGES AT IDLE SPEED AND $A=\Pi$ CASE                                                 | 63  |

| FIGURE 2.34: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENT FOR $0.5\mathrm{M}$ CABL                 | LΕ  |

| FAULT AT MAX SPEED AND $A=0$                                                                               | 64  |

| FIGURE 2.35: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENT FOR $0.5 \mathrm{M}$ CABL                | LΕ  |

| FAULT AT MAX SPEED AND $A=\Pi$                                                                             | 64  |

| FIGURE 2.36: PHASE VOLTAGES AT MAX SPEED AND $A=\Pi$ CASE                                                  | 65  |

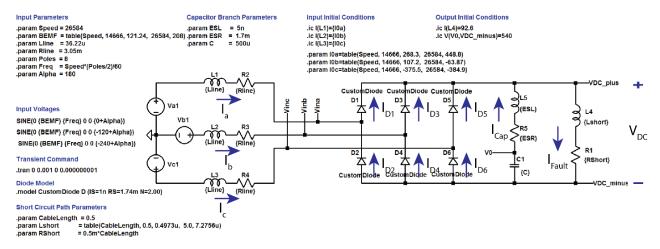

| FIGURE 2.37: COMBINED RESPONSE SIMULATION CIRCUIT (MAX SPEED CASE SHOWN)                                   | 65  |

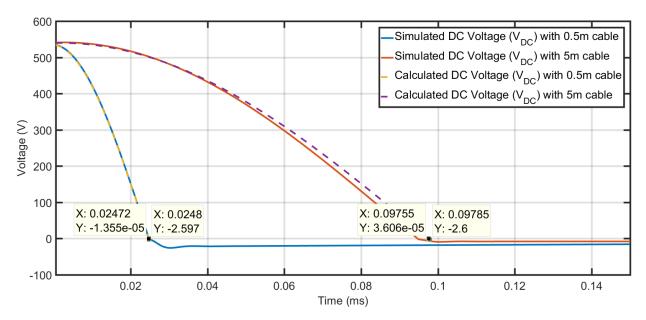

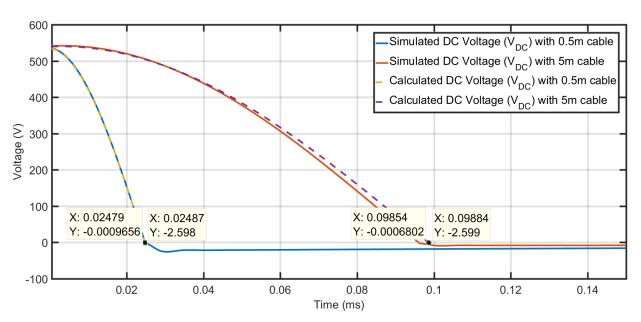

| FIGURE 2.38: COMPARISON OF SIMULATED AND CALCULATED DC-LINK VOLTAGE DURING A                               |     |

| FAULT AT IDLE SPEED OPERATION                                                                              | 66  |

| FIGURE 2.39: COMPARISON OF SIMULATED AND CALCULATED DC-LINK VOLTAGE DURING A                               |     |

| FAULT AT MAXIMUM SPEED OPERATION                                                                           | 67  |

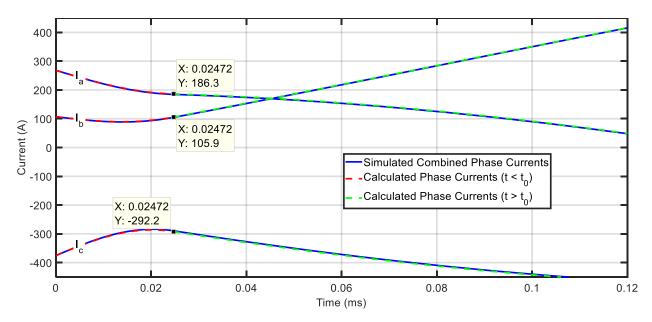

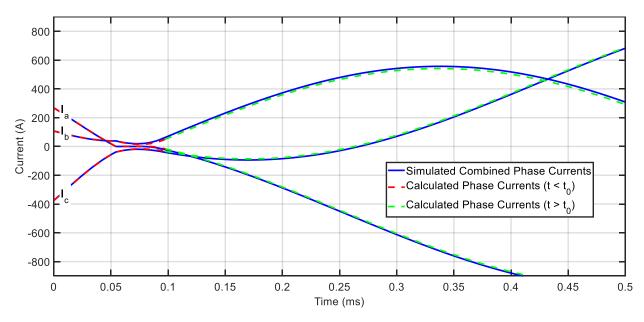

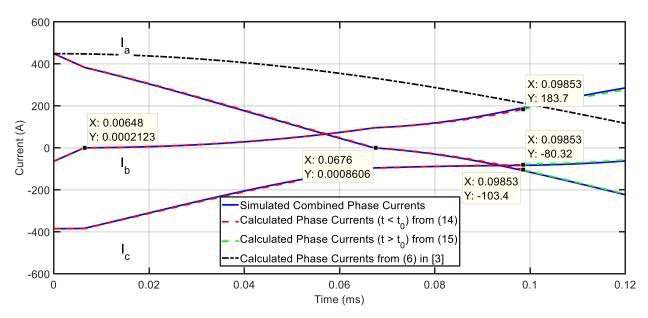

| FIGURE 2.40: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS ( $I_A$ , $I_B$ , AND $I_C$ )           |     |

| DURING A 0.5M CABLE FAULT AT IDLE SPEED OPERATION - ZOOMED                                                 | 68  |

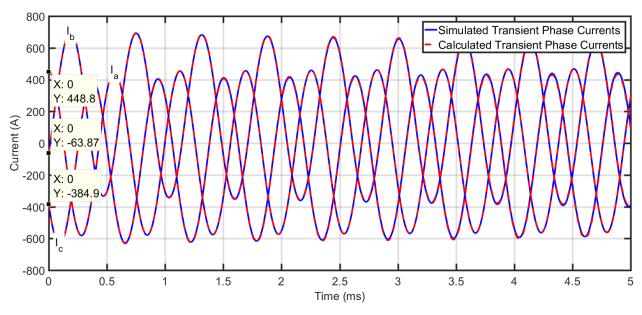

| FIGURE 2.41: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS ( $I_A$ , $I_B$ , AND $I_C$ )           |     |

| DURING A 0.5M CABLE FAULT AT IDLE SPEED OPERATION                                                          | 68  |

| FIGURE 2.42: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS ( $I_A$ , $I_B$ , AND $I_C$ )           |     |

| DURING A 5M CABLE FAULT AT IDLE SPEED OPERATION – ZOOMED                                                   | 69  |

| FIGURE 2.43: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS ( $I_A$ , $I_B$ , AND $I_C$ )           |     |

| DURING A 5M CABLE FAULT AT IDLE SPEED OPERATION                                                            | 69  |

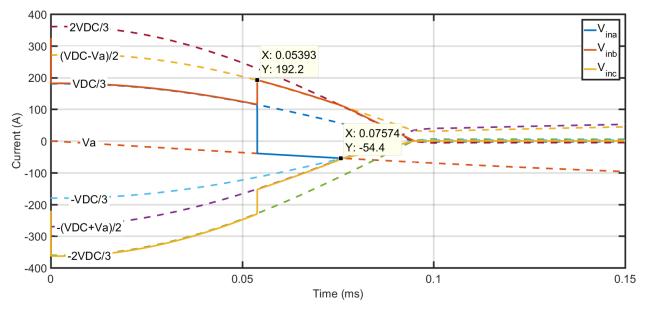

| FIGURE 2.44: SIMULATED PHASE VOLTAGES AT THE CONVERTER'S INPUT ( $V_{INA}$ , $V_{INB}$ , AND $V_{INC}$ ) F | OR  |

| A 5M CABLE FAULT AT IDLE SPEED OPERATION                                                                   | 70  |

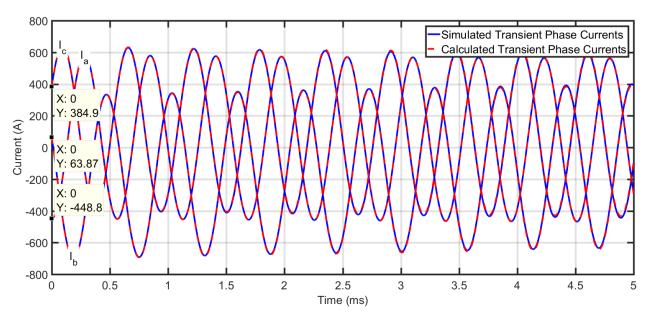

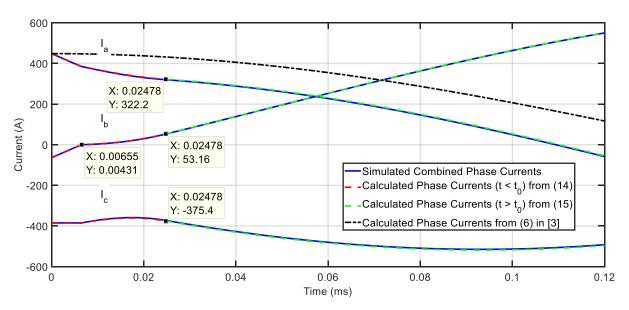

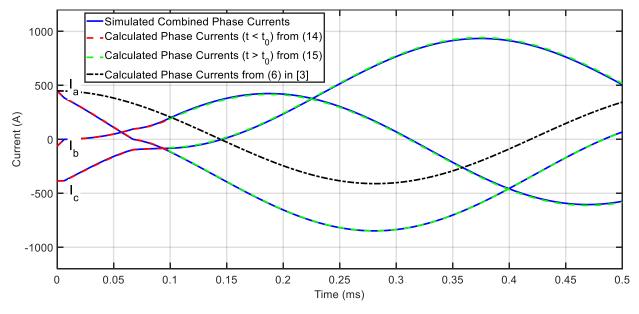

| FIGURE 2.45: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS $(I_A,I_B,\mathrm{AND}I_C)$             |     |

| DURING A 0.5M CABLE FAULT AT MAXIMUM SPEED OPERATION – ZOOMED                                              | 71  |

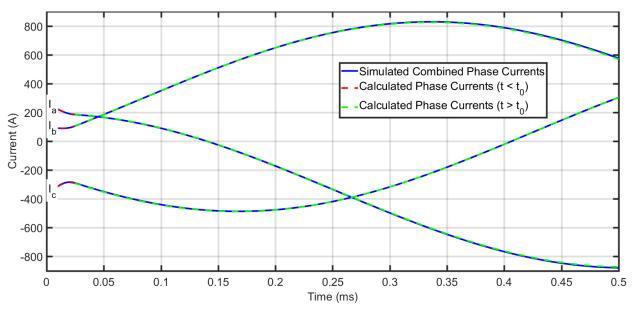

| FIGURE 2.46: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS ( $I_A$ , $I_B$ , AND $I_C$ )           |     |

| DURING A 0.5M CABLE FAULT AT MAXIMUM SPEED OPERATION                                                       | 71  |

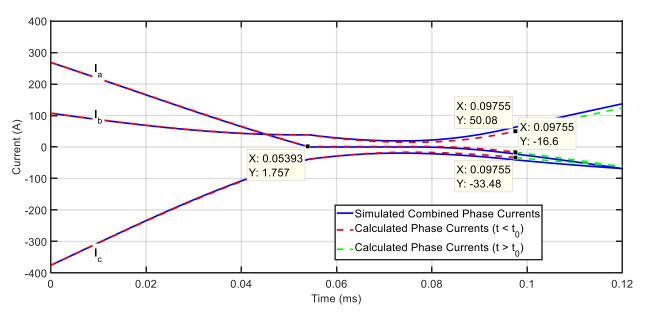

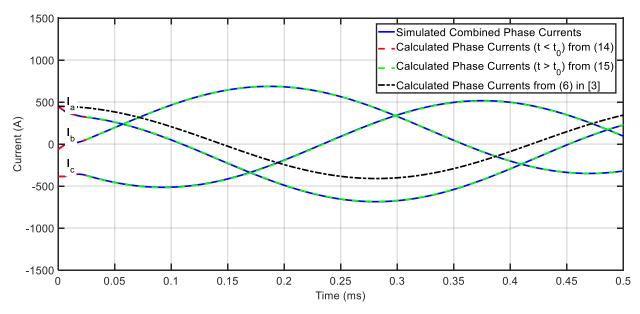

| FIGURE 2.47: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS $(I_A, I_B, \text{AND } I_C)$           |     |

| DURING A 5M CABLE FAULT AT MAXIMUM SPEED OPERATION – ZOOMED                                                | 72  |

| FIGURE 2.48: COMPARISON OF SIMULATED AND CALCULATED PHASE CURRENTS ( $I_A$ , $I_B$ , AND $I_C$ )           |     |

| DURING A 5M CABLE FAULT AT MAXIMUM SPEED OPERATION                                                         | 72  |

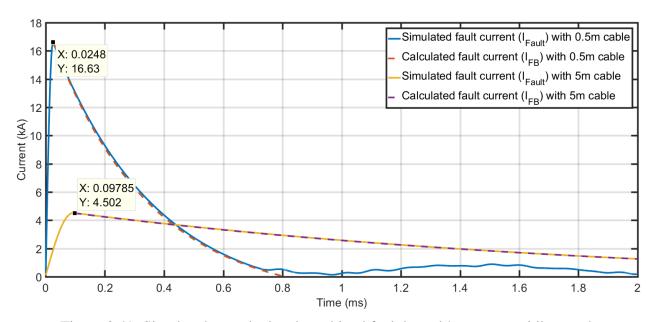

| FIGURE 2.49: SIMULATED VS. CALCULATED COMBINED FAULT BRANCH'S CURRENT AT IDLE                              |     |

| SPEED                                                                                                      | 73  |

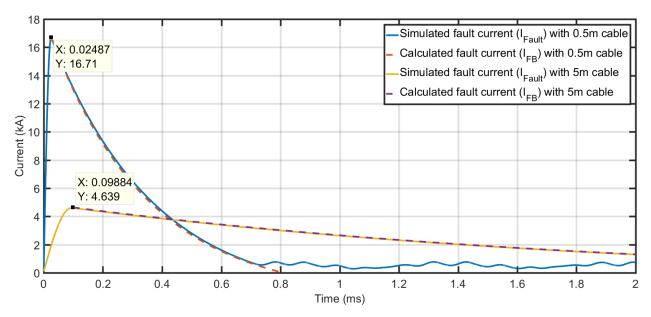

| FIGURE 2.50: SIMULATED VS. CALCULATED COMBINED FAULT BRANCH'S CURRENT AT                                   |     |

| MAXIMUM SPEED                                                                                              | 74  |

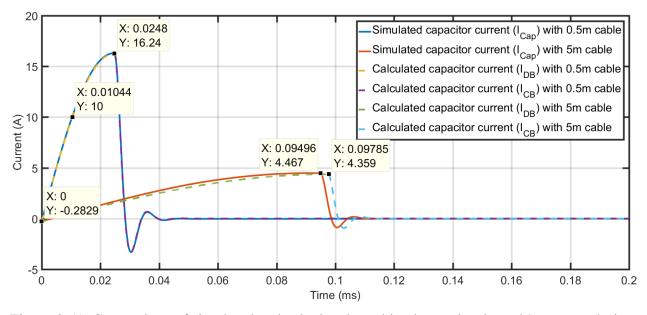

| FIGURE 2.51: COMPARISON OF SIMULATED AND CALCULATED COMBINED CAPACITOR BRANCH                              | ł'S |

| CURRENT DURING A FAULT AT IDLE SPEED OPERATION                                                             | 74  |

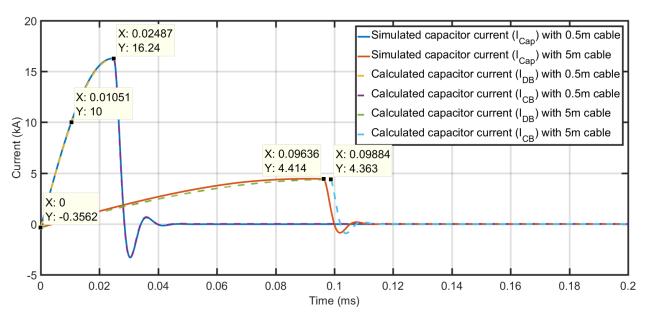

| FIGURE 2.52: COMPARISON OF SIMULATED AND CALCULATED COMBINED CAPACITOR BRANCI    | <b>1</b> ′S |

|----------------------------------------------------------------------------------|-------------|

| CURRENT DURING A FAULT AT MAXIMUM SPEED OPERATION                                | 75          |

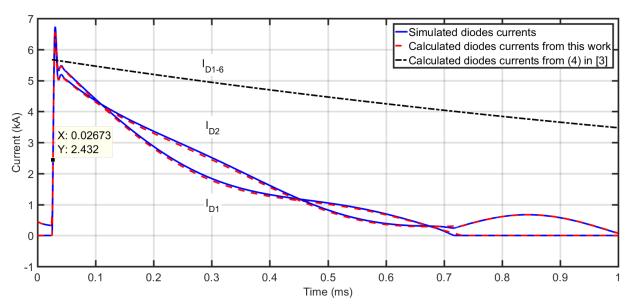

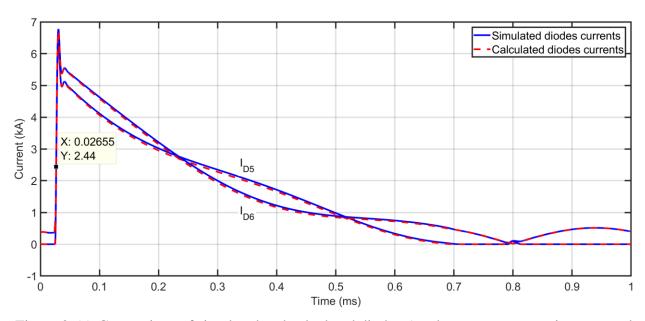

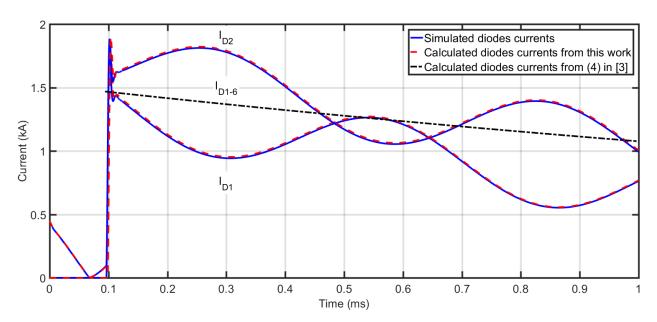

| FIGURE 2.53: COMPARISON OF SIMULATED AND CALCULATED DIODES 1 AND 2 CURRENTS AT   |             |

| MAXIMUM SPEED CONDITION WITH 0.5M CABLE FAULT                                    | 76          |

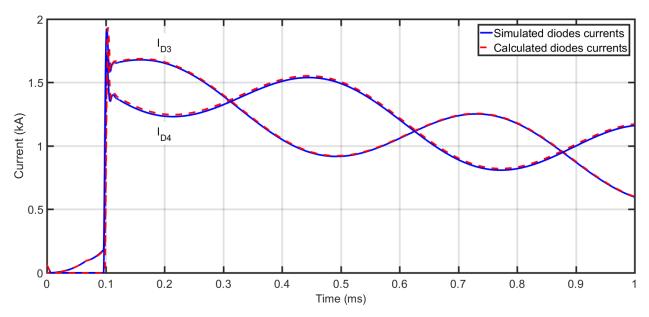

| FIGURE 2.54: COMPARISON OF SIMULATED AND CALCULATED DIODE 3 AND 4 CURRENTS AT    |             |

| MAXIMUM SPEED CONDITION WITH 0.5M CABLE FAULT                                    | 76          |

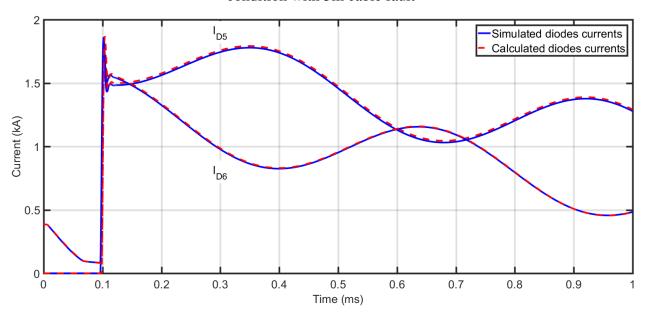

| FIGURE 2.55: COMPARISON OF SIMULATED AND CALCULATED DIODES 5 AND 6 CURRENTS AT   |             |

| MAXIMUM SPEED CONDITION WITH 0.5M CABLE FAULT                                    | 77          |

| FIGURE 2.56: COMPARISON OF SIMULATED AND CALCULATED DIODE 1 AND 2 CURRENTS AT    |             |

| MAXIMUM SPEED CONDITION WITH 5M CABLE FAULT                                      | 77          |

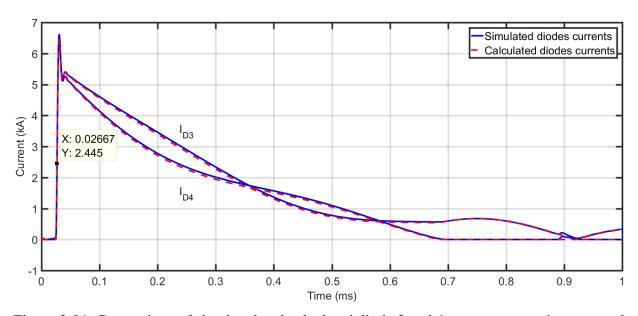

| FIGURE 2.57: COMPARISON OF SIMULATED AND CALCULATED DIODE 3 AND 4 CURRENTS AT    |             |

| MAXIMUM SPEED CONDITION WITH 5M CABLE FAULT                                      | 78          |

| FIGURE 2.58: COMPARISON OF SIMULATED AND CALCULATED DIODES 5 AND 6 CURRENTS AT   |             |

| MAXIMUM SPEED CONDITION WITH 5M CABLE FAULT                                      | 78          |

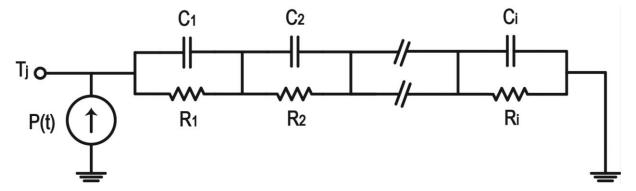

| FIGURE 2.59: ILLUSTRATION OF FOSTER EQUIVALENT THERMAL NETWORK                   | 80          |

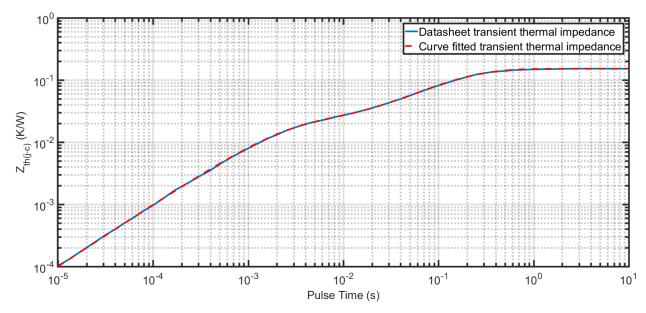

| FIGURE 2.60: COMPARISON OF DATASHEET THERMAL IMPEDANCE WITH THAT OBTAINED FROM   | M           |

| CURVE FITTING (2.98) USING PARAMETERS IN TABLE 2.4                               | 8           |

| FIGURE 2.61: DIODES JUNCTION TEMPERATURES RISE SIMULATION CIRCUIT (COMBINED      |             |

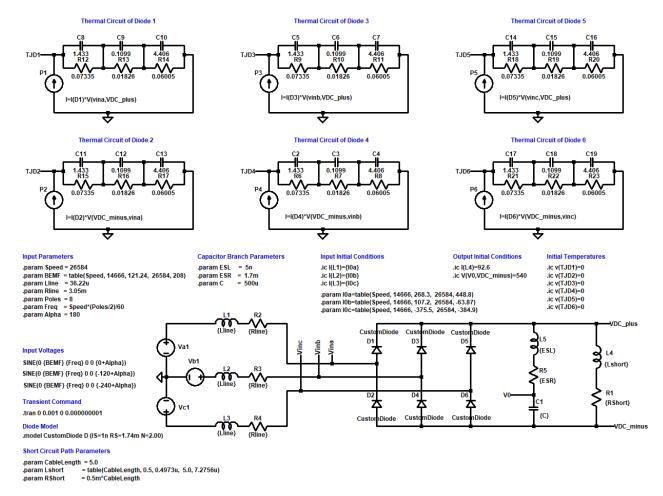

| RESPONSE AT MAXIMUM SPEED, 5M CABLE FAULT, AND $\alpha=\pi$ )                    | 82          |

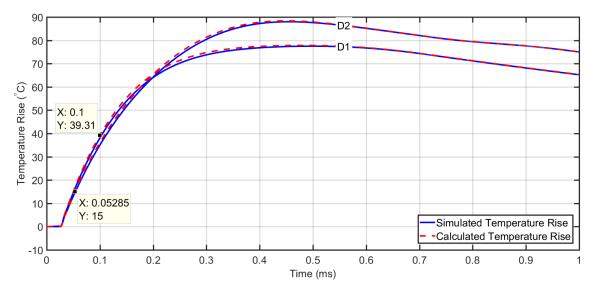

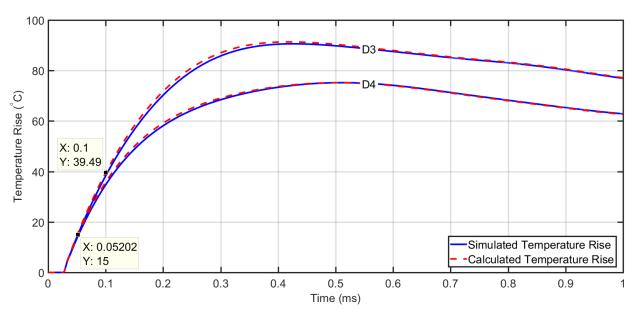

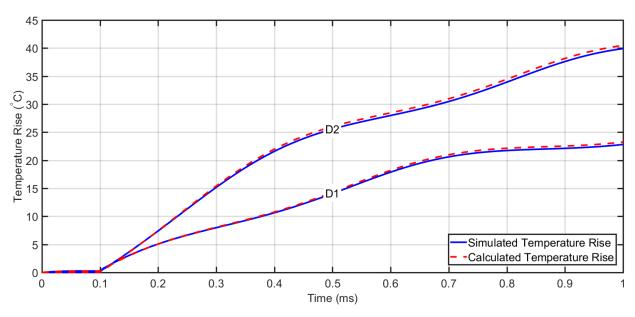

| FIGURE 2.62: COMPARISON OF SIMULATED AND CALCULATED D1 AND D2 TEMPERATURE RISE   |             |

| FOR A 0.5M CABLE FAULT AT MAXIMUM SPEED                                          | 82          |

| FIGURE 2.63: COMPARISON OF SIMULATED AND CALCULATED D3 AND D4 TEMPERATURE RISE   |             |

| FOR A 0.5M CABLE FAULT AT MAXIMUM SPEED                                          | 83          |

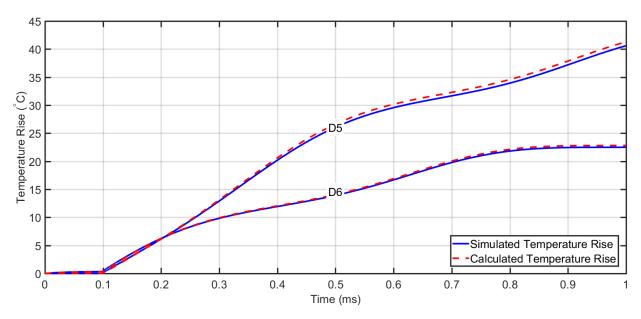

| FIGURE 2.64: COMPARISON OF SIMULATED AND CALCULATED D5 AND D6 TEMPERATURE RISE   |             |

| FOR A 0.5M CABLE FAULT AT MAXIMUM SPEED                                          | 83          |

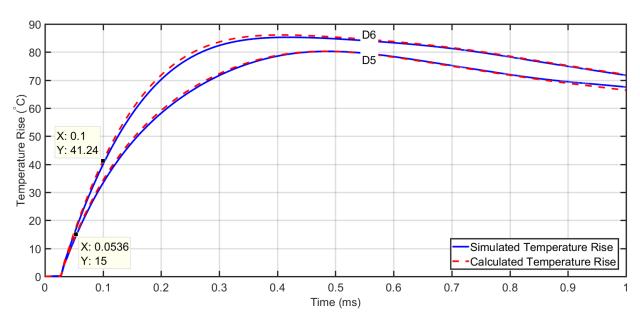

| FIGURE 2.65: COMPARISON OF SIMULATED AND CALCULATED D1 AND D2 TEMPERATURE RISE   |             |

| FOR A 5M CABLE FAULT AT MAXIMUM SPEED                                            | 84          |

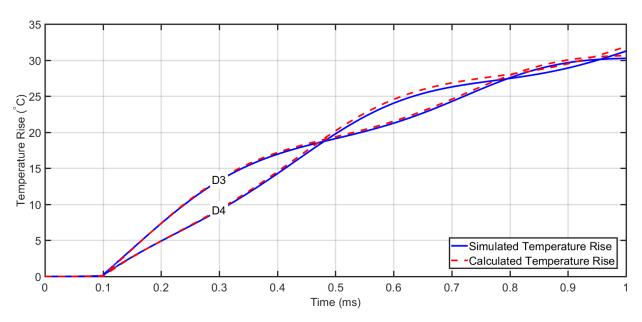

| FIGURE 2.66: COMPARISON OF SIMULATED AND CALCULATED D3 AND D4 TEMPERATURE RISE   |             |

| FOR A 5M CABLE FAULT AT MAXIMUM SPEED                                            | 84          |

| FIGURE 2.67: COMPARISON OF SIMULATED AND CALCULATED D5 AND D6 TEMPERATURE RISE   |             |

| FOR A 5M CABLE FAULT AT MAXIMUM SPEED                                            | 85          |

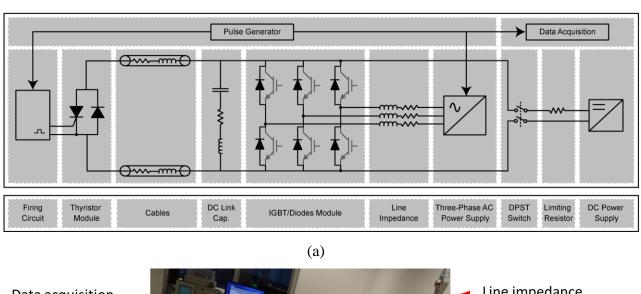

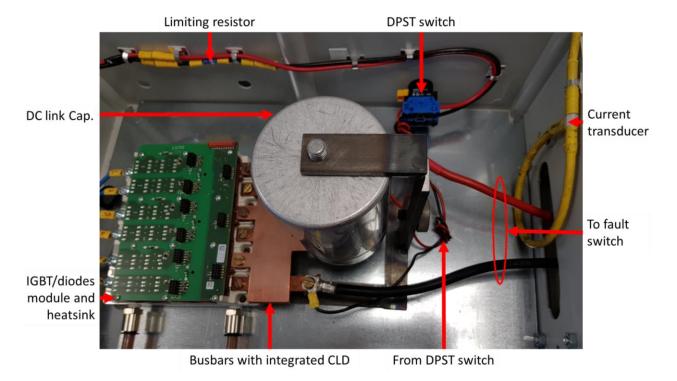

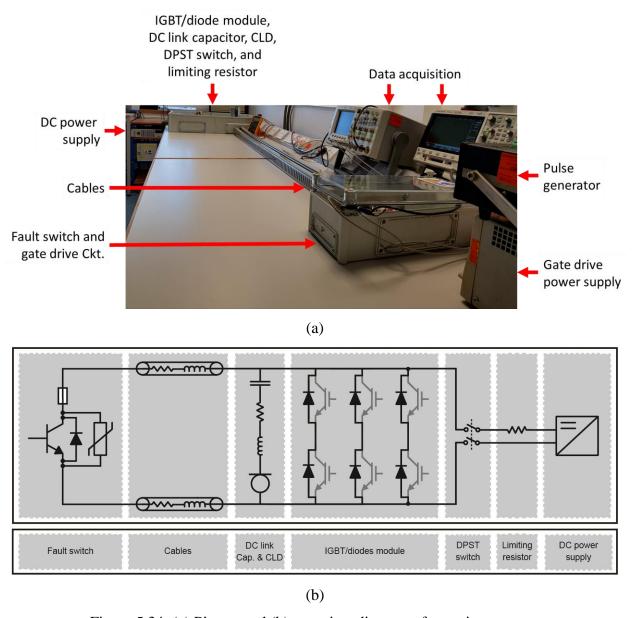

| FIGURE 3.1: (A) OVERVIEW DIAGRAM, AND (B) PICTURE OF EXPERIMENT SETUP            | 89          |

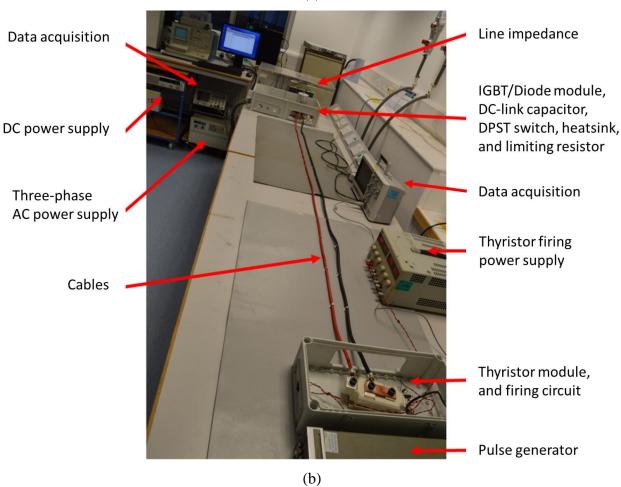

| FIGURE 3.2: THYRISTOR/DIODE MODULE (A) PICTURE, AND (B) INTERNAL CONNECTIONS [2] | 90          |

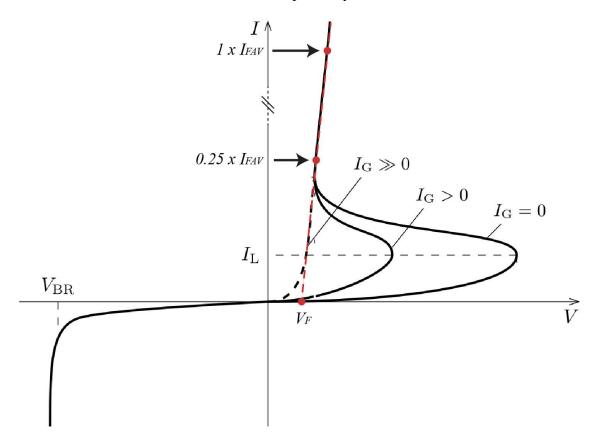

| FIGURE 3.3: TYPICAL THYRISTOR OUTPUT CHARACTERISTICS. MODIFIED FROM [4][4]       | 91          |

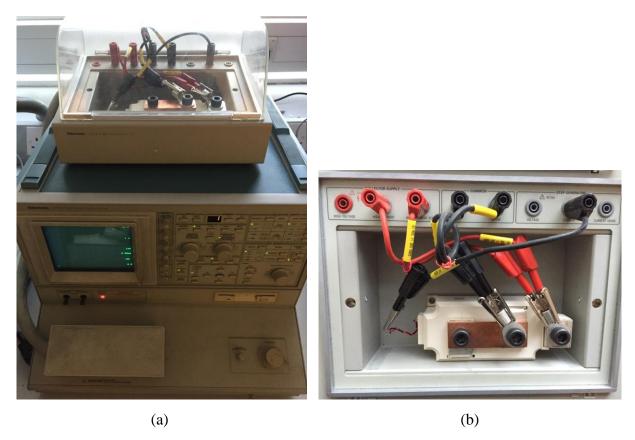

| FIGURE 3.4: (A) OUTPUT CHARACTERISTICS MEASUREMENT SETUP, AND (B) CONNECTIONS    | 92          |

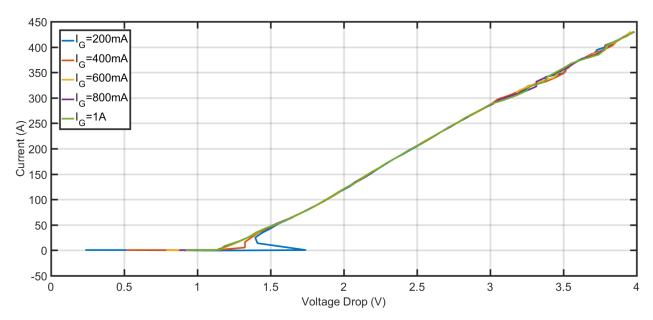

| FIGURE 3.5: MEASURED THYRISTOR OUTPUT CHARACTERISTICS                            | 93          |

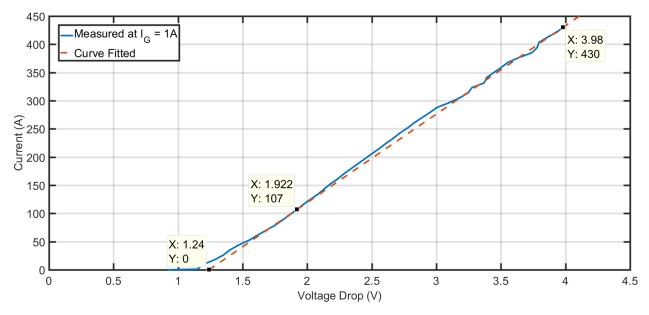

| FIGURE 3.6: COMPARISON OF MEASURED AND CURVE FITTED THYRISTOR OUTPUT                       |     |

|--------------------------------------------------------------------------------------------|-----|

| CHARACTERISTICS. CURVE FITTING EXTRACTION POINTS SHOWN                                     | 93  |

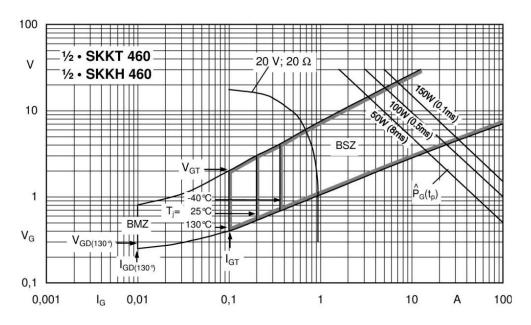

| FIGURE 3.7: THYRISTOR GATE TRIGGER CHARACTERISTICS [2]                                     | 95  |

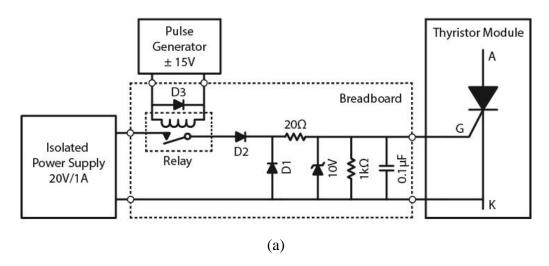

| FIGURE 3.8: (A) SCHEMATIC AND (B) PICTURE OF IMPLEMENTED FIRING CIRCUIT                    | 96  |

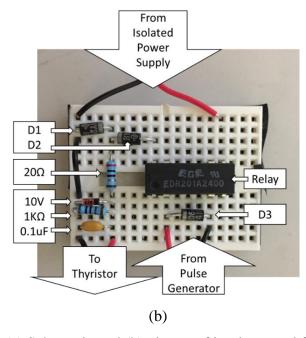

| FIGURE 3.9: PICTURE OF CABLES ARRANGEMENT                                                  | 97  |

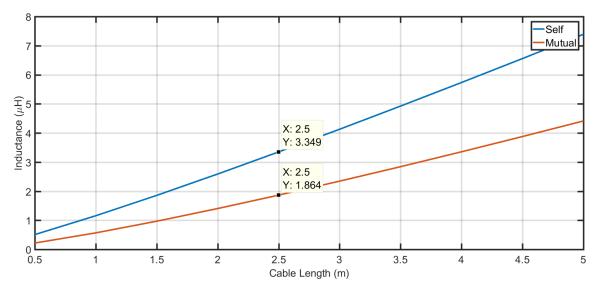

| FIGURE 3.10: CALCULATED CABLES SELF AND MUTUAL INDUCTANCES VS. LENGTH                      | 98  |

| FIGURE 3.11: LCR METER MEASUREMENT SETUP (A) VIEW FROM CONVERTER SIDE, (B) FROM            |     |

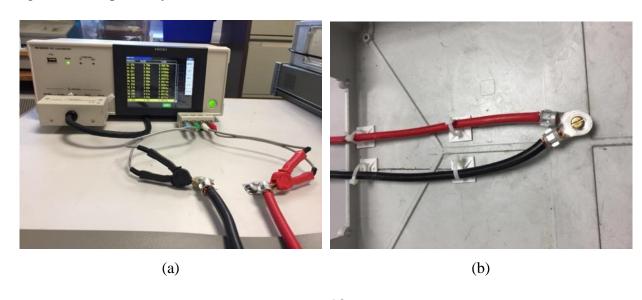

| THYRISTOR MODULE SIDE, AND (C) OVERVIEW                                                    | 99  |

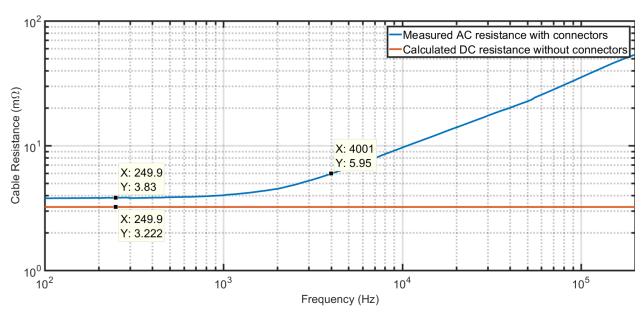

| FIGURE 3.12: MEASURED AND CALCULATED CABLES RESISTANCE                                     | 99  |

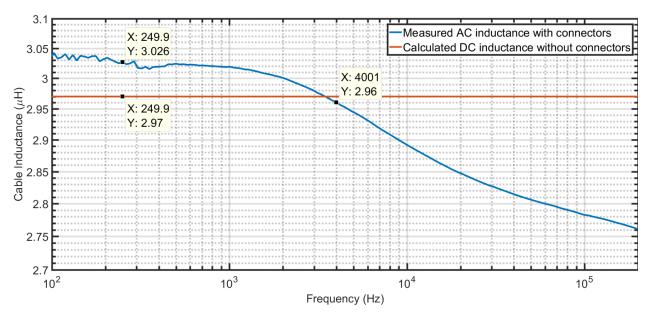

| FIGURE 3.13: MEASURED AND CALCULATED CABLES INDUCTANCE                                     | 100 |

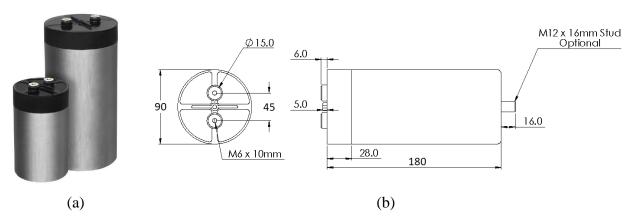

| FIGURE 3.14: DC-LINK CAPACITOR'S PACKAGE (A) PICTURE, AND (B) DIMENSIONS IN MM [6] $\dots$ | 101 |

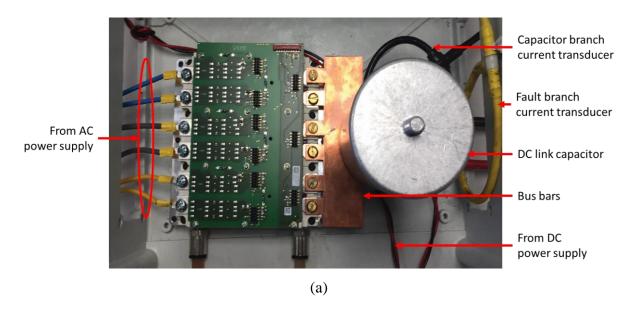

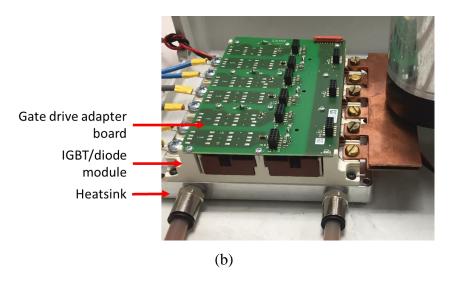

| FIGURE 3.15: (A) TOP AND, (B) SIDE PICTURES OF CONVERTER MODULE AND ATTACHMENTS            | 102 |

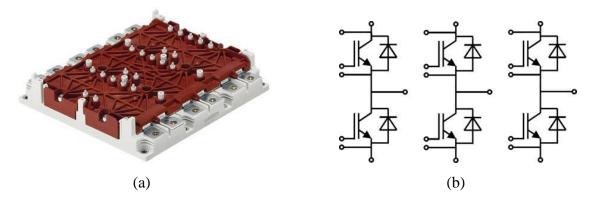

| FIGURE 3.16: CONVERTER MODULE (A) PICTURE AND (B) INTERNAL CONNECTIONS [8]                 | 102 |

| FIGURE 3.17: PICTURE OF ADAPTER BOARD'S (A) FRONT SIDE AND (B) BACK SIDE WITHOUT           |     |

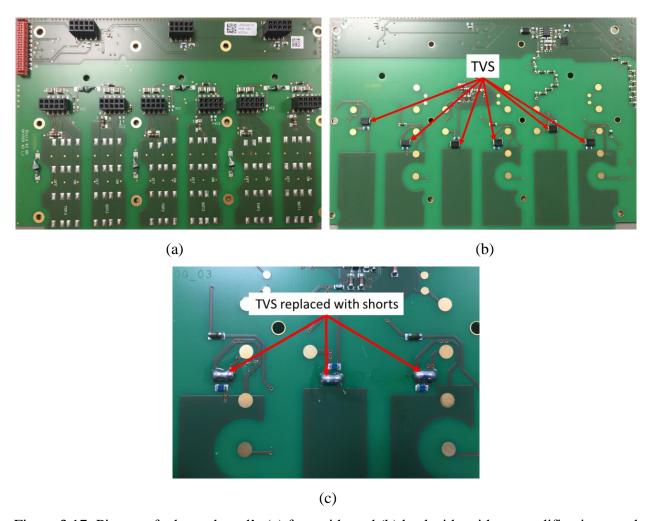

| MODIFICATIONS, AND (C) BACK SIDE AFTER MODIFICATIONS (ZOOMED)                              | 103 |

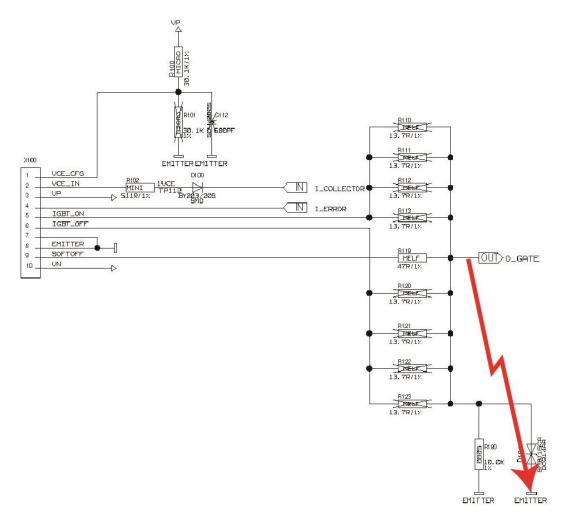

| FIGURE 3.18: LOCATION OF SHORTS IN ADAPTER BOARD'S SCHEMATIC [10]                          | 104 |

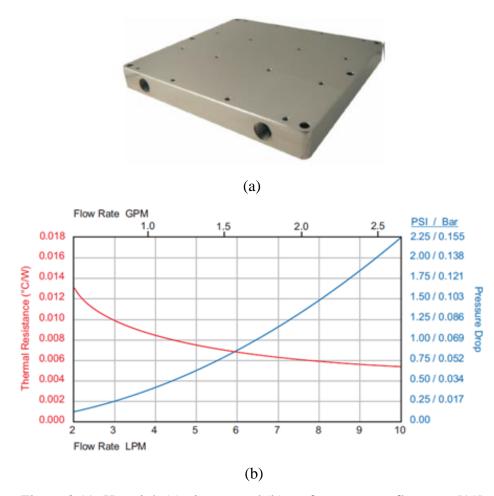

| FIGURE 3.19: HEATSINK (A) PICTURE, AND (B) PERFORMANCE VS. FLOW RATE [11]                  | 105 |

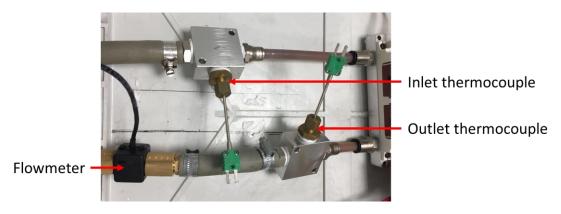

| FIGURE 3.20: PICTURE OF THERMOCOUPLES AND FLOWRATE METER                                   | 105 |

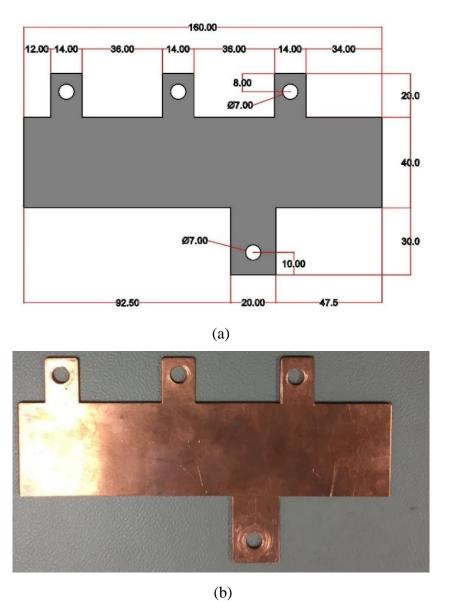

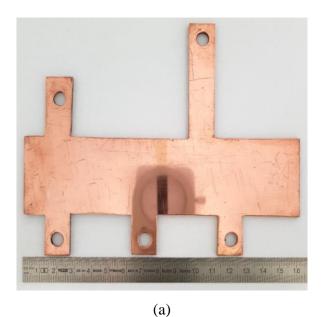

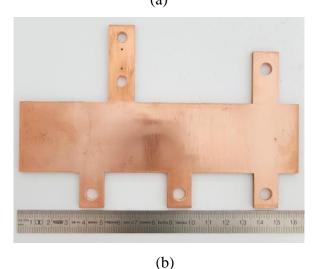

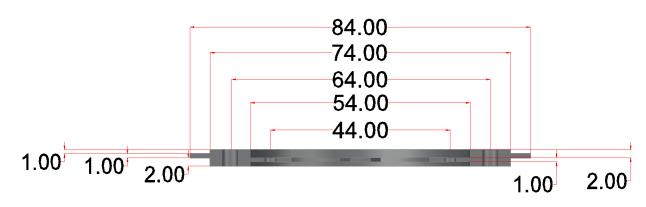

| FIGURE 3.21: BUSBARS (A) DIMENSIONS (IN MM), AND (B) PICTURE OF MACHINED PART              | 106 |

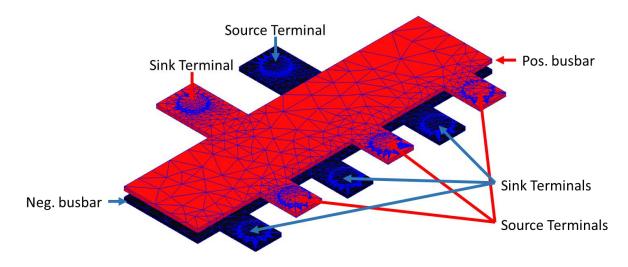

| FIGURE 3.22: ISOMETRIC VIEW OF ANALYZED BUSBARS GEOMETRY AND MESH                          | 107 |

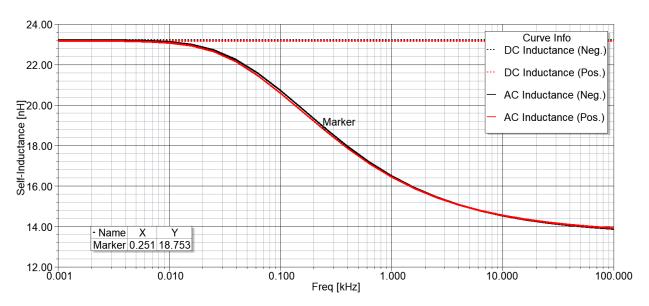

| FIGURE 3.23: AC AND DC SELF-INDUCTANCES OF POSITIVE (POS.) AND NEGATIVE (NEG.)             |     |

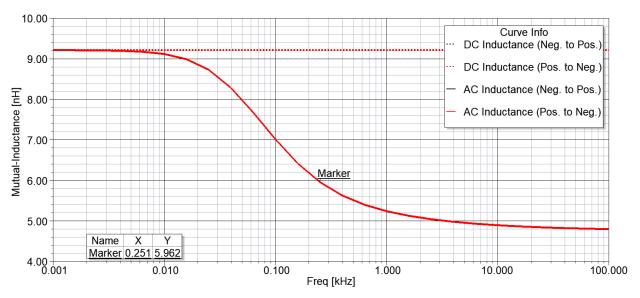

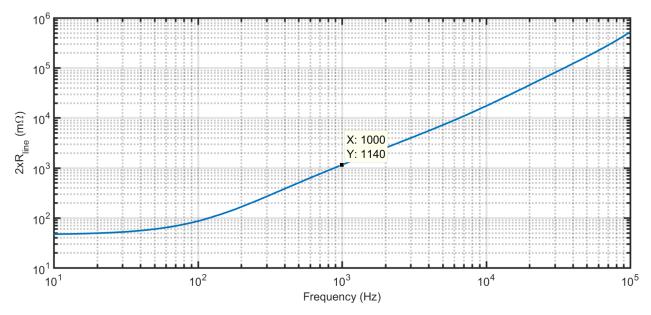

| POTENTIAL BUSBARS VS. FREQUENCY                                                            | 107 |

| FIGURE 3.24: AC AND DC MUTUAL-INDUCTANCES OF POSITIVE (POS.) AND NEGATIVE (NEG.)           |     |

| POTENTIAL BUSBARS VS. FREQUENCY                                                            | 108 |

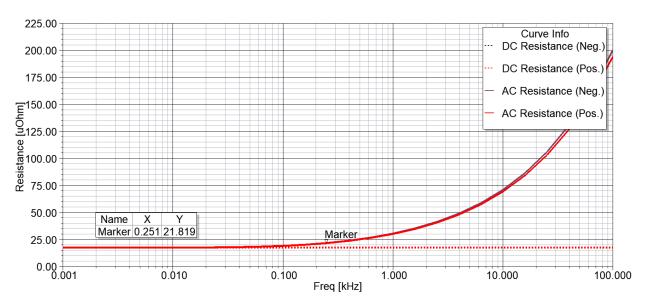

| FIGURE 3.25: AC AND DC RESISTANCE OF POSITIVE (POS.) AND NEGATIVE (NEG.) POTENTIAL         |     |

| BUSBARS VS. FREQUENCY                                                                      | 108 |

| FIGURE 3.26: PICTURE OF AC POWER SOURCE [12]                                               | 109 |

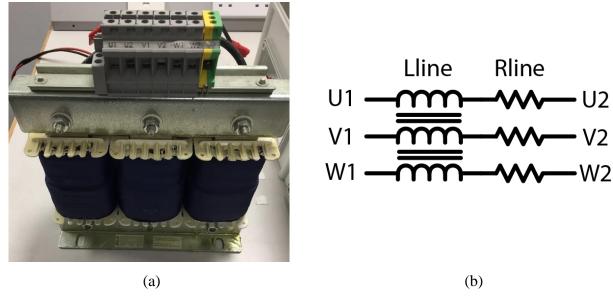

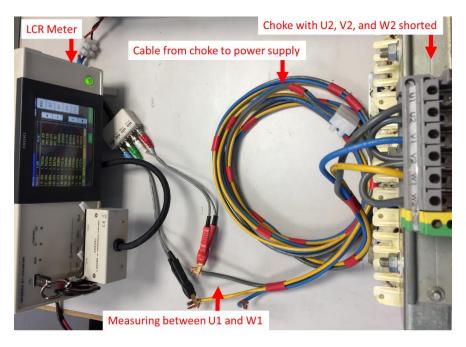

| FIGURE 3.27: AC CHOKE'S (A) PICTURE, AND (B) EQUIVALENT CIRCUIT                            | 109 |

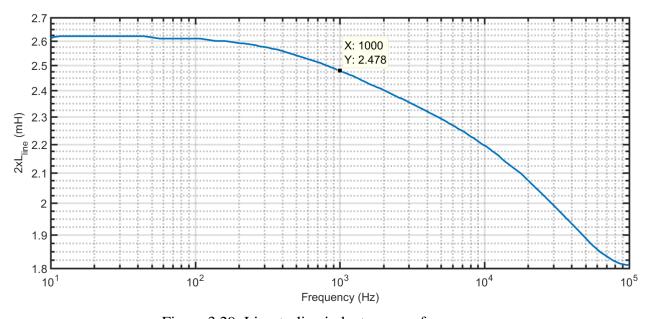

| FIGURE 3.28: LCR METER MEASUREMENT SETUP                                                   | 110 |

| FIGURE 3.29: LINE-TO-LINE INDUCTANCE VS. FREQUENCY                                         | 110 |

| FIGURE 3.30: LINE-TO-LINE RESISTANCE VS FREQUENCY                                          | 111 |

| FIGURE 3.31: PICTURE OF DC POWER SUPPLY'S FRONT PANEL                                      | 111 |

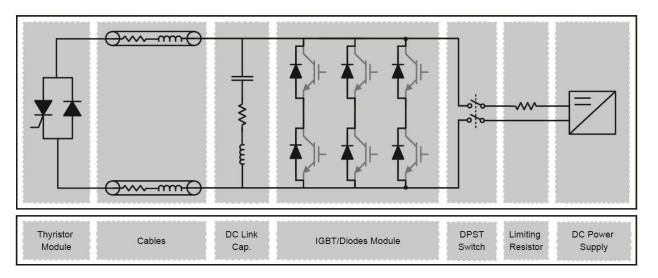

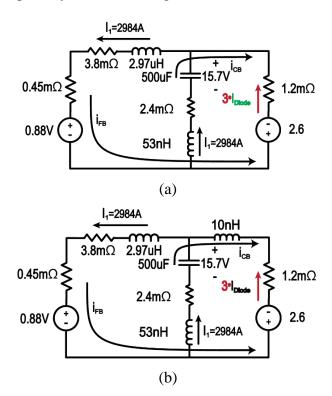

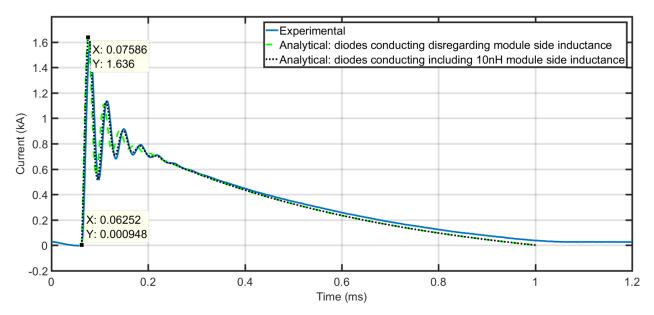

| FIGURE 3.32: OVERVIEW OF DC SIDE CONTRIBUTIONS EXPERIMENTAL SETUP                          | 112 |

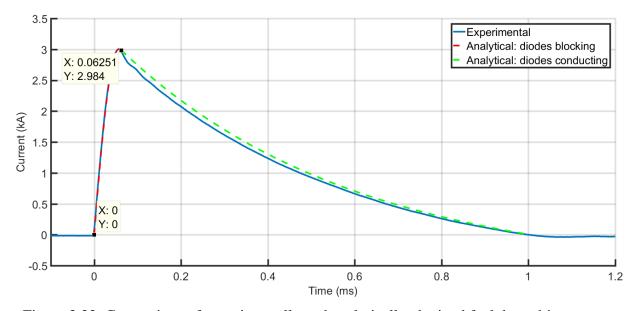

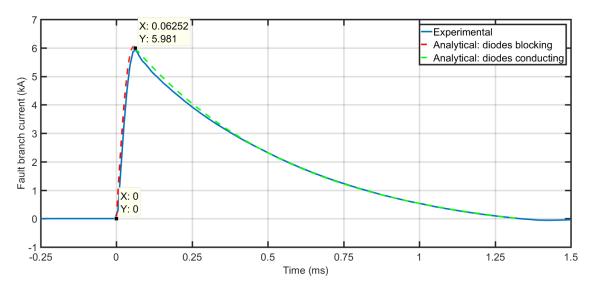

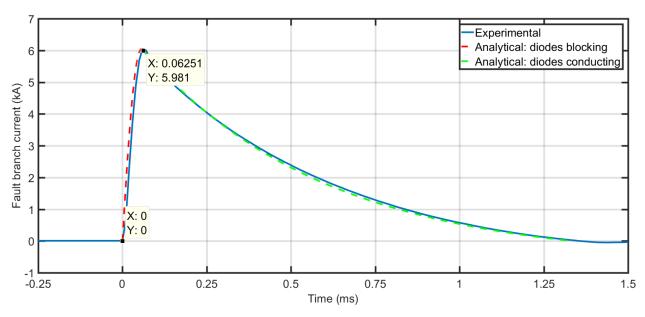

| FIGURE 3.33: COMPARISON OF EXPERIMENTALLY AND ANALYTICALLY OBTAINED FAULT                  |     |

| BRANCH'S CURRENTS                                                                          | 113 |

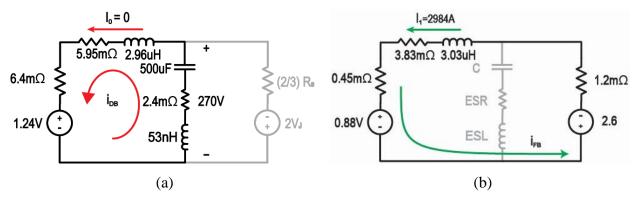

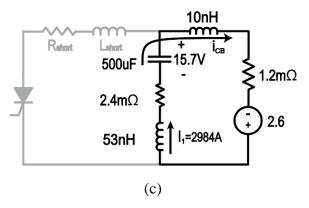

| FIGURE 3.34: EQUIVALENT CIRCUITS DURING (A) DIODES BLOCKING, AND (B) DIODES                |     |

| CONDUCTION STACES                                                                          | 111 |

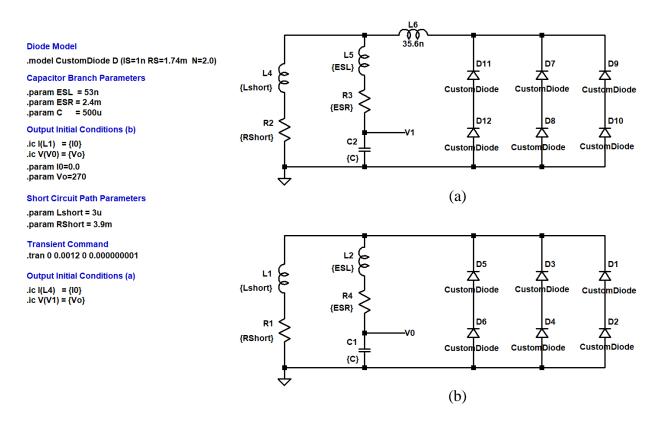

| FIGURE 3.35: SIMULATION CIRCUITS (A) INCLUDING AND (B) DISREGARDING MODULE SIDE         |

|-----------------------------------------------------------------------------------------|

| INDUCTANCES115                                                                          |

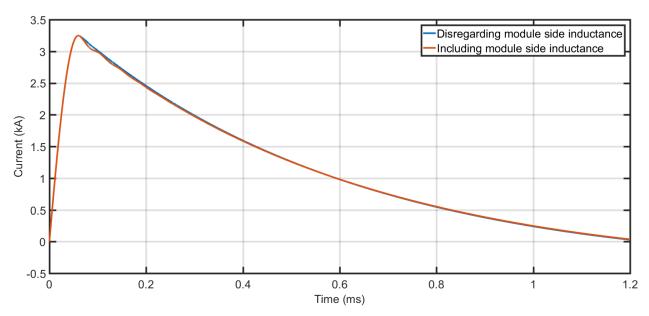

| FIGURE 3.36: SIMULATION RESULTS COMPARING FAULT BRANCH'S CURRENTS INCLUDING AND         |

| DISREGARDING MODULE SIDE INDUCTANCES115                                                 |

| FIGURE 3.37: COMPARISON OF EXPERIMENTALLY AND ANALYTICALLY OBTAINED CAPACITOR           |

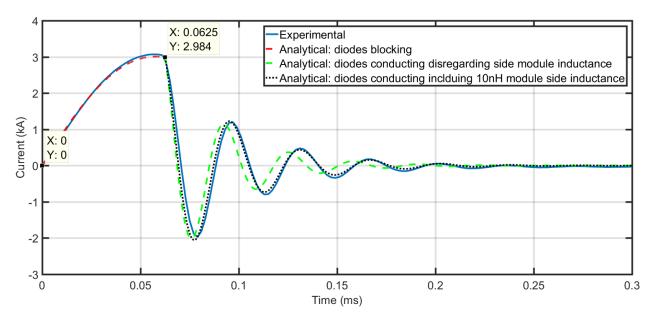

| CURRENTS116                                                                             |

| FIGURE 3.38: EQUIVALENT CIRCUITS DURING (A) DIODES BLOCKING, AND (B) DIODES             |

| CONDUCTION STAGES DISREGARDING, AND (C) INCLUDING 10NH MODULE SIDE                      |

| INDUCTANCE117                                                                           |

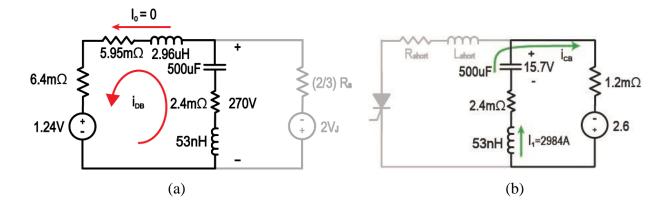

| FIGURE 3.39: EQUIVALENT CIRCUIT DURING DIODES CONDUCTION STAGES (A) DISREGARDING        |

| AND (B) INCLUDING MODULE SIDE INDUCTANCE117                                             |

| FIGURE 3.40: COMPARISON OF EXPERIMENTALLY AND ANALYTICALLY OBTAINED DIODES              |

| CURRENTS118                                                                             |

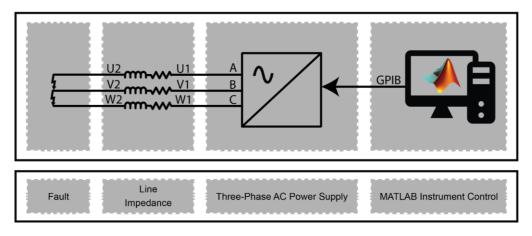

| FIGURE 3.41: OVERVIEW OF AC SIDE CONTRIBUTIONS EXPERIMENTAL SETUP118                    |

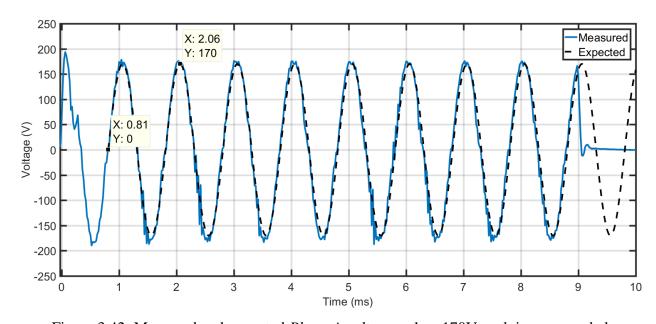

| FIGURE 3.42: MEASURED AND EXPECTED <i>PHASE A</i> VOLTAGES WHEN 170V PEAK IS COMMANDED  |

| 119                                                                                     |

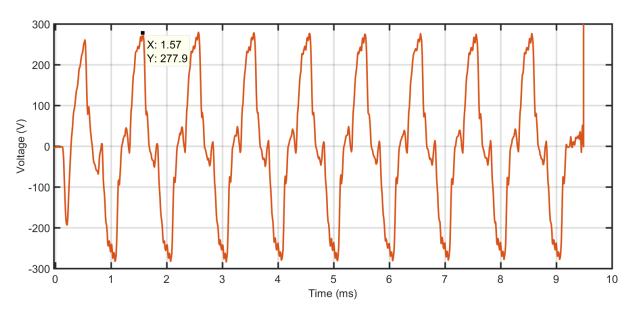

| FIGURE 3.43: MEASURED PHASE A VOLTAGE WHEN 150VRMS IS COMMANDED120                      |

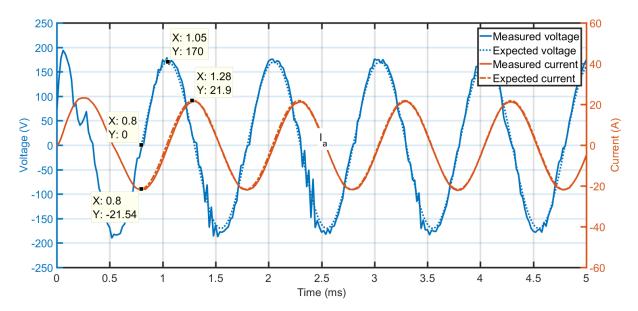

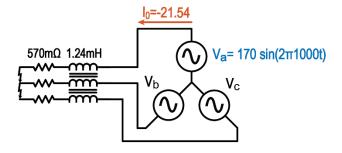

| FIGURE 3.44: COMPARISON OF MEASURED AND EXPECTED $\it{PHASE}$ A VOLTAGE AND CURRENT120  |

| FIGURE 3.45: EQUIVALENT CIRCUIT OF AC SIDE CONTRIBUTIONS                                |

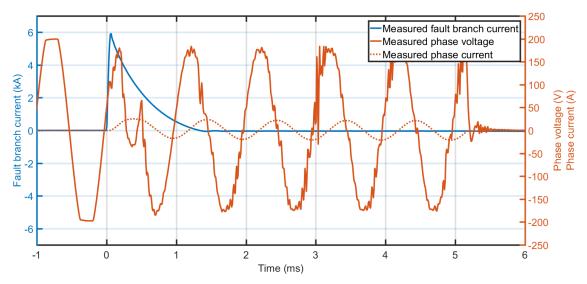

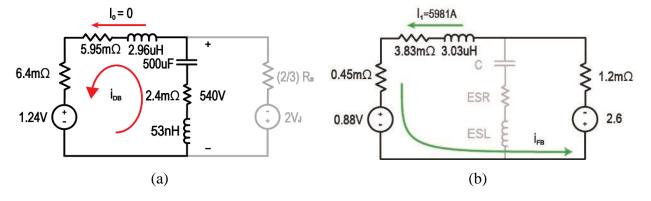

| FIGURE 3.46: COMBINED RESPONSE EXPERIMENT SETUP                                         |

| FIGURE 3.47: MEASURED AC AND DC SIDE CONTRIBUTIONS WITH INITIAL DC LINK VOLTAGE OF      |

| 540V AND A OF 18°                                                                       |

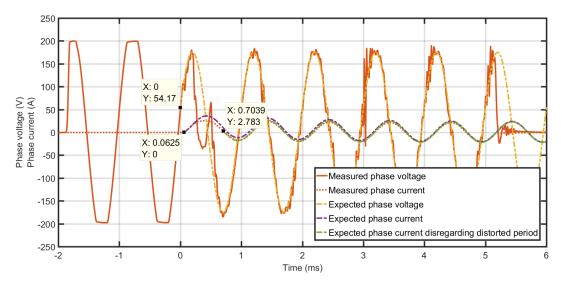

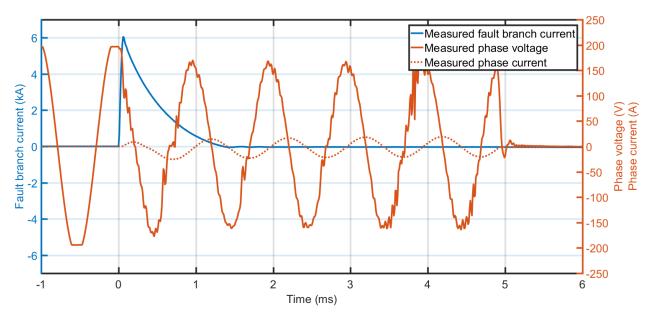

| FIGURE 3.48: COMPARISON OF MEASURED AND EXPECTED AC SIDE CONTRIBUTIONS WITH $\it A$ OF  |

| 18°                                                                                     |

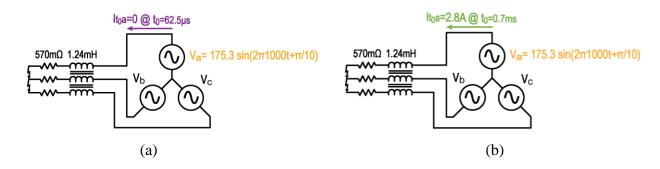

| FIGURE 3.49:EQUIVALENT CIRCUIT AND USED PARAMETERS (A) ACCOUNTING FOR, AND (B)          |

| DISREGARDING VOLTAGE DISTORTION PERIOD                                                  |

| FIGURE 3.50: COMPARISON OF MEASURED AND EXPECTED FAULT BRANCH'S CURRENT WITH $\it A$ OF |

| 18°                                                                                     |

| FIGURE 3.51: EQUIVALENT DC SIDE CONTRIBUTION CIRCUITS DURING (A) DIODES BLOCKING,       |

| AND (B) DIODES CONDUCTION STAGES                                                        |

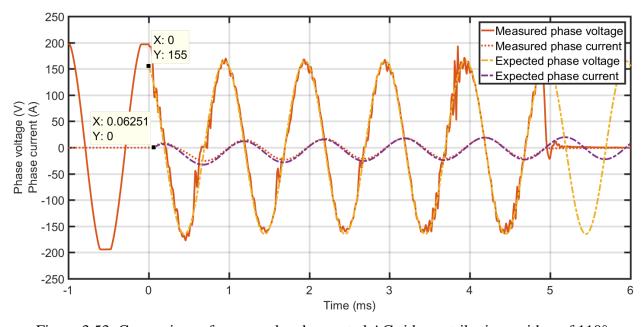

| FIGURE 3.52: MEASURED AC AND DC SIDE CONTRIBUTIONS WITH INITIAL DC LINK VOLTAGE OF      |

| 540V AND A OF 110°                                                                      |

| FIGURE 3.53: COMPARISON OF MEASURED AND EXPECTED AC SIDE CONTRIBUTIONS WITH $\it A$ OF  |

| 110°                                                                                    |

| FIGURE 3.54: COMPARISON OF MEASURED AND EXPECTED FAULT BRANCH'S CURRENT WITH $\it A$ OF |

| 110°                                                                                    |

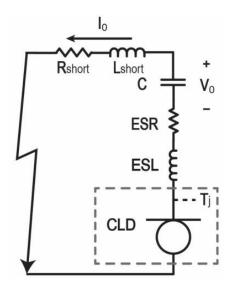

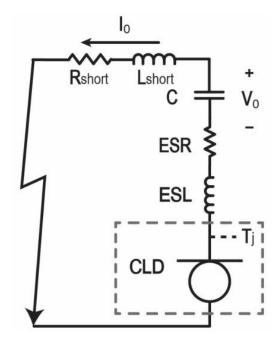

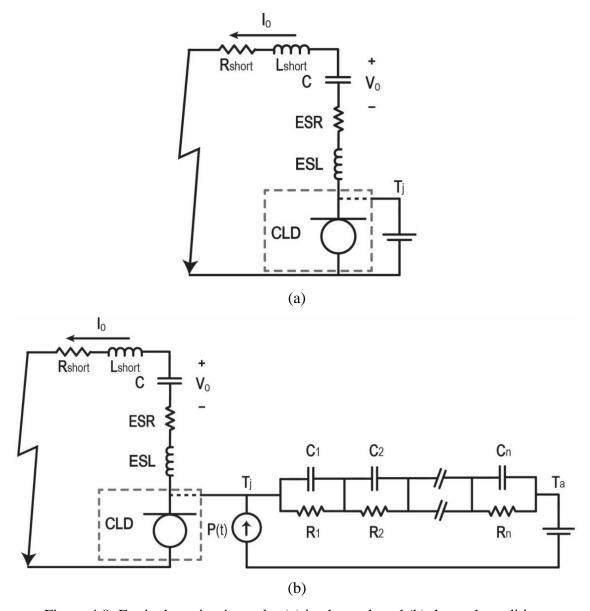

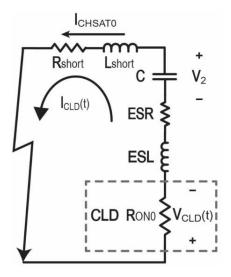

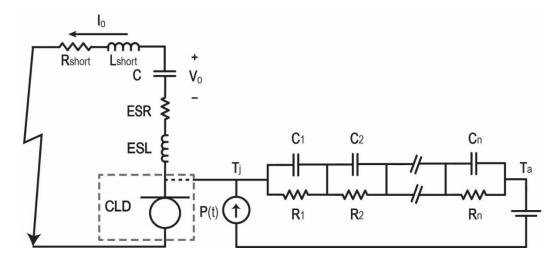

| FIGURE 4.1: EOUIVALENT FAULT CIRCUIT UNDER INVESTIGATION                                |

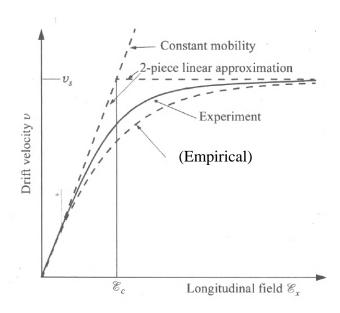

| FIGURE 4.2: COMPARISON OF DRIFT VELOCITY VS. ELECTRIC FIELD REPRESENTATIONS [3              | 5] 129   |

|---------------------------------------------------------------------------------------------|----------|

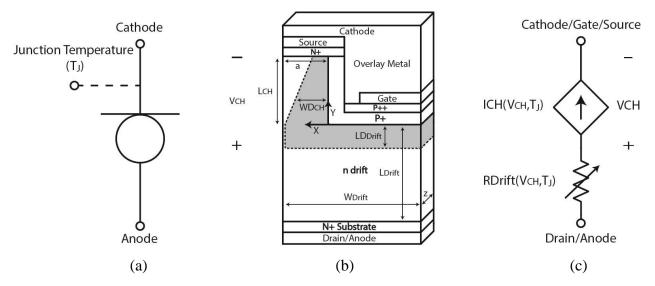

| FIGURE 4.3: (A) CLD SYMBOL, (B) STRUCTURE [4], AND (C) EQUIVALENT CIRCUIT                   | 131      |

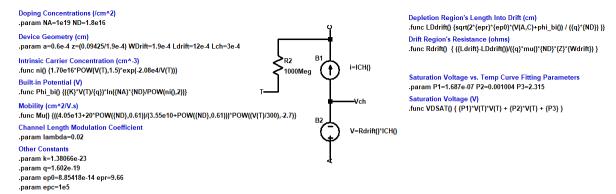

| FIGURE 4.4: IMPLEMENTATION OF CLD SPICE MODEL                                               | 136      |

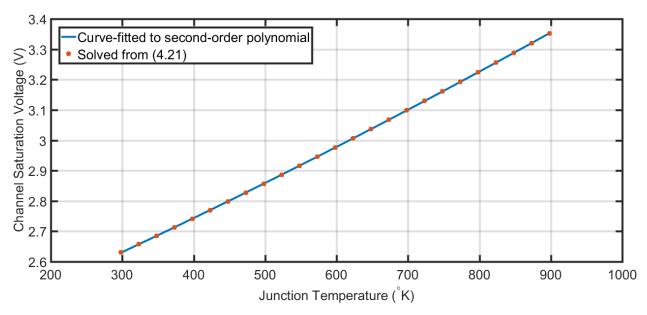

| FIGURE 4.5: COMPARISON OF CHANNEL SATURATION VOLTAGE (VCHSAT) VS. JUNCTION                  |          |

| TEMPERATURE FOUND BY SOLVING (4.21), AND CURVE FITTED USING A POLYNOMIA                     | AL       |

| FUNCTION WITH THE FORM AND PARAMETERS IN TABLE 4.1.                                         | 137      |

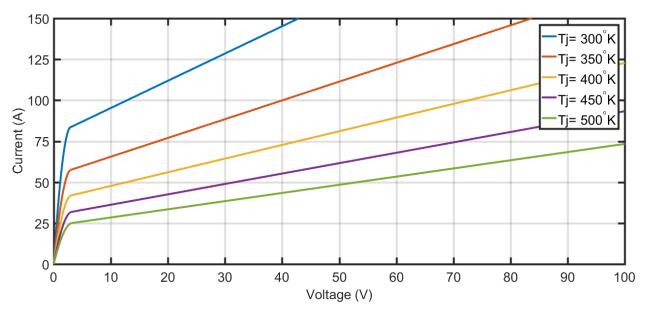

| FIGURE 4.6: OUTPUT CHARACTERISTICS OF SPICE MODELLED DEVICE FOR 350-500K JUNC               | TION     |

| TEMPERATURES WITH STEPS OF 50K                                                              | 137      |

| FIGURE 4.7: EQUIVALENT FAULT CIRCUIT UNDER CONSIDERATION                                    | 138      |

| FIGURE 4.8: EQUIVALENT CIRCUITS UNDER (A) ISOTHERMAL, AND (B) THERMAL CONDIT                | IONS 139 |

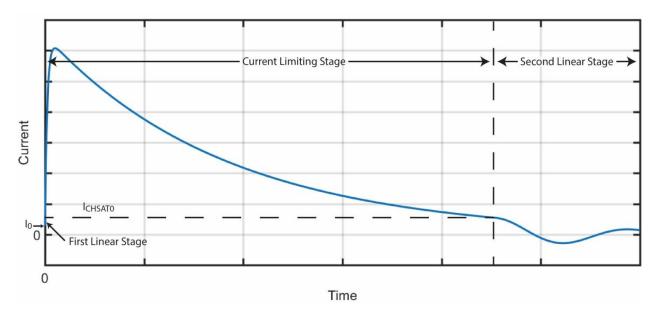

| FIGURE 4.9: TYPICAL CLD FAULT RESPONSE UNDER ISOTHERMAL CONDITION                           | 140      |

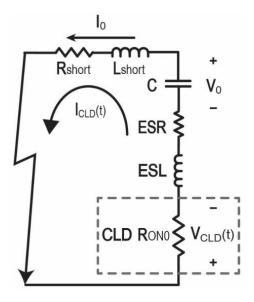

| FIGURE 4.10: EQUIVALENT CIRCUIT DURING FIRST LINEAR STAGE                                   | 141      |

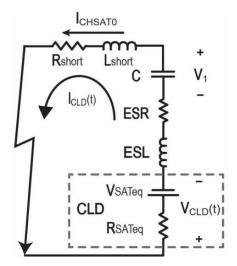

| FIGURE 4.11: EQUIVALENT CIRCUIT DURING SATURATION STAGE                                     | 142      |

| FIGURE 4.12: EQUIVALENT CIRCUIT DURING SECOND LINEAR STAGE                                  | 143      |

| FIGURE 4.13: EQUIVALENT CIRCUIT DURING SECOND LINEAR STAGE                                  | 144      |

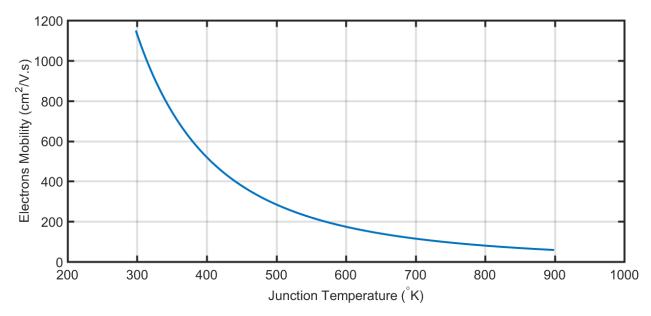

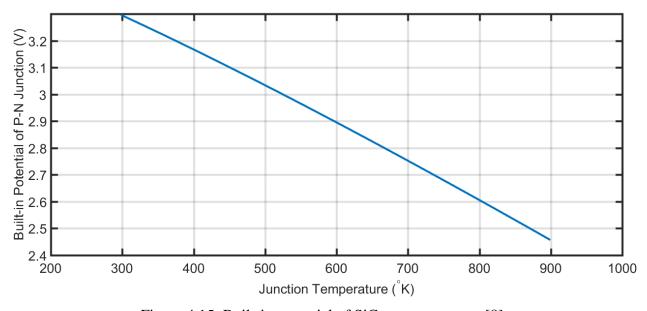

| FIGURE 4.14: ELECTRONS MOBILITY OF SIC VS. TEMPERATURE [8]                                  | 145      |

| FIGURE 4.15: BUILT-IN POTENTIAL OF SIC VS. TEMPERATURE [8]                                  | 145      |

| FIGURE 4.16: SIMULATION CIRCUIT UNDER ISOTHERMAL CONDITION                                  | 146      |

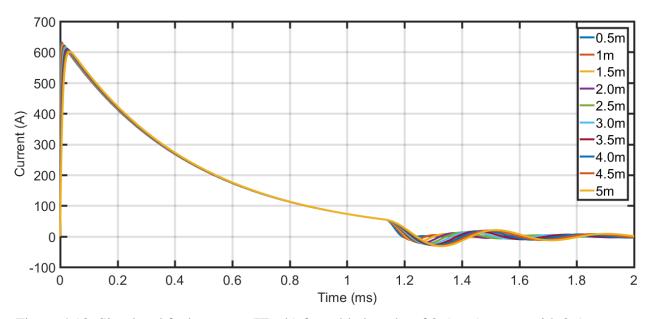

| FIGURE 4.17: SIMULATED FAULT CURRENT ( $\mathit{IFAULT}$ ) FOR CABLE LENGTHS OF 0.5 TO 5 ME | TERS     |

| WITH 0.5M STEPS (ZOOM TO INITIAL STAGE)                                                     | 147      |

| FIGURE 4.18: SIMULATED FAULT CURRENT (IFAULT) FOR CABLE LENGTHS OF 0.5 TO 5 ME              | ETERS    |

| WITH 0.5M STEPS                                                                             | 147      |

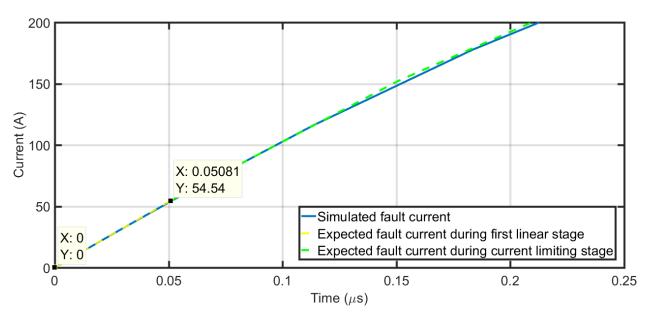

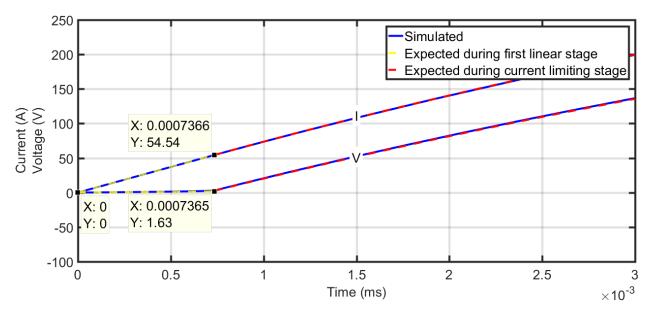

| FIGURE 4.19: COMPARISON OF SIMULATED AND EXPECTED FAULT CURRENTS DURING IN                  | IITIAL   |

| STAGE FOR THE 0.5M LINE-TO-LINE CABLE FAULT CONDITION                                       | 148      |

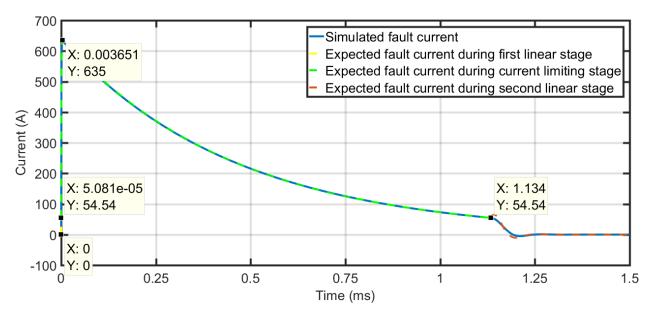

| FIGURE 4.20: COMPARISON OF SIMULATED AND EXPECTED FAULT CURRENT DURING ALL                  | L STAGES |

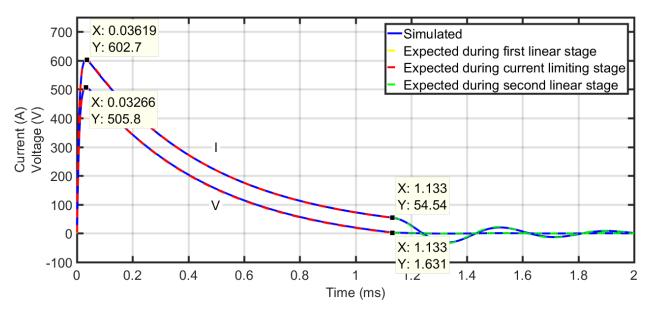

| OF THE 0.5M LINE-TO-LINE CABLE FAULT CONDITION                                              | 149      |

| FIGURE 4.21: COMPARISON OF SIMULATED AND EXPECTED FAULT CURRENT DURING SEC                  | COND     |

| LINEAR STAGE OF A 0.5M LINE-TO-LINE CABLE FAULT CONDITION WITH X1-X1.9 OF                   | 0A CLD   |

| ON-STATE RESISTANCE ( $R_{ON0}$ )                                                           | 149      |

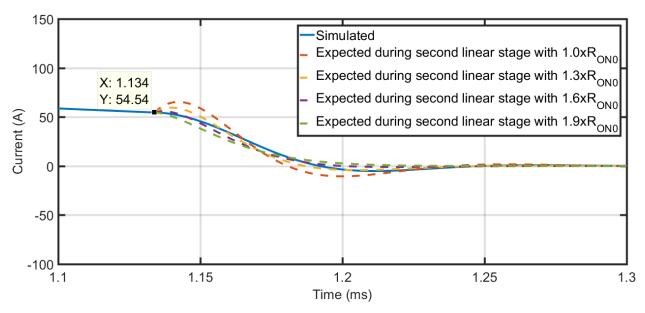

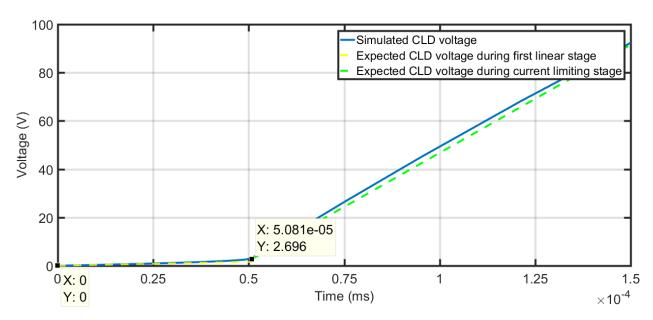

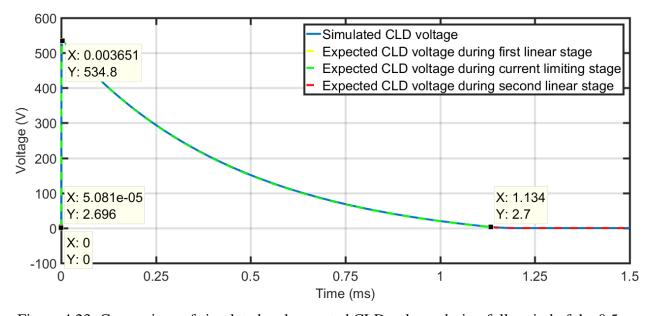

| FIGURE 4.22: COMPARISON OF SIMULATED AND EXPECTED CLD VOLTAGE DURING FIRST                  | LINEAR   |

| STAGE OF A 0.5M LINE-TO-LINE CABLE FAULT CONDITION                                          | 150      |

| FIGURE 4.23: COMPARISON OF SIMULATED AND EXPECTED CLD VOLTAGE DURING FULL                   | PERIOD   |

| OF THE 0.5M CABLE FAULT CONDITION                                                           | 150      |

| FIGURE 4.24: COMPARISON OF SIMULATED AND EXPECTED FAULT CURRENT, AND CLD V                  | OLTAGE   |

| DURING FULL PERIOD OF A 5M CABLE FAULT CONDITION                                            | 151      |

| FIGURE 4.25: COMPARISON OF SIMULATED AND EXPECTED FAULT CURRENT, AND CLD V                  |          |

| DURING FIRST LINEAR STAGE OF A 5M CARLE FALLET CONDITION                                    | 151      |

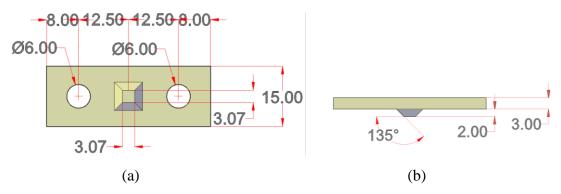

| FIGURE 4.26: (A) BOTTOM, AND (B) SIDE VIEWS OF CATHODE STRUCTURE                        | 152     |

|-----------------------------------------------------------------------------------------|---------|

| FIGURE 4.27: (A) BOTTOM, AND (B) SIDE VIEWS OF ANODE STRUCTURE                          | 152     |

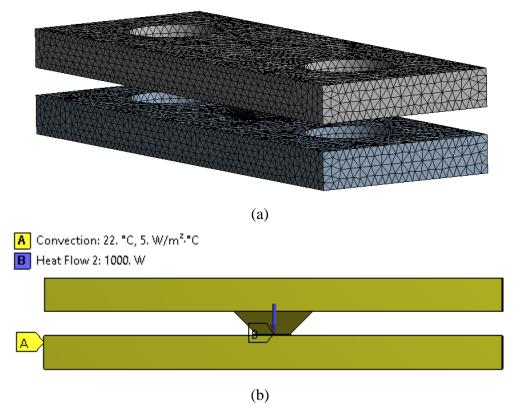

| FIGURE 4.28: (A) ISOMETRIC VIEW OF GEOMETRY AND MESH, AND (B) SIDE VIEW OF GEOMETRY     | 1ETRY   |

| WITH BOUNDARY CONDITIONS                                                                | 153     |

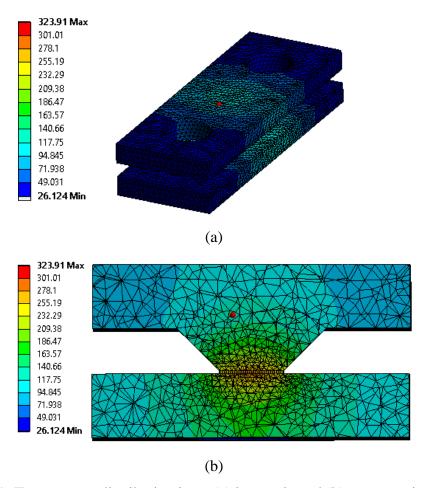

| FIGURE 4.29: TEMPERATURE DISTRIBUTION IN AN (A) ISOMETRIC AND (B) CROSS-SECTION         | AL      |

| VIEW OF GEOMETRY AFTER 0.5S                                                             | 154     |

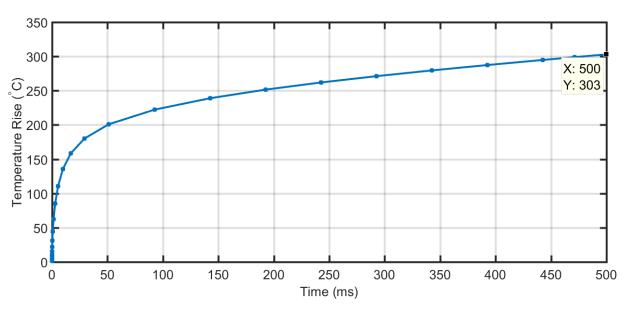

| FIGURE 4.30: MAXIMUM TEMPERATURE RISE IN CLD STRUCTURE VS. TIME AFTER 1KW HE            | AT      |

| LOAD AT <i>T=0</i>                                                                      | 154     |

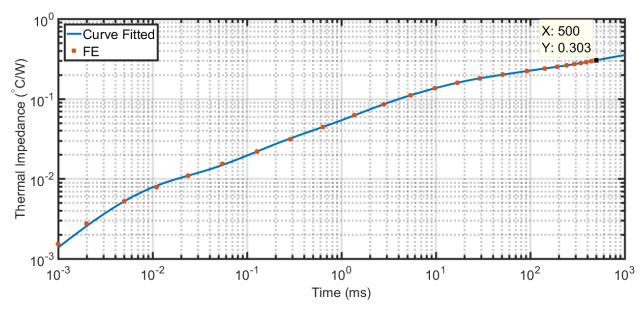

| FIGURE 4.31: FE-BASED THERMAL IMPEDANCE VS. CURVE FITTED FOSTER NETWORK IMPE            | EDANCE  |

|                                                                                         | 155     |

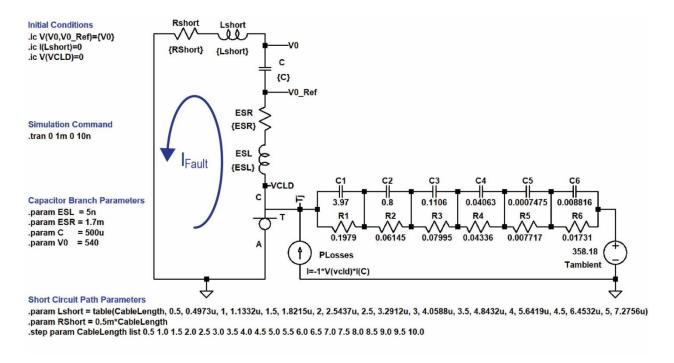

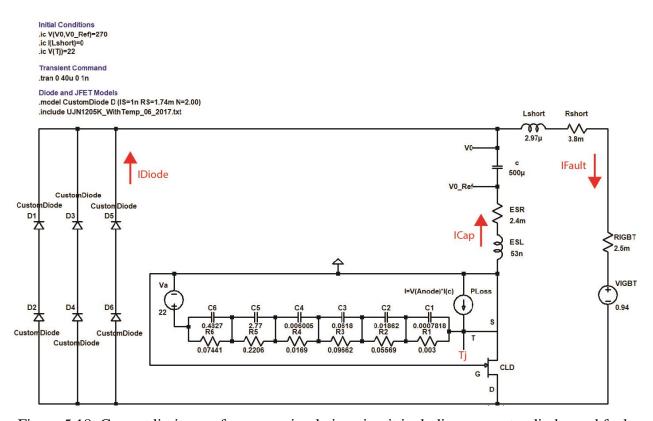

| FIGURE 4.32: SCHEMATIC OF SIMULATED CIRCUIT INCLUDING THERMAL EFFECTS                   | 156     |

| FIGURE 4.33: SIMULATED CLD CURRENT ( $I_{FAULT}$ ) UNDER LINE-TO-LINE FAULT CONDITION V | VITH    |

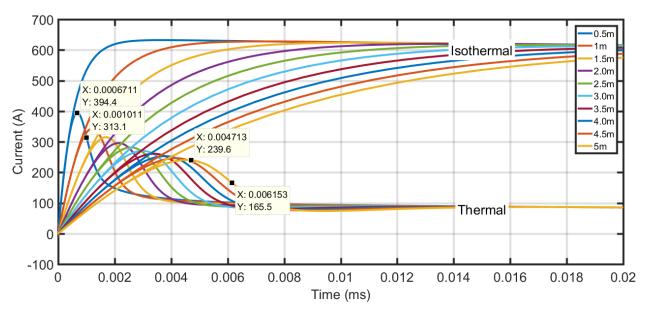

| AND WITHOUT THERMAL EFFECTS FOR CABLE LENGTHS OF 0.5-5M WITH 0.5 STEPS                  | 157     |

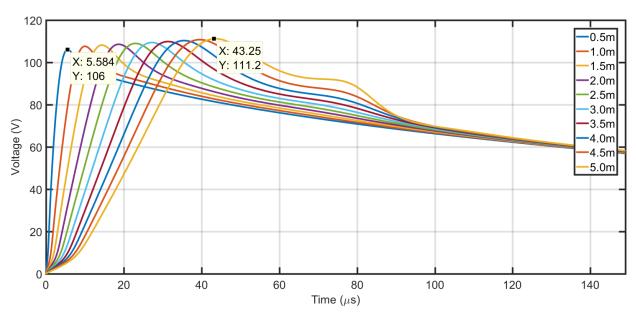

| FIGURE 4.34: SIMULATED CLD VOLTAGE (- $VCLD$ ) UNDER LINE-TO-LINE FAULT CONDITION       | WITH    |

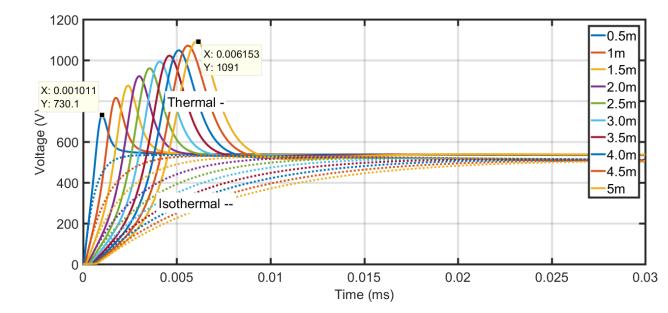

| AND WITHOUT THERMAL EFFECTS FOR CABLE LENGTHS OF 0.5-5M WITH 0.5 STEPS                  | 158     |

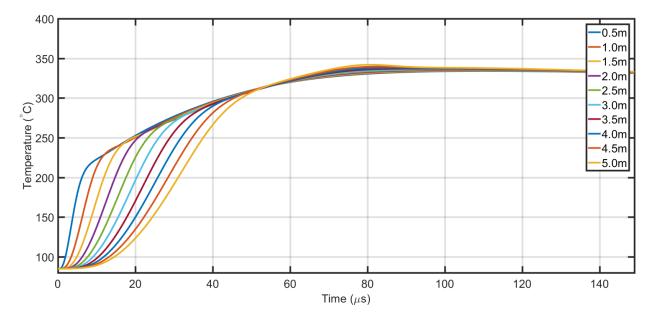

| FIGURE 4.35: SIMULATED CLD TEMPERATURE (V(TJ)) UNDER LINE-TO-LINE FAULT CONDIT          | TION    |

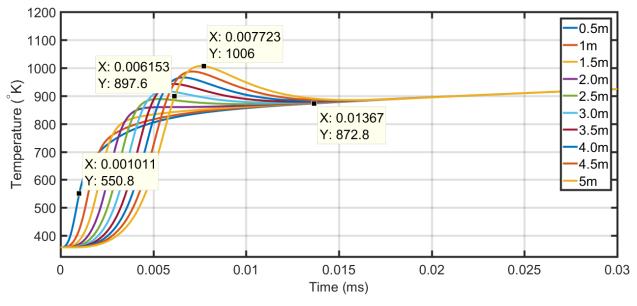

| FOR CABLE LENGTHS OF 0.5-5M WITH 0.5 STEPS                                              | 158     |

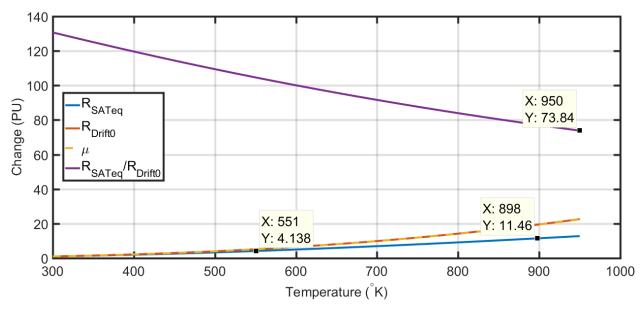

| FIGURE 4.36: CHANGE OF CLD RESISTANCES IN SATURATION WITH TEMPERATURE                   | 159     |

| FIGURE 4.37: CHANGE OF CLD EQUIVALENT CHANNEL VOLTAGE DROP IN SATURATION (V             | SATEQ)  |

| AND SATURATION VOLTAGE (VDSATO) WITH TEMPERATURE                                        | 160     |

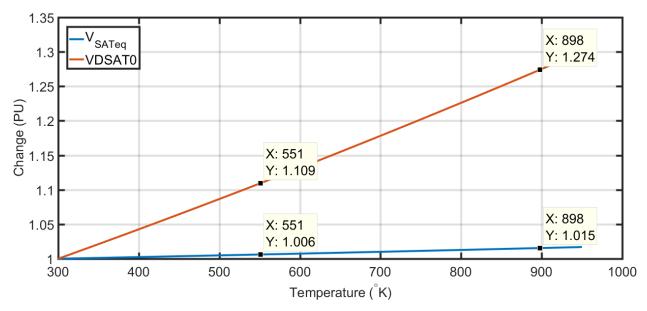

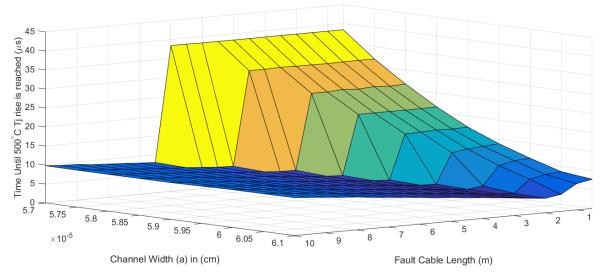

| FIGURE 4.38: SENSITIVITY OF THE TIME UNTIL 500°C JUNCTION TEMPERATURE RISE IS REA       | ACHED   |

| TO MESA WIDTH (A) AND FAULT CABLE LENGTH AT V <sub>0</sub> =540V                        | 161     |

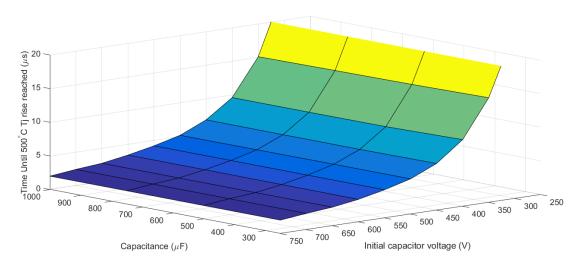

| FIGURE 4.39: SENSITIVITY OF THE TIME UNTIL 500°C JUNCTION TEMPERATURE RISE IS REA       | ACHED   |

| TO DC-LINK CAPACITANCE AND INITIAL VOLTAGE (V $_0$ ) AT MESA WIDTH OF $0.6\mu M$ AN     | ID      |

| CABLE LENGTHS FROM 0.5 TO 10M                                                           | 161     |

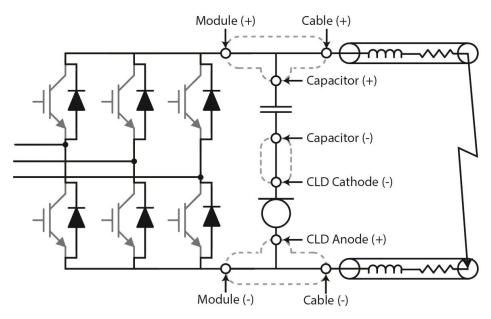

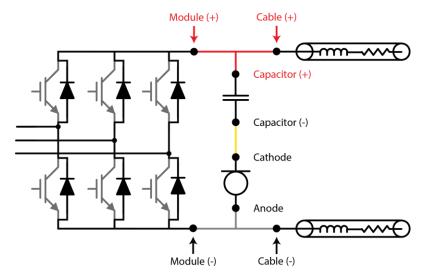

| FIGURE 5.1: LOCATION OF CURRENT LIMITER IN CONVERTER CIRCUIT, WITH BUSBARS CIRCUIT      | RCLED   |

| BY DASHED LINES                                                                         | 164     |

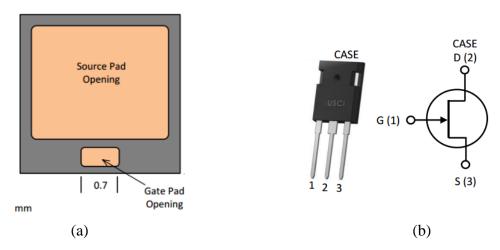

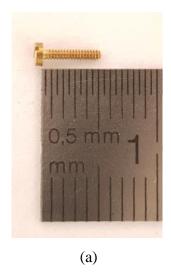

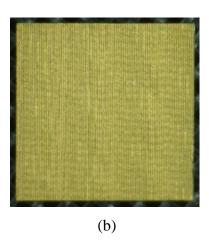

| FIGURE 5.2: PICTURE OF USCI JFETS IN (A) DIE AND (B) PLASTIC PACKAGED FORMS [10, 13]    | 165     |

| FIGURE 5.3: (A) PICTURE AND (B) PINOUT OF HERMETICALLY SEALED METAL-CAN PACKA           | GED SIC |

| JFETS FROM MICROSS COMPONENTS [14]                                                      | 166     |

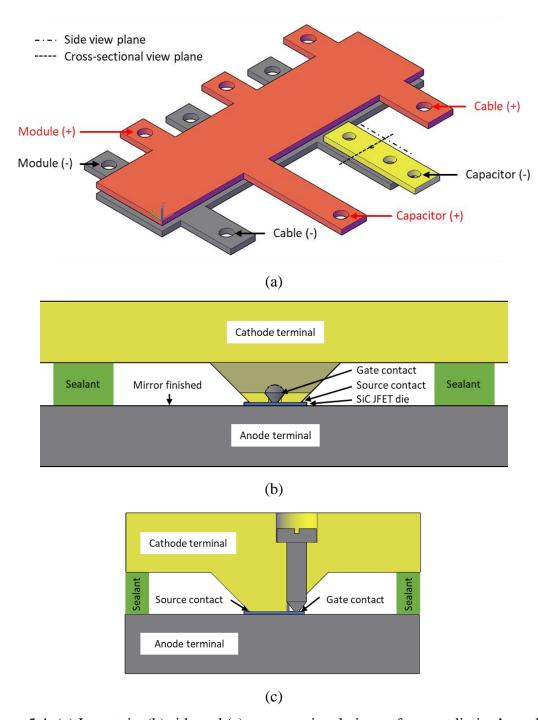

| FIGURE 5.4: (A) ISOMETRIC, (B) SIDE AND (C) CROSS-SECTIONAL VIEWS OF CURRENT LIMIT      | ΓER'S   |

| PACKAGE                                                                                 | 167     |

| FIGURE 5.5: SCHEMATIC OF CURRENT LIMITER PACKAGE'S ELECTRICAL CONNECTIONS               | 168     |

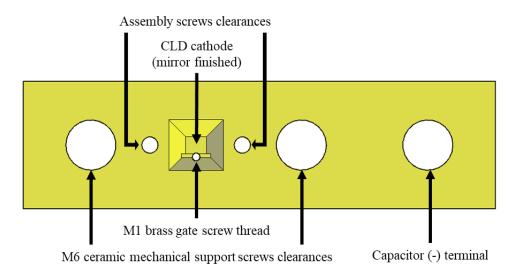

| FIGURE 5.6: BOTTOM SIDE VIEW OF CATHODE STRUCTURE                                       | 168     |

| FIGURE 5.7: PICTURE OF M6 CERAMIC SCREW [20]                                            | 169     |

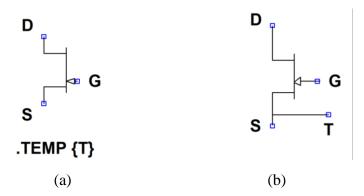

| FIGURE 5.8: SYMBOLS OF (A) ORIGINAL MANUFACTURER SPICE MODEL AND (B) MODIFIED           |         |

| MODEI                                                                                   | 170     |

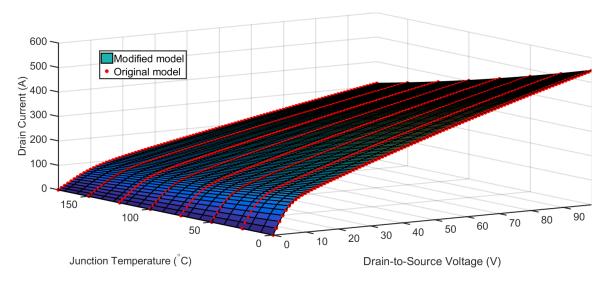

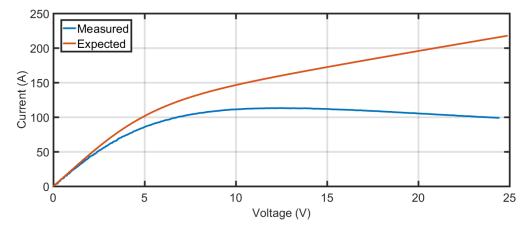

| FIGURE 5.9: COMPARISON OF OUTPUT CHARACTERISTICS OBTAINED FROM ORIGINAL AND      |     |

|----------------------------------------------------------------------------------|-----|

| MODIFIED MODELS                                                                  | 170 |

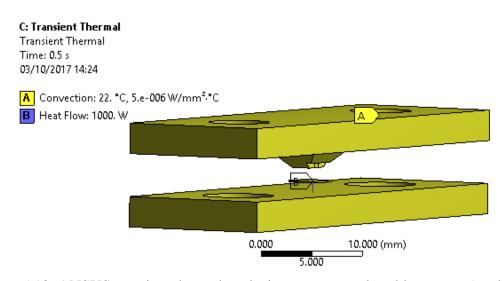

| FIGURE 5.10: ANSYS TRANSIENT THERMAL ANALYSIS GEOMETRY AND PROBLEM SETUP         |     |

| (EXPLODED)                                                                       | 171 |

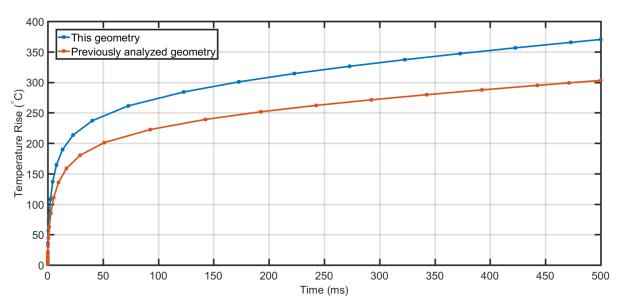

| FIGURE 5.11: MAXIMUM TEMPERATURE RISE RECORDED ON DIE VS. TIME                   | 172 |

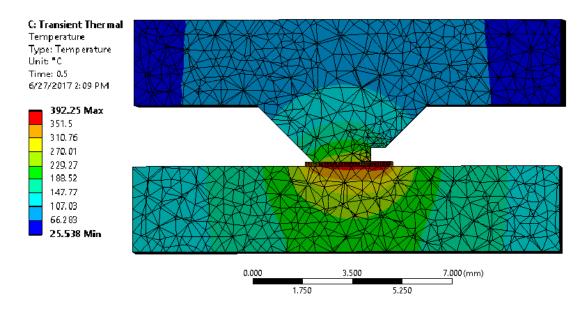

| FIGURE 5.12: TEMPERATURE DISTRIBUTION AT 0.5 SECONDS                             | 172 |

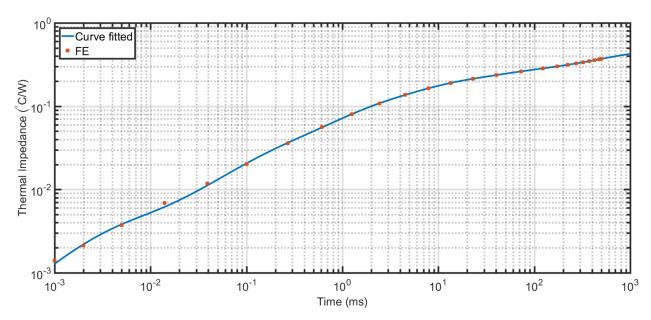

| FIGURE 5.13: THERMAL IMPEDANCE VS PULSE TIME                                     | 173 |

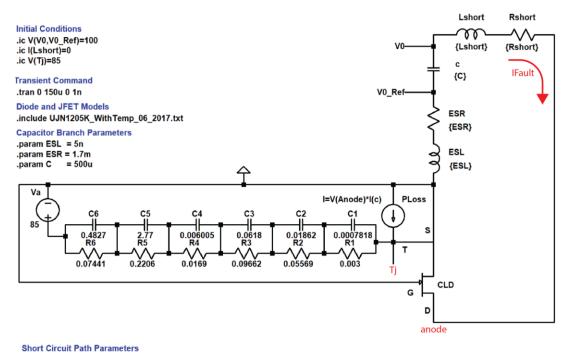

| FIGURE 5.14: CURRENT LIMITER PERFORMANCE SIMULATION CIRCUIT                      | 174 |

| FIGURE 5.15: SIMULATED CLD/FAULT CURRENT (IFAULT)                                | 175 |

| FIGURE 5.16: SIMULATED CLD VOLTAGE (V(ANODE))                                    | 175 |

| FIGURE 5.17: SIMULATED CLD TEMPERATURE (V(TJ))                                   | 176 |

| FIGURE 5.18: CURRENT LIMITER PERFORMANCE SIMULATION CIRCUIT INCLUDING CONVERT    | ΓER |

| DIODES AND FAULT SWITCH EQUIVALENT CIRCUIT (SHOWING $V_0 = 270V$ CASE)           | 177 |

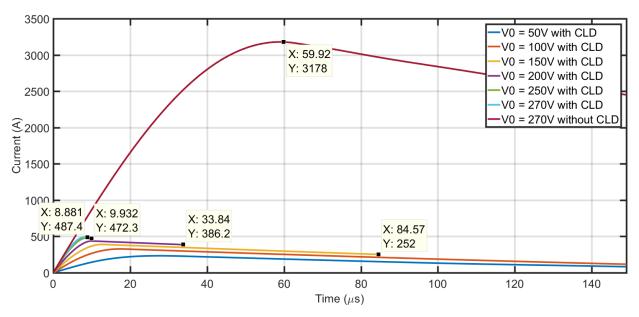

| FIGURE 5.19: SIMULATED FAULT CURRENT (IFAULT)                                    | 178 |

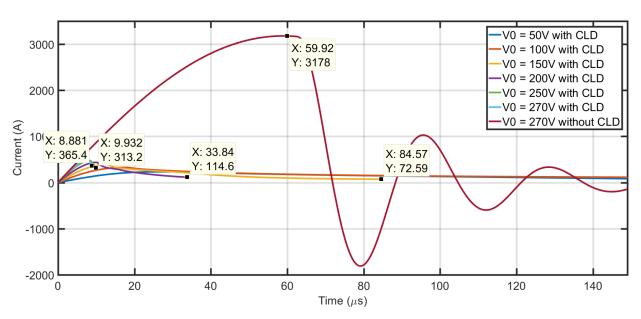

| FIGURE 5.20: SIMULATED CAPACITOR CURRENT (ICAP)                                  | 178 |

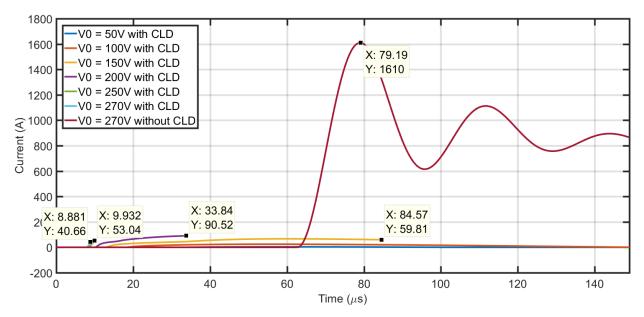

| FIGURE 5.21: SIMULATED DIODES CURRENT (IDIODE)                                   | 179 |

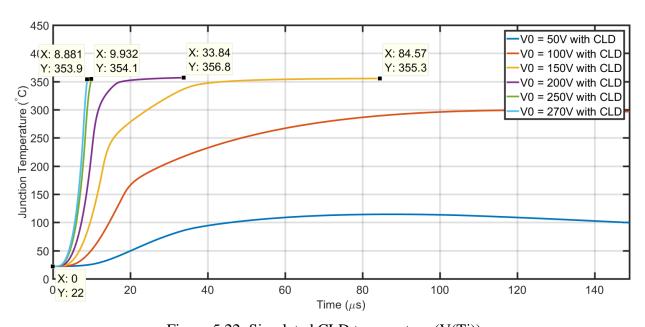

| FIGURE 5.22: SIMULATED CLD TEMPERATURE (V(TJ))                                   | 179 |

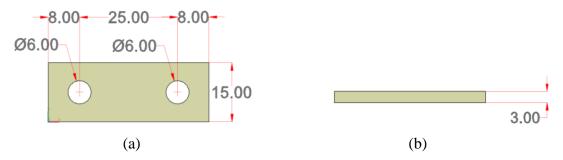

| FIGURE 5.23: TOP SIDE VIEW OF (A) POSITIVE AND (B) NEGATIVE POTENTIAL BUSBARS    | 180 |

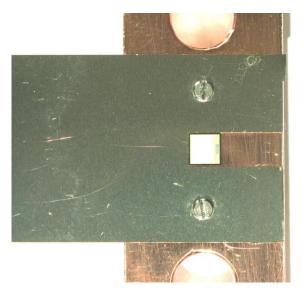

| FIGURE 5.24: (A) TOP AND (B) BOTTOM SIDE VIEWS OF CATHODE STRUCTURE              | 181 |

| FIGURE 5.25: PICTURE OF CERAMIC SCREW USED FOR MECHANICAL SUPPORT                | 181 |

| FIGURE 5.26: PICTURE OF M1 X 5 BRASS SCREW (A) BEFORE, AND (B) AFTER CUTTING AND |     |

| TAPERING                                                                         | 182 |

| FIGURE 5.27: (A) TOP AND (B) BOTTOM SIDE VIEWS OF SIC-JFET DIE                   | 182 |

| FIGURE 5.28: PICTURE OF MANUFACTURED STENCIL                                     | 183 |

| FIGURE 5.29: ZOOMED VIEW OF SURFACES THAT CONTACT THE DIE AFTER POLISHING AND    |     |

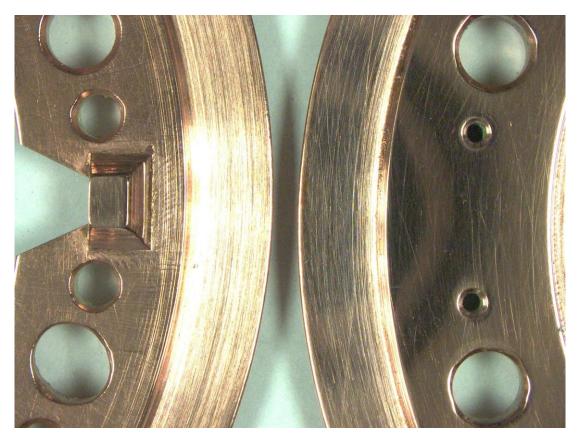

| CLEANING                                                                         | 183 |

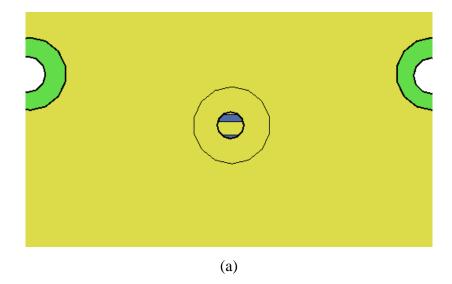

| FIGURE 5.30: VIEW OF DIE POSITIONING SETUP                                       | 184 |

| FIGURE 5.31: (A) EXPECTED AND (B) OBSERVED VIEWS FROM GATE SCREW'S HOLE          | 185 |

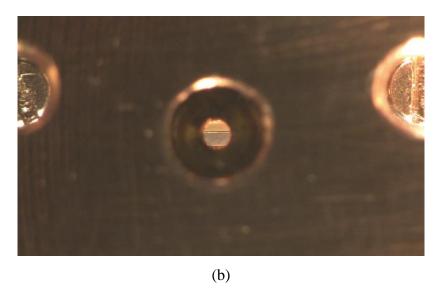

| FIGURE 5.32: BUSBARS AND CAPACITOR INTEGRATION SETUP (A) BEFORE AND (B) AFTER    |     |

| CONNECTION OF NEGATIVE POTENTIAL BUSBAR WITH INTEGRATED CLD                      | 185 |

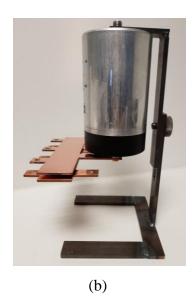

| FIGURE 5.33: FINAL VIEW OF BUSBAR INTEGRATED CURRENT LIMITER CONNECTED TO        |     |

| CONVERTER MODULE, DC CAPACITOR, CABLES, AND DC POWER SUPPLY                      | 186 |

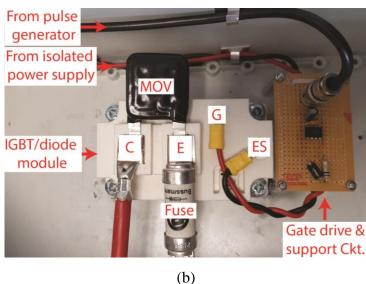

| FIGURE 5.34: (A) PICTURE AND (B) OVERVIEW DIAGRAM OF EXPERIMENT SETUP            | 187 |

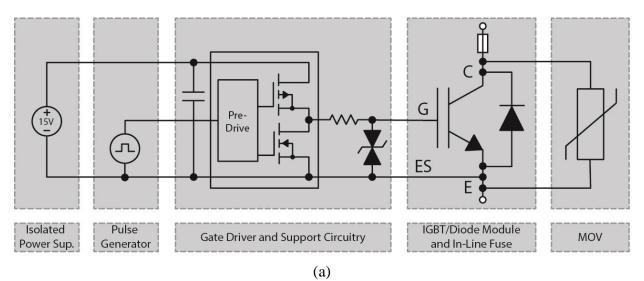

| FIGURE 5.35: (A) SCHEMATIC DIAGRAM, AND (B) PICTURE OF IGBT-BASED FAULT SWITCH   | 188 |

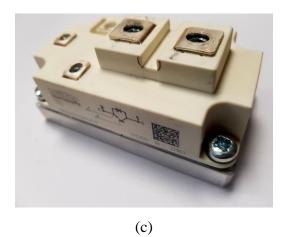

| FIGURE 5.36: PICTURE OF IGBT/DIODE MODULE [22]                                   | 189 |

| FIGURE 5.37: MEASURED IGBT OUTPUT CHARACTERISTICS VS. EXPECTED, SHOWING EQUIVA   |     |

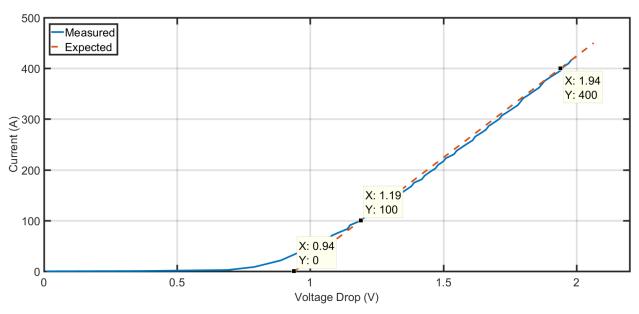

| CIRCUIT FYTR ACTION POINTS                                                       | 189 |

| FIGURE 5.38: PICTURE OF SELECTED MOV                                             | 190     |

|----------------------------------------------------------------------------------|---------|

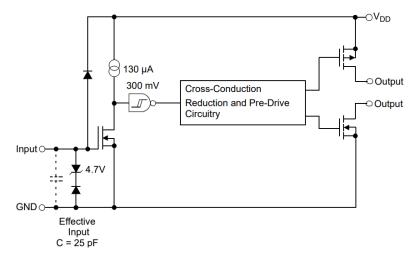

| FIGURE 5.39: FUNCTIONAL BLOCK DIAGRAM OF GATE DRIVER [24]                        | 190     |

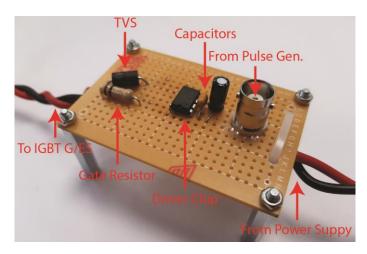

| FIGURE 5.40: PICTURE OF GATE DRIVER AND SUPPORT CIRCUITRY BOARD                  | 191     |

| FIGURE 5.41: (A) BOTTOM SIDE VIEW OF IGBT/DIODE MODULE, (B) TOP SIDE VIEW OF ALU | JMINIUM |

| BASEPLATE, AND (C) SIDE VIEW OF ASSEMBLED MODULE WITH BASEPLATE                  | 192     |

| FIGURE 5.42: IMAGE OF SELECTED FUSE                                              | 192     |

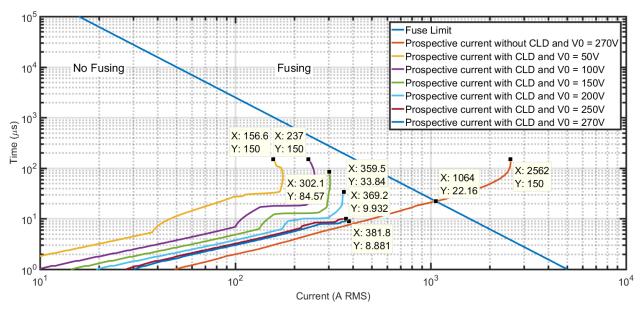

| FIGURE 5.43: PROSPECTIVE CURRENTS VS. TIME COMPARED WITH FUSE $I^2T$ LIMIT       | 193     |

| FIGURE 5.44: COMPARISON OF MEASURED, EXPECTED, AND PROSPECTIVE FAULT BRANC       | H'S     |

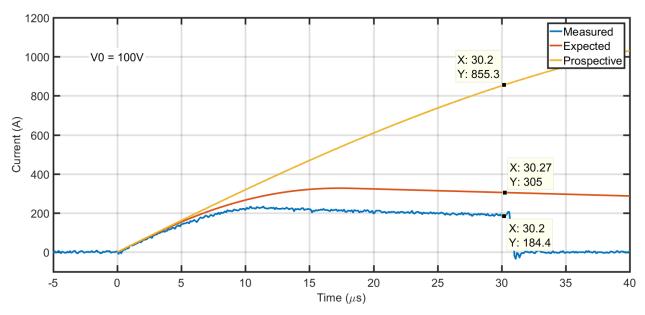

| CURRENT, FOR AN INITIAL DC LINK VOLTAGE OF 100V                                  | 194     |

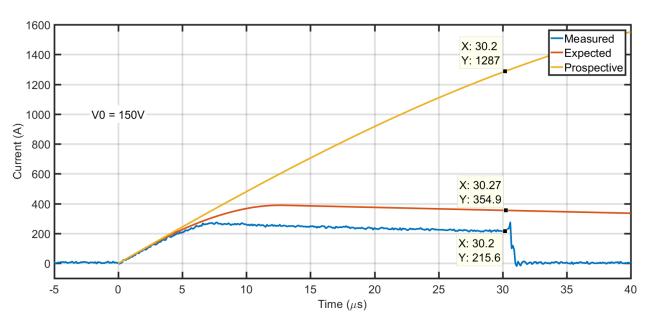

| FIGURE 5.45: COMPARISON OF MEASURED, EXPECTED, AND PROSPECTIVE FAULT BRANC       | H'S     |

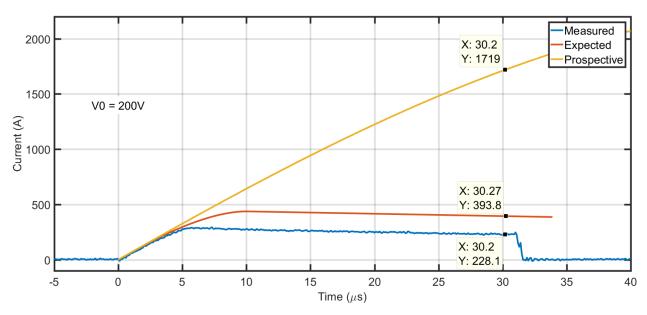

| CURRENT, FOR AN INITIAL DC LINK VOLTAGE OF 150V                                  | 194     |

| FIGURE 5.46: COMPARISON OF MEASURED, EXPECTED, AND PROSPECTIVE FAULT BRANC       | H'S     |

| CURRENT, FOR AN INITIAL DC LINK VOLTAGE OF 200V                                  | 195     |

| FIGURE 5.47: COMPARISON OF CLD'S OUTPUT CHARACTERISES OBTAINED FROM SPICE M      | IODEL   |

| AND MEASURED USING THE TEKTRONIX 371B CURVE TRACER                               | 195     |

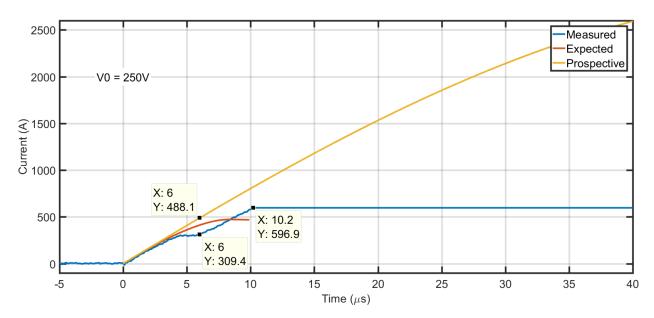

| FIGURE 5.48: COMPARISON OF MEASURED, EXPECTED, AND PROSPECTIVE FAULT BRANC       | H'S     |

| CURRENT, FOR AN INITIAL DC LINK VOLTAGE OF 250V                                  | 196     |

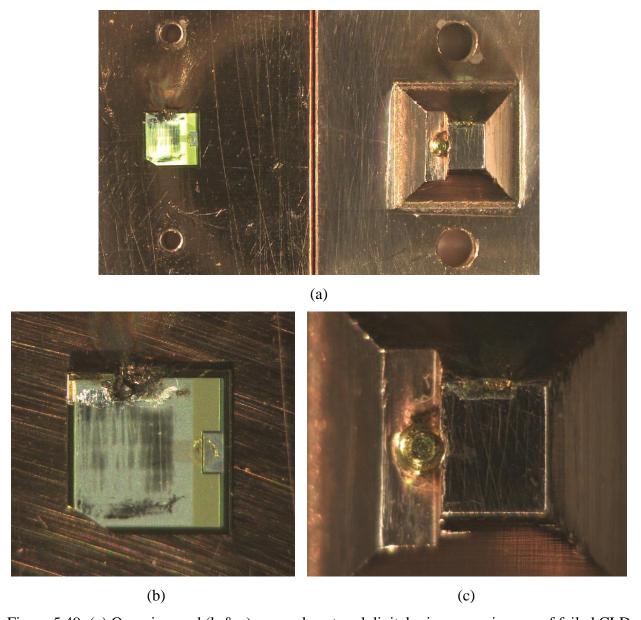

| FIGURE 5.49: (A) OVERVIEW AND (B & C) ZOOMED CAPTURED DIGITAL MICROSCOPE IMA     | GES OF  |

| FAILED CLD                                                                       | 197     |

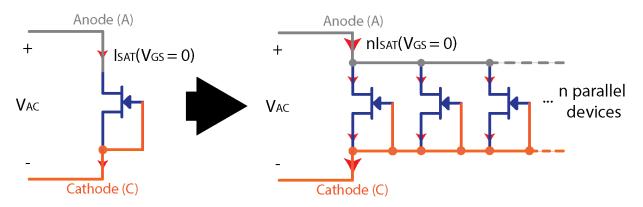

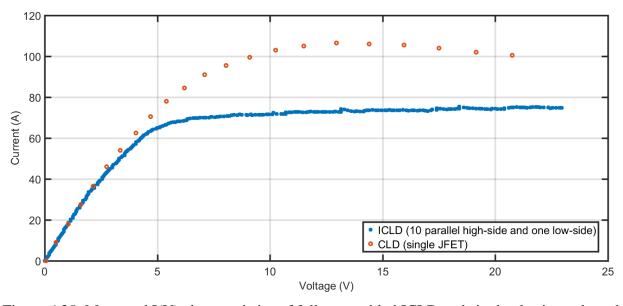

| FIGURE 6.1: ILLUSTRATION OF CURRENT MULTIPLICATION WHEN PARALLEL CONNECTIN       | NG SIC- |

| JFETS WITH V <sub>GS</sub> =0                                                    | 200     |

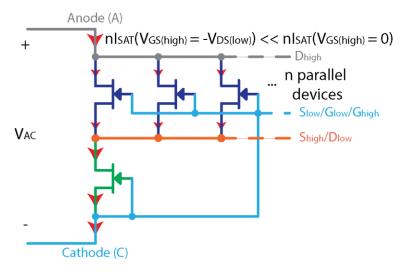

| FIGURE 6.2: SCHEMATIC OF ICLD CIRCUIT TOPOLOGY                                   | 201     |

| FIGURE 6.3: COMPARISON OF DATASHEET AND CURVE FITTED THERMAL IMPEDANCE DA        | ATA OF  |

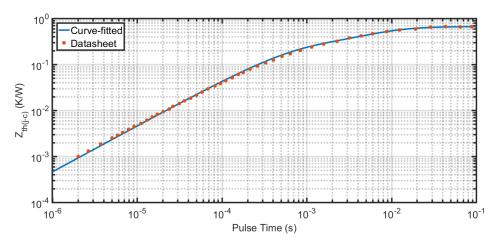

| BOTTOM SIDE DEVICE                                                               | 202     |

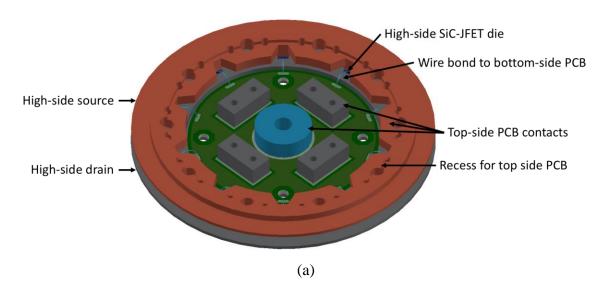

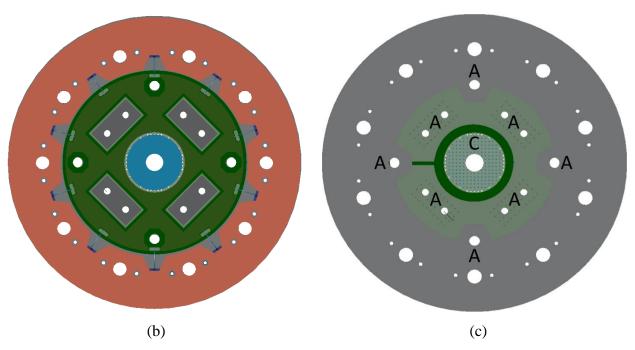

| FIGURE 6.4: (A) ISOMETRIC AND (B) TOP, AND (C) BOTTOM VIEWS OF ICLD PACKAGING    | 204     |

| FIGURE 6.5: EQUIVALENT CIRCUIT OF THE ICLD DEMONSTRATOR                          | 204     |

| FIGURE 6.6: LOCATIONS AND TYPES OF FASTENERS USED IN THE ICLD'S ASSEMBLY         | 205     |

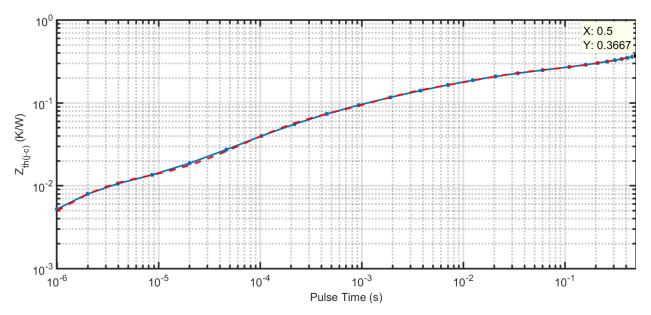

| FIGURE 6.7: (A) ANALYZED GEOMETRY & MESH, AND (B) BOUNDARY CONDITIONS            | 206     |

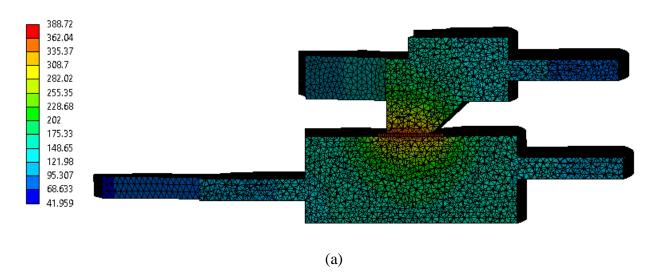

| FIGURE 6.8: TEMPERATURE DISTRIBUTION IN AN (A) CROSS-SECTIONAL AND (B) ISOMET    | RIC     |

| VIEWS OF ANALYZED GEOMETRY AFTER 0.5S                                            | 207     |

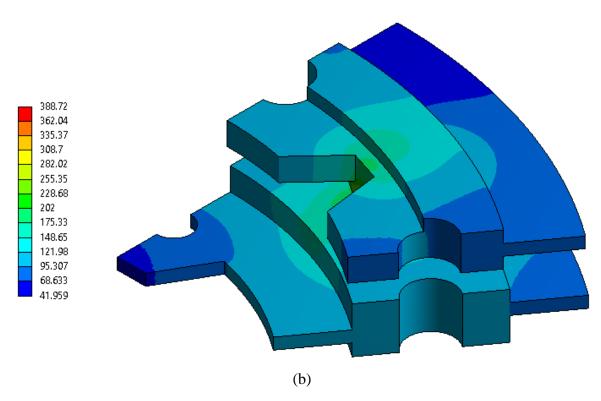

| FIGURE 6.9: MAXIMUM TEMPERATURE RISE IN ICLD STRUCTURE VS. TIME AFTER 1KW HI     | EAT     |

| LOAD AT T=0                                                                      | 207     |

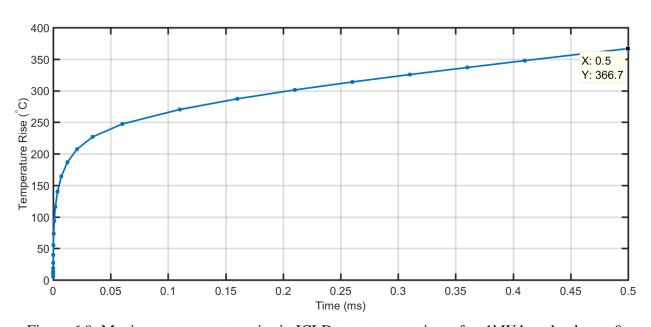

| FIGURE 6.10: FE-BASED THERMAL IMPEDANCE VS. CURVE FITTED FOSTER NETWORK IMP      | PEDANCE |

|                                                                                  | 208     |

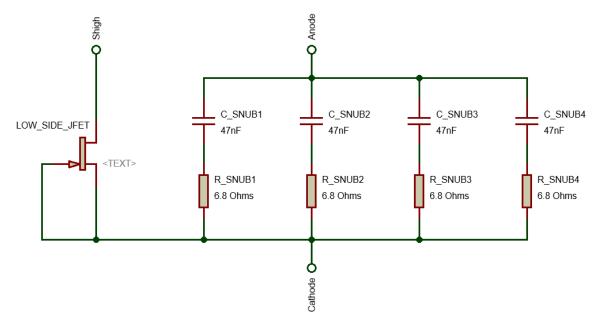

| FIGURE 6.11: SCHEMATIC OF BOTTOM-SIDE PCB                                        | 209     |

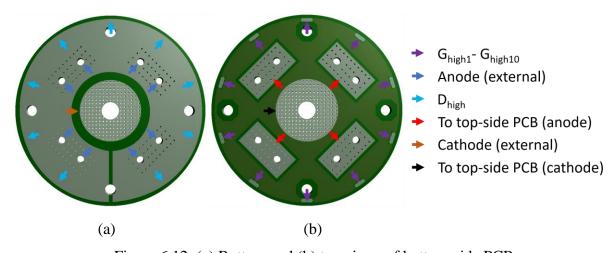

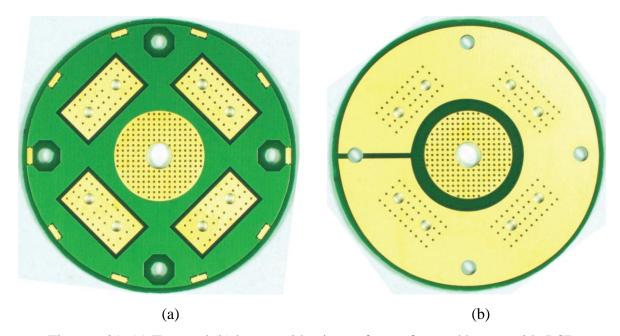

| FIGURE 6.12: (A) BOTTOM AND (B) TOP VIEWS OF BOTTOM-SIDE PCB                     | 209     |

| FIGURE 6.13: SCHEMATIC OF TOP-SIDE PCB                                           | 210     |

| TABLE 2.2: SUMMARY OF SIMULATION PARAMETERS                                         | 46   |

|-------------------------------------------------------------------------------------|------|

| TABLE 2.1: $B_X$ PER COMMUTATION STATE ( $sgnia(t)$ , $sgnib(t)$ , AND $sgnic(t)$ ) | 41   |

| List of Tables                                                                      |      |

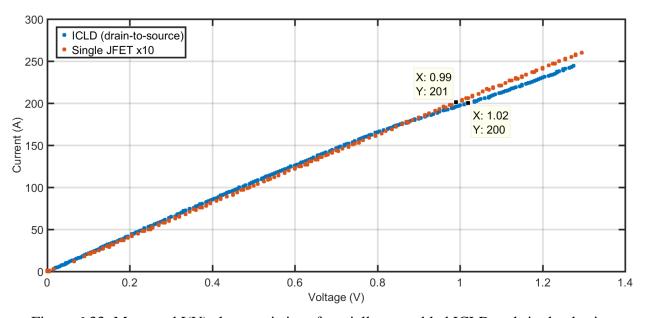

| PLASTIC-PACKAGED JFET WITH $V_{GS} = 0$ (CLD CONFIGURATION)                         | 226  |

| FIGURE 6.35: MEASURED I(V) CHARACTERISTICS OF FULLY ASSEMBLED ICLD AND SINGLE       |      |

| FIGURE 6.34: I(V) CHARACTERISTICS MEASUREMENT SETUP OF FULLY ASSEMBLED ICLD         | 226  |

| PLASTIC-PACKAGED JFET SCALED BY 10 WITH RESPECT TO CURRENT                          | 225  |

| FIGURE 6.33: MEASURED I(V) CHARACTERISTICS OF PARTIALLY ASSEMBLED ICLD AND SING     | LE   |

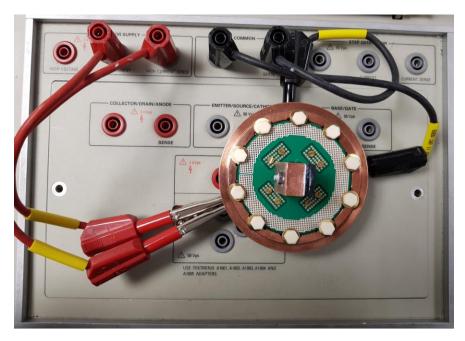

| AND (B) SINGLE PLASTIC PACKAGED JFET                                                |      |

| FIGURE 6.32: I(V) CHARACTERISTICS MEASUREMENT SETUP OF (A) PARTIALLY ASSEMBLED I    |      |

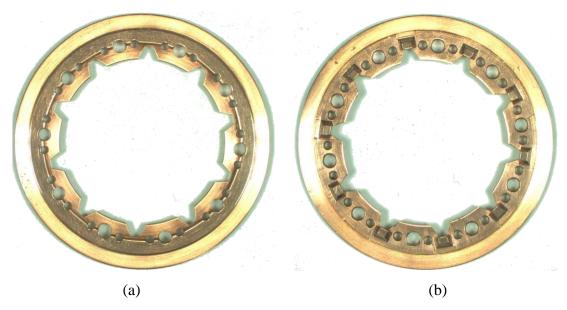

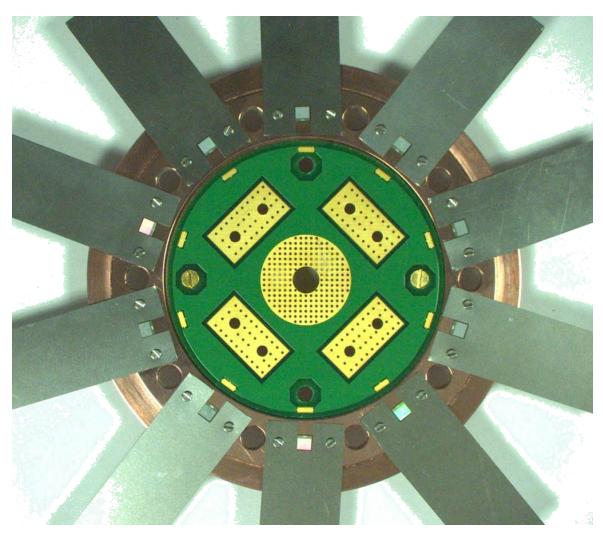

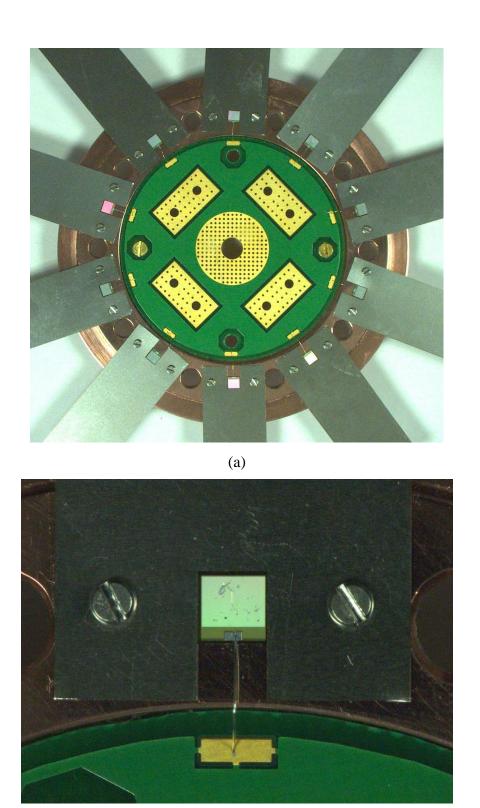

| FIGURE 6.31: (A) TOP AND (B) ISOMETRIC PICTURE OF ASSEMBLED ICLD                    |      |

| SCREWS CAN BE REMOVED, AND REMAINING COMPONENTS ASSEMBLED                           |      |

| FIGURE 6.30: PICTURE OF ICLD STRUCTURE HELD BY BINDER CLIPS SO THAT THE CERAMIC     |      |

| FIGURE 6.29: PICTURE OF ICLD AFTER ATTACHING HIGH-SIDE SOURCE STRUCTURE             | 221  |

| FIGURE 6.28: (A) FULL SCALE AND (B) ZOOMED VIEW OF STRUCTURE AFTER WIRE BONDING .   | 220  |

| FIGURE 6.27: VIEW OF DIE POSITIONING SETUP                                          | 219  |

| CLEANING                                                                            |      |

| FIGURE 6.26: ZOOMED VIEW OF SURFACES THAT CONTACT THE DIE AFTER POLISHING AND       |      |

| FIGURE 6.25: PICTURE OF M4 X 20 CERAMIC FASTENER USED IN ICLD ASSEMBLY              | 217  |

| FIGURE 6.24: TOP VIEW OF MANUFACTURED (A) BOTTOM, AND (B) TOP STENCILS              | 217  |

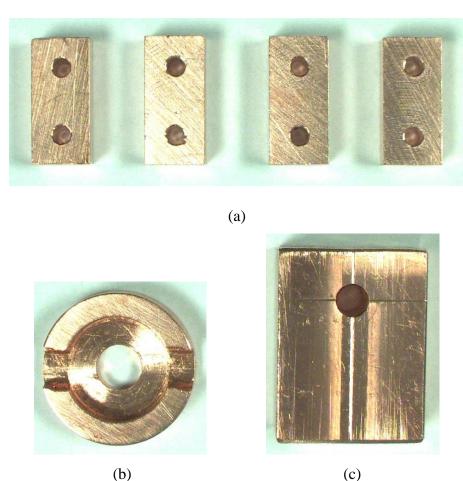

| SIDE PCBS, AND (C) THERMAL MASS FOR LOW-SIDE JFET                                   | 216  |

| CIRCULAR BLOCKS FOR ANODE AND CATHODE CONNECTION BETWEEN TOP AND BOTT               | OM   |

| FIGURE 6.23: OTHER MANUFACTURED ICLD COPPER STRUCTURES: (A) RECTANGULAR AND (I      | B)   |

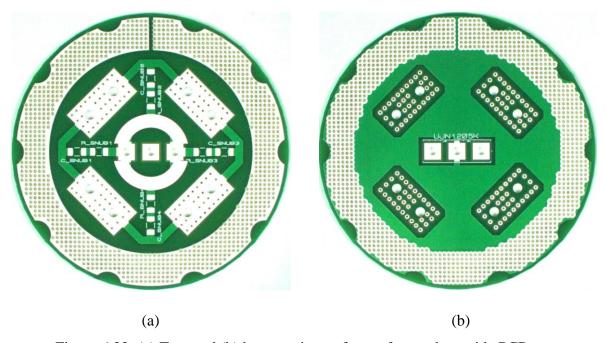

| FIGURE 6.22: (A) TOP, AND (B) BOTTOM VIEWS OF MANUFACTURED TOP-SIDE PCB             | 215  |

| FIGURE 6.21: (A) TOP, AND (B) BOTTOM SIDE VIEWS OF MANUFACTURED BOTTOM-SIDE PCB     | 215  |

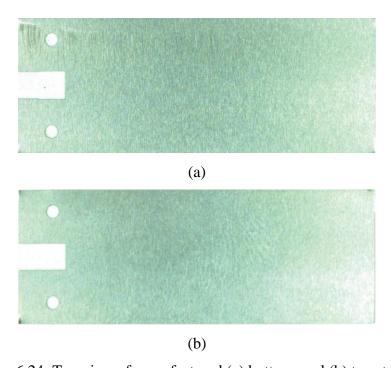

| TIGORE 0.20. (1) TOT, THE (B) BOTTOM VIEWS OF IMMINOTREFORED INOT SIDE DRAMVSTROE   |      |

| FIGURE 6.20: (A) TOP, AND (B) BOTTOM VIEWS OF MANUFACTURED HIGH-SIDE DRAIN STRUC    |      |

| STRUCTURE                                                                           | 214  |

| FIGURE 6.19: (A) TOP AND (B) BOTTOM VIEWS OF MANUFACTURED HIGH-SIDE SOURCE          | 212  |

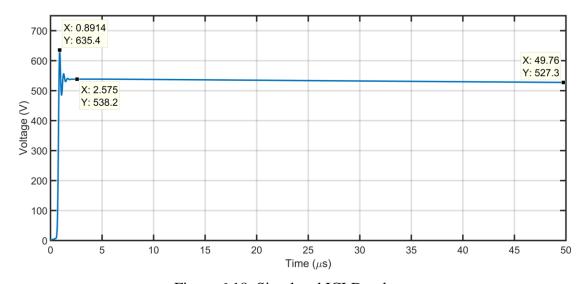

| FIGURE 6.18: SIMULATED ICLD VOLTAGE                                                 |      |

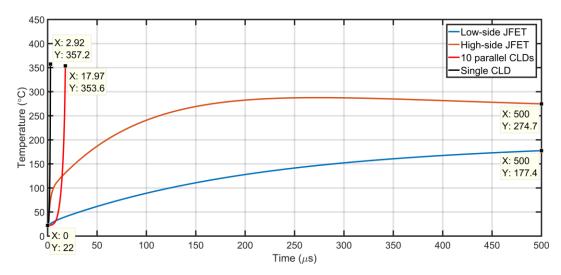

| FIGURE 6.17: SIMULATED JFETS TEMPERATURES                                           |      |

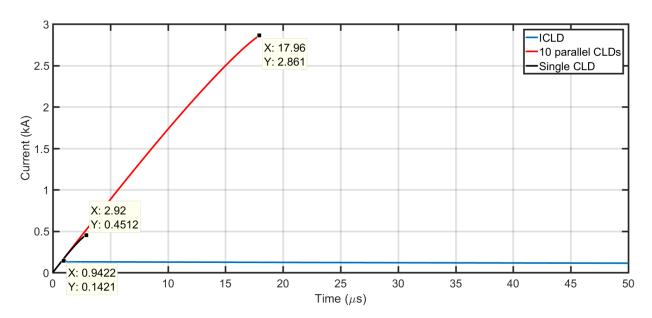

| FIGURE 6.16: SIMULATED ICLD CURRENT                                                 |      |

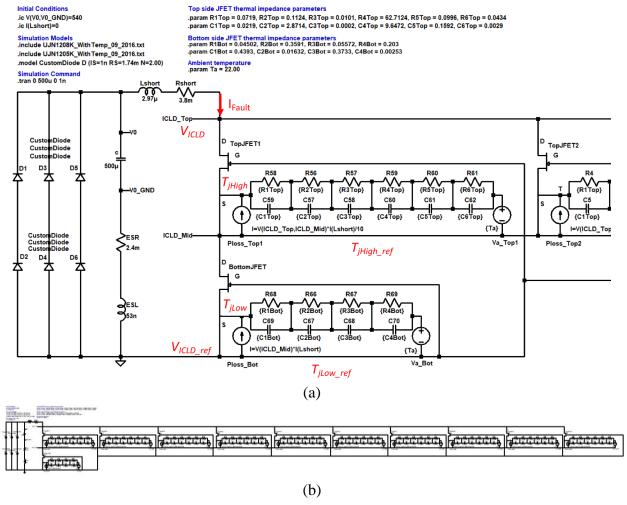

| FIGURE 6.15: (A) ZOOMED, AND (B) FULL ICLD PERFORMANCE SIMULATION CIRCUIT           |      |

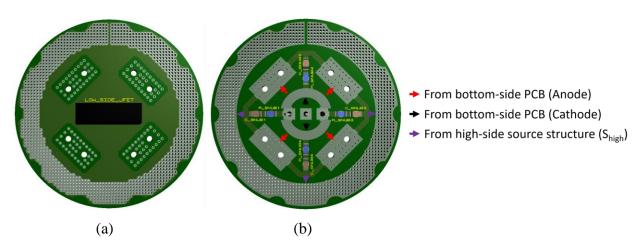

| FIGURE 6.14: (A) TOP AND (B) BOTTOM SIDE VIEWS OF TOP-SIDE PCB                      | 2.10 |

| TABLE 2.3: RECOMMENDED CABLE SIZE AND MAXIMUM CURRENT AT UP TO 70°C (FROM N | IIL-STD- |

|-----------------------------------------------------------------------------|----------|

| 975)                                                                        | 47       |

| TABLE 2.4: FOSTER THERMAL NETWORK CURVE FITTING PARAMETERS                  | 80       |

| TABLE 3.1: COMPARISON OF MEASURED AND DATASHEET THYRISTOR PARAMETERS        | 94       |

| TABLE 4.1: SUMMARY OF SPICE MODEL'S PARAMETERS                              | 136      |

| TABLE 4.2: FOSTER EQUIVALENT THERMAL CIRCUIT PARAMETERS                     | 155      |

| TABLE 5.1: EQUIVALENT FOSTER THERMAL NETWORK PARAMETERS                     | 173      |

| TABLE 6.1: FOSTER NETWORK CURVE FITTING PARAMETERS OF BOTTOM SIDE DEVICE    | 203      |

| TABLE 6.2: FOSTER NETWORK CURVE FITTING PARAMETERS FOR HIGH-SIDE DEVICES    | 208      |

# **List of Nomenclatures**

# Chapter 2:

| Symbol     | Definition                                                                    | Unit  |

|------------|-------------------------------------------------------------------------------|-------|

| Α          | Conductor cross-sectional area                                                | $m^2$ |

| $A_n$      | Initial conditions constants, where $n = 1, 2, 3$                             | -     |

| C          | Capacitance                                                                   | F     |

| $C_i$      | Capacitance of Foster thermal network's $i^{th}$ branch, where $i = 1, 2, 3,$ | F     |

| D          | Distance between two cables                                                   | m     |

| ESL        | Equivalent series inductance                                                  | Н     |

| ESR        | Equivalent series resistance                                                  | Ω     |

| $I_0$      | Initial current                                                               | A     |

| $I_{0x}$   | Initial current of phase $x$ , where $x = a$ , $b$ , or $c$                   | A     |

| $I_1$      | Initial current at diodes conducting stage                                    | A     |

| $i_{Cap0}$ | Initial capacitor branch's current                                            | A     |

| $i_{CB}$   | Capacitor branch current during diodes conducting stage                       | A     |

| $i_{DB}$   | Current during diodes blocking stage                                          | A     |

| $i_{DL}$   | Current through the lower diodes of a converter's leg (D2, D4, and D6)        | A     |

| $i_{Dn}$    | Current of diode <i>n</i>                                                    | A  |

|-------------|------------------------------------------------------------------------------|----|

| $i_{DU}$    | Current through the upper diodes of a converter's leg (D1, D3, and D5)       | A  |

| $i_{FB}$    | Fault branch current during diodes conducting stage                          | A  |

| $I_S$       | Diode saturation current                                                     | A  |

| $i_{S0}$    | Initial rectified AC side current                                            | A  |

| $I_{t_0x}$  | Initial current of phase $x$ at $t_0$ , where $x = a$ , $b$ , or $c$         | A  |

| $i_x$       | Current of phase $x$ , where $x = a$ , $b$ , or $c$                          | A  |

| $I_{xRMS}$  | Root-mean-square current of phase x, where $x = a$ , b, or c                 | A  |

| j           | Imaginary $j = \sqrt{-1}$                                                    | -  |

| L           | Cable length                                                                 | m  |

| $L_{self}$  | Cable self-inductance                                                        | Н  |

| $L_{short}$ | Inductance of the short-circuit path                                         | Н  |

| $L_{total}$ | Loop inductance                                                              | Н  |

| M           | Mutual inductance                                                            | Н  |

| n           | Diode emission coefficient                                                   | -  |

| P           | Active or real power                                                         | W  |

| $P_{nom}$   | Nominal real output power                                                    | W  |

| Q           | Reactive or imaginary power                                                  | Va |

| R           | Electrical resistance                                                        | Ω  |

| $R_i$       | Resistance of Foster thermal network's $i^{th}$ branch, where $i = 1, 2, 3,$ | Ω  |

| $R_S$       | Diode equivalent series resistance                                           | Ω  |

| $R_{short}$ | Resistance of the short-circuit path                                         | Ω  |

| S           | Apparent power                                                               | VA |

| t           | Time                                                                         | S  |

| $t_0$       | Time at which DC side voltage is zero                                        | S  |

| $t_b$         | Diodes blocking to conducting time boundary                                   |             |  |

|---------------|-------------------------------------------------------------------------------|-------------|--|

| $V_0$         | Initial Voltage                                                               | V           |  |

| $V_1$         | Initial voltage at diodes conducting stage                                    | V           |  |

| $V_D$         | Diode voltage drop                                                            | V           |  |

| $V_D'$        | Diode voltage accounting for series resistance                                | V           |  |

| $V_{DC}$      | DC side voltage                                                               | V           |  |

| $V_{j}$       | Diode equivalent forward voltage                                              | V           |  |

| $V_m$         | Peak line to neutral voltage                                                  | V           |  |

| $V_T$         | Diode thermal voltage (25.7mV at 25°C)                                        | V           |  |

| $v_{x}$       | Voltage of phase $x$ , where $x = a$ , $b$ , or $c$                           | V           |  |

| $V_{xRMS}$    | Root-mean-squared voltage of phase $x$ , where $x = a$ , $b$ , or             | V           |  |

| Z             | Line impedance                                                                | Ω           |  |

| $Z_{th(J-c)}$ | Junction to case thermal impedance                                            | °C/W        |  |

| α             | Phase angle of $v_a$ at which the fault occurs                                | rad         |  |

| β             | Damping factor                                                                | -           |  |

| $\beta_{xn}$  | Commutation state coefficient, where $x = a$ , $b$ , or $c$ and $n = 1, 2, 3$ | -           |  |

| $\Delta T_j$  | Junction temperature rise                                                     | °C          |  |

| $\mu$         | Magnetic permeability of material                                             | H/m         |  |

| ρ             | Electrical resistivity                                                        | $\Omega$ .m |  |

| $\phi$        | Impedance phase shift                                                         | rad         |  |

| $\phi_0$      | Impedance phase shift prior to fault instance                                 | rad         |  |

| ω             | Fundamental frequency                                                         | rad/s       |  |

| $\omega_r$    | Ringing frequency                                                             | rad/s       |  |

| $\omega_o$    | Resonance frequency                                                           | rad/s       |  |

# Chapter 4:

| Symbol     | Definition                                                                    | Unit  |

|------------|-------------------------------------------------------------------------------|-------|

| A          | Conductor cross-sectional area                                                | $m^2$ |

| $A_n$      | Initial conditions constants, where $n = 1, 2, 3$                             | -     |

| C          | Capacitance                                                                   | F     |

| $C_i$      | Capacitance of Foster thermal network's $i^{th}$ branch, where $i = 1, 2, 3,$ | F     |

| D          | Distance between two cables                                                   | m     |

| ESL        | Equivalent series inductance                                                  | Н     |

| ESR        | Equivalent series resistance                                                  | Ω     |

| $I_0$      | Initial current                                                               | A     |

| $I_{0x}$   | Initial current of phase $x$ , where $x = a$ , $b$ , or $c$                   | A     |

| $I_1$      | Initial current at diodes conducting stage                                    | A     |

| $i_{Cap0}$ | Initial capacitor branch's current                                            | A     |

| $i_{CB}$   | Capacitor branch current during diodes conducting stage                       | A     |

| $i_{DB}$   | Current during diodes blocking stage                                          | A     |

| $i_{DL}$   | Current through the lower diodes of a converter's leg (D2, D4, and D6)        | A     |

| $i_{Dn}$   | Current of diode <i>n</i>                                                     | A     |

| $i_{DU}$   | Current through the upper diodes of a converter's leg (D1, D3, and D5)        | A     |

| $i_{FB}$   | Fault branch current during diodes conducting stage                           | A     |

| $I_S$      | Diode saturation current                                                      | A     |

| $i_{S0}$   | Initial rectified AC side current                                             | A     |

| $I_{t_0x}$ | Initial current of phase $x$ at $t_0$ , where $x = a$ , $b$ , or $c$          | A     |

| $i_{\chi}$ | Current of phase $x$ , where $x = a$ , $b$ , or $c$                           | A     |

| $I_{xRMS}$ | Root-mean-square current of phase x, where $x = a$ , b, or c                  | A     |

| j          | Imaginary $j = \sqrt{-1}$                                                     | -     |

| L           | Cable length                                                                 | m   |

|-------------|------------------------------------------------------------------------------|-----|

| $L_{self}$  | Cable self-inductance                                                        | Н   |

| $L_{short}$ | Inductance of the short-circuit path                                         | Н   |

| $L_{total}$ | Loop inductance                                                              | Н   |

| M           | Mutual inductance                                                            | Н   |

| n           | Diode emission coefficient                                                   | -   |

| P           | Active or real power                                                         | W   |

| $P_{nom}$   | Nominal real output power                                                    | W   |

| Q           | Reactive or imaginary power                                                  | Var |

| R           | Electrical resistance                                                        | Ω   |

| $R_i$       | Resistance of Foster thermal network's $i^{th}$ branch, where $i = 1, 2, 3,$ | Ω   |

| $R_S$       | Diode equivalent series resistance                                           | Ω   |

| $R_{short}$ | Resistance of the short-circuit path                                         | Ω   |

| S           | Apparent power                                                               | VA  |

| t           | Time                                                                         | S   |

| $t_0$       | Time at which DC side voltage is zero                                        | S   |

| $t_b$       | Diodes blocking to conducting time boundary                                  | S   |

| $V_0$       | Initial Voltage                                                              | V   |

| $V_1$       | Initial voltage at diodes conducting stage                                   | V   |

| $V_D$       | Diode voltage drop                                                           | V   |

| $V_D'$      | Diode voltage accounting for series resistance                               | V   |

| $V_{DC}$    | DC side voltage                                                              | V   |

| $V_{j}$     | Diode equivalent forward voltage                                             | V   |

| $V_m$       | Peak line to neutral voltage                                                 | V   |

| $V_{T}$     | Diode thermal voltage (25.7mV at 25°C)                                       | V   |

| $v_x$             | Voltage of phase $x$ , where $x = a$ , $b$ , or $c$                            |             |

|-------------------|--------------------------------------------------------------------------------|-------------|

| $V_{xRMS}$        | Root-mean-squared voltage of phase $x$ , where $x = a$ , $b$ , or              | V           |

| Z                 | Line impedance                                                                 | Ω           |

| $Z_{th(J-c)}$     | Junction to case thermal impedance                                             | °C/W        |

| α                 | Phase angle of $v_a$ at which the fault occurs                                 | rad         |

| β                 | Damping factor                                                                 | -           |

| $\beta_{xn}$      | Commutation state coefficient, where $x = a$ , $b$ , or $c$ and $n = 1$ , 2, 3 | -           |

| $\Delta T_j$      | Junction temperature rise                                                      | °C          |

| μ                 | Magnetic permeability of material                                              | H/m         |

| ρ                 | Electrical resistivity                                                         | $\Omega$ .m |

| $\phi$            | Impedance phase shift                                                          | rad         |

| $\phi_0$          | Impedance phase shift prior to fault instance                                  | rad         |

| ω                 | Fundamental frequency                                                          | rad/s       |

| $\omega_r$        | Ringing frequency                                                              | rad/s       |

| $\omega_{\alpha}$ | Resonance frequency                                                            | rad/s       |

## **Chapter 1:** Introduction

This chapter is organized as follows: in the first section, factors that have historically limited the use of DC-based power systems are discussed. This section also includes a review of recent technology developments which have eliminated those factors. In the second section, the benefits of using DC networks are reviewed. In the third section, the use of DC in power systems of modern aircrafts is described. In the fourth and fifth sections, challenges hindering wider adoption of DC-based power systems for aircrafts are presented. In the sixth section, an outline of this thesis is presented. Finally, in the seventh section, a list of peer-reviewed publications which have resulted from this work is provided.

#### 1.1. The Uprising of DC: Historical Background and Technology Influence

Although most power systems today use AC to power heavy loads instead of DC, there has been an old and ongoing debate on the benefits and shortcomings of each. This debate goes back to the days of Edison and Tesla, who each advocated their preferred systems. It is obvious that Tesla, whose AC system has been the most commonly used had won. However, many arguments that resulted in the adoption of his system are no longer valid, and DC is now being widely considered in many high-power applications.

Previously, the lack of techniques for stepping up generated DC voltages for transmission required that generation occur close to the loads, so that power losses in transmission was minimized. The noise and pollution from generation made this impractical. It also meant that power had to be generated and transmitted at the same low voltage used by the loads, or slightly higher to account for voltage drop in transmission, because DC voltages could not be easily stepped up or down. This resulted in the distribution lines having to be made of thick and expensive wires to handle the large current with minimal losses, which was another important argument against DC. In addition, the lack of methods to convert electricity from AC to DC and vice versa meant that power had to be generated in DC and only DC loads could be used. This was problematic since DC motors and generators required brushes to commutate the current, which restricted their reliability, lifespan, and maximum speeds [1].

With modern power electronics, DC voltages can be stepped up as high as desired, resulting in more efficient power transmission with thinner cables than those used in AC. DC voltages of

600kV are being considered for new installations, compared to the typical 400kV AC transmission voltage [2]. Nowadays, power can also be efficiently converted from DC to AC and vice versa to accommodate different requirements of loads, sources, and auxiliaries. So that power can be generated in AC using synchronous generators or DC from solar arrays, combined and converted to High Voltage DC (HVDC) for transmission, then back to AC at the loads. It may also be advantageous to directly deliver DC power to loads instead of AC [3]. This is because most loads nowadays can more efficiently and easily be powered using DC.

At the times of Edison and Tesla, the most power consuming loads were AC motors, which thanks to modern power electronics can now be more efficiently powered with DC using motor drivers. Many other loads can more easily and efficiently be powered with DC without conversion, like modern electronics, LED lighting, and electric vehicles. Likewise, the sources of electricity have changed: a large portion of power is now generated from renewable energy sources, such as solar and wind, which can more easily be interfaced to DC networks. Furthermore, modern distribution networks are likely to contain energy storage devices, such as batteries and supercapacitors, which can be connected to DC networks without the need for inverters, rectifiers, or synchronization.

## 1.2. Advantages and Shortcomings of DC-based Power System Architectures

One of the key advantages of DC networks is that for the same conductor size DC power transmission is typically more efficient than AC. This is partially due to the absence of skin effect, which results in an increase of transmission lines resistances in AC, as current is constrained to the outer portions of the conductors. This effect can be minimized by using cable laminations or twisted bundles of thinner isolated conductors (litz wires) [4], at the expense of higher monetary cost. In addition, AC lines must typically carry both active (useful) power and reactive (useless) power, while DC lines naturally only carry active power. Therefore, there are no power losses due to the transmission of reactive power in DC systems, which can be substantial in AC. In addition to the improved transmission efficiency, cables used in DC networks require lower insulation voltages for the same power ratings. Transmission cables are rated based on the highest voltages their dielectric materials can isolate, which is the sinusoidal peak voltage in AC and the average voltage in DC. However, power transferred is proportional to the Root Mean Square (RMS) values,

which is 0.707 of the peak value in AC and the same DC voltage in DC. Therefore, a cable rated for certain voltage can carry around 1.4 the AC power, if used in a DC network.

Despite the preceding advantages, the use of DC networks is not always desired, especially when considering the monetary cost and difficulty of protection. Due to the high cost of power conversion and control equipment required, it is only economically viable to use DC for long distance power transmission. This distance is typically around 400-600km for overhead lines and 30-40km for cable lines [2]. The use of DC below these lengths is not economical because the cost savings from increased efficiency does not make up for the higher equipment costs. A more serious problem with DC networks is the difficulty of protection. Unlike AC power, DC power does not periodically go to zero, which means that an arc resulting from breaking a DC circuit is not eventually extinguished by a zero crossing, like in AC. Instead, if not extinguished by other means, like gases or liquids, the arc is maintained in the circuit. This can result in a fire hazard and damage to the contacts of the breakers. Thus, DC systems require special power controllers like Solid-State Circuit Breakers (SSCBs) for protection.

#### **1.3.** DC in Aircrafts Power Systems